## 特長

- 出力電流: 4A

- 入力電圧範囲: 2.25V~5.5V

- 低出力リップルのBurst Mode®動作:  $I_Q = 75\mu A$

- 出力電圧精度: ±1%

- 出力電圧: 最小0.6V

- 高効率: 最大95%

- 低ドロップアウト動作: デューティ・サイクル100%

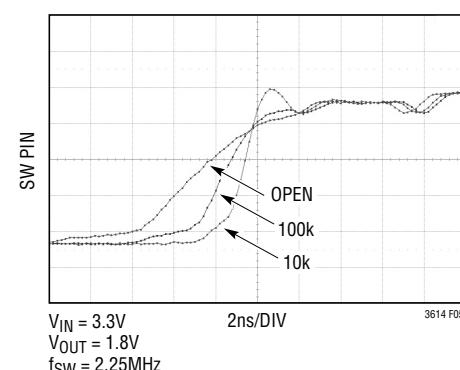

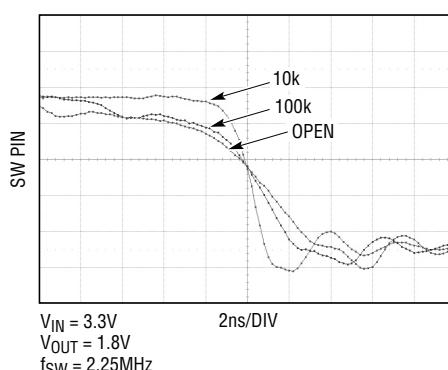

- SWノードのスルーレートをプログラムできるので、ノイズとEMIを低減

- 調整可能なスイッチング周波数: 最大4MHz

- オプションの内部補償付き

アクティブ電圧ポジショニング(AVP)

- パルススキップ動作/強制連続動作/バーストクランプを調整可能なBurst Mode動作を選択可能

- プログラム可能なソフトスタート

- 起動トラッキングまたは外部リファレンス用の入力

- DDRメモリ・モード、 $I_{Q\text{OUT}} = \pm 3A$

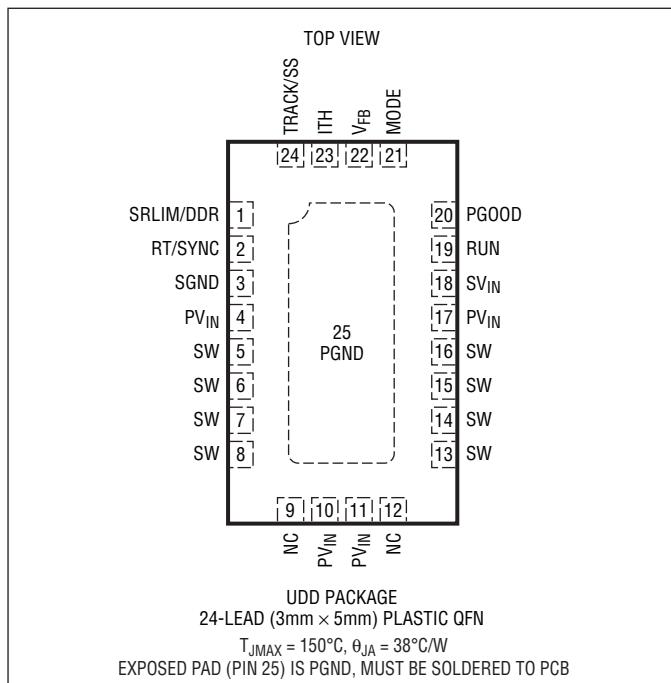

- 熱特性が改善された24ピン3mm×5mm QFNパッケージ

## アプリケーション

- ポイントオブロード電源

- 分配型電源

- 携帯型コンピュータ・システム

- DDRメモリの終端

- ハンドヘルド機器

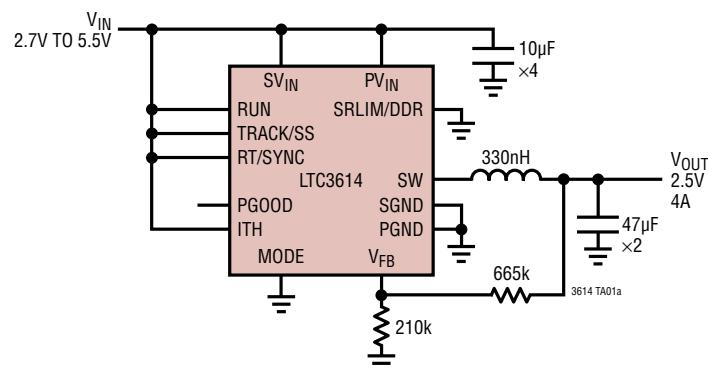

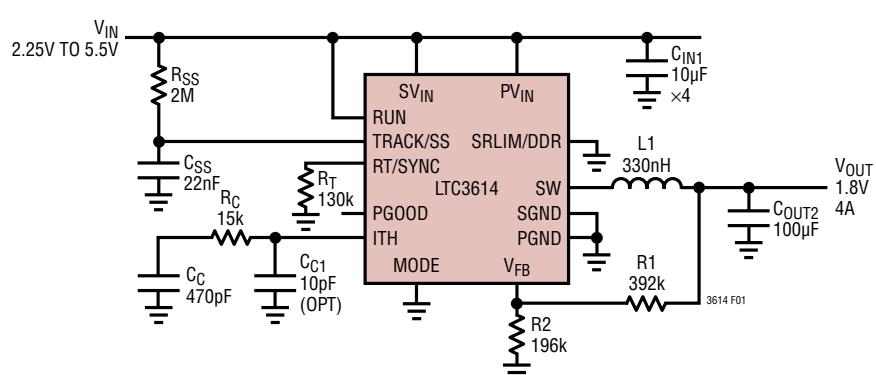

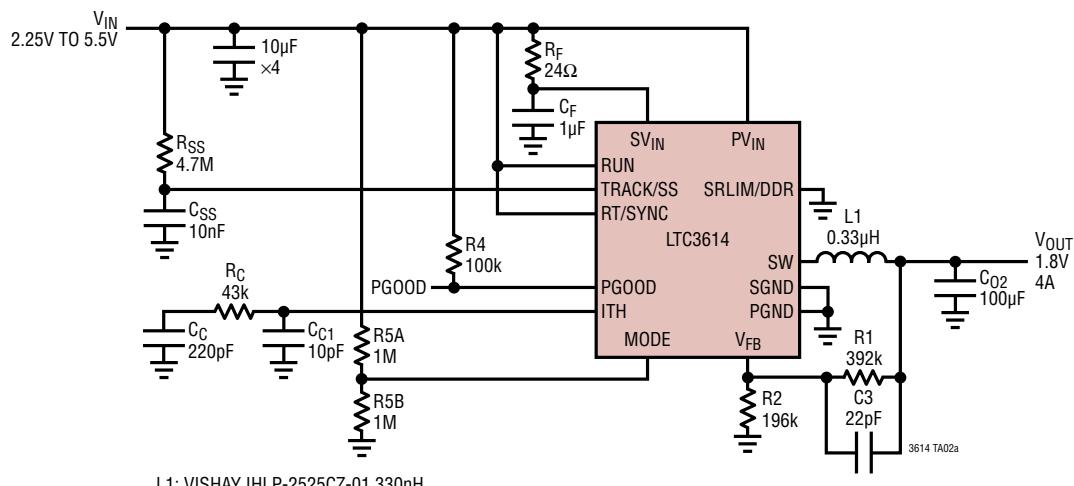

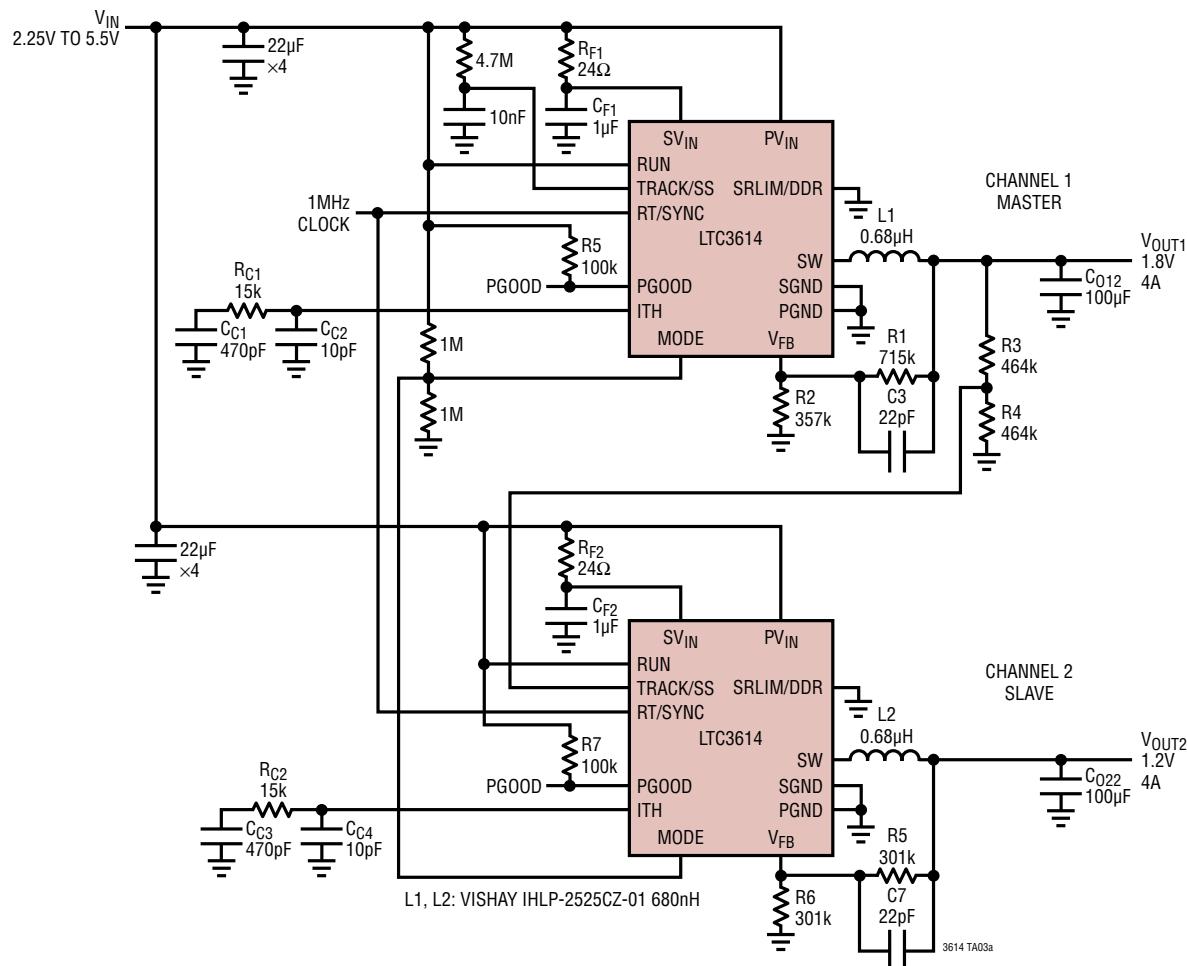

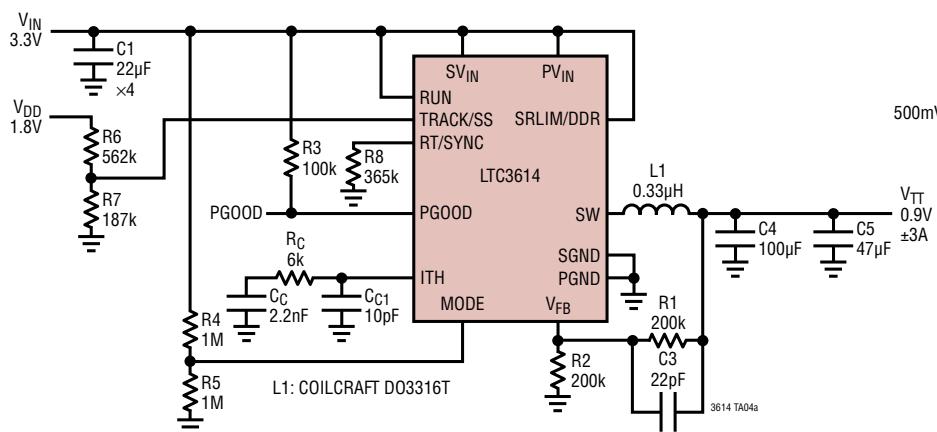

## 標準的応用例

## 概要

LTC®3614は、電流モードの固定周波数アーキテクチャを採用した低静止電流モノリシック同期整流式降圧レギュレータです。スリープ・モードでの無負荷時DC電源電流はわずか75μAでありながら、無負荷時に出力電圧を維持し(Burst Mode動作)、シャットダウン時には電流がゼロまで減少します。LTC3614は入力電圧範囲が2.25V~5.5Vなので、1本のリチウムイオン・バッテリや固定低電圧入力のアプリケーションに最適です。デューティ・サイクル100%が可能なので低ドロップアウト動作が確保され、バッテリ駆動システムでの動作時間が長くなります。

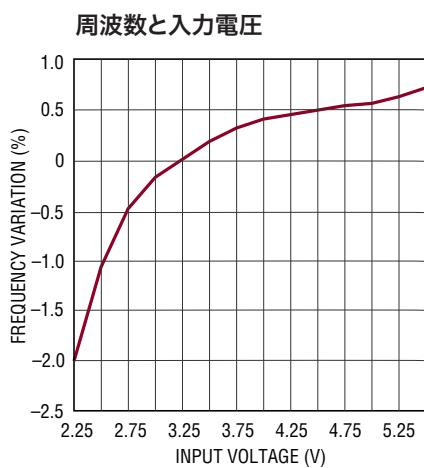

動作周波数は最大4MHzまで外部設定可能なので、小型の表面実装インダクタを使用できます。スイッチング・ノイズに敏感なアプリケーション向けに、LTC3614は最大4MHzの外部クロックに同期可能です。

LTC3614での強制連続モード動作により、ノイズおよびRF干渉が減少します。調整可能な補償回路により、広範な負荷および出力コンデンサにわたってトランジエント応答を最適化することができます。

内部同期スイッチによって効率が向上し、外付けのキャッチ・ダイオードが不要になるので、外付け部品と基板面積を節減できます。LTC3614は熱特性が改善されたリードレス24ピン3mm×5mm QFNパッケージで供給されます。

LT、LT、LTC、LTM、Linear Technology、LinearのロゴおよびBurst Modeはリニアテクノロジー社の登録商標です。他の全ての商標はそれぞれの所有者に所有権があります。6580258、5481178、5994885、6304066、6498466、6611131を含む米国特許により保護されています。

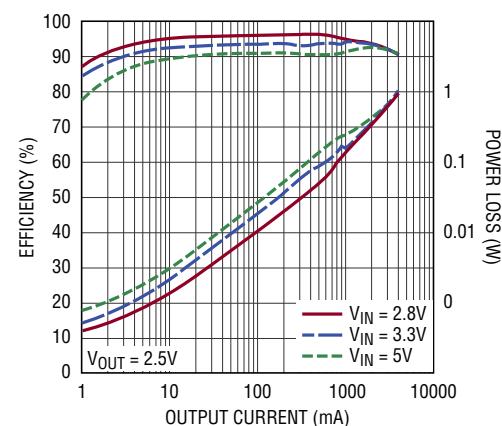

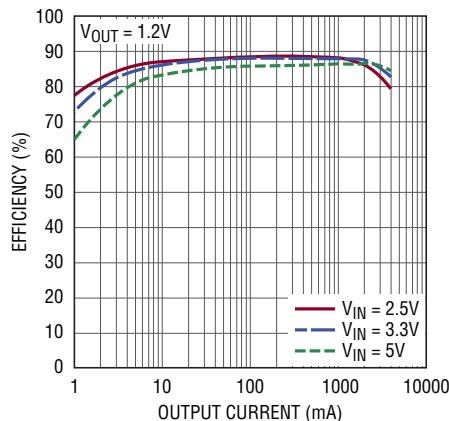

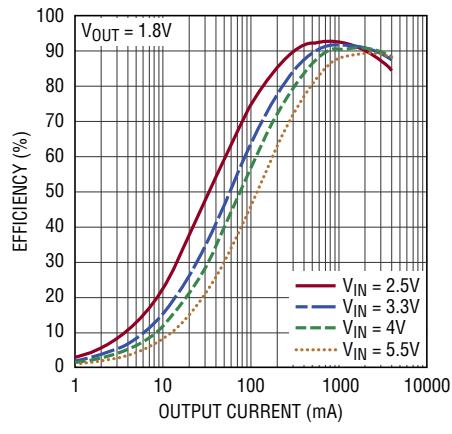

## 効率および電力損失と 負荷電流

## 絶対最大定格

(Note 1)

|                                        |                                |

|----------------------------------------|--------------------------------|

| PV <sub>IN</sub> 、SV <sub>IN</sub> の電圧 | -0.3V～6V                       |

| SWの電圧                                  | -0.3V～(PV <sub>IN</sub> +0.3V) |

| ITH、RT/SYNCの電圧                         | -0.3V～(SV <sub>IN</sub> +0.3V) |

| SRLIM、TRACK/SSの電圧                      | -0.3V～(SV <sub>IN</sub> +0.3V) |

| MODE、RUN、V <sub>FB</sub> の電圧           | -0.3V～(SV <sub>IN</sub> +0.3V) |

| PGOODの電圧                               | -0.3V～6V                       |

動作接合部温度範囲

(Note 2, 11) -55°C～150°C

保存温度 -65°C～150°C

## ピン配置

## 発注情報

| 無鉛仕上げ            | テープアンドリール          | 製品マーキング* | パッケージ                           | 温度範囲           |

|------------------|--------------------|----------|---------------------------------|----------------|

| LTC3614EUDD#PBF  | LTC3614EUDD#TRPBF  | LFVM     | 24-Lead (3mm × 5mm) Plastic QFN | -40°C to 125°C |

| LTC3614IUDD#PBF  | LTC3614IUDD#TRPBF  | LFVM     | 24-Lead (3mm × 5mm) Plastic QFN | -40°C to 125°C |

| LTC3614HUDD#PBF  | LTC3614HUDD#TRPBF  | LFVM     | 24-Lead (3mm × 5mm) Plastic QFN | -40°C to 150°C |

| LTC3614MPUDD#PBF | LTC3614MPUDD#TRPBF | LFVM     | 24-Lead (3mm × 5mm) Plastic QFN | -55°C to 150°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\*温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は規定動作接合部温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 2)注記がない限り、 $V_{IN} = 3.3\text{V}$ 、 $RT/SYNC = SV_{IN}$ 。

| SYMBOL                  | PARAMETER                                       | CONDITIONS                                                                                                                                                                                             | MIN      | TYP   | MAX             | UNITS            |               |

|-------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-----------------|------------------|---------------|

| $V_{IN}$                | Operating Voltage Range                         |                                                                                                                                                                                                        | 2.25     | 5.5   |                 | V                |               |

| $V_{UVLO}$              | Undervoltage Lockout Threshold                  | $SV_{IN}$ Ramping Down<br>$SV_{IN}$ Ramping Up                                                                                                                                                         | 1.7      |       | 2.25            | V                |               |

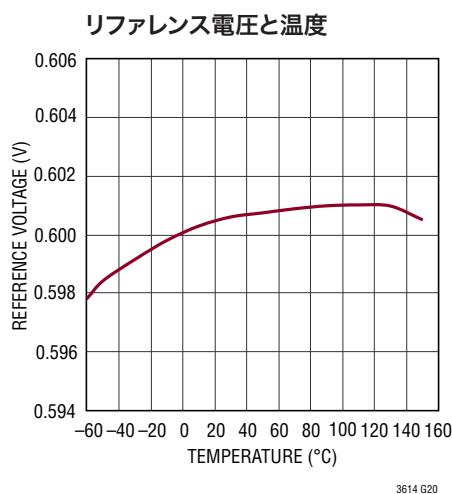

| $V_{FB}$                | Feedback Voltage Internal Reference             | (Note 3) $V_{TRACK} = SV_{IN}$ , $V_{DDR} = 0\text{V}$<br>$0^\circ\text{C} < T_J < 85^\circ\text{C}$<br>$-40^\circ\text{C} < T_J < 125^\circ\text{C}$<br>$-55^\circ\text{C} < T_J < 150^\circ\text{C}$ | 0.594    | 0.6   | 0.606           | V                |               |

|                         |                                                 |                                                                                                                                                                                                        | 0.591    |       | 0.609           | V                |               |

|                         |                                                 |                                                                                                                                                                                                        | 0.589    |       | 0.609           | V                |               |

|                         | Feedback Voltage External Reference<br>(Note 7) | (Note 3) $V_{TRACK} = 0.3\text{V}$ , $V_{DDR} = SV_{IN}$                                                                                                                                               | 0.288    | 0.300 | 0.312           | V                |               |

|                         |                                                 | (Note 3) $V_{TRACK} = 0.5\text{V}$ , $V_{DDR} = SV_{IN}$                                                                                                                                               | 0.488    | 0.500 | 0.512           | V                |               |

|                         |                                                 |                                                                                                                                                                                                        |          |       | $\pm 30$        | nA               |               |

| $I_{FB}$                | Feedback Input Current                          | $V_{FB} = 0.6\text{V}$                                                                                                                                                                                 |          |       |                 |                  |               |

| $\Delta V_{LINEREG}$    | Line Regulation                                 | $SV_{IN} = PV_{IN} = 2.25\text{V}$ to $5.5\text{V}$<br>(Notes 3, 4) $TRACK/SS = SV_{IN}$<br>$-40^\circ\text{C} < T_J < 125^\circ\text{C}$<br>$-55^\circ\text{C} < T_J < 150^\circ\text{C}$             |          |       | 0.2<br>0.3      | %/V<br>%/V       |               |

| $\Delta V_{LOADREG}$    | Load Regulation                                 | $ITH$ from $0.5\text{V}$ to $0.8\text{V}$ (Notes 3, 4)<br>$V_{ITH} = SV_{IN}$ (Note 5)                                                                                                                 |          |       | 0.25<br>2.6     | %<br>%           |               |

| $I_S$                   | Active Mode Supply Current                      | $V_{FB} = 0.5\text{V}$ , $V_{MODE} = SV_{IN}$ (Note 6)                                                                                                                                                 |          |       | 1100            | $\mu\text{A}$    |               |

|                         | Sleep Mode Supply Current                       | $V_{FB} = 0.7\text{V}$ , $V_{MODE} = 0\text{V}$ , $ITH = SV_{IN}$ (Note 5)                                                                                                                             |          |       | 75              | $\mu\text{A}$    |               |

|                         |                                                 | $V_{FB} = 0.7\text{V}$ , $V_{MODE} = 0\text{V}$ (Note 4)                                                                                                                                               |          |       | 130             | $\mu\text{A}$    |               |

|                         | Shutdown Current                                | $SV_{IN} = PV_{IN} = 5.5\text{V}$ , $V_{RUN} = 0\text{V}$                                                                                                                                              |          |       | 0.1             | $\mu\text{A}$    |               |

|                         | Top Switch On-Resistance                        | $PV_{IN} = 3.3\text{V}$ (Note 10)                                                                                                                                                                      |          |       | 35              | $\text{m}\Omega$ |               |

|                         | Bottom Switch On-Resistance                     | $PV_{IN} = 3.3\text{V}$ (Note 10)                                                                                                                                                                      |          |       | 25              | $\text{m}\Omega$ |               |

| $I_{LIM}$               | Top Switch Current Limit                        | Sourcing (Note 8), $V_{FB} = 0.5\text{V}$<br>Duty Cycle < 35%<br>Duty Cycle = 100%                                                                                                                     | 7.5<br>5 | 9     | 10.5            | A<br>A           |               |

|                         | Bottom Switch Current Limit                     | Sinking (Note 8), $V_{FB} = 0.7\text{V}$ ,<br>Forced Continuous Mode                                                                                                                                   |          | -6    | -8              | -11              | A             |

| $g_m(EA)$               | Error Amplifier Transconductance                | $-5\mu\text{A} < I_{ITH} < 5\mu\text{A}$ (Note 4)                                                                                                                                                      |          |       | 200             | $\mu\text{S}$    |               |

| $I_{EOA}$               | Error Amplifier Maximum Output Current          | (Note 4)                                                                                                                                                                                               |          |       | $\pm 30$        | $\mu\text{A}$    |               |

| $t_{SS}$                | Internal Soft-Start Time                        | $V_{FB}$ from $0.06\text{V}$ to $0.54\text{V}$ ,<br>$TRACK/SS = SV_{IN}$                                                                                                                               | 0.65     | 1.2   | 1.9             | ms               |               |

| $V_{TRACK/SS}$          | Enable Internal Soft-Start                      | (Note 7)                                                                                                                                                                                               | 0.62     |       |                 | V                |               |

| $t_{TRACK/SS\_DIS}$     | Soft-Start Discharge Time at Start-Up           |                                                                                                                                                                                                        | 60       |       |                 | $\mu\text{s}$    |               |

| $R_{ON(TRACK/SS\_DIS)}$ | TRACK/SS Pull-Down Resistor at Start-Up         |                                                                                                                                                                                                        |          |       | 200             | $\Omega$         |               |

| $f_{OSC}$               | Oscillator Frequency                            | $RT/SYNC = 370\text{k}$                                                                                                                                                                                | ●        | 0.8   | 1               | 1.2              | MHz           |

|                         | Internal Oscillator Frequency                   | $V_{RT/SYNC} = SV_{IN}$                                                                                                                                                                                | ●        | 1.8   | 2.25            | 2.7              | MHz           |

| $f_{SYNC}$              | Synchronization Frequency Range                 |                                                                                                                                                                                                        |          | 0.3   | 4               |                  | MHz           |

| $V_{RT/SYNC}$           | SYNC Input Threshold High                       |                                                                                                                                                                                                        |          | 1.2   |                 |                  | V             |

|                         | SYNC Input Threshold Low                        |                                                                                                                                                                                                        |          | .     |                 | 0.3              | V             |

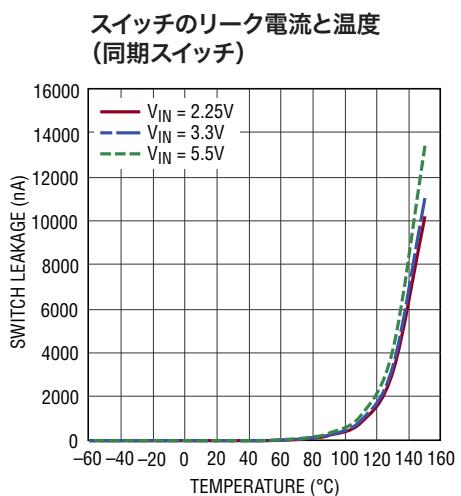

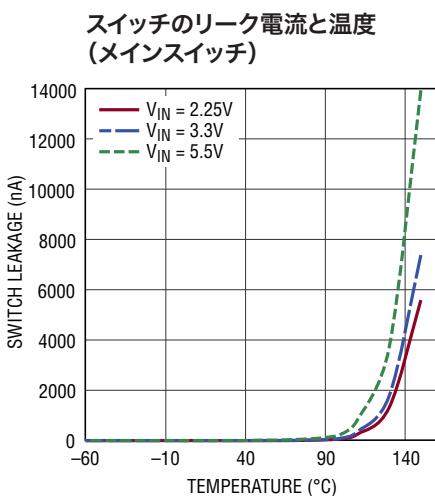

| $I_{SW(LKG)}$           | Switch Leakage Current                          | $SV_{IN} = PV_{IN} = 5.5\text{V}$ , $V_{RUN} = 0\text{V}$                                                                                                                                              |          |       | 0.1             | 1                | $\mu\text{A}$ |

| $V_{DDR}$               | DDR Option Enable Voltage                       |                                                                                                                                                                                                        |          |       | $SV_{IN} - 0.3$ |                  | V             |

## 電気的特性

●は規定動作接合部温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値 (Note 2)。注記がない限り、 $V_{IN} = 3.3\text{V}$ 、 $RT/SYNC = SV_{IN}$ 。

| SYMBOL                 | PARAMETER                          | CONDITIONS                                                                             | MIN             | TYP                  | MAX       | UNITS         |

|------------------------|------------------------------------|----------------------------------------------------------------------------------------|-----------------|----------------------|-----------|---------------|

| $V_{MODE}$<br>(Note 9) | Internal Burst Mode Operation      |                                                                                        |                 |                      | 0.3       | V             |

|                        | Pulse-Skipping Mode                |                                                                                        | $SV_{IN} - 0.3$ |                      |           | V             |

|                        | Forced Continuous Mode             |                                                                                        | 1.1             | $SV_{IN} \cdot 0.58$ |           | V             |

|                        | External Burst Mode Operation      |                                                                                        | 0.45            |                      | 0.8       | V             |

| PGOOD                  | Power Good Voltage Windows         | TRACK/SS = $SV_{IN}$ , Entering Window<br>$V_{FB}$ Ramping Up<br>$V_{FB}$ Ramping Down | -3<br>3         | -6<br>6              |           | %<br>%        |

|                        |                                    | TRACK/SS = $SV_{IN}$ , Leaving Window<br>$V_{FB}$ Ramping Up<br>$V_{FB}$ Ramping Down  |                 | 9<br>-9              | 11<br>-11 | %<br>%        |

| $t_{PGOOD}$            | Power Good Blanking Time           | Entering and Leaving Window                                                            | 70              | 105                  | 140       | $\mu\text{s}$ |

| $R_{PGOOD}$            | Power Good Pull-Down On-Resistance |                                                                                        | 8               | 17                   | 33        | $\Omega$      |

| $V_{RUN}$              | RUN voltage                        | Input High<br>Input Low                                                                | ●<br>●          | 1                    | 0.4       | V<br>V        |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**LTC3614は $T_J$ が $T_A$ にほぼ等しいパルス負荷条件でテストされている。LTC3614Eは $0^\circ\text{C} \sim 85^\circ\text{C}$ の接合部温度範囲で性能仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTC3614Hは $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲で動作することが保証されている。LTC3614MPは $-55^\circ\text{C} \sim 150^\circ\text{C}$ の全動作接合部温度範囲でテストされ、性能仕様に適合することが保証されている。高い接合部温度は動作寿命に悪影響を及ぼす。接合部温度が $125^\circ\text{C}$ を超えると、動作寿命は短くなる。これらの仕様と調和する最大周囲温度は、基板レイアウト、パッケージの定格熱抵抗などの環境要因と関連した特定の動作条件によって決まるに注意。

接合部温度 $T_J$ (単位:°C)は周囲温度 $T_A$ (単位:°C)および電力損失 $P_D$ (単位:W)から次式に従って計算される。

$$T_J = T_A + (P_D \cdot \theta_{JA})$$

ここで、 $\theta_{JA}$ (単位:°C/W)はパッケージの熱インピーダンス。最大周囲温度は、基板レイアウト、パッケージの定格熱抵抗および他の環境要因と関連した特定の動作条件によって決まるに注意。

**Note 3:**このパラメータは $V_{FB}$ を誤差アンプの中点( $V_{ITH} = 0.75\text{V}$ )にサーボ制御する帰還ループでテストされている。

**Note 4:** $ITH$ ピンの外部補償。

**Note 5:** $ITH$ ピンを $SV_{IN}$ に接続すると内部補償とAVPモードをイネーブルする。

**Note 6:**動作時消費電流はスイッチング周波数で供給される内部ゲート電荷により増加する。

**Note 7:**「ピン機能」のセクションのTRACK/SSピンの説明を参照。

**Note 8:**ソース・モードでは、平均出力電流はSWピンから流れ出す。シンク・モードでは、平均出力電流はSWピンに流れ込む。

**Note 9:**「ピン機能」のセクションのMODEピンの説明を参照。

**Note 10:**QFN パッケージでは、ウェハ・レベルの測定との相関および設計によって保証されている。

**Note 11:**このデバイスには短時間の過負荷状態の間デバイスを保護するための過温度保護機能が備わっている。過温度保護機能がアクティブなとき接合部温度は $150^\circ\text{C}$ を超える。規定された最高動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なうおそれがある。

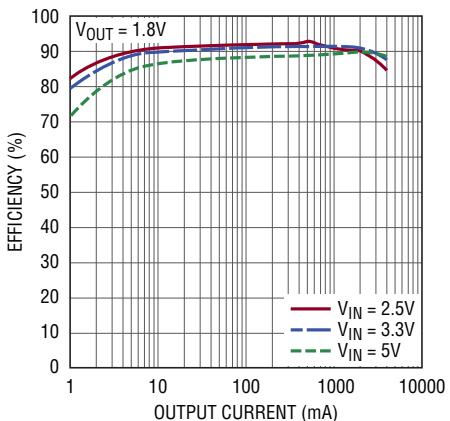

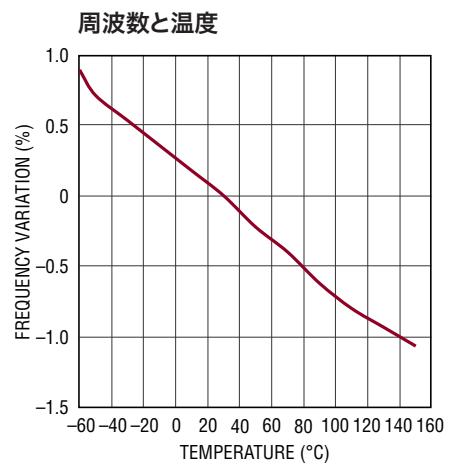

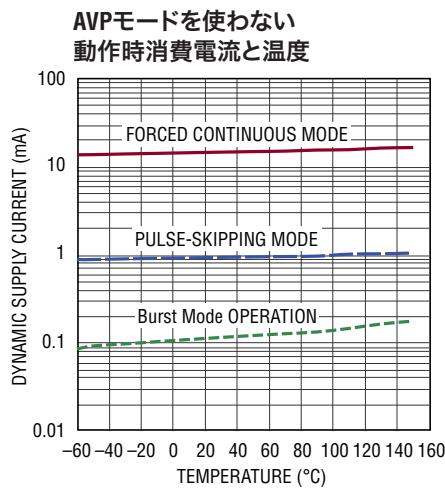

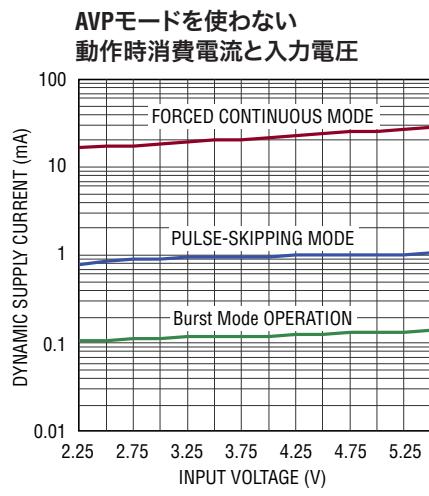

標準的性能特性 注記がない限り、 $V_{IN} = 3.3V$ 、RT/SYNC = SV<sub>IN</sub>。効率と負荷電流、Burst Mode動作

( $V_{MODE} = 0V$ )効率と負荷電流、Burst Mode動作

( $V_{MODE} = 0V$ )

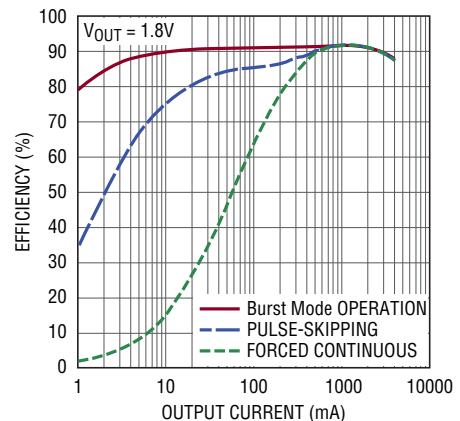

効率と負荷電流

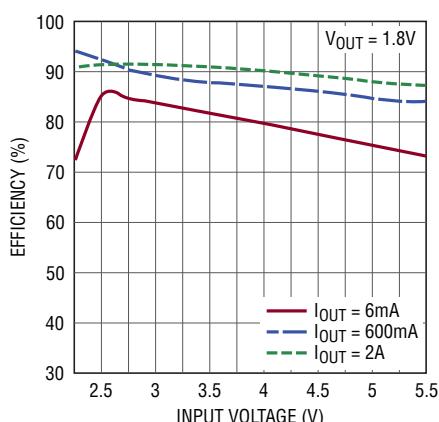

効率と入力電圧、Burst Mode動作

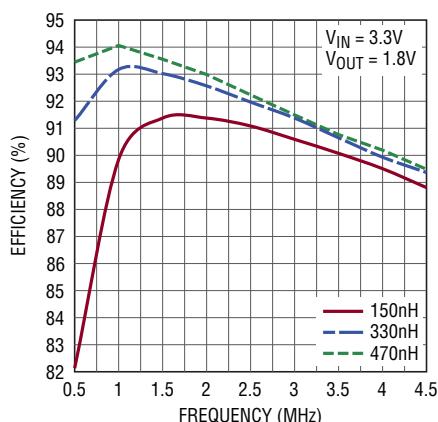

( $V_{MODE} = 0V$ )効率と周波数、Burst Mode動作

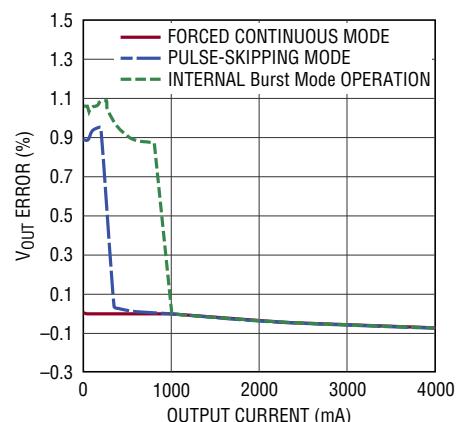

( $V_{MODE} = 0V$ )、 $I_{OUT} = 2A$ 負荷レギュレーション ( $V_{OUT} = 1.8V$ )

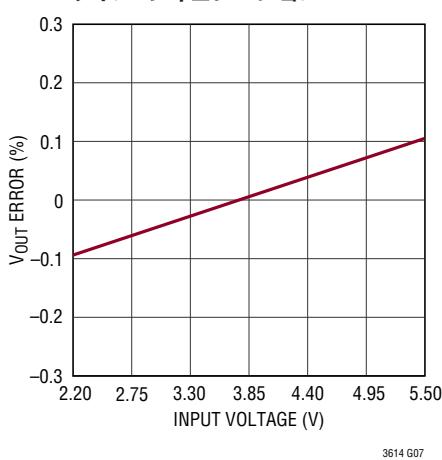

ライン・レギュレーション

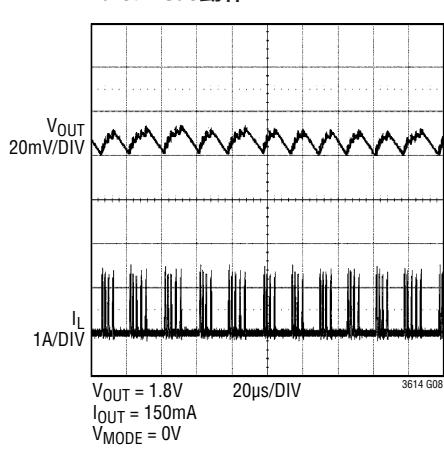

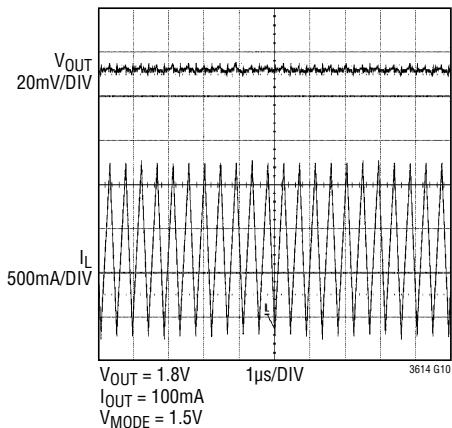

Burst Mode動作

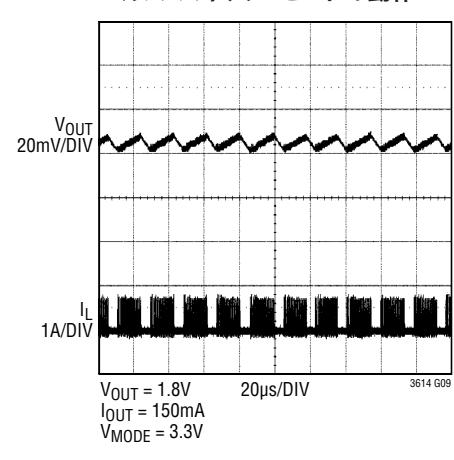

パルス・スキップ・モードの動作

標準的性能特性 注記がない限り、 $V_{IN} = 3.3V$ 、 $RT/SYNC = SV_{IN}$ 。

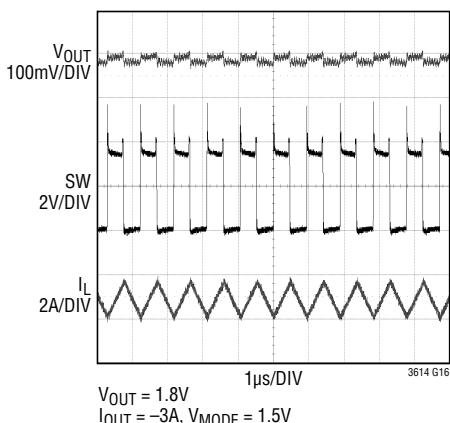

### 強制連続モードの動作

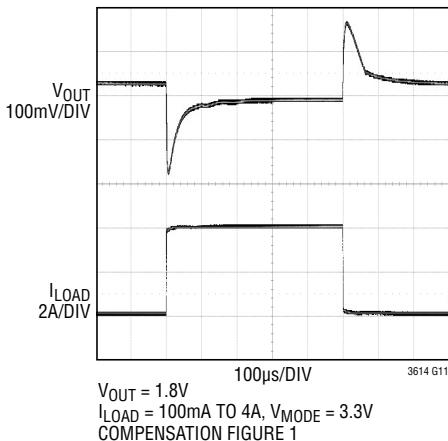

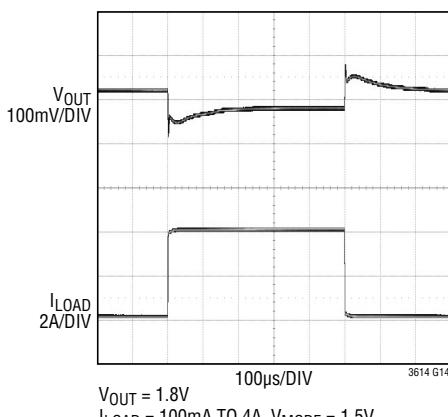

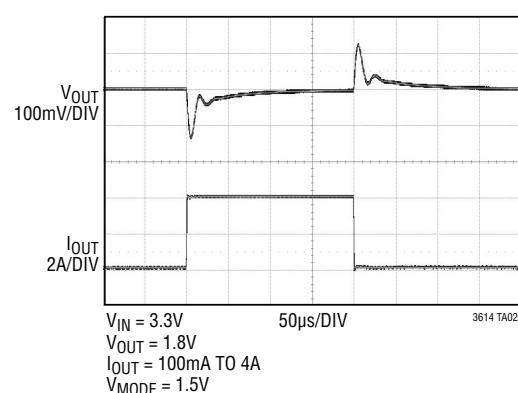

### パルス・スキップ・モードの負荷ステップ過渡

### Burst Mode動作の負荷ステップ過渡

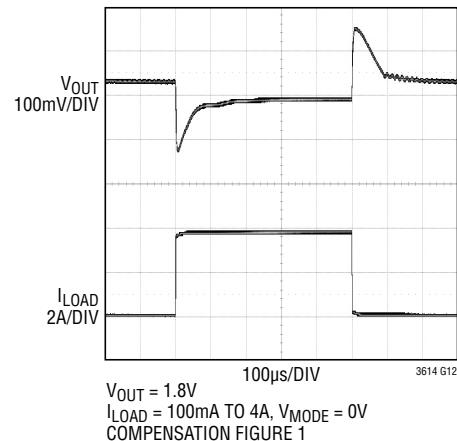

### AVPモードを使わない強制連続モードの負荷ステップ過渡応答

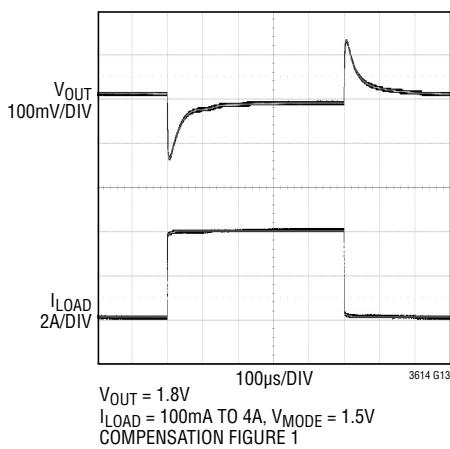

### AVPモードを使った強制連続モードの負荷ステップ過渡応答

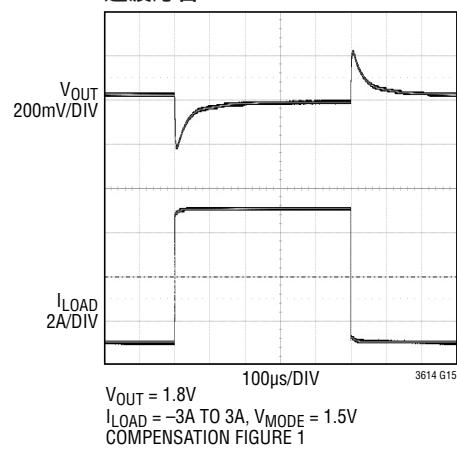

### 電流をソースおよびシンクする強制連続モードの負荷ステップ過渡応答

### 電流のシンク

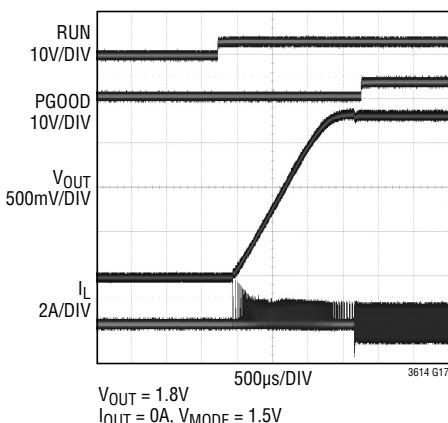

### 強制連続モードの内部スタートアップ

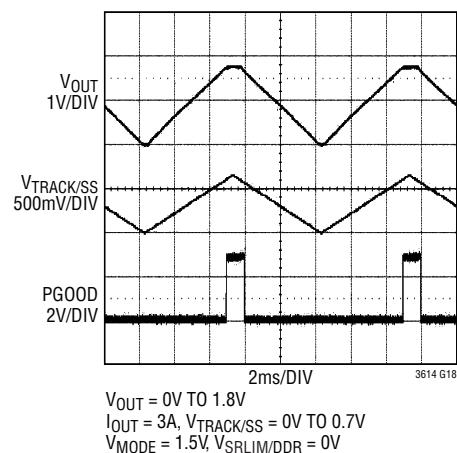

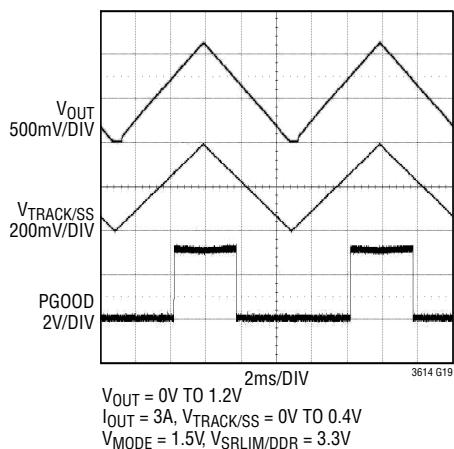

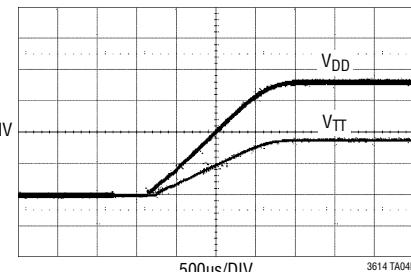

### 強制連続モード、非DDRモードでのトラッキングアップおよびトラッキングダウン

標準的性能特性 注記がない限り、 $V_{IN} = 3.3V$ 、RT/SYNC = SV<sub>IN</sub>。

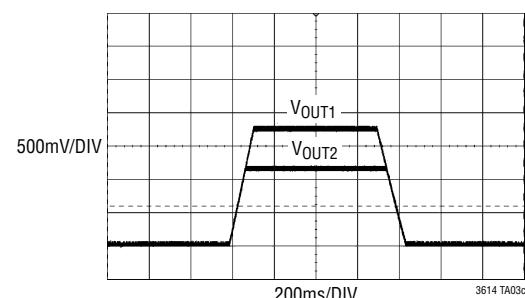

強制連続モードでのトラッキング

アップおよびトラッキングダウン、

DDRピンをSV<sub>IN</sub>に接続

標準的性能特性 注記がない限り、 $V_{IN} = 3.3V$ 、 $RT/SYNC = SV_{IN}$ 。

## ピン機能

**SRLIM/DDR(ピン1)**: スルーレート制限。このピンをグランドに接続すると最大スルーレートが選択されます。ピンがオープンだと最小スルーレートが選択されます。SRLIM/DDRからグランドに抵抗を接続すると、スルーレートを連続的に調整することができます。SRLIM/DDRをSV<sub>IN</sub>に接続すると、DDRモードが選択されます。DDRモードでは、スルーレートのリミットは最大に設定されます。

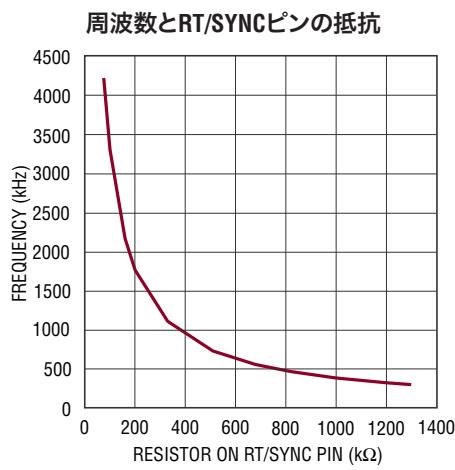

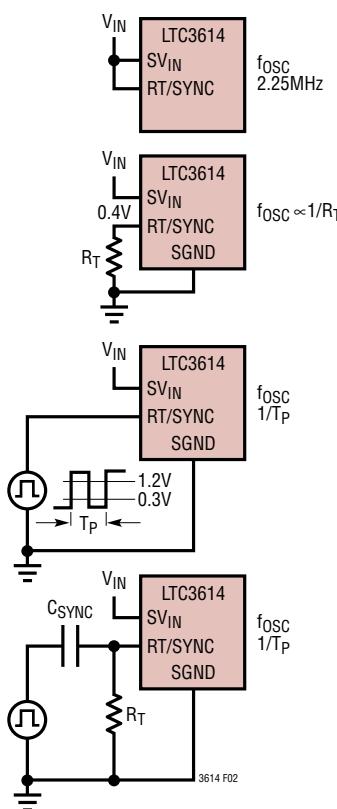

**RT/SYNC(ピン2)**: 発振器周波数。このピンは固定スイッチング周波数を設定する3つの方法を与えます。

1. RT/SYNCからグランドに抵抗を接続すると、抵抗の値に基づいてスイッチング周波数が設定されます。

2. RT/SYNCピンを外部クロック信号でドライブすると、LTC3614は与えられた周波数に同期します。スロープ補償は自動的に外部クロック周波数に適応します。

3. RT/SYNCピンをSV<sub>IN</sub>に接続すると内部2.25MHz発振器周波数をイネーブルします。

**SGND(ピン3)**: 信号グランド。全ての小信号用部品と補償用部品はこのグランドに接続し、このグランド自体はPGNDに一点接続します。

**PV<sub>IN</sub>(ピン4、10、11、17)**: 電力用入力電源。PV<sub>IN</sub>は内部のPチャネル・パワーMOSFETのソースに接続されています。このピンはSV<sub>IN</sub>からは独立しており、同じ電圧またはもっと低い電圧の電源に接続することができます。

**SW(ピン5、6、7、8、13、14、15、16)**: スイッチ・ノード。インダクタへの接続。これらのピンは内部のパワーMOSFETスイッチのドレインに接続されています。

**NC(ピン9、12)**: グランドに接続するか、オープンのままにすることができます。

**SV<sub>IN</sub>(ピン18)**: 信号用入力電源。このピンは内部制御回路に電力を供給し、低電圧ロックアウト・コンパレータによってモニタされます。

**RUN(ピン19)**: イネーブル・ピン。このピンをグランドに強制すると、LTC3614をシャットダウンします。シャットダウン時には全機能がディスエーブルされ、デバイスに流れる消費電流は1μA未満になります。

**PGOOD(ピン20)**: パワーグッド。このオープン・ドレイン出力は、スタートアップ時およびFB電圧がパワーグッド電圧 WINDOWから外れている間SGNDに引き下げられます。FB電圧が増加し、

パワーグッド・ウインドウ内に100μsを超えて留まると、PGOODピンがリリースされます。FB電圧がパワーグッド・ウインドウから100μs以上外れると、PGOODピンが引き下げられます。

DDRモードでは(DDR = V<sub>IN</sub>)、パワーグッド・ウインドウは実際のTRACK/SSピンの電圧に応じて動きます。パワーアップ/パワーダウンのトラッキングの間、PGOODピンは常にプルダウンされます。

シャットダウン状態では、PGOOD出力はアクティブにプルダウンするので、外部抵抗を介して出力コンデンサを放電するのに使うことができます。

**MODE(ピン21)**: モード選択。MODEピンをSV<sub>IN</sub>またはSGNDに接続すると、それぞれパルス・スキップ・モードまたはBurst Mode動作(内部Burst Modeクランプ付き)がイネーブルされます。このピンをSV<sub>IN</sub>の半分よりわずか上に保つと、強制連続モードが選択されます。このピンを0.45V～0.8Vの外部電圧に接続するとBurst Mode動作が選択され、バースト・クランプがこのピンの電圧に設定されます。詳細は「動作」のセクションを参照してください。

**V<sub>FB</sub>(ピン22)**: 電圧帰還入力ピン。出力に接続された外部抵抗分割器からの帰還電圧を検出します。

**ITH(ピン23)**: 誤差アンプの補償。電流コンパレータのスレッショルドはこの制御電圧に応じて増加します。このピンをSV<sub>IN</sub>に接続すると内部補償とAVPモードをイネーブルします。

**TRACK/SS(ピン24)**: トラッキング/外部ソフトスタート/外部リファレンス。スタートアップ動作はTRACK/SSピンでプログラム可能です。

1. このピンをSV<sub>IN</sub>に接続すると内部ソフトスタート回路が選択されます。

2. グランドへのコンデンサとSV<sub>IN</sub>への抵抗を使って、外部ソフトスタートのタイミングをプログラムすることができます。

3. TRACK/SSを使って、LTC3614が別の電源のスタートアップ動作をトラッキングするように強制することができます。

このピンを外部リファレンスの入力として使うこともできます。詳細については「アプリケーション情報」のセクションを参照してください。

**PGND(露出パッドのピン25)**: 電源グランド。このピンは内部Nチャネル・パワーMOSFETのソースに接続されています。このピンをC<sub>IN</sub>とC<sub>OUT</sub>の(-)端子に近づけて接続します。

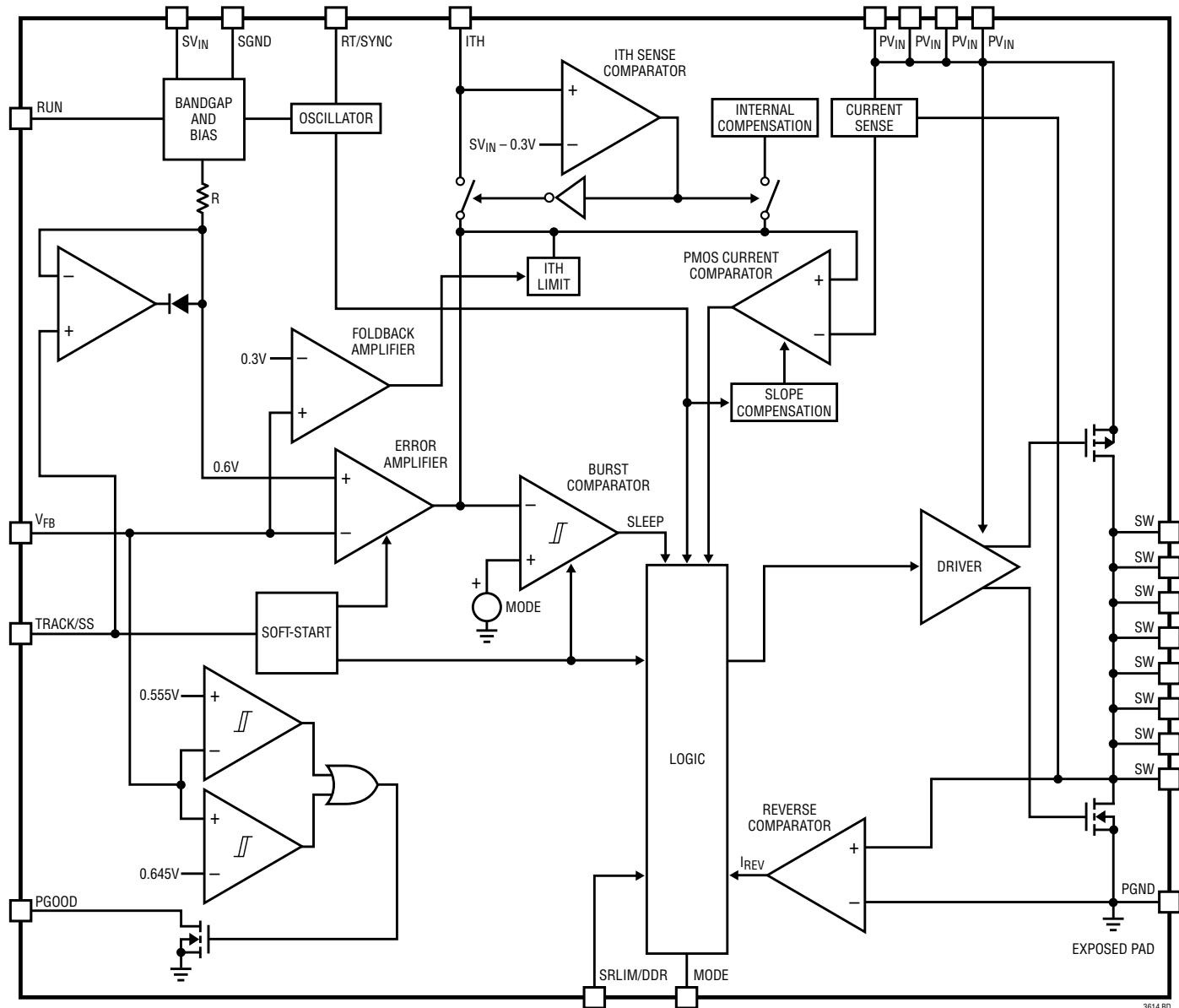

## 機能ブロック図

## 動作

### メイン制御ループ

LTC3614はモノリシック、固定周波数、電流モードの降圧DC/DCコンバータです。通常動作時、内部のトップ・パワースイッチ(PチャネルMOSFET)が各クロック・サイクルの始点でオンします。電流コンパレータがトリップしてトップ・パワースイッチをオフするまで、インダクタを流れる電流が増加します。電流コンパレータがトリップするピーク・インダクタ電流はITHピンの電圧によって制御されます。誤差アンプは、抵抗分割器からの帰還信号であるVFBピンの電圧を内部の0.6Vリファレンスと比較することによって、このITHピンの電圧を調節します。負荷電流が増加すると、リファレンスに比べて帰還電圧が低下します。誤差アンプは平均インダクタ電流が新しい負荷電流に釣り合うまでITH電圧を上昇させます。ITHピンの標準電圧範囲は0.1V～0.8Vで、0.45Vがゼロ電流に対応します。

トップ・パワースイッチがオフすると、ボトム電流リミットに達するか、次のクロック・サイクルが開始されるまで同期パワースイッチ(NチャネルMOSFET)がオンします。ボトム電流リミットは強制連続モードでは標準的に-8Aに設定され、Burst Mode動作およびパルス・スキップ・モードでは0Aに設定されます。

RT/SYNCがSV<sub>IN</sub>に接続されると、動作周波数は既定で2.25MHzになります。または、RT/SYNCピンとグランドの間に接続された外部抵抗によって、またはRT/SYNCピンに与えられるクロック信号によって動作周波数を設定することができます。スイッチング周波数は300kHz～4MHzに設定することができます。

過電圧コンパレータと低電圧コンパレータは、出力電圧が設定ポイントから±7.5% (標準)以上変化すると、PGOOD出力を“L”に引き下げます。

### モード選択

MODEピンは4種類の動作モードの1つを選択するのに使います。

#### モード選択電圧

#### Burst Mode動作(内部クランプ)

MODEピンをSGNDに接続すると、内部クランプによるBurst Mode動作をイネーブルします。Burst Mode動作では、内部パワースイッチは軽負荷では間欠的に動作します。このためスイッチング損失が減少するので効率が向上します。スイッチがアイドル状態の間、LTC3614はスリープ状態に入り、内部回路の多くがディスエーブルされて電力を節約します。Burst Mode動作の間、最小ピーク・インダクタ電流は内部でクランプされ、いつスリープ・モードをイネーブル/ディスエーブルするか決定するためITHピンの電圧がバースト・コンパレータによってモニタされます。平均インダクタ電流が負荷電流より大きいとITHピンの電圧が低下します。ITH電圧が内部クランプを下回ると、バースト・コンパレータがトリップしてスリープ・モードをイネーブルします。スリープ・モードの間、パワーMOSFETはオフに保たれ、負荷電流は出力コンデンサからだけ供給されます。出力電圧が下がると、トップ・パワースイッチが再度オンし、内部回路が再度イネーブルされます。この過程が負荷電流に依存した速度で繰り返されます。

## 動作

### Burst Mode動作(外部クランプ)

MODEピンを0.45V～0.8Vの範囲の電圧に接続すると、外部クランプを使うBurst Mode動作がイネーブルされます。この動作モードの間、ITHピンの最小電圧はMODEピンの電圧によって外部から設定されます。周囲温度が85°Cを超える場合は、内部バースト・クランプによるBurst Mode動作を使用することを推奨します。

### パルス・スキップ・モードの動作

パルス・スキップ・モードはBurst Mode動作に似ていますが、スリープ・モードの間LTC3614は内部回路への電力をディスエーブルしません。これにより、出力電圧リップルが改善されますが、消費電流が増え、軽負荷時の効率が下がります。

MODEピンをSV<sub>IN</sub>に接続すると、パルス・スキップ・モードがイネーブルされます。負荷電流が減少するにつれ、ピーク・インダクタ電流は(ITH電圧が0Aに対応する電圧レベルを下回るまでは)ITHピンの電圧によって決定されます。この時点で、ピーク・インダクタ電流は電流コンパレータの最小オン時間によって決定されます。最小オン時間に相当するインダクタ電流の平均よりも負荷需要が少ないと、スイッチング・サイクルをスキップし、出力電圧を安定化状態に保ちます。

### 強制連続モード

強制連続モードでは、インダクタ電流は一定のサイクルで流れ、全ての出力電流レベルで最小出力電圧リップルを生じます。

MODEピンを1.1V～SV<sub>IN</sub>・0.58の範囲の電圧に接続すると、強制連続モード動作がイネーブルされます。

強制連続モード動作はBurst Mode動作またはパルス・スキップ動作に比べて軽負荷では効率が劣りますが、スイッチングの高調波を信号の帯域幅の外に保つことが必要なアプリケーションにとっては望ましいことがあります。

出力が電流をシンクする必要があれば、強制連続モードを使う必要があります。

### ドロップアウト動作

入力電源電圧が出力電圧に近づくと、デューティ・サイクルが最大オン時間に向かって増加します。電源電圧がさらに低下すると、メイン・スイッチは1サイクルを超えてオン状態に留まり、ついには100%のデューティ・サイクルに達します。このときの出力電圧は、入力電圧から内部PチャネルMOSFETとインダクタの電圧降下を差し引いた電圧になります。

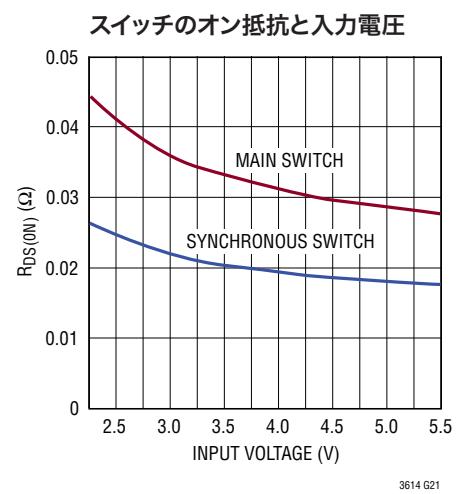

### 低電源電圧動作

LTC3614は2.25Vの入力電源電圧まで動作するように設計されています。低い入力電源電圧で考慮すべきことは、PチャネルとNチャネルのパワースイッチのR<sub>DS(ON)</sub>が増加することです。ユーザーは、低い入力電圧でLTC3614が100%デューティ・サイクルで使用されるときの電力損失を計算して、サーマル・リミットを超えないようにする必要があります。「標準的性能特性」のグラフを参照してください。

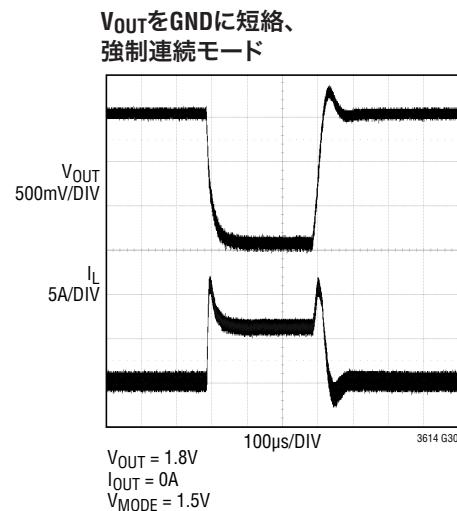

### 短絡保護

電流コンパレータがトップ・パワースイッチをオフするピーク・インダクタ電流はITHピンの電圧によって制御されます。

出力電流が増加すると、誤差アンプは平均インダクタ電流が新しい負荷電流に釣り合うまでITHピンの電圧を上昇させます。通常動作では、LTC3614は最大ITHピン電圧を、標準9Aのピーク・インダクタ電流に対応する約0.8Vにクランプします。

出力がグランドに短絡すると、インダクタ電流は1スイッチング・サイクルの間非常にゆっくり減衰します。LTC3614は2つの手法を使って電流の暴走を防ぎます。

## 動作

出力電圧がその公称値の50%より低くなると、ITHピンのクランプ電圧が下がり、最大ピーク・インダクタ電流が出力電圧に伴って徐々に減少します。出力電圧が0Vに達すると、ITHピンのクランプ電圧は通常動作時のクランプ電圧の40%に低下します。短絡時のピーク・インダクタ電流は、LTC3614の最小オン時間、入力電圧およびインダクタの値によって決まります。このフォールドバック動作は、出力がグランドに短絡したときピーク・インダクタ電流を制限するのに役立ちます。これは、内部または外部のソフトスタートおよびトラッキングアップ/トラッ

キングダウン動作の間ディスエーブルされます（「アプリケーション情報」のセクションを参照）。

また、2つめの制限が谷インダクタ電流に課せられます。ボトムMOSFETを介して測定されるインダクタ電流が標準12Aを超えて増加すると、トップ・パワーMOSFETがオフに保たれ、インダクタ電流が減少するまでスイッチング・サイクルをスキップします。

## アプリケーション情報

基本的なLTC3614の応用回路を図1に示します。

### 動作周波数

動作周波数の選択には、効率と部品サイズの間のトレードオフが必要です。動作周波数を高くすると、小さい値のインダクタとコンデンサを使うことができます。

低い周波数で動作させると内部ゲート電荷による損失が減り、効率が改善されますが、出力リップル電圧を低く抑えるには、インダクタンスや容量の値を大きくする必要があります。

LTC3614の動作周波数は、RT/SYNCピンとグランド間に接続した外部抵抗によって決まります。この抵抗の値により、発振器内の内部タイミング・コンデンサを充放電するのに使われるラン

プ電流が設定されます。この抵抗の値は次式を使って計算することができます。

$$R_T = \frac{3.82 \cdot 10^{11} \text{Hz}}{f_{\text{OSC}}(\text{Hz})} \Omega - 16 \text{k}\Omega$$

最高4MHzの周波数も可能ですが、LTC3614の最小オン時間により、動作デューティ・サイクルの最小値が制限されます。最小オン時間は標準60nsなので、最小デューティ・サイクルは  $60\text{ns} \cdot f_{\text{OSC}}(\text{Hz}) \cdot 100\%$  に等しくなります。

RT/SYNCピンをSV<sub>IN</sub>に接続すると、内部動作周波数を既定の2.25MHz±20%に設定します。

図1. 1.8V/4A 降圧レギュレータ

## アプリケーション情報

### 周波数同期

方形波クロック信号をRT/SYNCピンに与えることにより、LTC3614の内部発振器を外部周波数に同期させることができます。同期動作の間、トップ・スイッチのターンオンは外部周波数ソースの立ち下がりエッジにロックします。同期周波数範囲は300kHz～4MHzです。同期時、全ての動作モードを選択することができます。

インダクタの電流リップルを下げるため、RT/SYNCへのクロック信号を取り去る前にレギュレータをパワーダウンさせる(RUNピンをグランドに強制すること)を推奨します。

外部クロック発生器が、LTC3614のスタートアップ、動作時およびシャットダウンを通して連続してクロック信号を供給できないときは、AC結合します。コンデンサC<sub>SYNC</sub>のサイズはRT/SYNCピンの寄生容量に依存し、標準で10pF～22pFの範囲です。

図2. スイッチング周波数の設定

### インダクタの選択

所定の入力電圧と出力電圧に対して、インダクタの値と動作周波数によってリップル電流が決まります。リップル電流 $\Delta I_L$ は $V_{IN}$ が高いほど増加し、インダクタンスが高いほど減少します。

$$\Delta I_L = \left( \frac{V_{OUT}}{f_{SW} \cdot L} \right) \cdot \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

リップル電流を小さくすると、インダクタのコア損失、出力コンデンサのESR損失、さらに出力電圧リップルが減少します。リップル電流を選択するための妥当な出発点は $\Delta I_L = 0.3 \cdot I_{OUT(MAX)}$ です。最大 $V_{IN}$ で最大リップル電流が発生します。リップル電流が規定された最大値を超えないようにするには、次式に従ってインダクタンスを選択します。

$$L = \left( \frac{V_{OUT}}{f_{SW} \cdot \Delta I_{L(MAX)}} \right) \cdot \left( 1 - \frac{V_{OUT}}{V_{IN(MAX)}} \right)$$

インダクタンス値はBurst Mode動作にも影響を与えます。ピーク・インダクタ電流がバースト・クランプによって設定されたレベルを下回ると、低電流動作への移行が開始されます。インダクタンス値が小さいとリップル電流が大きくなるので、この移行がより低い負荷電流で起きるようになります。このため、低電流動作範囲の上の部分での効率が低下します。Burst Mode動作では、インダクタンス値が小さいほどバースト周波数が高くなります。

### インダクタのコアの選択

$L$ の値が求まつたら、次にインダクタの種類を選択します。インダクタンス値が同じ場合、実際のコア損失はコア・サイズではなく、選択したインダクタンスによって大きく異なります。インダクタンスが大きいほどコア損失が減少します。残念ながら、インダクタンスを大きくするにはワイヤの巻数を増やす必要があるため銅損失が増加します。

## アプリケーション情報

フェライトを使ったタイプはコア損失が極めて低く、高いスイッチング周波数には最適なので、設計目標を銅損失と飽和を防ぐことに集中することができます。フェライト・コアの材質は「ハードに」飽和します。つまり、ピーク設計電流を超えるとインダクタンスが急に減少します。このため、インダクタのリップル電流が急増して、出力電圧リップルが増加します。フェライト・コアを飽和させないでください。そして、アプリケーションの温度範囲を考慮して外部インダクタを選択してください。

コアの材質と形状が異なると、インダクタのサイズ/電流の関係および価格/電流の関係が変化します。フェライトやパーマロイを素材とするトロイド・コアやシールドされたポット型コアは小型で、エネルギー放射は大きくありませんが、類似の特性を有する鉄粉コアのインダクタより一般に高価です。使用するインダクタの種類の選択は価格とサイズの条件や放射フィールド/EMIの条件に主に依存します。LTC3614のアプリケーションで適切に動作する標準的表面実装インダクタをいくつか表1に示します。

### 入力コンデンサ( $C_{IN}$ )の選択

連続モードでは、トップPチャネルMOSFETのソース電流はデューティ・サイクルが( $V_{OUT}/V_{IN}$ )の方形波になります。大きな入力過渡電圧を防止するには、最大RMS電流に対応できるサイズの低ESRコンデンサを $V_{IN}$ に使用する必要があります。

コンデンサの最大RMS電流は次式で与えられます。

$$I_{RMS} = I_{OUT(MAX)} \cdot \frac{V_{OUT}}{V_{IN}} \cdot \sqrt{\left(\frac{V_{IN}}{V_{OUT}} - 1\right)}$$

この式は $V_{IN} = 2V_{OUT}$ で最大値をとります。ここで、 $I_{RMS} = I_{OUT}/2$ です。大きく変化させてもそれほど状況が改善されないため、一般にはこの単純な最悪条件が設計に使用されます。コンデンサ・メーカーの規定するリップル電流定格は多くの場合2000時間だけの寿命試験に基づいているので、コンデンサをさらにディレーティングする、つまり必要とされるよりも高い温度定格のコンデンサを選択することを推奨します。一般に、アプリケーションの温度範囲を考慮してコンデンサを選択してください。サイズまたは高さの設計条件を満たすため、複数のコンデンサを並列に接続することもできます。

表1. 標準的表面実装インダクタ

| INDUCTANCE<br>( $\mu$ H)                   | DCR<br>(m $\Omega$ ) | SATURATION<br>CURRENT (A) | DIMENSIONS<br>(mm) | HEIGHT<br>(mm) |

|--------------------------------------------|----------------------|---------------------------|--------------------|----------------|

| <b>Vishay IHLP-2525CZ-01</b>               |                      |                           |                    |                |

| 0.10                                       | 1.5                  | 60                        | 6.5 × 6.9          | 3              |

| 0.15                                       | 1.9                  | 52                        | 6.5 × 6.9          | 3              |

| 0.20                                       | 2.4                  | 41                        | 6.5 × 6.9          | 3              |

| 0.22                                       | 2.5                  | 40                        | 6.5 × 6.9          | 3              |

| 0.33                                       | 3.5                  | 30                        | 6.5 × 6.9          | 3              |

| 0.47                                       | 4                    | 26                        | 6.5 × 6.9          | 3              |

| <b>Sumida CDMC6D28 Series</b>              |                      |                           |                    |                |

| 0.2                                        | 2.5                  | 21.7                      | 7.25 × 4.4         | 3              |

| 0.3                                        | 3.2                  | 15.4                      | 7.25 × 4.4         | 3              |

| 0.47                                       | 4.2                  | 13.6                      | 7.25 × 4.4         | 3              |

| <b>Cooper HCP0703 Series</b>               |                      |                           |                    |                |

| 0.22                                       | 2.8                  | 23                        | 7 × 7.3            | 3.0            |

| 0.47                                       | 4.2                  | 17                        | 7 × 7.3            | 3.0            |

| 0.68                                       | 5.5                  | 15                        | 7 × 7.3            | 3.0            |

| <b>Wurth Electronik WE-HC744312 Series</b> |                      |                           |                    |                |

| 0.25                                       | 2.5                  | 18                        | 7 × 7.7            | 3.8            |

| 0.47                                       | 3.4                  | 16                        | 7 × 7.7            | 3.8            |

| <b>Coilcraft SLC7530 Series</b>            |                      |                           |                    |                |

| 0.100                                      | 0.123                | 20                        | 7.5 × 6.7          | 3              |

| 0.188                                      | 0.100                | 21                        | 7.5 × 6.7          | 3              |

| 0.272                                      | 0.100                | 14                        | 7.5 × 6.7          | 3              |

| 0.350                                      | 0.100                | 11                        | 7.5 × 6.7          | 3              |

| 0.400                                      | 0.100                | 8                         | 7.5 × 6.7          | 3              |

## アプリケーション情報

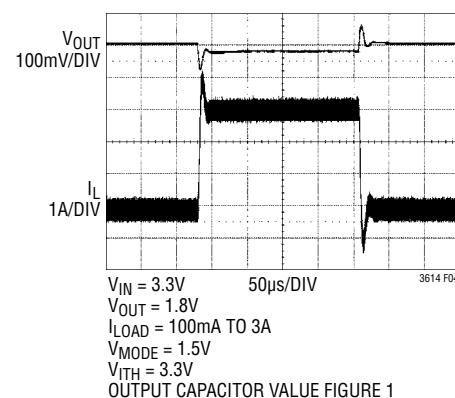

### 出力コンデンサ( $C_{OUT}$ )の選択

$C_{OUT}$ の選択は、電圧リップルおよび負荷ステップに対する過渡応答を小さくするために必要なESRによって一般に決まります(低ESRセラミック・コンデンサについては次のセクションで説明します)。一般に、ESRの要件が満たされると、その容量はフィルタ機能にとって十分です。出力リップル $\Delta V_{OUT}$ は次式で求められます。

$$\Delta V_{OUT} \leq \Delta I_L \cdot \left( ESR + \frac{1}{8 \cdot f_{SW} \cdot C_{OUT}} \right)$$

ここで、 $f_{OSC}$  = 動作周波数、 $C_{OUT}$  = 出力容量、 $\Delta I_L$  = インダクタのリップル電流です。 $\Delta I_L$ は入力電圧に応じて増加するので、出力リップルは入力電圧が最大のとき最大になります。

表面実装のアプリケーションでは、アプリケーションの要求する容量、ESRまたは実効電流の条件を満たすため、複数のコンデンサの並列接続が必要になることがあります。アルミ電解、特殊ポリマー、セラミック、および乾式タンタルの各コンデンサは全て表面実装パッケージで入手できます。

タンタル・コンデンサは最高の容量密度をもっていますが、ESRが大きいことがあり、スイッチング電源に使うためにサージテストされている必要があります。アルミ電解コンデンサのESRはかなり大きいのですが、リップル電流定格および長期信頼性に対して配慮すれば、コストに非常に敏感なアプリケーションに使うことができます。

### 入力と出力のセラミック・コンデンサ

セラミック・コンデンサは最もESRが小さく費用対効果が高いのですが、容量密度が低く、電圧係数と温度係数が高くて、可聴圧電効果を示します。さらに、寄生インダクタンスをともなったセラミック・コンデンサはQが高く、大きなリギングを引き起こすことがあります。

それらはESRが非常に小さいのでスイッチング・レギュレータに最適ですが、入力や出力に全てセラミック・コンデンサを使うときは細心の注意が必要です。

セラミック・コンデンサは温度の影響を受けやすいので、設計者は全動作温度範囲でループの安定性を確認する必要があります。大きな温度係数と電圧係数の影響を最小に抑えるため、X5RまたはX7Rのセラミック・コンデンサだけを使ってください。

セラミック・コンデンサを入力に使い、ACアダプタなど長いコードを通して電源を供給すると、出力の負荷ステップによって $V_{IN}$ ピンにリギングが誘起されることがあります。よくても、このリギングが出力に結合して、ループの不安定性と誤認されることがあります。最悪の場合、この入力のリギングがデバイスに損傷を与えるほど大きくなることがあります。

セラミック・コンデンサのESRは非常に小さいので、入力コンデンサと出力コンデンサは代りに電荷保存の要件を満たす必要があります。負荷ステップ発生時には、帰還ループがスイッチ電流を十分増加させて負荷を支えるまで、出力コンデンサが即座に電流を供給する必要があります。帰還ループが応答するのに要する時間は補償部品と出力コンデンサのサイズに依存します。負荷ステップに応答するには標準で3~4サイクルを要しますが、最初のサイクルだけ出力が直線的に低下します。出力の垂下( $V_{DROOP}$ )は通常最初のサイクルの直線的な低下の約2~4倍です。ただし、この振舞いは補償部品の値に依存して変化することがあります。したがって、およそ以下の出力コンデンサのサイズから開始するのが良いでしょう。

$$C_{OUT} \approx \frac{3.5 \cdot \Delta I_{OUT}}{f_{SW} \cdot V_{DROOP}}$$

これは近似にすぎません。デューティ・サイクルや負荷ステップの要件に依存して、さらに大きな容量が必要になることがあります。

ほとんどのアプリケーションでは、電源のインピーダンスは非常に小さいので、入力コンデンサは単に高周波をバイパスするのに必要です。

## アプリケーション情報

### 出力電圧のプログラミング

出力電圧は外部抵抗分割器によって次式のように設定されます。

$$V_{OUT} = 0.6 \cdot \left( 1 + \frac{R1}{R2} \right) V$$

図1に示されているように、V<sub>FB</sub>ピンは出力電圧を抵抗分割器によって分圧した電圧を検出することができます。

### バースト・クランプのプログラミング

MODEピンの電圧が0.8Vより下だと、Burst Mode動作がイネーブルされます。

MODEピンの電圧が0.3Vより下だと、内部の既定バースト・クランプ・レベルが選択されます。ITHピンの最小電圧は標準525mVです(内部クランプ)。

電圧が0.45Vと0.8Vの間だと、MODEピンの電圧(V<sub>BURST</sub>)はITHピンの最小電圧(外部クランプ)に等しく、バースト・クランプ・レベルI<sub>BURST</sub>(標準で0A～7A)を決めます。

ITH電圧が内部(または外部)クランプ電圧より下になると、スリープ状態がイネーブルされます。

出力負荷電流が減少すると、ピーク・インダクタ電流が減少し、出力電圧を安定化された状態に保ちます。出力負荷電流がI<sub>BURST</sub>より小さなピーク・インダクタ電流しか必要としなくなると、負荷電流のさらなる減少に関係なく、ピーク・インダクタ電流はバースト・クランプによって強制的にI<sub>BURST</sub>に等しく保たれます。

平均インダクタ電流が出力負荷電流より大きいので、ITHピンの電圧は低下します。ITH電圧が低下するとスリープ・モードがイネーブルされます。このモードでは、ほとんどの回路および両方のパワースイッチがオフし、電力消費が最小に抑えられます。出力電圧が安定化状態から外れると、全ての回路が再度オンして、パワースイッチが動作を再開します。I<sub>BURST</sub>の値は望みの出力電圧リップルの大きさによって決まります。I<sub>BURST</sub>の値の増加に応じて、パルス間のスリープ期間と出力電圧リップルが増加します。非常に高いV<sub>BURST</sub>電圧設定では、出力リップルがパワーグッド・ウィンドウより大きくなることがあるので、パワーグッド・コンパレータがトリップすることがあります。

低い出力電圧リップルと効率の間を妥協させたパルス・スキップ・モードは、MODEをSV<sub>IN</sub>に接続することによって実現することができます。これによりI<sub>BURST</sub>は0Aに設定されます。この条件では、ピーク・インダクタ電流は電流コンパレータの最小オン時間によって制限されます。不連続で動作しながら、最小の出力電圧リップルが達成されます。出力負荷が非常に軽いとき、パルス・スキップにより、出力電圧を安定化状態に保ったまま、スイッチングを数サイクルにわたってスキップすることができます。

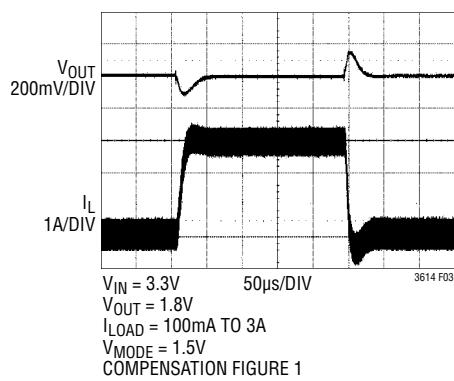

### 内部補償と外部補償

レギュレータのループ応答は負荷電流過渡応答を観察すればチェックできます。スイッチング・レギュレータはDC負荷電流ステップに対して応答するのに数サイクルを要します。負荷ステップが生じると、V<sub>OUT</sub>はΔI<sub>LOAD</sub>(ESR)に等しい量だけシフトします。ここで、ESRはC<sub>OUT</sub>の等価直列抵抗です。また、ΔI<sub>LOAD</sub>により、C<sub>OUT</sub>が充電または放電を開始して帰還誤差信号を生じ、レギュレータが電流変化に適応してV<sub>OUT</sub>をその定常状態の値に戻すように強制します。この回復期間に(安定性に問題があることを示す)過度のオーバーシュートやリンクギングが発生しないかV<sub>OUT</sub>をモニタすることができます。ITHピンを利用可能なので、広い範囲の出力コンデンサに対して過渡応答の最適化を図ることができます。

図1に示されているITHの外部部品(R<sub>C</sub>とC<sub>C</sub>)は、ほとんどのアプリケーションにおいて妥当な出発点として適切な補償を与えます。これらの値は、PCBのレイアウトを完了し、特定の出力コンデンサの種類と容量値を決定したら、過渡応答を最適化するために多少は変更することができます。出力コンデンサのさまざまな種類と値によってループの利得と位相が決まるので、まず出力コンデンサを選択する必要があります。ループの利得はR<sub>C</sub>を大きくすると増加し、ループの帯域幅はC<sub>C</sub>を小さくすると拡大します。C<sub>C</sub>を減少させるのと同じ比率でR<sub>C</sub>を増加させるとゼロの周波数は変化しないので、帰還ループの最も重要な周波数範囲で位相シフトが一定に保たれます。出力電圧のセトリングの様子は閉ループ・システムの安定性に関係します。外部コンデンサC<sub>C1</sub>(図1)はループの安定性には必要ありませんが、そのノードに結合する可能性のある高周波ノイズを除去するのに役立ちます。

「標準的応用例」セクションの最初の回路は、さらに高速な補償を採用することによりステップ応答を改善しています。

## アプリケーション情報

次に、大容量の( $>1\mu\text{F}$ )電源バイパス・コンデンサが接続されている負荷のスイッチが入れられると、さらに大きな過渡が発生します。放電しきったバイパス・コンデンサが実質的に $\text{C}_{\text{OUT}}$ と並列接続状態になるため、 $\text{V}_{\text{OUT}}$ が急低下します。負荷スイッチの抵抗が低く、しかも瞬間にドライブされると、どんなレギュレータでも出力電圧の急激なステップ変化を防止できるほど素早く電流供給を変えることはできません。デューティサイクルと負荷ステップの要件に依存して、さらに大きな出力容量が必要になることがあります。

### AVPモード

高速負荷過渡応答、制限された基板スペースおよび低コストは、マイクロプロセッサ用電源の典型的な要件です。マイクロプロセッサでは非常に高速のスルーレートの最大負荷ステップが普通に生じます。マイクロプロセッサの電圧は、このような負荷電流ステップに係わらず、公称値の約 $\pm 0.1\text{V}$ に保持しなければなりません。制御ループはこのように速く応答できないので、制御ループが応答できるまで出力コンデンサが負荷電流を供給しなければなりません。

一般的にマイクロプロセッサの過渡要件を満たすには、いくつかのコンデンサを並列に接続する必要があります。コンデンサのESRおよびESLは主に出力電圧の垂下またはオーバーシュートの大きさを決定します。

AVP機能を持たず、多数のタンタル出力コンデンサが並んだLTC3614を考えてみてください。非常に高速なスルーレートの負荷ステップが生じると、電圧変動が両方向に(最大負荷から最小負荷への過渡、および最小負荷から最大負荷への過渡に対して)見られるでしょう。

ITHピンが $\text{SV}_{\text{IN}}$ に接続されると、アクティブ電圧ポジショニング(AVP)モードと内部補償が選択されます。

AVPモードでは帰還回路の利得を下げて意図的に負荷レギュレーションを弛めるので、負荷電流によって出力電圧がわずかに変化します。負荷電流が突然増加するとき、出力電圧は公称値よりわずかに高いレベルからスタートするので、より大きく垂下しても規定電圧範囲内に留まることができます。負荷電流が突然減少すると、出力電圧は公称値より低いレベルからスタートするので、より大きくオーバーシュートしても規定電圧範囲内にとどまることができます(図3と図4を参照)。

利点は、出力フィルタの容量を大きくしなくとも、一定の負荷ステップに対してピーク・トゥ・ピーク出力電圧変化が下がることです。あるいは、出力電圧フィルタの容量を減らしながら同じピーク・トゥ・ピーク過渡応答を維持することができます。AVPモードではループ利得が下がるので、外部補償は不要です。

図3. 強制連続モードの負荷ステップ過渡

(AVPは非アクティブ)

図4. 強制連続モードの負荷ステップ過渡

(AVPモード)

## アプリケーション情報

### DDRモード

LTC3614は、MODEピンが強制連続モードに設定されていると、電流をソースすることもシンクすることもできます。

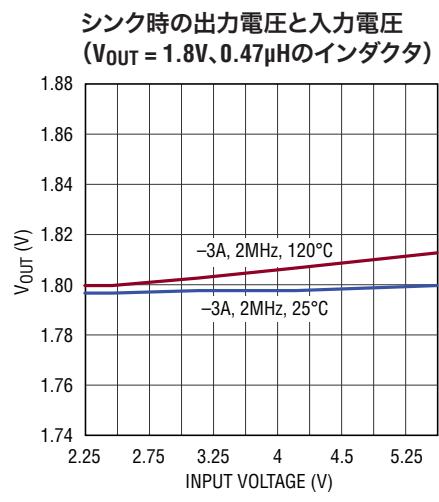

1MHzの周波数および0.47μHのインダクタでは、電流シンクは標準3Aに制限されますが、もっと高い周波数および低い出力電圧ではさらに下がることがあります。より高いリップル電流を許容できれば、より小さいインダクタ値を使ってシンク電流のリミットを上げることができます。詳細については、「標準的性能特性」の曲線を参照してください。

さらに、SRLIM/DDRピンをSV<sub>IN</sub>に接続すると、より低い外部リファレンス電圧とトラッキング出力電圧が可能です。「出力電圧トラッキング入力」と「外部リファレンス入力」のセクションを参照してください。

### ソフトスタート

RUNピンを使ってLTC3614をシャットダウンすることができます。RUNピンをSGNDに接続すると、LTC3614は低消費電流( $I_Q < 1\mu A$ )のシャットダウン状態になります。

LTC3614は、RUNピンを“H”にすることによってイネーブルされます。ただし、印加される電圧はSV<sub>IN</sub>を超えてはなりません。アプリケーションによっては、SV<sub>IN</sub>とPV<sub>IN</sub>がまだ0Vの間にRUN信号が別の電源領域で生成され、“H”にドライブされます。この場合、SV<sub>IN</sub>に1MΩ抵抗または100kΩ抵抗のいずれかとショットキーダイオードを追加接続することにより、RUNピンに流れ込む電流を制限する必要があります。

RUNピンを“H”に引き上げてLTC3614をイネーブルすると、デバイスはソフトスタート状態になります。ソフトスタートのタイプはTRACK/SSピンによって設定されます。

1. TRACK/SSをSV<sub>IN</sub>に接続すると内部ソフトスタート回路が選択されます。この回路は出力電圧を1ms以内に最終値までランプさせます。

2. ソフトスタートの時間を延長したい場合、図1に示されているように、TRACK/SSピンに抵抗とコンデンサを接続してそれを外部から設定することができます。TRACK/SSピンは、TRACK/SSが0.6Vより上に引き上げられるまではV<sub>FB</sub>の内部リファレンスの値を減らします。外部ソフトスタートによる起動時間は次式を使って計算することができます。

$$t_{SS} = R_{SS} \cdot C_{SS} \cdot \ln\left(\frac{SV_{IN}}{SV_{IN} - 0.6V}\right)$$

3. 別の電源の出力電圧をトラッキングするのにTRACK/SSピンを使うことができます。

RUNピンが“H”に引き上げられ、LTC3614がオンするたびに、外部コンデンサを放電するためにTRACK/SSピンが内部で10マイクロ秒の間プルダウンされます。この放電時間は一般に約33nFまでのコンデンサに適切です。もっと大きなコンデンサが必要であれば、外部ソフトスタート抵抗をRUNピンに接続します。

図5. SWピンのスルーレートとSRLIM/DDRの抵抗:オープン、100k、10k

## アプリケーション情報

内部と外部のどちらのソフトスタート状態でも、MODEピンは無視されて、ソフトスタートでは常にパルス・スキップ・モードになります。さらに、PGOODピンは“L”に保たれ、スイッチング周波数のフォールドバックはディスエーブルされます。

### プログラム可能なスイッチ・ピンのスルーレート

スイッチング周波数を上げるほど、スイッチングするときに必要な遷移時間を最小にして、電力損失およびスイッチがセトリングするためのブランディング時間を最小にすることは望ましいことです。ただし、スイッチ・ノードのスルーレートが高速だと、外部放射EMIが比較的高くなり、内蔵電源の過渡が高くなり、アプリケーションによっては問題を生じことがあります。

ユーザーはLTC3614のSRLIM/DDRピンを使ってスイッチング・ノードSWのスルーレートを制御することができます。このピンをグランドに接続すると最速スルーレートが選択されます。ピンがオープンだと最も遅いスルーレートが選択されます。SRLIMピンからグランドに10k~100Kの抵抗を接続すると、スルーレートが最大値と最小値の中間に調整されます。スイッチ・ノードのdV/dtを下げる、電源とグランドのリンクが大幅に減少し、放射EMIが低下します。

非常に高いスイッチング周波数では特に注意が必要です。最も遅いスルーレートを使うと(SRLIMをオープン)、最小デューティ・サイクル能力が低下する可能性があります。

### 出力電圧トラッキング入力

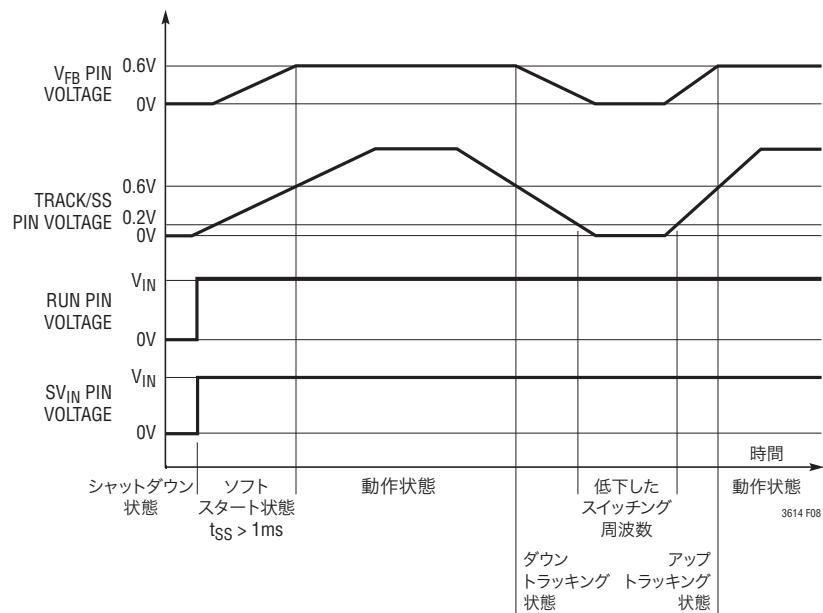

DDRピンがSVINに接続されていない場合、VTRACK/SSが0.6Vを超えると動作状態に入り、MODE選択、パワーグッドおよび電流フォールドバックの回路がイネーブルされます。

動作状態では、別の電源の出力電圧をトラッキングダウン/トラッキングアップするのにTRACK/SSピンを使うことができます。VTRACK/SSが0.6Vより下になると、LTC3614はダウントラッキング状態に入り、VOUTはTRACK/SS電圧を基準にします。TRACK/SSピンが0.2Vより下になると、スイッチング周波数が下がり、最小デューティ・サイクルの制限のために出力がTRACK/SSピンに従うことが妨げられないようになります。VTRACK/SSが再度0.6Vを超えると、VOUTが内部精密リファレンスを基準にするようになると、再び動作状態になります(図8を参照)。

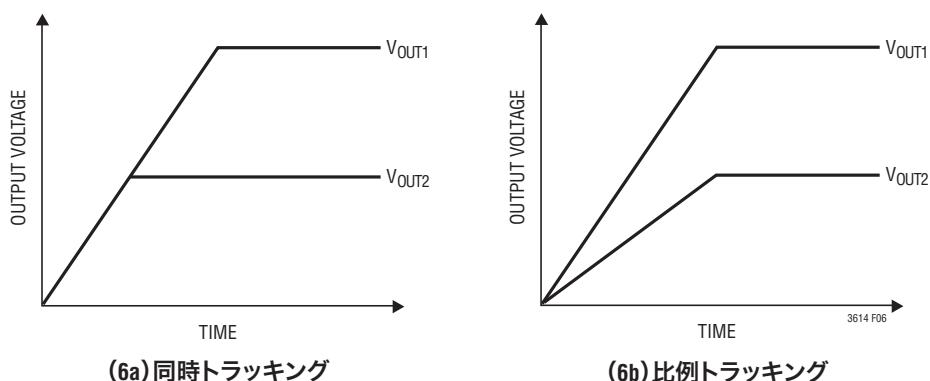

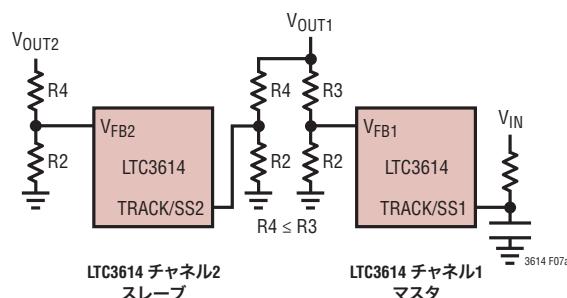

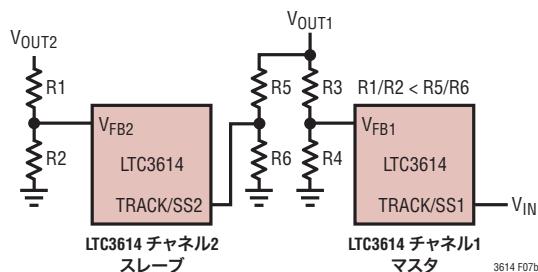

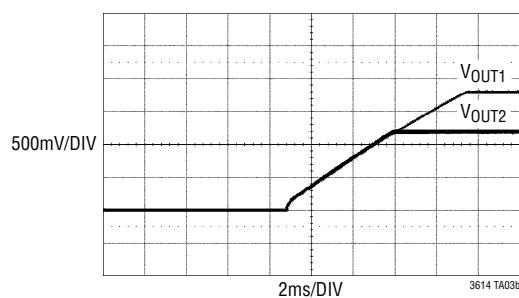

TRACK/SSピンを使って、図6に示されているように、出力電圧を同時トラッキングまたは比例トラッキングに設定することができます。

図6. 出力電圧トラッキングの2つの異なるモード

## アプリケーション情報

図6aの同時トラッキング動作を実現するには、追加の抵抗分割器をマスタ・チャネルの出力に接続し、そのミッドポイントをスレーブ・チャネルのTRACK/SSピンに接続します。この分割器の比はスレーブ・チャネルの帰還分割器の比と同じになります(図7a)。このトラッキング・モードでは、マスタ・チャネルの出力をスレーブ・チャネルの出力よりも高く設定する必要があります。図6bの比例トラッキング動作を実現するには、図7bで指定されているように、異なる抵抗分割器の値を使う必要があります。

図7a. 同時トラッキングのセットアップ

図7b. 比例トラッキングのセットアップ

同時スタートアップでは、スレーブ・チャネルのTRACK/SSピンの電圧値は、内部ソフトスタート時間(約1ms)の後、最終リファレンス値に達する必要があります。確実にこうするため、マスタのスタートアップ時間を外部コンデンサと抵抗によって調整する必要があります。

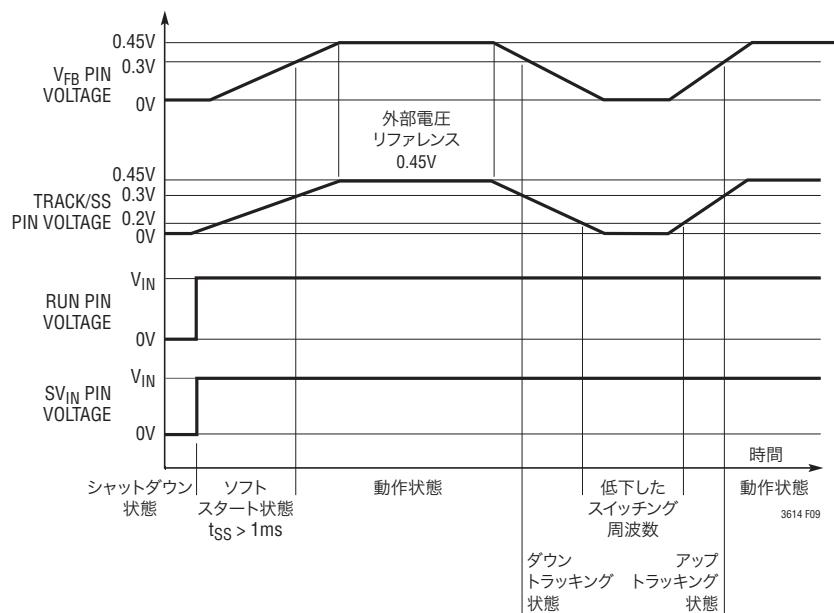

### 外部リファレンス入力(DDRモード)

DDRピンがSVINに接続されている場合(DDRモード)、VTRACK/SSが0.3Vを超えると動作状態に入り、VTRACK/SS電圧が0.6Vより下がるとトラッキングダウン動作が可能です。

これにより、必要に応じて、TRACK/SSを0.3Vと0.6Vの間の外部リファレンスとして使うことができます。DDRモードの動作状態の間、実際のTRACK/SSピンの電圧値が0.3Vと0.6Vの間であれば、パワーグッド・ウィンドウはその電圧に関連して移動します。注記:TRACK/SSの電圧が0.6Vの場合、トラッキング回路または内部リファレンスのどちらでも使うことができます。

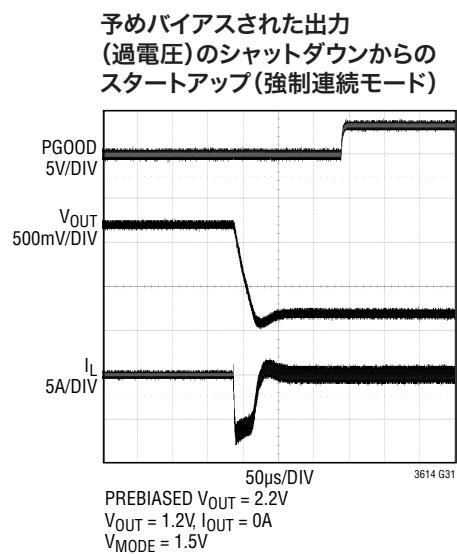

パワーアップ/パワーダウンのトラッキングの間、出力電流フォールドバックはディスエーブルされ、PGOODピンは常にプルダウンされます(図9)。

## アプリケーション情報

図8. DDRピンはSV<sub>IN</sub>に接続されていない

図9. DDRピンはSV<sub>IN</sub>に接続されている。DDRアプリケーションの例

## アプリケーション情報

### 効率に関する検討事項

スイッチング・レギュレータの効率は「出力電力÷入力電力×100%」で表されます。個々の損失を解析して、効率を制限する要素がどれであり、また何が変化すれば最も効率が改善されるかを判断できる場合がよくあります。効率は次式で表すことができます。

$$\text{効率} = 100\% - (L_1 + L_2 + L_3 + \dots)$$

ここで、 $L_1$ 、 $L_2$ などは入力電力に対するパーセンテージで表した個々の損失です。

回路内の電力を消費する全ての要素で損失が生じますが、損失の大部分は2つの主な損失要因によって生じます。 $V_{IN}$ の消費電流による損失と $I^2R$ 損失です。非常に低い負荷電流では $V_{IN}$ の消費電流による損失が効率の損失を支配するのに対して、中程度から高い負荷電流では $I^2R$ 損失が効率の損失を支配します。標準的な効率曲線では、非常に低い負荷電流での効率曲線は誤解を与えかねません。というのは、実際の電力損失は通常大したことはないからです。

1.  $V_{IN}$ の消費電流は2つの要素からなります。「電気的特性」で与えられているDCバイアス電流および内部のメイン・スイッチと同期スイッチのゲート充電電流です。内部パワーMOSFETスイッチのゲート容量をスイッチングすると、ゲート充電電流が流れます。ゲートが“L”から“H”、そして再び“L”に切り替わるたびに、 $V_{IN}$ からグランドに微小電荷 $dQ$ が移動します。したがって、 $dQ/dt$ はゲート電荷により $V_{IN}$ から流出する電流であり、一般にDCバイアス電流より大きくなります。DCバイアス損失とゲート電荷損失は両方とも $V_{IN}$ に比例するので、それらの影響は電源電圧が高くなると顕著になります。

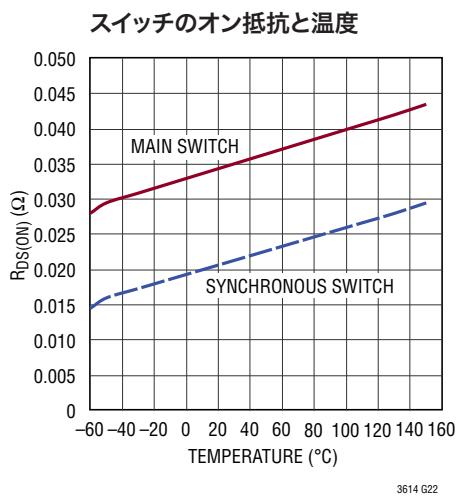

2.  $I^2R$ 損失は内部スイッチの抵抗 $R_{SW}$ と外部インダクタの抵抗 $R_L$ から計算されます。連続モードでは、インダクタ $L$ を流れる平均出力電流は、メイン・スイッチと同期スイッチの間で「こま切れ」にされます。したがって、SWピンを見たときの直列抵抗は、次式のとおり、トップMOSFETとボトムMOSFETの両方の $R_{DS(ON)}$ およびデューティサイクル(DC)の関数になります。

$$R_{SW} = (R_{DS(ON)TOP}(DC) + (R_{DS(ON)BOT})(1-DC))$$

トップMOSFETとボトムMOSFETの両方の $R_{DS(ON)}$ を「標準的性能特性」の曲線から求めることができます。 $I^2R$ 損失を求めるには、単に $R_{SW}$ を $R_L$ に加え、その結果に平均出力電流の2乗を掛けます。

$C_{IN}$ や $C_{OUT}$ のESRによる損失やインダクタのコア損失などの他の損失は一般に全損失の2%以下に過ぎません。

## パッケージ

### 熱に関する検討事項

ほとんどのアプリケーションで、LTC3614は効率が高いので大きな発熱はありません。

ただし、周囲温度が高く、(ドロップアウトの場合のように)低い電源電圧、高いデューティ・サイクルでLTC3614が動作するアプリケーションでは、発熱がデバイスの最大接合部温度を超えることがあります。接合部温度が約170°Cに達すると、両方のパワースイッチがオフし、SWノードが高インピーダンスになります。

LTC3614が最大接合部温度を超えるのを防ぐには、熱解析が必要です。温度上昇は次式で与えられます。

$$T_{RISE} = (P_D) (\theta_{JA})$$

ここで、 $P_D$ はレギュレータの電力損失、 $\theta_{JA}$ はダイの接合部から周囲温度への熱抵抗です。接合部温度 $T_J$ は次式で与えられます。

$$T_J = T_A + T_{RISE}$$

ここで、 $T_A$ は周囲温度です。

一例として、入力電圧が3.3V、負荷電流が4A、周囲温度が85°Cでドロップアウト状態のLTC3614について考えます。「標準的性能特性」の「スイッチ抵抗」のグラフから、Pチャネル・スイッチの $R_{DS(ON)}$ 抵抗は0.038Ωです。したがって、デバイスによる電力損失は次のとおりです。

$$P_D = (I_{OUT})^2 \cdot R_{DS(ON)} = 0.61W$$

QFNパッケージの場合、 $\theta_{JA}$ は38°C/Wです。

したがって、85°Cの周囲温度で動作しているレギュレータの接合部温度はおよそ次のようにになります。

$$T_J = 0.61W \cdot 38^{\circ}\text{C}/\text{W} + 85^{\circ}\text{C} = 108^{\circ}\text{C}$$

実際の接合部温度は125°Cの絶対最大接合部温度を超えると判断できます。

非常に低い入力電圧では、スイッチ抵抗( $R_{DS(ON)}$ )が増加するので、接合部温度はさらに高くなることに注意してください。高い周囲温度および低い入力電圧で最大負荷電流を使うことは推奨しません。

LTC3614の熱性能を最大にするには、露出パッドをグランド・プレーンに半田付けします。「PCボードのレイアウトのチェックリスト」を参照してください。

### 設計例

設計例として、以下の仕様のアプリケーションにLTC3614を使う場合を考えます。

$V_{IN} = 2.25V \sim 5.5V$ ,  $V_{OUT} = 1.8V$ ,  $I_{OUT}(\text{MAX}) = 4A$ ,  $I_{OUT}(\text{MIN}) = 200mA$ ,  $f = 2.6MHz$ .

高負荷電流と低負荷電流の両方で効率が重要なので、Burst Mode動作を利用します。

最初に、タイミング抵抗を計算します。

$$R_T = \frac{3.82^{11}\text{Hz}}{2.6\text{MHz}} k - 16k = 130k\Omega$$

次に、最大 $V_{IN}$ で約33%のリップル電流になるようにインダクタ値を計算します。

$$L = \left( \frac{1.8V}{2.6MHz \cdot 1.3A} \right) \cdot \left( 1 - \frac{1.8V}{5.5V} \right) = 0.35\mu\text{H}$$

0.33μHの標準値のインダクタを使うと、最大リップル電流は以下のようになります。

$$\Delta I_L = \left( \frac{1.8V}{2.6MHz \cdot 0.33\mu\text{H}} \right) \cdot \left( 1 - \frac{1.8V}{5.5V} \right) = 1.41A$$

$C_{OUT}$ は出力電圧リップルの要件を満たすESRとループの安定性に必要なバルク容量に基づいて選択します。このデザインでは、X5RまたはX7Rの誘電体と共に100μFのセラミック・コンデンサを使います。

## パッケージ

$V_{IN} = 2V_{OUT}$ のワーストケース条件を仮定して、次のような最大電流定格に対して  $C_{IN}$  を選択します。

$$I_{RMS} = 4A \cdot \frac{1.8V}{3.6V} \cdot \sqrt{\left(\frac{3.6V}{1.8V} - 1\right)} = 2A_{RMS}$$

ほとんどのアプリケーションでは、 $P_{IN}$  を4個の  $10\mu F$ ~ $22\mu F$  のコンデンサでデカップリングすれば十分です。

$R_2 = 196k$  に設定すると、次式を解いて  $R_1$  の値を決定することができます。

$$R_1 = 196k \cdot \left(\frac{1.8V}{0.6V} - 1\right)$$

$R_1$  には  $392k$  の値を選択します。

最後に、TRACK/SS に接続するコンデンサと抵抗の適切な値を選択して、ソフトスタートの時間を定めます。最小  $t_{SS} = 5ms$  および  $2M\Omega$  の抵抗を設定すると、最大  $SV_{IN} = 5.5V$  を使って次式を解くことができます。

$$C_{SS} = \frac{5ms}{2M\Omega \cdot \ln\left(\frac{5.5V}{5.5V - 0.6V}\right)} = 21.6nF$$

$22nF$  の標準値により、 $5ms$  の最小ソフトスタート時間が保証されます。

この設計例の回路を図1に示します。

## PCボードのレイアウトのチェックリスト

プリント回路基板をレイアウトするときには、以下のチェックリストを使用して LTC3614 が正しく動作するようにします。

1. グランド・プレーンを推奨します。グランド・プレーン層が使われていなければ、信号グランドと電源グランドを分離し、小信号用部品は1点で SGND ピンに戻し、この1点を LTC3614 の近くで PGND ピンに接続します。

2. 入力コンデンサ ( $C_{IN}$ ) の (+) 端子は  $P_{IN}$  ピンにできるだけ近づけ、(-) 端子は露出パッド (PGND) にできるだけ近づけて接続します。このコンデンサは内部パワーMOSFETに AC 電流を供給します。

3. スイッチング・ノード SW は全ての敏感な小信号ノードから離します。

4. 全ての層の全ての未使用領域を銅で覆います。銅で覆うと電力部品の温度上昇が小さくなります。最良の性能を得るため、銅領域を PGND (露出パッド) に接続します。

5.  $V_{FB}$  ピンは帰還抵抗に直接接続します。抵抗分割器は  $V_{OUT}$  と SGND の間に接続する必要があります。

## 標準的応用例

高速補償を備え、ステップ応答を改善した、

2.25MHz の汎用降圧レギュレータ

効率と出力電流

負荷ステップ応答

(強制連続モード)

## 標準的応用例

1MHz の外部クロックを使った同時トラッキング出力のマスターとスレーブ

同時スタートアップ

同時トラッキングアップおよびトラッキングダウン

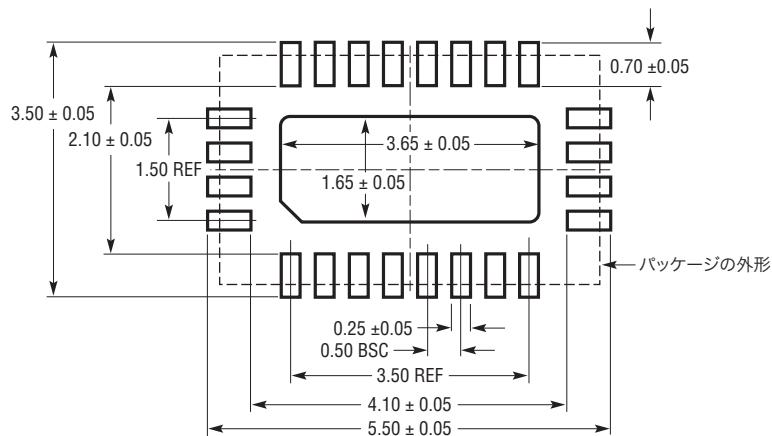

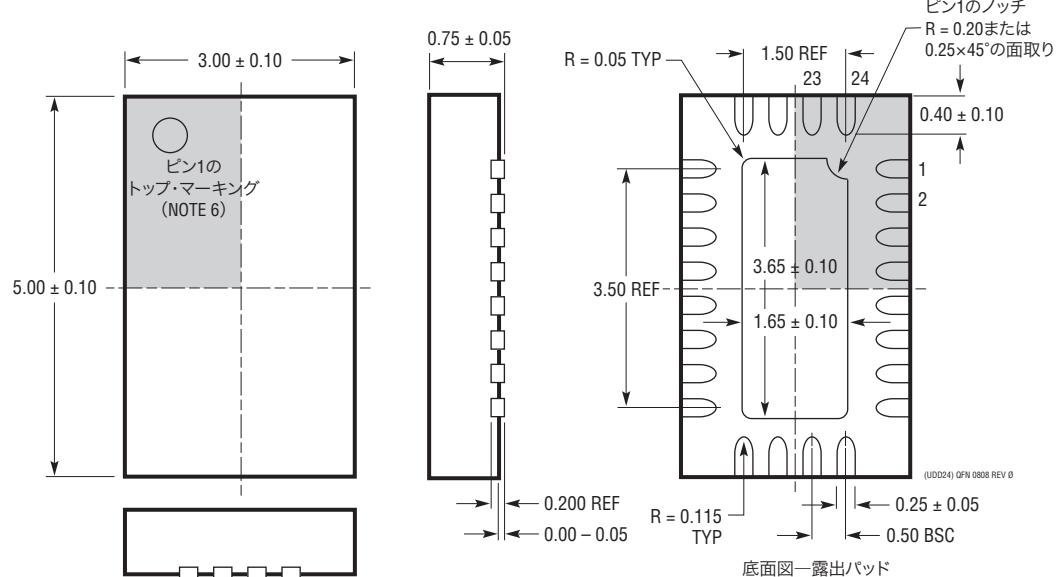

## パッケージ

最新のパッケージの図面については、<http://www.linear-tech.co.jp/designtools/packaging/> をご覧ください。

**UDD Package**

**24-Lead Plastic QFN (3mm × 5mm)**

(Reference LTC DWG # 05-08-1833)

推奨する半田パッドのピッチと寸法

半田付けされない領域には半田マスクを使用する

### 注記:

1. 図はJEDECのパッケージ外形ではない

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで0.15mmを超えないこと

5. 露出パッドは半田マッキとする

6. 灰色の部分はパッケージの上面と底面のピン1の位置の参考に過ぎない

## 改訂履歴

| REV | 日付    | 概要                                                                                                                                                            | ページ番号                               |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| A   | 11/10 | 電気的特性表のLoad Regulation $I_{TH}$ Voltageを更新。<br>「電気的特性」セクションのNote 2を更新。<br>「アプリケーション情報」の「ソフトスタート」セクションの文章を更新。<br>「関連製品」を更新。                                    | 3、11、12<br>4<br>19<br>30            |

| B   | 11/13 | HグレードおよびMPグレードと、適用可能な温度範囲に対する言及を追加。<br>Note 2を修正。<br>「標準的性能特性」のグラフを修正。<br>「インダクタのコアの選択」セクションを修正。<br>「入力コンデンサ( $C_{IN}$ )の選択」セクションを修正。<br>「熱に関する検討事項」セクションを修正。 | 全体<br>4<br>6、7<br>14、15<br>15<br>24 |

| C   | 5/14  | Top Switch Current Limit(Duty Cycle=100%)のMin値を5Aに変更。                                                                                                         | 3                                   |

LTC3614

## 標準的應用例

### V<sub>DD</sub>の比例トラッキングによるDDRの終端(1MHz)

## 比例スタートアップ

## 関連製品

| 製品番号     | 説明                                                                     | 注釈                                                                                                                                                                     |

|----------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3616  | 5.5V、6A (I <sub>OUT</sub> )、4MHz同期整流式降圧DC/DCコンバータ                      | 95%の効率、V <sub>IN(MIN)</sub> = 2.25V、V <sub>IN(MAX)</sub> = 5.5V、V <sub>OUT(MIN)</sub> = 0.6V、I <sub>Q</sub> = 70μA、I <sub>SD</sub> < 1μA、3mm×5mm QFN-24パッケージ           |

| LTC3612  | 5.5V、3A (I <sub>OUT</sub> )、4MHz同期整流式降圧DC/DCコンバータ                      | 95%の効率、V <sub>IN(MIN)</sub> = 2.25V、V <sub>IN(MAX)</sub> = 5.5V、V <sub>OUT(MIN)</sub> = 0.6V、I <sub>Q</sub> = 70μA、I <sub>SD</sub> < 1μA、3mm×4mm QFN-20、TSSOP20Eパッケージ  |

| LTC3418  | 5.5V、8A (I <sub>OUT</sub> )、4MHz同期整流式降圧DC/DCコンバータ                      | 95%の効率、V <sub>IN(MIN)</sub> = 2.25V、V <sub>IN(MAX)</sub> = 5.5V、V <sub>OUT(MIN)</sub> = 0.8V、I <sub>Q</sub> = 380μA、I <sub>SD</sub> < 1μA、5mm×7mm QFN-38パッケージ          |

| LTC3415  | 5.5V、7A (I <sub>OUT</sub> )、1.5MHz同期整流式降圧DC/DCコンバータ                    | 95%の効率、V <sub>IN(MIN)</sub> = 2.5V、V <sub>IN(MAX)</sub> = 5.5V、V <sub>OUT(MIN)</sub> = 0.6V、I <sub>Q</sub> = 450μA、I <sub>SD</sub> < 1μA、5mm×7mm QFN-38パッケージ           |

| LTC3416  | 5.5V、4A (I <sub>OUT</sub> )、4MHz同期整流式降圧DC/DCコンバータ                      | 95%の効率、V <sub>IN(MIN)</sub> = 2.25V、V <sub>IN(MAX)</sub> = 5.5V、V <sub>OUT(MIN)</sub> = 0.8V、I <sub>Q</sub> = 64μA、I <sub>SD</sub> < 1μA、TSSOP20Eパッケージ                 |

| LTC3413  | 5.5V、3A (I <sub>OUT</sub> シンク/ソース)、2MHzモリシック同期整流式レギュレータ(DDR/QDRメモリ終端用) | 90%の効率、V <sub>IN(MIN)</sub> = 2.25V、V <sub>IN(MAX)</sub> = 5.5V、V <sub>OUT(MIN)</sub> = V <sub>REF</sub> /2、I <sub>Q</sub> = 280μA、I <sub>SD</sub> < 1μA、TSSOP16Eパッケージ |

| LTC3412A | 5.5V、3A (I <sub>OUT</sub> )、4MHz同期整流式降圧DC/DCコンバータ                      | 95%の効率、V <sub>IN(MIN)</sub> = 2.5V、V <sub>IN(MAX)</sub> = 5.5V、V <sub>OUT(MIN)</sub> = 0.8V、I <sub>Q</sub> = 60μA、I <sub>SD</sub> < 1μA、4mm×4mm QFN-16、TSSOP16Eパッケージ   |