## 特長

- 3.3A、42Vの結合されたパワースイッチ

- マスタ/スレーブ (1.9A/1.4A) スイッチ設計

- 出力の短絡保護

- 広い入力電圧範囲: 2.5V~22Vで動作、過渡電圧は最大40V

- スイッチング周波数: 最大2.5MHz

- 昇圧、SEPIC、反転またはフライバック・コンバータとして容易に構成可能

- ユーザーが設定可能な低電圧ロックアウト

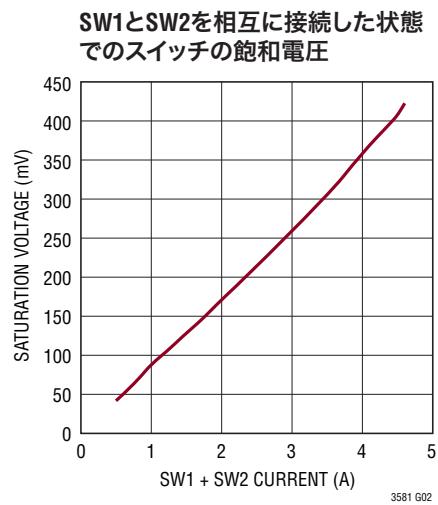

- 低V<sub>CESAT</sub>スイッチ: 250mV/2.75A (標準)

- 外部クロックに同期可能

- 他のスイッチング・レギュレータに同期可能

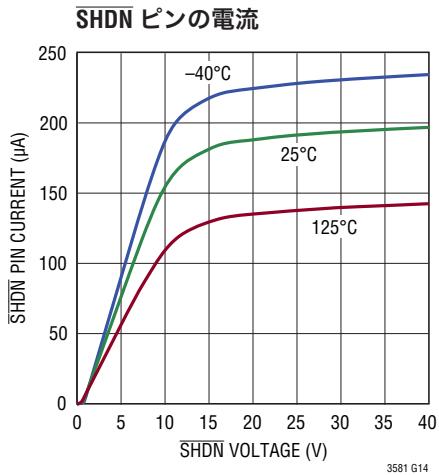

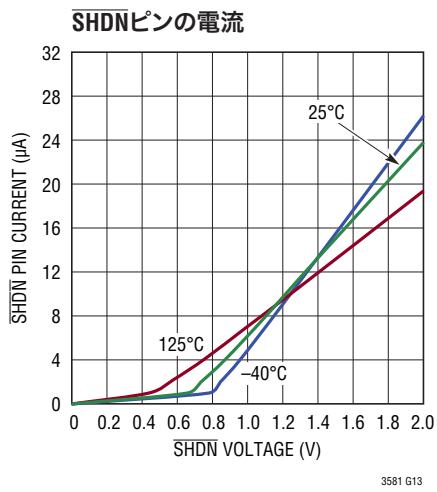

- ゆっくり変化する入力信号を受容する高利得のSHDNピン

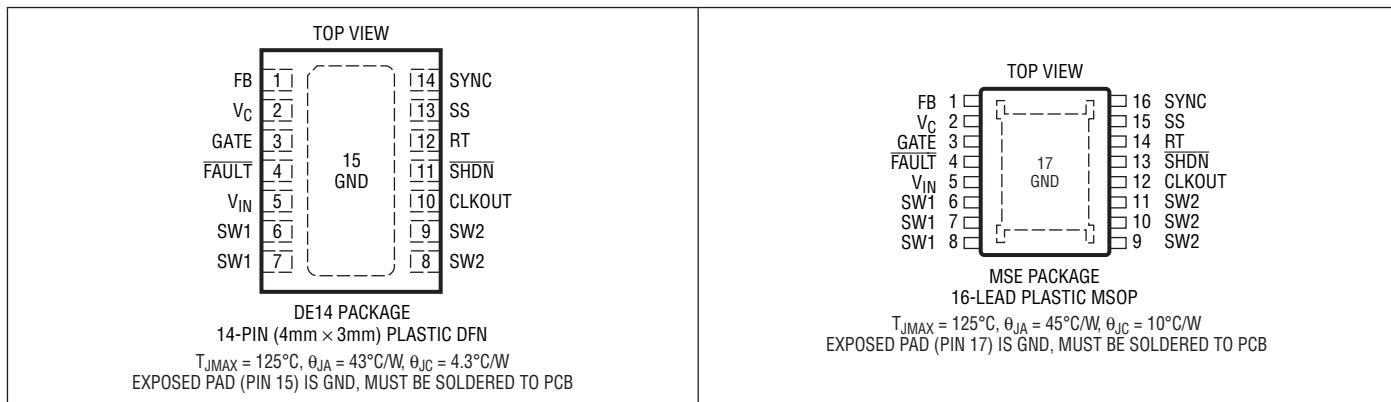

- 14ピン4mm × 3mm DFNパッケージと16ピンMSEパッケージ

## アプリケーション

- ローカル電源

- 真空蛍光ディスプレイ (VFD) のバイアス電源

- TFT-LCDのバイアス電源

- 車載エンジン制御ユニット (ECU) の電源

、LT、LTC、LTM、Linear Technology および Linear のロゴはリニアテクノロジー社の登録商標です。他の全ての商標はそれぞれの所有者に所有権があります。7579816 を含む米国特許によって保護されています。

## 概要

LT<sup>®</sup>3581 は、出力の短絡状態、入力 / 出力の過電圧状態、および過熱状態からデバイスを保護するのに役立つフォルト保護機能を内蔵した PWM DC/DC コンバータです。このデバイスは 42V のマスタ・スイッチと 42V のスレーブ・スイッチで構成されており、これらのスイッチを互いに接続することにより、電流制限値を合計 3.3A することができます。

LT3581 は多くのローカル電源設計に最適です。このデバイスは昇圧コンバータ、SEPIC コンバータ、反転コンバータまたはフライバック・コンバータのいずれかに容易に構成可能で、5V 入力から 12V/830mA または -12V/625mA を生成可能です。さらに、LT3581 はスレーブ・スイッチを備えているので、非常に効率的で、従来の回路に比べて外付け部品が少なくてすむ高電圧、高電力のチャージポンプ構成にすることができます。

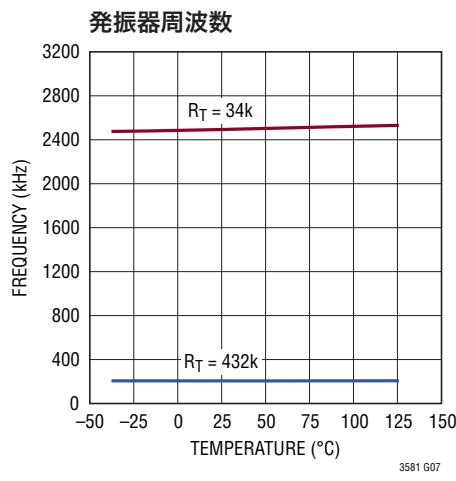

LT3581 のスイッチング周波数は 200kHz ~ 2.5MHz の範囲で設定できます。このデバイスは、RT ピンとグランドの間に接続された抵抗によって周波数が設定される内部クロックに同期することも、外部クロックに同期することもできます。バッファされたクロック信号は CLKOUT ピンからドライブされるので、これを使用して他の互換スイッチング・レギュレータ IC を LT3581 に同期させることができます。

また、LT3581 は、緩やかに変化する入力信号を受容する革新的な SHDN ピン回路と調整可能な低電圧ロックアウトを特長としています。この他に、周波数フォールドバックやソフトスタートなどの機能も内蔵しています。LT3581 は 14 ピン 4mm×3mm DFN パッケージと 16 ピン MSE パッケージで供給されます。

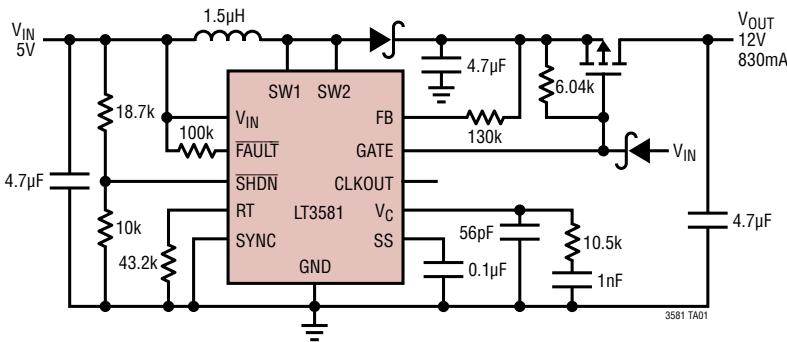

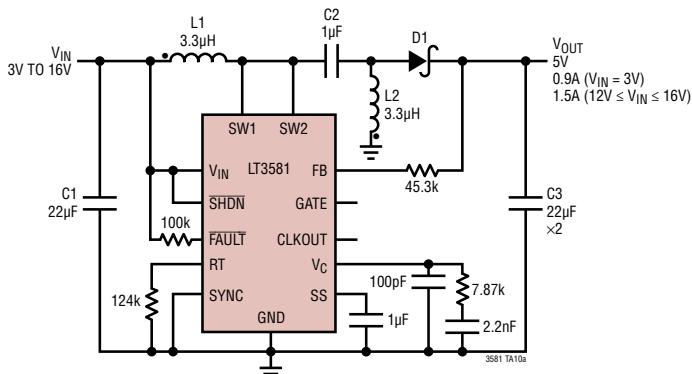

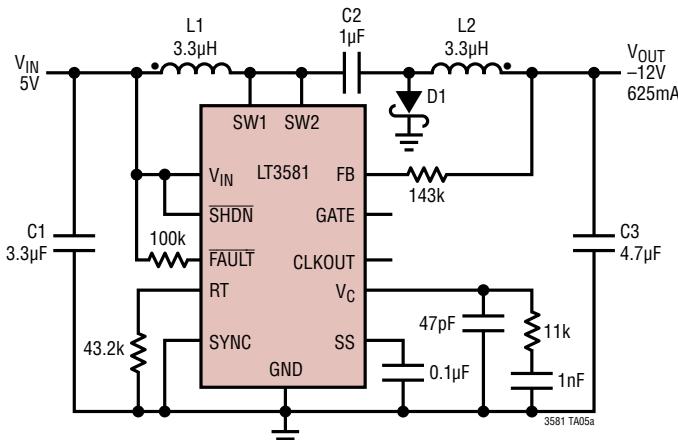

## 標準的応用例

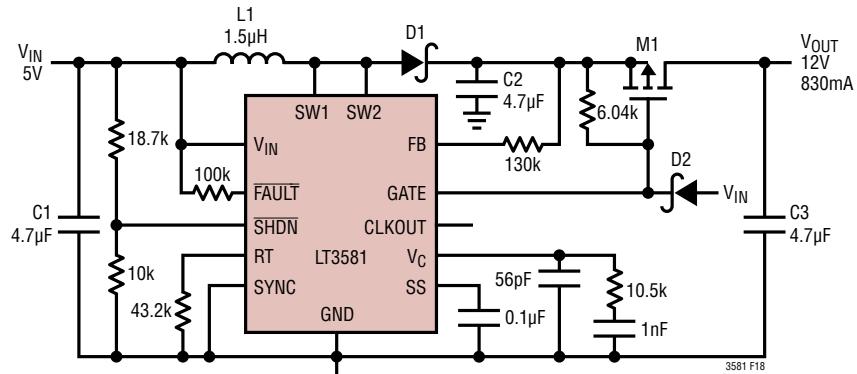

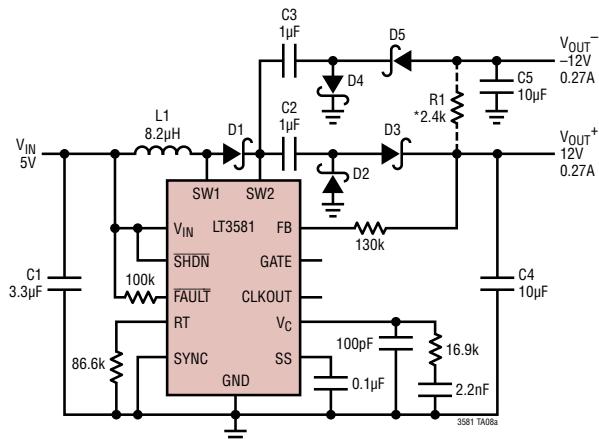

### 出力の短絡に対して保護された、2MHzで動作する5Vから12Vの昇圧コンバータ

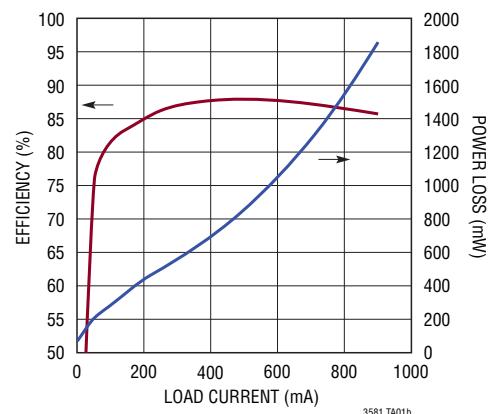

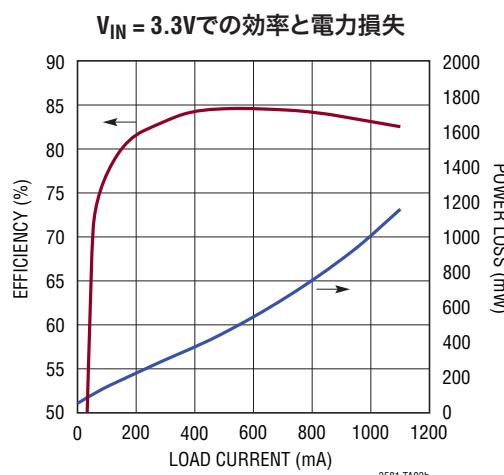

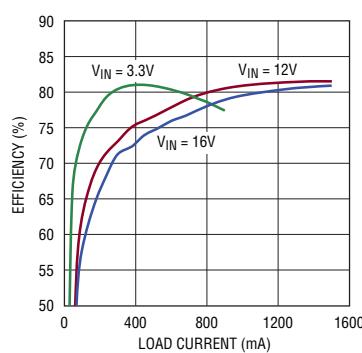

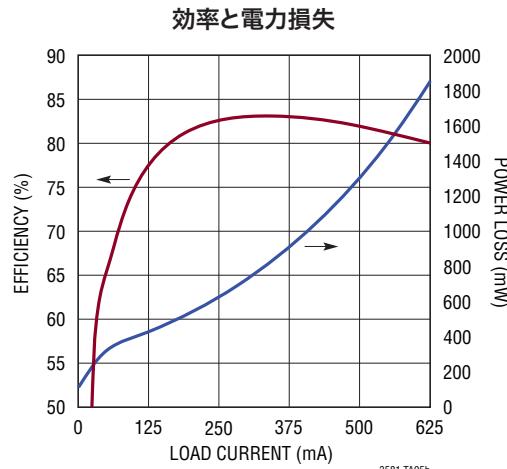

### 効率および電力損失と負荷電流

## 絶対最大定格

(Note 1)

|             |            |                      |                |

|-------------|------------|----------------------|----------------|

| $V_{IN}$ 電圧 | -0.3V~40V  | FAULTの電流             | $\pm 500\mu A$ |

| SW1/SW2の電圧  | -0.4V~42V  | CLKOUTの電圧            | -0.3V~3V       |

| RTの電圧       | -0.3V~5V   | CLKOUTの電流            | 1mA            |

| SS、FBの電圧    | -0.3V~2.5V | 動作接合部温度範囲            |                |

| $V_C$ 電圧    | -0.3V~2V   | LT3581E (Note 2, 4)  | -40°C~125°C    |

| SHDNの電圧     | -0.3V~40V  | LT3581I (Note 2, 4)  | -40°C~125°C    |

| SYNCの電圧     | -0.3V~5.5V | LT3581H (Notes 2, 4) | -40°C~150°C    |

| GATEの電圧     | -0.3V~80V  | 保存温度範囲               | -65°C~150°C    |

| FAULTの電圧    | -0.3V~40V  |                      |                |

## ピン配置

## 発注情報

| 無鉛仕上げ          | テープアンドリール        | 製品マーキング* | パッケージ                           | 温度範囲           |

|----------------|------------------|----------|---------------------------------|----------------|

| LT3581EDE#PBF  | LT3581EDE#TRPBF  | 3581     | 14-Lead (4mm x 3mm) Plastic DFN | -40°C to 125°C |

| LT3581IDE#PBF  | LT3581IDE#TRPBF  | 3581     | 14-Lead (4mm x 3mm) Plastic DFN | -40°C to 125°C |

| LT3581HDE#PBF  | LT3581HDE#TRPBF  | 3581     | 14-Lead (4mm x 3mm) Plastic DFN | -40°C to 150°C |

| LT3581EMSE#PBF | LT3581EMSE#TRPBF | 3581     | 16-Lead Plastic MSOP            | -40°C to 125°C |

| LT3581IMSE#PBF | LT3581IMSE#TRPBF | 3581     | 16-Lead Plastic MSOP            | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

\*温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

**電気的特性** ●は全動作温度範囲の規格値を意味する。それ以外は $T_A=25^\circ\text{C}$ での値。

注記がない限り、 $V_{IN} = 5\text{V}$ 、 $V_{SHDN} = V_{IN}$ 、 $V_{FAULT} = V_{IN}$  (Note 2)

| PARAMETER                                         | CONDITIONS                                                  | MIN | TYP   | MAX   | UNITS            |

|---------------------------------------------------|-------------------------------------------------------------|-----|-------|-------|------------------|

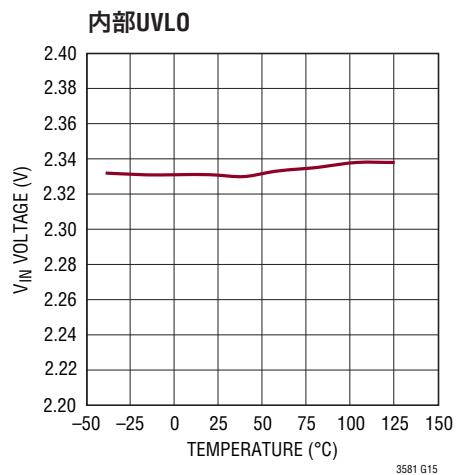

| Minimum Input Voltage                             |                                                             | ●   | 2.3   | 2.5   | V                |

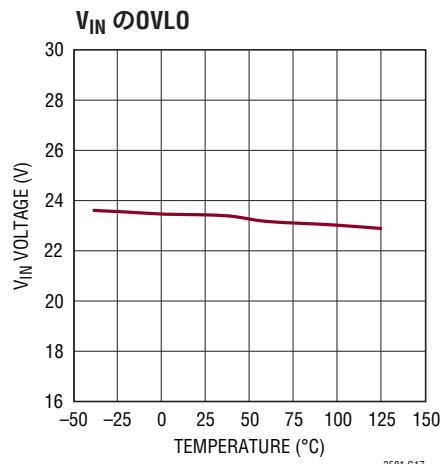

| $V_{IN}$ Overvoltage Lockout                      |                                                             |     | 22.1  | 23.5  | 25               |

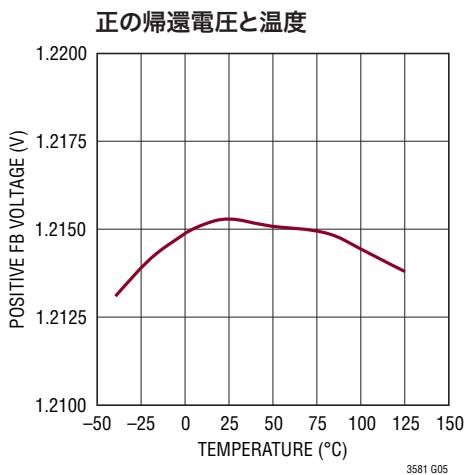

| Positive Feedback Voltage                         |                                                             | ●   | 1.195 | 1.215 | 1.230            |

| Negative Feedback Voltage                         |                                                             | ●   | 3     | 9     | 16               |

| Positive FB Pin Bias Current                      | $V_{FB}$ = Positive Feedback Voltage, Current into Pin      | ●   | 81    | 83.3  | 85               |

| Negative FB Pin Bias Current                      | $V_{FB}$ = Negative Feedback Voltage, Current out of Pin    | ●   | 81    | 83.3  | 85.5             |

| Error Amp Transconductance                        | $\Delta I = 10\mu\text{A}$                                  |     |       | 270   | $\mu\text{mhos}$ |

| Error Amp Voltage Gain                            |                                                             |     |       | 70    | V/V              |

| Quiescent Current                                 | Not Switching                                               |     |       | 1.9   | 2.3              |

| Quiescent Current in Shutdown                     | $V_{SHDN} = 0\text{V}$                                      |     |       | 0     | 1                |

| Reference Line Regulation                         | $2.5\text{V} \leq V_{IN} \leq 20\text{V}$                   |     |       | 0.01  | 0.05             |

| Switching Frequency, $f_{osc}$                    | $R_T = 34\text{k}$                                          | ●   | 2.25  | 2.5   | 2.75             |

|                                                   | $R_T = 432\text{k}$                                         | ●   | 180   | 200   | 220              |

| Switching Frequency in Foldback                   | Compared to Normal $f_{osc}$                                |     |       | 1/6   | ratio            |

| Switching Frequency Range                         | Free-Running or Synchronizing                               | ●   | 200   | 2500  | kHz              |

| SYNC High Level for Synchronization               |                                                             | ●   | 1.3   |       | V                |

| SYNC Low Level for Synchronization                |                                                             | ●   |       | 0.4   | V                |

| SYNC Clock Pulse Duty Cycle                       | $V_{SYNC} = 0\text{V}$ to $2\text{V}$                       |     | 20    | 80    | %                |

| Recommended Minimum SYNC Ratio $f_{SYNC}/f_{osc}$ |                                                             |     |       | 3/4   |                  |

| Minimum Off-Time                                  |                                                             |     |       | 45    | ns               |

| Minimum On-Time                                   |                                                             |     |       | 55    | ns               |

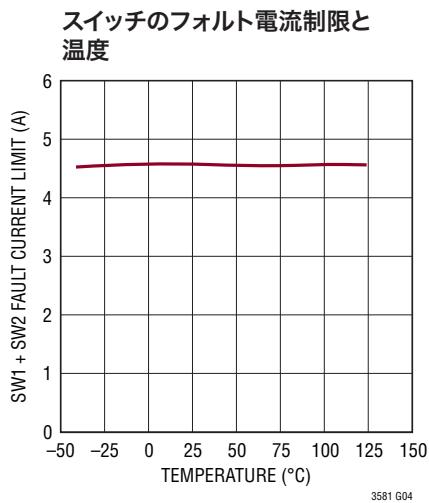

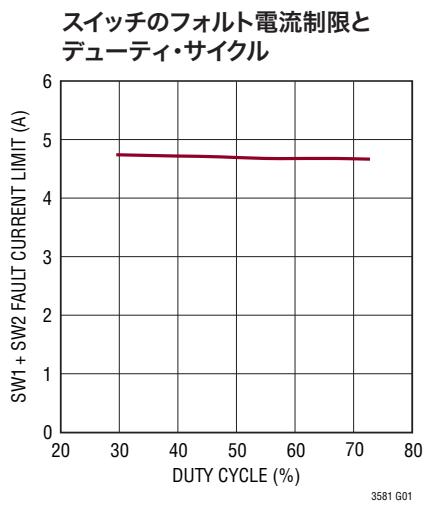

| SW1 Current Limit                                 | At All Duty Cycles                                          | ●   | 1.9   | 2.4   | 3                |

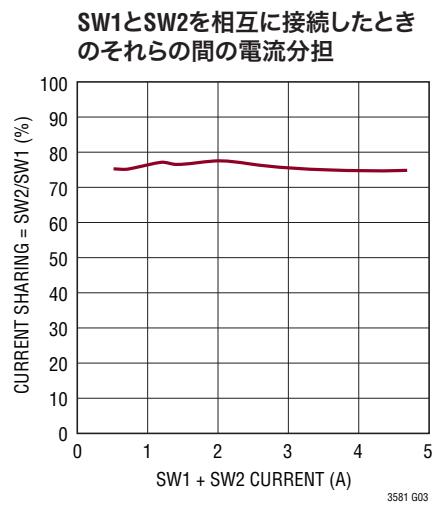

| Current Sharing (SW2/SW1)                         |                                                             |     |       | 78    | %                |

| SW1 + SW2 Current Limit                           | At All Duty Cycles, $SW2/SW1 = 78\%$ (Note 3)               | ●   | 3.3   | 4.3   | 5.4              |

| Switch $V_{CESAT}$                                | SW1 & SW2 Tied Together, $I_{SW1} + I_{SW2} = 2.75\text{A}$ |     |       | 250   | mV               |

| SW1 Leakage Current                               | $V_{SW1} = 5\text{V}$                                       |     |       | 0.01  | 1                |

| SW2 Leakage Current                               | $V_{SW2} = 5\text{V}$                                       |     |       | 0.01  | 1                |

**電気的特性** ●は全動作温度範囲の規格値を意味する。それ以外は $T_A=25^\circ\text{C}$ での値。

注記がない限り、 $V_{IN} = 5\text{V}$ 、 $V_{SHDN} = V_{IN}$ 、 $V_{FAULT} = V_{IN}$  (Note 2)

| PARAMETER                         | CONDITIONS                                                                                                                                                                        |             | MIN                  | TYP                 | MAX                  | UNITS                                           |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|---------------------|----------------------|-------------------------------------------------|

| Soft-Start Charge Current         | $V_{SS} = 30\text{mV}$ , Current Flows Out of SS pin                                                                                                                              | ●           | 5.7                  | 8.7                 | 11.3                 | $\mu\text{A}$                                   |

| Soft-Start Discharge Current      | Part in FAULT, $V_{SS} = 2.1\text{V}$ , Current Flows into SS Pin                                                                                                                 | ●           | 5.7                  | 8.7                 | 11.3                 | $\mu\text{A}$                                   |

| Soft-Start High Detection Voltage | Part in FAULT                                                                                                                                                                     | ●           | 1.65                 | 1.8                 | 1.95                 | V                                               |

| Soft-Start Low Detection Voltage  | Part Exiting FAULT                                                                                                                                                                | ●           | 30                   | 50                  | 85                   | mV                                              |

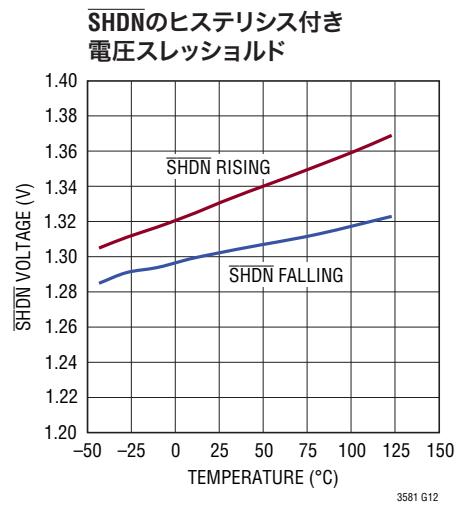

| SHDN Minimum Input Voltage High   | Active Mode, $\overline{SHDN}$ Rising (LT3581E, LT3581I)<br>Active Mode, $\overline{SHDN}$ Rising (LT3581H)<br>Active Mode, $\overline{SHDN}$ Falling (LT3581E, LT3581I, LT3581H) | ●<br>●<br>● | 1.27<br>1.27<br>1.24 | 1.33<br>1.33<br>1.3 | 1.41<br>1.44<br>1.38 | V                                               |

| SHDN Input Voltage Low            | Shutdown Mode                                                                                                                                                                     | ●           |                      |                     | 0.3                  | V                                               |

| SHDN Pin Bias Current             | $V_{SHDN} = 3\text{V}$<br>$V_{SHDN} = 1.3\text{V}$<br>$V_{SHDN} = 0\text{V}$                                                                                                      |             | 9.7                  | 40<br>11.4<br>0     | 60<br>13.4<br>0.1    | $\mu\text{A}$<br>$\mu\text{A}$<br>$\mu\text{A}$ |

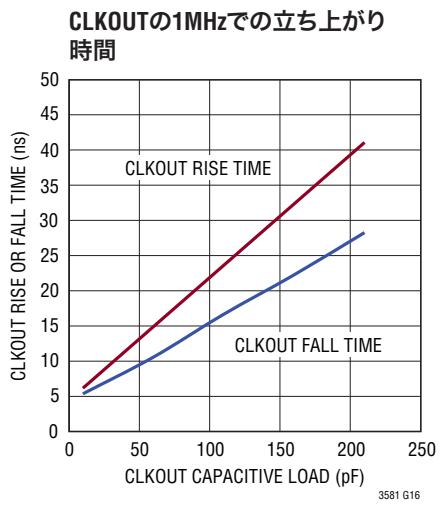

| CLKOUT Output Voltage High        | $C_{CLKOUT} = 50\text{pF}$                                                                                                                                                        |             | 1.9                  | 2.1                 | 2.3                  | V                                               |

| CLKOUT Output Voltage Low         | $C_{CLKOUT} = 50\text{pF}$                                                                                                                                                        |             |                      | 5                   | 200                  | mV                                              |

| CLKOUT Duty Cycle                 | $T_J = 25^\circ\text{C}$                                                                                                                                                          |             |                      |                     | 42                   | %                                               |

| CLKOUT Rise Time                  | $C_{CLKOUT} = 50\text{pF}$                                                                                                                                                        |             |                      |                     | 12                   | ns                                              |

| CLKOUT Fall Time                  | $C_{CLKOUT} = 50\text{pF}$                                                                                                                                                        |             |                      |                     | 8                    | ns                                              |

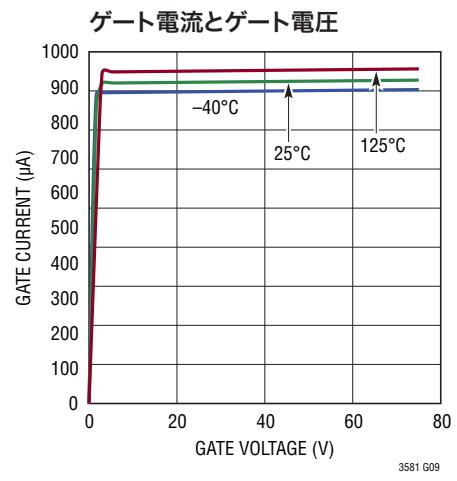

| GATE Pull Down Current            | $V_{GATE} = 3\text{V}$ (LT3581E, LT3581I)<br>$V_{GATE} = 3\text{V}$ (LT3581H)<br>$V_{GATE} = 80\text{V}$ (LT3581E, LT3581I, LT3581H)                                              | ●<br>●<br>● | 800<br>700<br>800    | 933<br>900<br>933   | 1100<br>1100<br>1100 | $\mu\text{A}$<br>$\mu\text{A}$<br>$\mu\text{A}$ |

| GATE Leakage Current              | $V_{GATE} = 50\text{V}$ , GATE Off                                                                                                                                                |             |                      |                     | 0.01                 | $\mu\text{A}$                                   |

| FAULT Output Voltage Low          | 50 $\mu\text{A}$ into $\overline{FAULT}$ Pin (LT3581E, LT3581I)<br>50 $\mu\text{A}$ into $\overline{FAULT}$ Pin (LT3581H)                                                         | ●<br>●      |                      | 100<br>100          | 300<br>400           | mV                                              |

| FAULT Leakage Current             | $V_{FAULT} = 40\text{V}$ , $\overline{FAULT}$ Off                                                                                                                                 |             |                      |                     | 0.01                 | $\mu\text{A}$                                   |

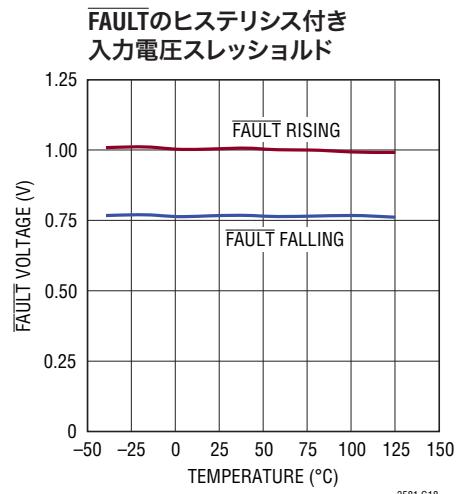

| FAULT Input Voltage Low           |                                                                                                                                                                                   | ●           | 700                  | 750                 | 800                  | mV                                              |

| FAULT Input Voltage High          |                                                                                                                                                                                   | ●           | 950                  | 1000                | 1050                 | mV                                              |

**Note 1 :** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2 :** LT3581E は  $0^\circ\text{C} \sim 125^\circ\text{C}$  の温度範囲で性能仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$  の接合部温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LT3581I は  $-40^\circ\text{C} \sim 125^\circ\text{C}$  の全動作接合部温度範囲で動作することが保証されている。LT3581IH は  $-40^\circ\text{C} \sim 150^\circ\text{C}$  の全動作接合部温度範囲で動作す

ることが保証されている。接合部温度が  $125^\circ\text{C}$  を超えると、動作寿命は短くなる。

**Note 3 :** 電流制限は設計および静的テストとの相関によって保証されている。

**Note 4 :** このデバイスには短時間の過負荷状態の間デバイスを保護するための過温度保護機能が備わっている。過温度保護機能がアクティブなとき接合部温度は  $150^\circ\text{C}$  を超える。規定された最高動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なうおそれがある。

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 。

# LT3581

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 。

## ピン機能 (DFN/MSOP)

**FB (ピン1/ピン1)**: 正と負の帰還ピン。昇圧または反転のコンバータでは、以下の式に従って抵抗を FB ピンから V<sub>OUT</sub> へ接続します。

$$R_{FB} = \left( \frac{V_{OUT} - 1.215V}{83.3 \cdot 10^{-6}} \right); \text{Boost or SEPIC Converter}$$

$$R_{FB} = \left( \frac{|V_{OUT}| + 9mV}{83.3 \cdot 10^{-6}} \right); \text{Inverting Converter}$$

**V<sub>C</sub> (ピン2/ピン2)**: 誤差アンプの出力ピン。外部補償回路をこのピンに接続します。

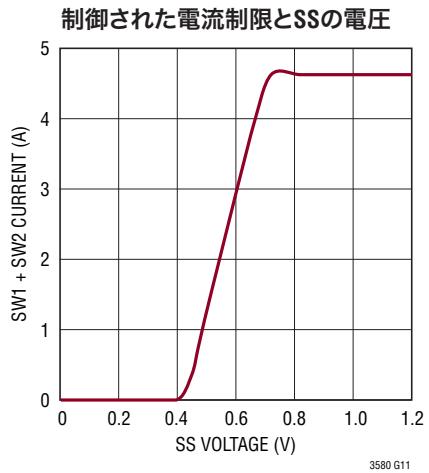

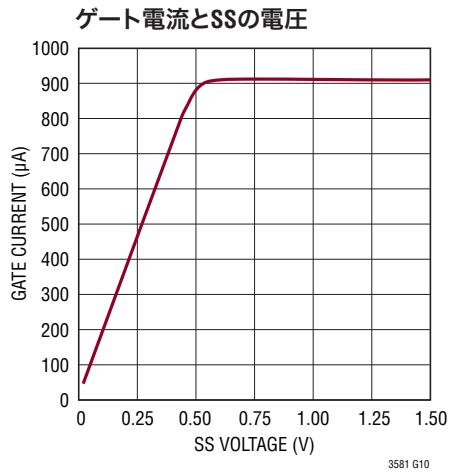

**GATE (ピン3/ピン3)**: PMOS ゲート・ドライブ・ピン。GATE ピンはプルダウン電流源であり、出力の短絡に対する保護または出力の切断のために外部 PMOS のゲートをドライブするのに使います。GATE ピンの電流は SS ピンの電圧に従ってリニアに増加し、SS の電圧が 500mV を超えるとプルダウン電流は最大 933μA になります。SS の電圧が 500mV より大きく、GATE ピンの電圧が 2V より小さいと、GATE ピンはグランドに接続された 2kΩ のインピーダンスのように見えることに注意してください。詳細については「付録」を参照してください。

**FAULT (ピン4/ピン4)**: フォルト表示ピン。このアクティブ“L”的双方向ピンは、フォルトを表示するために、外部ソースによって、あるいは内部でデバイスによって“L”(750mV より下) に引き下げることができます。このピンが“L”に引き下げられると、パワースイッチがオフし、GATE ピンが高インピーダンスになり、CLKOUT ピンがディスエーブルされ、さらに SS ピンが充電/放電のシーケンスを遂行します。このピンの電圧が 1V を超えると、フォルトの終結/不在が表示されます。フォルトが存在しないときこのピンを 1V より上にするにはプルアップ抵抗または電流源が必要です。

**V<sub>IN</sub> (ピン5/ピン5)**: 入力電源ピン。ローカルにバイパスする必要があります。

**SW1 (ピン6、7/ピン6、7、8)**: マスタスイッチ・ピン。これは内部のマスタ NPN パワースイッチのコレクタです。このピンに接続されるメタル・トレースの面積を小さくして EMI を抑えます。

**SW2 (ピン8、9/ピン9、10、11)**: スレーブスイッチ・ピン。これは内部のスレーブ NPN パワースイッチのコレクタです。このピンに接続されるメタル・トレースの面積を小さくして EMI を抑えます。

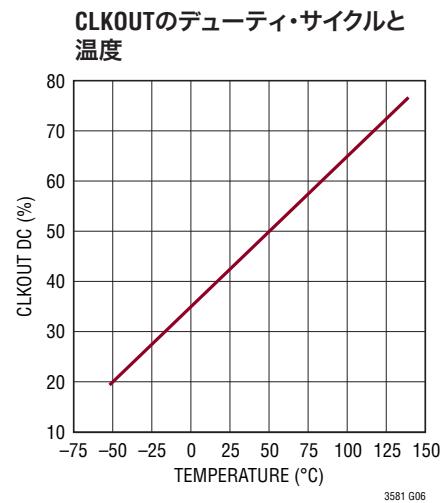

**CLKOUT (ピン10/ピン12)**: クロック出力ピン。このピンを使って、1 個または複数の他の互換性のあるスイッチング・レギュレータ IC を LT3581 に同期させます。このピンが出力するクロックは、デバイス内部の発振器または SYNC ピンと同じ周波数で動作します。CLKOUT ピンのデューティ・サイクルはデバイスの接合部温度に従ってリニアに変化するので、CLKOUT は温度モニタとしても使うことができます。CLKOUT ピンは最大 50pF までの容量性負荷をドライブすることだけが意図されていることに注意してください。

**SHDN (ピン11/ピン13)**: シャットダウン・ピン。UVLO (低電圧ロックアウト) 回路と組み合わせて、このピンを使ってデバイスをイネーブル/ディスエーブルし、ソフトスタートのシーケンスを再度開始します。デバイスをディスエーブルするには 300mV より下にドライブします。デバイスをアクティブにしてソフトスタート・シーケンスを再度開始するには 1.33V (標準) より上にドライブします。このピンはフロート状態にしないでください。

**RT (ピン12/ピン14)**: タイミング抵抗ピン。LT3581 のスイッチング周波数を調節します。このピンからグランドに抵抗を接続して、周波数を固定自走レベルに設定します。このピンはフロート状態にしないでください。

**SS (ピン13/ピン15)**: ソフトスタート・ピン。ソフトスタート・コンデンサをここに接続します。起動すると、SS ピンは (公称) 250k の抵抗を通して約 2.1V に充電されます。フォルトの間、タイムアウト・シーケンスの一部として、SS ピンはゆっくり充電され、ついには放電されます (フォルト・イベントの間の SS ピンの役目について、「状態図」を参照)。

**SYNC (ピン14/ピン16)**: スイッチング周波数を外部クロックに同期させるには、単にこのピンをクロックでドライブします。クロックの “H” 電圧レベルは 1.3V を超えなければならず、“L” 電圧レベルは 0.4V より低くなければなりません。このピンを 0.4V より下にドライブすると内部自走クロックに戻ります。詳細については「アプリケーション情報」のセクションを参照してください。

**GND (露出パッドのピン15/露出パッドのピン17)**: グランド。露出パッドはローカル・グランド・プレーンに直接半田付けする必要があります。

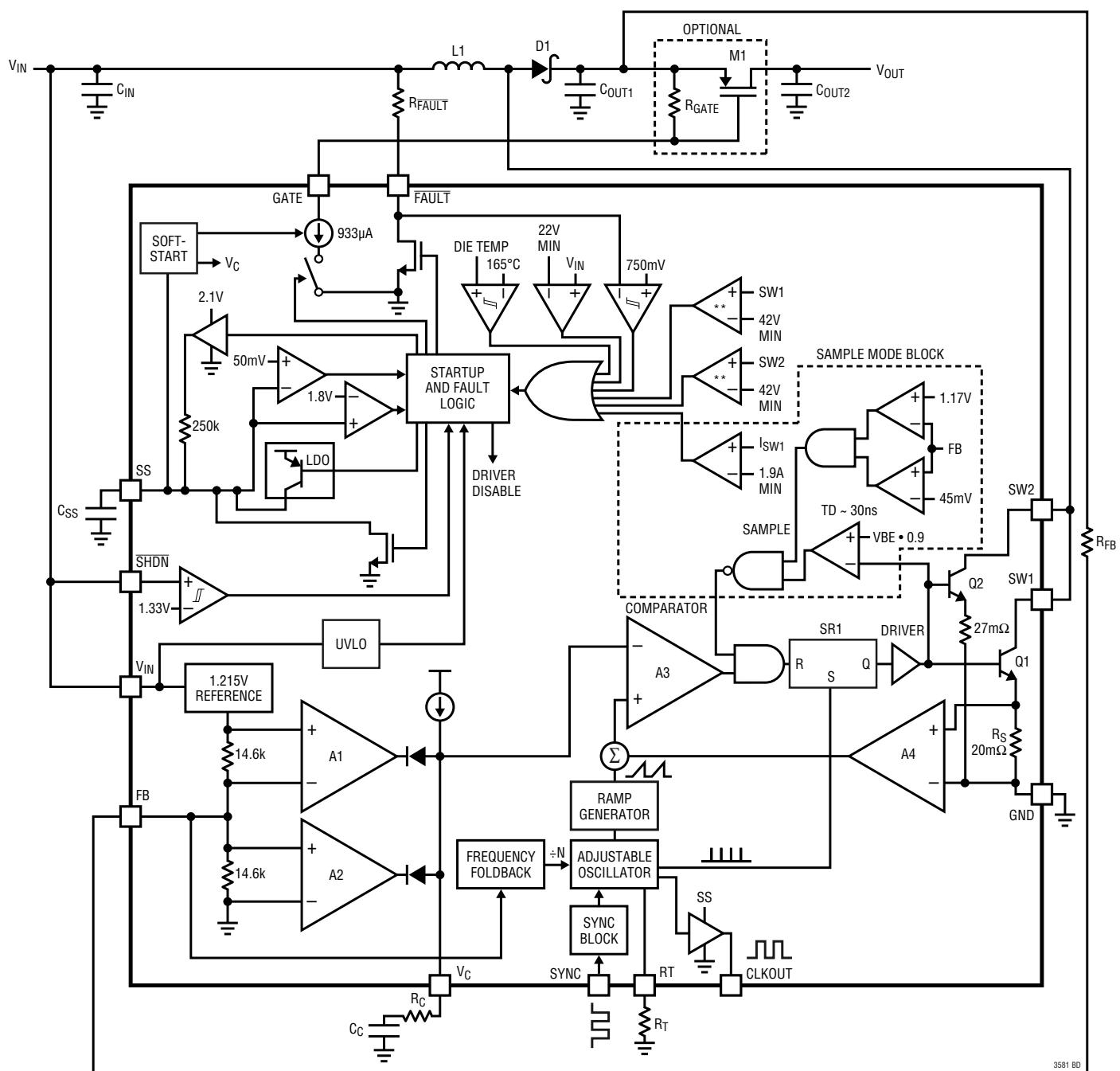

## ブロック図

\*\*SW OVERVOLTAGE PROTECTION IS NOT GUARANTEED TO PROTECT THE LT3581 DURING SW OVERVOLTAGE EVENTS

図1. ブロック図

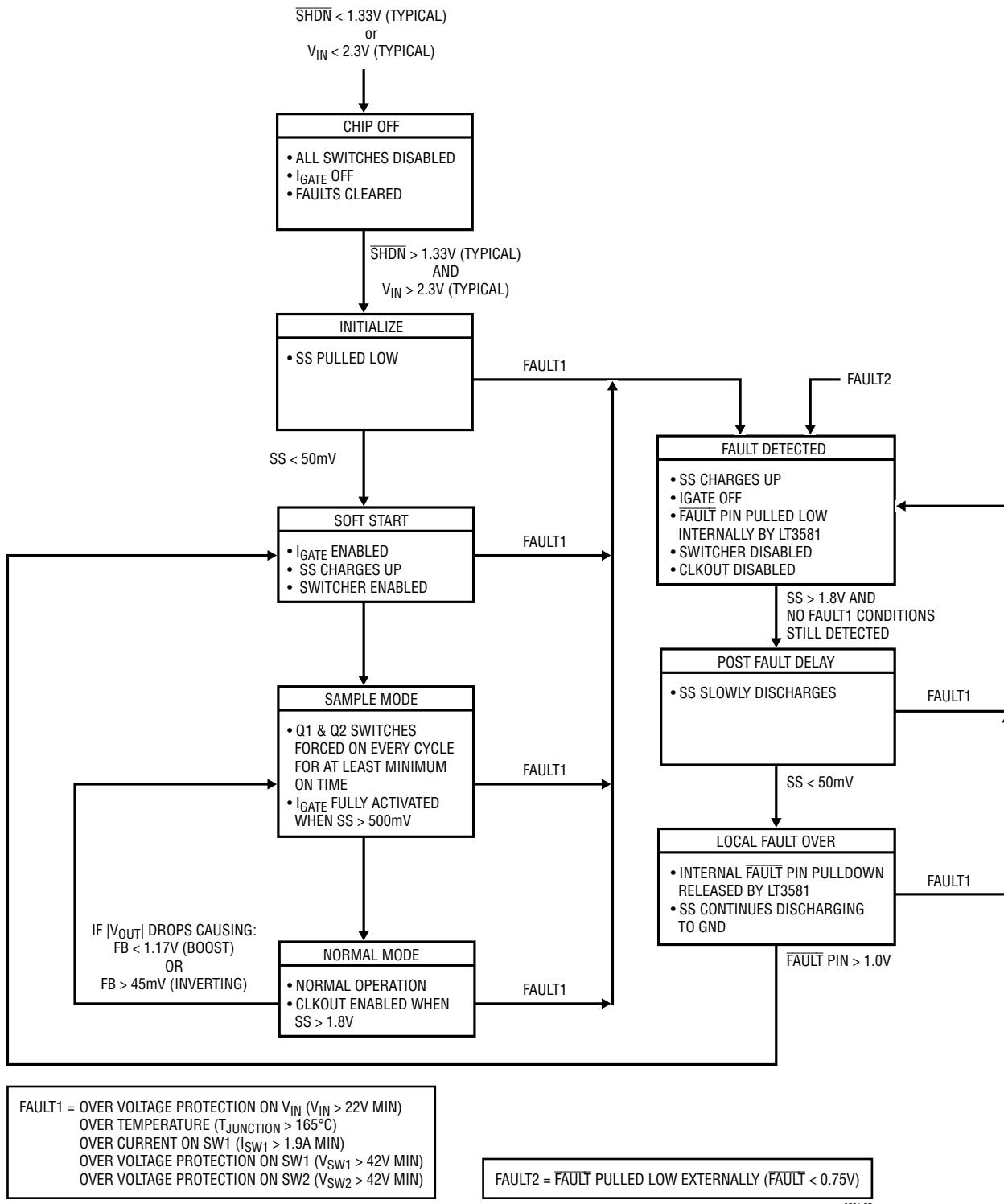

## 状態図

図2. 状態図

3581 SD

## 動作

### 動作 - 概要

LT3581 は固定周波数の電流モード制御方式を使って、優れたライン・レギュレーションとロード・レギュレーションを実現します。デバイスの低電圧ロックアウト(UVLO)機能は、ソフトスタートおよび周波数フォールドバックとともに、スタートアップを制御する手段を与えます。LT3581 にはフォルト機能が組み込まれており、出力短絡、過電圧、および過温度状態の検出に役立ちます。デバイスの動作の以下の説明に関しては、ブロック図(図1)および状態図(図2)を参照してください。

### 動作 - スタートアップ

LT3581 のクリーンな起動を可能にするため、いくつかの機能が備わっています。

#### 精密ターンオン電圧

$\overline{SHDN}$  ピンが内部電圧リファレンスと比較され、精密なターンオン電圧レベルが与えられます。 $\overline{SHDN}$  ピンを 1.33V(標準)より上にするとデバイスがイネーブルされます。 $\overline{SHDN}$  ピンを 300mVより下にするとデバイスがシャットダウンし、消費電流が非常に低くなります。 $\overline{SHDN}$  ピンには 30mV のヒステリシスがあり、グリッチと低速ランピングに対して保護します。

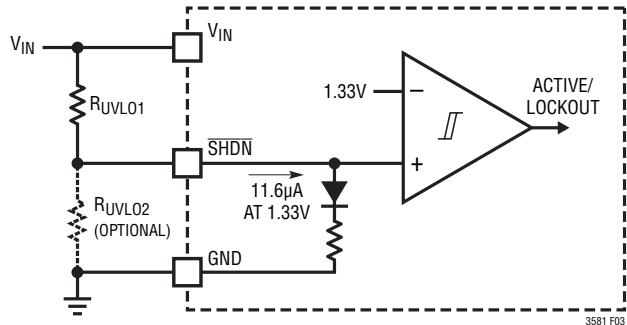

#### 低電圧ロックアウト(UVLO)

$\overline{SHDN}$  ピンを使って構成可能な UVLO を構成することができます。UVLO 機能は LT3581 のオン/オフを望みの入力電圧( $V_{INUVLO}$ )に設定します。どのように抵抗分割器(または1個の抵抗)を  $V_{IN}$  から  $\overline{SHDN}$  ピンに接続して  $V_{INUVLO}$  を設定できるかを図3に示します。 $R_{UVLO2}$  はオプションです。これは省略することができ、その場合はそれを下の式で無限大にします。精度を上げるには  $R_{UVLO2} \leq 10k$  にします。 $R_{UVLO1}$  は次のように選択します。

$$R_{UVLO1} = \frac{V_{INUVLO} - 1.33V}{\left(\frac{1.33V}{R_{UVLO2}}\right) + 11.6\mu A}$$

LT3581 は UVLO 回路も内蔵しており、 $V_{IN} < 2.3V$ (標準)のときデバイスをディスエーブルします。

図3. 構成可能なUVLO

#### スイッチ電流のソフトスタート

ソフトスタート回路はスイッチ電流を徐々にランプアップさせます(「標準的性能特性」の「制御された電流制限と SS の電圧」を参照)。デバイスがシャットダウンから抜け出ると、外部 SS コンデンサがまず放電し、それによりデバイス内のロジック回路の状態がリセットされます。次いで、内蔵されている 250k 抵抗が SS ピンを約 1.8V に引き上げます。SS ピンの電圧のランプレートはこの 250k 抵抗とこのピンに接続されている外部コンデンサによって設定されます。SS ピンが 1.8V に達すると、CLKOUT ピンがイネーブルされ、内部レギュレータがこのピンを即座に約 2.1V に引き上げます。外部のソフトスタート・コンデンサの標準値は 100nF ~ 1μF の範囲です。

#### 外部 PMOS(もし使用されていれば)のソフトスタート

また、ソフトスタート回路は GATE ピンのプルダウン電流を徐々にランプアップするので、外部 PMOS(「ブロック図」の M1)をゆっくりオンすることができます。GATE ピンの電流は SS ピンの電圧に従ってリニアに増加し、SS の電圧が 500mV を超えると最大電流は 933μA になります。SS の電圧が 500mV を超えていても、GATE ピンの電圧が 2V より下だと、GATE ピンのグランドへのインピーダンスは 2kΩ であることに注意してください。外部 PMOS のソフト・ターンオンによりスタートアップ時の突入電流が制限されるので、LT3581 の活線挿入は可能であり、安全です。

## 動作

### サンプル・モード

サンプル・モードは LT3581 によって使われるメカニズムで、出力の短絡の検出に役立ちます。これは、インダクタ電流を「サンプル」するために、マスタ・スイッチとスレーブ・スイッチ (Q1 と Q2) が、クロック・サイクルごとに（または周波数フォールドバックのときは数クロック・サイクルごとに）最小時間の間オンする LT3581 の状態を指しています。Q1 を通してサンプルされた電流が 1.9A（最小）のマスタ・スイッチ電流リミットを超えると、LT3581 は内部で過電流フォルトをトリガします（詳細については、「動作 - フォルト」のセクションを参照）。サンプル・モードは FB が約 3.7% 以上安定化状態から外れるとアクティブになります ( $45\text{mV} < \text{FB} < 1.17\text{V}$ )。

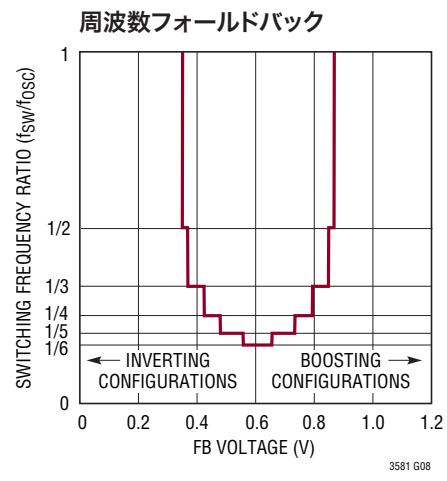

### 周波数フォールドバック

周波数フォールドバック回路は、 $350\text{mV} < \text{FB} < 900\text{mV}$ （標準）のときスイッチング周波数を下げます。この機能はデバイスが達成できる最小デューティ・サイクルを下げて、起動時のインダクタ電流をさらに良く制御できるようにします。FB 電圧がこの範囲の外に出ると、スイッチング周波数は正常の値に戻ります。

スタートアップ時のピーク・インダクタ電流は、負荷プロファイル、出力容量、目標とする  $\text{V}_{\text{OUT}}$ 、 $\text{V}_{\text{IN}}$ 、スイッチング周波数など多くの変数の関数であることに注意してください。**スタートアップ時のアプリケーションの全ての性能をもれなくテストし、ピーク・インダクタ電流が最小フォルト電流リミットを超えないようにします。**

### 動作 - レギュレーション

LT3581 の動作の以下の説明では、FB の電圧がその安定化の目標に十分近いので、デバイスはサンプル・モードではないと仮定しています。レギュレーション状態で動作している LT3581 の動作の以下の説明を読み進む際、ブロック図を参照してください。発振器の各サイクルの開始点で、SR ラッチ (SR1) がセットされ、パワースイッチ Q1 と Q2 をオンします。2つのスイッチのコレクタが相互に接続されているとき、マスタ・スイッチ (Q1) のコレクタ電流は、スレーブ・スイッチ (Q2) のコレクタ電流の約 1.3 倍です。

Q1 のエミッタ電流は電流検出抵抗 ( $R_S$ ) を通って流れ、全スイッチ電流に比例した電圧を発生します。（A4 によって増幅された）この電圧が安定化ランプへ加算され、その和が PWM コンパレータ A3 の正端子に与えられます。A3 の正入力の電圧が負入力の電圧を超えると、SR ラッチがリセットされ、マスタとスレーブのパワースイッチをオフします。A3 の負入力 ( $V_C$  ピン) の電圧が A1（または A2）によって設定されます。これは単に FB ピンの電圧とリファレンス電圧の差を増幅したものですが（LT3581 が昇圧コンバータとして構成されていると 1.215V、反転コンバータとして構成されていると 9mV）。このようにして、誤差アンプは正しいピーク電流レベルを設定し、出力を安定化された状態に保ちます。

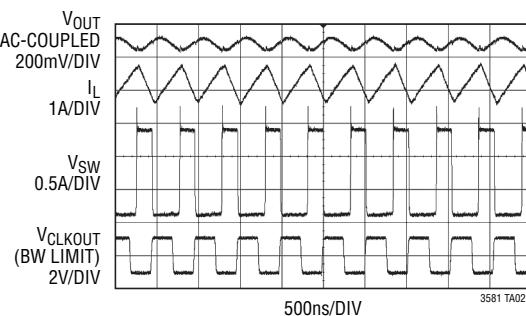

デバイスがフォルト状態ではなく（「動作 - フォルト」のセクションを参照）、SS ピンが 1.8V を超えている限り、LT3581 はその CLKOUT ピンを RT ピンまたは SYNC ピンによって設定される周波数でドライブします。CLKOUT ピンを使って、（LT3581 を含む）他の適合性のあるスイッチング・レギュレータ IC を同期させることができます。さらに、CLKOUT のデューティ・サイクルはデバイスの接合部温度に従ってリニアに変化するので、温度モニタとしても使うことができます。

### 動作 - フォルト

LT3581 の FAULT ピンはアクティブ“L”的双方向ピンで、“L”になってフォルトを表示します。以下の各イベントにより、LT3581 のフォルトがトリガされます。

#### A. FAULT1 のイベント：

1. SW の過電流：

- a.  $I_{\text{SW1}} > 1.9\text{A}$ （最小）

- b.  $(I_{\text{SW1}} + I_{\text{SW2}}) > 3.3\text{A}$ （最小）

2.  $\text{V}_{\text{IN}}$  の電圧  $> 22\text{V}$ （最小）

3. SW1 の電圧および/または SW2 の電圧  $> 42\text{V}$ （最小）

4. ダイ温度  $> 165^\circ\text{C}$

#### B. FAULT2 のイベント：

1. 外部から FAULT ピンを “L” に引き下げる

## 動作

LT3581 のフォルト・イベント発生時の動作の以下の説明に関しては、状態図（図 2）を参照してください。フォルトが検出されると、 $\overline{\text{FAULT}}$  ピンが内部で “L” に引き下げられるのに加えて、LT3581 はその CLKOUT ピンもディスエーブルし、そのパワースイッチをオフし、GATE ピンが高インピーダンスになります。外部  $R_{\text{GATE}}$  抵抗によって外部 PMOS (M1) のゲートがそのソースまで引き上げられると、M1 がオフします（ブロック図を参照）。外部 PMOS がオフすると  $V_{\text{IN}}$  から  $V_{\text{OUT}}$  への電力経路が遮断され、下流の電力部品を保護します。

同時に、タイムアウト・シーケンスが開始され、SS ピンが 1.8V まで充電され ( $\overline{\text{FAULT1}}$  のイベントがまだ終了しない場合は SS ピンは 2.1V まで充電し続け、そこに保持され)、次いで 50mV に放電されます。このタイムアウト時間は、SS ピンの電圧ランプ・レートによって設定される最小時間の間、デバイス、PMOS、その他の下

流の電源部品への電気的および熱的ストレスを緩和します。

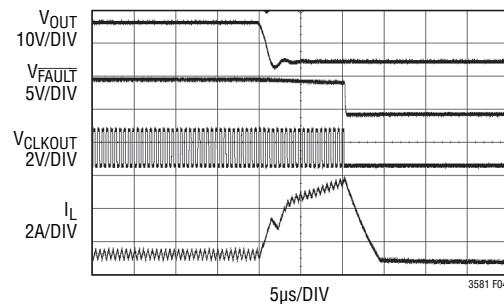

フォルトが存在しないと、 $\overline{\text{FAULT}}$  ピンは外部  $R_{\overline{\text{FAULT}}}$  抵抗（標準 100k）によって “H” に引き上げられます。LT3581 の出力の短絡の検出に伴うイベントを図 4 に示します。

図4. LT3581の出力の短絡に対する保護

## アプリケーション情報

### 昇圧コンバータの部品の選択

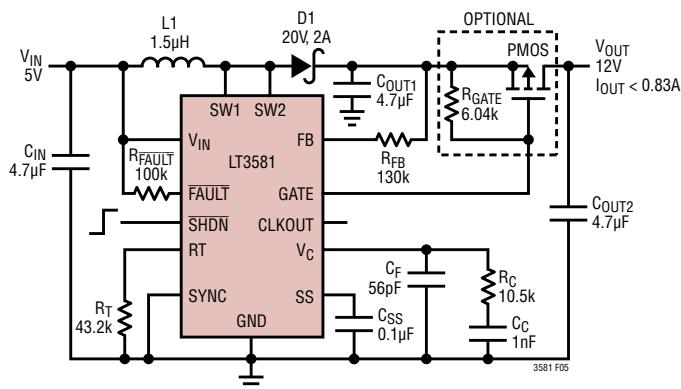

図5. 昇圧コンバータ - 与えられている部品値および電圧は、2MHz、5Vから12Vの昇圧の場合の標準値

LT3581は、図5に示されているように、昇圧コンバータとして構成することができます。このトポロジーでは、入力電圧より高い正の出力電圧が可能です。LT3581のGATEピンによってドライブされる外部PMOS（オプション）により、フォルト・イベントの間入力または出力を切断することができます。1個の帰還抵抗により出力電圧が設定されます。40Vより高い出力電圧の場合、「チャージポンプを使ったレギュレータ」のセクションを参照してください。

昇圧コンバータとして動作するLT3581の部品値を計算する式が、順を追って表1に示してあります。入力するパラメータは、入力電圧、出力電圧、スイッチング周波数（それぞれ $V_{IN}$ 、 $V_{OUT}$ 、 $f_{OSC}$ ）です。表1に示されている設計式の詳細については、「付録」を参照してください。

#### 変数の定義：

$V_{IN}$  = 入力電圧

$V_{OUT}$  = 出力電圧

$DC$  = パワースイッチのデューティ・サイクル

$f_{OSC}$  = スイッチング周波数

$I_{OUT}$  = 最大平均出力電流

$I_{RIPPLE}$  = インダクタ・リップル電流

$R_{DSON\_PMOS}$  = 外部PMOSの $R_{DSON}$ （PMOSを使わない場合は0に設定）

表1. 昇圧の設計式

|                                 | パラメータ/式                                                                                                                                                                                                                                       |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step 1:<br>Inputs               | $V_{IN}, V_{OUT}, f_{OSC}$ を選択して以下の式を計算する。                                                                                                                                                                                                    |

| Step 2:<br>DC                   | $DC \geq \frac{V_{OUT} - V_{IN} + 0.5V}{V_{OUT} + 0.5V - 0.3V}$                                                                                                                                                                               |

| Step 3:<br>L1                   | $L_{TYP} = \frac{(V_{IN} - 0.3V) \cdot DC}{f_{OSC} \cdot 1A}$ (1)<br>$L_{MIN} = \frac{(V_{IN} - 0.3V) \cdot (2 \cdot DC - 1)}{2.2A \cdot f_{OSC} \cdot (1 - DC)}$ (2)<br>$L_{MAX} = \frac{(V_{IN} - 0.3V) \cdot DC}{f_{OSC} \cdot 0.35A}$ (3) |

|                                 | • $L_{TYP}$ または $L_{MIN}$ のどちらか高い方によってその範囲の最小値が設定されるインダクタ値の範囲からL1を選択する。この範囲の最大値は $L_{MAX}$ によって設定される。選択されたインダクタ値に対する電流定格の選択方法については「付録」を参照。                                                                                                    |

| Step 4:<br>$I_{RIPPLE}$         | $I_{RIPPLE} = \frac{(V_{IN} - 0.3V) \cdot DC}{f_{OSC} \cdot L_1}$                                                                                                                                                                             |

| Step 5:<br>$I_{OUT}$            | $I_{OUT} = \left( 3.3A - \frac{I_{RIPPLE}}{2} \right) \cdot (1 - DC)$                                                                                                                                                                         |

| Step 6:<br>D1                   | $V_R > V_{OUT}; I_{AVG} > I_{OUT}$                                                                                                                                                                                                            |

| Step 7:<br>$C_{OUT1}, C_{OUT2}$ | $C_{OUT1} = C_{OUT2} \geq \frac{I_{OUT} \cdot DC}{f_{OSC} [0.01 \cdot V_{OUT} - 0.50 \cdot I_{OUT} \cdot R_{DSON\_PMOS}]}$<br>• PMOSを使用しない場合、 $C_{OUT} = C_{OUT1} + C_{OUT2}$ となるコンデンサを1個使用する。                                                |

| Step 8:<br>$C_{IN}$             | $C_{IN} \geq C_{VIN} + C_{PWR} \geq \frac{3.3A \cdot DC}{45 \cdot f_{OSC} \cdot 0.005 \cdot V_{IN}} + \frac{I_{RIPPLE}}{8 \cdot f_{OSC} \cdot 0.005 \cdot V_{IN}}$<br>• $C_{VIN}$ と $C_{PWR}$ の定義については、「付録」の「入力コンデンサの選択」を参照。                  |

| Step 9:<br>$R_{FB}$             | $R_{FB} = \frac{V_{OUT} - 1.215V}{83.3\mu A}$                                                                                                                                                                                                 |

| Step 10:<br>$R_T$               | $R_T = \frac{87.6}{f_{OSC}} - 1; f_{OSC}$ in MHz and $R_T$ in kΩ                                                                                                                                                                              |

| Step 11:<br>PMOS                | 入力または出力の切断のためにのみ必要。PMOS、 $R_{GATE}$ の大きさの決定と適切なUVLO用部品の選択に関しては、「付録」の「PMOSの選択」を参照。                                                                                                                                                             |

Note 1: ピーク・スイッチ電流の最大設計目標値は3.3Aであり、この表で使われている。

Note 2: 望みの負荷過渡性能を得るために、 $C_{OUT1}$ 、 $C_{OUT2}$ 、 $C_{IN}$ の最終値は上の式から外れてもかまわない。

## アプリケーション情報

SEPICコンバータの部品の選択

(結合された、または結合されていないインダクタ)

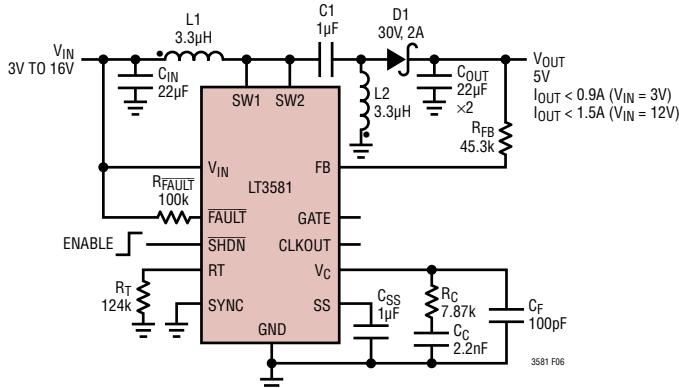

図6. SEPIKコンバータ - 与えられている部品値および電圧は、700kHz、広い入力範囲(3V~16V)のSEPIKコンバータ(5V出力)の場合の標準値

LT3581は、図6に示されているように、SEPIKとして構成することもできます。このトポロジーでは、入力電圧に比べて、低い、等しい、または高い正の出力電圧が可能です。出力の切断はSEPIKトポロジーに本来的に組み込まれています。つまり、コンデンサC1により、入出力間にDC経路が存在しません。これは、GATEピンによって制御されるPMOSが電力経路に不要であることを意味します。

SEPIKコンバータとして動作するLT3581の部品値を計算する式が、順を追って表2に示してあります。入力するパラメータは、入力電圧、出力電圧、スイッチング周波数(それぞれV<sub>IN</sub>、V<sub>OUT</sub>、f<sub>OSC</sub>)です。表2に示されている設計式の詳細については、「付録」を参照してください。

## 変数の定義：

V<sub>IN</sub> = 入力電圧

V<sub>OUT</sub> = 出力電圧

DC = パワースイッチのデューティ・サイクル

f<sub>OSC</sub> = スイッチング周波数

I<sub>OUT</sub> = 最大平均出力電流

I<sub>RIPPLE</sub> = インダクタのリップル電流

表2. SEPIKの設計式

|                                | パラメータ/式                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step 1:<br>Inputs              | V <sub>IN</sub> 、V <sub>OUT</sub> 、f <sub>OSC</sub> を選択して以下の式を計算する。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Step 2:<br>DC                  | DC $\approx \frac{V_{OUT} + 0.5V}{V_{IN} + V_{OUT} + 0.5V - 0.3V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Step 3:<br>L                   | $L_{TYP} = \frac{(V_{IN} - 0.3V) \cdot DC}{f_{OSC} \cdot 1A} \quad (1)$ $L_{MIN} = \frac{(V_{IN} - 0.3V) \cdot (2 \cdot DC - 1)}{2.2A \cdot f_{OSC} \cdot (1-DC)} \quad (2)$ $L_{MAX} = \frac{(V_{IN} - 0.3V) \cdot DC}{f_{OSC} \cdot 0.35A} \quad (3)$ <ul style="list-style-type: none"> <li>• L<sub>TYP</sub>またはL<sub>MIN</sub>のどちらか高い方によってその範囲の最小値が設定されるインダクタ値の範囲からLを選択する。この範囲の最大値はL<sub>MAX</sub>によって設定される。選択されたインダクタ値に対する電流定格の選択方法については「付録」を参照。</li> <li>• 結合されたインダクタの場合、L<sub>1</sub> = L<sub>2</sub> = Lを選択する。</li> <li>• 結合されていないインダクタの場合、L<sub>1</sub>  L<sub>2</sub> = Lを選択する。</li> </ul> |

| Step 4:<br>I <sub>RIPPLE</sub> | $I_{RIPPLE} = \frac{(V_{IN} - 0.3V) \cdot DC}{f_{OSC} \cdot L}$ <ul style="list-style-type: none"> <li>• 結合されたインダクタの場合、L = L<sub>1</sub> = L<sub>2</sub>を選択する。</li> <li>• 結合されていないインダクタの場合、L = L<sub>1</sub>  L<sub>2</sub>を選択する。</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |

| Step 5:<br>I <sub>OUT</sub>    | $I_{OUT} = \left( 3.3A - \frac{I_{RIPPLE}}{2} \right) \cdot (1-DC)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Step 6:<br>D1                  | $V_R > V_{IN} + V_{OUT}; I_{AVG} > I_{OUT}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Step 7:<br>C1                  | $C1 \geq 1\mu F; V_{RATING} \geq V_{IN}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Step 8:<br>C <sub>OUT</sub>    | $C_{OUT} \geq \frac{I_{OUT} \cdot DC}{f_{OSC} \cdot 0.005 \cdot V_{OUT}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Step 9:<br>C <sub>IN</sub>     | $C_{IN} \geq C_{VIN} + C_{PWR} \geq \frac{3.3A \cdot DC}{45 \cdot f_{OSC} \cdot 0.005 \cdot V_{IN}} + \frac{I_{RIPPLE}}{8 \cdot f_{OSC} \cdot 0.005 \cdot V_{IN}}$ <ul style="list-style-type: none"> <li>• C<sub>VIN</sub>とC<sub>PWR</sub>の定義については、「付録」の「入力コンデンサの選択」を参照。</li> </ul>                                                                                                                                                                                                                                                                                                                 |

| Step 10:<br>R <sub>FB</sub>    | $R_{FB} = \frac{V_{OUT} - 1.215V}{83.3\mu A}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Step 11:<br>R <sub>T</sub>     | $R_T = \frac{87.6}{f_{OSC}} - 1; f_{OSC} \text{ in MHz and } R_T \text{ in k}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Note 1: ピーク・スイッチ電流の最大設計目標値は3.3Aであり、この表で使われている。

Note 2: 望みの負荷過渡性能を得るため、C<sub>OUT</sub>、C<sub>IN</sub>、C<sub>1</sub>の最終値は上の式から外れてもかまわない。

## アプリケーション情報

### デュアル・インダクタ反転コンバータの部品の選択 (結合された、または結合されていないインダクタ)

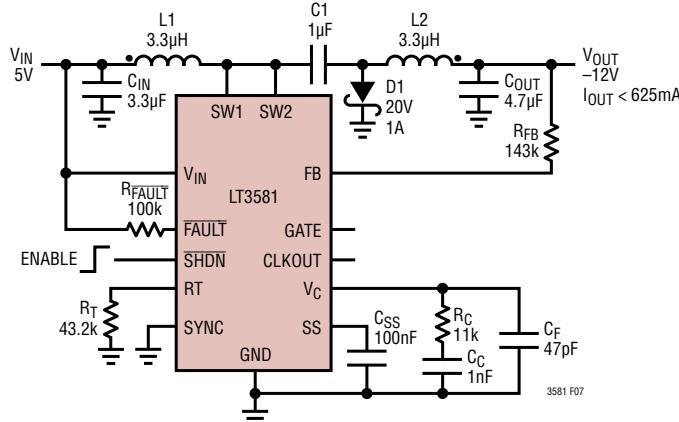

図7. デュアル・インダクタ反転コンバータ – 与えられている部品値および電圧は、2MHz、5Vから-12Vの、結合されたインダクタを使った反転トポロジーの場合の標準値

LT3581は、そのユニークなFBピンにより、図7に示されているようなデュアル・インダクタ反転構成で動作することができます。SEPICトポロジーのL2とショットキー・ダイオードの接続を変更すると、負の出力電圧が発生します。このソリューションにより、出力に直列に接続されたインダクタL2による出力電圧リップルが非常に低くなります。コンデンサC1により、このトポロジーには出力の切断機能が本来組み込まれています。

デュアル・インダクタ反転コンバータとして動作するLT3581の部品値を計算する式が、順を追って表3に示してあります。入力するパラメータは、入力電圧、出力電圧、スイッチング周波数（それぞれV<sub>IN</sub>、V<sub>OUT</sub>、f<sub>OSC</sub>）です。表3に示されている設計式の詳細については、「付録」を参照してください。

#### 変数の定義：

V<sub>IN</sub> = 入力電圧

V<sub>OUT</sub> = 出力電圧

DC = パワースイッチのデューティ・サイクル

f<sub>OSC</sub> = スイッチング周波数

I<sub>OUT</sub> = 最大平均出力電流

I<sub>RIPPLE</sub> = インダクタ・リップル電流

表3. デュアル・インダクタ反転の設計式

|                                   | パラメータ/式                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Step 1: Inputs</b>             | V <sub>IN</sub> 、V <sub>OUT</sub> 、f <sub>OSC</sub> を選択して以下の式を計算する。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>Step 2: DC</b>                 | $DC \cong \frac{ V_{OUT}  + 0.5V}{V_{IN} +  V_{OUT}  + 0.5V - 0.3V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>Step 3: L</b>                  | $L_{TYP} = \frac{(V_{IN} - 0.3V) \cdot DC}{f_{OSC} \cdot 1A} \quad (1)$ $L_{MIN} = \frac{(V_{IN} - 0.3V) \cdot (2 \cdot DC - 1)}{2.2A \cdot f_{OSC} \cdot (1 - DC)} \quad (2)$ $L_{MAX} = \frac{(V_{IN} - 0.3V) \cdot DC}{f_{OSC} \cdot 0.35A} \quad (3)$ <ul style="list-style-type: none"> <li>L<sub>TYP</sub>またはL<sub>MIN</sub>のどちらか高い方によってその範囲の最小値が設定されるインダクタ値の範囲からしを選択する。この範囲の最大値はL<sub>MAX</sub>によって設定される。選択されたインダクタ値に対する電流定格の選択方法については「付録」を参照。</li> <li>結合されたインダクタの場合、L<sub>1</sub> = L<sub>2</sub> = Lを選択する。</li> <li>結合されていないインダクタの場合、L<sub>1</sub>  L<sub>2</sub> = Lを選択する。</li> </ul> |

| <b>Step 4: I<sub>RIPPLE</sub></b> | $I_{RIPPLE} = \frac{(V_{IN} - 0.3V) \cdot DC}{f_{OSC} \cdot L}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>Step 5: I<sub>OUT</sub></b>    | $I_{OUT} = \left( 3.3A - \frac{I_{RIPPLE}}{2} \right) \cdot (1 - DC)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>Step 6: D1</b>                 | $V_R > V_{IN} +  V_{OUT} ; I_{AVG} > I_{OUT}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>Step 7: C<sub>1</sub></b>      | $C_1 \geq 1\mu F; V_{RATING} \geq V_{IN} +  V_{OUT} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>Step 8: C<sub>OUT</sub></b>    | $C_{OUT} \geq \frac{I_{RIPPLE}}{8 \cdot f_{OSC} (0.005 \cdot  V_{OUT} )}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>Step 9: C<sub>IN</sub></b>     | $C_{IN} \geq C_{VIN} + C_{PWR} \geq \frac{3.3A \cdot DC}{45 \cdot f_{OSC} \cdot 0.005 \cdot V_{IN}} + \frac{I_{RIPPLE}}{8 \cdot f_{OSC} \cdot 0.005 \cdot V_{IN}}$ <ul style="list-style-type: none"> <li>C<sub>VIN</sub>とC<sub>PWR</sub>の定義については、「付録」の「入力コンデンサの選択」を参照。</li> </ul>                                                                                                                                                                                                                                                                                                               |

| <b>Step 10: R<sub>FB</sub></b>    | $R_{FB} = \frac{ V_{OUT}  + 5mV}{83.3\mu A}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>Step 11: R<sub>T</sub></b>     | $R_T = \frac{87.6}{f_{OSC}} - 1; f_{OSC} \text{ in MHz and } R_T \text{ in k}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Note 1: ピーク・スイッチ電流の最大設計目標値は3.3Aであり、この表で使われている。

Note 2: 望みの負荷過渡性能を得るため、C<sub>OUT</sub>、C<sub>IN</sub>、C<sub>1</sub>の最終値は上の式から外れてもかまわない。

## アプリケーション情報

### 昇圧、SEPIC、およびデュアル・インダクタ反転トポロジーのレイアウトのガイドライン

#### 一般的なレイアウトのガイドライン

- 熱性能を最適化するには、LT3581 の露出グランド・パッドをグランド・プレーンに半田付けします。多数のビアをパッドの周囲に置いて追加のグランド・プレーンに接続します。

- プレーン間のカップリングおよび全体のノイズを防ぐため、スイッチャ回路の下にグランド・プレーンを使います。

- 高速スイッチング経路（詳細については特定のトポロジーを参照）はできるだけ短くする必要があります。

- $V_C$ 、 $FB$ 、および  $RT$  に関連する部品はできるだけ LT3581 に近づけ、スイッチ・ノードからできるだけ離して配置します。これらの部品のグランドはスイッチ電流の経路から離します。

- $V_{IN}$  ピンのバイパス・コンデンサはできるだけ LT3581 に近づけて配置します。

- インダクタのバイパス・コンデンサはできるだけインダクタに近づけて配置します。

- 最良の負荷レギュレーションを得るには、負荷を出力コンデンサの正端子と負端子に直接接続します。

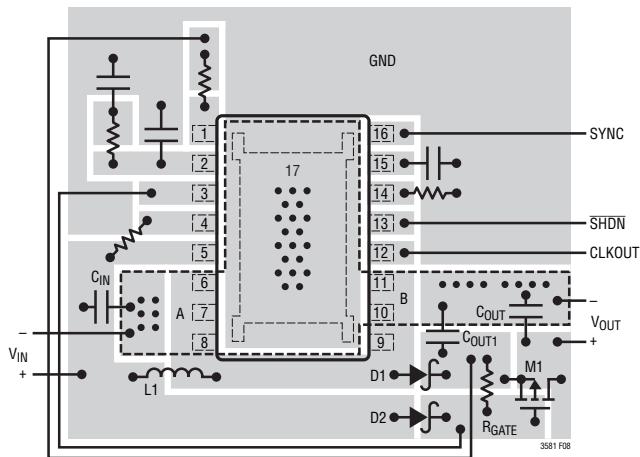

A: RETURN  $C_{IN}$  GROUND DIRECTLY TO LT3581 EXPOSED PAD PIN 17. IT IS ADVISED TO NOT COMBINE  $C_{IN}$  GROUND WITH GND EXCEPT AT THE EXPOSED PAD.

B: RETURN  $C_{OUT}$  AND  $C_{OUT1}$  GROUND DIRECTLY TO LT3581 EXPOSED PAD PIN 17. IT IS ADVISED TO NOT COMBINE  $C_{OUT}$  AND  $C_{OUT1}$  GROUND WITH GND EXCEPT AT THE EXPOSED PAD.

**図8.** 昇圧トポロジーの推奨部品配置 (MSOPが示されており、DFNも同様。実寸とは異なる)。DFNのピン15またはMSOPのピン17は露出パッドであり、適切な熱性能を得るために、ローカル・グランド・プレーンに直接半田付けする必要がある。多数のビアを追加のグランド・プレーンに通すと熱性能が改善される。

### 昇圧トポロジーに固有のレイアウトのガイドライン

- スイッチ、ダイオード D1、出力コンデンサ  $C_{OUT1}$ 、およびグランド・リターンを制御するループ（高速スイッチング経路）ができるだけ短くして、スイッチングの際のスイッチ・ノードの寄生誘導性スパイクを最小に抑えます。

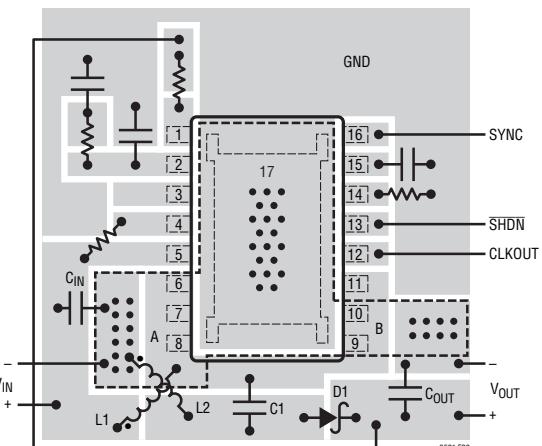

### SEPICトポロジーに固有のレイアウトのガイドライン

- スイッチ、フライング・コンデンサ  $C_1$ 、ダイオード D1、出力コンデンサ  $C_{OUT}$ 、およびグランド・リターンを制御するループ（高速スイッチング経路）ができるだけ短くして、スイッチングの際のスイッチ・ノードの寄生誘導性スパイクを最小に抑えます。

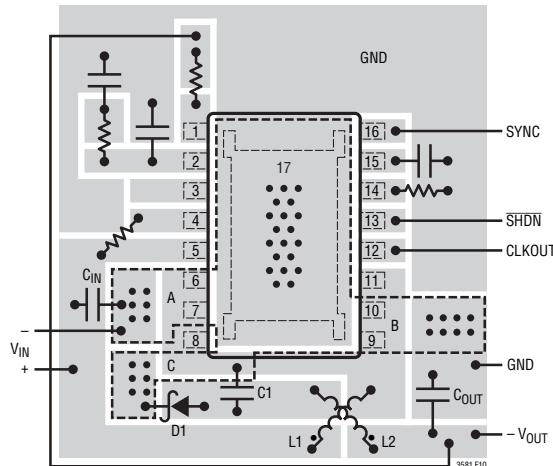

### 反転トポロジーに固有のレイアウトのガイドライン

- 出力に結合するスイッチング・ノイズを最小に抑えるため、D1 のカソードから（デバイスへ）のグランド・リターン経路を、出力コンデンサ  $C_{OUT}$  の（デバイスへの）グランド・リターン経路から離します。

- スイッチ、フライング・コンデンサ  $C_1$ 、ダイオード D1、およびグランド・リターンを制御するループ（高速スイッチング経路）ができるだけ短くして、スイッチングの際のスイッチ・ノードの寄生誘導性スパイクを最小に抑えます。

A: RETURN  $C_{IN}$  AND  $L_2$  GROUND DIRECTLY TO LT3581 EXPOSED PAD PIN 17. IT IS ADVISED TO NOT COMBINE  $C_{IN}$  AND  $L_2$  GROUND WITH GND EXCEPT AT THE EXPOSED PAD.

B: RETURN  $C_{OUT}$  GROUND DIRECTLY TO LT3581 EXPOSED PAD PIN 17. IT IS ADVISED TO NOT COMBINE  $C_{OUT}$  GROUND WITH GND EXCEPT AT THE EXPOSED PAD.

L1, L2: MOST COUPLED INDUCTOR MANUFACTURERS USE CROSS PINOUT FOR IMPROVED PERFORMANCE.

**図9.** SEPICトポロジーの推奨部品配置 (MSOPが示されており、DFNも同様。実寸とは異なる)。DFNのピン15またはMSOPのピン17は露出パッドであり、適切な熱性能を得るために、ローカル・グランド・プレーンに直接半田付けする必要がある。多数のビアを追加のグランド・プレーンに通すと熱性能が改善される。

## アプリケーション情報

A: RETURN  $C_{IN}$  GROUND DIRECTLY TO LT3581 EXPOSED PAD PIN 17. IT IS ADVISED TO NOT COMBINE  $C_{IN}$  GROUND WITH GND EXCEPT AT THE EXPOSED PAD.

B: RETURN  $C_{OUT}$  GROUND DIRECTLY TO LT3581 EXPOSED PAD PIN 17. IT IS ADVISED TO NOT COMBINE  $C_{OUT}$  GROUND WITH GND EXCEPT AT THE EXPOSED PAD.

C: RETURN D1 GROUND DIRECTLY TO LT3581 EXPOSED PAD PIN 17. IT IS ADVISED TO NOT COMBINE D1 GROUND WITH GND EXCEPT AT THE EXPOSED PAD.

L1, L2: MOST COUPLED INDUCTOR MANUFACTURERS USE CROSS PINOUT FOR IMPROVED PERFORMANCE.

**図10. デュアル・インダクタ反転トポロジーの推奨部品配置 (MSOPが示されており、DFNも同様。実寸とは異なる)。** DFNのピン15またはMSOPのピン17は露出パッドであり、適切な熱性能を得るために、ローカル・グランド・プレーンに直接半田付けする必要がある。多数のピアを追加のグランド・プレーンに通すと熱性能が改善される。

## 熱に関する検討事項

## 概要

LT3581 が最大出力で電力を供給するには、パッケージ内部で発生した熱を放散するのに十分な熱経路を与えることが不可欠です。これはデバイス底部の熱パッドの利点を利用して実現することができます。プリント回路板のビアを多数使って、できるだけ面積の大きな銅プレーンにデバイスの熱を逃がすことを推奨します。

## 電力と熱の計算

LT3581 の電力消費は 4 つの主要因から生じます。スイッチの  $I^2R$  損失、スイッチのダイナミック損失、NPN のベース・ドライブの DC 損失、および他の入力電流損失。これらの式は連続モード動作を仮定しているので、不連続モードまたは軽負荷電流での熱損失や効率の計算には使用しません。

次の例では、特定の昇圧アプリケーションの LT3581 の電力損失を計算します ( $V_{IN} = 5V$ 、 $V_{OUT} = 12V$ 、 $I_{OUT} = 0.83A$ 、 $f_{OSC} = 2MHz$ 、 $V_D = 0.45V$ 、 $V_{CESAT} = 0.21V$ )。

ダイの接合部温度を計算するには、適切な熱抵抗値を使い、ワーストケースの周囲温度を加算します。

$$T_J = T_A + \theta_{JA} \cdot P_{TOTAL}$$

**表4. 昇圧アプリケーションの電力損失の例:**  $V_{IN} = 5V$ 、 $V_{OUT} = 12V$ 、 $I_{OUT} = 0.83A$ 、 $f_{OSC} = 2MHz$ 、 $V_D = 0.45V$ 、 $V_{CESAT} = 0.21V$

| 変数の定義                                                                         | 式                                                               | 設計例                                                   | 値                    |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------|----------------------|

| DC = スイッチのデューティ・サイクル                                                          | $DC = \frac{V_{OUT} - V_{IN} + V_D}{V_{OUT} + V_D - V_{CESAT}}$ | $DC = \frac{12V - 5V + 0.45V}{12V + 0.45V - 0.21V}$   | DC = 60.9%           |

| $I_{IN}$ = 平均スイッチ電流<br>$\eta$ = 電力変換効率<br>(高電流で一般に 88%)                       | $I_{IN} = \frac{V_{OUT} \cdot I_{OUT}}{V_{IN} \cdot \eta}$      | $I_{IN} = \frac{12V \cdot 0.83A}{5V \cdot 0.88}$      | $I_{IN} = 2.3A$      |

| $P_{SWDC}$ = スイッチの $I^2R$ 損失 (DC)<br>$R_{SW}$ = スイッチの抵抗 (SW1と SW2を結合して標準90mΩ) | $P_{SWDC} = DC \cdot I_{IN}^2 \cdot R_{SW}$                     | $P_{SWDC} = 0.609 \cdot (2.3A)^2 \cdot 90m\Omega$     | $P_{SWDC} = 290mW$   |

| $P_{SWAC}$ = スイッチのダイナミック損失 (AC)                                               | $P_{SWAC} = 13ns \cdot I_{IN} \cdot V_{OUT} \cdot f_{OSC}$      | $P_{SWAC} = (13ns) \cdot 2.3A \cdot 12V \cdot (2MHz)$ | $P_{SWAC} = 718mW$   |

| $P_{BDC}$ = ベースのドライブ損失 (DC)                                                   | $P_{BDC} = \frac{V_{IN} \cdot I_{IN} \cdot DC}{45}$             | $P_{BDC} = \frac{5V \cdot 2.3A \cdot 0.609}{45}$      | $P_{BDC} = 156mW$    |

| $P_{INP}$ = 入力電力損失                                                            | $P_{INP} = 9mA \cdot V_{IN}$                                    | $P_{INP} = 9mA \cdot 5V$                              | $P_{INP} = 45mW$     |

|                                                                               |                                                                 |                                                       | $P_{TOTAL} = 1.209W$ |

3581fb

## アプリケーション情報

ここで、 $T_J$  = ダイの接合部温度、 $T_A$  = 周囲温度、 $P_{TOTAL}$  は表 4 に示されている計算による最終結果、 $\theta_{JA}$  はシリコンの接合部から周囲の空気までの熱抵抗です。

出版された ([http://www.linear.com/designtools/packaging/Linear\\_Technology\\_Thermal\\_Resistance\\_Table.pdf](http://www.linear.com/designtools/packaging/Linear_Technology_Thermal_Resistance_Table.pdf))  $\theta_{JA}$  の値は、4mm×3mm 14 ピン DFN パッケージでは 43°C/W、16 ピン MSOP パッケージでは 45°C/W です。実際には、基板レイアウトが（基板のヒートシンク特性を考慮に入れた）適切な接地および「レイアウトのガイドライン」のセクションに示されている検討事項に従って行われれば、 $\theta_{JA}$  の値はもっと低くなります。たとえば、基板のレイアウトが「基板レイアウトのガイドライン」のセクションで推奨されているように最適化されていると、( $V_{IN} = 5V$ 、 $V_{OUT} = 12V$ 、 $I_{OUT} = 0.83A$ 、 $f_{OSC} = 2MHz$  のとき) LT3581 の MSE と DFN の両方のパッケージで約 24°C/W の  $\theta_{JA}$  が確実に実現されています。

### 接合部温度の測定

CLKOUT 信号のデューティ・サイクルはダイの接合部温度 ( $T_J$ ) にリニアに比例します。温度を測定するには、CLKOUT 信号のデューティ・サイクルを測定し、次式を使って接合部温度を近似します。

$$T_J = \frac{DC_{CLKOUT} - 35\%}{0.3\%}$$

ここで、 $DC_{CLKOUT}$  は CLKOUT のデューティ・サイクル (%)、 $T_J$  はダイの接合部温度 (°C) です。実際のダイ温度は上式から ±15°C 偏ることがありますが、CLKOUT のデューティ・サイクルの変化とダイ温度の変化の間の関係は十分定められています。基本的には、CLKOUT のデューティ・サイクルの 1% の変化は、ダイ温度の 3.33°C の変化に対応します。CLKOUT ピンは最大 50pF までの容量性負荷をドライブすることだけが意図されていることに注意してください。

### サーマル・ロックアウト

ダイ温度が 165°C を超えるとフォルト状態が生じ（「動作」のセクションを参照）、デバイスはサーマル・ロックアウト状態になります。ダイの温度が約 5°C (公称) 低下するとフォルト状態が解消されます。

### スイッチング周波数

コンバータの動作周波数を選択する際、検討事項がいくつかあります。まず、どんなスペクトル・ノイズも許容できない敏感な周波数帯には近づけないことです。たとえば、RF 通信を組み込んだ製品では、455kHz の IF 周波数はどんなノイズに対しても敏感なので、600kHz を超えるスイッチングが望れます。ある通信方式では 1.1MHz に対して敏感で、この場合、1.5MHz のスイッチング・コンバータ周波数を採用することができます。2つ目の検討事項はコンバータの物理的なサイズです。動作周波数が高くなるにつれ、インダクタおよびフィルタ・コンデンサの値とサイズが小さくなります。スイッチングの動特性による損失（「熱に関する検討事項」を参照）、ショットキー・ダイオードの電荷、および他の容量性損失の項は周波数に比例して増加するので、トレードオフは効率です。

### 発振器のタイミング抵抗 ( $R_T$ )

LT3581 の動作周波数は内部自走発振器によって設定することができます。SYNC ピンを “L” (< 0.4V) にドライブすると、動作周波数は  $R_T$  ピンからグランドに接続した抵抗によって設定されます。このデバイスには内部でトリミングされたタイミング・コンデンサが内蔵されています。発振器の周波数は次式を使って計算されます。

$$f_{OSC} = \frac{87.6}{R_T + 1}$$

ここで、 $f_{OSC}$  の単位は MHz、 $R_T$  の単位は kΩ です。逆に、 $R_T$  (kΩ) は次式を使って望みの周波数 (MHz) から計算することができます。

$$R_T = \frac{87.6}{f_{OSC}} - 1$$

## アプリケーション情報

### クロックの同期

LT3581 の動作周波数は単にデジタル・クロック信号を SYNC ピンに与えるだけで外部ソースによって設定することができます (RT 抵抗は依然必要です)。SYNC ピンが自走クロックの数周期の間 0.4V より下にドライブされると、LT3581 は (RT 抵抗によって設定される) 内部自走発振器のクロックに戻ります。

SYNC を長時間 “H” にドライブすると、動作中のクロックを实际上停止し、ラッチ SR1 がセットされるのを防ぎます (ブロック図を参照)。その結果、LT3581 のスイッチング動作が停止し、CLKOUT ピンはグランドに保持されます。

SYNC 信号のデューティ・サイクルは、適切に動作するためには 20% ~ 80% でなければなりません。また、SYNC 信号の周波数は以下の 2 つの基準を満たす必要があります。

- (1) 自走発振器をイネーブルするために SYNC が “L” (0.4V より下) に停止する以外は、SYNC は 200kHz ~ 2.5MHz の周波数範囲の外側でトグルすることはできません。

- (2) SYNC 周波数は (RT 抵抗によって設定される) 自走発振器の周波数 ( $f_{OSC}$ ) より常に高くすることができますが、 $f_{OSC}$  の 25% 下より低くしてはいけません。

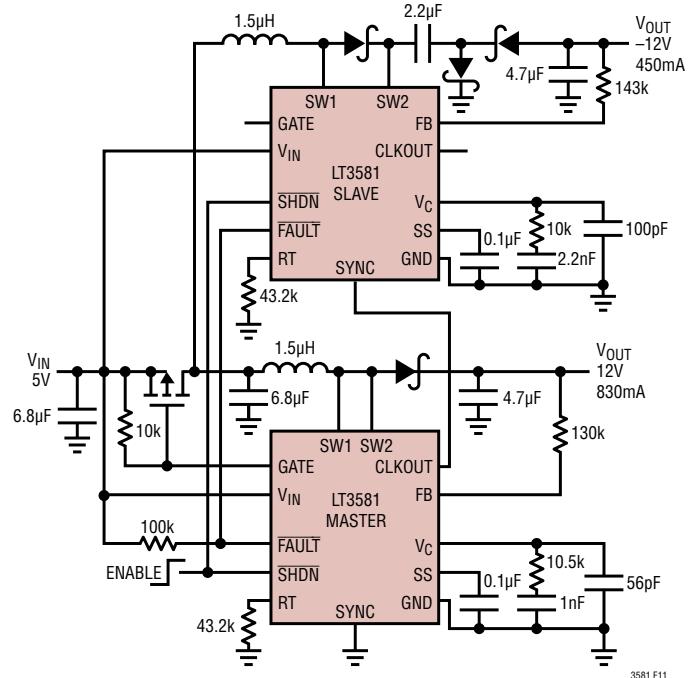

### 追加レギュレータのクロックの同期

図 11 に示されているように、LT3581 の CLKOUT ピンを使って、1 個または複数の他の適合性のあるスイッチング・レギュレータ IC を同期させることができます。

マスタ LT3581 の周波数は外部 RT 抵抗によって設定されます。スレーブ LT3581 の SYNC ピンはマスタ LT3581 の CLKOUT ピンによってドライブされます。スレーブ LT3581 の RT ピンには、グランドに接続した抵抗が必要であることに注意してください。CLKOUT 信号が発振し始めるには数クロック・サイクルが必要で、全ての LT3581 の内部自走周波数を同じにするのが望ましいことです。したがって、一般に、同期させる全ての LT3581 に同じ値の RT 抵抗を使います。

図11. 単一インダクタの反転トポロジーを昇圧レギュレータに同期させて、-12Vと12Vの出力を発生する。FAULT発生時に入力を電力経路から切断するのに外部PMOSが役立つ

また、FAULT ピンを相互に接続することにより、1 つの LT3581 がフォルト状態になると、そのフォルト状態が解消するまで、全ての LT3581 をフォルト状態にすることができます。

### チャージポンプを使うレギュレータ

LT3581 を使ってチャージポンプを設計すると、IC のマスター / スレーブのスイッチ構成により、従来の回路に比べて少ない部品で効率の良いソリューションを実現することができます。スレーブ・スイッチ (SW2) はマスター・スイッチ (SW1) と同じ位相で動作しますが、電流帰還ループの一部として電流コンパレータ (ブロック図の A4) によって検出されるのは、マスター・スイッチ (SW1) を流れる電流だけです。マスター / スレーブ・スイッチによるこの動作方法は、チャージポンプの設計に以下のようないい處をもたらすことができます。

## アプリケーション情報

- スレーブ・スイッチはマスタ・スイッチのように電流検出動作を行わないので、フライング・コンデンサが充電するとき、かなり大きな電流スパイクでも耐えることができます。この電流スパイクは SW2 を流れるので、電流コンパレータ（ブロック図の A4）の動作に影響を与えません。

- マスタ・スイッチは（スレーブ・スイッチにだけ現れる）コンデンサの電流スパイクから免れており、インダクタ電流を精確に検出することができます。

- スレーブ・スイッチは大きな電流スパイクに耐えられるので、フライング・コンデンサに電流を供給するダイオードには電流制限抵抗が不要であり、効率と熱特性が改善されます。

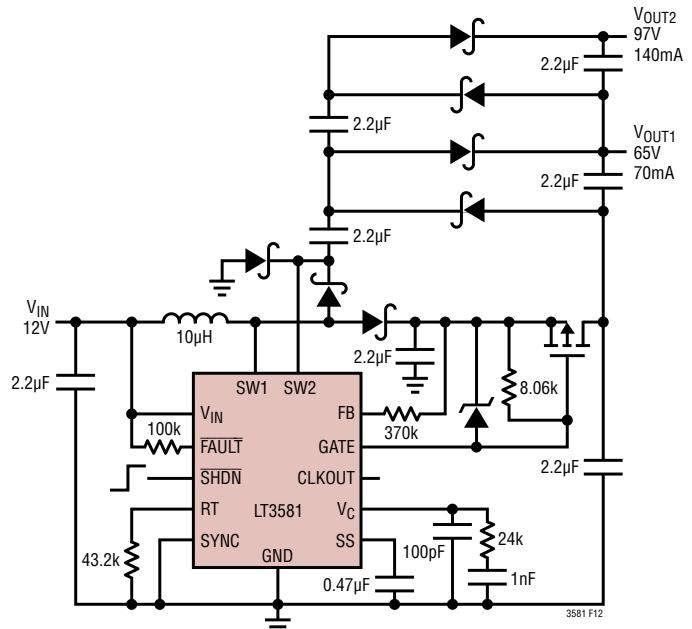

### 高い $V_{OUT}$ のチャージポンプ・トポロジー

LT3581 は図 12 に示されているようなチャージポンプ・トポロジーを使って、誘導性の昇圧コンバータの出力を上げることができます。マスタ・スイッチ (SW1) を使って誘導性昇圧コンバータ（チャージポンプの初段）をドライブすることができます。スレーブ・スイッチ (SW2) を使って 1 個または複数の他のチャージポンプ段をドライブすることができます。このトポロジーは、VFD のバイアス電源などの高電圧アプリケーションに役立ちます。

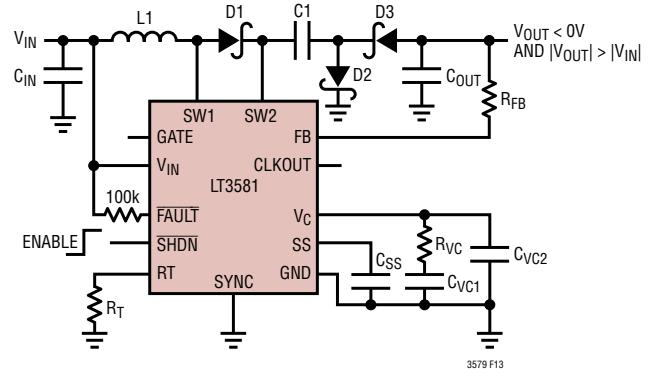

### 単一インダクタ反転トポロジー

インダクタを 1 個だけ使って  $V_{IN}$  より大きな負の出力電圧を発生させる必要がある場合、(図 13 に示されている) 単一インダクタ反転トポロジーを使うことができます。マスタ・スイッチとスレーブ・スイッチはショットキー・ダイオードによって絶縁されているので、C1 を流れる電流スパイクはスレーブ・スイッチだけを流れ、そのため、電流コンパレータ（ブロック図の A4）が誤ってトリップするのが防がれます。単一インダクタ・トポロジーには出力の切断機能が本来組み込まれています。

図12. 高出力電圧のチャージポンプ・トポロジーを使ってVFD用バイアス電源を構築することができる

図13. 単一インダクタ反転トポロジー

## アプリケーション情報

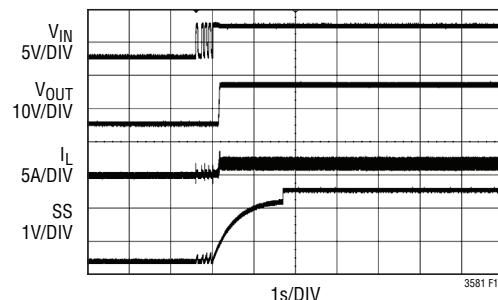

### 活線挿入

$V_{IN}$  の活線挿入に伴う高い突入電流は、外部 PMOS を使って大部分除去することができます。外部 PMOS を  $V_{IN}$  に直列に接続することにより、簡単な活線挿入コントローラを設計することができます。PMOS のゲートは LT3581 の GATE ピンでドライブします。GATE ピンのプルダウン電流は SS 電圧にリニアに比例し、SS の充電時間は比較的遅いので、GATE ピンのプルダウン電流は徐々に増加し、外部 PMOS をゆっくりオンします。このように制御されるので、 $V_{IN}$  が活線挿入されるとき、または急激にランプアップするとき、PMOS は入力電流制限として機能します。

同様に、PMOS が出力に直列に接続されていると、活線挿入時に出力コンデンサへの突入電流を制限することができます。これを説明するため、図 18 の回路は、大きな  $1500\mu F$  のコンデンサを出力に追加して構成し直され

ています。 $18\Omega$  の抵抗負荷が使われており、 $2.2\mu F$  のコンデンサが SS に接続されています。この再構成された回路の活線挿入の結果を図 14 に示します。インダクタ電流がいかに良く制御されているか注意してください。

図14. 図18の再構成された昇圧コンバータが活線挿入されたにも係わらず、突入電流が良く制御されている

## 付録

### 出力電圧の設定

出力電圧は抵抗 ( $R_{FB}$ ) を  $V_{OUT}$  から FB ピンに接続して設定します。 $R_{FB}$  は次式を使って決定します。

$$R_{FB} = \frac{|V_{OUT} - V_{FB}|}{83.3\mu A}$$

ここで、非反転トポロジー（つまり、昇圧およびSEPICのレギュレータ）では  $V_{FB}$  は 1.215V（標準）、反転トポロジーでは 5mV（標準）です。

### パワースイッチのデューティ・サイクル

ループの安定性を維持し、適切な電流を負荷に供給するため、パワー NPN（ブロック図の Q1 と Q2）は各クロック・サイクルの 100% の間「オン」に留まることはできません。最大許容デューティ・サイクルは次式で与えられます。

$$DC_{MAX} = \frac{(T_P - MinOffTime)}{T_P} \cdot 100\%$$

ここで、 $T_P$  はクロックの周期、「電気的特性」に示されている  $MinOffTime$  は標準 60ns です。

逆に、パワー NPN（「ブロック図」の Q1 と Q2）は各クロック・サイクルの 100% の間オフのままでいることはできず、安定化状態では最小オン時間（ $MinOnTime$ ）の間オンします。この  $MinOnTime$  は次式で与えられる最小許容デューティ・サイクルを支配します。

$$DC_{MIN} = \frac{(MinOnTime)}{T_P} \cdot 100\%$$

ここで、 $T_P$  はクロックの周期、「電気的特性」に示されている  $MinOnTime$  は標準 100ns です。

動作デューティ・サイクルが  $DC_{MIN}$  と  $DC_{MAX}$  の間になるようにアプリケーションを設計します。

いくつかの一般的トポロジーのデューティ・サイクルの式を下に示します。ここで、 $V_D$  はダイオードの順方向電圧降下、 $V_{CESAT}$  はスイッチのコレクタ-エミッタの飽和電圧です。SW1 と SW2 が相互に接続された状態で、合わせたスイッチ電流 ( $I_{SW1} + I_{SW2}$ ) が 2.75A のとき  $V_{CESAT}$  は標準 250mV です。

昇圧トポロジーでは次のようになります（図 5 を参照）。

$$DC_{BOOST} \cong \frac{V_{OUT} - V_{IN} + V_D}{V_{OUT} + V_D - V_{CESAT}}$$

SEPIC トポロジーまたはデュアル・インダクタ反転トポロジーでは次のようになります（図 6 と図 7 を参照）。

$$DC_{SEPIC\_&\_INVERT} \cong \frac{V_D + |V_{OUT}|}{V_{IN} + |V_{OUT}| + V_D - V_{CESAT}}$$

单一インダクタ反転トポロジーでは次のようになります（図 13 を参照）。

$$DC_{SI\_INVERT} = \frac{|V_{OUT}| - V_{IN} + V_{CESAT} + 3 \cdot V_D}{|V_{OUT}| + 3 \cdot V_D}$$

LT3581 はデューティ・サイクルが  $DC_{MAX}$  より高い構成で使うことができますが、実効デューティ・サイクルが減少するように、不連続導通モードで動作させる必要があります。

### インダクタの選択

一般的ガイドライン：LT3581 は高い周波数で動作するので小型の表面実装インダクタを使用できます。高効率を実現するには、フェライトなどの高周波用コア材のインダクタを選択して、コア損失を減らします。また、効率を改善するため、与えられたインダクタンスに対してサイズの大きなインダクタを選択します。 $I^2R$  損失を減らすため、インダクタは DCR（銅線抵抗）が小さく、飽和せずにピーク・インダクタ電流を流すことができるものにします。各インダクタが全スイッチ電流の半分しか流さない SEPIC トポロジーのようなアプリケーションでは、インダクタに要求される処理電流は大きくないことに注意してください。モールド型チョークコイルやチップ・インダクタのコア面積は一般に 2A ~ 6A の範囲のピーク・インダクタ電流を担うのに十分ではありません。放射ノイズを抑えるには、トロイド、またはシールドされたインダクタを使用します。インダクタのメーカーについては表 5 を参照してください。

表5. インダクタ・メーカー

|             |                                                          |                                                          |

|-------------|----------------------------------------------------------|----------------------------------------------------------|

| Sumida      | CDR6D28MN and CDR7D28MN Series                           | <a href="http://www.sumida.com">www.sumida.com</a>       |

| Coilcraft   | MSD7342 Series                                           | <a href="http://www.coilcraft.com">www.coilcraft.com</a> |

| Vishay      | IHLP-1616BZ-01, IHLP-2020BZ-01 and IHLP-2525CZ-01 Series | <a href="http://www.vishay.com">www.vishay.com</a>       |

| Taiyo Yuden | NR Series                                                | <a href="http://www.t-yuden.com">www.t-yuden.com</a>     |

| Wurth       | WE-PD Series                                             | <a href="http://www.we-online.com">www.we-online.com</a> |

| TDK         | VLF, SLF and RLF Series                                  | <a href="http://www.tdk.com">www.tdk.com</a>             |

## 付録

### 最小インダクタンス

効率が犠牲になる可能性があるとはいっても、小さなインダクタを選択して基板スペースを最小に抑えるのが望ましい場合があります。インダクタを選択するとき、最小インダクタンスを制限する3つの条件があります。

- (1) 適切な負荷電流の供給、(2) 低調波発振の防止、および(3) 電流コンパレータの誤ったトリップを防ぐための最小リップル電流の供給です。

### 適切な負荷電流

値の小さなインダクタだとリップル電流が増加するので、(ピーク・スイッチ電流が制限されるため) 負荷に供給できる平均電流が減少します。適切な負荷電流を供給するため、Lは少なくとも次のようにします。

$$\left. \begin{aligned} L_{\text{BOOST}} &> \frac{DC \cdot (V_{IN} - V_{CESAT})}{2 \cdot f_{OSC} \cdot \left( I_{PK} - \frac{|V_{OUT}| \cdot I_{OUT}}{V_{IN} \cdot \eta} \right)} \\ &\quad \text{or} \\ L_{\text{DUAL}} &> \frac{DC \cdot (V_{IN} - V_{CESAT})}{2 \cdot f_{OSC} \cdot \left( I_{PK} - \frac{|V_{OUT}| \cdot I_{OUT} - I_{OUT}}{V_{IN} \cdot \eta} \right)} \end{aligned} \right\} \begin{array}{l} \text{Boost} \\ \text{Topology} \\ \text{or} \\ \text{SEPIC} \\ \text{or} \\ \text{Inverting} \\ \text{Topologies} \end{array}$$

ここで、

- $L_{\text{BOOST}}$  = 昇圧トポロジーの場合の  $L_1$  (図5を参照)

- $L_{\text{DUAL}}$  =  $L_1$  = 結合されたデュアル・インダクタ・トポロジーの場合の  $L_2$  (図6と図7を参照)

- $L_{\text{DUAL}}$  = 結合されていないデュアル・インダクタ・トポロジーの場合の  $L_1 \parallel L_2$  (図6と図7)

- $DC$  = スイッチのデューティ・サイクル ('付録' の「パワースイッチのデューティ・サイクル」のセクションを参照)

- $I_{PK}$  = 最大ピーク・スイッチ電流；3.3Aの結合されたSW1+SW2電流、またはSW1だけが使用される場合は1.9AのSW1電流を超えないようにする。

- $\eta$  = 電力変換効率 (高電流のとき昇圧トポロジーでは標準88%、デュアル・インダクタ・トポロジーでは75%)

- $f_{OSC}$  = スイッチング周波数

- $I_{OUT}$  = 最大出力電流

$L_{\text{BOOST}}$  または  $L_{\text{DUAL}}$  の負の値は、出力負荷電流 ( $I_{OUT}$ ) がLT3581のスイッチ電流制限能力を超えていることを示しています。

### 低調波発振の防止

LT3581の内部スロープ補償回路は、インダクタンスが特定の最小値を超えていれば、デューティ・サイクルが50%を超えると発生する可能性のある低調波発振を防止します。50%を超えるデューティ・サイクルで動作するアプリケーションでは、インダクタンスは少なくとも次の値でなければなりません。

$$L_{\text{MIN}} = \frac{(V_{IN} - V_{CESAT}) \cdot (2 \cdot DC - 1)}{2.2A \cdot f_{OSC} \cdot (1 - DC)}$$

ここで、

- $L_{\text{MIN}}$  = 昇圧トポロジーの場合の  $L_1$  (図5を参照)

- $L_{\text{MIN}}$  =  $L_1$  = 結合されたデュアル・インダクタ・トポロジーの場合の  $L_2$  (図6と図7を参照)

- $L_{\text{MIN}}$  = 結合されていないデュアル・インダクタ・トポロジーの場合の  $L_1 \parallel L_2$  (図6と図7)

### 最大インダクタンス

インダクタンスがあまりにも大きいと、電流コンパレータ ('ブロック' 図のA4) が明瞭に区別するのが困難なレベルにまでリップル電流が減少し、デューティ・サイクルのジッタやレギュレーションの低下が生じます。最大インダクタンスは次式で計算することができます。

$$L_{\text{MAX}} = \frac{V_{IN} - V_{CESAT}}{350\text{mA}} \cdot \frac{DC}{f_{OSC}}$$

ここで、

- $L_{\text{MAX}}$  = 昇圧トポロジーの場合の  $L_1$  (図5を参照)

- $L_{\text{MAX}}$  =  $L_1$  = 結合されたデュアル・インダクタ・トポロジーの場合の  $L_2$  (図6と図7を参照)

- $L_{\text{MAX}}$  = 結合されていないデュアル・インダクタ・トポロジーの場合の  $L_1 \parallel L_2$  (図6と図7)

## 付録

### インダクタ電流定格

インダクタはそれらのピーク動作電流より大きな定格のものでなければならず、そうでないと飽和して、効率低下を生じことがあります。最大インダクタ電流は（スタートアップ条件および定常条件を考慮して）次式で与えられます。

$$I_{L\_PEAK} = I_{LIM} + \frac{V_{IN} \cdot T_{MIN\_PROP}}{L}$$

ここで、

$I_{L\_PEAK}$  = 昇圧トポロジーの場合の  $L_1$  のピーク・インダクタ電流、またはデュアル・インダクタ・トポロジーの場合の  $L_1$  と  $L_2$  のインダクタ電流の和のピーク

$I_{LIM}^{**}$  = 相互に結合された SW1 と SW2 では 3.3A、または SW1 だけでは 1.9A（これは鉄粉コアなどコア材がソフトに飽和するインダクタの使用を仮定している）。

$T_{MIN\_PROP} = 100\text{ns}$  (電流帰還ループの伝播遅延)。

\*\* コア材がハードに飽和するインダクタを使用する場合（たとえば、フェライト）、SW1 と SW2 が相互に結合されるときは  $I_{LIM}$  が 5.4A になるように、SW1 だけが使われるときは 3A になるように選択します。

これらの式は必要なインダクタ電流定格の控えめな値を与えることに注意してください。SS のコンデンサのサイズを適切に定めてスタートアップ時のインダクタ電流を制限すれば、負荷が軽いアプリケーションでは電流定格を下げることができます。

### ダイオードの選択

ショットキー・ダイオードは順方向電圧降下が小さく、スイッチング速度が速いので、LT3581 と一緒に使うのに推奨します。寄生容量が低いショットキー・ダイオードを選択して、LT3581 のパワースイッチを流れる逆電流スパイクを減らします。Central Semiconductor Corp. の CMMHS2-40 ダイオードは逆電圧定格が 40V、平均順方向電流が 2A であり、最適です。

### 出力コンデンサの選択

出力リップル電圧を下げるため、出力には低 ESR（等価直列抵抗）のコンデンサを使います。多層セラミック・

コンデンサは ESR が非常に小さく、小型パッケージのものが入手できるので、最適です。X5R や X7R の誘電体は広い電圧範囲と温度範囲にわたってそれらの容量を保持するので最も好まれます。10 $\mu\text{F}$  ~ 22 $\mu\text{F}$  の出力コンデンサはほとんどのアプリケーションに十分ですが、出力電流が非常に低いシステムには 2.2 $\mu\text{F}$  ~ 10 $\mu\text{F}$  の出力コンデンサしか必要ないかもしれません。必ず電圧定格が十分大きなコンデンサを使ってください。ほとんどのセラミック・コンデンサ（特に 0805 または 0603 のケース・サイズ）は望みの出力電圧で容量が大きく減少します。タンタルポリマー・コンデンサまたは OS-CON コンデンサを使うことができますが、セラミック・コンデンサよりも大きなボード面積を占め、ESR が大きくなり、出力リップルが増加する可能性が高くなります。

### 入力コンデンサの選択

セラミック・コンデンサは入力デカップリング・コンデンサに最適です。デバイスの  $V_{IN}$  のすぐ近くで、さらに電力経路の入力に接続されたインダクタのすぐ近くにくるように配置します。1 個の入力コンデンサを最善の位置に配置できない場合、2 個のコンデンサを使用します。1 個はデバイスの  $V_{IN}$  (表1、表2、表3 の  $C_{VIN}$  の式を参照)、1 個は電力経路の入力 (表1、表2、表3 の  $C_{PWR}$  の式を参照) に使います。4.7 $\mu\text{F}$  ~ 20 $\mu\text{F}$  の入力コンデンサがほとんどのアプリケーションで十分です。

セラミック・コンデンサのメーカーを数社表6 に示します。セラミック部品の全製品の詳細についてはメーカーへお問い合わせください。

表6:セラミック・コンデンサのメーカー

|             |                                                      |

|-------------|------------------------------------------------------|

| AVX         | <a href="http://www.avxcorp.com">www.avxcorp.com</a> |

| Murata      | <a href="http://www.murata.com">www.murata.com</a>   |

| Taiyo Yuden | <a href="http://www.t-yuden.com">www.t-yuden.com</a> |

### PMOS の選択

LT3581 の GATE ピンによって制御される外部 PMOS を使って、入力または出力を切断することができます。GATE ピンはスタートアップ時に PMOS を徐々にオンし（「動作」のセクションの「外部 PMOS のソフトスタート」を参照）、LT3581 がシャットダウン状態またはフォルト状態のとき PMOS をオフします。

## 付録

GATE ピンによって制御される外部 PMOS の使用は、昇圧レギュレータの偶発的出力短絡に対処するとき特に有用です。従来の昇圧レギュレータでは、インダクタ、ショットキー・ダイオード、およびパワースイッチは、グランドへの出力短絡が発生したとき損傷を受けやすくなります。昇圧レギュレータの電力経路 ( $V_{IN}$  から  $V_{OUT}$  への経路) 内に、GATE ピンによって制御される外部 PMOS を使うと、出力がグランドに短絡したとき入力を出力から切断して、IC および電力経路内の他の部品を損傷から保護するのに役立ちます。ダイオードとインダクタの両方とも、それらの定常状態のレベルの 3 倍～4 倍の低デューティ・サイクル電流パルスに対して確実に耐え抜くことができるようになります。

選択された PMOS は、その PMOS が入力に使われているか (図 11 を参照) それとも出力に使われているか (図 18 を参照) に依存して、最大入力電流または最大出力電流を処理する能力が必要です。

PMOS が、3 極動作するのに十分なだけエンハンスされるソース - ゲート電圧 ( $V_{SG}$ ) で確実にバイアスされるようにします。PMOS を 3 極動作状態にバイアスする  $V_{SG}$  電圧が高いほど、PMOS の  $R_{DS(ON)}$  が低くなるので、通常動作時のデバイス内の電力損失が下がり、PMOS が使用されているアプリケーションの効率が改善されます。以下の式は、 $R_{GATE}$  (「ブロック図」を参照) と、PMOS がバイアスされる望みの  $V_{SG}$  との関係を示しています。

$$V_{SG} = \begin{cases} V_{IN} \frac{R_{GATE}}{R_{GATE} + 2k\Omega} & \text{if } V_{GATE} < 2V \\ 933\mu A \cdot R_{GATE} & \text{if } V_{GATE} \geq 2V \end{cases}$$

PMOS を使う場合、対象となるアプリケーションを低電圧ロックアウトを実現するように構成することを推奨します (「動作」のセクションを参照)。目標は、 $V_{IN}$  がある最小電圧に達するようにして、そこでは PMOS に十分な空き高があって十分高い  $V_{SG}$  が得られ、スタートアップ時に PMOS が飽和モードの動作になるのを防ぐことです。

出力に直列に接続されていて、フォルト状態の間出力を切断する PMOS を図 18 に示します。 $V_{IN}$  ピンから GATE ピンに接続されたショットキー・ダイオードはオプションで、ハードな短絡発生時に PMOS を素早くオフするのに役立ちます。 $V_{IN}$  から  $\overline{SHDN}$  ピンに接続された抵抗分割器により、このアプリケーションの 4V の UVLO が設定されます。

PMOS を出力に直列に接続すると、入力に直列に接続するよりも利点が与えられます。

- 昇圧コンバータでは負荷電流が常に入力電流より少ないので、PMOS の電流定格が低下します。

- 出力に直列な PMOS は、 $V_{OUT} > V_{IN}$  なので、入力に直列に使われる PMOS より高いオーバードライブ電圧でバイアスすることができます。オーバードライブがこのように高くなるので PMOS の  $R_{DS(ON)}$  定格が下がり、そのため、レギュレータの効率が改善されます。

対照的に、入力に接続された PMOS は簡単な活線挿入コントローラとして機能します (詳細は「活線挿入」のセクションで説明されています)。入力に接続された PMOS は、LT3581 を他の適合性のある IC と同期させる昇圧コンバータ・アプリケーションで生じる複数の出力短絡に対して保護する低成本の手段としても機能します (図 11 参照)。

ディスクリート PMOS のメーカーをいくつか表 7 に示します。PMOS デバイスの全製品の詳細についてはメーカーへお問い合わせください。

表7. ディスクリートPMOSメーカー

|                         |                                                                  |

|-------------------------|------------------------------------------------------------------|

| Vishay                  | <a href="http://www.vishay.com">www.vishay.com</a>               |

| Fairchild Semiconductor | <a href="http://www.fairchildsemi.com">www.fairchildsemi.com</a> |

### 補償 - 調整

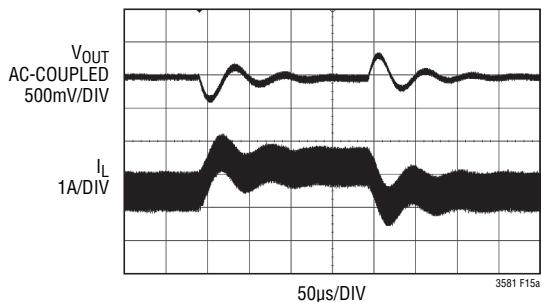

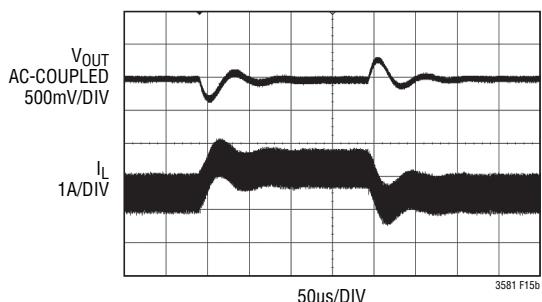

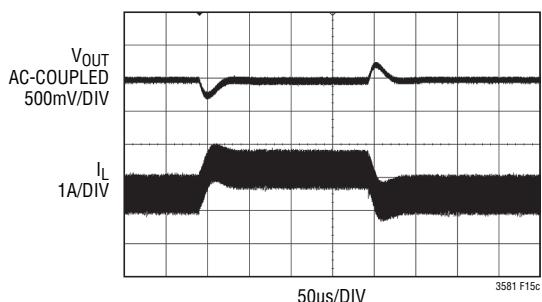

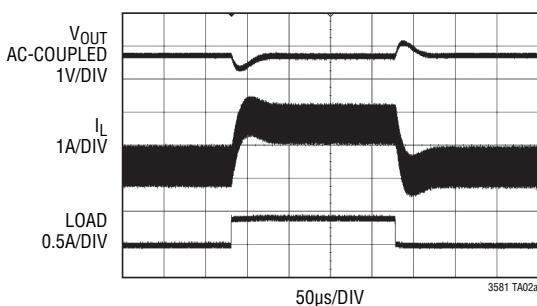

LT3581 の帰還ループを補償するには、1 個のオプションのコンデンサに並列な直列 RC ネットワークを COMP ピンから GND に接続します。ほとんどのアプリケーションでは、1nF ~ 10nF の直列コンデンサを選択します。2.2nF が出発点の値として適当でしょう。オプションの並列コンデンサの値は 47pF ~ 160pF にします。100pF が出発点の値として適当でしょう。補償抵抗 ( $R_C$ ) は通常 5k ~ 50k の範囲です。10k が出発点の値として適当でしょう。新しいアプリケーションを補償する良い手法として、直列抵抗  $R_C$  の代わりに 100kΩ のポテンショメータを使います。それぞれ 2.2nF と 100pF の直列コンデンサと並列コンデンサを使って、過渡応答を観察しながらポテンショメータを調節し、 $R_C$  の最適値を見つけることができます。負荷電流を 540mA と 800mA の間でステップさせたときの図 18 の回路のこの過程を図 15a ~ 図 15c に示します。 $R_C$  が 1k に等しいときの過渡応答を図 15a

## 付録

に示します。出力電圧とインダクタ電流の過度のリングから明らかのように、位相マージンが良くありません。図15bでは、 $R_C$ の値を3kに増やしているので、もっと減衰した応答になっています。 $R_C$ をさらに10.5kにまで増やしたときの結果を図15cに示します。過渡応答が十分減衰し、補償の調整は完了です。

図15a. 過度のリングを示す過渡応答

図15b. 改善された過渡応答

図15c. 十分減衰した過渡応答

## 補償 - 理論

他のすべての電流モード・スイッチング・レギュレータと同様、LT3581を安定して効率よく動作させるには補償が必要です。LT3581には2個の帰還ループがあります。補償の不要な高速電流ループと、補償の必要な低速電圧ループです。標準ボーデ図の分析方法を使って、電圧帰還ループを理解し、調節することができます。

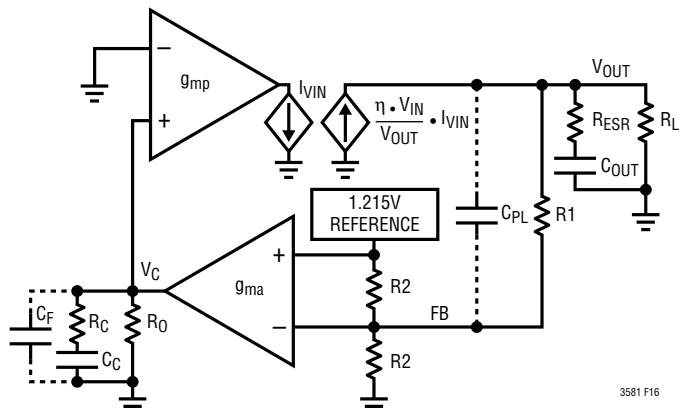

どんな帰還ループの場合でもそうですが、ループ内の多様な素子が利得や位相に与える影響を知ることが決定的に重要です。昇圧コンバータの主要な等価素子を図16に示します。高速電流制御ループのため、ICの電力段、インダクタ、およびダイオードは同等のトランジスタコンダクタンス・アンプ  $g_{mp}$  と ( $I_{VIN}$  を  $\eta \cdot V_{IN}/V_{OUT} \cdot I_{VIN}$  に変換する) 電流制御電流源の組み合わせで置き換えてあります。 $g_{mp}$  はピーク入力電流 ( $I_{VIN}$ ) が  $V_C$  電圧に比例する電流源として機能します。 $\eta$  はスイッチング・レギュレータの効率で標準で約80%です。

$g_{mp}$ 段と $g_{ma}$ 段の最大出力電流は有限であることに注意してください。 $g_{mp}$ 段の出力は最小スイッチ電流制限によって制限されており(「電気的特性」を参照)、 $g_{ma}$ 段の出力は約 $\pm 12\mu A$ (公称)に制限されています。

C<sub>F</sub>: COMPENSATION CAPACITOR

C<sub>OUT</sub>: OUTPUT CAPACITOR

C<sub>PPL</sub>: PHASE LEAD CAPACITOR

C<sub>F</sub>: HIGH FREQUENCY FILTER CAPACITOR

$g_{ma}$ : TRANSCONDUCTOR AMPLIFIER INSIDE IC

$g_{mp}$ : POWER STAGE TRANSCONDUCTANCE AMPLIFIER

R<sub>c</sub>: COMPENSATION RESISTOR

R<sub>f</sub>: OUTPUT RESISTANCE DEFINED AS  $V_{OUT}/I_{LOAD(MAX)}$

R<sub>O</sub>: OUTPUT RESISTANCE OF  $g_{ma}$

R<sub>1</sub>, R<sub>2</sub>: FEEDBACK RESISTOR DIVIDER NETWORK

R<sub>ESR</sub>: OUTPUT CAPACITOR ESR

図16. 昇圧コンバータの等価モデル

## 付録

図 16 から、DC 利得、ポール、およびゼロは以下のように計算されます。

### DC Gain:

(Breaking loop at FB pin)

$$A_{DC} = A_{OL}(0) = \frac{\partial V_C}{\partial V_{FB}} \cdot \frac{\partial I_{VIN}}{\partial V_C} \cdot \frac{\partial V_{OUT}}{\partial I_{VIN}} \cdot \frac{\partial V_{FB}}{\partial V_{OUT}} =$$

$$(g_{ma} \cdot R_0) \cdot g_{mp} \cdot \left( \eta \cdot \frac{V_{IN}}{V_{OUT}} \cdot \frac{R_L}{2} \right) \cdot \frac{0.5R_2}{R_1 + 0.5R_2}$$

$$\text{Output Pole: } P_1 = \frac{2}{2 \cdot \pi \cdot R_L \cdot C_{OUT}}$$

$$\text{Error Amp Pole: } P_2 = \frac{1}{2 \cdot \pi \cdot [R_0 + R_C] \cdot C_C}$$

$$\text{Error Amp Zero: } Z_1 = \frac{1}{2 \cdot \pi \cdot R_C \cdot C_C}$$

$$\text{ESR Zero: } Z_2 = \frac{1}{2 \cdot \pi \cdot R_{ESR} \cdot C_{OUT}}$$

$$\text{RHP Zero: } Z_3 = \frac{V_{IN}^2 \cdot R_L}{2 \cdot \pi \cdot V_{OUT}^2 \cdot L}$$

$$\text{High Frequency Pole: } P_3 > \frac{f_S}{3}$$

$$\text{Phase Lead Zero: } Z_4 = \frac{1}{2 \cdot \pi \cdot R_1 \cdot C_{PL}}$$

$$\text{Phase Lead Pole: } P_4 = \frac{1}{2 \cdot \pi \cdot \frac{R_1 \cdot R_2}{R_1 + \frac{2}{R_2} \cdot C_{PL}}}$$

### Error Amp Filter Pole:

$$P_5 = \frac{1}{2 \cdot \pi \cdot \frac{R_C \cdot R_0}{R_C + R_0} \cdot C_F}, C_F < \frac{C_C}{10}$$

電流モードのゼロ (Z3) は右半平面のゼロで、これは帰還制御の設計では問題になることがあります。外部部品を適切に選択して調整可能です。

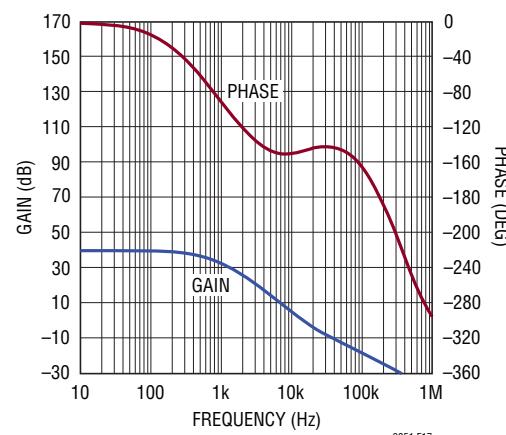

図 18 の回路を一例として使って、図 17 に示されているボーデ図を描くのに使われたパラメータを表 8 に示します。

表8. ボーデ図のパラメータ

| パラメータ            | 値     | 単位   | 説明          |

|------------------|-------|------|-------------|

| R <sub>L</sub>   | 14.5  | Ω    | アプリケーションに固有 |

| C <sub>OUT</sub> | 9.4   | μF   | アプリケーションに固有 |

| R <sub>ESR</sub> | 1     | mΩ   | アプリケーションに固有 |

| R <sub>0</sub>   | 305   | kΩ   | 調整不可        |

| C <sub>C</sub>   | 1000  | pF   | 調整可         |

| C <sub>F</sub>   | 56    | pF   | オプション/調整可   |

| C <sub>PL</sub>  | 0     | pF   | オプション/調整可   |

| R <sub>C</sub>   | 10.5  | kΩ   | 調整可         |

| R <sub>1</sub>   | 130   | kΩ   | 調整可         |

| R <sub>2</sub>   | 14.6  | kΩ   | 調整不可        |

| V <sub>REF</sub> | 1.215 | V    | 調整不可        |

| V <sub>OUT</sub> | 12    | V    | アプリケーションに固有 |

| V <sub>IN</sub>  | 5     | V    | アプリケーションに固有 |

| g <sub>ma</sub>  | 270   | μmho | 調整不可        |

| g <sub>mp</sub>  | 15.1  | mho  | 調整不可        |

| L                | 1.5   | μH   | アプリケーションに固有 |

| f <sub>osc</sub> | 2     | MHz  | 調整可         |

図 17 から、利得が 0dB に達するときの位相は -130° で、位相マージンが 50° になります。クロスオーバー周波数は 17kHz です。これは RHP のゼロ Z3 の周波数の 1/3 以下で、適切な位相マージンを達成します。

図17. 昇圧コンバータの例のボーデ図

## 標準的応用例

C1: 4.7μF 16V, X7R, 1206

C2, C3: 4.7μF 25V, X7R, 1206

D1: DIODES INC. PD3S230H-7

L1: SUMIDA CDR6D28MN-IR5

M1: VISHAY SILICONIX SI7123DN

図18. 出力の短絡に対して保護された、2MHz、5Vから12V、830mAの昇圧コンバータ

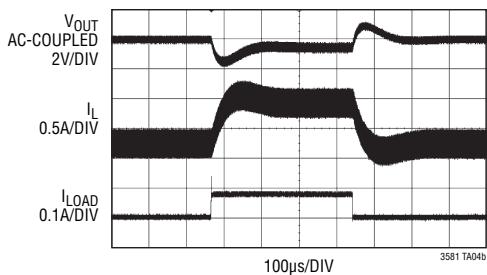

430mAから830mA、さらに430mAへの負荷ステップに対する過渡応答

830mA負荷でのスイッチング波形

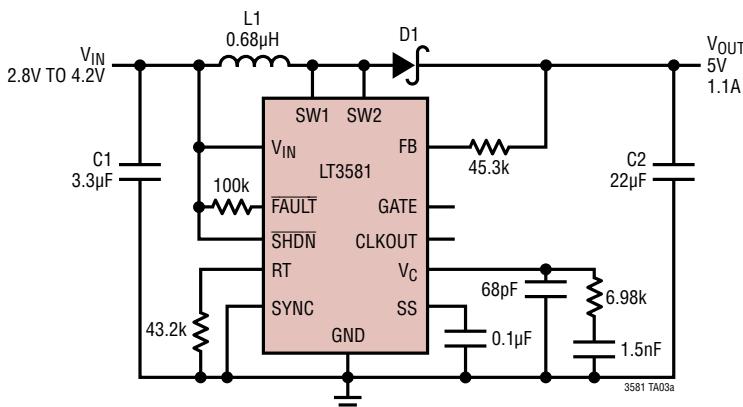

2.8V～4.2Vの入力範囲で動作する、2MHz、5V、1.1Aの昇圧コンバータ

C1: 3.3μF 16V, X7R, 1206

C2: 22μF 16V, X7R, 1210

D1: DIODES INC. PD3S230H-7

L1: VISHAY IHLP1616 BZ-01-OR68 (ONLY 4.1mm × 4.5mm × 2mm)

## 標準的応用例

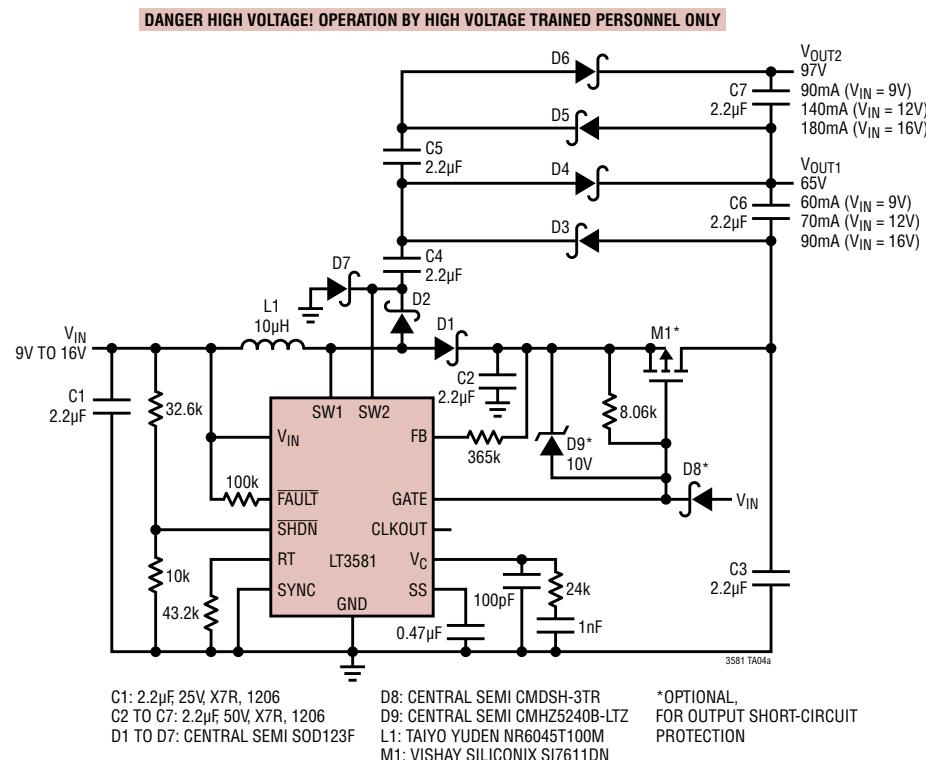

AMバンドを避けるため2MHzでスイッチングするVFD(真空蛍光ディスプレイ)用の高効率電源

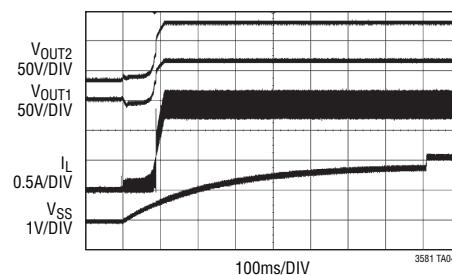

60mAから140mA、さらに60mAへの負荷ステップに対するV<sub>OUT2</sub>の過渡応答 (V<sub>IN</sub> = 12V)

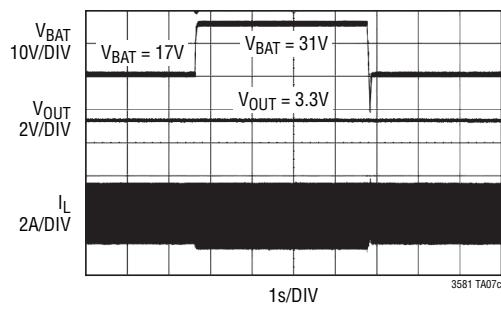

スタートアップ波形

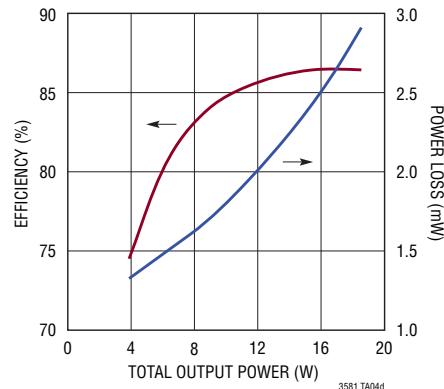

V<sub>IN</sub> = 12Vでの効率と電力損失

3581fb

## 標準的応用例

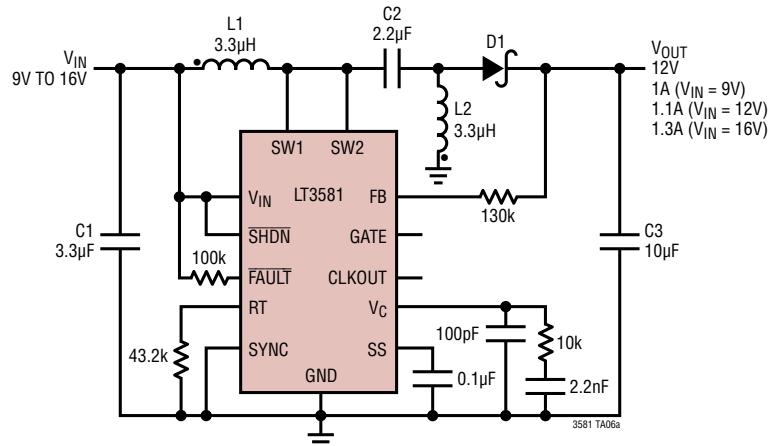

9V～16Vの入力電圧を受け入れ可能な、2MHz、12VのSEPICコンバータ

C1: 3.3 $\mu$ F 25V, X7R, 1206

C2: 2.2 $\mu$ F 50V, X7R, 1206

C3: 10 $\mu$ F 25V, X7R, 1210

D1: CENTRAL SEMI CTLSH2-40M832

L1, L2: COILCRAFT MSD7342-332MLB

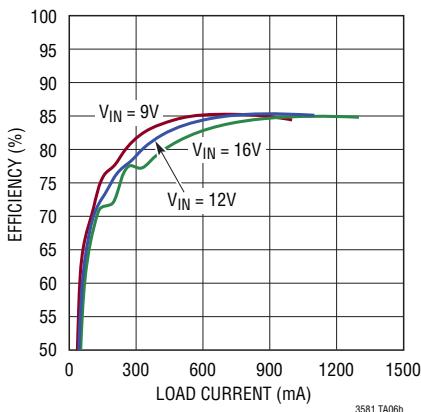

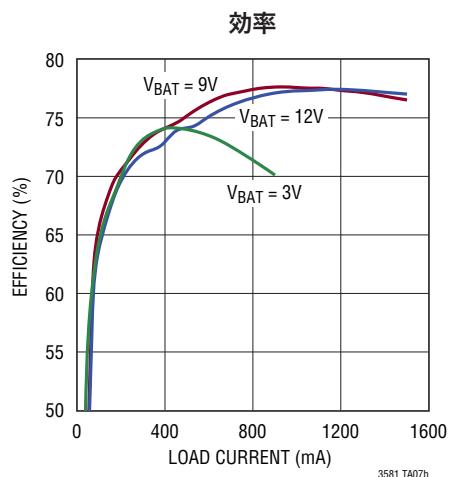

効率

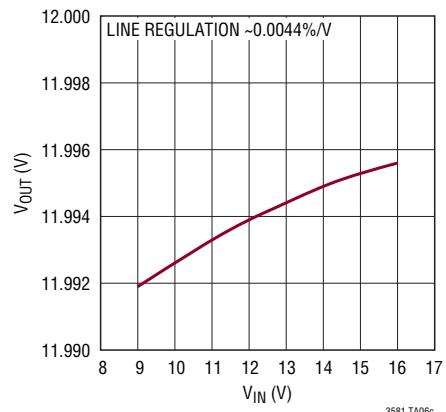

無負荷でのライン・レギュレーション

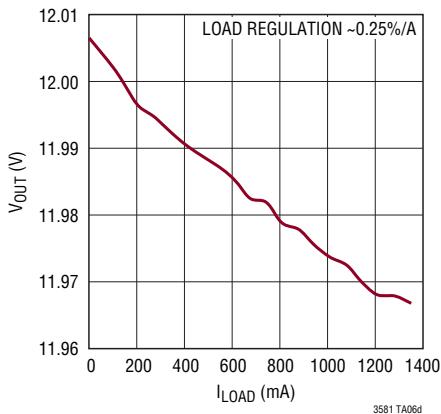

V<sub>IN</sub> = 12での負荷レギュレーション

## 標準的応用例

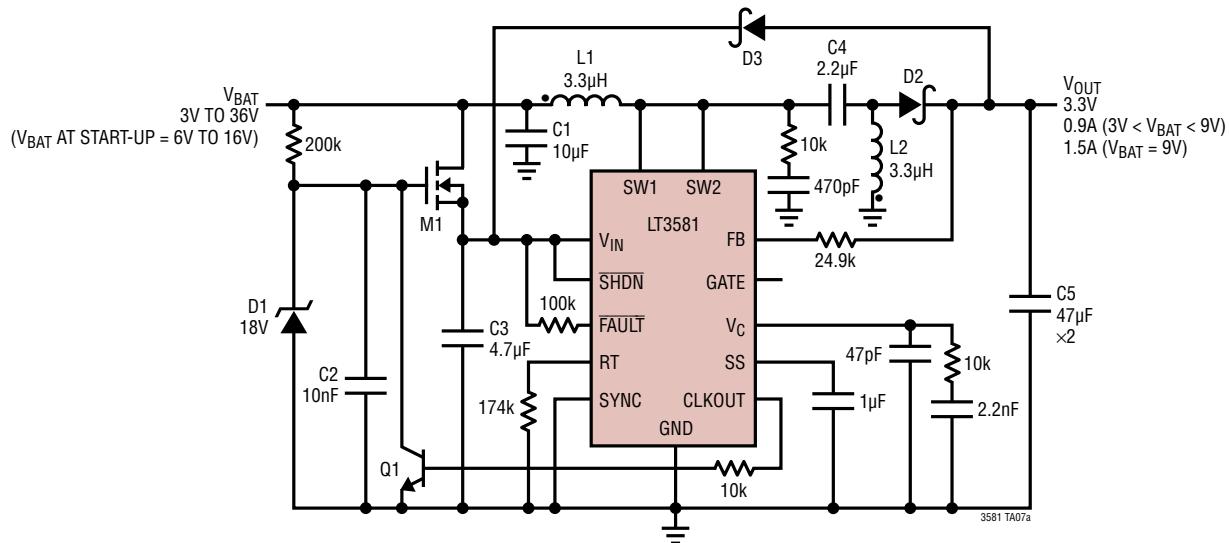

3V～36Vで動作可能な、入力範囲の広い3.3VのSEPICコンバータ

C1: 10 $\mu$ F, 50V, X7R, 1210

C2: 10nF, 25V, X7R, 0603

C3: 4.7 $\mu$ F, 25V, X7R, 1206

C4: 2.2 $\mu$ F, 50V, X7R, 1206

C5: 47 $\mu$ F, 10V, X7R, 1210

D1: CENTRAL SEMI CMHZ5248B-LT

D2: CENTRAL SEMI CMMSSH2-40

D3: DIODES INC. PD3S230H-7

L1, L2: COILCRAFT MSD7342-332MLB

M1: 2N7002

Q1: MMBT3904

$V_{IN\_OVP}$ より高い $V_{BAT}$ 電圧に耐え抜くことができる、

入力範囲の広いSEPIC

## 標準的応用例

インダクタを1個だけ使う、1MHz、±12Vのチャージポンプ・トポロジー

C1: 3.3μF, 25V, X7R, 1206

C2, C3: 1μF, 25V, X7R, 1206

C4, C5: 10μF, 50V, X7R, 1210

D1 TO D5: DIODES INC. PD3S230H-7

L1: VISHAY IHLP-2525CZ-01-8R2

R1: 2.4k, 2W

\*IF DRIVING ASYMMETRICAL LOADS,

PLACE A 2.4k, 2W RESISTOR FROM THE 12V

OUTPUT TO THE -12V OUTPUT FOR IMPROVED

LOAD REGULATION OF THE -12V OUTPUT

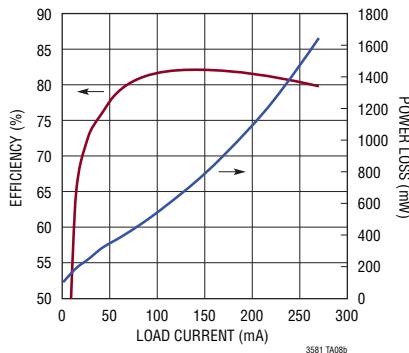

対称的負荷での効率および

電力損失

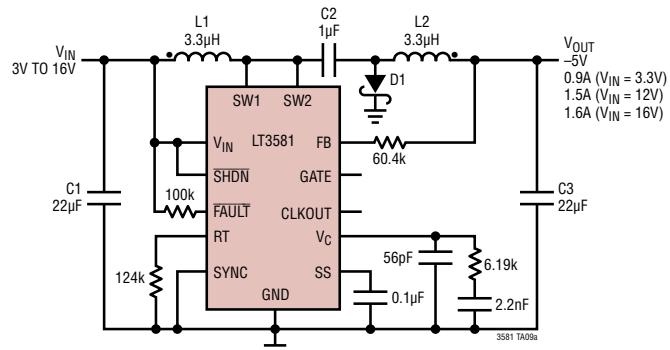

3V～16Vの入力電圧を受け入れ可能な、700kHz、-5Vの反転コンバータ

C1: 22μF, 25V, X7R, 1210

C2: 1μF, 50V, X7R, 1206

C3: 22μF, 16V, X7R, 1210

D1: VISHAY SS844

L1, L2: COILCRAFT MSD7342-332MLB

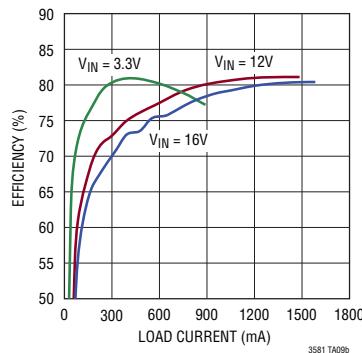

効率

3V～16Vの入力電圧を受け入れ可能な、700kHz、5VのSEPICコンバータ

C1: 22μF, 25V, X7R, 1210

C2: 1μF, 50V, X7R, 1206

C3: 22μF, 16V, X7R, 1210

D1: DIODES INC. B230LA

L1, L2: COILCRAFT MSD7342-332MLB

効率

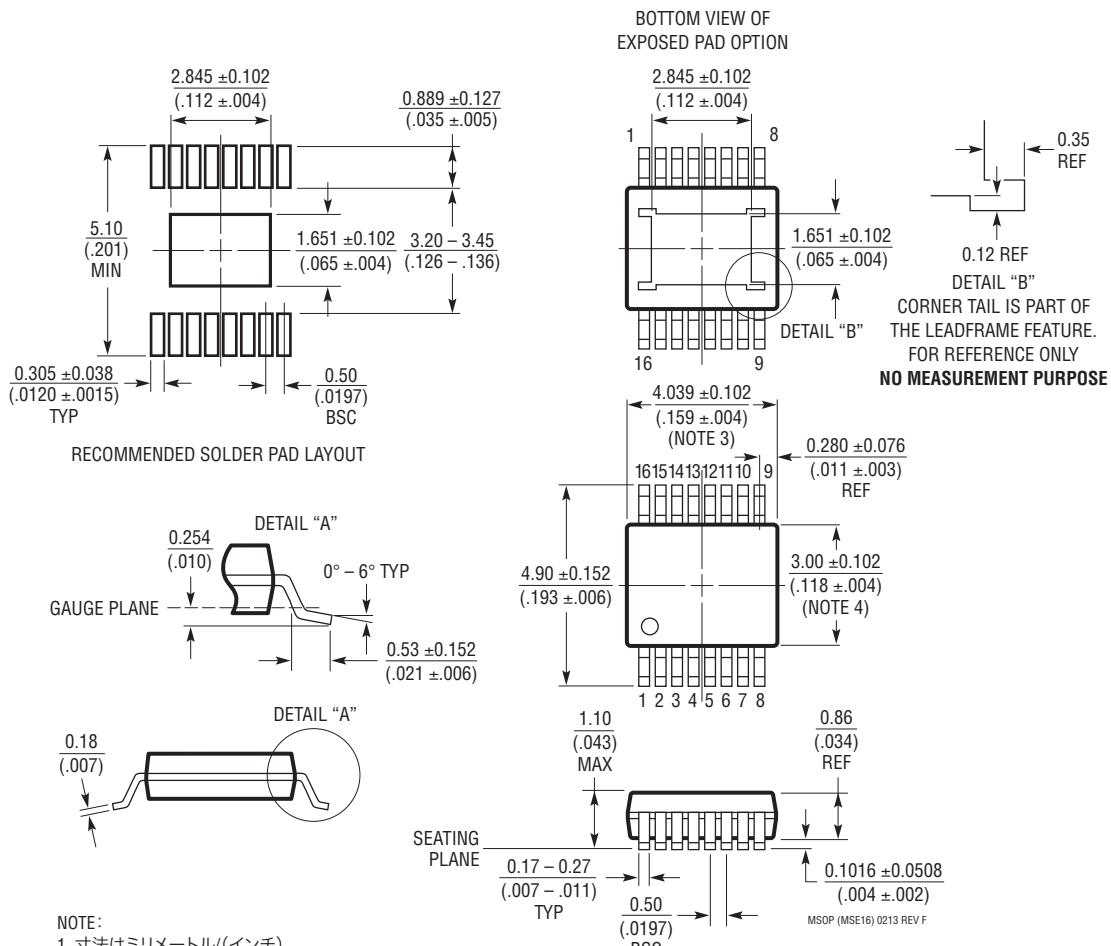

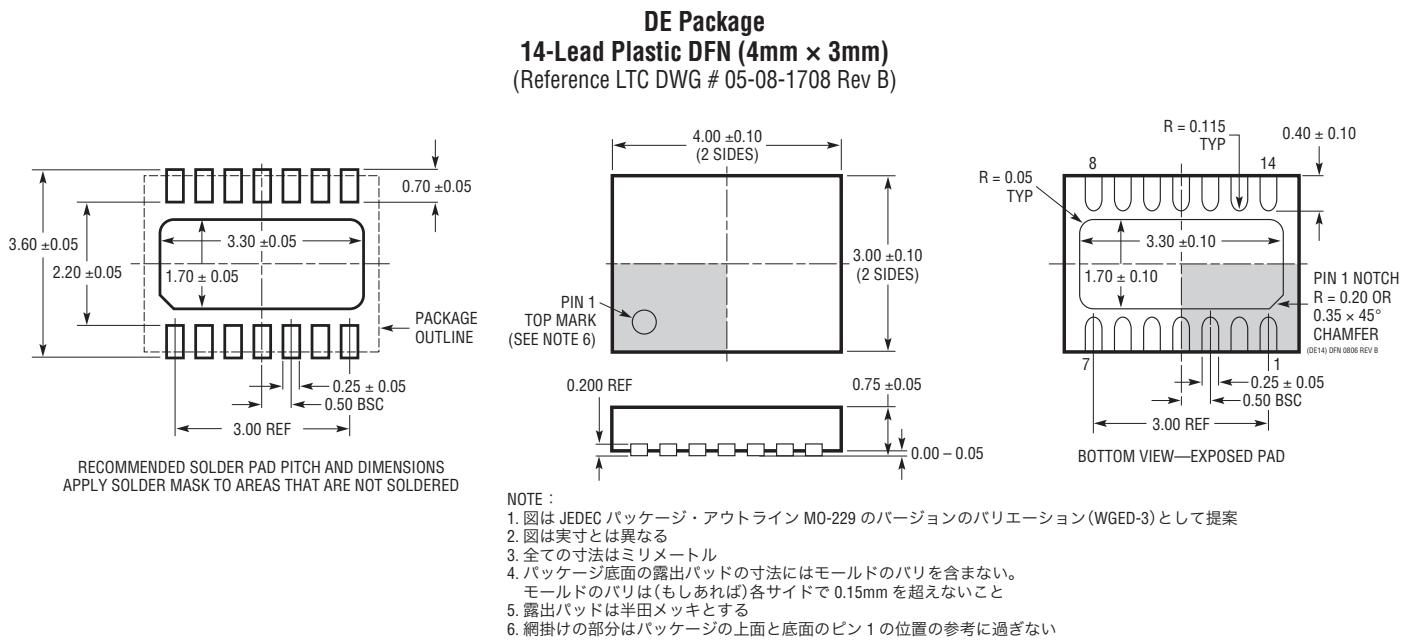

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>をご覧ください。

### MSE Package 16-Lead Plastic MSOP, Exposed Die Pad (Reference LTC DWG # 05-08-1667 Rev F)

#### NOTE:

- 寸法はミリメートル/(インチ)

- 図は実寸とは異なる

- 寸法にはモールドのバリ、突出部、またはゲートのバリを含まない。

モールドのバリ、突出部、またはゲートのバリは、各サイドで0.152mm(0.006")を超えないこと

- 寸法には、リード間のバリまたは突出部を含まない。

- リード間のバリまたは突出部は、各サイドで0.152mm(0.006")を超えないこと

- リードの平坦度(成形後のリードの底面)は最大0.102mm(0.004")であること

- 露出パッドの寸法にはモールドのバリを含まない

露出パッドのモールドのバリは各サイドで0.254mm(0.010")を超えないこと

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging>をご覧ください。

## 改訂履歴

| REV | 日付    | 概要                                                          | ページ番号  |

|-----|-------|-------------------------------------------------------------|--------|

| A   | 11/13 | 「絶対最大定格」と「発注情報」の表にHグレードを追加。<br>「電気的特性」を明確化。                 | 2<br>4 |

| B   | 7/14  | 「電気的特性」の表のFAULT Output Voltage Lowを明確化。標準値を150mVから100mVに変更。 | 4      |

## 標準的応用例

2MHzでスイッチングする5V～12Vの反転コンバータ

C1: 3.3 $\mu$ F, 16V, X7R, 1206

C2: 1 $\mu$ F, 25V, X7R, 1206

C3: 4.7 $\mu$ F, 25V, X7R, 1206

D1: DIODES INC. PD35230H-7

L1, L2: COILCRAFT MSD7342-332MLB

## 関連製品

| 製品番号           | 説明                                              | 注釈                                                                                                                 |

|----------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| LT3580         | 2A ( $I_{SW}$ )、2.5MHz、高効率昇圧DC/DCコンバータ          | $V_{IN} = 2.5V \sim 32V$ , $V_{OUT(MAX)} = 42V$ , $I_Q = 1mA$ , $I_{SD} < 1\mu A$ , 3mm × 3mm DFN-8, MSOP-8E パッケージ |

| LT3471         | デュアル出力、1.3A ( $I_{SW}$ )、1.2MHz、高効率昇圧DC/DCコンバータ | $V_{IN} = 2.4V \sim 16V$ , $V_{OUT(MAX)} = \pm 40V$ , $I_Q = 2.5mA$ , $I_{SD} < 1\mu A$ , 3mm × 3mm DFN-10 パッケージ   |

| LT3479         | ソフトスタートと突入電流保護を備えた、40V、3A、フル機能DC/DCコンバータ        | $V_{IN} = 2.5V \sim 24V$ , $V_{OUT(MAX)} = 40V$ , $I_Q = $ アナログ/PWM, $I_{SD} < 1\mu A$ , DFN, TSSOP パッケージ          |

| LT3477         | 40V、3A、フル機能DC/DCコンバータ                           | $V_{IN} = 2.5V \sim 25V$ , $V_{OUT(MAX)} = 40V$ , $I_Q = $ アナログ/PWM, $I_{SD} < 1\mu A$ , QFN, TSSOP-20E パッケージ      |

| LT1946/LT1946A | 1.5A ( $I_{SW}$ )、1.2MHz/2.7MHz、高効率昇圧DC/DCコンバータ | $V_{IN} = 2.6V \sim 16V$ , $V_{OUT(MAX)} = 34V$ , $I_Q = 3.2mA$ , $I_{SD} < 1\mu A$ , MS8E パッケージ                   |

| LT1935         | 2A ( $I_{SW}$ )、40V、1.2MHz、高効率昇圧DC/DCコンバータ      | $V_{IN} = 2.3V \sim 16V$ , $V_{OUT(MAX)} = 40V$ , $I_Q = 3mA$ , $I_{SD} < 1\mu A$ , ThinSOT パッケージ                  |

| LT1310         | 2A ( $I_{SW}$ )、40V、1.2MHz、高効率昇圧DC/DCコンバータ      | $V_{IN} = 2.3V \sim 16V$ , $V_{OUT(MAX)} = 40V$ , $I_Q = 3mA$ , $I_{SD} < 1\mu A$ , ThinSOT パッケージ                  |

| LT3436         | 3A ( $I_{SW}$ )、800kHz、34V昇圧DC/DCコンバータ          | $V_{IN} = 3V \sim 25V$ , $V_{OUT(MAX)} = 34V$ , $I_Q = 0.9mA$ , $I_{SD} < 6\mu A$ , TSSOP-16E パッケージ                |