3A/1Aまたは2A/2Aに設定可能な

デュアル同期整流式

降圧DC/DCレギュレータ

## 特長

- $V_{IN}$ 範囲: 2.25V～5.5V

- $V_{OUT}$ 範囲: 0.6V～5V

- プログラム可能な周波数動作:

2.25MHz、または0.75MHz～4MHz範囲で調整可能

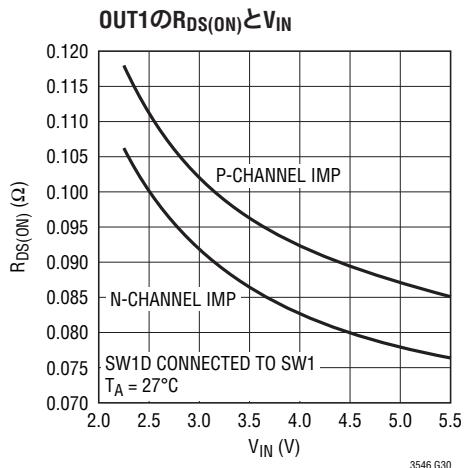

- 低 $R_{DS(ON)}$ の内部スイッチ

- 高効率: 最大96%

- ショットキーダイオード不要

- 短絡保護

- 電流モード動作による優れた入力および負荷過渡応答

- 低リップルのBurst Mode動作 (30mV<sub>P-P</sub>)、 $I_Q = 160\mu A$

- 超低シャットダウン電流:  $I_Q < 1\mu A$

- 低損失動作: 100%デューティサイクル

- 各チャネルごとのパワーグッド出力

- 外部または内部設定可能なバースト・レベル

- 外部または内部ソフトスタートまたは電源トラッキング

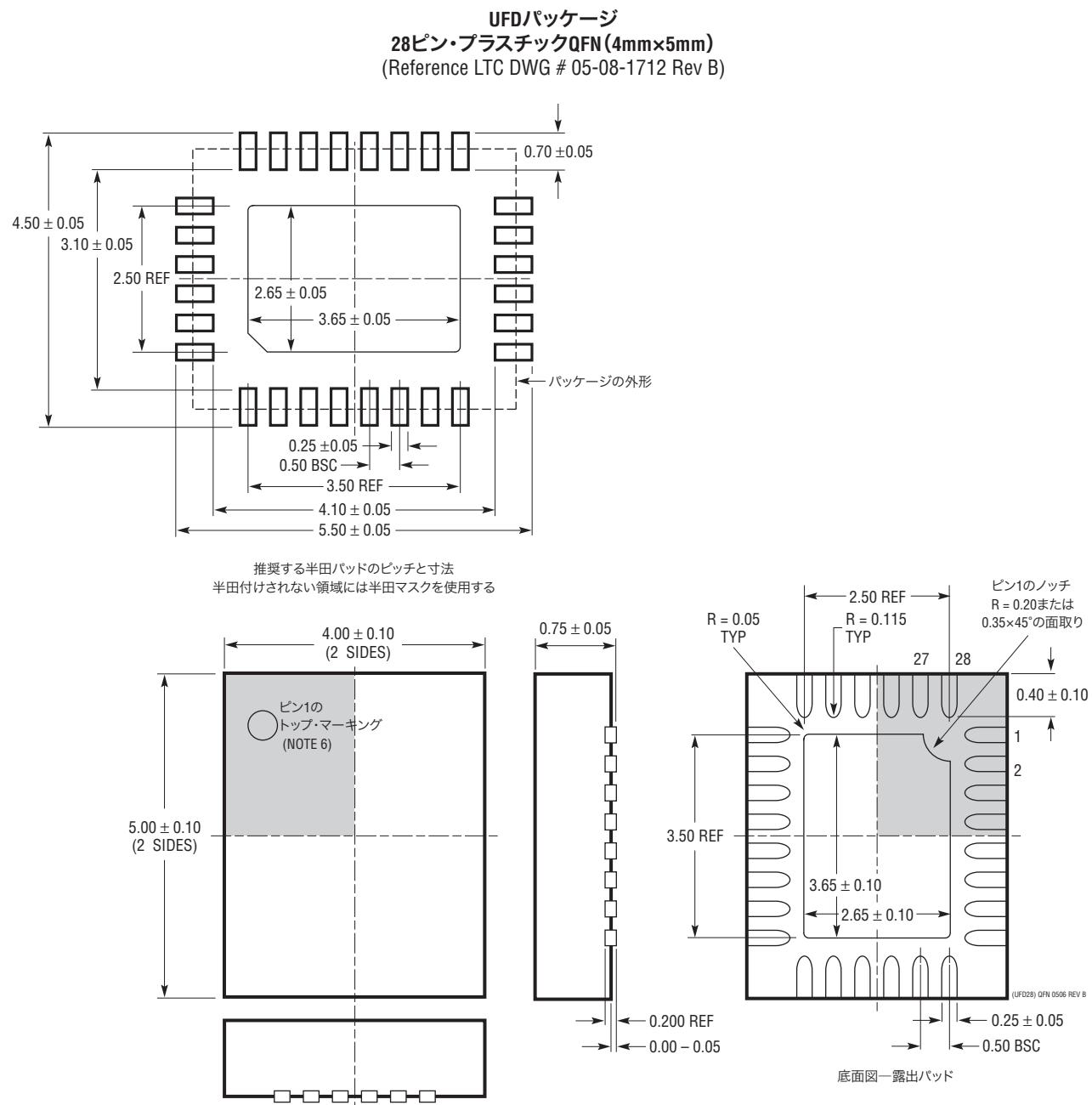

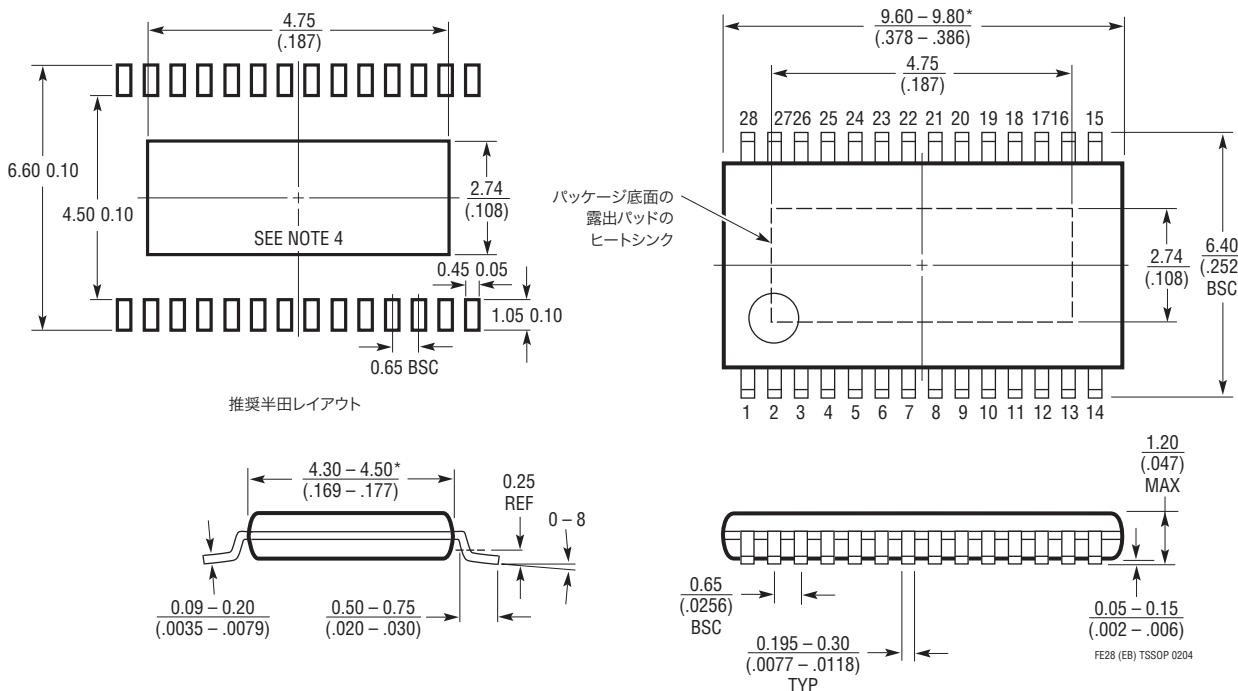

- 熱特性が改善された28ピン(4mmx5mm)QFNおよびTSSOPパッケージ

## アプリケーション

- ネットブック/ウルトラモバイルPC

- PCカード

- ワイヤレスおよびDSLモデム

- ポイントオブロードDC/DC変換

## 概要

**LTC<sup>®</sup>3546**は、中電力アプリケーション向けのデュアル固定周波数同期整流式降圧DC/DCコンバータです。このデバイスは2Aと1Aの主出力スイッチで構成されています、この2A/1Aに加えて、1Aの従属出力スイッチをいずれかの主出力に外部で接続することにより、3A/1Aデュアル・レギュレータ構成または2A/2Aデュアル・レギュレータ構成が可能です。

電源動作は2.25V～5.5Vです。スイッチング周波数は2.25MHzに設定、または0.75MHz～4MHzの範囲で調整可能で、外部クロックに同期することもできます。各出力は0.6V～5Vの範囲で調整可能で、起動時電源トラッキングを備えています。低 $R_{DS(ON)}$ の内部同期パワースイッチにより、外付けショットキーダイオードなしで高効率を達成します。

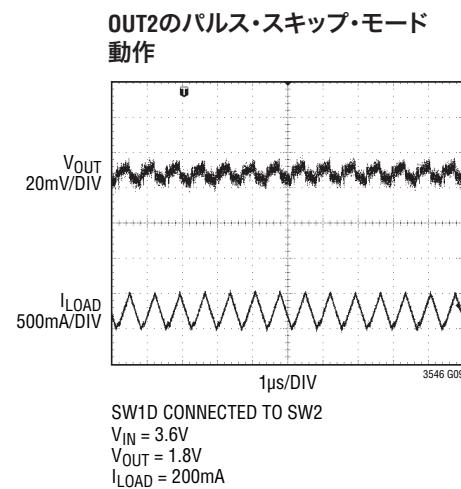

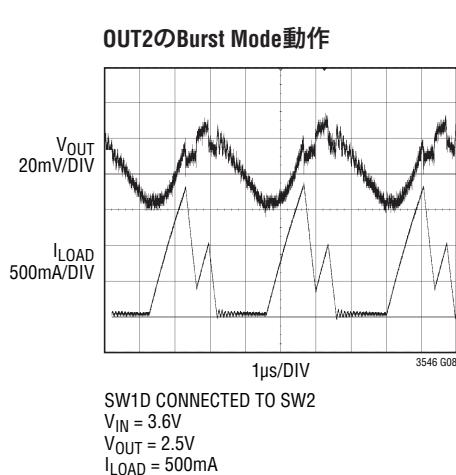

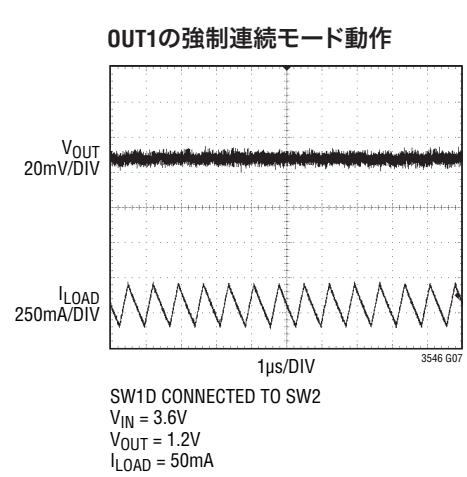

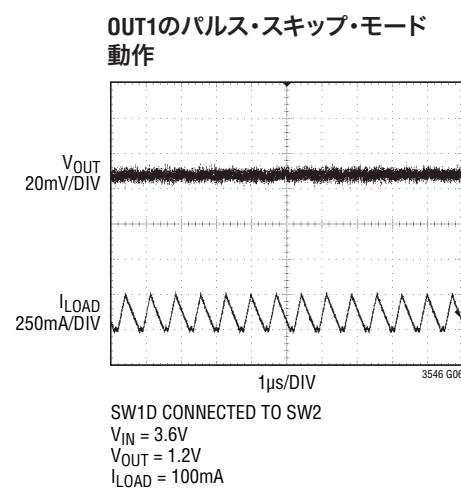

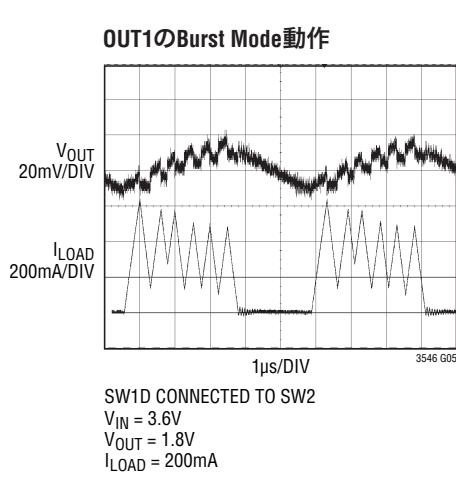

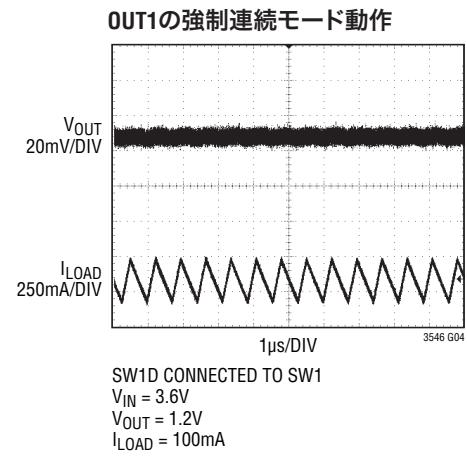

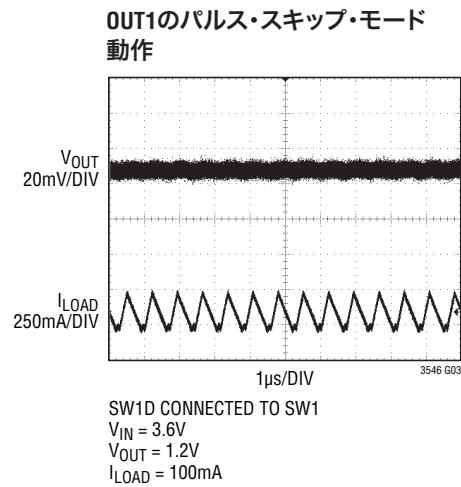

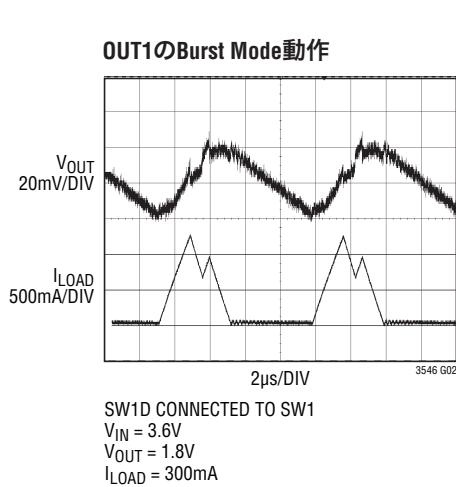

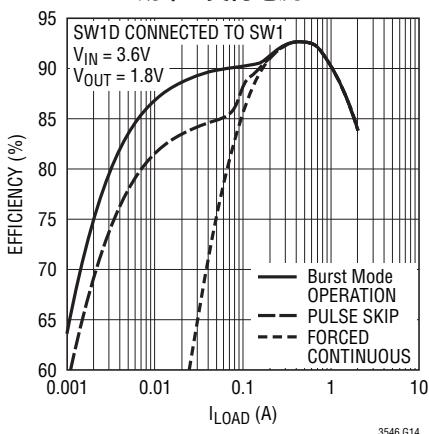

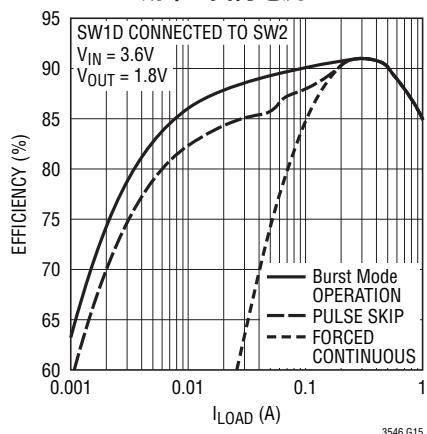

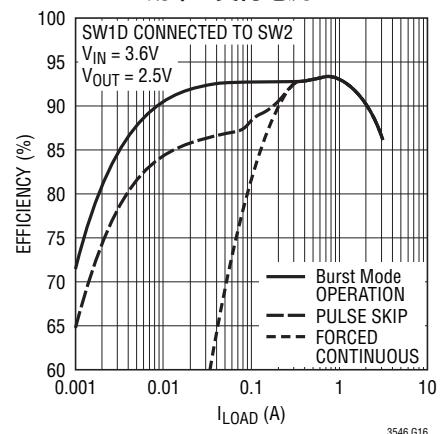

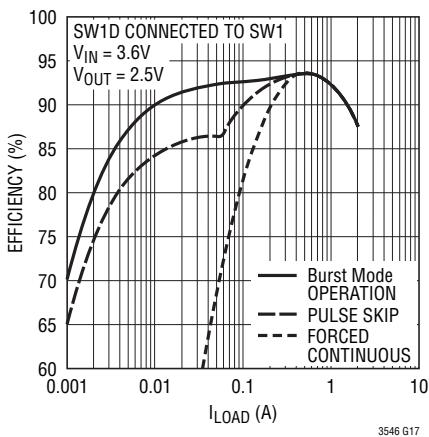

ユーザーが選択可能なモード(Burst Mode<sup>®</sup>動作、パルススキップ、強制連続)により、リップル・ノイズと電力効率のトレードオフが可能です。Burst Mode動作は軽負荷時に高効率を維持し、パルススキップ・モードでは軽負荷時にリップル・ノイズを低く抑えます。

このデバイスは低損失構成が可能で、両チャネルとも100%デューティサイクルで動作できます。また、シャットダウン時のデバイスの消費電流は1 $\mu A$ を下回ります。

**L**、LT、LTC、LTM、Linear Technology、LinearのロゴおよびBurst Modeはリニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。他の全ての商標はそれぞれの所有者に所有権があります。

5481178, 6611131, 6304066, 6498466, 6580258を含む米国特許により保護されています。

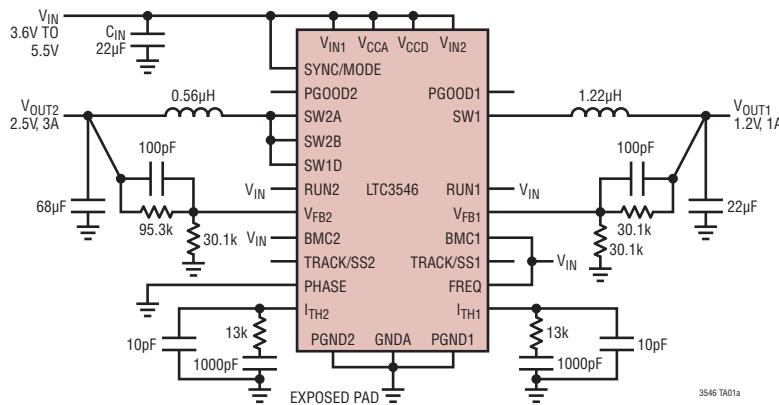

## 標準的応用例

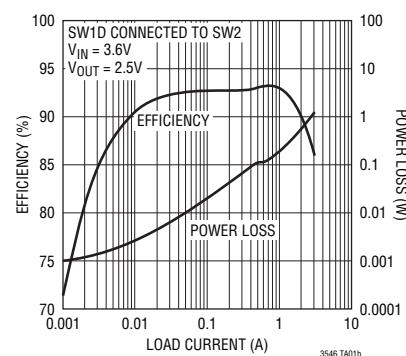

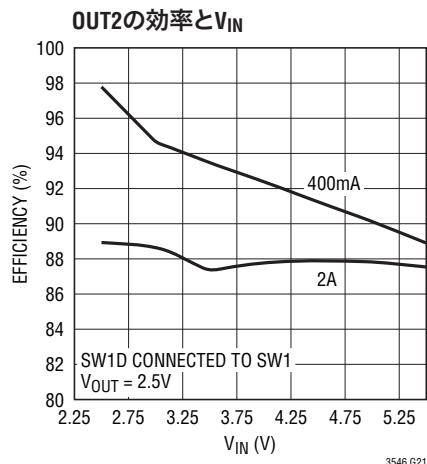

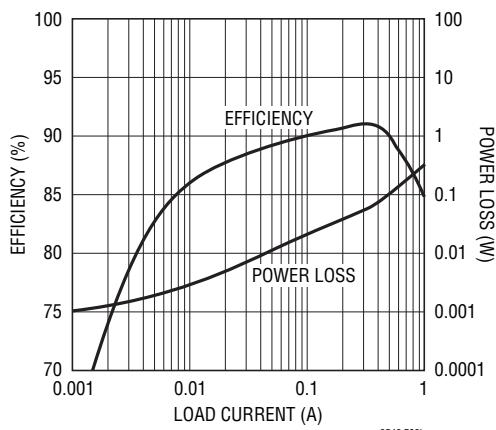

**$V_{OUT2}$ の効率 (Burst Mode動作)**

3546fc

# LTC3546

## 絶対最大定格

(Note 1)

$V_{IN1}$ 、 $V_{IN1D}$ 、 $V_{IN2}$ 、 $V_{CCA}$ 、 $V_{CCD}$ の電圧 .....  $-0.3V \sim 6V$

SYNC/MODE、SW1、SW1D、SW2A、SW2B、

RUN1、RUN2、 $V_{FB1}$ 、 $V_{FB2}$ 、PHASE、FREQ、

$I_{TH1}$ 、 $I_{TH2}$ 、TRACK/SS1、TRACK/SS2、BMC1、

BMC2の電圧 .....  $-0.3V \sim (V_{IN1} \text{または} V_{IN2}) + 0.3V$

$V_{IN1}$ 、 $V_{IN1D}$ 、 $V_{IN2}$ 、 $V_{CCA}$ 、 $V_{CCD}$ 相互の間の最大差 .....  $0.3V$

PGOOD1、PGOOD2の電圧 .....  $-0.3V \sim 6V$

動作接合部温度範囲 (Note 2, 6, 7) .....  $-40^\circ C \sim 125^\circ C$

保存温度範囲 .....  $-65^\circ C \sim 125^\circ C$

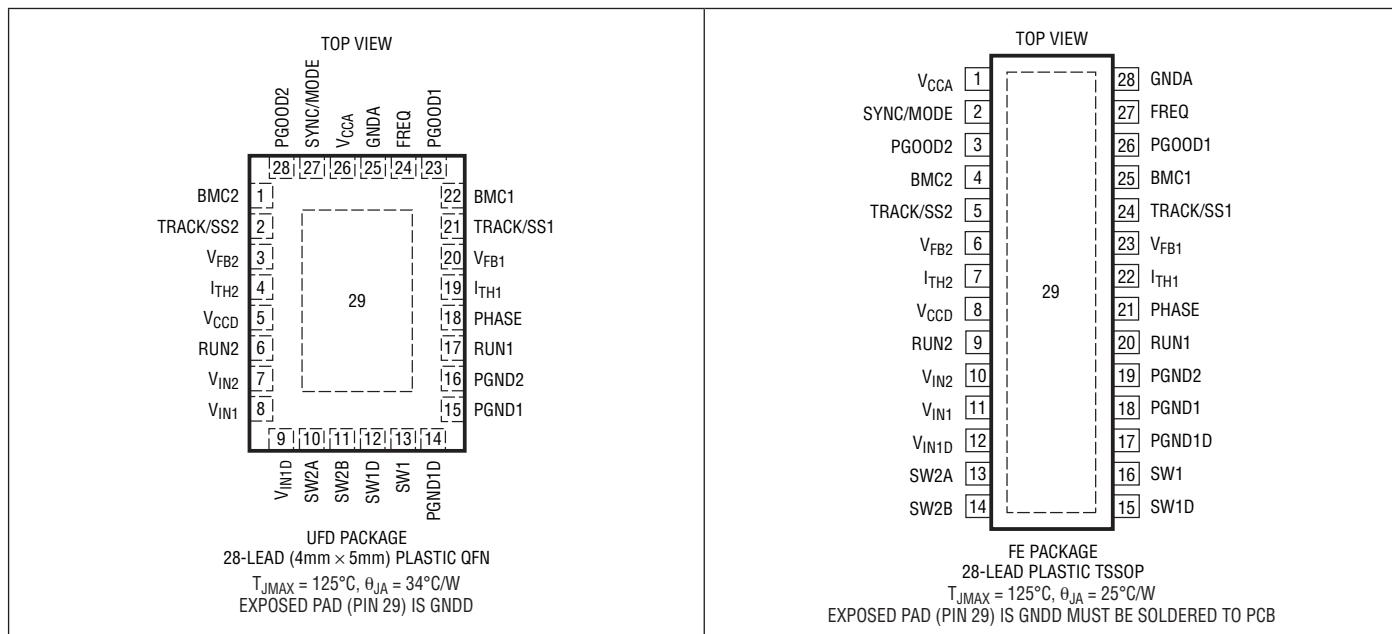

## ピン配置

## 発注情報

| 無鉛仕上げ          | テープアンドリール        | 製品マーキング*  | パッケージ                           | 温度範囲                           |

|----------------|------------------|-----------|---------------------------------|--------------------------------|

| LTC3546EUF#PBF | LTC3546EUF#TRPBF | 3546      | 28-Lead (4mm x 5mm) Plastic QFN | $-40^\circ C$ to $85^\circ C$  |

| LTC3546IUF#PBF | LTC3546IUF#TRPBF | 3546      | 28-Lead (4mm x 5mm) Plastic QFN | $-40^\circ C$ to $125^\circ C$ |

| LTC3546EFE#PBF | LTC3546EFE#TRPBF | LTC3546FE | 28-Lead Plastic TSSOP           | $-40^\circ C$ to $85^\circ C$  |

| LTC3546IFE#PBF | LTC3546IFE#TRPBF | LTC3546FE | 28-Lead Plastic TSSOP           | $-40^\circ C$ to $125^\circ C$ |

| 鉛仕上げ           | テープアンドリール        | 製品マーキング*  | パッケージ                           | 温度範囲                           |

| LTC3546EUF     | LTC3546EUF#TR    | 3546      | 28-Lead (4mm x 5mm) Plastic QFN | $-40^\circ C$ to $85^\circ C$  |

| LTC3546IUF     | LTC3546IUF#TR    | 3546      | 28-Lead (4mm x 5mm) Plastic QFN | $-40^\circ C$ to $125^\circ C$ |

| LTC3546EFE     | LTC3546EFE#TR    | LTC3546FE | 28-Lead Plastic TSSOP           | $-40^\circ C$ to $85^\circ C$  |

| LTC3546IFE     | LTC3546IFE#TR    | LTC3546FE | 28-Lead Plastic TSSOP           | $-40^\circ C$ to $125^\circ C$ |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は規定動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = V_{CCA} = 3.6\text{V}$  (Note 2)。

| SYMBOL                                         | PARAMETER                                                                                                | CONDITIONS                                                                                                     | MIN    | TYP                | MAX              | UNITS           |                      |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------|--------------------|------------------|-----------------|----------------------|

| $V_{IN1}, V_{IN1D}, V_{IN2}, V_{CCA}, V_{CCD}$ | Operating Voltage Range                                                                                  | $V_{IN1} = V_{IN1D} = V_{IN2} = V_{CCA} = V_{CCD}$                                                             | 2.25   |                    | 5.5              | V               |                      |

| $I_{FB1}, I_{FB2}$                             | Feedback Pin Input Current                                                                               | (Note 3)                                                                                                       |        |                    | $\pm 0.1$        | $\mu\text{A}$   |                      |

| $V_{FB1}, V_{FB2}$                             | Feedback Voltage                                                                                         | (Note 3)                                                                                                       | ●      | 0.588              | 0.6              | 0.612           | V                    |

| $\Delta V_{LINEREG}$                           | Reference Voltage Line Regulation<br>%/V is The Percentage Change in $V_{OUT}$ with a Change in $V_{IN}$ | $V_{IN} = 2.25\text{V}$ to $5.5\text{V}$ (Note 3)                                                              |        |                    | 0.04             | 0.2             | %/V                  |

| $\Delta V_{LOADREG}$                           | Output Voltage Load Regulation                                                                           | $I_{TH1}, I_{TH2} = 0.36\text{V}$ (Note 3)<br>$I_{TH1}, I_{TH2} = 0.84\text{V}$ (Note 3)                       | ●<br>● | 0.02<br>-0.02      | 0.2<br>-0.2      | %<br>%          |                      |

| $g_m(EA)$                                      | Error Amplifier Transconductance                                                                         | (Note 3)                                                                                                       |        |                    | 1400             | $\mu\text{S}$   |                      |

| $V_{TRACK/SS1}, V_{TRACK/SS2}$                 | Tracking Voltage Offset                                                                                  | $V_{TRACK/SS1,2} = 0.3\text{V}$                                                                                |        |                    | 15               | mV              |                      |

| $I_{TRACK/SS1}, I_{TRACK/SS2}$                 | Tracking Current Source                                                                                  | $V_{TRACK/SS1,2} = 0\text{V}$                                                                                  |        | 0.8                | 1.15             | 1.5             | $\mu\text{A}$        |

| $I_S$                                          | Input DC Supply Current (Note 4)                                                                         |                                                                                                                |        |                    |                  |                 |                      |

|                                                | Active Mode                                                                                              | $V_{FB1} = V_{FB2} = 0.55\text{V}$ , $V_{MODE} = V_{IN}$ ,<br>$V_{RUN1} = V_{RUN2} = V_{IN}$                   |        |                    | 600              | 990             | $\mu\text{A}$        |

|                                                | Half Active Mode ( $V_{RUN1} = V_{IN}$ , $V_{RUN2} = 0$ )                                                | $V_{FB1} = 0.55\text{V}$ , $V_{MODE} = V_{IN}$ , $V_{RUN1} = V_{IN}$ ,<br>$V_{RUN2} = 0\text{V}$               |        |                    | 400              | 800             | $\mu\text{A}$        |

|                                                | Half Active Mode ( $V_{RUN1} = 0$ , $V_{RUN2} = V_{IN}$ )                                                | $V_{FB2} = 0.55\text{V}$ , $V_{MODE} = V_{IN}$ , $V_{RUN1} = 0\text{V}$ ,<br>$V_{RUN2} = V_{IN}$               |        |                    | 400              | 800             | $\mu\text{A}$        |

|                                                | Both Channels in Sleep Mode                                                                              | $V_{FB1} = V_{FB2} = 0.75\text{V}$ , $V_{MODE} = V_{IN}$ ,<br>$V_{RUN1} = V_{RUN2} = V_{IN}$                   |        |                    | 160              | 300             | $\mu\text{A}$        |

|                                                | Shutdown                                                                                                 | $V_{RUN1} = V_{RUN2} = 0\text{V}$                                                                              |        |                    | 0.2              | 1               | $\mu\text{A}$        |

| $f_{osc}$                                      | Oscillator Frequency                                                                                     | $V_{FREQ}: R_T = V_{IN}$<br>$V_{FREQ}: R_T = 143\text{k}$<br>$V_{FREQ}: \text{Resistor}$ (Note 5)              | ●      | 1.8<br>1.2<br>0.75 | 2.25<br>1.5<br>4 | 2.9<br>1.8<br>4 | MHz<br>MHz<br>MHz    |

| $I_{LIM1}$                                     | Peak Switch Current Limit on SW1 (1A)                                                                    | $\text{BMC1} = V_{IN}, V_{ITH1} = 1.4\text{V}$<br>$\text{BMC1} = 0.4\text{V}, V_{ITH1} = 0\text{V}$            |        | 1.4                | 1.6<br>0.45      |                 | A<br>A               |

| $I_{LIM2}$                                     | Peak Switch Current Limit on SW2A/B (2A)                                                                 | $\text{BMC2} = V_{IN}, V_{ITH1} = 1.4\text{V}$<br>$\text{BMC2} = 0.4\text{V}, V_{ITH1} = 0\text{V}$            |        | 2.8                | 3.2<br>0.9       |                 | A<br>A               |

| $I_{LIM1+1D}$                                  | Peak Switch Current Limit on SW1 + SW1D (2A)                                                             | SW1 Externally Connected to SW1D<br>$\text{BMC1} = V_{IN}$ (Note 8)<br>$\text{BMC1} = 0.4\text{V}$ (Note 8)    |        | 2.5                | 3.2<br>1.6       |                 | A<br>A               |

| $I_{LIM2+1D}$                                  | Peak Switch Current Limit on SW2A/B + SW1D (3A)                                                          | SW2A/B Externally Connected to SW1D<br>$\text{BMC2} = V_{IN}$ (Note 8)<br>$\text{BMC2} = 0.4\text{V}$ (Note 8) |        | 3.75               | 4.8<br>2.4       |                 | A<br>A               |

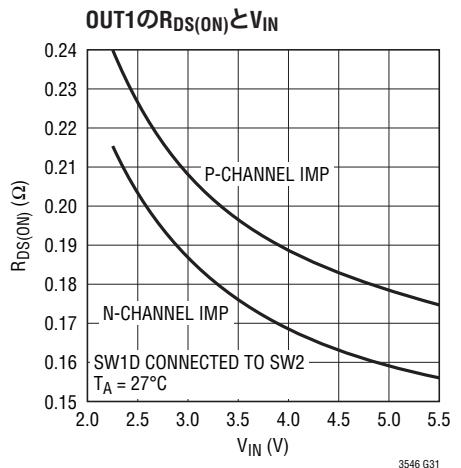

| $R_{DS(ON)1}$                                  | SW1 Top Switch On-Resistance (1A)<br>SW1 Bottom Switch On-Resistance                                     | $V_{IN2} = 3.6\text{V}$<br>$V_{IN2} = 3.6\text{V}$                                                             |        |                    | 0.19<br>0.18     |                 | $\Omega$<br>$\Omega$ |

| $R_{DS(ON)1D}$                                 | SW1D Top Switch On-Resistance (1A)<br>SW1D Bottom Switch On-Resistance                                   | $V_{IN2} = 3.6\text{V}$<br>$V_{IN2} = 3.6\text{V}$                                                             |        |                    | 0.19<br>0.17     |                 | $\Omega$<br>$\Omega$ |

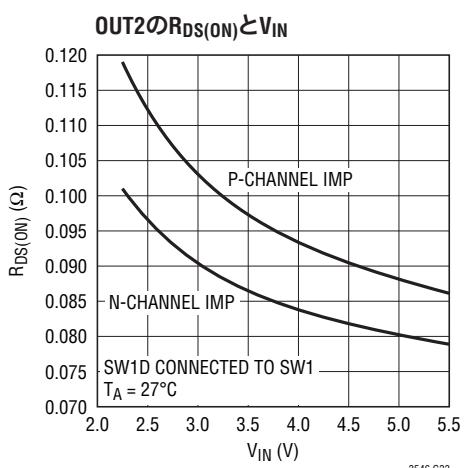

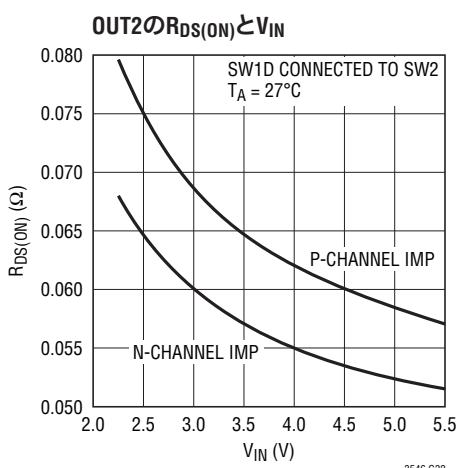

| $R_{DS(ON)2}$                                  | SW2A/B Top Switch On-Resistance (2A)<br>SW2A/B Bottom Switch On-Resistance                               | $V_{IN1} = 3.6\text{V}$<br>$V_{IN1} = 3.6\text{V}$                                                             |        |                    | 0.096<br>0.085   |                 | $\Omega$<br>$\Omega$ |

| $I_{SW1(LKG)}$                                 | Switch Leakage Current SW1                                                                               | $V_{IN} = 6\text{V}$<br>$V_{ITH1} = 0\text{V}$<br>$V_{RUN1} = 0\text{V}$                                       |        |                    | 0.01             | 1               | $\mu\text{A}$        |

## 電気的特性

●は規定動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = V_{CCA} = 3.6\text{V}$  (Note 2)。

| SYMBOL                          | PARAMETER                                                                                | CONDITIONS                                                                                     | MIN          | TYP          | MAX             | UNITS                    |

|---------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------|--------------|-----------------|--------------------------|

| $I_{SW1D(LKG)}$                 | Switch Leakage Current SW1D                                                              | $V_{IN} = 6\text{V}$<br>$V_{ITH1} = V_{ITH2} = 0\text{V}$<br>$V_{RUN1} = V_{RUN2} = 0\text{V}$ |              | 0.01         | 1               | $\mu\text{A}$            |

| $I_{SW2A/B(LKG)}$               | Switch Leakage Current SW2A/B                                                            | $V_{IN} = 6\text{V}$<br>$V_{ITH2} = 0\text{V}$<br>$V_{RUN2} = 0\text{V}$                       |              | 0.01         | 1               | $\mu\text{A}$            |

| $V_{UVLO}$                      | Undervoltage Lockout Threshold                                                           | $V_{IN1}, V_{IN2}, V_{CCA}, V_{CCD}$ Rising<br>$V_{IN1}, V_{IN2}, V_{CCA}, V_{CCD}$ Falling    | 2.03<br>1.86 | 2.14<br>1.97 | 2.2<br>2.03     | $\text{V}$<br>$\text{V}$ |

| $T_{PGOOD1}$                    | Threshold for Power Good Percentage Deviation from Regulated $V_{FB1}$ (Typically 0.6V). | $V_{FB1}$ Ramping Up, $V_{SYNC/MODE} = 0\text{V}$                                              |              | -8           |                 | %                        |

| $T_{PGOOD2}$                    | Threshold for Power Good Percentage Deviation from Regulated $V_{FB2}$ (Typically 0.6V). | $V_{FB2}$ Ramping Up, $V_{SYNC/MODE} = 0\text{V}$                                              |              | -8           |                 | %                        |

| $R_{PGOOD1}$                    | Power Good Pull-Down On-Resistance                                                       |                                                                                                |              | 132          | 300             | $\Omega$                 |

| $R_{PGOOD2}$                    | Power Good Pull-Down On-Resistance                                                       |                                                                                                |              | 132          | 300             | $\Omega$                 |

| $t_{SS}$                        | Soft-Start Internal Time.                                                                | $V_{FB}$ from 0% to 95%, $V_{TRACK/SS}$ Is Floating                                            | 0.8          | 1.2          | 1.9             | ms                       |

| $V_{RUN1}, V_{RUN2}, V_{PHASE}$ | RUN1, RUN2, and PHASE Threshold                                                          |                                                                                                | 0.3          | 0.8          | 1.2             | $\text{V}$               |

| $I_{RUN1}, I_{RUN2}, I_{PHASE}$ | RUN1, RUN2, and PHASE Leakage Current                                                    | $V_{IN} = 6\text{V}, V_{PHASE} = 3\text{V}, V_{RUN1} = V_{RUN2} = 3\text{V}$                   |              | $\pm 0.01$   | $\pm 1$         | $\mu\text{A}$            |

| $V_{TLYNCSYNC/MODE}$            | SYNC/MODE Threshold Voltage Low to Put the Part into Pulse-Skipping Mode                 |                                                                                                |              |              | 0.5             | $\text{V}$               |

| $V_{THSYNC/MODE}$               | SYNC/MODE Threshold Voltage High to Put the Part into Burst Mode Operation               |                                                                                                |              |              | $V_{IN} - 0.5$  | $\text{V}$               |

| $V_{SYNC/MODE}$                 | SYNC/MODE Threshold for Clock Synchronization                                            |                                                                                                | 0.3          | 0.8          | 1.2             | $\text{V}$               |

| $I_{SYNC/MODE}$                 | SYNC/MODE Leakage Current                                                                | $V_{IN} = 6\text{V}, V_{SYNC/MODE} = 3\text{V}$                                                |              | $\pm 0.01$   | $\pm 1$         | $\mu\text{A}$            |

| $V_{THFREQ}$                    | FREQ Threshold Voltage High                                                              |                                                                                                |              |              | $V_{IN} - 0.85$ | $\text{V}$               |

| $I_{BMC1}, I_{BMC2}$            | BMC1, BMC2 Leakage Current                                                               | $V_{IN} = 6\text{V}, V_{BMC} = 3\text{V}$                                                      |              |              | $\pm 0.4$       | $\mu\text{A}$            |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**LTC3546は $T_J$ が $T_A$ にほぼ等しいバ尔斯負荷条件でテストされている。LTC3546は $0^\circ\text{C} \sim 85^\circ\text{C}$ の接合部温度範囲で性能仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTC3546は $-40^\circ\text{C} \sim 125^\circ\text{C}$ の全動作接合部温度範囲で動作することが保証されている。これらの仕様と調和する最大周囲温度は、基板レイアウト、パッケージの定格熱インピーダンスなどの環境要因と関連した特定の動作条件によって決まるに注意。

**Note 3:**LTC3546は $V_{FB1}$ を誤差アンプの中点 ( $V_{ITH1} = 0.6\text{V}$ ) にサーボ制御し、 $V_{FB2}$ を誤差アンプの中点 ( $V_{ITH2} = 0.6\text{V}$ ) にサーボ制御する帰還ループでテストされる。

**Note 4:**スイッチング周波数で供給される内部ゲート電荷により合計消費電流が増加する。

**Note 5:**抵抗を使った可変周波数動作は設計によって保証されており、デューティサイクルのリミットによって制約を受ける。

**Note 6:**このデバイスには短時間の過負荷状態の間デバイスを保護するための過温度保護機能が備わっている。過温度保護機能がアクティブなとき接合部温度は $125^\circ\text{C}$ を超える。規定された最大動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なうおそれがある。

**Note 7:** $T_J$ は周囲温度 ( $T_A$ ) および電力損失 ( $P_D$ ) から次式に従って計算される。

$$T_J = T_A + (P_D \cdot 34^\circ\text{C/W})$$

**Note 8:**最小電流リミットは設計と、 $R_{DS(ON)1D}$ 、 $I_{LIM1}$ および $I_{LIM2}$ の測定との相関によって保証されている。

## 標準的性能特性

## 標準的性能特性

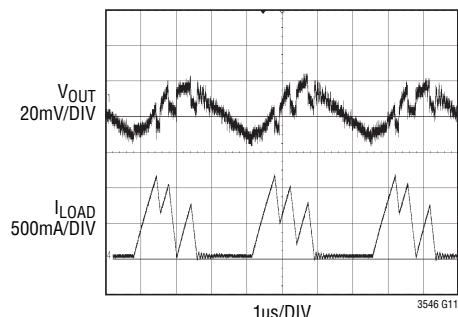

OUT2のBurst Mode動作

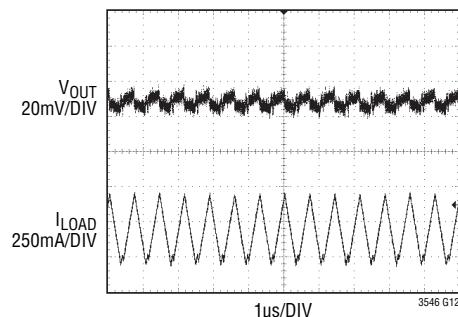

OUT2のパルス・スキップ・モード動作

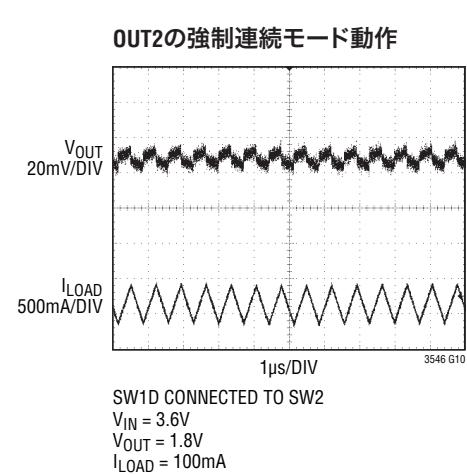

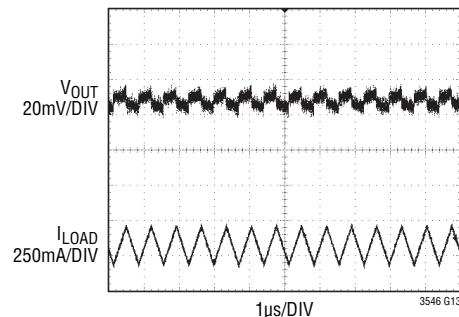

OUT2の強制連続モード動作

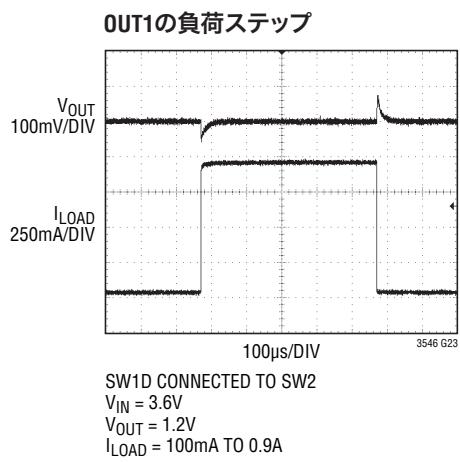

OUT1の効率と負荷電流

OUT1の効率と負荷電流

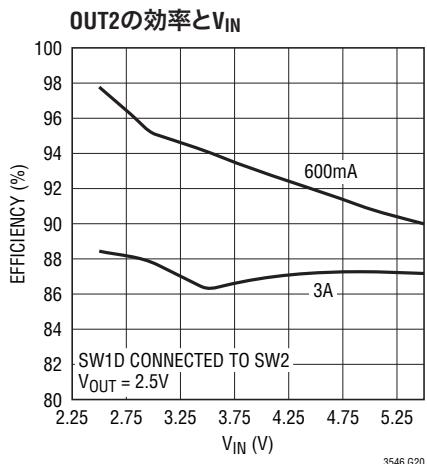

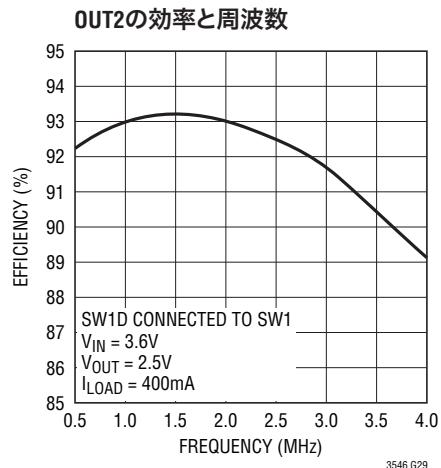

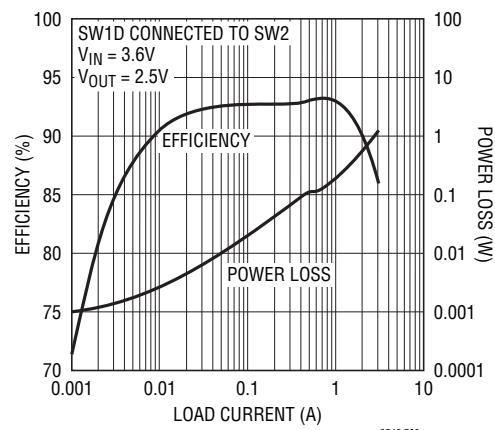

OUT2の効率と負荷電流

OUT2の効率と負荷電流

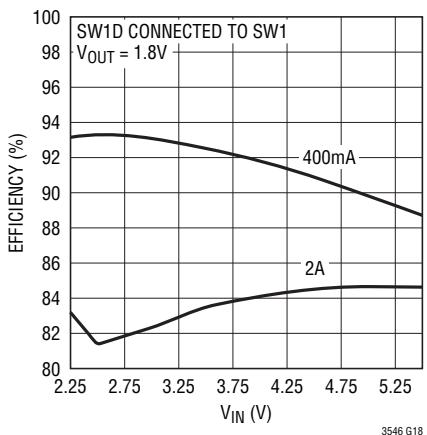

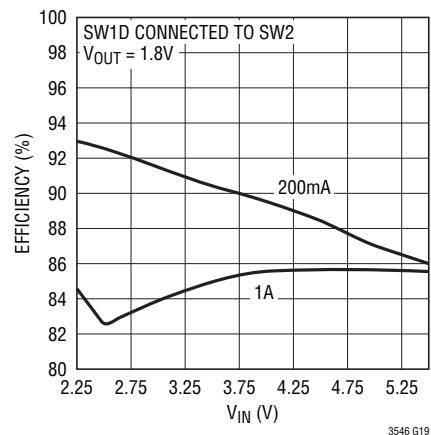

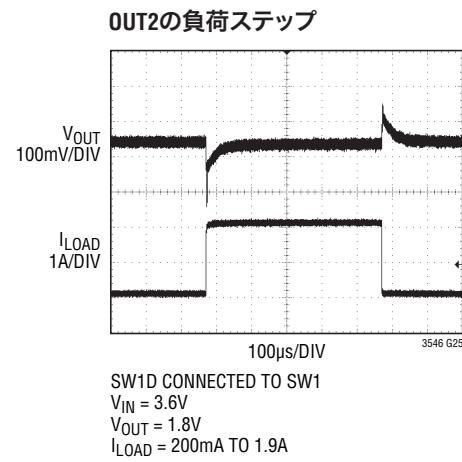

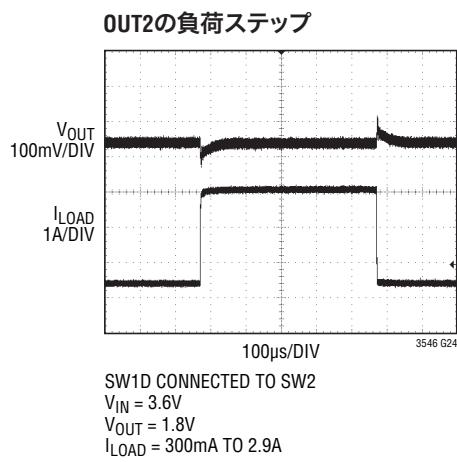

OUT1の効率とVIN

OUT1の効率とVIN

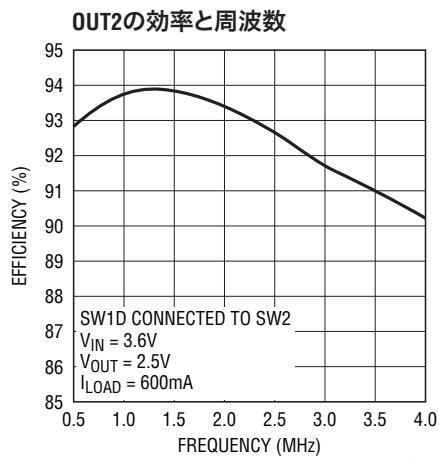

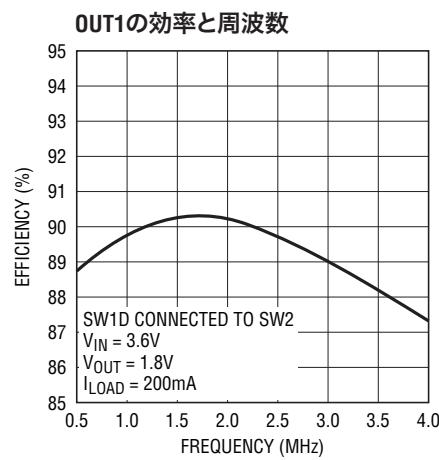

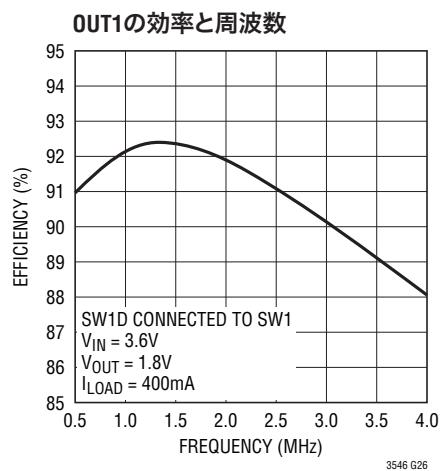

## 標準的性能特性

## 標準的性能特性

## ピン機能 (UFD/FE)

**BMC2(ピン1/ピン4)**: チャネル2のBurst Modeクランプ。このピンを0V～0.6Vの外部電圧に接続するとBurst Modeクランプ・レベルが設定されます。このピンをV<sub>CCA</sub>に引き上げると、内部Burst Modeクランプ・レベルが使われます。Burst Mode動作を選択しない時は、このピンをグランドに接続します。

**TRACK/SS2(ピン2/ピン5)**: チャネル2の出力のトラッキング入力またはオプションの外部ソフトスタート入力。V<sub>OUT2</sub>はこのピンの外部電圧をトラッキングします。このピンをフロートさせておくと、V<sub>OUT2</sub>は内部ソフトスタートを使って起動することができます。このピンとグランドの間にコンデンサを接続して、外部ソフトスタートをプログラムすることができます。外部ソフトスタートのランプ時間は、1.2msの内部ソフトスタート時間よりも長くする必要があります。詳細については「アプリケーション情報」のセクションを参照してください。

**V<sub>FB2</sub>(ピン3/ピン6)**: チャネル2のレギュレータ出力に接続された外部抵抗分割器からの帰還電圧。このピンの公称電圧は0.6Vです。

**I<sub>TH2</sub>(ピン4/ピン7)**: チャネル2のレギュレータの誤差アンプの補償。このピンの電圧増加に伴ってピーク電流が増加します。このピンの公称電圧範囲は0V～1.5Vです。

**V<sub>CCD</sub>(ピン5/ピン8)**: 内部デジタル回路の電源ピン。

**RUN2(ピン6/ピン9)**: 低レベルのロジック入力。チャネル2のイネーブル。“H”に引き上げられると、レギュレータが動作します。0Vのとき、レギュレータはオフします。RUN1とRUN2が両方0Vのとき、デバイスはシャットダウンします。

**V<sub>IN2</sub>(ピン7/ピン10)**: V<sub>IN2</sub>からSW2A/Bに接続された、2AのPチャネル・スイッチの電源ピン。

**V<sub>IN1</sub>(ピン8/ピン11)**: V<sub>IN1</sub>からSW1に接続された、1AのPチャネル・スイッチの電源ピン。

**V<sub>IN1D</sub>(ピン9/ピン12)**: V<sub>IN1D</sub>からSW1Dに接続された、1Aの従属Pチャネル・スイッチの電源ピン。

**SW2A(ピン10/ピン13)**: チャネル2のインダクタへのスイッチ・ノード接続の半分。SW2AとSW2Bは外部で一緒に接続する必要があります。このピンはV<sub>IN2</sub>からPGND2まで振幅します。

**SW2B(ピン11/ピン14)**: チャネル2のインダクタへのスイッチ・ノード接続の半分。SW2AとSW2Bは外部で一緒に接続する必要があります。このピンはV<sub>IN2</sub>からPGND2まで振幅します。

**SW1D(ピン12/ピン15)**: 従属スイッチ・ノードの接続。このピンは、2A/2Aレギュレータでは外部でSW1に接続され、3A/1AレギュレータではSW2A/Bに接続されます。SW1Dが外部でどちらのピン(SW1またはSW2A/B)に接続されているかを内部回路が検知します。このピンはV<sub>IN1D</sub>からPGND1Dまで振幅します。SW1Dのスイッチングは、それが接続されている出力スイッチ(つまり、SW1またはSW2A/SW2B)によって制御されます。従属1A電力段はSW1Dピンをフロートさせてディスエーブルすることができます。SW1DピンはV<sub>IN</sub>またはGNDに決して接続しないでください。ディスエーブルされると、SW1Dは内部で“H”に引き上げられます。

**SW1(ピン13/ピン16)**: チャネル1のレギュレータのインダクタへのスイッチ・ノードの接続。このピンはV<sub>IN1</sub>からPGND1まで振幅します。

**PGND1D(ピン14/ピン17)**: SW1Dのスイッチング用Nチャネル・ドライバのグランド。

**PGND1(ピン15/ピン18)**: SW1のスイッチング用Nチャネル・ドライバのグランド。

**PGND2(ピン16/ピン19)**: SW2AとSW2Bのスイッチング用Nチャネル・ドライバのグランド。

**RUN1(ピン17/ピン20)**: 低レベルのロジック入力。チャネル1のイネーブル。“H”に引き上げられると、レギュレータが動作します。0Vのとき、レギュレータはオフします。RUN1とRUN2が両方0Vのとき、デバイスはシャットダウンします。

**PHASE(ピン18/ピン21)**: 低レベルのロジック入力。チャネル1のレギュレータのスイッチングを基準にしたチャネル2のレギュレータのスイッチングの位相を選択します。“H”に引き上げられると、SW1レギュレータとSW2A/Bレギュレータは同相になります。PHASEが0Vのとき、SW1レギュレータとSW2A/Bレギュレータは180°位相がずれてスイッチングします。

**I<sub>TH1</sub>(ピン19/ピン22)**: チャネル1の誤差アンプの補償。このピンの電圧増加に伴ってピーク電流が増加します。このピンの公称電圧範囲は0V～1.5Vです。

## ピン機能 (UFD/FE)

**V<sub>FB1</sub>(ピン20/ピン23)**: チャネル1の出力に接続された外部抵抗分割器からの帰還電圧。このピンの公称電圧は0.6Vです。

**TRACK/SS1(ピン21/ピン24)**: チャネル1の出力のトラッキング入力またはオプションの外部ソフトスタート入力。V<sub>OUT1</sub>はこのピンの外部電圧をトラッキングします。このピンをフロートさせておくと、V<sub>OUT1</sub>は内部ソフトスタートを使って起動することができます。このピンとグランドの間にコンデンサを接続して、外部ソフトスタートをプログラムすることができます。外部ソフトスタートのランプ時間は、1.2msの内部ソフトスタート時間より長くする必要があります。詳細については「アプリケーション情報」のセクションを参照してください。

**BMC1(ピン22/ピン25)**: チャネル1のBurst Modeクランプ。このピンを0V～0.6Vの外部電圧に接続するとBurst Modeクランプ・レベルが設定されます。このピンをV<sub>CCA</sub>に引き上げると、内部Burst Modeクランプ・レベルが使われます。Burst Mode動作を選択しない時は、このピンをグランドに接続します。

**PGOOD1(ピン23/ピン26)**: 1Aレギュレータのパワーグッド・ピン。このコモン・ドレインのロジック出力は、チャネル1の出力電圧がレギュレーション電圧の8%下より低くなるとGNDに引き下げられます。

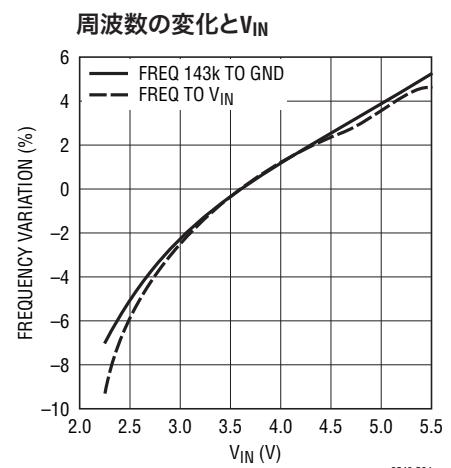

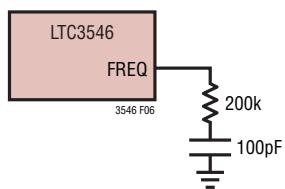

**FREQ(ピン24/ピン27)**: 周波数設定ピン。FREQがV<sub>CCA</sub>のとき、内部発振器は2.25MHzで発振します。このピンからGNDAに抵抗を接続して、内部発振器の周波数を0.75MHz～4MHzの範囲で変化させることができます。外部同期を使うとき、このピン

は内部PLLを補償します。標準的な補償部品は100pFコンデンサとそれに直列な200k抵抗です。

**GNDA(ピン25/ピン28)**: 内部アナログ回路のグランド・ピン。

**V<sub>CCA</sub>(ピン26/ピン1)**: 内部アナログ回路の電源ピン。

**SYNC/MODE(ピン27/ピン2)**: 組合せモードの選択と発振器の同期のためのピン。このピンはデバイスの動作を制御します。SYNC/MODEピンの電圧が $>(V_{IN}-0.5V)$ のとき、両方のレギュレータにBurst Mode動作が選択されます。SYNC/MODEピンの電圧が $<0.5V$ のとき、両方のレギュレータにパルス・スキップ・モードが選択されます。SYNC/MODEピンが $V_{IN}/2$ に保たれると、両方のレギュレータに強制連続モードが選択されます。発振周波数はこのピンに接続された外部発振器に同期させることができます。外部クロックに同期しているときはパルス・スキップ・モードが選択されます。

**PGOOD2(ピン28/ピン3)**: チャネル2のパワーグッド・ピン。このコモン・ドレインのロジック出力は、チャネル2の出力電圧がレギュレーション電圧の8%下より低くなるとGNDに引き下げられます。

**GNDD(露出パッド・ピン29/露出パッド・ピン29)**: デジタル・グランド。サブストレートと内部デジタル回路の電気的グランドに接続します。定格熱性能を与えるため、PCBに半田付けします。

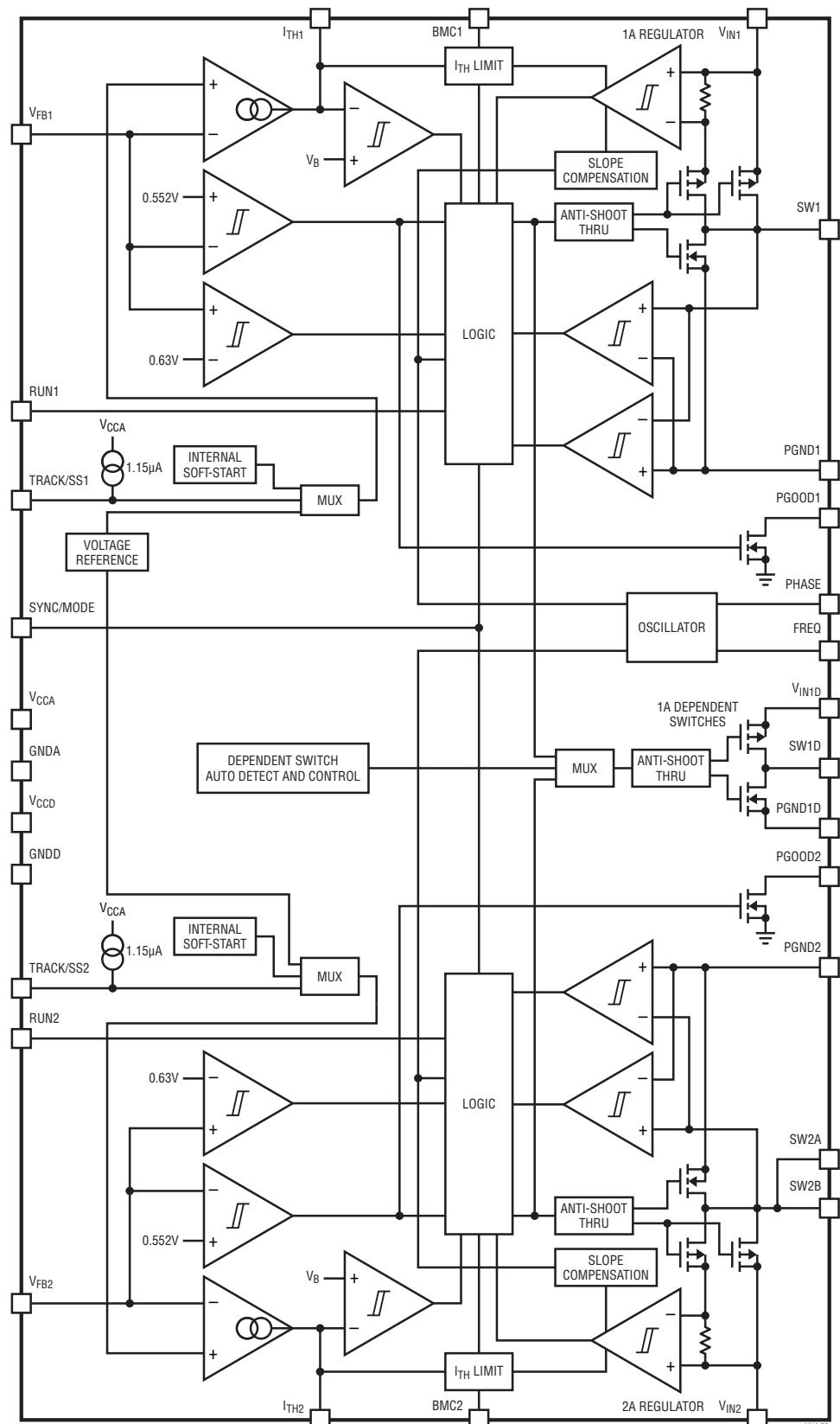

## 機能図

## 動作

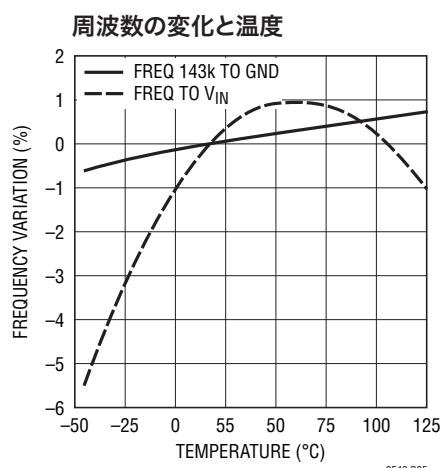

LTC3546には固定周波数、電流モード・アーキテクチャが採用されています。両方のチャネルが同じクロック周波数を共有します。PHASEピンは、チャネルを同相で動作させるか、それとも180°位相をずらして動作させるかを設定します。動作周波数は、2.25MHz動作の場合はFREQピンをVINに接続して設定し、0.75MHz～4MHzの周波数の場合は抵抗をFREQからGNDAに接続して設定します。143kの抵抗をGNDAに接続すると周波数は1.5MHzに設定されます。SYNC/MODEピンを使ってデバイスを外部クロックに同期させることもできます。多様なアプリケーションに適合させるため、ユーザーは選択可能なSYNC/MODEピンを使ってノイズと効率のトレードオフを図ることができます。

出力電圧はVFB1ピンとVFB2ピンに戻される外部分圧器によって設定されます。誤差アンプが分圧された出力電圧を0.6Vのリファレンス電圧と比較し、それに従って内部ピーク・インダクタ電流の設定を調節します。Burst Mode動作時のピーク・インダクタ電流は、BMC1ピンとBMC2ピンを使って外部から設定することもできます。低電圧コンパレータは、PGOOD1出力またはPGOOD2出力のそれぞれに対応する出力が設定された出力電圧の8%下より低くなると、PGOOD1出力またはPGOOD2出力を“L”に引き下げます。

TRACK/SSピンは、外部または内部で発生した電圧ランプを介してスタートアップを制御することができます。外部から加えられた電圧をトラッキングすることもできます。

1Aの従属スイッチ(SW1D)は、SW1出力またはSW2A/SW2B出力に外部で接続することができます。内部回路はSW1Dがどちらの出力に接続されているかを自動検知し、それに従ってそれらを制御します。このように柔軟性があるので、LTC3546は、(SW1DがSW1に接続されているとき)2A/2Aデュアル・レギュレータとして、または(SW1がSW2A/SW2Bに接続されているとき)3A/1Aデュアル・レギュレータとして構成設定することができます。

### メイン制御ループ

各レギュレータで、通常動作時、VFB電圧が0.6Vのリファレンス電圧より低いと、PチャネルMOSFETのパワースイッチがクロック・サイクルの始点でオンします。電流リミットに達するまで、インダクタと負荷に流れる電流が増加します。スイッチがオフし、インダクタに蓄えられたエネルギーがボトムNチャネルMOSFETスイッチを通って次のクロック・サイクルまで負荷に流れます。

ピーク・インダクタ電流はITHピンの電圧によって制御されます。この電圧は帯域幅2.5MHzの誤差アンプの出力です。この誤差アンプはVFBピンを0.6Vのリファレンスと比較します。負荷電流が増加すると、VFB電圧が減少し、リファレンスよりもわずか下に下がります。この減少により、誤差アンプは平均インダクタ電流が新しい負荷電流に合致するまでITHの電圧を上昇させます。

RUNピンをグランドに引き下げる、メイン制御ループがシャットダウンします。RUNピンを“H”に引き上げると、コントローラはスタートアップします。スタートアップはTRACK/SSピンに依存します。TRACK/SSをフロートさせたままにすると、内部ソフトスタートがイネーブルされ、出力電圧を望みのレベルまで1.2msでランプアップさせます。出力電圧はそれに関連したTRACK/SSピンの電圧をトラッキングします。TRACK/SSピンが(他のLTC3546レギュレータの出力電圧など)別の電源の抵抗分割器を通して接続されていると、出力電圧はこの電源をトラッキングするので、LTC3546の出力電圧は他の電源のスタートアップをトラッキングすることができます。TRACK/SSピンからグランドにコンデンサが接続されている場合、RUNが“H”になると、内部1.15μA電流源が外部コンデンサを充電し、出力電圧のスタートアップを制御します。外部スタートアップのランプ時間は1.2msの内部スタートアップ時間より長くするように注意してください。

### 低電流動作

低電流でLTC3546の動作を制御するには3つのモードを利用することができます。3つのモードは全て負荷電流が低いとき、連続動作から選択されたモードに自動的に切り替えられます。

効率を最適化するにはBurst Mode動作を選択することができます。負荷が比較的軽いとき、LTC3546は自動的にBurst Mode動作に切り替わります。この場合、スイッチは負荷需要に応じて間欠的に動作します。サイクルを間欠的に実行することにより、パワーMOSFETのゲート電荷損失によって支配されるスイッチング損失が小さく抑えられます。出力電圧が望みの安定値に達したらメイン制御ループが中断します。

ITHが0.24Vより低くなるとヒステリシスをもった電圧コンパレータがトリップし、スイッチをオフして電力を減少させます。ITHが0.31Vを超えて、スイッチとメイン制御ループをオンし、新たなサイクルを開始するまで、出力コンデンサとインダクタが負荷に電力を供給します。

## 動作

Burst Modeのピーク・インダクタ電流はBMCピンを使って外部で設定することができます。このピンを0V～0.6Vのどこかに設定すると、このピンの電圧がBurst Modeのクランプ・レベルを制御します。

BMCピンをV<sub>IN</sub>に引き上げると、内部Burst Modeクランプ・レベルが使われます。

低電流で出力電圧リップルを下げるには、パルス・スキップ・モードを使うことができます。このモードでは、LTC3546は非常に低い電流まで固定周波数でスイッチングを継続します。この場合、最終的にはパルスをスキップし始めます。

最後に、強制連続モードでは、インダクタ電流は一定のサイクルで流れ、全ての出力電流レベルで固定された出力電圧リップルを生じます。この機能は遠距離通信に適しています。なぜなら、ノイズが一定の周波数になるのでフィルタで除去するのが容易だからです。このモードの別の利点は、レギュレータが負荷へ電流をソースするだけでなく、出力からいくらかの電流

をシンクすることもできます。強制連続動作では、過電圧コンパレータがV<sub>FB</sub>ピンをモニタし、過電圧状態が検出されると(V<sub>FB</sub> > 0.63V)電流リミットを減少させます。

SYNC/MODEピンはLTC3546をどのモードにするかを選択します。SYNC/MODEピンは両方のレギュレータのモードを設定します。

### ドロップアウト動作

入力電源電圧が出力電圧に向かって低下すると、デューティサイクルが100%に増加しますが、これがドロップアウト状態です。ドロップアウト状態では、PMOSスイッチが連続的にオンし、このときの出力電圧は、入力電圧から内部PチャネルMOSFETとインダクタの電圧降下を差し引いた電圧に等しくなります。

### 低電源電圧動作

LTC3546は低電圧ロックアウト回路を内蔵しており、この回路は入力電圧が約2.14Vより下に下がるとデバイスをシャットダウンして不安定な動作を防ぎます。

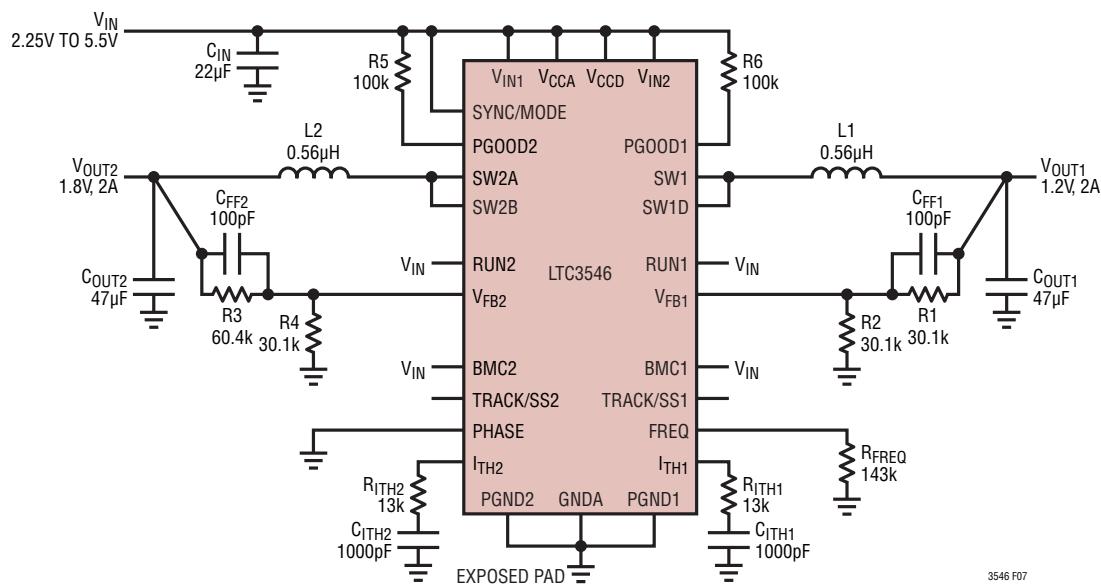

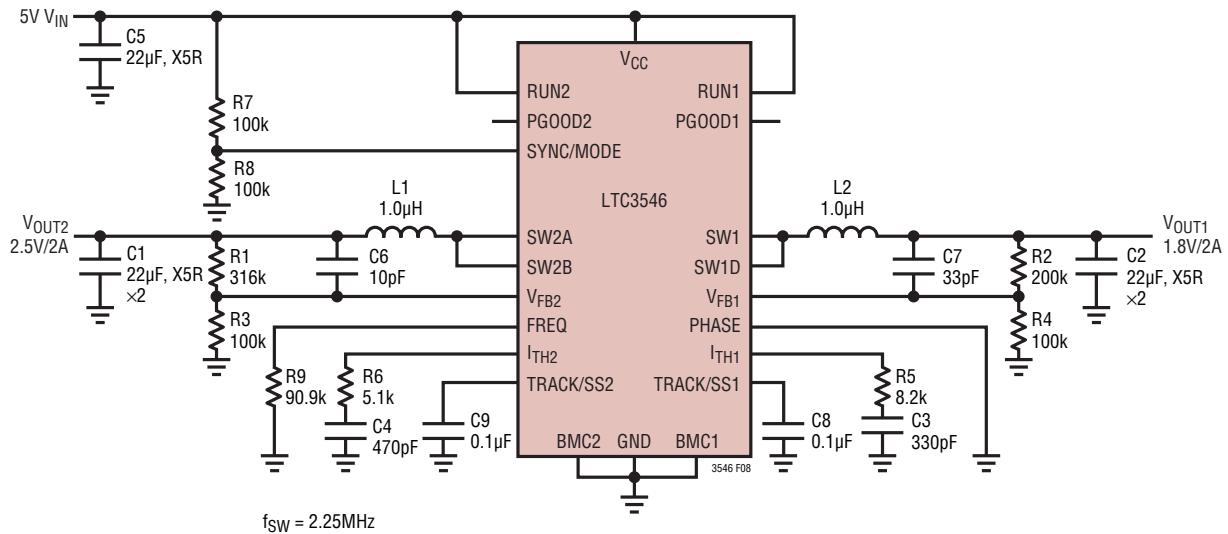

## アプリケーション情報

一般的なLTC3546の応用回路を図7に示します。外付け部品の選択は負荷の要求条件に基づいて行われ、インダクタのL1とL2の選択から始めます。L1とL2が選択されると、C<sub>IN</sub>、C<sub>OUT1</sub>およびC<sub>OUT2</sub>を選択することができます。

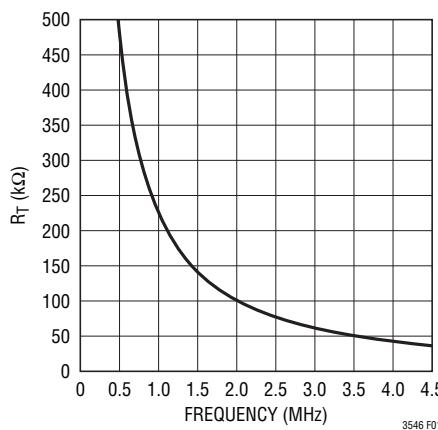

### 動作周波数

動作周波数の選択には効率と部品サイズの間のトレードオフを考慮します。動作周波数を高くすると、小さい値のインダクタとコンデンサを使うことができます。低い周波数で動作させると内部ゲート電荷による損失が減り、効率が改善されますが、出力リップル電圧を低く抑えるには、インダクタンスや容量の値を大きくする必要があります。

LTC3546の動作周波数(f<sub>O</sub>)は、FREQピンをV<sub>IN</sub>に引き上げて2.25MHz動作に設定するか、外付け抵抗をFREQからグランドに接続するか、または外部クロック信号でSYNC/MODEをドライブして設定します。

外部抵抗を使って発振器の周波数を設定するとき、0.75MHz ≤ f<sub>O</sub> ≤ 4MHzでは次式を使います。

$$R_T = \frac{2.51 \cdot 10^{11}}{f_0} (\Omega) - 20\text{k}\Omega$$

または、図1を使ってR<sub>T</sub>の値を選択します。

最大動作周波数は、特に強制連続モードが選択されていると、最小オン時間(標準70ns)とデューティサイクルによっても

制限されます。150nsのワーストケースの最小オン時間を想定すると、これは次のように計算することができます。

$$f_{O(\text{MAX})} \approx 6.67 \left( \frac{V_{\text{OUT}}}{V_{\text{IN}(\text{MAX})}} \right) (\text{MHz})$$

最小周波数はR<sub>T</sub>の抵抗値が大きいため、リークとノイズ・カップリングによって制限されます。

### インダクタの選択

インダクタは動作周波数には影響しませんが、インダクタの値はリップル電流に直接影響します。インダクタ・リップル電流ΔI<sub>L</sub>は次式で示すようにインダクタンスが高いほど減少し、V<sub>IN</sub>またはV<sub>OUT</sub>が高いほど増加します。

$$\Delta I_L = \frac{V_{\text{OUT}}}{f_0 \cdot L} \left( 1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}} \right)$$

大きなΔI<sub>L</sub>の値を許容すれば低インダクタンスを使用できますが、出力電圧リップルが高くなり、コア損失が大きくなり、出力電流能力が低下します。

リップル電流を設定するための妥当な出発点は、ΔI<sub>L</sub> = 0.35I<sub>LOAD(MAX)</sub>です。ここで、I<sub>LOAD(MAX)</sub>は最大出力電流です。最大入力電圧で最大リップル(ΔI<sub>L</sub>)が発生します。リップル電流が規定された最大値を超えないようにするには、次式に従ってインダクタ値を選択します。

$$L \geq \frac{V_{\text{OUT}}}{f_0 \cdot \Delta I_L} \left( 1 - \frac{V_{\text{OUT}}}{V_{\text{IN}(\text{MAX})}} \right)$$

図1. 周波数とR<sub>T</sub>

## アプリケーション情報

### Burst Mode動作に関する検討事項

LTC3546がBurst Mode動作に入る負荷電流を決める2つの要因があります。インダクタの値とBMCピンの電圧です。ピーク・インダクタ電流がバースト・クランプによって設定されたレベルより下に下がると、低電流動作からの移行が開始されます。インダクタ値が小さいとリップル電流が大きくなるので、このBurst Mode動作が低い負荷電流で起きるようになります。低いインダクタの値は、低電流動作範囲の上の部分での効率低下も引き起こします。低いインダクタの値は、Burst Mode動作でバースト周波数の上昇も引き起こします。

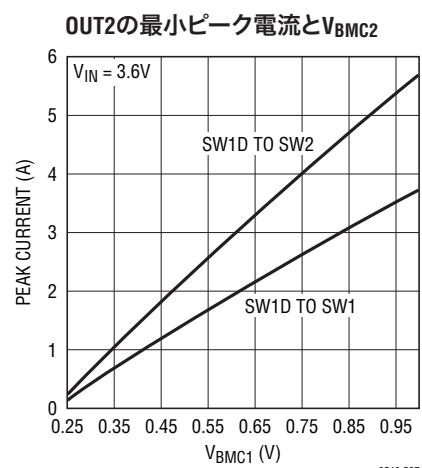

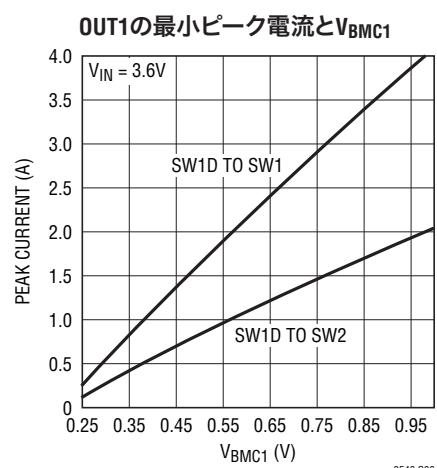

バースト・クランプ・レベルは、BMCピンの電圧によって設定することができます。BMCをVINに接続すると、内部で設定されているレベルが使われます。BMCピンの0V～0.6Vの電圧はバースト・クランプ・レベルを設定します（「標準的性能特性」のセクションの「OUT1の最小ピーク電流とV<sub>BMC1</sub>」および「OUT2の最小ピーク電流とV<sub>BMC2</sub>」のチャートを参照）。一般に、クランプ・レベルが高いほど、軽負荷での効率が改善され、出力電圧リップルが高くなりますが、クランプ・レベルが低いほど、効率を代償にして出力電圧リップルが小さくなります。Burst Mode動作を選択しないときは、BMCピンをグランドに接続します。

### インダクタのコアの選択

コアの材質と形状が異なると、インダクタのサイズ/電流の関係が変化します。フェライトやパーマロイを素材とするトロイド・コアやシールドされた壺型コアは小型で、エネルギー放射は大きくありませんが、類似の電気的特性を有する鉄粉コアのインダクタより一般に高価です。使用するインダクタの種類の選択は、LTC3546の動作条件に依存するよりも、価格とサイズの要件や放射フィールド/EMIの要件に多くの場合依存します。LTC3546のアプリケーションで適切に動作する標準的表面実装インダクタをいくつか表1に示します。

### 入力コンデンサ( $C_{IN}$ )の選択

連続モードでは、コンバータの入力電流は、デューティサイクルがほぼ $V_{OUT1}/V_{IN}$ および $V_{OUT2}/V_{IN}$ の2つの方形波の和によって近似することができます。大きな過渡電圧を防止するには、最大RMS電流に対応できる大きさの低等価直列抵抗(ESR)の入力コンデンサを使用する必要があります。コンデンサによっては、最大RMS電流に対するディレーティング仕様が規定されています。使用されるコンデンサにこの規定があれば、最大RMS電流を計算する必要があります。デバイスが同

表1.

| MANUFACTURER     | PART NUMBER           | VALUE ( $\mu$ H) | MAX DC CURRENT (A) | DCR    | DIMENSIONS L × W × H (mm) |

|------------------|-----------------------|------------------|--------------------|--------|---------------------------|

| Würth Elektronik | WE-PD2 MS 7447745012  | 1.2              | 4.6                | 0.017  | 5.2 × 5.8 × 2             |

| Würth Elektronik | WE-PD2 MS 74477450056 | 0.56             | 6.5                | 0.0078 | 5.2 × 5.8 × 2             |

| Vishay           | IHLP-1616AB-11        | 1.2              | 3.75               | 0.068  | 4.06 × 4.45 × 1.20        |

| Vishay           | IHLP-1616AB-11        | 0.47             | 6                  | 0.019  | 4.06 × 4.45 × 1.20        |

| Coilcraft        | LPS6225-122           | 1.2              | 5.4                | 0.04   | 6.2 × 6.2 × 2.5           |

| Coilcraft        | DO1813H-561           | 0.56             | 7.7                | 0.01   | 6.10 × 8.89 × 5.00        |

| Coiltronics      | SD20-1R2              | 1.2              | 2.55               | 0.0275 | 5.2 × 5.2 × 2             |

| Coiltronics      | SD20-R47              | 0.47             | 4                  | 0.02   | 5.2 × 5.2 × 2             |

| Sumida           | CDRH3D23NP-1R5NC      | 1                | 2.8                | 0.025  | 3.8 × 3.8 × 2.3           |

## アプリケーション情報

相で使用されるか位相をずらして使用されるかによって、RMS電流の計算が異なります。

同相の場合、2つの異なった式があります。

$V_{OUT1} > V_{OUT2}$ :

$$I_{RMS} = \sqrt{2 \cdot I1 \cdot I2 \cdot D2(1-D1) + I2^2(D2-D2^2) + I1^2(D1-D1^2)}$$

$V_{OUT2} > V_{OUT1}$ :

$$I_{RMS} = \sqrt{2 \cdot I1 \cdot I2 \cdot D1(1-D2) + I2^2(D2-D2^2) + I1^2(D1-D1^2)}$$

ここで、

$$D1 = \frac{V_{OUT1}}{V_{IN}} \text{ および } D2 = \frac{V_{OUT2}}{V_{IN}}$$

$D1 = D2$  の場合、式は次のように簡単になります。

$$I_{RMS} = (I1 + I2) \sqrt{D(1-D)}$$

つまり

$$I_{RMS} = (I1 + I2) \frac{\sqrt{V_{OUT}(V_{IN} - V_{OUT})}}{V_{IN}}$$

ここで、最大平均出力電流  $I1$  と  $I2$  はピーク電流からピーク-ピーク間リップル電流の半分を差し引いたものに等しくなります。

$$I1 = I_{LIM1} - \frac{\Delta I_{L1}}{2}$$

$$I2 = I_{LIM2} - \frac{\Delta I_{L2}}{2}$$

これらの式は  $V_{IN} = 2V_{OUT}$  のとき最大値をとります。ここで、 $I_{RMS} = (I1 + I2)/2$  です。この単純なワーストケース条件がワーストケースの  $I_{RMS}$  を求めるのに一般に使用されます。

位相をずらした場合(PHASEピンはグランド)、位相が合っている場合よりもリップル電流を低くすることができます。

位相をずらした場合、 $I_{RMS}$  は  $V_{OUT1} = V_{OUT2}$  のとき最大になりません。一般に、 $V_{OUT1} - V_{IN}/2 = V_{OUT2}$  および  $V_{OUT2} -$

$V_{IN}/2 = V_{OUT1}$  のとき最大になります。およそのところ、ワーストケースのリップルの大きさは同相モードのワーストケースのリップルの約75%です。 $V_{OUT1} = V_{OUT2} = V_{IN}/2$  および  $I1 = I2$  のとき、リップルは最小であることに注意してください。

コンデンサ・メーカーのリップル電流定格は多くの場合わずか2000時間の寿命時間によって規定されていることに注意してください。このため、コンデンサをさらにディレーティングする、つまり要件よりも高い温度定格のコンデンサを選択することを推奨します。サイズまたは高さの設計条件に適合させるため、複数のコンデンサを並列に接続することもできます。全てセラミック・コンデンサを使うソリューションを採用しない場合は、高周波のデカップリングのために、0.1μF～1μFのセラミック・コンデンサを  $V_{IN}$  に追加することも推奨します。

### 出力コンデンサ( $C_{OUT1}$ と $C_{OUT2}$ )の選択

$C_{OUT1}$ と $C_{OUT2}$ の選択は、電圧リップルおよび負荷ステップに対する過渡を小さくするために必要なESRによって決まります。一般に、ESRの要件が満たされると、その容量はフィルタ機能にとって十分です。出力リップル( $\Delta V_{OUT}$ )は次式で決まります。

$$\Delta V_{OUT} \approx \Delta I_L \left( ESR + \frac{1}{8 \cdot f_0 \cdot C_{OUT}} \right)$$

ここで、 $f_0$  = 動作周波数、 $C_{OUT}$  = 出力容量、 $\Delta I_L$  = インダクタのリップル電流です。 $\Delta I_L$  は入力電圧に応じて増加するので、出力リップルは入力電圧が最大のとき最大になります。

$C_{OUT}$ のESRの要件が満たされれば、全てセラミックを使ったソリューションの場合を除いて、一般にRMS電流定格は  $I_{RIPPLE(P-P)}$  の要件をはるかに上回ります。

表面実装のアプリケーションでは、アプリケーションの容量、ESRまたはRMS電流の処理要件を満たすため、複数のコンデンサの並列接続が必要になることがあります。アルミ電解、特殊ポリマー、セラミック、および乾式タンタルの各コンデンサは全て表面実装パッケージで入手できます。三洋製のOS-CON半導体誘電体コンデンサは、アルミ電解コンデンサの中で(ESR・サイズ)の積が最も小さいのですが、やや高価です。三洋製のPOSCAPなど特殊ポリマー・コンデンサはESRが非常に小さいのですが、他のタイプに比べて容量密度が低くなります。タンタル・コンデンサは最高の容量密度をもっていますが、ESRが大きく、スイッチング電源に使うためにサージテストされていることが必須条件です。ケースの高さが2mm～

## アプリケーション情報

4mmの表面実装タンタル・コンデンサのAVX TPSシリーズが最適です。アルミ電解コンデンサははるかに高いESRをもっていますが、リップル電流定格および長期信頼性に対して配慮すれば、コスト要求の非常に厳しいアプリケーションでよく使用されます。セラミック・コンデンサは最もESRが小さく廉価ですが、容量密度が低く、電圧係数と温度係数が高くて、可聴圧電効果を示します。さらに、トレース・インダクタンスをともなったセラミック・コンデンサはQが高く、大きなリンクギングを引き起こすことがあります。他のコンデンサのタイプにはパナソニック製の特殊ポリマー（SP）コンデンサがあります。

### 入力と出力のセラミック・コンデンサ

値の大きな低価格セラミック・コンデンサが今では小さなケース・サイズで入手できるようになりました。LTC3546の制御ループの安定動作は出力コンデンサのESRに依存しないので、自由にセラミック・コンデンサを使用して出力リップルを非常に低くし、回路サイズを小さくすることができます。入力と出力にセラミック・コンデンサを選択する場合は、X5RまたはX7Rの誘電体のものを選択します。これらの誘電体はある特定の値とサイズに対して全てのセラミックの中で温度特性と電圧特性が最も優れています。

入力と出力にセラミック・コンデンサだけを使う場合、十分注意する必要があります。セラミック・コンデンサを入力に使い、ACアダプタなど長いコードを通して電力を供給すると、出力の負荷ステップによってV<sub>IN</sub>ピンにリンクギングが誘起されることがあります。よくても、このリンクギングが出力に結合して、ループの不安定性と誤認されることがあります。最悪の場合、この入力のリンクギングが回路動作を中断させるか、またはデバイスに損傷を与えるほど大きくなることがあります。

セラミック・コンデンサのESRは非常に小さいので、入力コンデンサと出力コンデンサはそれよりも電荷保存の要件を満たす必要があります。負荷ステップ発生時には、帰還ループがスイッチ電流を十分増加させて負荷を支えるまで、出力コンデンサが即座に電流を供給して負荷を支える必要があります。帰

還ループが応答するのに要する時間は補償部品と出力コンデンサのサイズに依存します。負荷ステップに応答するには標準で3~4サイクルを要しますが、最初のサイクルだけ出力が直線的に低下します。出力の垂下V<sub>DROOP</sub>は通常最初のサイクルの直線的な垂下の約2~3倍です。したがって、およそ以下の出力コンデンサのサイズから開始するのが良いでしょう。

$$C_{OUT} \approx 2.5 \frac{\Delta I_{OUT}}{f_0 V_{DROOP}}$$

デューティサイクルと負荷ステップの要件によっては、さらに大きな容量が必要になることがあります。

ほとんどのアプリケーションでは、電源のインピーダンスは非常に小さいので、入力コンデンサは単に高周波をバイパスするのに必要です。これらの条件では、通常10μFセラミック・コンデンサで十分です。

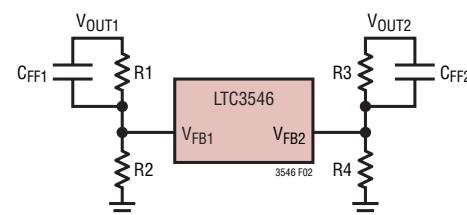

### 出力電圧の設定

LTC3546は帰還ピンV<sub>FB1</sub>およびV<sub>FB2</sub>と信号グランドとの間に0.6Vのリファレンス電圧を発生します。出力電圧は次式に従って抵抗分割器によって設定されます。

$$V_{OUT1} \approx 0.6V \left( 1 + \frac{R1}{R2} \right)$$

$$V_{OUT2} \approx 0.6V \left( 1 + \frac{R3}{R4} \right)$$

抵抗の位置を図2に示します。

図2. 出力電圧の設定

## アプリケーション情報

これらの抵抗を流れる電流を小さく(<20μA)抑えると効率が向上しますが、この電流を小さくしすぎると、浮遊容量がノイズの問題を発生させ、誤差アンプのループの位相マージンが減少するおそれがあります。

周波数応答を改善するには、フィードフォワード・コンデンサ  $C_{FF}$  を使うこともできます。ここで使われる標準値は10pF～100pFです。 $V_{FB}$  ノードはインダクタやSWラインなどのノイズ源から離して配線するように十分注意してください。

### シャットダウン、ソフトスタート およびスタートアップのトラッキング

LTC3546のスタートアップは2つの入力(内部の1.2msリニア・ソフトスタート・ランプとTRACK/SSピン)を比較することによって動作します。どちらであれ電圧の低い方の入力がスタートアップに使われる制御電圧になります。内部スタートアップは1.2msで0.6Vまでランプします。もっと遅いスタートアップを望むなら、TRACK/SSピンには1.15μAのプルアップ電流が備わっているので、スタートアップのランプ・レートを外部コンデンサによってプログラムすることができます。または、別の信号からの分圧器をTRACK/SSピンに接続することができます。

スタートアップ時、出力がスイッチングを開始するには制御電圧が120mVを超える必要があります。

RUNピンが“L”的とき、内部の1.2msソフトスタート・ランプとTRACK/SSピンの両方ともグランドに引き下げられます。RUNピンが“H”に引き上げられると、内部のソフトスタート・ランプとTRACK/SSピンの両方ともリリースされます。RUNピンがアサートされた時点から制御電圧が0.6Vに達するまで、レギュレータはスタートアップ状態にあります。この状態では、誤差アンプは $V_{FB}$ の帰還信号を制御電圧(TRACK/SS電圧または内部のランプ電圧のどちらか低い方)と比較し、レギュレータはそれらを強制的に等しくします。この状態では、レギュレータのモードはパルス・スキップに強制されます。レギュレータは制御電圧が0.6Vより上に上昇するまでこの状態を継続します。制御ランプ信号が0.6Vを超えた後、誤差アンプは内部0.6Vリファレンスを使い、動作モードはSYNC/MODEピンで設定されているモードに切り替わります。

TRACK/SSピンがスタートアップ後にランプダウンすると、TRACK/SSの電圧が0.6Vの内部リファレンス電圧より6%下(0.564V)に下がった後は、誤差アンプは $V_{FB}$ の帰還信号をTRACK/SSピンの電圧と比較します。出力をこのレートで引

き下げるのに十分な負荷電流が存在すると、レギュレータは $V_{FB}$ 電圧をTRACK/SS電圧に等しくなるように強制します。そうでなければ、出力は出力コンデンサの放電レートでランプダウンします。TRACK/SSの電圧が約100mVより下になると、全てのスイッチング機能が停止し、レギュレータはパルス・スキップ・モードに強制的に戻されます。TRACK/SSがランプダウンしている間の動作モードはMODE/SYNCピンによって設定されます。

内部の1.2msリニア・ソフトスタート制御電圧を使うには、TRACK/SSピンをフロートさせたままにします。TRACK/SSピンをフロートさせることにより、内部の1.15μAのプルアップ電流がTRACK/SSピンを内部の1.2msのランプより速く引き上げます。TRACK/SSのランプアップ時間(0Vから0.6Vまで)が内部の1.2msのランプ時間よりはるかに短くなるように注意する必要があります。このピンの寄生容量が次の値よりずっと小さくなるようにします。

$$C_{PARASITICTRACK/SS} \ll \frac{1.15\mu A \cdot 1.2ms}{0.6V}$$

つまり

$$C_{PARASITICTRACK/SS} \ll 2.3nF$$

外部で制御されるソフトスタート・ランプは、外部コンデンサがTRACK/SSピンからグランドに接続されており、そのランプ・レートが内部のソフトスタート・ランプより遅いとき得られます。この構成設定では、1.2msより長いソフトスタート時間を達成することができます。RUNが“H”に引き上げられると、内部1.15μA電流源が外部コンデンサを0Vから直線的に充電します。TRACK/SSピンが0.6Vより低い間、誤差アンプはレギュレータを強制して $V_{FB}$ ピンをTRACK/SSピンの電圧までドライブします。 $V_{FB}$ ピンが0.6Vに達すると、レギュレータは内部0.6Vリファレンスに切り替わります。出力のランプアップ時間は次のように計算されます。

$$t_{RAMP} = \frac{C_{TRACK/SS} \cdot 0.6V}{1.15\mu A}$$

この式が有効であるためには、ランプ時間が1.2msより大きくなければならないので、次のようにになります。

$$C_{TRACK/SS} \geq \frac{1.15\mu A \cdot 1.2ms}{0.6V}$$

つまり

$$C_{TRACK/SS} \geq 2.3nF$$

## アプリケーション情報

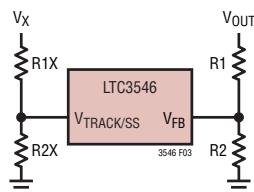

LTC3546は、TRACK/SSピンに接続された外部分圧器を使い、またTRACK/SSピンのランプ・レートが内部1.2msのランプ・レートより遅いことを保証することにより、スタートアップの間外部の電圧をトラッキングすることも可能です。

図3に示されているように、外部電圧からの抵抗分割器をTRACK/SSピンに接続することができるので、V<sub>OUT</sub>のスタートアップは外部電圧V<sub>X</sub>をレシオメトリックに(一定の割合で)トラッキングすることができます。

V<sub>TRACKSS</sub> < 0.6Vの場合

$$V_{OUT} = V_X \cdot \frac{R_{2X}}{R_{1X} + R_{2X}} \cdot \frac{R_1 + R_2}{R_2}$$

図3. 外部電圧のトラッキング

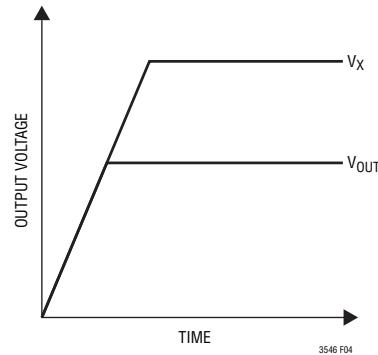

同時トラッキングはスタートアップの間V<sub>OUT</sub> = V<sub>X</sub>の場合です。同時トラッキングを実現するには、図3のR1XをR1と同じ値に設定し、R2XをR2の値に設定します。同時トラッキングを図4に示します。V<sub>X</sub>がその最終値のときTRACK/SSの電圧が(0.6Vのリファレンスより上に十分なマージンをとって)≥ 0.8Vとなるようにします。

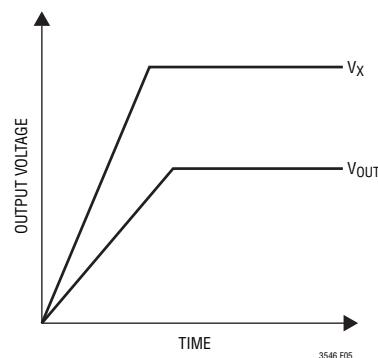

レシオメトリック・トラッキングは、スタートアップの間V<sub>OUT</sub> ≠ V<sub>X</sub>であり、V<sub>OUT</sub>がV<sub>X</sub>の一定割合に設定される場合です。図5に示されているように、レシオメトリック・トラッキングを実現するには、図3のR1XをR1と同じ値に設定し、R2XをR2 + ΔRの値に設定します。R2に追加されるΔRは、V<sub>X</sub>がその最終値に達したときTRACK/SSの電圧が(0.6Vのリファレンスより上に十分なマージンをとって)≥ 0.8Vになるのに十分な値にします。

TRACK/SSに抵抗分割器を使うと、TRACK/SSの内部1.15μA プルアップ電流によりV<sub>OUT</sub>にトラッキング誤差を生じることがあります。たとえば、R2Xに59kの抵抗を選択すると、R2Xの電流は約10μA (0.6V/59k)になります。この場合、1.15μAの内部電流源により約11% (1.15μA/10μA) のトラッキング誤差が生じ、V<sub>FB</sub>を基準にして約66mVになります。これはほとんどのアプリケーションで許容できます。もっと良いトラッキング精度が必要な場合、R2Xの値を減らすことができ、または1.15μAの電流を式の中に取り入れることができます。

図4. 同時トラッキング

図5. レシオメトリック・トラッキング

TRACK/SSを使用できる異なった状態を表2に示します。

表2. TRACK/SSピンの状態

| TRACK/SS PIN        | RESULT                                                       |

|---------------------|--------------------------------------------------------------|

| Capacitor to Ground | External Soft-Start                                          |

| Floating            | Internal Soft-Start                                          |

| Resistor Divider    | V <sub>OUT</sub> Tracking an External Voltage V <sub>X</sub> |

実現されるモードが何であれ、TRACK/SSピンは決して外部から“H”に引き上げないでください。そうするとシャットダウン時に過度の電流が生じるからです。

LTC3546は予めバイアスされている出力に対してスムーズに起動することができます。トラッキング機能により、予めバイアスされている電圧を検出して出力をそこからランプアップさせます。

### モード選択

SYNC/MODEピンは多目的ピンで、モード選択機能と周波数同期機能を備えています。このピンをV<sub>IN</sub>に接続すると、両方のレギュレータに対してBurst Mode動作をイネーブルします。

## アプリケーション情報

このモードは、出力電圧リップルが大きくなる代償を払って最も低電流効率を与えます。SYNC/MODEピンをグランドに接続すると、両方のレギュレータにパルス・スキップ動作が選択されます。このモードは、低電流での効率が下がる代償を払って、出力の電圧リップルと電流リップルを下げます。VIN/2を与えると、両方のレギュレータは強制連続モードになります。このモードは出力リップルを固定し、いくらかの電流(約1/2 •  $\Delta I_L$ )をシンクすることができます。このモードではスイッチング・ノイズが一定なので、フィルタによる除去も簡単です。最初のスタートアップの間、PGOODピンが“H”になるまでパルス・スキップ・モードが強制されます。

SYNC/MODEピンを使ってLTC3546を外部クロック信号に同期させることもできます。内部のフェーズロック・ループは入ってくる信号にロックして、正しいスロープ補償とともに180°位相のずれた動作を与えます。外部同期では、内部フェーズロック・ループを外部で補償するのにFREQピンが使われます。図6に示されているように、補償に使われる標準値は200kと100pFです。同期状態の間、レギュレータの動作モードはパルス・スキップに強制されます。Pチャネル・スイッチのターンオンは外部クロックの立上りエッジに同期します。

PHASEピンを“L”にして外部クロックを使うとき、2つのチャネルのスイッチングは180°位相がずれます。

図6. PLL補償

### 過渡応答のチェック

$I_{TH}$ ピンの補償により、広範な負荷と出力コンデンサに対して過渡応答の最適化を図ることができます。 $I_{TH}$ ピンが備わっているので制御ループ動作を最適化できるだけでなく、DC結合されACフィルタを通した閉ループ応答のテスト・ポイントが与えられます。このテスト・ポイントでのDCステップ、立上り時間、およびセトリングは、真の閉ループ応答を反映します。2次特性が支配的なシステムを想定すれば、位相マージンや減衰係数はこのピンで見られるオーバーシュートのパーセンテージを使って推定することができます。このピンで見られるオーバー

シュートのパーセンテージを使って、あるいはこのピンの立上り時間を調べることにより、帯域幅も推定できます。

図9の回路に示されている $I_{TH}$ ピンの外部部品はほとんどのアプリケーションにおいて妥当な出発点となります。直列R-Cフィルタにより、支配的なポール-ゼロのループ補償が設定されます。これらの値は、プリント基板のレイアウトを完了し、特定の出力コンデンサの種類と容量値を決定したら、過渡応答を最適化するために多少は(推奨値の0.5倍~2倍)変更することができます。出力コンデンサのさまざまなタイプと値によってループの帰還係数の利得と位相が決まるので、まず出力コンデンサを選択する必要があります。立上り時間が1μs~10μsの最大負荷電流の20%~100%の出力電流パルスによって発生する出力電圧波形と $I_{TH}$ ピンの波形により、帰還ループを開くことなく全体的なループの安定性を判断することができます。

スイッチング・レギュレータは負荷電流ステップに対して応答するのに数サイクルを要します。負荷ステップが生じると、 $V_{OUT}$ は $\Delta I_{LOAD} \cdot ESR$ に等しい量だけ直ちにシフトします。ここで、ESRは $C_{OUT}$ の等価直列抵抗です。 $\Delta I_{LOAD}$ はさらに $C_{OUT}$ の充電あるいは放電を開始し、レギュレータが $V_{OUT}$ をその定常値に戻すために使う帰還誤差信号を発生します。この回復時間の間、安定性に問題があることを示すオーバーシュートやリンギングがないか $V_{OUT}$ をモニタすることができます。

初期出力電圧ステップが帰還ループの帯域幅内にない場合があるため、位相マージンを決定するのに、標準的2次オーバーシュート/DC比を使用することはできません。ループの利得は $R_{ITH}$ を大きくすると増加し、ループの帯域幅は $C_{ITH}$ を小さくすると拡大します。 $C_{ITH}$ が減少したのと同じ比率だけ $R_{ITH}$ を増大させると、ゼロ周波数は同じに維持されますので、帰還ループの最も重要な周波数範囲で位相を同じに維持します。さらに、フィードフォワード・コンデンサ( $C_{FF1}$ と $C_{FF2}$ )を追加して、図9に示されているように、高周波応答を改善することができます。コンデンサ $C_{FF1}$ はR1とともに高い周波数のゼロを作つて位相リードを与え、1AのSW1チャネルの位相マージンを改善します。コンデンサ $C_{FF2}$ はR3とともに高い周波数のゼロを作つて位相リードを与え、3A SW1D/SW2チャネルの位相マージンを改善します。

出力電圧のセトリングの様子は閉ループ・システムの安定性に関係し、電源全体の実際の性能を表します。

## アプリケーション情報

制御ループ理論の要点を含む補償部品の最適化の詳細については、弊社の「アプリケーションノート76」を参照してください。

降圧レギュレータはドロップアウト状態で最大出力電流を供給する能力をもっていますが、入力電圧  $V_{IN}$  が  $V_{OUT}$  に向かって低下するにつれ、インダクタ両端の電圧が減少するため、負荷ステップに対応する能力が低下することに注意する必要があります。ドロップアウトの近くで大きな負荷ステップに対応する能力を必要とするアプリケーションでは、SEPIC、Zeta、または単一インダクタを使ったポジティブ昇降圧など別のトポロジーを使います。

アプリケーションによっては、(1 $\mu$ Fを超える)大きな入力コンデンサが接続されている負荷のスイッチがオンすると、さらに大きな過渡を生じる可能性があります。放電した入力コンデンサが実質的に  $C_{OUT}$  と並列接続状態になるため、 $V_{OUT}$  が急速に下降します。負荷を接続するスイッチの抵抗が低く、しかも瞬間にドライブされると、どんなレギュレータでもこの問題を防止するだけの十分な電流を供給することはできません。解決策は負荷スイッチのドライバのターンオン速度を制限することです。ホットスワップ・コントローラは特にこの目的のために設計されており、電流制限、短絡保護、およびソフトスタート機能を通常備えています。

### 効率に関する検討事項

スイッチング・レギュレータのパーセント効率は、出力電力を入力電力で割って100%を掛けたものに等しくなります。個々の損失を解析して、効率を制限する要素がどれであり、また何が変化すれば最も効率が改善されるかを判断できる場合がよくあります。パーセント表示の効率は次式で表すことができます。

$$\% \text{効率} = 100\% - (P_1 + P_2 + P_3 + \dots)$$

ここで、 $P_1, P_2$ などは入力電力に対するパーセンテージで表した個々の損失です。

回路内の電力を消費する全ての要素で損失が生じますが、LTC3546の回路の損失の大部分は通常4つの主な損失要因によって生じます。これらは1)LTC3546の  $V_{IN}$  の電流、2)スイッチング損失、3) $I^2R$  損失、4)その他の損失です。

1.  $V_{IN}$  電流は電気的特性に記載したDC電源電流であり、MOSFETドライバと制御回路の電流は含まれません。無負荷でも、 $V_{IN}$  電流によって小さな(0.1%未満の)損失が発生し、この損失は  $V_{IN}$  に従って増加します。

2. スイッチング電流はMOSFETドライバ電流および制御回路電流の和です。MOSFETドライバ電流はパワーMOSFETのゲート容量をスイッチングすることによって流れます。MOSFETゲートが“L”から“H”、そして再び“L”に切り替わるたびに、 $V_{IN}$  からグランドに微小電荷が移動します。このようにスイッチング周期にわたって移動する電荷は  $V_{IN}$  から流出する電流であり、一般にDCバイアス電流よりはるかに大きくなります。ゲート電荷損失は  $V_{IN}$  に比例するので、それらの影響は電源電圧が高くなると顕著になります。

3.  $I^2R$  損失は内部スイッチのDC抵抗( $R_{SW}$ )と外部インダクタのDC抵抗( $R_L$ )から計算されます。連続モードでは、インダクタ  $L$  を流れる平均出力電流は内部のトップ・スイッチとボトム・スイッチの間で「こま切れ」にされます。したがって、SWピンを見たときの直列抵抗は、次式のとおり、トップMOSFETとボトムMOSFETの両方の  $R_{DS(ON)}$  およびデューティサイクル(DC)に応じて変化します。

$$R_{SW} = (R_{DS(ON)} \text{TOP})(DC) + (R_{DS(ON)} \text{BOT})(1-DC)$$

トップMOSFETとボトムMOSFETの両方の  $R_{DS(ON)}$  を「標準的性能特性」の曲線から求めることができます。したがって、 $I^2R$  損失は次式で求められます。

$$I^2R \text{損失} = I_{OUT}^2 (R_{SW} + R_L)$$

ここで、 $R_L$  はインダクタの抵抗です。

4. 銅トレースや内部バッテリの抵抗など他の隠れた損失が携帯用システムではさらなる効率低下の原因になる可能性があります。これらの「システム」レベルの損失をシステムの設計に含めることが非常に重要です。内部バッテリとヒューズの抵抗損失は、スイッチング周波数において  $C_{IN}$  の電荷蓄積を適切にし、ESRを非常に低くすれば最小に抑えることができます。デッドタイム中のダイオードの導通損失やインダクタのコア損失などその他の損失は、一般に全追加損失の2%以下にしかなりません。

### 熱に関する検討事項

LTC3546はバックプレーン・メタル(ピン29)をPCボードに十分半田付けする必要があります。これにより、UFDパッケージに(このサイズの同様のパッケージに比べて)類の無い熱特性が与えられ、通常動作ではデバイスの最大接合部温度を超えることはまずありません。大半のアプリケーションでは、LTC3546は効率が高いので大きな発熱はありません。

## アプリケーション情報

ただし、周囲温度が高く、(ドロップアウトの場合のように)低い電源電圧、高いデューティサイクルでLTC3546が動作するアプリケーションでは、発熱がデバイスの最大接合部温度を超えることがあります。接合部温度が約150°Cに達すると両方のレギュレータの両方のスイッチがオフし、SWノードが高インピーダンスになります。

LTC3546が最大接合部温度を超えないようにするには、熱に関する分析を行う必要があります。熱解析の目的は、電力損失によりデバイスが最大接合部温度を超えるかどうかを判断することです。温度上昇は次式で与えられます。

$$T_{RISE} = P_D \cdot \theta_{JA}$$

ここで、 $P_D$ はレギュレータの電力損失、 $\theta_{JA}$ はダイの接合部から周囲温度への熱抵抗です。

接合部温度 $T_J$ は次式で与えられます。

$$T_J = T_{RISE} + T_{AMBIENT}$$

一例として、入力電圧が3.3V、負荷電流が3A(SW1Dが外部でSW2に接続されている)および1Aのとき、LTC3546が両方のレギュレータでドロップアウト状態である場合について考えます。「標準的性能特性」の「スイッチ抵抗」のグラフから、SW2とSW1Dの並列組合せの3A用Pチャネル・スイッチの $R_{DS(ON)}$ 抵抗は0.06Ω、1A用Pチャネル・スイッチの $R_{DS(ON)}$ は0.18Ωです。デバイスの電力損失は次のとおりです。

$$P_D = I1^2 R_{DS(ON)1} + I2^2 R_{DS(ON)2}$$

$$P_D = 3^2 \cdot 0.064 + 1^2 \cdot 0.19$$

$$P_D = 0.77W$$

UFDパッケージの接合部-周囲の熱抵抗 $\theta_{JA}$ は約34°C/Wです。したがって、85°Cの周囲温度で動作しているレギュレータの接合部温度はおよそ次のとおりです。

$$T_J = 0.77 \cdot 34 + 85$$

$$T_J = 111.2^\circ\text{C}$$

上の接合部温度は25°Cの $R_{DS(ON)}$ から得られました。125°Cでは、 $R_{DS(ON)}$ は約30%増加します。これにより接合部温度は122°Cになります。電源がもっと低いと(たとえば2.25V)、 $R_{DS(ON)}$ はさらに高くなります。デバイスがドロップアウト状態で動作することが予想される場合、最大接合部温度の125°Cを超えないように特に注意する必要があります。

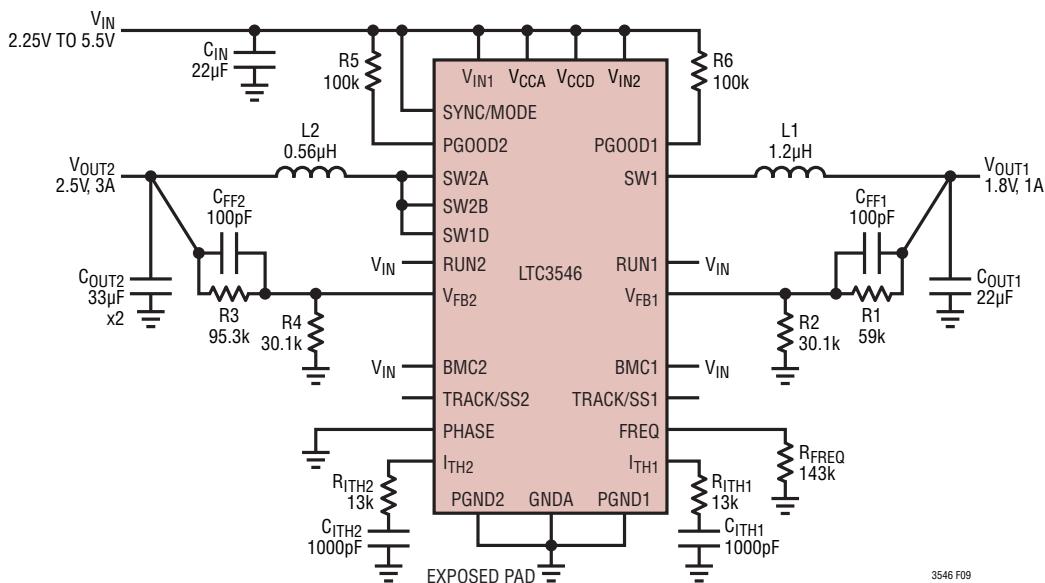

### 設計例

設計例として、リチウムイオン・バッテリを使った携帯用アプリケーションにLTC3546を使う場合を考えます。バッテリは $V_{IN} = 2.25V \sim 4.2V$ を供給します。片方の出力はアクティブ・モードで1.8V/2.5Aを必要とし、スタンバイ・モードで1mAを必要とします。他方の出力はアクティブ・モードで1.2V/800mAを必要とし、スタンバイ・モードで500μAを必要とします。両方の負荷ともスタンバイでも電力を必要とするので、低負荷での効率を良くするためにBurst Mode動作を選択します。

どの周波数を使うかを最初に決めます。周波数が高いほど、与えられた $\Delta I_L$ に対してインダクタの値が小さくなります( $\Delta I_L$ は0.35 $I_{LOAD(MAX)}$ として見積もられます)。表面実装型巻線インダクタの妥当な値は1μH以上です。 $\Delta I_L = 0.35I_{LOAD(MAX)}$ を使って異なる周波数を検討します。

| コンバータの出力       | $I_{LOAD(MAX)}$ | $\Delta I_L$ |

|----------------|-----------------|--------------|

| SW2/SW1D, 1.2V | 2.5A            | 875mA        |

| SW1, 1.8V      | 800mA           | 280mA        |

1.5MHzの周波数設定( $FREQ = GNDA$ に接続した143k)を使うと、L1とL2に関する以下の式が得られます。

$$L1 = \frac{1.2V}{1.5\text{MHz} \cdot 875\text{mA}} \cdot \left(1 - \frac{1.2V}{4.2V}\right) = 2\mu\text{H}$$

$$L2 = \frac{1.8V}{1.5\text{MHz} \cdot 280\text{mA}} \cdot \left(1 - \frac{1.8V}{4.2V}\right) = 0.78\mu\text{H}$$

1μHと2.2μHを使います。

$C_{OUT}$ は一般にリップルの要件ではなく、負荷ステップに基づいて選択します。必要な最小容量は、補償ループの帯域幅の減少や最大負荷ステップまたは出力電圧の許容誤差の増加に伴って増加します。

## アプリケーション情報

1.5MHzの公称動作周波数で1Aの出力電流当り約22μFとし、約300mA/Aの負荷ステップを想定するのが出発点として良いでしょう。

$$C_{OUT1} = \frac{22\mu F}{A} \cdot 0.8A \cdot \frac{280mA}{\frac{300mA}{A} \cdot 0.8A} = 20.5\mu F$$

$$C_{OUT1} = \frac{22\mu F}{A} \cdot 2.5A \cdot \frac{875mA}{\frac{300mA}{A} \cdot 2.5A} = 64.2\mu F$$

最も近い値は22μFと68μFです。

ここで、出力電圧はR1、R2、R3およびR4の値を選択してプログラムすることができます。高効率を維持するには、これらの抵抗を流れる電流を小さく保ちます。0.6の帰還電圧で2μAを選択すると、R2とR4は300kに等しくなります。これに近い標準1%抵抗は301kです。したがって、R1 = 300kになります。これに近い標準1%抵抗は301kです。次いでR3は600kに等しくなります。これに近い標準1%抵抗は604kです。

補償は、負荷ステップ応答を検討することにより、これらの部品に対して最適化されますが、LTC3546の場合、I<sub>TH1</sub>とI<sub>TH2</sub>の両方とも13kΩと1000pFのフィルタから始めるのが適当でしょう。負荷ステップの間の実際のトランジエントに応じて出力コンデンサを大きくする必要があるかもしれません。

PGOODピンはコモン・ドレイン出力で、プルアップ抵抗が必要です。適切な速度にするため、100kの抵抗を使います。この設計の完全な回路を図9に示します。

### 基板レイアウトの検討事項

PCボードをレイアウトするときには、以下のチェックリストを使用してLTC3546が正しく動作するようにします。これらの項目は図7のレイアウト図にも図示してあります。レイアウトでは以下の項目をチェックしてください。

1. SW1、SW2A、SW2BおよびSW1Dが幅の広い銅によってPCボード上で接続されていることを確認します。

2. C<sub>IN</sub>の全て(または一部)を、デバイスと同じPCボードの同じ側でデバイスにできるだけ近づけて、SWのトレースがコンデンサの直下を通るところで、ピン9からピン14に接続します。C<sub>IN</sub>は内部パワーMOSFETとそれらのドライバにAC電流を供給します。

3. それぞれのC<sub>OUT</sub>とLは近づけて接続されていますか。C<sub>OUT1</sub>の(-)プレートは電流をPGND1に戻し、C<sub>OUT2</sub>の(-)プレートは電流をPGND2に戻します。C<sub>IN</sub>の(-)プレートが電流をPGND1とPGND2にも戻すようにします。

4. 抵抗分割器(R1とR2)は、C<sub>OUT1</sub>の(+)プレートと、GNDAピンの近くで終端されたグランド・ラインの間に接続する必要があります。抵抗分割器(R3とR4)は、C<sub>OUT2</sub>の(+)プレートと、GNDAピンに終端されたグランド接続の間に接続する必要があります。帰還信号V<sub>FB1</sub>とV<sub>FB2</sub>はSWラインのようなノイズの多い部品やトレースから離して配線し、トレースをできるだけ短くします。

5. RFREQ抵抗を使うとき、抵抗のグランド接続はGNDAに終端します。内部PLLを使うとき、R-C補償ネットワークのグランド接続はGNDAピンに終端します。

6. 敏感な部品はSWピンから離します。入力コンデンサC<sub>IN</sub>、補償コンデンサC<sub>FF1</sub>、C<sub>FF2</sub>、C<sub>ITH1</sub>およびC<sub>ITH2</sub>、さらに全ての抵抗R1、R2、R3、R4、R<sub>ITH1</sub>およびR<sub>ITH2</sub>は、SWトレースとインダクタL1およびL2から離して配線します。

7. グランド・プレーンが望ましいのですが、それが利用できなければ信号グランドと電源グランドを分離し、小信号部品は1点でSGNDピンに戻し、この1点をPGND1/PGND2/PGND1D/GNDDの各ピンに接続します。

8. 全ての層の全ての未使用領域を銅で覆います。銅で覆うと電力部品の温度上昇が小さくなります。これらの銅領域は露出パッド(ピン29)に接続します。

## アプリケーション情報

図7. 2A/2Aレギュレータの標準的回路図

3546fc

図8. 2.25MHz固定周波数2A/2Aレギュレータ

## アプリケーション情報

図9. 3A/1Aレギュレータの標準的回路図

OUT1の効率(Burst Mode動作)

3546 F09b

OUT2の効率(Burst Mode動作)

3546 F09c

3546fc

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>をご覧ください。

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>をご覧ください。

FEパッケージ

28ピン・プラスチックTSSOP(4.4mm)

(Reference LTC DWG# 05-08-1663)

露出パッドのバリエーションEB

NOTE:

1.標準寸法:ミリメートル

2.寸法は  $\frac{\text{ミリメートル}}{(\text{インチ})}$

3.図は実寸とは異なる

4.露出パッド接着のための推奨最小PCBメタルサイズ

\*これらの寸法にはモールドのバリまたは突出部を含まない

モールドのバリまたは突出部は各サイドで0.150mm(0.006")を超えないこと

## 改訂履歴 (改訂履歴は Rev C から開始)

| REV | 日付   | 概要                                                                 | ページ番号            |

|-----|------|--------------------------------------------------------------------|------------------|

| C   | 3/13 | 標準的応用例のVIN範囲を修正。<br>電気的特性のNoteの温度範囲を明確化。<br>BMC、BMC1、GNDDピンの動作を明確化 | 1<br>3、4<br>9、10 |

# LTC3546

## 関連製品

| 製品番号                                | 説明                                                                             | 注釈                                                                                                |

|-------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| LTC3406A/<br>LTC3406B               | 600mA、1.5MHz同期整流式降圧DC/DCコンバータ                                                  | 効率:96%、VIN(MIN):2.5V~5.5V、VOUT(MIN) = 0.6V、IQ = 20µA、<br>ISD < 1µA、ThinSOT™パッケージ                  |

| LTC3407A-2                          | デュアル800mA/800mA、2.25MHz同期整流式降圧DC/DCコンバータ                                       | 効率:95%、VIN(MIN):2.5V~5.5V、VOUT(MIN) = 0.6V、IQ = 40µA、<br>ISD < 1µA、MS10Eおよび3mm×3mm DFN-10パッケージ    |

| LTC3409                             | 600mA、1.7MHz/2.6MHz同期整流式降圧DC/DCコンバータ                                           | 効率:96%、VIN(MIN):1.6V~5.5V、VOUT(MIN) = 0.6V、IQ = 65µA、<br>ISD < 1µA、3mm×3mm DFN-8パッケージ             |

| LTC3410/<br>LTC3410B                | 300mA、2.25MHz同期整流式降圧DC/DCコンバータ                                                 | 効率:95%、VIN(MIN):2.5V~5.5V、VOUT(MIN) = 0.8V、IQ = 26µA、<br>ISD < 1µA、SC70パッケージ                      |

| LTC3411A                            | 1.25A、4MHz同期整流式降圧DC/DCコンバータ                                                    | 効率:95%、VIN(MIN):2.5V~5.5V、VOUT(MIN) = 0.8V、IQ = 60µA、<br>ISD < 1µA、MS10および3mm×3mm DFN-10パッケージ     |

| LTC3412A                            | 2.5A、4MHz同期整流式降圧DC/DCコンバータ                                                     | 効率:95%、VIN(MIN):2.5V~5.5V、VOUT(MIN) = 0.8V、IQ = 60µA、<br>ISD < 1µA、4mm×4mm QFN-16、TSSOP-16Eパッケージ  |

| LTC3417A-2                          | デュアル1.5A/1A、4MHz同期整流式降圧DC/DCコンバータ                                              | 効率:95%、VIN(MIN):2.3V~5.5V、VOUT(MIN) = 0.8V、IQ = 125µA、<br>ISD < 1µA、TSSOP-16E、3mm×5mm DFN-16パッケージ |

| LTC3419/<br>LTC3419-1               | デュアル600mA/600mA、2.25MHz同期整流式降圧DC/DCコンバータ                                       | 効率:95%、VIN(MIN):2.5V~5.5V、VOUT(MIN) = 0.6V、IQ = 35µA、<br>ISD < 1µA、MS10および3mm×3mm DFN-10パッケージ     |

| LTC3542                             | 500mA、2.25MHz同期整流式降圧DC/DCコンバータ                                                 | 効率:95%、VIN(MIN):2.5V~5.5V、VOUT(MIN) = 0.6V、IQ = 26µA、<br>ISD < 1µA、2mm×2mm DFN-6およびThinSOTパッケージ   |

| LTC3544/<br>LTC3544B                | クワッド100mA/200mA/200mA/300mA、2.25MHz同期整流式降圧DC/DCコンバータ                           | 効率:95%、VIN(MIN):2.3V~5.5V、VOUT(MIN) = 0.8V、IQ = 70µA、<br>ISD < 1µA、3mm×3mm QFN-16パッケージ            |

| LTC3545/<br>LTC3545-1               | トリプル800mA×3、2.25MHz同期整流式降圧DC/DCコンバータ                                           | 効率:95%、VIN(MIN):2.3V~5.5V、VOUT(MIN) = 0.6V、IQ = 58µA、<br>ISD < 1µA、3mm×3mm QFN-16パッケージ            |

| LTC3547/<br>LTC3547B                | デュアル、300mA、2.25MHz同期整流式降圧DC/DCコンバータ                                            | 効率:95%、VIN(MIN):2.5V~5.5V、VOUT(MIN) = 0.6V、IQ = 40µA、<br>ISD < 1µA、DFN-8パッケージ                     |

| LTC3548/<br>LTC3548-1/<br>LTC3548-2 | デュアル、400mAと800mA I <sub>OUT</sub> 、2.25MHz同期整流式降圧DC/DCコンバータ                    | 効率:95%、VIN(MIN):2.5V~5.5V、VOUT(MIN) = 0.6V、IQ = 40µA、<br>ISD < 1µA、MS10Eおよび3mm×3mm DFN-10パッケージ    |

| LTC3560                             | 800mA、2.25MHz同期整流式降圧DC/DCコンバータ                                                 | 効率:95%、VIN(MIN):2.5V~5.5V、VOUT(MIN) = 0.6V、IQ = 16µA、<br>ISD < 1µA、ThinSOTパッケージ                   |

| LTC3561                             | 1.25A、4MHz同期整流式降圧DC/DCコンバータ                                                    | 効率:95%、VIN(MIN):2.5V~5.5V、VOUT(MIN) = 0.8V、IQ = 240µA、<br>ISD < 1µA、3mm×3mm DFN-8パッケージ            |

| LTC3562                             | クワッド、I <sup>2</sup> Cインターフェース、600mA/600mA/400mA/400mA、2.25MHz同期整流式降圧DC/DCコンバータ | 効率:95%、VIN(MIN):2.9V~5.5V、VOUT(MIN) = 0.425V、IQ = 100µA、<br>ISD < 1µA、3mm×3mm QFN-20パッケージ         |

ThinSOTはリニアテクノロジー社の商標です。