## 特長

- 広い入力電圧範囲: 2.7V ~ 40V

- 広い出力電圧範囲: 2.7V ~ 40V

- 出力電流 ( $V_{IN} \geq 3.6V$ 、 $V_{OUT} = 5V$ ): 1A

- 出力電流 ( $V_{IN} \geq 6V$  の降圧動作時): 2A

- プログラム可能な周波数: 100kHz ~ 2MHz

- 最大 2MHz まで外部クロックと同期可能

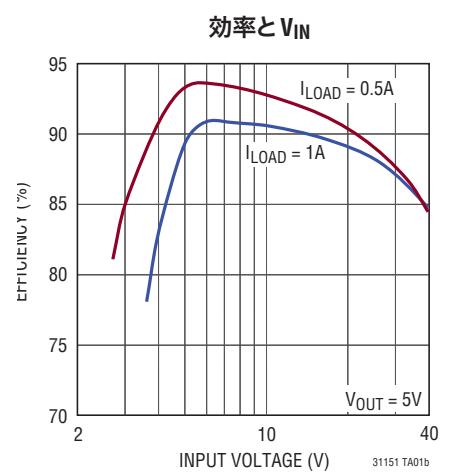

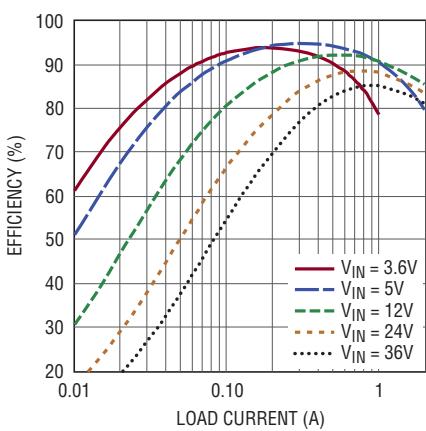

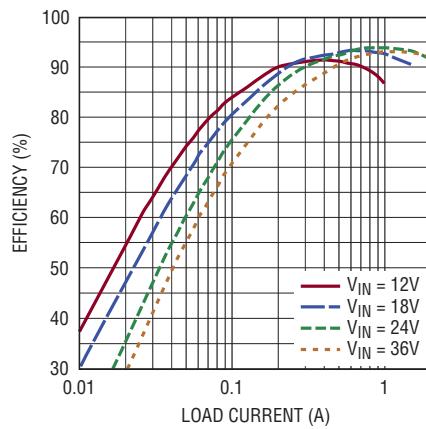

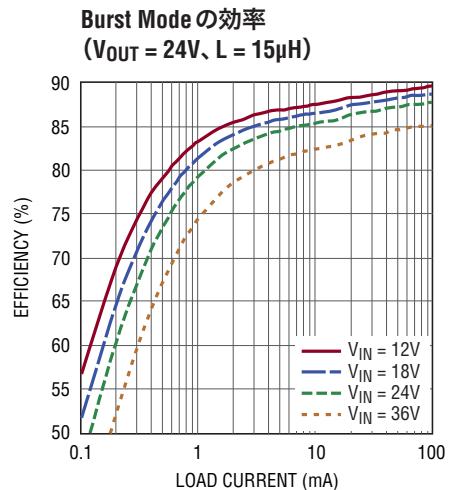

- 効率: 最大 95%

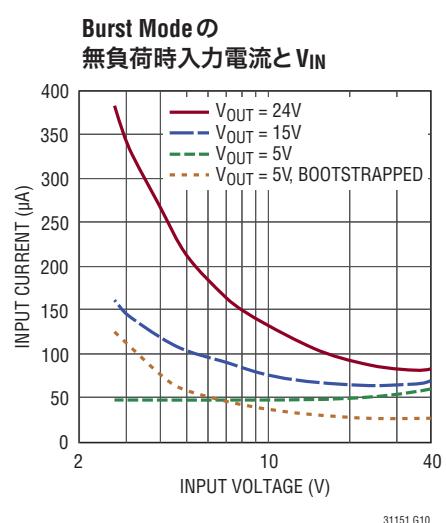

- Burst Mode® 動作時の無負荷時静止電流: 30µA

- 超低ノイズの昇降圧 PWM

- 内部ソフトスタート

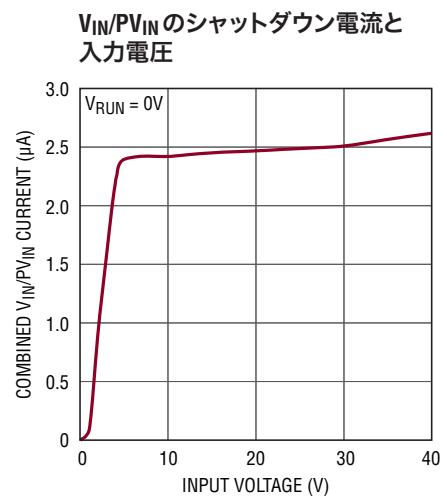

- シャットダウン時の電源電流: 3µA

- 入力の低電圧ロックアウトをプログラム可能

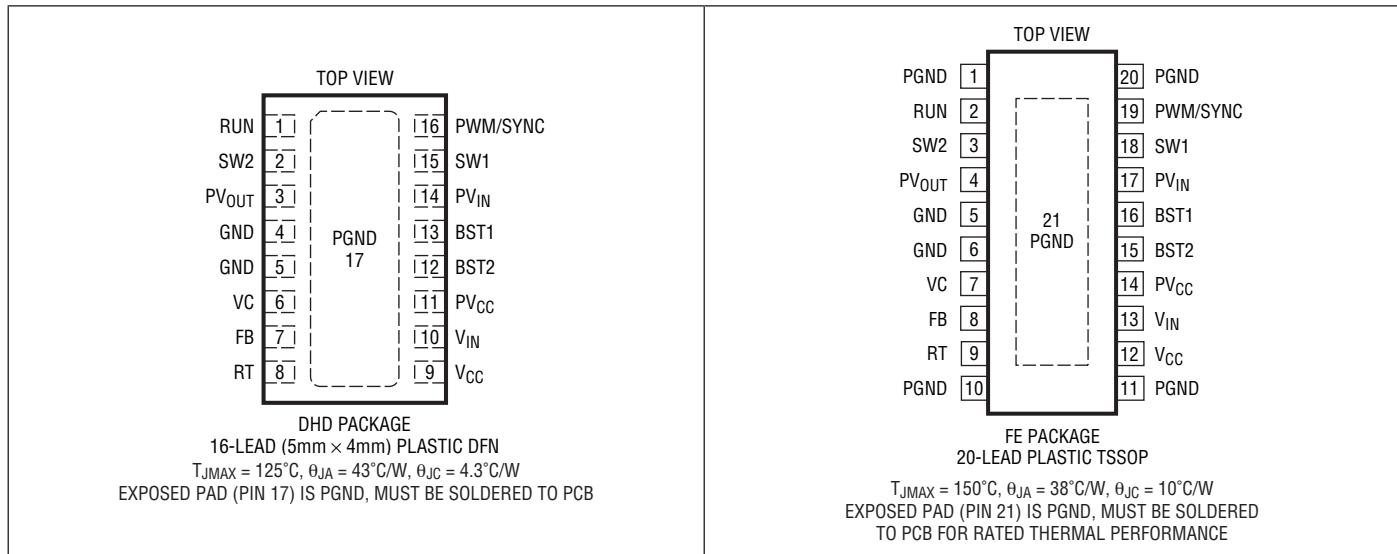

- 小型 4mm×5mm×0.75mm DFN パッケージ

- 熱特性が改善された 20 ピン TSSOP パッケージ

## アプリケーション

- 24V/28V 産業用アプリケーション

- 自動車用電源システム

- 通信機器、サーバおよびネットワーク機器

- FireWire レギュレータ

- 複数電源供給装置

## 概要

LTC®3115-1 は高電圧モノリシック同期整流式昇降圧 DC/DC コンバータです。入力電圧範囲および出力電圧範囲が 2.7V ~ 40V と広いので、幅広い自動車用アプリケーションや産業用アプリケーションに最適です。独自の低ノイズ・スイッチング・アルゴリズムにより、入力電圧が出力電圧を上回るまたは下回る、あるいは出力電圧と等しい場合でも、効率が最適化され、動作モード間の移行がシームレスに行われます。

プログラム可能な周波数 PWM モード動作により、低ノイズ、高効率の動作を実現し、スイッチングを外部クロックに同期可能です。最大 2MHz のスイッチング周波数に対応し、値の小さいインダクタを使用可能なので、アプリケーション回路を小型化できます。また、ピンで選択可能な Burst Mode 動作によりスタンバイ電流が減少し、軽負荷時の効率が向上します。シャットダウン電流が 3µA であることと合わせて、LTC3115-1 はバッテリ駆動アプリケーションに最適です。この他に、シャットダウン時の出力切断、短絡保護、内部ソフトスタートを特長としています。LTC3115-1 は熱特性が改善された 4mm×5mm ×0.75mm の 16 ピン DFN パッケージと 20 ピン TSSOP パッケージで供給されます。

**L**、**LT**、**LTC**、**LTM**、**Burst Mode**、**LTspice**、**Linear Technology** および **Linear** のロゴはリニアテクノロジー社の登録商標です。No RSENSE はリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。6404251、6166527、その他出願中を含む米国特許によって保護されています。

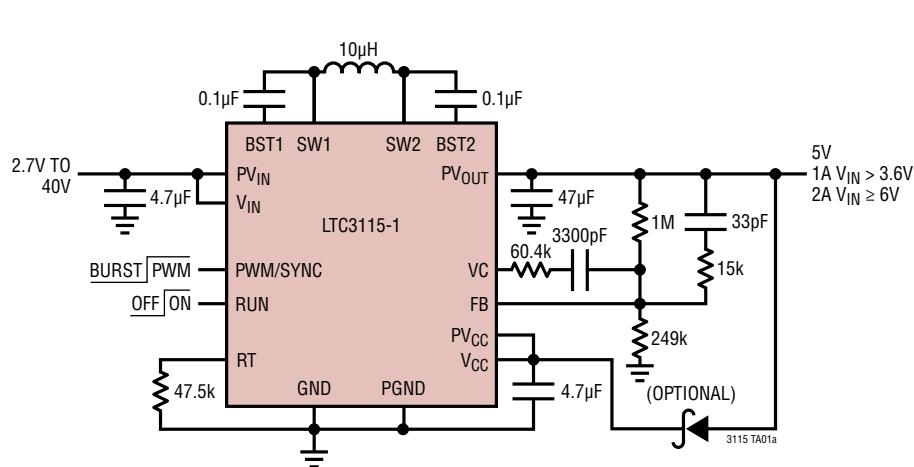

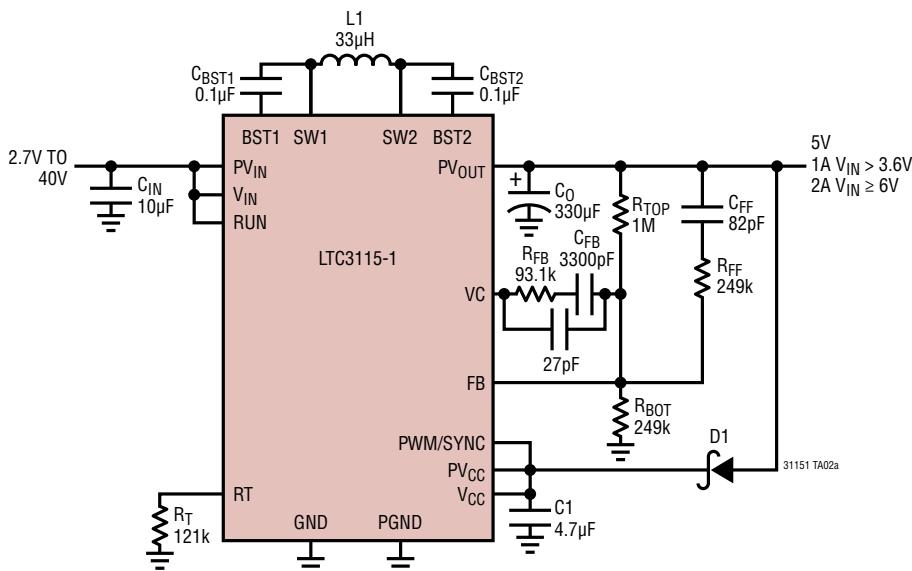

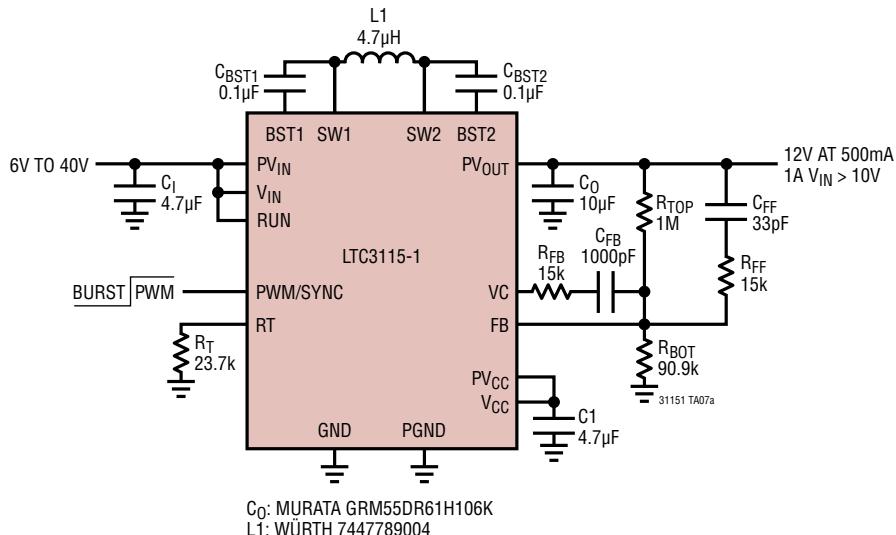

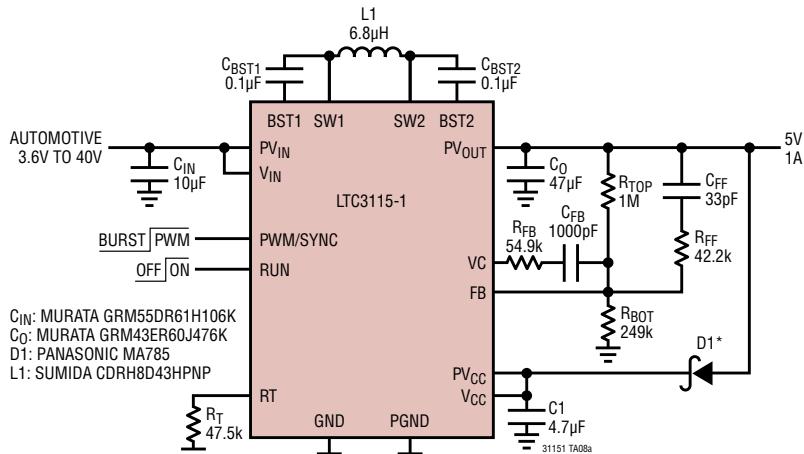

## 標準的応用例

## 絶対最大定格 (Note 1)

|                                         |                                         |                             |               |

|-----------------------------------------|-----------------------------------------|-----------------------------|---------------|

| $V_{IN}$ 、 $PV_{IN}$ 、 $PV_{OUT}$ ..... | -0.3V ~ 45V                             | $V_{PWM/SYNC}$ .....        | -0.3V ~ 6V    |

| $V_{SW1}$                               |                                         | 電圧、他のすべてのピン .....           | -0.3V ~ 6V    |

| DC .....                                | -0.3V ~ ( $PV_{IN}$ + 0.3V)             | 動作接合部温度範囲 (Note 2, 4)       |               |

| パルス (<100ns) .....                      | -1.5V ~ ( $PV_{IN}$ + 1.5V)             | LTC3115E-1/LTC3115I-1 ..... | -40°C ~ 125°C |

| $V_{SW2}$                               |                                         | LTC3115H-1 .....            | -40°C ~ 150°C |

| DC .....                                | -0.3V ~ ( $PV_{OUT}$ + 0.3V)            | LTC3115MP-1 .....           | -55°C ~ 150°C |

| パルス (<100ns) .....                      | -1.5V ~ ( $PV_{OUT}$ + 1.5V)            | 保存温度範囲 .....                | -65°C ~ 150°C |

| $V_{RUN}$ .....                         | -0.3V ~ ( $V_{IN}$ + 0.3V)              | リード温度 (半田付け、10秒) .....      |               |

| $V_{BST1}$ .....                        | ( $V_{SW1}$ - 0.3V) ~ ( $V_{SW1}$ + 6V) | FE .....                    | 300°C         |

| $V_{BST2}$ .....                        | ( $V_{SW2}$ - 0.3V) ~ ( $V_{SW2}$ + 6V) |                             |               |

## ピン配置

## 発注情報

| 無鉛仕上げ             | テープアンドリール           | 製品マーキング*    | パッケージ                           | 温度範囲           |

|-------------------|---------------------|-------------|---------------------------------|----------------|

| LTC3115EDHD-1#PBF | LTC3115EDHD-1#TRPBF | 31151       | 16-Lead (5mm × 4mm) Plastic DFN | -40°C to 125°C |

| LTC3115IDHD-1#PBF | LTC3115IDHD-1#TRPBF | 31151       | 16-Lead (5mm × 4mm) Plastic DFN | -40°C to 125°C |

| LTC3115EFE-1#PBF  | LTC3115EFE-1#TRPBF  | LTC3115FE-1 | 20-Lead Plastic TSSOP           | -40°C to 125°C |

| LTC3115IFE-1#PBF  | LTC3115IFE-1#TRPBF  | LTC3115FE-1 | 20-Lead Plastic TSSOP           | -40°C to 125°C |

| LTC3115HFE-1#PBF  | LTC3115HFE-1#TRPBF  | LTC3115FE-1 | 20-Lead Plastic TSSOP           | -40°C to 150°C |

| LTC3115MPFE-1#PBF | LTC3115MPFE-1#TRPBF | LTC3115FE-1 | 20-Lead Plastic TSSOP           | -55°C to 150°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全規定動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 2)。注記がない限り、 $PV_{\text{IN}}=V_{\text{IN}}=24\text{V}$ 、 $PV_{\text{OUT}}=5\text{V}$

| PARAMETER                                               | CONDITIONS                                                                                                                                        | MIN                                         | TYP                               | MAX  | UNITS                                                                        |   |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------|------|------------------------------------------------------------------------------|---|

| Input Operating Voltage                                 |                                                                                                                                                   | ● 2.7                                       | 40                                |      | V                                                                            |   |

| Output Operating Voltage                                |                                                                                                                                                   | ● 2.7                                       | 40                                |      | V                                                                            |   |

| Input Undervoltage Lockout Threshold                    | $V_{\text{IN}}$ Falling<br>$V_{\text{IN}}$ Rising<br>$V_{\text{IN}}$ Rising ( $0^\circ\text{C}$ to $125^\circ\text{C}$ )                          | ● 2.4<br>● 2.6<br>● 2.7<br>● 2.8<br>● 2.725 | 2.7<br>2.6<br>2.7<br>2.8<br>2.725 |      | V                                                                            |   |

| Input Undervoltage Lockout Hysteresis                   |                                                                                                                                                   |                                             | 100                               |      | mV                                                                           |   |

| $V_{\text{CC}}$ Undervoltage Lockout Threshold          | $V_{\text{CC}}$ Falling                                                                                                                           | ● 2.4                                       | 2.6                               |      | V                                                                            |   |

| $V_{\text{CC}}$ Undervoltage Lockout Hysteresis         |                                                                                                                                                   |                                             | 200                               |      | mV                                                                           |   |

| Input Current in Shutdown                               | $V_{\text{RUN}} = 0\text{V}$                                                                                                                      |                                             | 3                                 | 10   | $\mu\text{A}$                                                                |   |

| Input Quiescent Current in Burst Mode Operation         | $V_{\text{FB}} = 1.1\text{V}$ (Not Switching), $V_{\text{PWM/SYNC}} = \text{Low}$                                                                 |                                             | 50                                |      | $\mu\text{A}$                                                                |   |

| Oscillator Frequency                                    | $R_T = 35.7\text{k}$ , $V_{\text{PWM/SYNC}} = \text{High}$                                                                                        | ● 900                                       | 1000                              | 1100 | kHz                                                                          |   |

| Oscillator Operating Frequency                          | $V_{\text{PWM/SYNC}} = \text{High}$                                                                                                               | ● 100                                       | 2000                              |      | kHz                                                                          |   |

| PWM/SYNC Clock Input Frequency                          |                                                                                                                                                   | ● 100                                       | 2000                              |      | kHz                                                                          |   |

| PWM/SYNC Input Logic Threshold                          |                                                                                                                                                   | ● 0.5                                       | 1.0                               | 1.5  | V                                                                            |   |

| Soft-Start Duration                                     |                                                                                                                                                   |                                             | 9                                 |      | ms                                                                           |   |

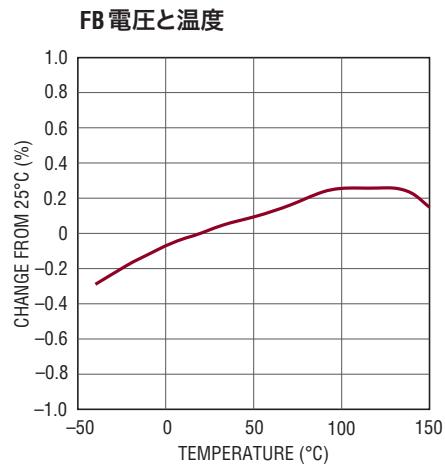

| Feedback Voltage                                        |                                                                                                                                                   | ● 977                                       | 1000                              | 1017 | mV                                                                           |   |

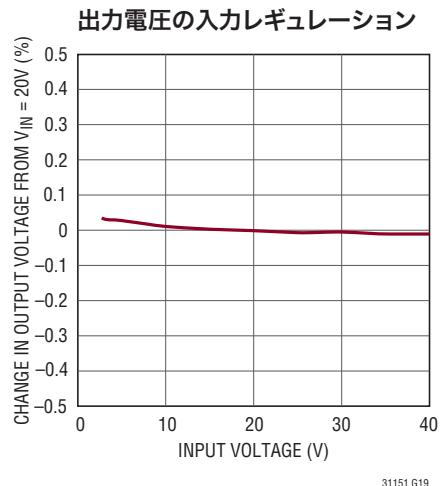

| Feedback Voltage Line Regulation                        | $V_{\text{IN}} = 2.7\text{V}$ to $40\text{V}$                                                                                                     |                                             | 0.1                               |      | %                                                                            |   |

| Feedback Pin Input Current                              |                                                                                                                                                   |                                             | 1                                 | 50   | nA                                                                           |   |

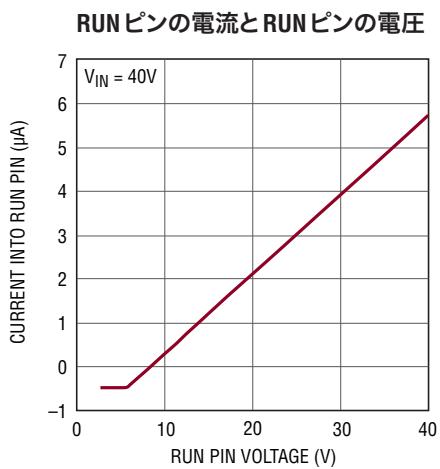

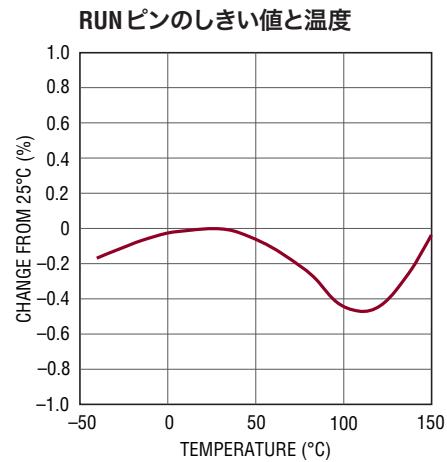

| RUN Pin Input Logic Threshold                           |                                                                                                                                                   | ● 0.3                                       | 0.8                               | 1.1  | V                                                                            |   |

| RUN Pin Comparator Threshold                            | $V_{\text{RUN}}$ Rising                                                                                                                           | ● 1.16                                      | 1.21                              | 1.26 | V                                                                            |   |

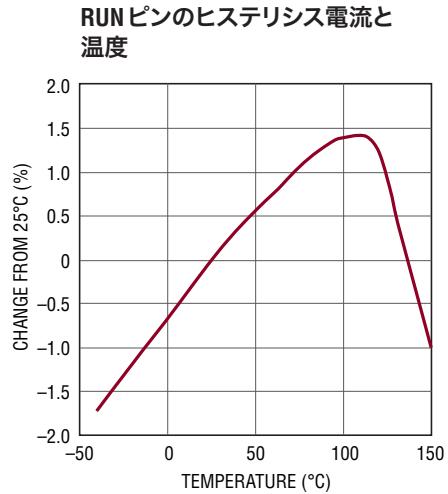

| RUN Pin Hysteresis Current                              |                                                                                                                                                   |                                             | 500                               |      | nA                                                                           |   |

| RUN Pin Hysteresis Voltage                              |                                                                                                                                                   |                                             | 100                               |      | mV                                                                           |   |

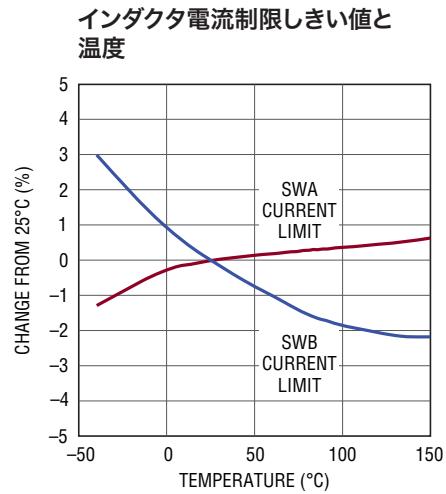

| Inductor Current Limit                                  | (Note 3)                                                                                                                                          | ● 2.4                                       | 3.0                               | 3.7  | A                                                                            |   |

| Reverse Inductor Current Limit                          | Current into $PV_{\text{OUT}}$ (Note 3)                                                                                                           |                                             | 1.5                               |      | A                                                                            |   |

| Burst Mode Inductor Current Limit                       | (Note 3)                                                                                                                                          |                                             | 0.65                              | 1.0  | 1.35                                                                         | A |

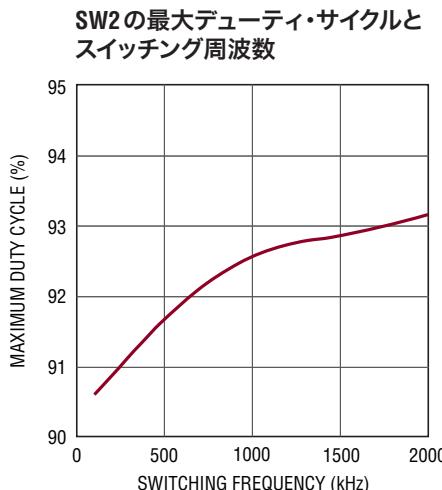

| Maximum Duty Cycle                                      | Percentage of Period SW2 is Low in Boost Mode,<br>$R_T = 35.7\text{k}$ (Note 5)                                                                   | ● 90                                        | 95                                |      | %                                                                            |   |

| Minimum Duty Cycle                                      | Percentage of Period SW1 is High in Buck Mode,<br>$R_T = 35.7\text{k}$ (Note 5)                                                                   | ● 0                                         |                                   | 0    | %                                                                            |   |

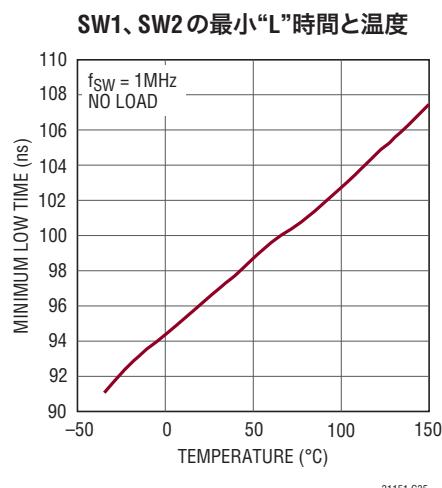

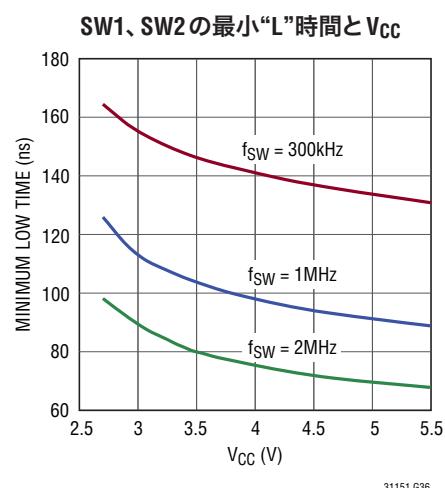

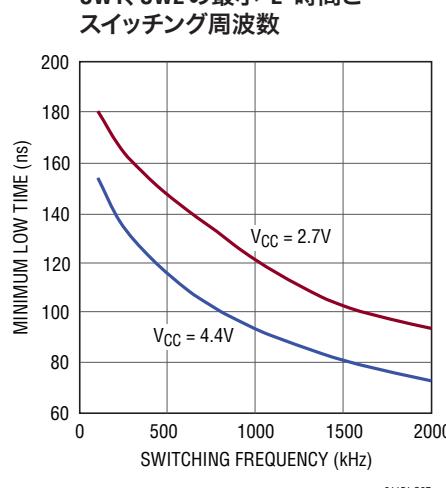

| SW1, SW2 Minimum Low Time                               | $R_T = 35.7\text{k}$ (Note 5)                                                                                                                     |                                             | 100                               |      | ns                                                                           |   |

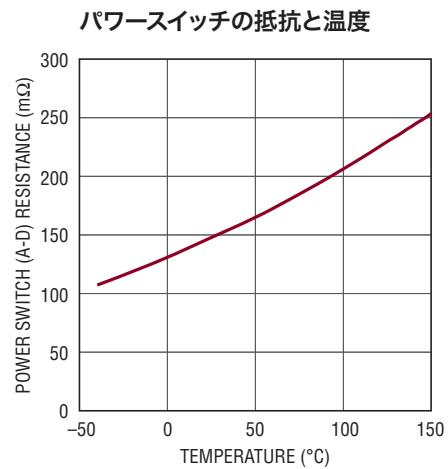

| N-Channel Switch Resistance                             | Switch A (From $PV_{\text{IN}}$ to SW1)<br>Switch B (From SW1 to PGND)<br>Switch C (From SW2 to PGND)<br>Switch D (From $PV_{\text{OUT}}$ to SW2) |                                             | 150<br>150<br>150<br>150          |      | $\text{m}\Omega$<br>$\text{m}\Omega$<br>$\text{m}\Omega$<br>$\text{m}\Omega$ |   |

| N-Channel Switch Leakage                                | $PV_{\text{IN}} = PV_{\text{OUT}} = 40\text{V}$                                                                                                   |                                             | 0.1                               | 10   | $\mu\text{A}$                                                                |   |

| $PV_{\text{CC}}/V_{\text{CC}}$ External Forcing Voltage |                                                                                                                                                   |                                             | 4.58                              | 5.5  | V                                                                            |   |

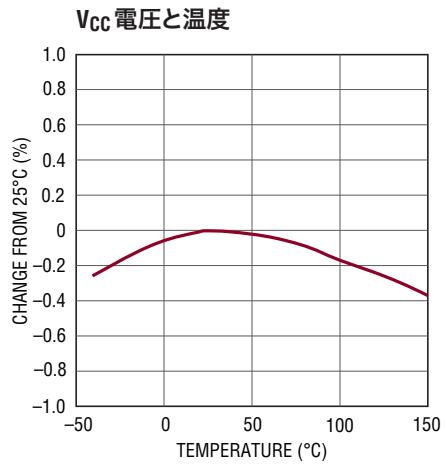

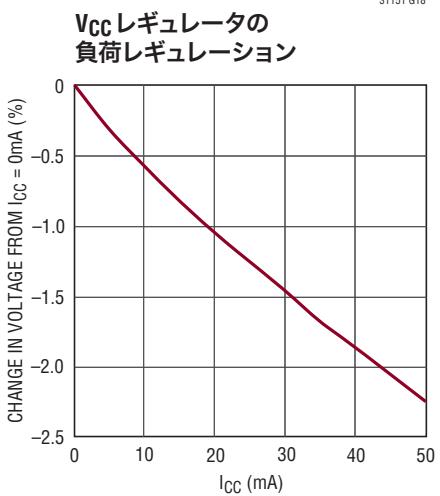

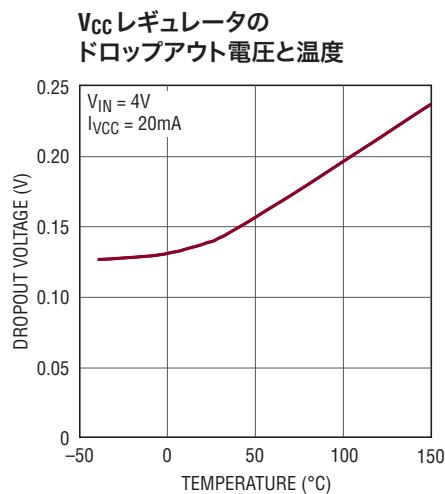

| $V_{\text{CC}}$ Regulation Voltage                      | $I_{\text{VCC}} = 1\text{mA}$                                                                                                                     |                                             | 4.33                              | 4.45 | 4.58                                                                         | V |

| $V_{\text{CC}}$ Load Regulation                         | $I_{\text{VCC}} = 1\text{mA}$ to $20\text{mA}$                                                                                                    |                                             | 1.2                               |      | %                                                                            |   |

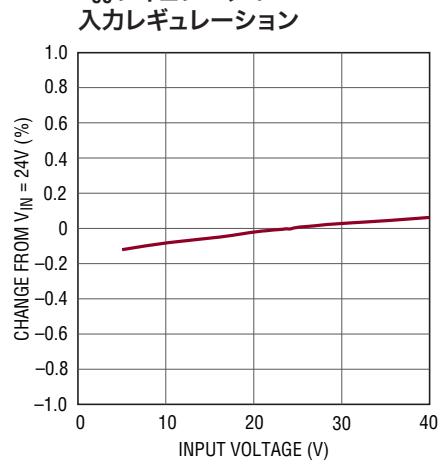

| $V_{\text{CC}}$ Line Regulation                         | $I_{\text{VCC}} = 1\text{mA}$ , $V_{\text{IN}} = 5\text{V}$ to $40\text{V}$                                                                       |                                             | 0.5                               |      | %                                                                            |   |

| $V_{\text{CC}}$ Current Limit                           | $V_{\text{CC}} = 2.5\text{V}$                                                                                                                     |                                             | 50                                | 110  | mA                                                                           |   |

| $V_{\text{CC}}$ Dropout Voltage                         | $I_{\text{VCC}} = 5\text{mA}$ , $V_{\text{IN}} = 2.7\text{V}$                                                                                     |                                             | 50                                |      | mV                                                                           |   |

| $V_{\text{CC}}$ Reverse Current                         | $V_{\text{CC}} = 5\text{V}$ , $V_{\text{IN}} = 3.6\text{V}$                                                                                       |                                             | 10                                |      | $\mu\text{A}$                                                                |   |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** LTC3115-1は $T_J$ が $T_A$ にほぼ等しいパルス負荷条件でテストされる。LTC3115E-1は、 $0^\circ\text{C}$ ～ $85^\circ\text{C}$ の接合部温度で仕様に適合することが保証されている。 $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の動作接合部温度範囲での仕様は設計、特性評価および統計的なプロセス・コントロールとの相関で確認されている。LTC3115H-1の仕様は $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の動作接合部温度範囲で保証されている。LTC3115MP-1の仕様は $-55^\circ\text{C}$ ～ $150^\circ\text{C}$ の動作接合部温度範囲で保証されている。高い接合部温度は動作寿命に悪影響を及ぼす。接合部温度が $125^\circ\text{C}$ を超えると、動作寿命は短くなる。

合部温度範囲での仕様は設計、特性評価および統計的なプロセス・コントロールとの相関で確認されている。LTC3115H-1の仕様は $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の動作接合部温度範囲で保証されている。LTC3115MP-1の仕様は $-55^\circ\text{C}$ ～ $150^\circ\text{C}$ の動作接合部温度範囲で保証されている。高い接合部温度は動作寿命に悪影響を及ぼす。接合部温度が $125^\circ\text{C}$ を超えると、動作寿命は短くなる。

## 電気的特性

これらの仕様と調和する最大周囲温度は、基板レイアウト、パッケージの定格熱抵抗および他の環境要因と関連した特定の動作条件によって決まる。

接合部温度( $T_J$  (°C))は周囲温度( $T_A$  (°C))および電力損失( $P_D$  (W))から次式に従って計算される。

$$T_J = T_A + (P_D \cdot \theta_{JA})$$

ここで、 $\theta_{JA}$ はパッケージの熱インピーダンス。

**Note 3:** 電流の測定は、LTC3115-1がスイッチング動作を行っていないときに行われる。動作時に測定された電流制限値は、コンバレータの伝搬遅延のためにいくらか大きめの値となる。

**Note 4:** このデバイスには短時間の過負荷状態の間デバイスを保護するための過熱保護機能が備わっている。この保護が動作しているときは、最大定格接合部温度を超える。規定された絶対最大動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なうか、またはデバイスに永続的損傷を与える恐れがある。

**Note 5:** スイッチ・タイミングの測定は開ループ・テスト構成で行われる。スイッチ・ピンの電圧がインダクタ電流の大きさと方向に左右される場合、非重複期間の間スイッチ・ピンに電圧差が生じることにより、アプリケーションのタイミングがこれらの値からいくらか変化する可能性がある。

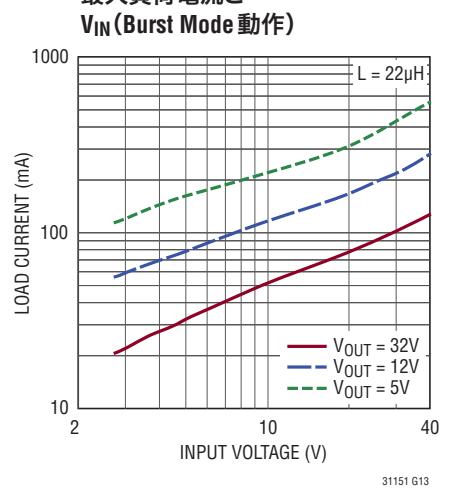

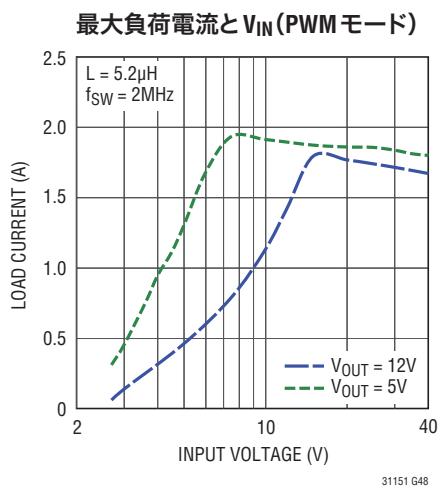

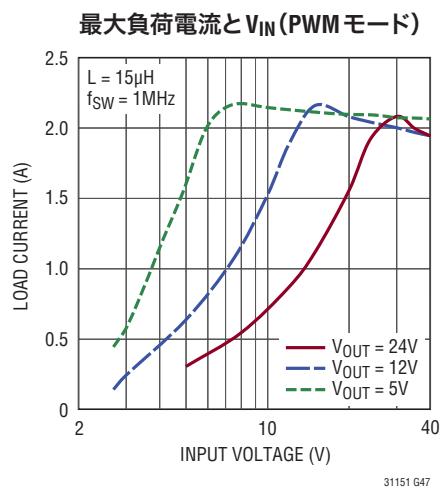

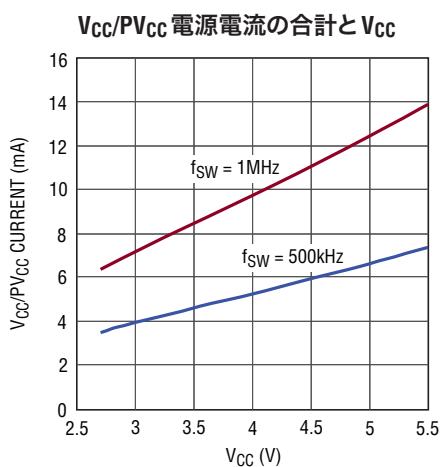

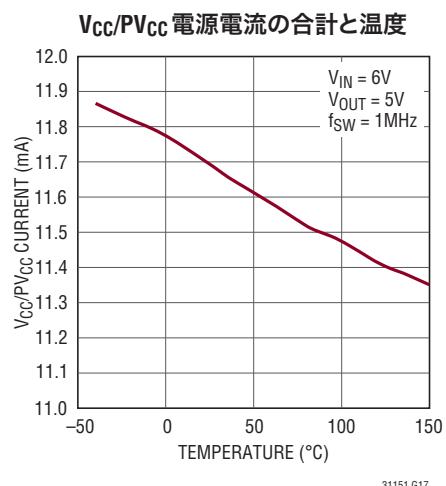

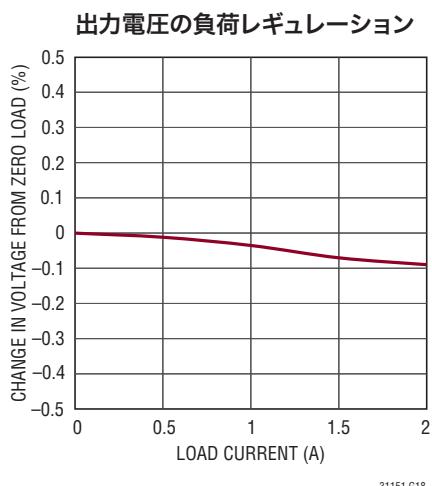

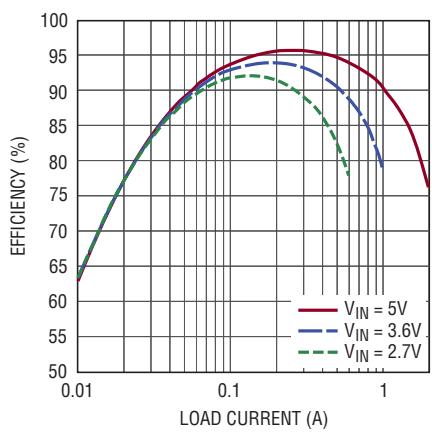

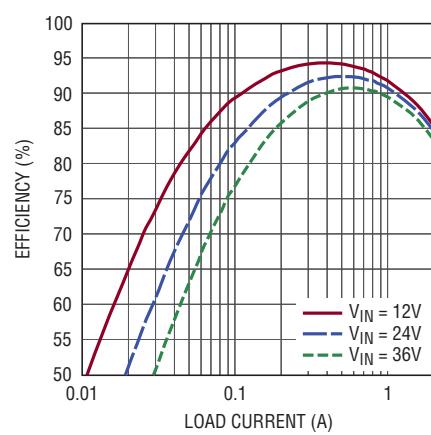

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

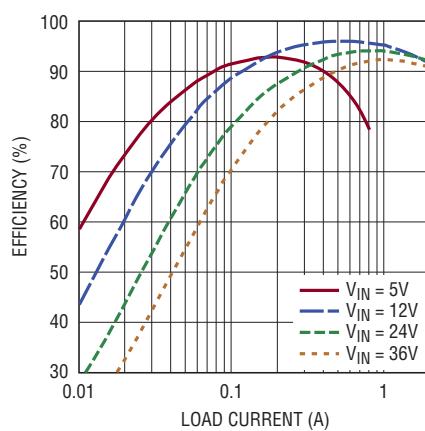

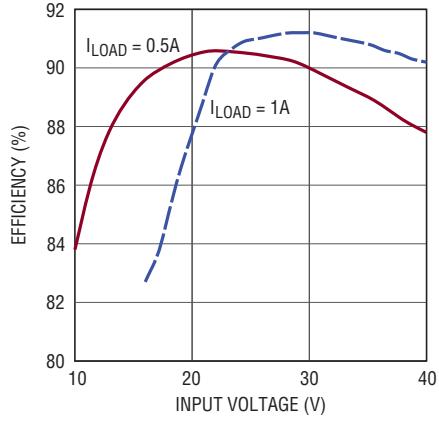

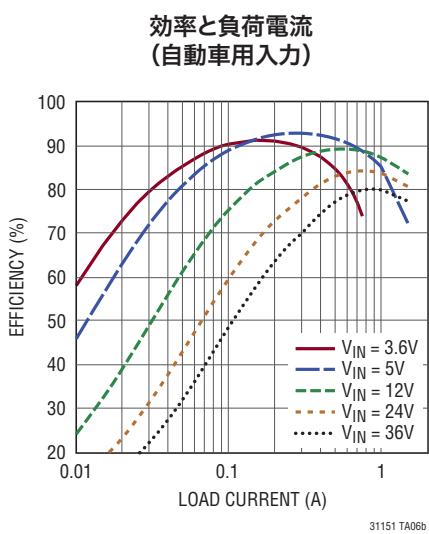

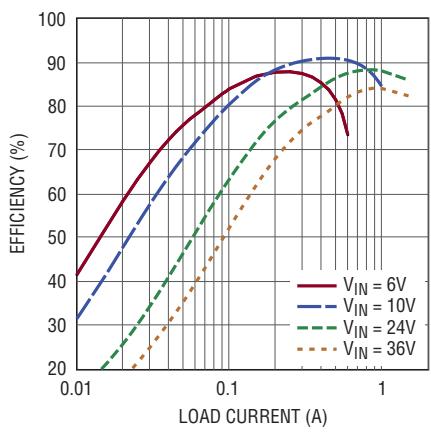

PWM モードの効率( $V_{OUT} = 5\text{V}$ 、 $f_{SW} = 500\text{kHz}$ 、ブートストラップなし)

PWM モードの効率

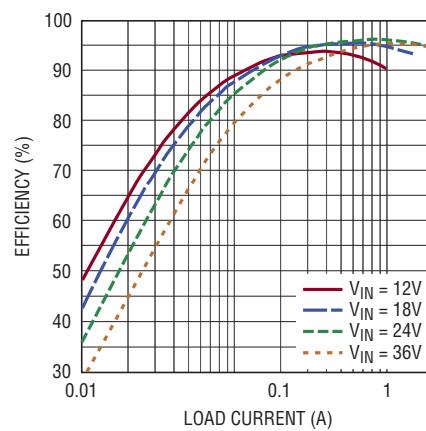

( $V_{OUT} = 12\text{V}$ 、 $f_{SW} = 500\text{kHz}$ )

PWM モードの効率

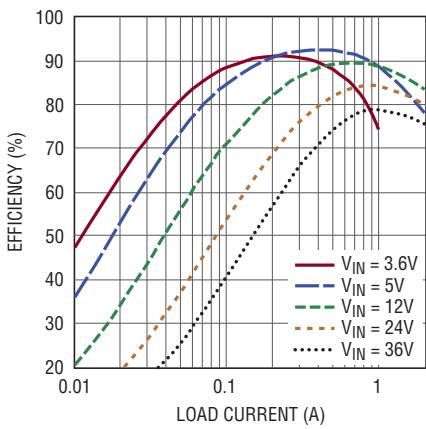

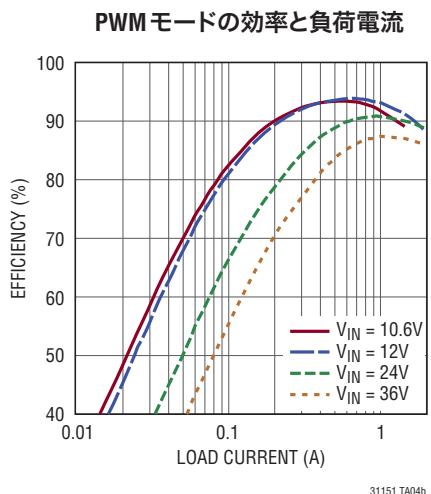

( $V_{OUT} = 24\text{V}$ 、 $f_{SW} = 500\text{kHz}$ )

PWM モードの効率( $V_{OUT} = 5\text{V}$ 、 $f_{SW} = 1\text{MHz}$ 、ブートストラップなし)

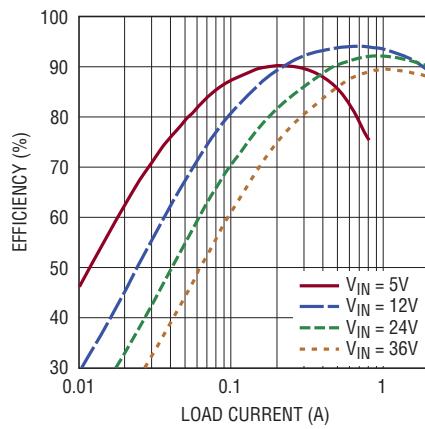

PWM モードの効率

( $V_{OUT} = 12\text{V}$ 、 $f_{SW} = 1\text{MHz}$ )

PWM モードの効率

( $V_{OUT} = 24\text{V}$ 、 $f_{SW} = 1\text{MHz}$ )

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

31151 G14

31151 G15

31151 G16

31151 G17

31151 G18

31151 G19

31151 G20

31151 G21

31151 G22

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

31151 G32

31151 G33

31151 G34

31151 G35

31151 G36

31151 G37

31151 G38

31151 G49

31151 G50

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

## ピン機能 (DHD/FE)

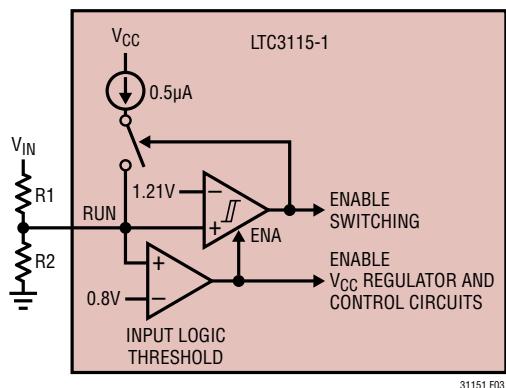

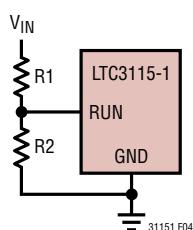

**RUN (ピン1/ピン2)** : デバイスのイネーブルとディスエーブル、および個別の入力UVLOしきい値の設定を行う入力。RUNピンを外部ロジック信号によってドライブすることにより、デバイスのイネーブルとディスエーブルを行うことができます。また、高精度な低電圧ロックアウトしきい値を生成するために、入力電圧に接続された抵抗分割器によってこのピンの電圧を設定することができます。RUNピンの電圧が公称1.21Vを超えると、デバイスはイネーブルされます。イネーブルされると、RUNピンによって0.5μAの電流がソースされてヒステリシスが生成されます。デバイスを継続的にイネーブルするために、このピンを入力電圧に直接接続することができます。どのような場合でも、RUNピンをVINより0.3V以上高い電圧に強制することはできません。

**SW2 (ピン2/ピン3)** : 昇降圧コンバータのパワースイッチ・ピン。このピンは昇降圧インダクタの片側に接続します。

**PVOUT (ピン3/ピン4)** : 昇降圧コンバータの電力出力。このピンは少なくとも10μFの低ESRコンデンサに接続します。コンデンサはできるだけデバイスの近くに配置し、グランドまでのリターン・パスを短くします。出力の過負荷状態や短絡状態を生じやすいVOUTが20Vより高いアプリケーションでは、SW2(アノード)からPVOUT(カソード)にショットキ・ダイオードを接続することを推奨します。誘導性負荷によって出力短絡を生じやすいアプリケーションでは、グランド(アノード)からPVOUT(カソード)にショットキ・ダイオードを接続し、短絡トランジエント時にPVOUTがグランドより下にドライブされる範囲を制限することを推奨します。

**GND (ピン4、5/ピン5、6)** : 信号グランド。これらのピンは、デバイスの制御回路のグランドに接続されているので、アプリケーションのグランドに接続する必要があります。

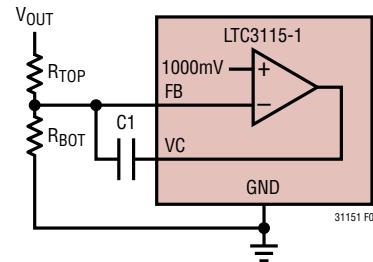

**VC (ピン6/ピン7)** : エラーアンプの出力。このピンとFBの間に周波数補償ネットワークを接続し、電圧制御ループを安定化させる必要があります。

**FB (ピン7/ピン8)** : 帰還電圧の入力。このピンに接続された抵抗分割器によって昇降圧コンバータの出力電圧が設定されます。公称FB電圧は1000mVです。スイッチ・ピンのトレースへの浮遊結合を最小限に抑えるため、このピンに接続する配線には注意する必要があります。

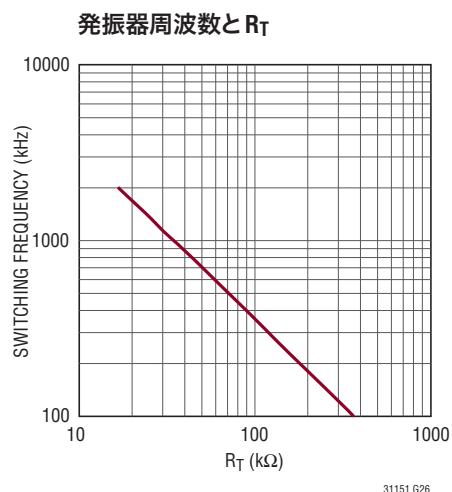

**RT (ピン8/ピン9)** : 発振器周波数の設定ピン。このピンとグランドの間に接続された抵抗により、昇降圧コンバータのスイッチング周波数が設定されます。

**V<sub>CC</sub> (ピン9/ピン12)** : デバイスの制御回路用低電源入力。このピンはデバイスの内部制御回路に給電するので、アプリケーションではPV<sub>CC</sub>ピンに接続する必要があります。このピンとグランドの間に4.7μF以上のバイパス・コンデンサを接続します。アプリケーションではV<sub>CC</sub>ピンとPV<sub>CC</sub>ピンを相互接続する必要があります。

**V<sub>IN</sub> (ピン10/ピン13)** : 内部回路およびV<sub>CC</sub>レギュレータ用の電源接続ピン。このピンは内部V<sub>CC</sub>レギュレータの給電と、VIN除算器の入力電圧検出接続に使用されます。このピンとグランドの間に0.1μFのバイパス・コンデンサを接続します。バイパス・コンデンサはできるだけデバイスの近くに配置し、グランドまでのリターン・パスを短くします。

**PV<sub>CC</sub> (ピン11/ピン14)** : 内部V<sub>CC</sub>レギュレータの出力。このピンはVINからV<sub>CC</sub>レールを生成する内部リニア・レギュレータの出力ピンです。PV<sub>CC</sub>ピンはパワースイッチのゲート・ドライバ用の電源接続ピンにもなります。PV<sub>CC</sub>をV<sub>CC</sub>に接続するトレースを短くできない場合、このピンとグランドの間に追加のバイパス・コンデンサを接続します。アプリケーションではV<sub>CC</sub>ピンとPV<sub>CC</sub>ピンを相互接続する必要があります。

**BST2 (ピン12/ピン15)** : SW2のフライング・コンデンサ・ピン。このピンは0.1μFのコンデンサを介してSW2に接続する必要があります。このピンを使ってパワースイッチDのゲート駆動レールを生成します。

**BST1 (ピン13/ピン16)** : SW1のタイミング・コンデンサ・ピン。このピンは0.1μFのコンデンサを介してSW1に接続する必要があります。このピンを使ってパワースイッチAのゲート駆動レールを生成します。

**PV<sub>IN</sub> (ピン14/ピン17)** : 昇降圧コンバータの電源入力。このピンとグランドの間に4.7μF以上のバイパス・コンデンサを接続します。バイパス・コンデンサはできるだけデバイスの近くに配置し、ビアをグランド・プレーンまで直接通します。長いリード線を介して給電するか、または高ESRの電源から給電するときは、より大きなバルク入力コンデンサ(標準で47μF～100μF)が必要になる場合があります。

**SW1 (ピン15/ピン18)** : 昇降圧コンバータのパワースイッチ・ピン。このピンは昇降圧インダクタの片側に接続します。

## ピン機能 (DHD/FE)

**PWM/SYNC (ピン16/ピン19)** : Burst Mode/PWMモードの制御ピンおよび同期入力。このピンを“H”に強制すると、デバイスは、すべての負荷でRTピンによって設定される周波数の内部発振器を使った固定周波数PWMモードで動作します。このピンを“L”に強制すると、デバイスはBurst Mode動作になり、軽負荷時の効率が改善されてスタンバイ電流が低減されます。このピンに外部クロック信号を接続すると、昇降圧コンバータは、固定周波数PWMモード動作を使ってスイッチングを外部クロックに同期させます。与えるクロックのパルス幅(負または正)は少なくとも100nsが必要です。PWM/SYNCピンの最大動作電圧は5.5Vです。PWM/SYNCピンをV<sub>CC</sub>に接続することで、このピンを持続的に“H”に強制することができます。

**PGND (露出パッドのピン17/ピン1、10、11、20、露出パッドのピン21)** : 電源グランド接続ピン。これらのピンはアプリケーションの電源グランドに接続します。露出パッドは電源グランドに接続されています。露出パッドは、PCBに半田付けし、できるだけ短く最小のインピーダンスの接続を介して電気的にグランドに接続する必要があり、最適な熱性能を引き出すためにPCBのグランド・プレーンに接続します。

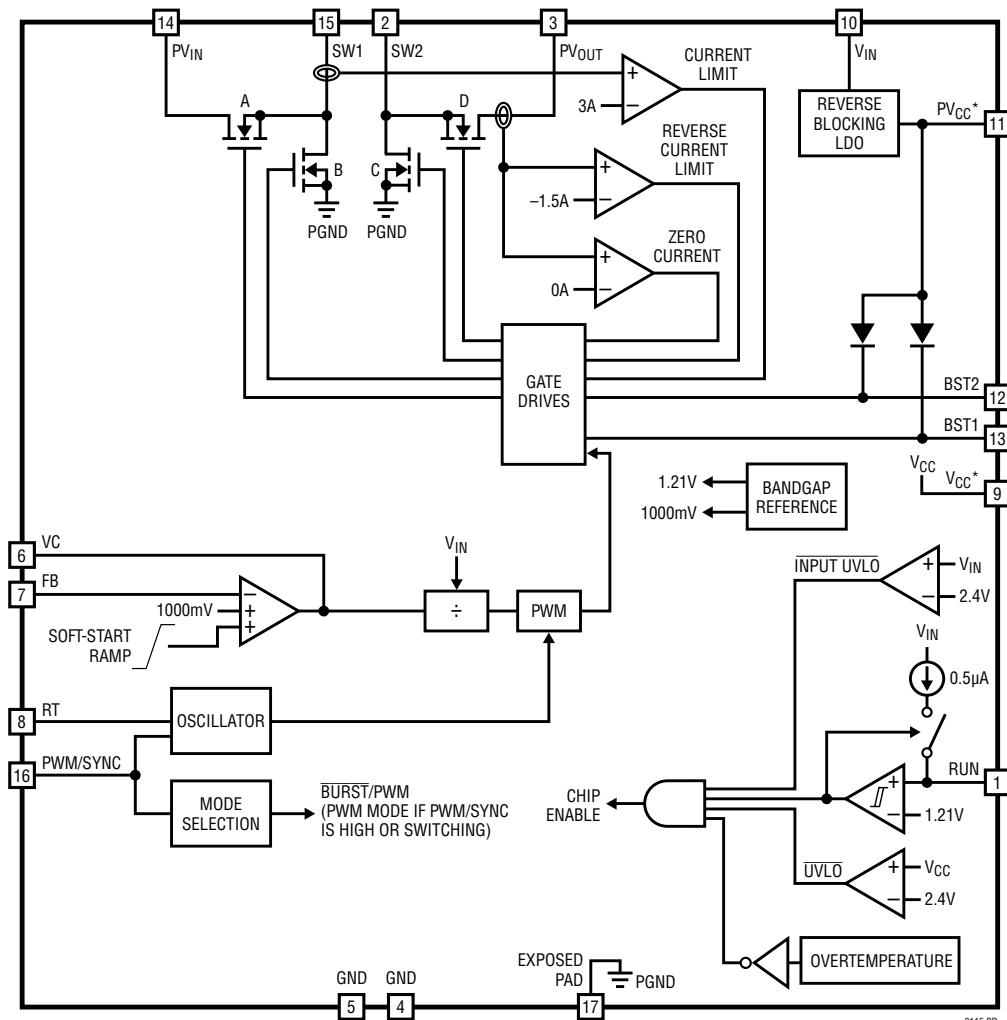

ブロック図 ピン番号はDHDパッケージのみを示す。

## 動作

### はじめに

LTC3115-1は、最小2.7Vから最大40Vの入力および出力電圧で動作可能なモノリシック昇降圧コンバータです。4個の内部低抵抗NチャネルDMOSスイッチにより、アプリケーション回路のサイズが最小限に抑えられ、電力損失が低減されて効率が最大化されます。2個の小容量外付けコンデンサの追加のみを必要とする内部ハイサイド・ゲート・ドライバにより、設計プロセスがさらに簡素化されます。独自のスイッチ制御アルゴリズムにより、昇降圧コンバータは、入力電圧が出力電圧を上回るまたは下回る、あるいは出力電圧と等しい場合でも、出力電圧レギュレーションを維持します。これらの動作モード間の移行はシームレスで、トランジエントや低調波スイッチングが生じません。LTC3115-1は100kHz～2MHzの幅広いスイッチング周波数範囲で動作するように構成できるので、アプリケーションでの基板面積と効率に対する最適化が可能です。LTC3115-1は柔軟に構成可能で動作電圧範囲が広いので、鉛蓄電池、USBポート、産業用電源レールをはじめとする様々な入力電源と互換性を要する幅広い電源システムや、FireWire、非安定化ACアダプタなど、電圧範囲が広かつたり電圧範囲の制御が不十分な電源を持つ電源システムに最適です。

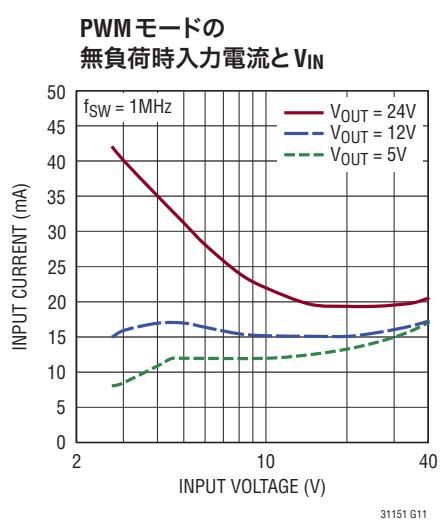

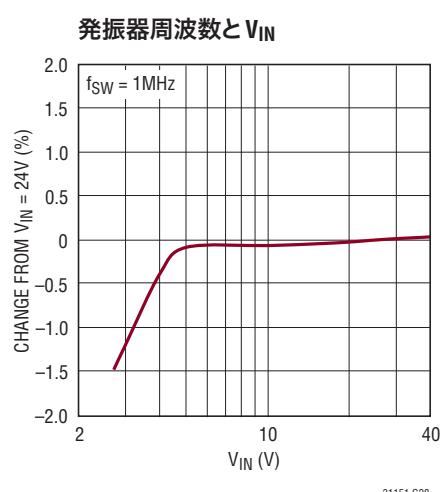

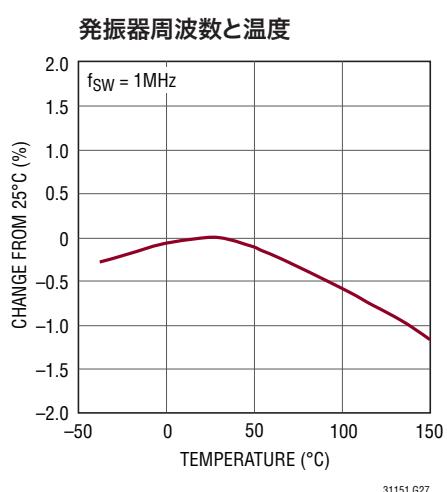

LTC3115-1は、スイッチング周波数が1本の外付け抵抗で容易に設定可能な、固定周波数の発振器を内蔵しています。ノイズに敏感なアプリケーションでは、PWM/SYNCピンを介してコンバータを外部クロックに同期させることもできます。LTC3115-1は、バッテリ駆動装置など静止電流が重視されるアプリケーションに対して、シャットダウン時とスタンバイ時の入力電流を低減するように最適化されています。Burst Mode動作では、無負荷でのスタンバイ電流はわずか50µA（標準）で、シャットダウン時には、全電源電流は3µA（標準）に減少します。

### PWMモードの動作

PWM/SYNCピンを“H”に強制するか、または外部クロックでドライブすると、LTC3115-1は、電圧モード制御ループを使った固定周波数のパルス幅変調(PWM)モードで動作します。このモードの動作では、コンバータから供給することができる出力電流が最大になり、出力電圧リップルが減少し、固定周波数のスイッチング・スペクトラムが低ノイズになります。独自のスイッチング・アルゴリズムにより、すべての動作領域にわたり動作モード間をシームレスに移行し、平均インダクタ電

流、インダクタ電流リップル、およびループの伝達関数の不連続性を除去します。これらの利点により、従来の4スイッチ昇降圧コンバータに比べて効率が向上し、ループの安定性が改善され、出力電圧リップルが小さくなります。

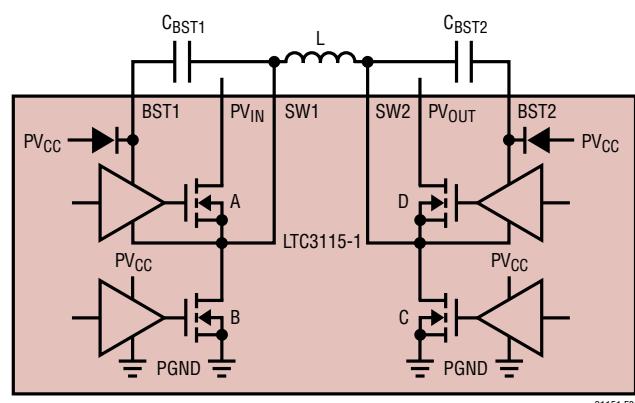

4個のNチャネルDMOSスイッチ、およびこれらの関連ゲート・ドライバで構成されるLTC3115-1の電力段のトポロジーを図1に示します。PWMモードの動作では、入力および出力の電圧に関係なく、両方のスイッチ・ピンがサイクルごとに遷移します。エラーアンプの出力に応答して、内部のパルス幅変調器がスイッチの適正なデューティ・サイクルを生成し、出力電圧のレギュレーションを維持します。

高い入力電圧から低い出力電圧に降圧する場合、コンバータが降圧モードで動作し、スイッチの最小“L”時間（標準100ns）を除き、全スイッチング・サイクルの間スイッチDがオンのままになります。スイッチの“L”時間にスイッチCがオンすることにより、SW2が“L”に強制されてフライング・コンデンサCBST2が充電され、スイッチDのゲート・ドライバの電源レールの電圧が維持されるようにします。スイッチAおよびスイッチBのデューティ・サイクルは適切な降圧モードのデューティ・サイクルが得られるように調整されます。

入力電圧が出力電圧より低いと、コンバータは昇圧モードで動作します。スイッチの最小“L”時間（標準100ns）を除き、全スイッチング・サイクルの間スイッチAがオンのまになりますが、スイッチCとスイッチDは必要な昇圧モードのデューティ・サイクルを維持するように調整されます。スイッチの最小“L”時間により、フライング・コンデンサCBST1が十分に充電されてBST1レールの電圧が維持されるようになります。

図1. 電力段の回路図

## 動作

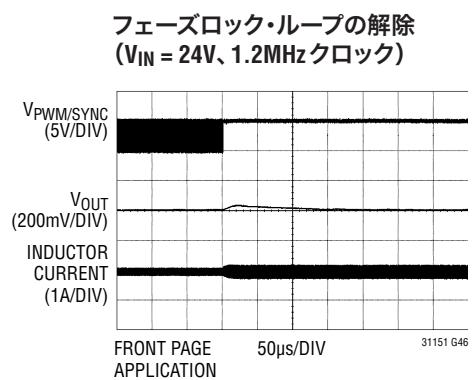

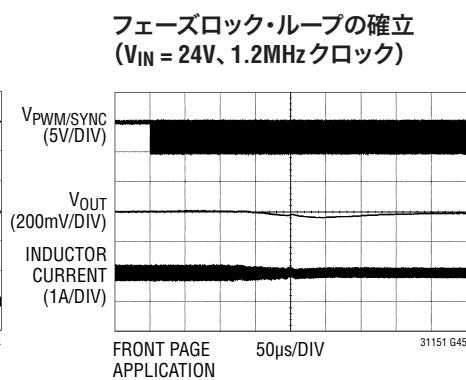

### 発振器とフェーズロック・ループ

LTC3115-1は、RTピンとグランドの間の1本の外付け抵抗で設定されるスイッチング周波数の内部発振器で動作します。ノイズに敏感なアプリケーションでは、内部フェーズロック・ループにより、LTC3115-1をPWM/SYNCピンに与えられる外部クロック信号に同期させることができます。フェーズロック・ループは、内部発振器の周波数を上げて同期させることだけが可能ですが、したがって、RT抵抗は、内部発振器をPWM/SYNCピンに与えられるクロックの周波数より低い周波数に設定するように選択する必要があります。外部同期クロックの周波数変動や内部発振器のワーストケースの周波数変動を考慮して、十分なマージンを含んでいなければなりません。内部発振器で動作するときも外部クロック信号に同期するときも、LTC3115-1は、100kHz～2MHzのスイッチング周波数で動作することができるので、外付け部品のサイズを最小限に抑え電力変換効率を最適化します。

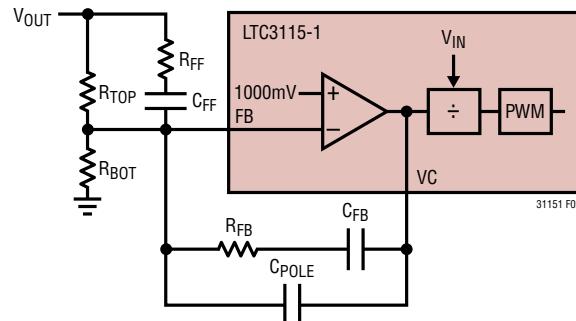

### エラーアンプと $V_{IN}$ 除算器

LTC3115-1は、出力電圧レギュレーションを維持する制御ループの周波数補償を行う高利得オペアンプを内蔵しています。この制御ループを安定させるため、アプリケーション回路に外部補償ネットワークを実装する必要があります。ほとんどのアプリケーションには図2に示すようなタイプIIIの補償ネットワークを推奨します。それは、コンバータのトランジエント応答を最適化する柔軟性を与えると同時に、出力電圧のDC誤差を最小限に抑えるからです。

図2に示すように、エラーアンプには内部アナログ除算器が接続されています。この除算器は、入力電圧の逆数によってループ利得を調整することで入力電圧の変化に対するループ利得の変動を最小限に抑えます。これにより、補償ネットワークの設計が簡素化され、入力電圧の全範囲でのトランジエント応答が最適化されます。LTC3115-1のアプリケーションでの補償ネットワークの設計の詳細については、このデータシートの「アプリケーション情報」のセクションを参照してください。

図2. エラーアンプと補償ネットワーク

### インダクタの電流制限

LTC3115-1は、ピーク・インダクタ電流を制限して、出力短絡状態や過負荷状態のときにスイッチ電流をデバイスの能力以内に抑えるように設計された、2つの電流制限回路を備えています。主インダクタ電流制限では、インダクタ電流が電流制限しきい値(標準3A)を超える分に比例して電流を帰還ピンに注入します。この帰還ループは利得が大きいので、この注入された電流は、インダクタを流れる平均電流がほぼ電流制限しきい値まで減少するまでエラーアンプの出力が低下するよう強制します。この電流制限回路はエラーアンプをアクティブ状態に保つことにより、電流制限フォルト状態が解消するとスムーズに回復しオーバーシュートを最小限に抑えます。ただし、この電流制限回路の応答速度はエラーアンプの動特性によって制限されます。ハードな出力短絡では、平均電流制限が応答してインダクタ電流を減らす前に、インダクタ電流が電流制限しきい値を超えて大幅に増加する可能性があります。このため、補助の電流制限回路があり、パワースイッチAを流れる電流が主インダクタ電流制限しきい値の約160%を超えると、パワースイッチAをオフします。これにより、瞬時のハードな出力短絡が生じた場合に追加の保護が行われ、主電流制限が応答するための時間が与えられます。さらに、Voutが1.85Vを下回ると、インダクタ電流制限が公称値の半分にフォールドバックして電力損失を最小限に抑えます。

## 動作

### 逆電流制限

PWMモードの動作では、LTC3115-1は4つすべてのパワーデバイスを同期してスイッチします。そのため、コンバータは、出力に電流を供給可能になるほか、レギュレーションを維持する必要があるときに出力からアクティブに電流を流すことができます。出力がレギュレーションを超えた状態に保たれると、これによって大きな逆電流が生じる可能性があります。この状況は、LTC3115-1の出力が、パワーアップやパワーダウンのシーケンスの間に生じることがあるように、別の電源によって一時的に保持されるときに発生する可能性があります。このような状態でのデバイスの損傷を防ぐため、LTC3115-1は、負荷からパワースイッチDに流入する電流をモニタする逆電流コンパレータを備えています。この電流が $\pm 1.5\text{A}$ （標準）を超えると、逆インダクタ電流が安全でないレベルに達するのを防ぐため、スイッチング・サイクルの残りの時間スイッチDをオフします。

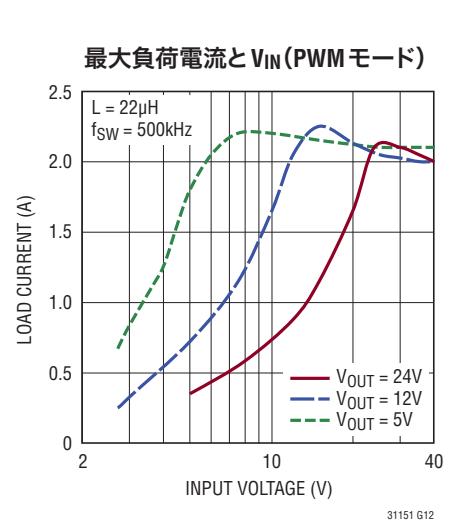

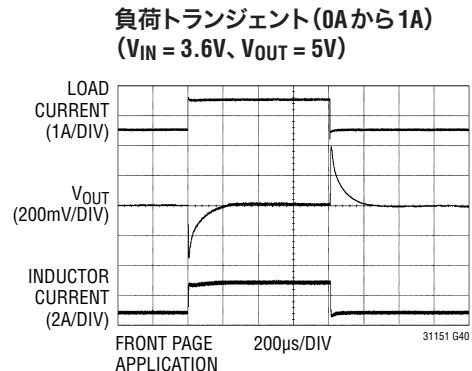

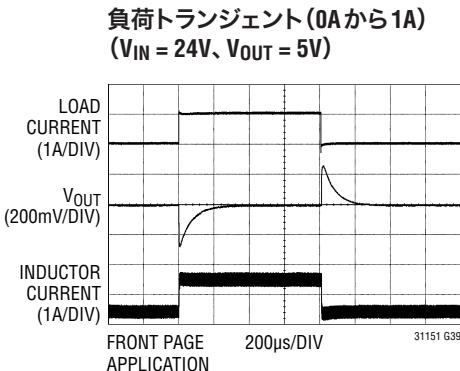

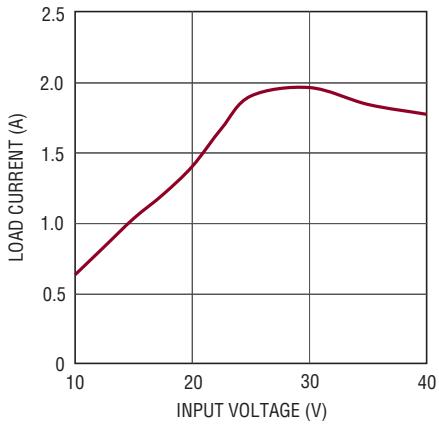

### 出力電流能力

LTC3115-1から供給可能な最大出力電流は多くの要因に依存しますが、最も影響が大きいのは入力電圧と出力電圧です。 $V_{\text{OUT}} = 5\text{V}$ および $V_{\text{IN}} \geq 3.6\text{V}$ の場合、LTC3115-1は最大1Aの負荷を継続的にサポートすることができます。 $V_{\text{OUT}} = 12\text{V}$ および $V_{\text{IN}} \geq 12\text{V}$ の場合、LTC3115-1は最大2Aの負荷を継続的にサポートすることができます。一般に、出力電流能力は入力電圧が出力電圧にほぼ等しいときに最大になります。昇圧電圧比が大きいときは、スイッチDのデューティ・サイクルが減少することによって所定の負荷をサポートするのに必要なインダクタ電流が増加するので、出力電流能力は低下します。また、降圧電圧比が大きいときは、達成可能な最大インダクタ電流を低減するインダクタ電流リップルが大きくなるので、一般に出力電流能力は低下します。

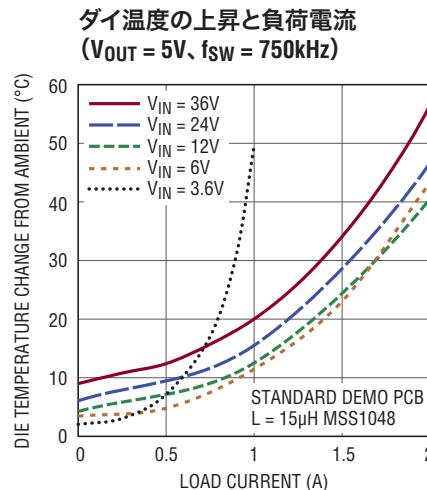

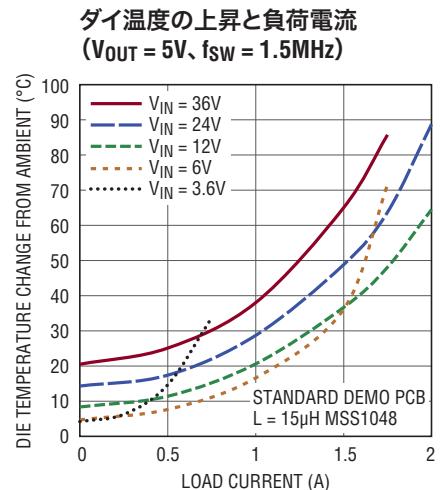

出力電流能力はインダクタの特性によって影響されることもあります。インダクタのDC抵抗が大きいと、特に昇圧モード動作で出力電流能力は低下します。インダクタの値を大きくすると、一般にインダクタ電流リップルを小さくすることによって出力電流能力を最大化します。さらに、スイッチング周波数が高くなる（特に750kHz以上）と、供給可能な最大出力電流が減少します（詳細については「標準的性能特性」を参照）。

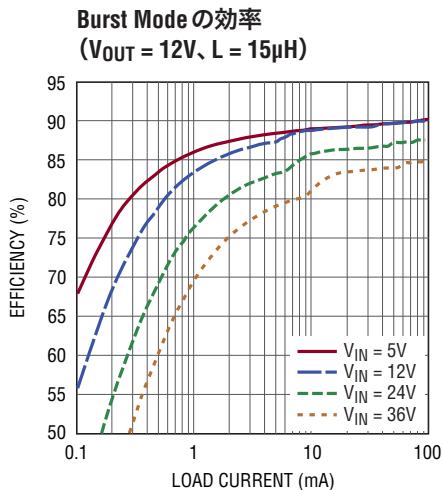

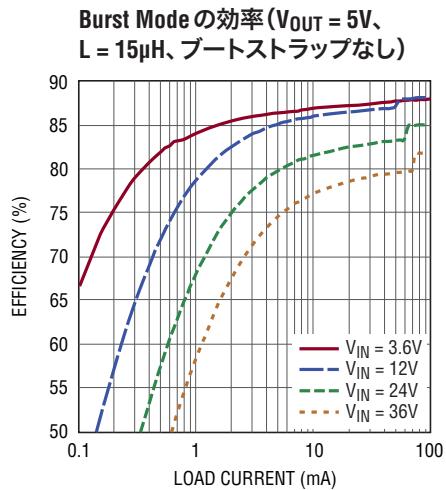

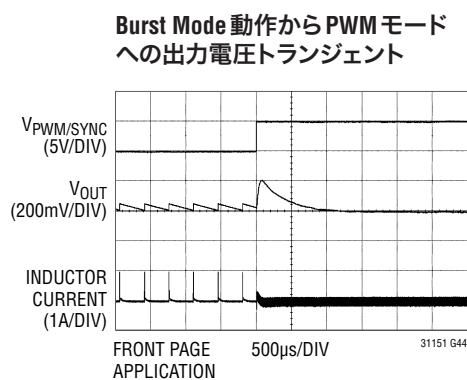

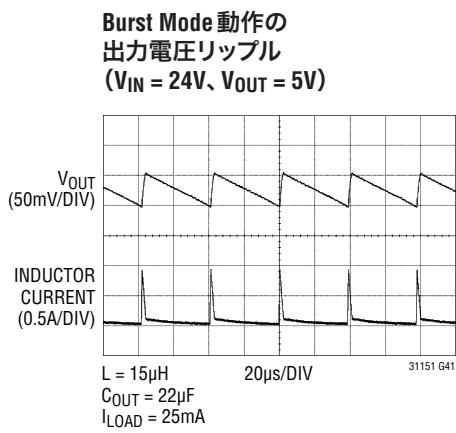

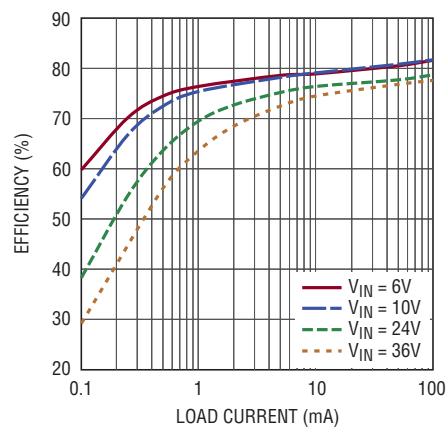

### Burst Mode動作

PWM/SYNCピンが“L”に保持されると、昇降圧コンバータは可変周波数スイッチング・アルゴリズムを使ったBurst Mode動作を行います。このアルゴリズムは、無負荷の入力静止電流を最小限に抑え、軽負荷時には、スイッチングの量をその負荷をサポートするのに必要な最小レベルに抑えることによって効率を改善します。Burst Mode動作の出力電流能力はPWMモードよりはるかに低く、軽いスタンバイ負荷（標準で50mA以下）のサポートを意図したものです。Burst Modeの最大負荷電流と入力電圧および出力電圧の関係を示す曲線については、このデータシートの「標準的性能特性」のセクションを参照してください。Burst Mode動作のコンバータの負荷がBurst Modeの最大電流能力を超えると、出力が不安定になります。

スイッチAおよびCがオンしてインダクタに流れる電流がリニアに増加すると、各Burst Modeサイクルが開始されます。インダクタ電流がBurst Modeの電流制限（標準1A）に達すると、スイッチBおよびDがオンし、インダクタに蓄積されたエネルギーが出力コンデンサと負荷に放出されます。インダクタ電流がゼロに達すると、すべてのスイッチがオフしてサイクルが終了します。このようにして生成された電流パルスは、必要に応じて繰り返し生成されて出力電圧のレギュレーションを維持します。Burst Mode動作ではエラーアンプは使用されませんが、代わりに低電流スタンバイ・モードになり、電源電流を減らして軽負荷の効率を改善します。

### ソフトスタート

パワーアップ時の入力電流トランジエントを最小限に抑えるため、LTC3115-1は公称持続時間が9msのソフトスタート回路を内蔵しています。ソフトスタートは、ソフトスタート時間の間にエラーアンプのリファレンス電圧がリニアに上昇することによって行われます。そのため、ソフトスタートの継続時間が出力コンデンサのサイズや出力安定化電圧に影響されることはありません。ソフトスタートに閉ループ特性がある場合、コンバータはソフトスタート時間の間に生じる負荷トランジエントに応答することができます。ソフトスタート時間は、サーマル・シャットダウンと、 $V_{\text{IN}}$ と $V_{\text{CC}}$ の両方のUVLOイベントによってリセットされます。

## 動作

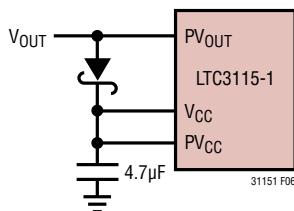

### V<sub>CC</sub>レギュレータ

内部低ドロップアウト・レギュレータがV<sub>IN</sub>から4.45V(公称)のV<sub>CC</sub>レールを生成します。V<sub>CC</sub>レールは、LTC3115-1の内部制御回路とパワーデバイスのゲート・ドライバに電力を供給します。V<sub>CC</sub>レギュレータは、静止電流を低減するためにシャットダウン時にディスエーブルされ、RUNピンをロジックしきい値より上に強制することによってイネーブルされます。V<sub>CC</sub>レギュレータには電流制限による保護機能が搭載されており、V<sub>CC</sub>レールの短絡に対して保護します。出力電圧が5Vに設定されるアプリケーションの場合、V<sub>CC</sub>レールはショットキ・ダイオードを介して出力レールからドライブすることができます。このようにしてブーストアップすることにより、特に電圧降圧比が大きいときに効率を大幅に改善することができ、低い入力電圧までの動作も可能になります。V<sub>CC</sub>ピンの最大動作電圧は5.5Vです。V<sub>CC</sub>を外部電圧に強制する場合には、この制限を超えないように注意する必要があります。

### 低電圧ロックアウト

入力電圧が低すぎるときの不安定な動作をなくして適切な動作を保証するため、LTC3115-1には低電圧ロックアウト(UVLO)回路が内蔵されています。2つのUVLOコンパレータがあり、1つはV<sub>IN</sub>をモニタし、もう1つはV<sub>CC</sub>をモニタします。V<sub>IN</sub>またはV<sub>CC</sub>のどちらかがそれぞれのUVLOしきい値を下回ると、昇降圧コンバータはディスエーブルされます。入力電圧のUVLOコンパレータの下降時しきい値は2.4V(標準)です。入力電圧がこのレベルを下回ると、入力電圧が2.6V(公称)を上回るまでスイッチングがディスエーブルされます。V<sub>CC</sub>のUVLOコンパレータの下降時しきい値は2.4Vです。V<sub>CC</sub>がこのしきい値を下回ると、V<sub>CC</sub>が2.6Vを上回るまで昇降圧コンバータのスイッチングが阻止されます。

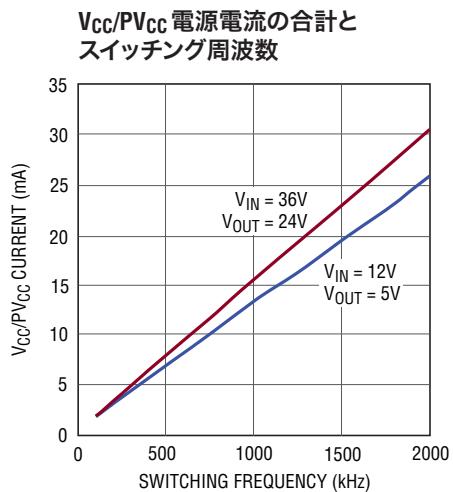

個々のアプリケーション回路により、これらのUVLOしきい値のどちらかがLTC3115-1の最小入力動作電圧を制限する要因になる可能性があります。支配的な要因はV<sub>IN</sub>とV<sub>CC</sub>の間の電圧降下に依存します。この電圧降下は、V<sub>CC</sub>レギュレータのドロップアウト電圧によって決まり、V<sub>CC</sub>から流れる総負荷電流に比例します。V<sub>CC</sub>レギュレータの負荷電流は主にゲート・ドライバの電源電流によって生成されます。ゲート・ドライバの電源電流は動作周波数に比例し、通常、入力電圧と出力電圧が高くなるに従って増加します。この結果、スイッチング周波数が高くなり入力電圧と出力電圧が高くなると、V<sub>CC</sub>

レギュレータのドロップアウト電圧が上昇するので、V<sub>CC</sub>のUVLOしきい値が制限要因になる可能性が高くなります。このデータシートの「標準的性能特性」のセクションの曲線に標準的なV<sub>CC</sub>電流が示されており、個々のアプリケーションのV<sub>CC</sub>レギュレータのドロップアウト電圧を推定するのに使用できます。V<sub>CC</sub>がブーストアップされる(ショットキ・ダイオードを介してV<sub>OUT</sub>または補助電源レールによって給電される)アプリケーションの場合、最小入力動作電圧は入力電圧のUVLOしきい値によってのみ制限されます。

### RUNピンのコンパレータ

RUNピンは、デバイスをイネーブルするロジックレベル入力として機能するほか、高精度内部コンパレータを備えているので、外付け抵抗分割器を追加することにより、個別の上昇時および下降時の入力低電圧ロックアウトしきい値を設定するのに使用できます。RUNピンがロジックしきい値(標準0.8V)より上にドライブされると、V<sub>CC</sub>レギュレータがイネーブルされることによってデバイスの内部制御回路に電力が供給され、RUNピンの高精度コンパレータがイネーブルされます。RUNピンの電圧がさらに上昇してRUNコンパレータのしきい値(公称1.21V)を超えると、昇降圧コンバータがイネーブルされます。

RUNピンがRUNコンパレータのしきい値を下回ると、昇降圧コンバータはスイッチングを停止しますが、RUNピンがロジックしきい値を下回らない限り、V<sub>CC</sub>レギュレータと制御回路は給電されたままです。したがって、デバイスをシャットダウン状態にして入力電流を最小レベル(標準3μA)に低減するためには、RUNピンがワーストケースのロジックしきい値(0.3V)を下回るようにする必要があります。RUNピンは高電圧入力であり、入力電源が接続されている場合、V<sub>IN</sub>に直接接続してデバイスを継続的にイネーブルすることができます。RUNピンは、約5Vより上に強制されると、次式によって求められる小電流をシンクします。

$$I_{RUN} \approx \frac{V_{RUN} - 5V}{5M\Omega}$$

図3に示す外付け抵抗分割器を追加することにより、RUNピンを使って個別の入力低電圧ロックアウトしきい値を設定できます。RUNピンが1.21Vに達すると、昇降圧コンバータがイネーブルされ、それにより抵抗分割器の比によって上昇時のUVLOしきい値を設定できるようになります。RUNピンがしきい値電圧に達すると、コンパレータが遷移して昇降圧コン

## 動作

図3.RUNピンの高精度コンパレータ

バータがイネーブルされます。さらに、 $0.5\mu\text{A}$ （標準）の内部電流源がイネーブルされると、RUNピンから電流がソースされてRUNピンの電圧がしきい値よりかなり高くなります。デバイスをディスエーブルするためには、 $V_{IN}$ を十分に下げることにより、この電流によって生成されるヒステリシスのほかRUNコンパレータの $100\text{mV}$ のヒステリシスを無効にする必要があります。したがって、両方の抵抗の値を調整することによって上昇時のUVLOしきい値に影響を与えることなく、ヒステリシスの値を個別に設定できます。

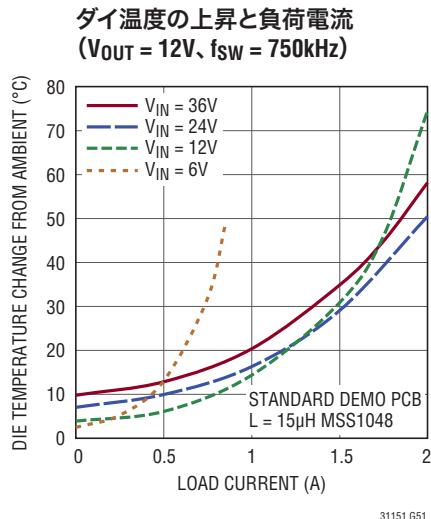

## 熱に関する検討事項

LTC3115-1のパワースイッチは、内部電流制限しきい値までの電流で継続的に動作するように設計されています。ただし、高電流レベルで動作しているときは、デバイス内部でかなりの熱が発生する可能性があります。さらに、多くのアプリケーションでは $V_{CC}$ レギュレータが大きな入力-出力間電圧差で動作する結果、パス素子の電力損失がかなりのレベルになり、デバイス内部の全電力損失が大幅に増えます。そのため、効率を最適化してLTC3115-1が最大定格出力電流を供給できるようにするために、デバイスの温度環境に関して注意深く検討する必要があります。特に、DHDパッケージとFEパッケージのどちらの露出ダイアタッチ・パッドもPC基板に半田付けし、PC基板はデバイスのパッケージからの放熱が最大になるように設計します。これは、露出した大きな銅箔領域を含む他のPCBの層に接続されたダイアタッチ・パッドからの複数のビアを使用することによって実現できます。

ダイ温度が約 $165^\circ\text{C}$ を超えると、デバイスは過熱シャットダウン状態になってすべてのスイッチングが停止します。デバイスは、ダイが約 $10^\circ\text{C}$ 冷えるまでディスエーブルされたままになります。ソフトスタート回路は過熱シャットダウン時に再初期化され、フォルト状態が解除されるとスムーズに回復します。

## アプリケーション情報

LTC3115-1の基本的なアプリケーション回路がこのデータシートの表紙の「標準的応用例」に示されています。外付け部品を適切に選択するには、アプリケーションごとにそのデバイスに必要な性能に基づいて、PCBの面積、コスト、出力電圧および入力電圧、許容リップル電圧、効率、熱などのトレードオフに配慮します。ここでは、外付け部品の選択とアプリケーション回路の設計に役立ついくつかの基本的ガイドラインと検討事項について説明します。

### V<sub>CC</sub>コンデンサの選択

LTC3115-1のV<sub>CC</sub>出力は内部低ドロップアウト・レギュレータによって入力電圧から生成されます。V<sub>CC</sub>レギュレータは様々な出力コンデンサで安定して動作するように設計されています。ほとんどのアプリケーションでは、少なくとも4.7μFの低ESRセラミック・コンデンサを使用します。このコンデンサはできるだけピンの近くに配置し、できるだけ短いトレースを介してPV<sub>CC</sub>ピンとグランドに接続します。PV<sub>CC</sub>ピンは、レギュレータの出力であり、ゲート・ドライバと昇圧レール充電ダイオードの内部電源ピンもあります。V<sub>CC</sub>ピンは制御回路の残りの部分の電源接続ピンです。アプリケーションのPCBではPV<sub>CC</sub>ピンとV<sub>CC</sub>ピンを相互接続する必要があります。V<sub>CC</sub>をPV<sub>CC</sub>に接続するトレースを短くできない場合、V<sub>CC</sub>ピンとグランドの間に0.1μFのバイパス・コンデンサをできるだけ短い距離で接続します。

### インダクタの選択

LTC3115-1のアプリケーション回路に使用されるインダクタの選択により、供給可能な最大出力電流、インダクタ電流リップルの大きさ、および電力変換効率が決まります。インダクタはDC直列抵抗が小さくなければなりません。つまり、出力電流能力と効率は妥協することになります。インダクタンス値を大きくするとインダクタ電流リップルが減るので、一般に出力電流能力が上がります。DC抵抗が一定の場合、インダクタンスの値を大きくすると、ピーク電流が減少して平均出力電流に近づくことにより効率が上がるのに、高RMS電流による抵抗損失が最小限に抑えられます。ただし、所定のインダクタ・ファミリ内での大きなインダクタは一般に直列抵抗が大きいので、この効率向上が抑制されます。一般に、インダクタンス値

が大きくDC抵抗が小さいインダクタでは、供給可能な出力電流が増加し、LTC3115-1のアプリケーションの効率が改善されます。

LTC3115-1のアプリケーションで使用されるインダクタは、飽和電流定格がワーストケースの平均インダクタ電流にリップル電流の半分を加えた電流を超えている必要があります。各動作モードのピーク・トゥ・ピーク・インダクタ電流リップルは以下の式から計算することができます。ここで、fはスイッチング周波数、Lはインダクタンス、t<sub>LOW</sub>はスイッチ・ピンの最小“L”時間です。スイッチ・ピンの最小“L”時間は、このデータシートの「標準的性能特性」のセクションに示されている曲線から求めることができます。

$$\Delta I_{L(P-P)(BUCK)} = \frac{V_{OUT}}{L} \left( \frac{V_{IN} - V_{OUT}}{V_{IN}} \right) \left( \frac{1}{f} - t_{LOW} \right)$$

$$\Delta I_{L(P-P)(BOOST)} = \frac{V_{IN}}{L} \left( \frac{V_{OUT} - V_{IN}}{V_{OUT}} \right) \left( \frac{1}{f} - t_{LOW} \right)$$

電力変換効率に対する影響に加え、インダクタのDC抵抗は特に低入力電圧での昇降圧コンバータの最大出力電流能力にも影響を与えることがあります。降圧モードでは、一般に昇降圧コンバータの出力電流はインダクタ電流が電流制限しきい値に達することによってのみ制限されます。ただし、昇圧モードの場合、特に大きな昇圧比では、出力電流能力は電力段の総抵抗損失によっても制限されます。これらにはスイッチ抵抗、インダクタ抵抗およびPCBのトレース抵抗が含まれます。DC抵抗が大きいインダクタを使用すると、出力電流能力が、このデータシートの「標準的性能特性」のセクションに示されている値から低下することがあります。ガイドラインとして、ほとんどのアプリケーションでは、インダクタのDC抵抗を150mΩの標準パワースイッチ抵抗より大幅に小さくします。

インダクタのコア材と種類により、所定の電流定格でのインダクタのサイズと価格が異なります。シールドされた構造は、他の回路との干渉の可能性を最小限に抑えるので一般に適しています。インダクタの種類の選択は、特定のアプリケーションの価格、サイズ、およびEMIに対する要件に依存します。LTC3115-1の多くのアプリケーションに最適なインダクタのサンプルを表1に示します。

## アプリケーション情報

$V_{OUT} \geq 20V$  のアプリケーションの場合、次の最小インダクタンス値  $L_{MIN}$  を使用することを推奨します。ここで、 $f$  はスイッチング周波数です。

$$L_{MIN} = \frac{12H}{(f/Hz)}$$

表1. 代表的な表面実装インダクタ

| 製品番号                   | 値<br>( $\mu$ H) | DCR<br>( $m\Omega$ ) | 最大DC電流<br>(A) | サイズ(mm)<br>W × L × H |

|------------------------|-----------------|----------------------|---------------|----------------------|

| <b>Coilcraft</b>       |                 |                      |               |                      |

| LPS6225                | 4.7             | 65                   | 3.2           | 6.2 × 6.2 × 2.5      |

| LPS6235                | 6.8             | 75                   | 2.8           | 6.2 × 6.2 × 3.5      |

| MSS1038                | 22              | 70                   | 3.3           | 10.2 × 10.5 × 3.8    |

| D03316P                | 15              | 50                   | 3.0           | 12.9 × 9.4 × 5.2     |

| <b>Cooper-Bussmann</b> |                 |                      |               |                      |

| CD1-150-R              | 15              | 50                   | 3.6           | 10.5 × 10.4 × 4.0    |

| DR1030-100-R           | 10              | 40                   | 3.18          | 10.3 × 10.5 × 3.0    |

| FP3-8R2-R              | 8.2             | 74                   | 3.4           | 7.3 × 6.7 × 3.0      |

| DR1040-220-R           | 22              | 54                   | 2.9           | 10.3 × 10.5 × 4.0    |

| <b>パナソニック</b>          |                 |                      |               |                      |

| ELLCTV180M             | 18              | 30                   | 3.0           | 12 × 12 × 4.2        |

| ELLATV100M             | 10              | 23                   | 3.3           | 10 × 10 × 4.2        |

| <b>スミダ電機</b>           |                 |                      |               |                      |

| CDRH8D28/HP            | 10              | 78                   | 3.0           | 8.3 × 8.3 × 3        |

| CDR10D48MNNP           | 39              | 105                  | 3.0           | 10.3 × 10.3 × 5      |

| CDRH8D28NP             | 4.7             | 24.7                 | 3.4           | 8.3 × 8.3 × 3        |

| <b>太陽誘電</b>            |                 |                      |               |                      |

| NR10050T150M           | 15              | 46                   | 3.6           | 9.8 × 9.8 × 5        |

| <b>東光</b>              |                 |                      |               |                      |

| B1047AS-6R8N           | 6.8             | 36                   | 2.9           | 7.6 × 7.6 × 5        |

| B1179BS-150M           | 15              | 56                   | 3.3           | 10.3 × 10.3 × 4      |

| 892NAS-180M            | 18              | 42                   | 3.0           | 12.3 × 12.3 × 4.5    |

| <b>Würth</b>           |                 |                      |               |                      |

| 7447789004             | 4.7             | 33                   | 2.9           | 7.3 × 7.3 × 3.2      |

| 744771133              | 33              | 49                   | 2.7           | 12 × 12 × 6          |

| 744066150              | 15              | 40                   | 3.2           | 10 × 10 × 3.8        |

## 出力コンデンサの選択

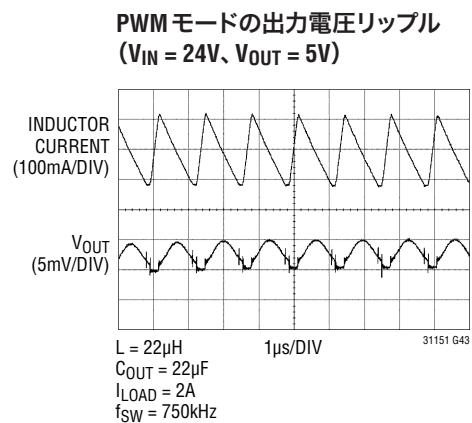

出力電圧リップルを最小限に抑えるため、昇降圧コンバータの出力には低ESRの出力コンデンサを使用します。積層セラミック・コンデンサはESRが小さく、実装面積の小さいものが入手できるので最適です。十分大きな値のコンデンサを選択して出力電圧リップルを許容レベルに下げます。コンデンサのESRおよびESLを無視すると、ピーク・トゥ・ピーク出力電圧リップルは以下の式で計算することができます。ここで、 $f$  はスイッチング周波数、 $C_{OUT}$  は容量、 $t_{LOW}$  はスイッチ・ピンの最小“L”時間、 $I_{LOAD}$  は出力電流です。 $t_{LOW}$  の値とスイッチング周波数の関係を示す曲線については、このデータシートの「標準的性能特性」のセクションを参照してください。

$$\Delta V_{P-P(BUCK)} = \frac{I_{LOAD}t_{LOW}}{C_{OUT}}$$

$$\Delta V_{P-P(BOOST)} = \frac{I_{LOAD}}{fC_{OUT}} \left( \frac{V_{OUT} - V_{IN} + t_{LOW}fV_{IN}}{V_{OUT}} \right)$$

出力電圧リップルは負荷電流とともに増加し、降圧モードより昇圧モードの方が一般に大きくなります。これらの式は、出力電流が不連続であることから生じる出力電圧リップルだけを考慮しています。これらの式により、ある程度の大きさの負荷電流でのリップルについてはかなり正確な概算値が出ますが、出力電圧リップルがインダクタ電流リップルに左右される非常に軽負荷時の出力電圧リップルは小さめの概算値となります。

出力容量の両端に生じる出力電圧リップルに加えて、出力コンデンサの内部抵抗の両端にも出力電圧リップルが生じます。ESRによって生じる出力電圧リップルは出力コンデンサの直列抵抗に比例し、次式で与えられます。ここで、 $R_{ESR}$  は出力コンデンサの直列抵抗、他のすべての項は前述のとおりです。

$$\Delta V_{P-P(BUCK)} = \frac{I_{LOAD}R_{ESR}}{1-t_{LOW}f} \approx I_{LOAD}R_{ESR}$$

$$\Delta V_{P-P(BOOST)} = \frac{I_{LOAD}R_{ESR}V_{OUT}}{V_{IN}(1-t_{LOW}f)} \approx I_{LOAD}R_{ESR} \left( \frac{V_{OUT}}{V_{IN}} \right)$$

## 入力コンデンサの選択

$P_{VIN}$  ピンは全インダクタ電流を流し、デバイスの内部制御回路に電力を供給します。入力電圧リップルを最小限に抑えてデバイスに適切な動作をさせるため、少なくとも  $4.7\mu F$  の値の低ESRバイパス・コンデンサをこのピンにできるだけ近づけて配置します。このコンデンサを  $P_{VIN}$  とグランド・プレーンに接続するトレースはできるだけ短くします。 $V_{IN}$  ピンは  $V_{CC}$  レギュレータとその他の内部回路に電力を供給します。 $V_{IN}$  を  $P_{VIN}$  に接続するPCBトレースが長いと、 $V_{IN}$  ピンの近くに小さな値のバイパス・コンデンサの追加が必要になる場合があります。

長いリード線を介して給電するか、または高ESRの電源から給電するときは、より大きな値のバルク入力コンデンサが必要になる場合があります。このようなアプリケーションでは、 $1\mu F$  のセラミック・コンデンサと並列に  $47\mu F \sim 100\mu F$  の電解コンデンサを接続すると、高性能で低コストのソリューションが得られます。

## アプリケーション情報

### 推奨する入力および出力のコンデンサ

LTC3115-1の入力と出力のフィルタに使用するコンデンサは、低ESRであり、スイッチング・コンバータが発生する大きなAC電流に対応した定格である必要があります。これはデバイスの適切な動作を維持し、出力電圧リップルを減らすのに重要です。このようなアプリケーションに最適なコンデンサには、積層セラミック、低ESRタンタル、OS-CON、POSCAPなど多くのタイプがあります。さらに、低ESRおよび高AC電流向けに設計された固体アルミ有機ポリマー・コンデンサなどの特定のタイプの電解コンデンサがあり、これらもLTC3115-1のアプリケーションに最適です(表2)。コンデンサの種類の選択は、主にコスト、サイズ、漏れ電流のトレードオフによって決まります。OS-CONやPOSCAPなどのコンデンサは、DC漏れ電流が大きい可能性があり、Burst Mode動作時に無負荷での低静止電流を必要とするデバイスでの適用が制限される場合があることに注意してください。

スイッチング・コンバータのアプリケーションには、小型、低ESR、および低漏れ電流であることから、多くの場合セラミック・コンデンサが使用されます。ただし、電力アプリケーション用に設計されたセラミック・コンデンサの多くは、DCバイアス電圧が上昇するにつれ、容量が定格値から大きく減少します。たとえば、小型表面実装セラミック・コンデンサがその定格電圧近くで動作するとき、その定格容量の50%以上を失うことは珍しくありません。そのため、場合によっては最大動作電圧で意図する容量を実現させるため、大きな値の容量や必要以上に電圧定格の高いコンデンサを使用する必要があります。アプリケーション回路で意図する容量を実現させるため、コンデンサ・メーカーの容量対DCバイアス電圧の曲線を必ず参照してください。

表2. 代表的なバイパス・コンデンサおよび出力コンデンサ

| メーカー、製品番号          | 値(μF) | 電圧(V) | サイズ L × W × H(mm)、タイプ、ESR         |

|--------------------|-------|-------|-----------------------------------|

| <b>AVX</b>         |       |       |                                   |

| 12103D226MAT2A     | 22    | 25    | 3.2 × 2.5 × 2.79<br>X5R セラミック     |

| TPME226K050R0075   | 22    | 50    | 7.3 × 4.3 × 4.1<br>タンタル、75mΩ      |

| <b>Kemet</b>       |       |       |                                   |

| C2220X226K3RACTU   | 22    | 25    | 5.7 × 5.0 × 2.4<br>X7R セラミック      |

| A700D226M016ATE030 | 22    | 16    | 7.3 × 4.3 × 2.8<br>アルミ・ポリマー、30mΩ  |

| <b>村田製作所</b>       |       |       |                                   |

| GRM32ER71E226KE15L | 22    | 25    | 3.2 × 2.5 × 2.5<br>X7R セラミック      |

| <b>ニチコン</b>        |       |       |                                   |

| PLV1E121MDL1       | 82    | 25    | 8 × 8 × 12<br>アルミ・ポリマー、25mΩ       |

| <b>パナソニック</b>      |       |       |                                   |

| ECJ-4YB1E226M      | 22    | 25    | 3.2 × 2.5 × 2.5<br>X5R セラミック      |

| <b>三洋電機</b>        |       |       |                                   |

| 25TQC22MV          | 22    | 25    | 7.3 × 4.3 × 3.1<br>POSCAP、50mΩ    |

| 16TQC100M          | 100   | 16    | 7.3 × 4.3 × 1.9<br>POSCAP、45mΩ    |

| 25SVPF47M          | 47    | 25    | 6.6 × 6.6 × 5.9<br>OS-CON、30mΩ    |

| <b>太陽誘電</b>        |       |       |                                   |

| UMK325BJ106MM-T    | 10    | 50    | 3.2 × 2.5 × 2.5<br>X5R セラミック      |

| TMK325BJ226MM-T    | 22    | 25    | 3.2 × 2.5 × 2.5<br>X5R セラミック      |

| <b>TDK</b>         |       |       |                                   |

| KTJ500B226M55BFT00 | 22    | 50    | 6.0 × 5.3 × 5.5<br>X7R セラミック      |

| C5750X7R1H106M     | 10    | 50    | 5.7 × 5.0 × 2.0<br>X7R セラミック      |

| CKG57NX5R1E476M    | 47    | 25    | 6.5 × 5.5 × 5.5<br>X5R セラミック      |

| <b>Vishay</b>      |       |       |                                   |

| 94SVPD476X0035F12  | 47    | 35    | 10.3 × 10.3 × 12.6<br>OS-CON、30mΩ |

## アプリケーション情報

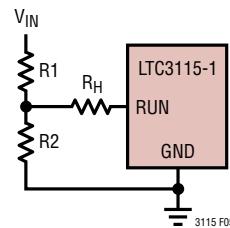

### 個別の入力UVLOしきい値の設定

図4に示すように、入力電圧に外付け抵抗分割器を接続することにより、RUNピンを使ってLTC3115-1がイネーブルおよびディスエーブルされる入力電圧を設定できます。

上昇時の入力電圧の場合、LTC3115-1はV<sub>IN</sub>が次式で与えられるしきい値に達するとイネーブルされます。ここで、R1とR2は抵抗分割器の抵抗の値です。

$$V_{TH(RISING)} = 1.21V \left( \frac{R1+R2}{R2} \right)$$

ノイズが存在するときの堅牢な動作を保証するため、RUNピンには2つの形態のヒステリシスがあります。RUNピンのコンパレータの100mV固定のヒステリシスは、抵抗分割器の値に関係なく、入力ターンオン電圧の8.3%に等しいRUNピンの最小ヒステリシスを与えます。さらに、動作時にRUNピンからソースされる内部ヒステリシス電流がヒステリシスの追加レベルを発生します。このレベルはR1の値によって設定され、全体のヒステリシスを増加させて個々のアプリケーションの要件を満たすことができます。

デバイスはいったんイネーブルされると、入力電圧がコンパレータのしきい値を次式で与えられるヒステリシス電圧V<sub>HYST</sub>だけ下回るまでイネーブルされたままになります。ここで、R1とR2は分割器抵抗の値です。

$$V_{HYST} = R1 \cdot 0.5\mu A + \left( \frac{R1+R2}{R2} \right) 0.1V$$

したがって、上昇時のUVLOしきい値とヒステリシスの大きさは、抵抗R1およびR2を適切に選択することによって個別に設定できます。ハイレベルのヒステリシスの場合、R1の値は実用上望ましい値よりも大きくなる可能性があります(1MΩ～2MΩ以上)。このような場合、図5に示すように、追加の抵抗R<sub>H</sub>を接続することにより、ヒステリシスをさらに大きくすることができます。

図4. 入力のUVLOしきい値およびヒステリシスの設定

追加のR<sub>H</sub>抵抗を使用すると、上昇時のRUNピンしきい値は元の式で与えられる値に保たれ、ヒステリシスは次式で与えられます。

$$V_{HYST} = \left( \frac{R1+R2}{R2} \right) 0.1V + \frac{R_H R2 + R_H R1 + R1 R2}{R2} (0.5\mu A)$$

図5. 入力UVLOヒステリシスの増加

ノイズに対する堅牢性とUVLOしきい値の精度を改善するため、RUNからGNDに1000pFのコンデンサを追加することによってRUNピンの入力をフィルタすることができます。大きな値のコンデンサはヒステリシスの動作を妨害する可能性があるので使用しないようにします。

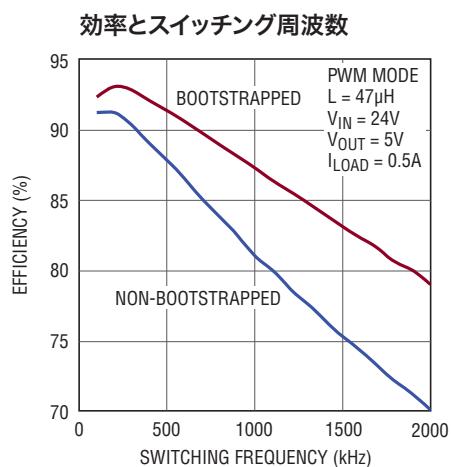

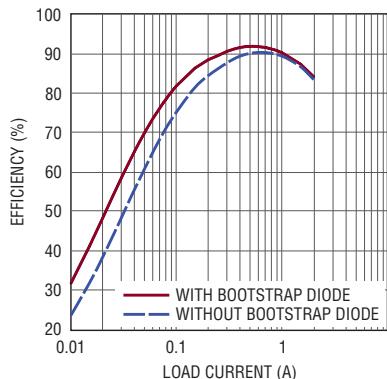

### V<sub>CC</sub>レギュレータのブートストラップ

ハイサイドおよびローサイドのゲート・ドライバは、入力電圧から内部リニア・レギュレータを介して生成されるPV<sub>CC</sub>レールから給電されます。アプリケーションによっては、特に高い動作周波数と高い入力および出力電圧で、リニアV<sub>CC</sub>レギュレータの電力損失がコンバータの変換効率における主な要因になる可能性があり、発熱の大きな要因になる可能性もあります。たとえば、1.2MHzのスイッチング周波数、36Vの入力電圧、24Vの出力電圧では、このデータシートの「標準的性能特性」のセクションに示すように、PV<sub>CC</sub>/V<sub>CC</sub>電流の合計は約18mAになります。この結果、V<sub>CC</sub>レギュレータに568mWの電力損失が生じることにより、DFNパッケージでダイ温度が周囲温度より約24°上昇します。この大きな電力損失は変換効率にかなりの影響を与え、さらに発熱すると、アプリケーションの最大周囲動作温度を制限する可能性があります。

## アプリケーション情報

出力電圧がPVCCレールとVCCレールの給電に使用される場合、コンバータの出力電圧が5Vに設定されるアプリケーションでは、性能面で大きな利点が得られます。これは図6に示すように、VOUTからPVCC/VCCにショットキ・ダイオードを接続することによって実現できます。このブートストラップ・ダイオードを実装した場合、ゲート・ドライバの電流は、内部リニア・レギュレータを介して生成されるのではなく、昇降圧コンバータによって高効率で直接生成されます。出力から流出する電流を最小限に抑えるため、内部VCCレギュレータは逆方向ブロッキング回路を備えており、PVCC/VCCピンが入力電圧より上にドライブされるときに、これらのピンに流れ込む電流を最小限に抑えます。

図6.PVCCとVccのブートストラップ

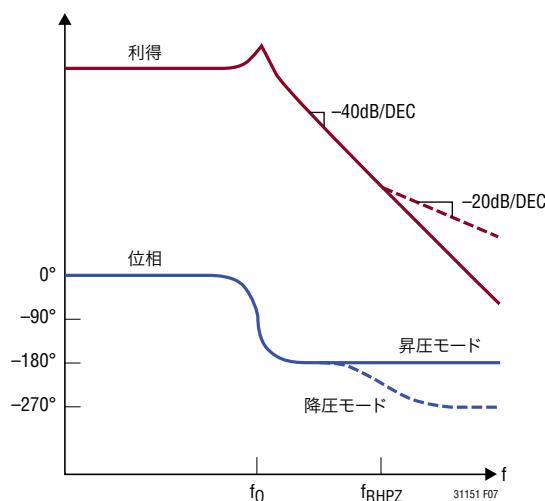

### 降圧モードの小信号モデル

LTC3115-1は電圧モード制御ループを使って出力電圧のレギュレーションを維持します。外部補償されたエラーアンプはVCピンをドライブして、パワースイッチの適切なデューティ・サイクルを発生します。外部補償ネットワークの使用により、広い範囲の出力電圧、スイッチング周波数、およびLTC3115-1がサポートする外付け部品の値に対して、閉ループ性能を最適化できる柔軟性が得られます。

昇降圧コンバータの小信号伝達関数は降圧モードと昇圧モードの動作で異なるので、両方の動作領域で確実に安定するように注意する必要があります。高い入力電圧から低い出力電圧に降圧する場合、コンバータは降圧モードで動作し、エラーアンプの出力VCからコンバータの出力電圧への小信号伝達関数は次式で与えられます。

$$\left. \frac{V_0}{V_C} \right|_{BUCK \text{ MODE}} = G_{BUCK} \frac{\left( 1 + \frac{s}{2\pi f_Z} \right)}{1 + \frac{s}{2\pi f_0 Q} + \left( \frac{s}{2\pi f_0} \right)^2}$$

利得の項 $G_{BUCK}$ は3つの異なる要素からなります。以下の式で与えられるアナログ除算器の利得、パルス幅変調器の利得、および電力段の利得です。ここで、 $V_{IN}$ はコンバータの入力電圧、 $f$ はスイッチング周波数、 $R$ は負荷抵抗、 $t_{LOW}$ はスイッチ・ピンの最小“L”時間です。スイッチ・ピンの最小“L”時間を示す曲線がこのデータシートの「標準的性能特性」のセクションに示されています。パラメータ $R_S$ は電力段の平均直列抵抗を表しており、平均パワースイッチ抵抗の2倍とインダクタのDC抵抗の和で近似することができます。

$$G_{BUCK} = G_{DIVIDER} G_{PWM} G_{POWER}$$

$$G_{DIVIDER} = \frac{19.8}{V_{IN}}$$

$$G_{PWM} = 1.5(1 - t_{LOW} f)$$

$$G_{POWER} = \frac{V_{IN} R}{(1 - t_{LOW} f)(R + R_S)}$$

アナログ除算器の利得によって電力段の入力電圧への依存が解消される点に注意してください。その結果、降圧モードの利得は次式で与えられる定数によって正しく近似されます。

$$G_{BUCK} = 29.7 \frac{R}{R + R_S} \approx 29.7 = 29.5 \text{dB}$$

降圧モードの伝達関数は、出力コンデンサのESRによって生じる単一のゼロを有します。ゼロ周波数 $f_Z$ は次式で与えられます。ここで、 $R_C$ と $C_O$ はそれぞれ出力フィルタ・コンデンサのESRと値です。

$$f_Z = \frac{1}{2\pi R_C C_O}$$

ほとんどのアプリケーションでは、出力電圧リップルを許容レベルに下げるため、ESRが非常に小さい出力コンデンサが使用されます。コンデンサのESRのこのように小さい値は非常に高い周波数のゼロを生じるので、このゼロは帰還ループの補償に大きな影響を与えるには一般に周波数が高すぎます。

## アプリケーション情報

降圧モードの伝達関数の分母は電力段のLCフィルタによって生じる1対の共振ポールを示しています。電力段の共振周波数 $f_0$ は次式で与えられます。ここで、Lはインダクタの値です。

$$f_0 = \frac{1}{2\pi} \sqrt{\frac{R+R_S}{LC_0(R+R_C)}} \approx \frac{1}{2\pi} \sqrt{\frac{1}{LC_0}}$$

クオリティ・ファクタQは電圧ループの補償に大きく影響します。高いQファクタによって共振周波数の近くで位相が急激に遅延するからです。クオリティ・ファクタは電力段の減衰量に対して反比例の関係にあり、電力段の平均直列抵抗 $R_S$ によって大きく影響されます。 $R_S$ の値が小さいとQが増加して共振周波数の近くで位相が急激に遅延するので、位相ブーストを強めるか、または適切な位相マージンを維持するために帯域幅を狭める必要があります。

$$Q = \frac{\sqrt{LC_0(R+R_C)(R+R_S)}}{RR_C C_0 + L + C_0 R_S (R+R_C)} \approx \frac{\sqrt{LC_0}}{\frac{L}{R} + C_0 R_S}$$

### 昇圧モードの小信号モデル

低い入力電圧から高い出力電圧に昇圧する場合、昇降圧コンバータは昇圧モードで動作し、制御電圧 $V_C$ から出力電圧への小信号伝達関数は次式で与えられます。

$$\left. \frac{V_0}{V_C} \right|_{\text{BOOST MODE}} = G_{\text{BOOST}} \frac{\left(1 + \frac{s}{2\pi f_L}\right) \left(1 - \frac{s}{2\pi f_{RHPZ}}\right)}{1 + \frac{s}{2\pi f_0 Q} + \left(\frac{s}{2\pi f_0}\right)^2}$$

昇圧モード動作では、降圧モードと同様に、1対の共振ポールと出力コンデンサのESRによって生じる1個のゼロによって伝達関数の特性が決まります。ただし、これらに加えて右半平面にゼロがあり、高い周波数では利得が増加し、位相が遅延します。したがって、十分な位相マージンを維持するため、昇圧モード動作のクロスオーバー周波数は一般に降圧モードの場合より低く設定する必要があります。

昇圧モードの利得 $G_{\text{BOOST}}$ は、アナログ除算器、パルス幅変調器、電力段の3つの要素からなります。アナログ除算器とPWMの利得は降圧モード動作と同様ですが、昇圧モードの電力段の利得は次式で与えられます。

$$G_{\text{POWER}} \approx \frac{V_{\text{OUT}}^2}{(1-t_{\text{LOW}} f) V_{\text{IN}}}$$

個々の項を結合することにより、昇圧モードの総利得は次式にまとめることができます。降圧モードの場合とは異なり、昇圧モードの利得は入力電圧と出力電圧両方の関数であることに注意してください。

$$G_{\text{BOOST}} \approx \frac{29.7 V_{\text{OUT}}^2}{V_{\text{IN}}^2}$$

昇圧モード動作では、右半平面のゼロの周波数 $f_{RHPZ}$ は次式で与えられます。右半平面のゼロの周波数は高負荷および大きなインダクタでは減少します。

$$f_{RHPZ} = \frac{R(1-t_{\text{LOW}} f)^2 V_{\text{IN}}^2}{2\pi L V_{\text{OUT}}^2}$$

昇圧モードでは、次式で示されているように、電力段の共振周波数は入力電圧と出力電圧に依存します。

$$f_0 = \frac{1}{2\pi} \sqrt{\frac{R_S + \frac{RV_{\text{IN}}^2}{V_{\text{OUT}}^2}}{LC_0(R+R_C)}} \approx \frac{1}{2\pi} \cdot \frac{V_{\text{IN}}}{V_{\text{OUT}}} \sqrt{\frac{1}{LC}}$$

最終的に、昇圧モード動作の電力段のクオリティ・ファクタの大きさは次式で与えられます。

$$Q = \frac{\sqrt{LC_0 R \left( R_S + \frac{RV_{\text{IN}}^2}{V_{\text{OUT}}^2} \right)}}{L + C_0 R_S R}$$

## アプリケーション情報

### 電圧ループの補償

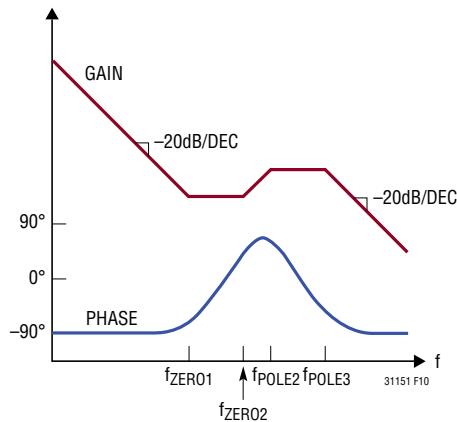

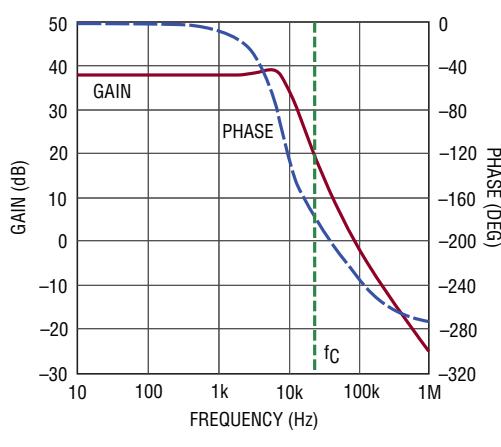

図7のボード線図に示すように、エラーアンプの出力VCから出力電圧への伝達関数の特性は、1組の共振ポールと出力コンデンサのESRによって生じる可能性のある1個のゼロによって決まることを、LTC3115-1の小信号モデルは明らかにしています。昇圧モード動作では、右半平面に追加のゼロがあり、高い周波数では位相遅延を生じて利得が増加します。一般に、ループのクロスオーバー周波数が十分低くて右半平面のゼロによる位相の遅延が最小限に抑えられるように、補償ネットワークは設計されます。降圧モードの低周波数利得は一定ですが、昇圧モードでは $V_{IN}$ と $V_{OUT}$ の両方に伴って変化します。

図7. 昇降圧コンバータのボード線図

充電など最適化された出力電圧のトランジェント応答を必要としないアプリケーションでは、図8に示すようなシンプルなタイプIの補償ネットワークを使って電圧ループを安定化することができます。十分な位相マージンを確保するため、制御ループのクロスオーバー周波数が共振周波数より十分低くなるようにエラーアンプの利得を十分小さくする必要があります。

図8. タイプIの補償を備えたエラーアンプ

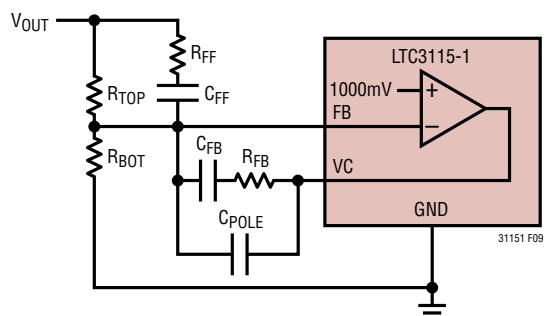

ほとんどのアプリケーションでは、タイプIで補償されたループが狭帯域なので、十分なトランジェント応答性能が得られません。広い帯域幅の帰還ループを実現し、トランジェント応答を最適化し、出力コンデンサのサイズを最小限に抑えるには、図9に示すようなタイプIIIの補償ネットワークが必要です。

図9. タイプIIIの補償を備えたエラーアンプ

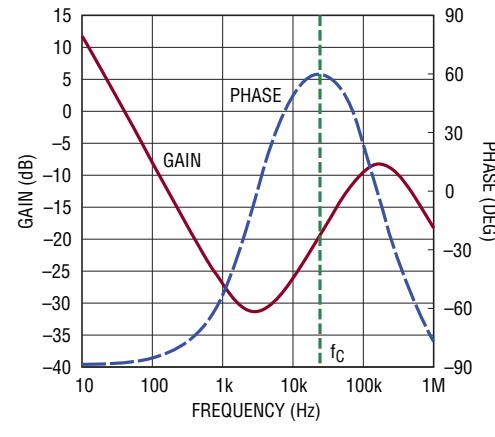

タイプIIIの補償ネットワークのボード線図を図10に示します。タイプIIIの補償ネットワークは原点近くのポールを与え、DCで非常に高いループ利得を生じ、レギュレーション電圧の定常状態の誤差を最小限に抑えます。 $f_{ZERO1}$ と $f_{ZERO2}$ に位置する2個のゼロは十分な位相ブーストを与えるので、ループのクロスオーバー周波数を電力段の共振周波数 $f_0$ より上に設定することができます。タイプIIIの補償ネットワークは2番目と3番目のポールも生じます。周波数 $f_{POLE2}$ に位置する2番目のポールはエラーアンプの利得をゼロ勾配に減少させて、ループのクロスオーバーが高すぎる周波数に拡張するのを防ぎます。周波数 $f_{POLE3}$ に位置する3番目のポールは高周波スイッチング・ノイズを減衰させます。

## アプリケーション情報

図10. タイプIIIの補償のボード線図

補償されたタイプ III のエラーアンプの、抵抗分割器の入力からエラーアンプの出力 VC への伝達関数は次のとおりです。

$$\frac{V_C(s)}{V_{OUT}(s)} = G_{EA} \frac{\left(1 + \frac{s}{2\pi f_{ZERO1}}\right) \left(1 + \frac{s}{2\pi f_{ZERO2}}\right)}{s \left(1 + \frac{s}{2\pi f_{POLE2}}\right) \left(1 + \frac{s}{2\pi f_{POLE3}}\right)}$$

エラーアンプの利得は次式で与えられます。 $C_{FB}$  は一般に  $C_{POLE}$  よりはるかに値が大きいので、ほとんどの場合、簡単な近似値で十分高精度です。

$$G_{EA} = \frac{1}{R_{TOP}(C_{FB} + C_{POLE})} \approx \frac{1}{R_{TOP}C_{FB}}$$

タイプ III の補償ネットワークのポールとゼロの周波数は以下の式を使って計算することができます。ここで、すべての周波数の単位は Hz、抵抗の単位はオーム、容量の単位はファラードです。

$$f_{ZERO1} = \frac{1}{2\pi R_{FB} C_{FB}}$$

$$f_{ZERO2} = \frac{1}{2\pi(R_{TOP} + R_{FF})C_{FF}} \approx \frac{1}{2\pi R_{TOP} C_{FF}}$$

$$f_{POLE2} = \frac{C_{FB} + C_{POLE}}{2\pi C_{FB} C_{POLE} R_{FB}} \approx \frac{1}{2\pi C_{POLE} R_{FB}}$$

$$f_{POLE3} = \frac{1}{2\pi C_{FF} R_{FF}}$$

ほとんどのアプリケーションでは、ループのクロスオーバー周波数は電力段の共振周波数よりは上でも、昇圧モードの右半平面のゼロよりは下になるように補償ネットワークが設計されており、追加の位相遅延が最小限に抑えられています。クロスオーバー周波数が決定されると、位相マージンを最大にするため、補償ネットワークによって与えられる位相ブーストはそのポイントを中心します。ゼロと高次のポールの周波数が大きく離れていると、大きなピーク位相ブーストが与えられますが、エラーアンプの利得も増加して、ループのクロスオーバー周波数を押し上げることがあります。

電力段の Q はどれだけ急速に電力段の 180° の位相遅延が生じるかを決定するので、この Q は補償ネットワークの設計に大きく影響する可能性があります。直列抵抗  $R_S$  の値が非常に小さいと Q が大きくなり、急峻な位相遅延が生じます。このような場合、共振周波数より上で電力段の位相は急速に -180° に遅延し、総位相マージンは補償ネットワークによって与える必要があります。ただし、電力段の損失が大きい ( $R_S$  が大きい) と、Q ファクタは小さくなり、位相遅延は徐々に生じます。その結果、電力段の位相はクロスオーバー周波数で -180° にそれほど近づかず、補償ネットワークに要求される位相ブーストは小さくなります。

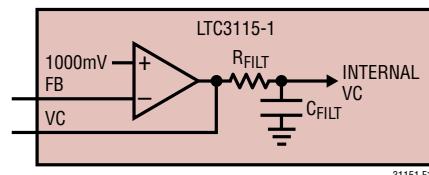

LTC3115-1 のエラーアンプは、スイッチング・ノイズを除去してそれが制御ループに干渉するのを防ぐため、固定最大帯域幅になるように設計されています。周波数領域の観点からは、図 11 に示されているように、これは追加のシングル・ポールと見ることができます。このポールの公称周波数は 300kHz です。約 50kHz より下の標準的ループのクロスオーバー周波数の場合、この追加ポールが寄与する位相は微小です。ただし、クロスオーバー周波数の高いループでは、この追加の位相遅延を考慮に入れて補償ネットワークを設計します。

図11. 内部ループ・フィルタ

## アプリケーション情報

### ループ補償の例

このセクションでは、LTC3115-1の標準的なアプリケーション回路の補償ネットワークの設計を例を使って説明します。この例では、3.5V～30Vの範囲の入力電力源から500mAの負荷に給電する能力のある5V安定化出力電圧を発生します。スイッチング損失を減らすため、この例では750kHzのスイッチング周波数が選択されています。このアプリケーションでは、最大インダクタ電流リップルは最大入力電圧で発生します。ワーストケースのインダクタ電流リップルを約600mAに制限するため、8.2μHのインダクタの値が選択されています。値が20μFの低ESR出力コンデンサが指定され、(ワーストケースの昇圧比と最大負荷電流で生じる)約12mVのワーストケースの出力電圧リップルを生じます。まとめると、このLTC3115-1のアプリケーションの電力段の主な仕様は以下のとおりです。

$$f = 0.75\text{MHz}, t_{\text{LOW}} = 0.1\mu\text{s}$$

$$V_{\text{IN}} = 3.5\text{V} \sim 30\text{V}$$

$$V_{\text{OUT}} = 5\text{V} (500\text{mA})$$

$$C_{\text{OUT}} = 20\mu\text{F}, R_C = 10\text{m}\Omega$$

$$L = 8.2\mu\text{H}, R_L = 45\text{m}\Omega$$

電力段のパラメータが規定されたので、補償ネットワークを設計することができます。ほとんどのアプリケーションでは、最も補償の困難な箇所は最大の昇圧比および最大の負荷電流での昇圧モード動作です。この条件では、周波数が最小の右半平面のゼロが発生し、そのため位相が最も遅延するからです。したがって、妥当な方法として、このワーストケースの箇所で補償ネットワークを設計し、他の動作条件全体で十分な位相マージンが存在することを検証します。このアプリケーションの例( $V_{\text{IN}} = 3.5\text{V}$ 、最大500mAの負荷電流)では、右半平面のゼロは70kHzに位置し、これが制御ループの帯域幅を決定する支配的な要因になります。

補償ネットワークの設計の最初のステップとして、補償されるループの目標クロスオーバー周波数を決定します。妥当な出発点として、補償ネットワークは約60°のピーク位相ブーストを発生するとします。したがって、60°の位相マージンを得るため、ループのクロスオーバー周波数 $f_C$ を、そこで昇降圧コンバータの位相が-180°に達する周波数として選択します。その結果、ループのクロスオーバー周波数では、以下に示すように、合計された位相は単にエラーアンプによって与えられる60°の位相になります。

$$\begin{aligned} \text{位相マージン} &= \phi_{\text{BUCK-BOOST}} + \phi_{\text{ERRORAMPLIFIER}} + 180^\circ \\ &= -180^\circ + 60^\circ + 180^\circ = 60^\circ \end{aligned}$$

同様に、45°の位相マージンが必要であれば、目標とするクロスオーバー周波数は、そこで昇降圧コンバータの位相が-195°に達する周波数を選択して、クロスオーバー周波数での合計位相が望みの45°の位相マージンになるようにします。

この例では、パラメータのばらつきや動作条件の変動にわたって適切な性能が得られるように、60°の位相マージンで設計します。その結果、目標クロスオーバー周波数 $f_C$ はそこで昇降圧コンバータが-180°に達するポイントになります。この周波数を解析的に求めることは、電力段の共振のQファクタに大きく影響されるため、一般に困難です。そのため、図12に示すように、昇降圧コンバータのボード線図から求めるのが最善です。このボード線図は前に規定した電力段のパラメータを使ったLTC3115-1昇降圧コンバータのものであり、LTspice®ソフトウェアを使って小信号モデルの式から作成しました。この場合、位相は24kHzで-180°に達するので、 $f_C = 24\text{kHz}$ が補償ループの目標クロスオーバー周波数になります。

図12のボード線図から、目標クロスオーバー周波数での電力段の利得は19dBです。したがって、この周波数を補償されたループのクロスオーバー周波数にするため、 $f_C$ での全ループ利得を0dBに調整する必要があります。これを達成するため、補償ネットワークの利得を、クロスオーバー周波数で-19dBに設計する必要があります。

## アプリケーション情報

図12. コンバータのボード線図( $V_{IN} = 3.5V$ 、 $I_{LOAD} = 500mA$ )

設計プロセスのこの時点で、補償ネットワークに対して設定された3つの制約があります。その利得は $f_C = 24\text{kHz}$ で $-19\text{dB}$ 、ピーク位相ブーストは $60^\circ$ 、位相ブーストの中心は $f_C = 24\text{kHz}$ でなければなりません。これらの目標を満たす補償ネットワークを設計する1つの方法として、このデータシートの表紙に示されている標準的補償ネットワークの補償されたエラーアンプのボード線図をLTspiceでシミュレーションします。次いで、要求される制約を満たすまで、利得、ポール周波数およびゼロ周波数を繰り返し調整することができます。

代わりに、解析的手法を使って、望みの位相ブースト、中心周波数および利得を備えた補償ネットワークを設計することができます。タイプIIIの補償ネットワークは自由度が大きいため、この手順は一般に容易ではありません。ただし、両方の補償のゼロが同じ周波数 $f_Z$ で生じ、両方の高次ポール( $f_{POLE2}$ と $f_{POLE3}$ )が共通の周波数 $f_P$ で生じると仮定することにより、設計プロセスを簡素化することができます。ほとんどの場合、これは妥当な仮定です。ゼロは一般に $1\text{kHz}$ と $10\text{kHz}$ の間に位置し、ポールは一般にはるかに高い周波数で互いに近くに位置するからです。これを仮定すると、補償されたエラーアンプによって与えられる最大位相ブースト $f_{MAX}$ は、次式で示されるように、単にポールとゼロの間隔によって決まります。

$$\phi_{MAX} = 4 \tan^{-1} \left( \sqrt{\frac{f_P}{f_Z}} \right) - 270^\circ$$

妥当な選択として、ポールの周波数 $f_P$ がゼロの周波数 $f_Z$ の約50倍になるように選択します。これにより、前に仮定したように、約 $\phi_{MAX} = 60^\circ$ のピーク位相ブーストが与えられます。次に、ピーク位相が目標クロスオーバー周波数で生じるように位相ブーストの中心を定める必要があります。最大位相ブーストの周波数 $f_{CENTER}$ は、次のようにポール周波数とゼロ周波数の相乗平均になります。

$$f_{CENTER} = \sqrt{f_P \cdot f_Z} = \sqrt{50} \cdot f_Z \approx 7 \cdot f_Z$$

したがって、ポール周波数とゼロ周波数の間に50倍の開きがある場合に位相の中心を定めるには、以下の式で与えられているように、ゼロをクロスオーバー周波数の $1/7$ に位置させ、ポールをクロスオーバー周波数の7倍に位置させます。

$$f_Z = \frac{1}{7} \cdot f_C = \frac{1}{7} (24\text{kHz}) = 3.43\text{kHz}$$

$$f_P = 7 \cdot f_C = 7 (24\text{kHz}) = 168\text{kHz}$$

ポールとゼロのこの配置により、クロスオーバー周波数 $f_C$ を中心とした $60^\circ$ のピーク位相ブーストが生じます。次に、望みの目標クロスオーバー周波数を実現するため、最大位相ブースト・ポイントでの補償ネットワークの利得 $G_{CENTER}$ を $-19\text{dB}$ に設定する必要があります。最大位相利得のポイントでの補償されたエラーアンプの利得は次式で与えられます。

$$G_{CENTER} = 10 \log \left[ \frac{2\pi f_P}{(2\pi f_Z)^3 (R_{TOP} C_{FB})^2} \right] \text{dB}$$

## アプリケーション情報

ポール周波数とゼロ周波数の間の50倍の開きを仮定すると、上式は次式に簡略化されます。

$$G_{\text{CENTER}} = 20 \log \left[ \frac{50}{2\pi f_C R_{\text{TOP}} C_{\text{FB}}} \right] \text{dB}$$

この式は補償部品の値の決定に必要な1組の制約をすべて満たします。特に、2つのゼロ( $f_{\text{ZERO1}}$ と $f_{\text{ZERO2}}$ )は3.43kHzの近くに位置させます。2つのポール( $f_{\text{POLE2}}$ と $f_{\text{POLE3}}$ )は168kHzの近くに位置させ、クロスオーバー周波数の利得 $G_{\text{CENTER}} = -19\text{dB}$ となるように利得を設定します。

補償部品の値を定める最初のステップとして、抵抗分割器を流れる静止電流を許容できる程度に小さくする $R_{\text{TOP}}$ の値を選択します。妥当な選択値は $R_{\text{TOP}} = 1\text{M}\Omega$ です。次に、クロスオーバー周波数でのエラーアンプの利得を-19dBに設定するため、 $C_{\text{FB}}$ の値を次のように求めることができます。

$$G_{\text{CENTER}} = -19.1\text{dB}$$

$$= 20 \log \left[ \frac{50}{2\pi(24\text{kHz})(1\text{M}\Omega)C_{\text{FB}}} \right]$$

$$C_{\text{FB}} = \frac{50}{2\pi(24\text{kHz})(1\text{M}\Omega) \text{a} \log \left( \frac{-19.1}{20} \right)} \approx 3.0\text{nF}$$

前のセクションに与えられているポールとゼロの周波数の式を使って、補償ポールを168kHzに、ゼロを3.43kHzに設定することができます。最初のゼロの周波数 $f_{\text{ZERO1}}$ を3.43kHzに設定すると、 $R_{\text{FB}}$ は次の値になります。

$$R_{\text{FB}} = \frac{1}{2\pi(3\text{nF})(3.43\text{kHz})} \approx 15.4\text{k}\Omega$$

これにより、自由なパラメータ $C_{\text{POLE}}$ が次のように、周波数 $f_{\text{POLE1}}$ を168kHzの共通ポール周波数に設定します。

$$C_{\text{POLE}} = \frac{1}{2\pi(15.4\text{k}\Omega)(168\text{kHz})} \approx 62\text{pF}$$

次に、 $C_{\text{FF}}$ を選択して、2番目のゼロ $f_{\text{ZERO2}}$ を3.43kHzの共通ゼロ周波数に設定することができます。

$$C_{\text{FF}} = \frac{1}{2\pi(1\text{M}\Omega)(3.43\text{kHz})} \approx 47\text{pF}$$

最後に、抵抗値 $R_{\text{FF}}$ を選択して2番目のポールを168kHzに配置することができます。

$$R_{\text{FF}} = \frac{1}{2\pi(47\text{pF})(168\text{Hz})} \approx 20.0\text{k}\Omega$$

補償ネットワークのポール周波数、ゼロ周波数および利得が確定したので、次のステップでは、補償されたエラーアンプのボード線図を作成して利得と位相の特性を確認します。設計された補償部品の値を使ったエラーアンプのボード線図を図13に示します。ボード線図から、ピーク位相が24kHzに生じ、そのポイントの位相ブーストが57.7°であることが確認できます。さらに、ピーク位相周波数での利得は-19.3dBで、設計目標に近い値です。

図13. 補償されたエラーアンプのボード線図

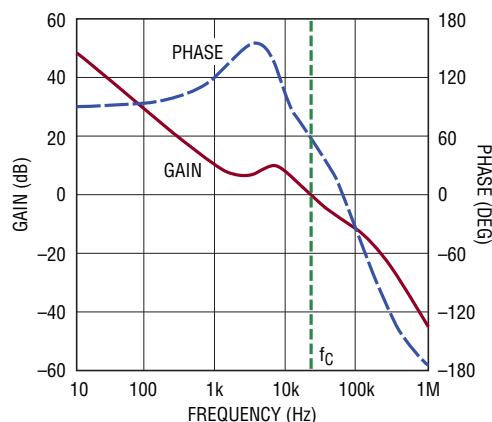

## アプリケーション情報

設計プロセスの最後のステップとして、設計された補償ネットワークを使ってループ全体のボード線図を計算し、その位相マージンとクロスオーバー周波数を確認します。この例のループ全体のボード線図を図14に示します。ループのクロスオーバー周波数は設計目標に近い22kHzで、位相マージンは約60°です。

ループ全体のボード線図を全動作条件および部品の値のばらつきに対してチェックして、すべての場合に十分な位相マージンが存在することを確認します。時間領域のシミュレーションによって、また実際の回路でコンバータのトランジエント応答を評価して、ループの安定性も確認します。

### 出力電圧の設定

図8と図9に示すように、出力電圧は抵抗 $R_{TOP}$ および $R_{BOT}$ で構成される外付け抵抗分割器によって設定されます。抵抗分割器の値は次式に従って出力のレギュレーション電圧を決定します。

$$V_{OUT} = 1.000V \left( 1 + \frac{R_{TOP}}{R_{BOT}} \right)$$

31151 F14

図14. ループ全体のボード線図

出力電圧の設定に加えて、 $R_{TOP}$ の値は補償ネットワークの動作を制御する手段にもなります。この抵抗の値を変更するときは、それが補償ネットワークに与える影響を理解する必要があります。

さらに、抵抗分割器のテブナン等価抵抗によって電流制限の利得が制御されます。このループで十分な利得を維持するためには、 $1M\Omega$ 以上の $R_{TOP}$ の値を選択することを推奨します。

### スイッチング周波数の選択

スイッチング周波数は、 $RT$ ピンとグランドの間に接続された抵抗の値によって設定されます。スイッチング周波数 $f$ は次式のように抵抗値と相関関係があります。ここで、 $R_T$ は抵抗です。

$$f = \frac{35.7\text{MHz}}{(R_T/k\Omega)}$$

スイッチング周波数を高くすると、小さなインダクタとともに小さな入力と出力のフィルタ・コンデンサを使用することができる所以、ソリューション・サイズが小さくなつて部品の高さが低くなります。ただし、スイッチング周波数を高くすることは、一般に、スイッチング損失が増すことによって変換効率を低下させることになります。

さらに、スイッチング周波数が高くなる(750kHz以上)と、供給可能な最大出力電流が減少します(詳細については「標準的性能特性」を参照)。 $V_{OUT} \geq 20V$ のアプリケーションでは、 $1MHz$ の最大スイッチング周波数を推奨します。

## アプリケーション情報

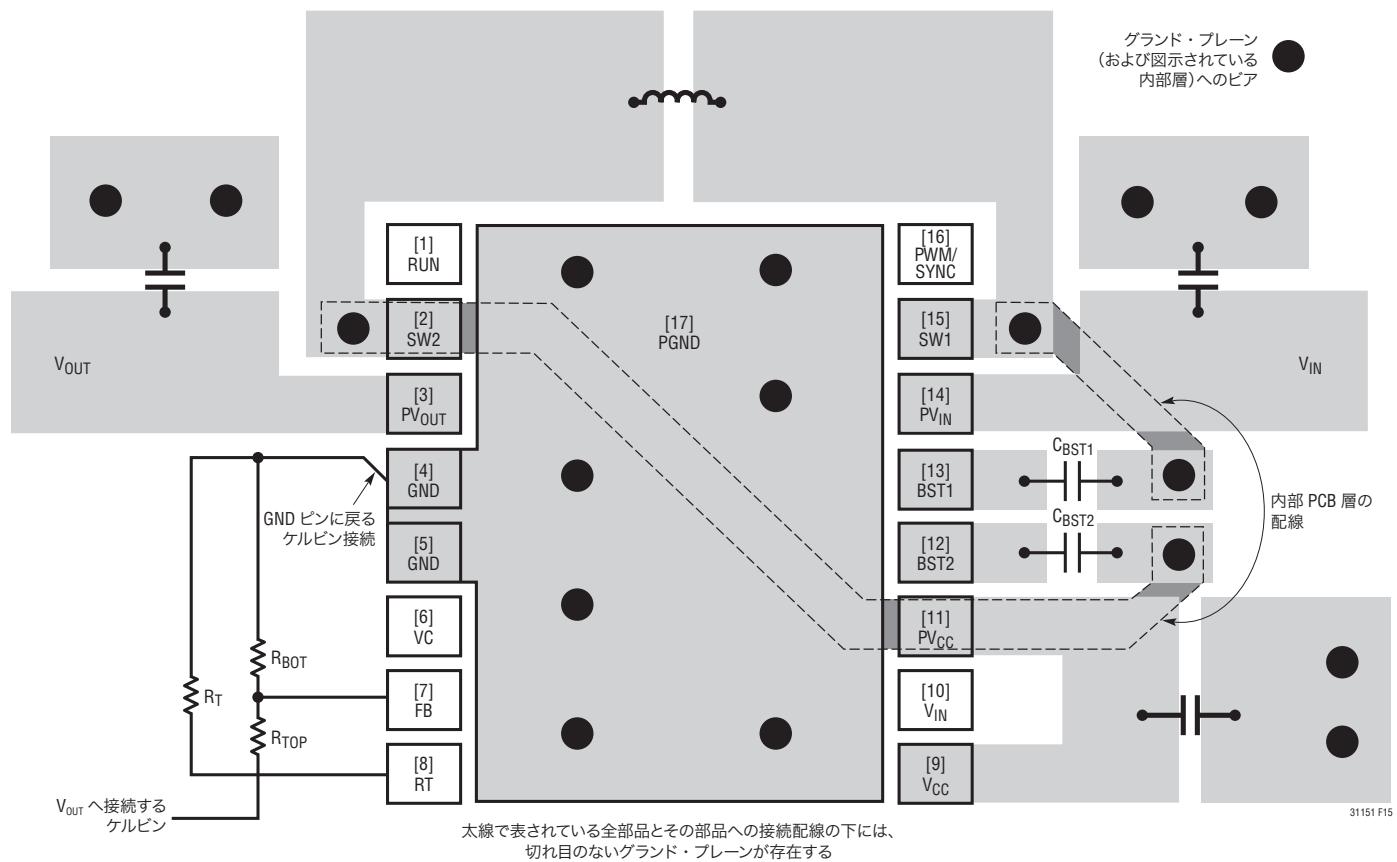

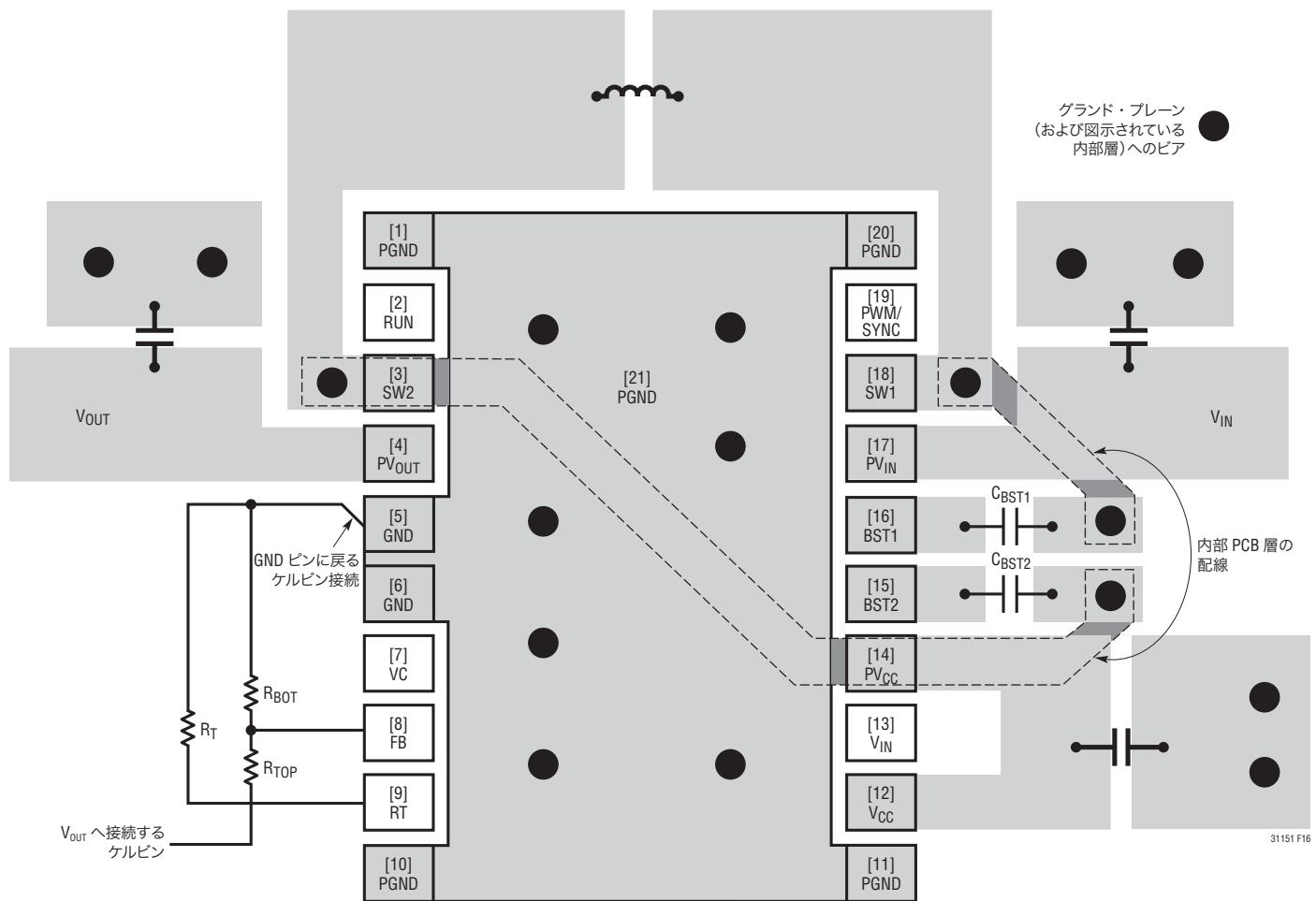

### PCBのレイアウトに関する検討事項

LTC3115-1の昇降圧コンバータは大きな電流を高い周波数でスイッチングします。安定したノイズのない効率の良いアプリケーション回路にするには、PC基板レイアウトに特に注意する必要があります。図15と図16は各パッケージの代表的なPCBレイアウトで、主な検討事項のいくつかを示しています。主なガイドラインを以下に説明します。

1. 循環するすべての高電流経路の寄生インダクタンスと寄生抵抗を最小限に抑えます。これは図15と図16の太線で表されているすべての部品への配線をできるだけ短くかつ幅広くすることによって実現できます。コンデンサのグランドはできるだけ短い配線を通し、ビアを使ってグランド・プレーンに接続します。PV<sub>IN</sub>、PV<sub>OUT</sub>、およびPV<sub>CC/VCC</sub>のバイパス・コンデンサはできるだけデバイスの近くに配置し、グランドへの経路をできるだけ短くします。

2. DHDパッケージのLTC3115-1では、露出パッドが電源グランドに電気的に接続されています。多数のビアで背面パッドを直接グランド・プレーンに接続します。さらに、背面パッドに接続されるメタルを最大にすると温度環境が改善され、FEとDHDのどちらのパッケージのデバイスの電力処理能力も改善されます。

3. 太線で表されている部品とそれらの接続はすべて完全なグランド・プレーン上に配置し、ループの断面積を最小限に抑えます。これにより、EMIが最小限に抑えられ、誘導性の電圧降下が減ります。

4. 太線で表されているすべての部品への接続をできるだけ幅広くして直列抵抗を減らします。これにより、効率が改善され、昇降圧コンバータの出力電流能力が最大化されます。

5. グランド・プレーンの大きな循環電流がLTC3115-1の動作を妨害しないように、すべての小信号グランドは専用のケルビン(4線)配線を経由してGNDに直接戻します。これには、図15と図16に示すように、RTピンの抵抗のグランド接続と帰還ネットワークのグランド接続が含まれます。

6. 高インピーダンスでノイズに敏感な入力FBおよびRTに接続する配線は、ノイズの混入を減らすためにできるだけ短くします。

7. BST1ピンとBST2ピンは、スイッチング周波数でそれぞれ最大入力電圧と最大出力電圧まで遷移します。ノイズの放射と結合を最小限に抑えるため、BST1とBST2の配線はできるだけ短くし、すべての敏感な回路やピン(VC、FB、RT)から離します。多くのアプリケーションでは、昇圧コンデンサをPC基板の裏面に配置し、内部銅箔層のトレースを介して配線することにより、昇圧コンデンサに接続するトレース長を最小限に抑えることができます。

## アプリケーション情報

図15.DHDパッケージの推奨PCBレイアウト

## アプリケーション情報

図16.FEパッケージの推奨PCBレイアウト

## 標準的応用例

広入力電圧範囲(2.7V~40V)、高効率300kHz、低ノイズ5Vレギュレータ

$C_{IN}$ : MURATA GRM55DR61H106K

$C_0$ : POSCAP 6TPB330M (7.3mm × 4.3mm × 2.8mm)

$D1$ : PANASONIC MA785

$L1$ : COILCRAFT MSS1260

PWMモードの効率と負荷電流

31151 TA02b

PWMモードの効率と負荷電流

31151 TA02c

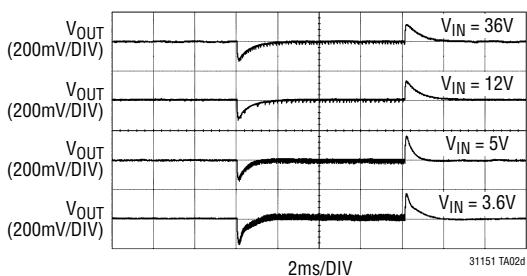

0Aから1Aの負荷ステップに対する $V_{OUT}$ トランジエント

2ms/DIV

0Aから2Aの負荷ステップに対する $V_{OUT}$ トランジエント( $V_{IN} = 24V$ )

2ms/DIV

31151fa

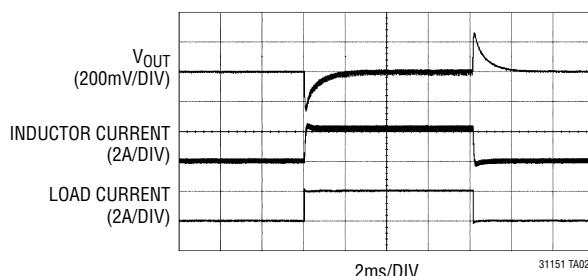

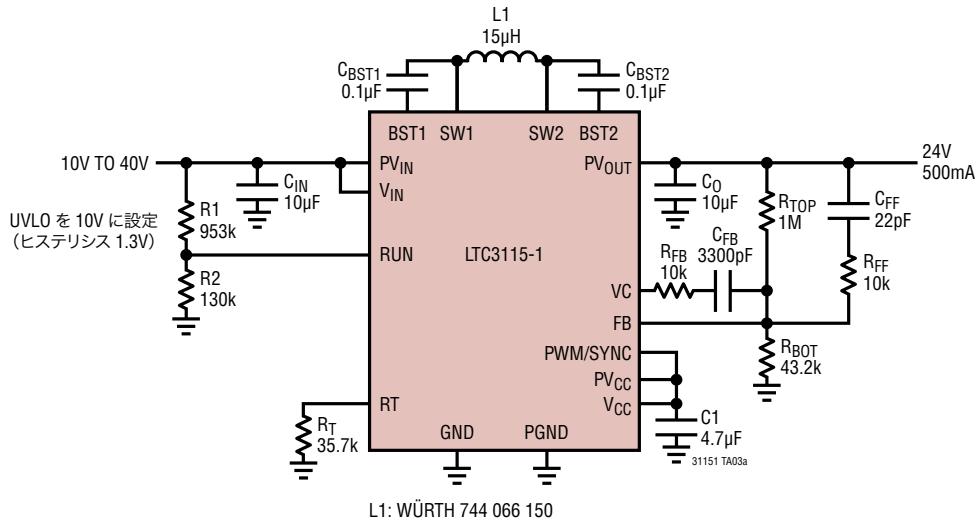

## 標準的応用例

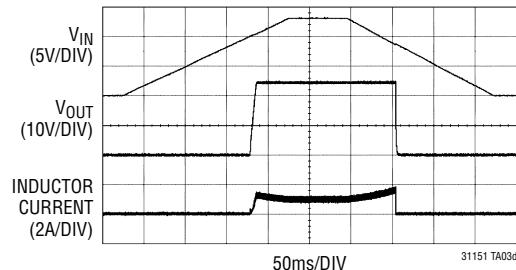

広入力電圧範囲(10V～40V)、1MHz、24V/500mA電源

最大負荷電流と  $V_{IN}$

31151 TA03b

効率と  $V_{IN}$

31151 TA03c

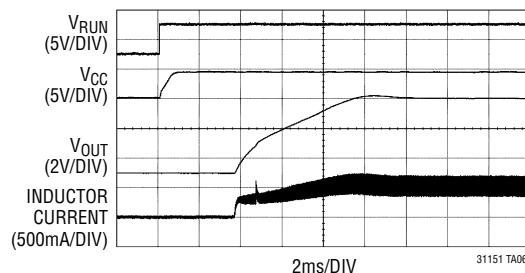

パワーアップ/パワーダウン波形

( $I_{LOAD} = 0.5A$ )

31151 TA03d

31151fa

## 標準的應用例

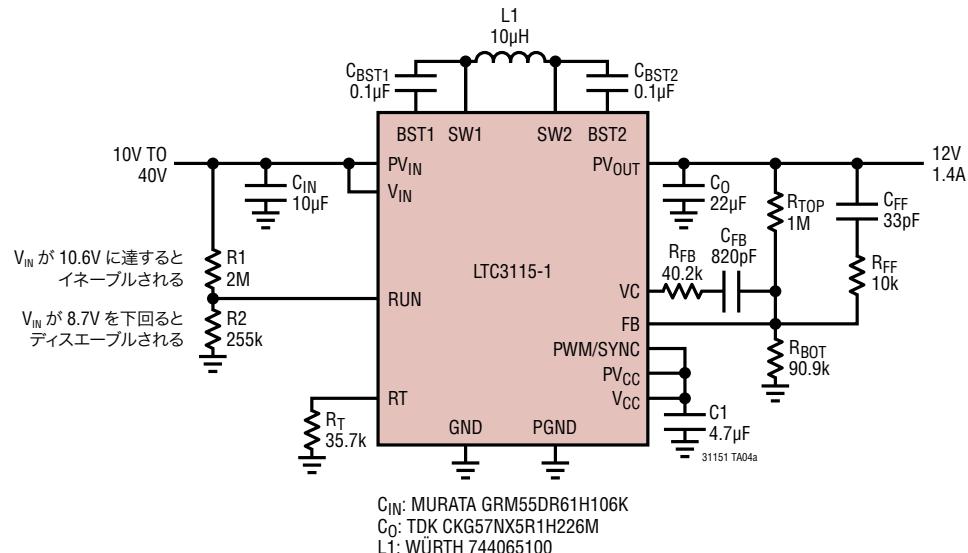

個別の入力低電圧ロックアウトしきい値を備えた産業用 12V、1MHz レギュレータ

## 標準的応用例

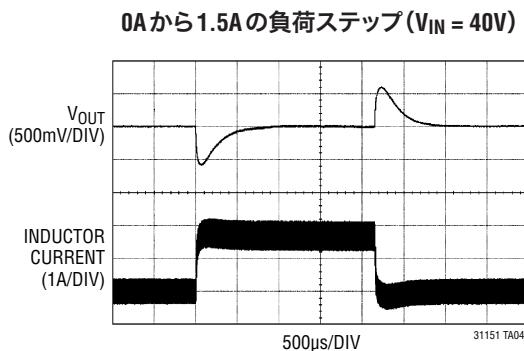

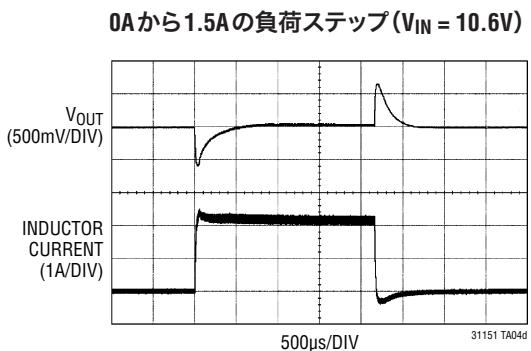

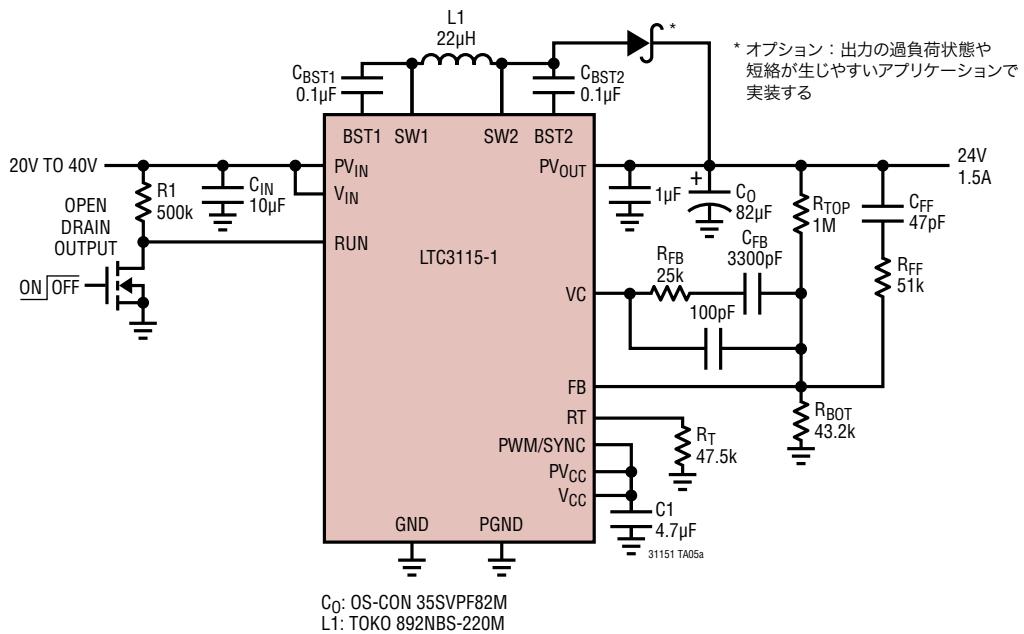

### 24V、750kHz産業用レール補償回路

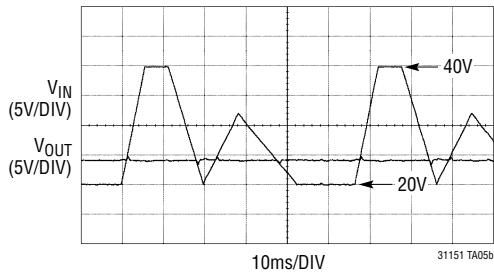

時間的に変化する入力レールからの

安定化出力電圧

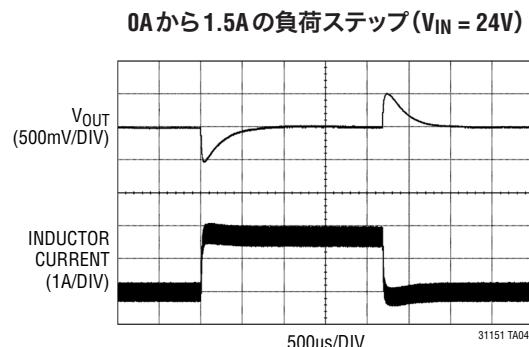

0Aから1.5Aの負荷ステップ( $V_{IN} = 20V$ )

効率と負荷電流

31151fa

## 標準的応用例

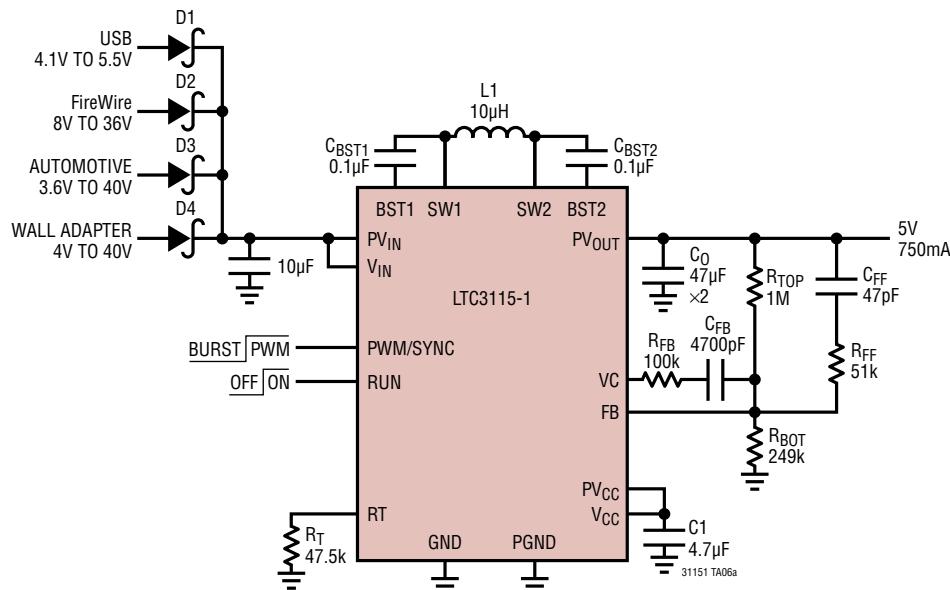

USB、FireWire、自動車、および非安定化ACアダプタの電源を5Vに安定化(750kHz)

$C_{IN}$ : MURATA GRM55DR61H106K $C_0$ : GRM43ER60J476

D1-D4: B360A-13-F

L1: COILCRAFT LPS6225

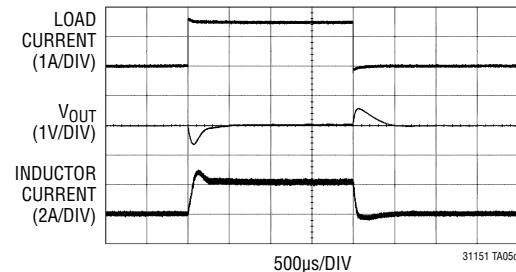

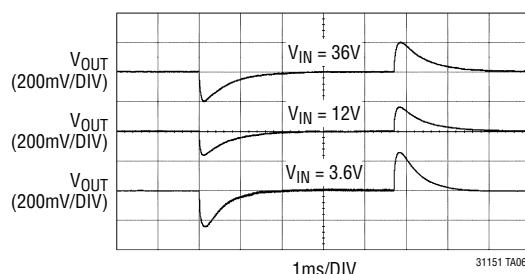

ソフトスタート波形( $V_{IN} = 24V$ 、 $I_{LOAD} = 0.5A$ )出力電圧のトランジエント応答

(750mAの負荷ステップ、自動車用入力から給電)

31151fa

## 標準的応用例

小型サイズの1.5MHz、12V電源

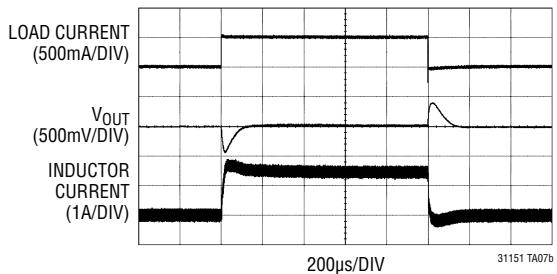

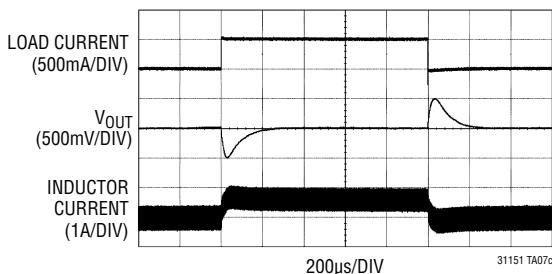

負荷ステップのトランジエント応答

(0mAから500mA、V<sub>IN</sub> = 6V)

負荷ステップのトランジエント応答

(0mAから500mA、V<sub>IN</sub> = 24V)

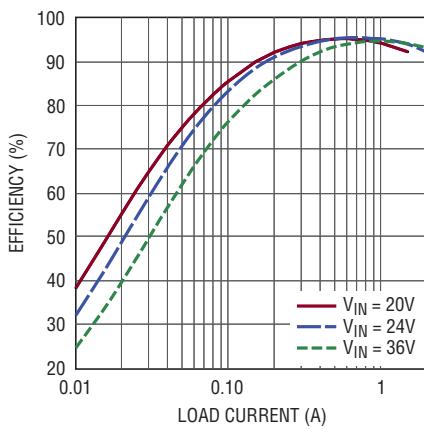

効率と出力電流(PWMモード)

効率と負荷電流(Burst Mode動作)

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/design-tools/packaging/> を参照してください。

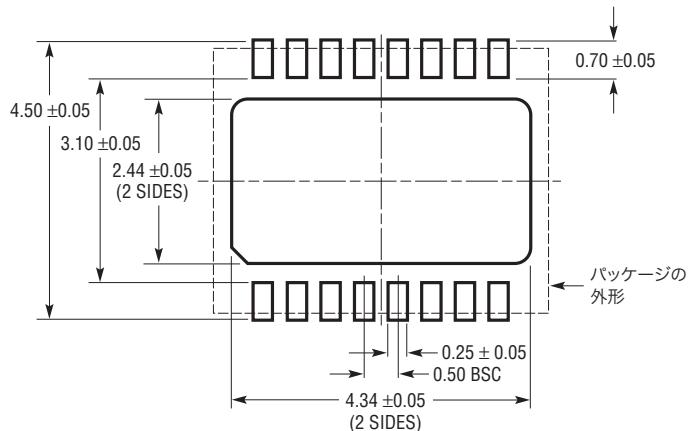

**DHDパッケージ

16ピン・プラスチックDFN(5mm×4mm)**

(Reference LTC DWG # 05-08-1707)

推奨する半田パッドのピッチと寸法

- NOTE:

1. 図は JEDEC パッケージ・アウトライン MO-229 のバージョンのバリエーション (WJGD-2) として提案

2. 図は実寸とは異なる

3. すべての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで 0.15mm を超えないこと

5. 露出パッドは半田メッキとする

6. 灰色の部分はパッケージの上面と底面のピン 1 の位置の参考に過ぎない

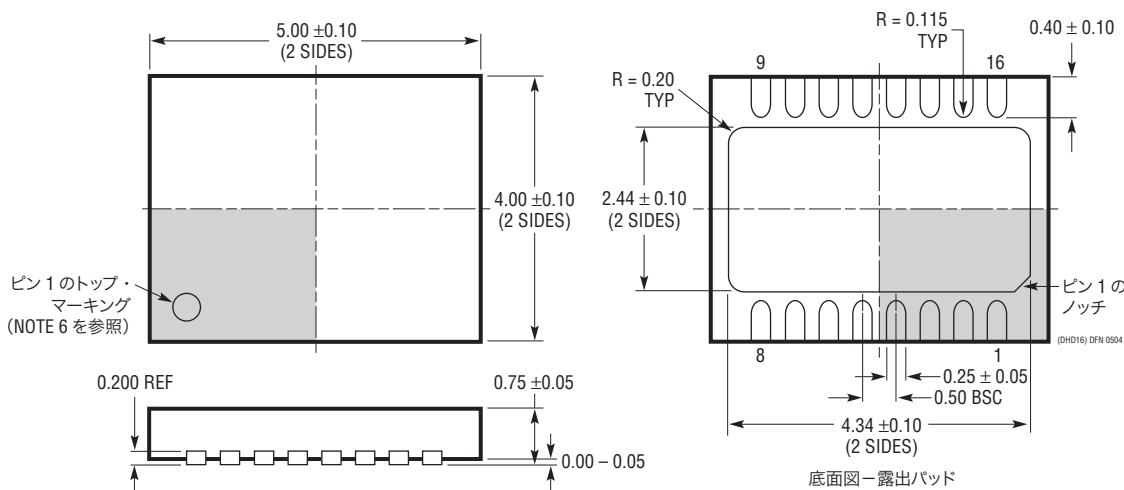

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging> を参照してください。

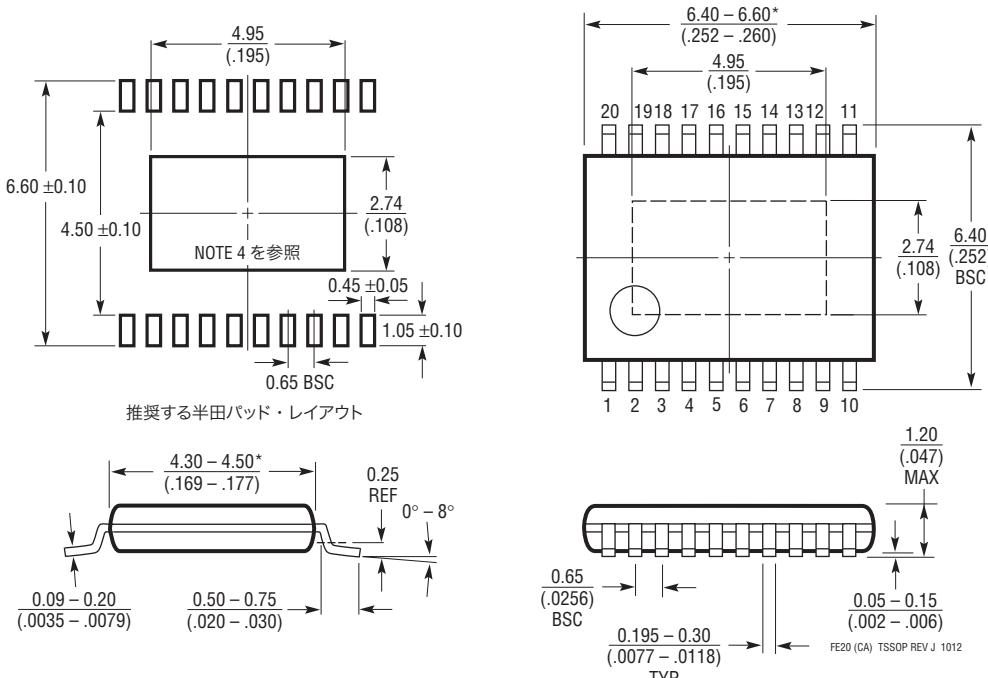

FEパッケージ

20ピン・プラスチックTSSOP(4.4mm)

(Reference LTC DWG # 05-08-1663 Rev J)

露出パッドのバリエーションCA

## 改訂履歴

| REV | 日付   | 概要                                                                              | ページ番号                   |

|-----|------|---------------------------------------------------------------------------------|-------------------------|

| A   | 4/13 | 効率のグラフを明確化。<br>絶対最大定格、パッケージ図、発注情報を明確化。<br>電気的特性表を明確化。<br>ピン機能を明確化。<br>補償の式を明確化。 | 1<br>2<br>3<br>11<br>25 |

## 標準的応用例

### コールドクランクに対応できる自動車用 750kHz、5V レギュレータ

\* オプション : D1 を実装することにより、効率を高め入力動作電圧を低くすることが可能

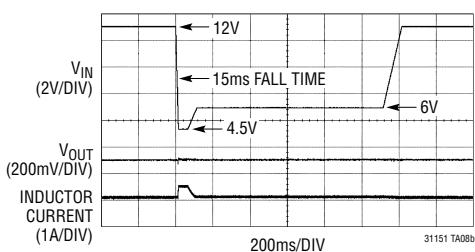

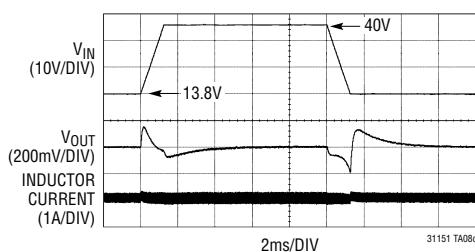

#### 1A負荷でのコールドクランク時 入力トランジエント

#### 1A負荷での負荷遮断時 入力トランジエント

#### 効率と負荷電流 V IN = 12V

31151 TA08d

## 関連製品

| 製品番号    | 説明                                                 | 注釈                                                                                    |

|---------|----------------------------------------------------|---------------------------------------------------------------------------------------|

| LTC3112 | 2.5A (I OUT)、15V 同期整流式昇降圧 DC/DC コンバータ              | V IN: 2.7V ~ 15V、V OUT: 2.5V ~ 14V、I Q = 40μA、ISD < 1μA、DFN および TSSOP パッケージ           |

| LTC3113 | 3A (I OUT)、2MHz 同期整流式昇降圧 DC/DC コンバータ               | V IN: 1.8V ~ 5.5V、V OUT: 1.8V ~ 5.25V、I Q = 30μA、ISD < 1μA、DFN および TSSOP パッケージ        |

| LTC3127 | 1A (I OUT)、1.2MHz 昇降圧 DC/DC コンバータ、プログラム可能な入力電流制限付き | 96% の効率、V IN: 1.8V ~ 5.5V、V OUT: 1.8V ~ 5.25V、I Q = 35μA、ISD < 4μA、MSOP および DFN パッケージ |

| LTC3789 | 高効率、同期整流式、4スイッチ昇降圧コントローラ                           | V IN: 4V ~ 38V、V OUT: 0.8V ~ 38V、I Q = 3mA、ISD < 60μA、SSOP-28 および QFN-28 パッケージ        |

| LTC3785 | ≤10A (I OUT)、高効率、1MHz 同期整流式、No RSENSE™ 昇降圧コントローラ   | V IN: 2.7V ~ 10V、V OUT: 2.7V ~ 10V、I Q = 86μA、ISD < 15μA、QFN パッケージ                    |

| LTC3534 | 7V、500mA (I OUT)、1MHz 同期整流式昇降圧 DC/DC コンバータ         | 94% の効率、V IN: 2.4V ~ 7V、V OUT: 1.8V ~ 7V、I Q = 25μA、ISD < 1μA、DFN および GN パッケージ        |

31151fa