## 特長

- 出力電圧より高い、低い、または等しい入力電圧で出力電圧を安定化

- 入力電圧範囲: 2.7V~15V

- 出力電圧範囲: 2.5V~14V

- 2.5Aの連続出力電流:  $V_{IN} \geq 5V$ ,  $V_{OUT} = 5V$ , PWMモード

- 出力電流モニタ

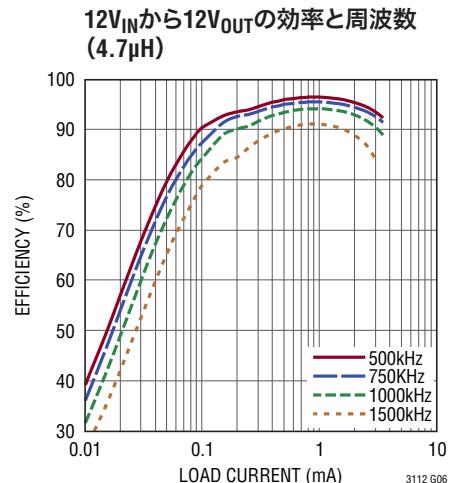

- 効率: 最大95%

- 750kHzのスイッチング周波数、300kHz~1.5MHzの範囲で同期可能

- NチャネルMOSFET内蔵

- 選択可能なBurst Mode<sup>®</sup>動作、 $I_Q = 50\mu A$

- シャットダウン電流: 1μA未満

- 過電圧保護

- シャットダウン時の出力切断

- 内部ソフトスタート

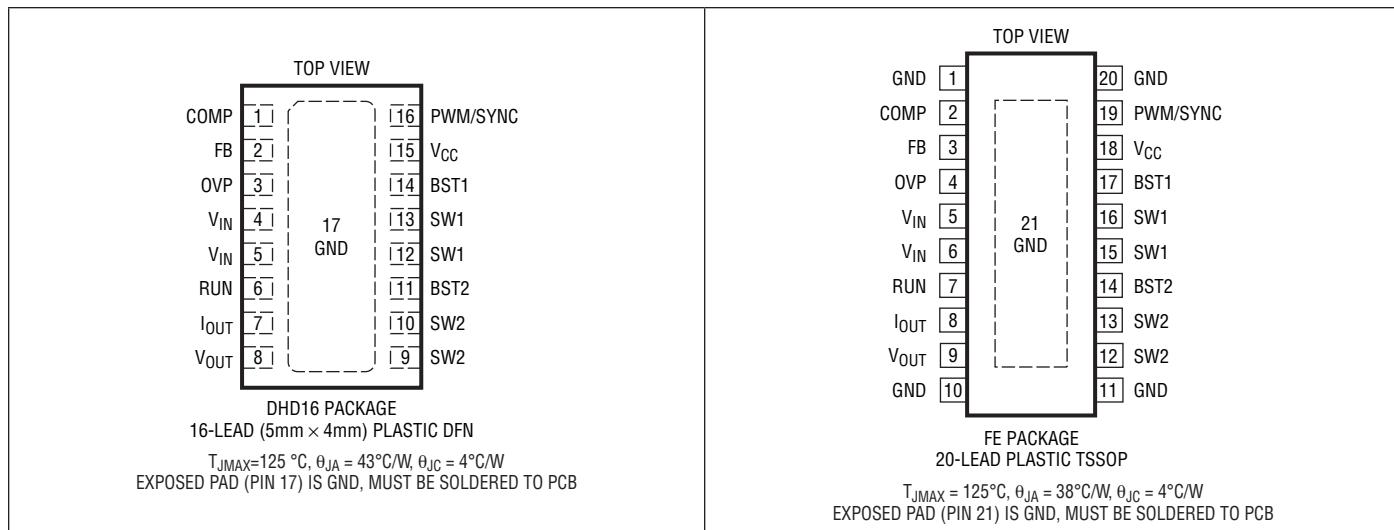

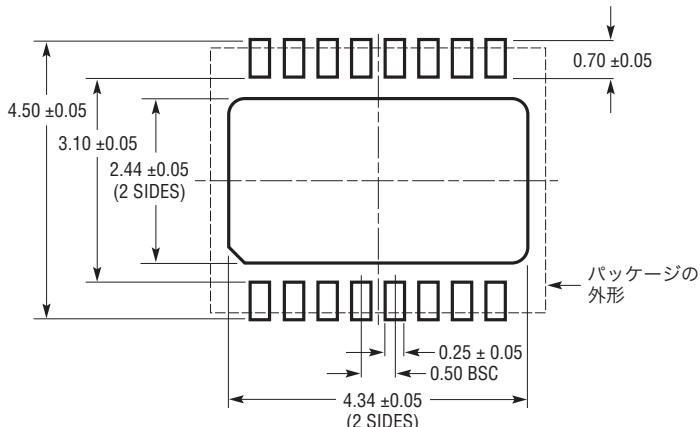

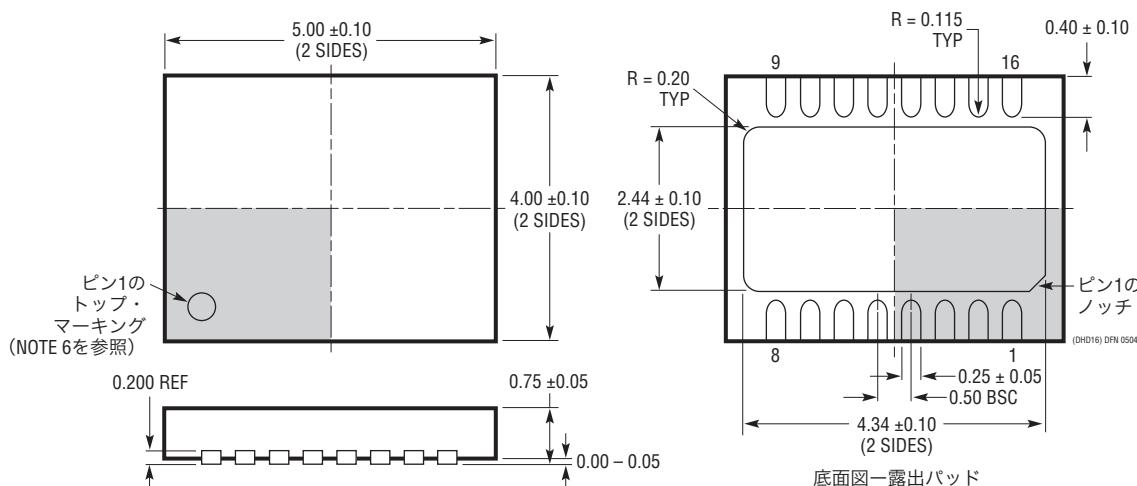

- 熱特性が改善された小型16ピン (4mm×5mm×0.75mm) DFNまたは20ピンTSSOPパッケージ

## アプリケーション

- 1セル、2セルまたは3セルのリチウムイオン・バッテリ、バッカアップ・コンデンサ・スタックによる3.3Vまたは5Vの供給

- ハンドヘルド在庫端末

- RFトランスマッタ

- 12V同期整流式昇圧コンバータ

- 複合電源入力システム

- 電流レギュレーション機能を備えたLED照明

- 12V鉛蓄電池を入力とする12V出力

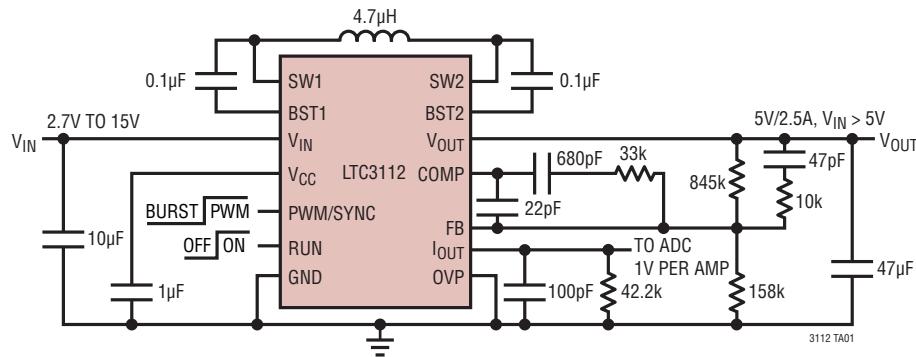

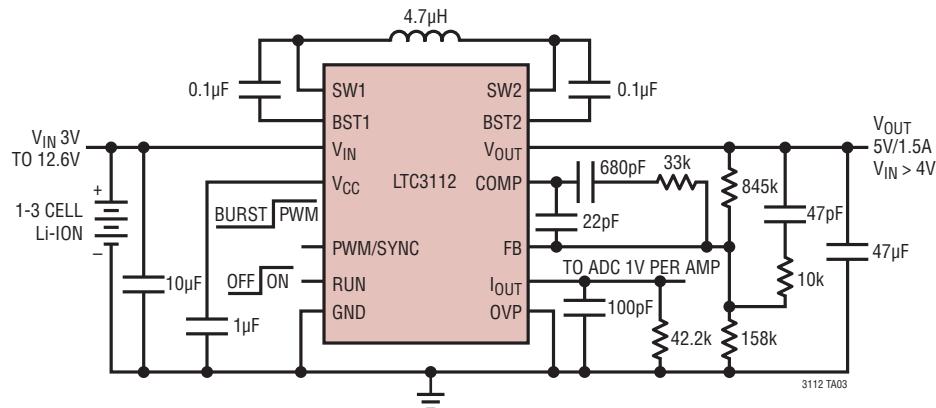

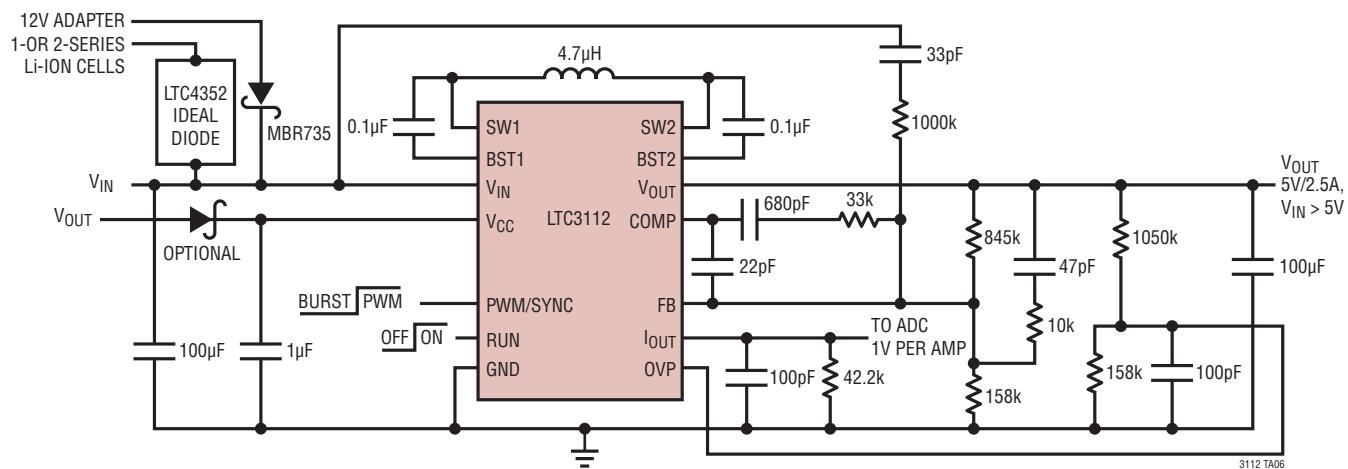

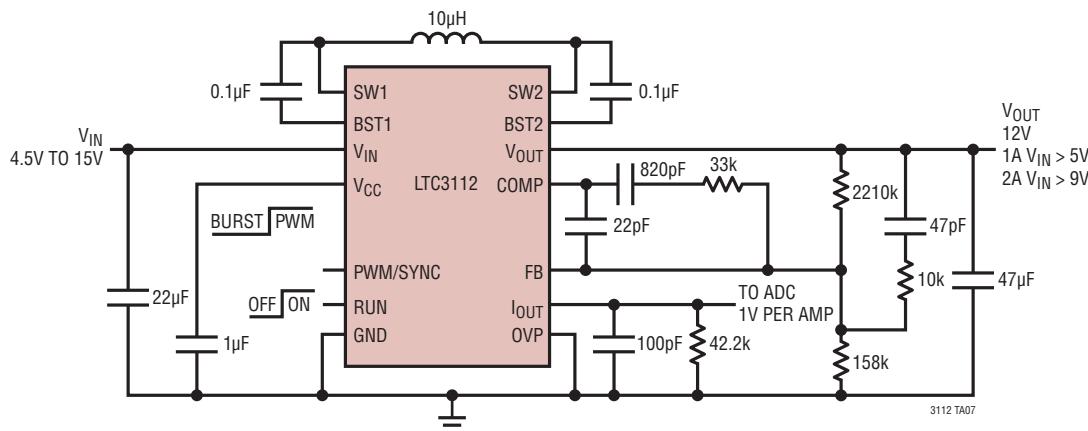

## 標準的応用例

入力電圧の広い、5V、750kHz昇降圧レギュレータ

## 概要

LTC<sup>®</sup>3112は、入力および出力電圧範囲の広い固定周波数同期整流式昇降圧DC/DCコンバータです。独自の4スイッチ・シングル・インダクタ・アーキテクチャにより、出力電圧より高い、低い、または等しい入力電圧から低ノイズで継ぎ目のない動作を実現します。

LTC3112は入力電圧範囲が2.7V~15Vと広いので、1セルまたは複数セルのバッテリ、バックアップ・コンデンサ、ACアダプタなどのさまざまな電源アプリケーションに適しています。内蔵のNチャネルMOSFETスイッチはRDS(ON)が低いので、大きな負荷電流が要求されるアプリケーションで高効率で動作します。

LTC3112は選択可能なPWMまたはBurst Mode動作、容易に同期可能な発振器、シャットダウン時の出力切断を特長としています。出力電流モニタ回路により、負荷電流の制御または測定が可能です。このほかに、1μA未満のシャットダウン電流、短絡保護、ソフトスタート、電流制限、サーマル・シャットダウンなどの特長を備えています。

LTC3112は16ピン(4mm×5mm×0.75mm)DFNパッケージと20ピンTSSOPパッケージで供給されます。

**L**、LT、LTC、LTM、Linear Technology、Burst Mode、LTSpice および Linear のロゴはリニアテクノロジー社の登録商標です。No RSENSE および PowerPath はリニアテクノロジー社の商標です。他の全ての商標はそれぞれの所有者に所有権があります。5481178 を含む米国特許によって保護されています。

## 絶対最大定格

### (Note 1,3)

|                 |                                       |

|-----------------|---------------------------------------|

| $V_{IN}$ 電圧     | -0.3V~16V                             |

| $V_{OUT}$ 電圧    | -0.3V~15V                             |

| SW1の電圧 (Note 4) | -0.3V~( $V_{IN}$ + 0.3V)              |

| SW2の電圧 (Note 4) | -0.3V~( $V_{OUT}$ + 0.3V)             |

| $V_{BST1}$ の電圧  | ( $V_{SW1}$ - 0.3V)~( $V_{SW1}$ + 6V) |

| $V_{BST2}$ の電圧  | ( $V_{SW2}$ - 0.3V)~( $V_{SW2}$ + 6V) |

|                                    |             |

|------------------------------------|-------------|

| RUNの電圧                             | -0.3V~16V   |

| PWM/SYNC、 $V_{CC}$ 、 $I_{OUT}$ の電圧 | -0.3V~6V    |

| FB、COMP、OVPの電圧                     | -0.3V~6V    |

| 動作接合部温度範囲 (Note 2, 6)              | -40°C~125°C |

| 最大接合部温度 (Note 3)                   | 125°C       |

| 保存温度範囲                             | -65°C~150°C |

| リード温度(半田付け、10秒)、TSSOP              | 300°C       |

## ピン配置

## 発注情報

| 鉛フリー仕様          | テープアンドリール         | 製品マーキング* | パッケージ                           | 温度範囲           |

|-----------------|-------------------|----------|---------------------------------|----------------|

| LTC3112EDHD#PBF | LTC3112EDHD#TRPBF | 3112     | 16-Lead (5mm × 4mm) Plastic DFN | -40°C to 125°C |

| LTC3112IDHD#PBF | LTC3112IDHD#TRPBF | 3112     | 16-Lead (5mm × 4mm) Plastic DFN | -40°C to 125°C |

| LTC3112EFE#PBF  | LTC3112EFE#TRPBF  | 3112FE   | 20-Lead Plastic TSSOP           | -40°C to 125°C |

| LTC3112IFE#PBF  | LTC3112IFE#TRPBF  | 3112FE   | 20-Lead Plastic TSSOP           | -40°C to 125°C |

より広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

鉛ベースの非標準仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー製品のマーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

**電気的特性**

●は全動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 2)。

注記がない限り、 $V_{IN} = V_{OUT} = \text{PWM/SYNC} = \text{RUN} = 5\text{V}$ 。

| PARAMETER                                | CONDITIONS                                                                                            | MIN          | TYP           | MAX            | UNITS                                           |   |

|------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------|---------------|----------------|-------------------------------------------------|---|

| Input Operating Range                    | 0°C to 125°C<br>-40°C to 0°C                                                                          | 2.7<br>2.85  | 15<br>15      |                | V                                               |   |

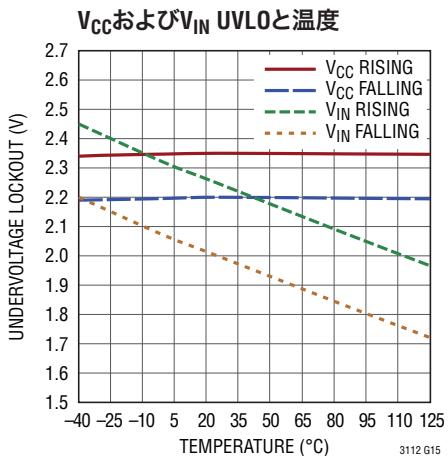

| $V_{IN}$ UVLO Threshold                  | Rising                                                                                                | 2.0          | 2.3           | 2.7            | V                                               |   |

| $V_{IN}$ UVLO Hysteresis                 |                                                                                                       |              | 300           |                | mV                                              |   |

| $V_{CC}$ UVLO Threshold                  | Rising                                                                                                | ● 2.2        | 2.35          | 2.5            | V                                               |   |

| $V_{CC}$ UVLO Hysteresis                 |                                                                                                       |              | 150           |                | mV                                              |   |

| Output Voltage Adjust Range              |                                                                                                       | ● 2.5        |               | 14             | V                                               |   |

| INT $V_{CC}$ Clamp Voltage               | $V_{IN} = 5\text{V}$ or $15\text{V}$                                                                  | ● 3.8        | 4.2           | 4.6            | V                                               |   |

| $V_{CC}$ Voltage in Dropout              | $V_{IN} = 2.7\text{V}$ , $I_{VCC} = 10\text{mA}$                                                      |              | 2.6           |                | V                                               |   |

| Quiescent Current – Burst Mode Operation | $V_{FB} = 1\text{V}$ , $V_{PWM/SYNC} = 0\text{V}$                                                     |              | 50            | 75             | $\mu\text{A}$                                   |   |

| Quiescent Current – Shutdown             | $\text{RUN} = V_{OUT} = V_{CC} = 0\text{V}$ , Not Including Switch Leakage                            |              | 0             | 1              | $\mu\text{A}$                                   |   |

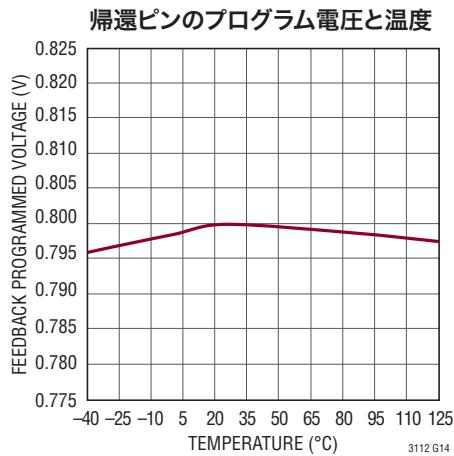

| Feedback Voltage = PWM Mode Operation    |                                                                                                       | ● 0.778      | 0.8           | 0.818          | V                                               |   |

| Feedback Leakage                         | $V_{FB} = 0.8\text{V}$                                                                                |              | 0             | 50             | nA                                              |   |

| OVP Threshold                            | Rising Threshold                                                                                      | 0.78         | 0.83          | 0.88           | V                                               |   |

| OVP Hysteresis                           | Measured at OVP Pin                                                                                   |              | 20            |                | mV                                              |   |

| OVP Leakage                              | OVP = 0.8V                                                                                            |              | 0             | 100            | nA                                              |   |

| NMOS Switch Leakage                      | Switch A, B, C, D, $V_{IN} = V_{OUT} = 12\text{V}$                                                    |              | 1             | 10             | $\mu\text{A}$                                   |   |

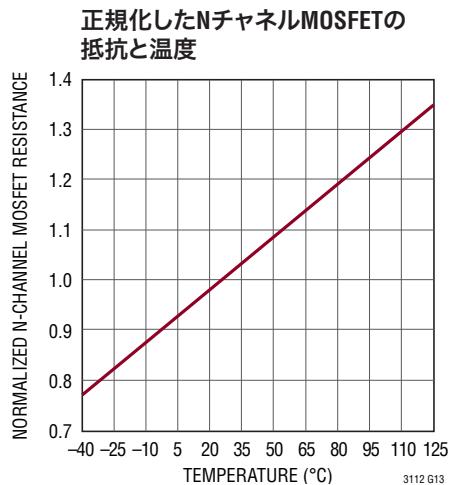

| NMOS Switch On Resistance                | Switch A                                                                                              |              | 40            |                | $\text{m}\Omega$                                |   |

| NMOS Switch On Resistance                | Switch B, C                                                                                           |              | 50            |                | $\text{m}\Omega$                                |   |

| NMOS Switch On Resistance                | Switch D                                                                                              |              | 60            |                | $\text{m}\Omega$                                |   |

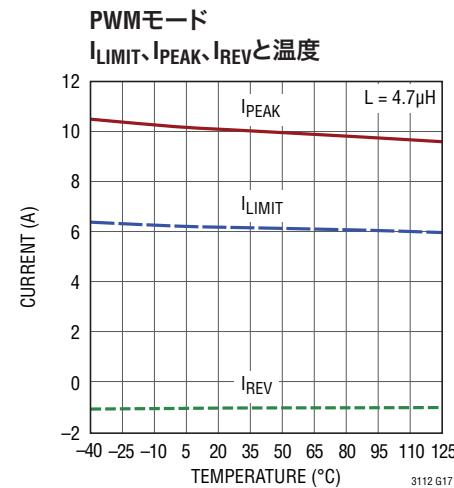

| Input Current Limit                      | $L = 4.7\mu\text{H}$                                                                                  | ● 4.5        | 6             | 8.5            | A                                               |   |

| Peak Current Limit                       | $L = 4.7\mu\text{H}$                                                                                  | 7            | 10            | 12             | A                                               |   |

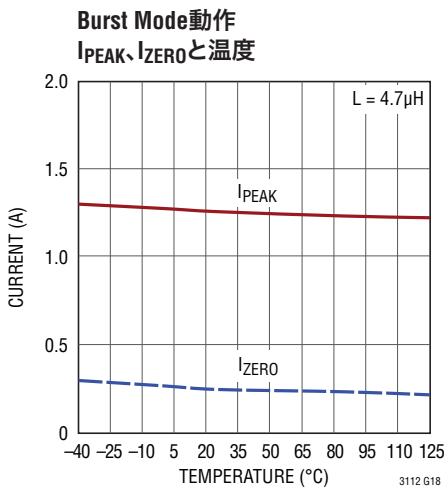

| Burst Current Limit                      | $L = 4.7\mu\text{H}$                                                                                  | 0.7          | 1.3           | 2              | A                                               |   |

| Burst Zero Current Threshold             | $L = 4.7\mu\text{H}$                                                                                  |              | 0.3           |                | A                                               |   |

| Reverse Current Limit                    | $L = 4.7\mu\text{H}$                                                                                  |              | -0.5          | -1             | -1.5                                            | A |

| $I_{OUT}$ Accuracy (Note 5)              | SW2 to $V_{OUT}$ Current = 1.5A<br>SW2 to $V_{OUT}$ Current = 1.0A<br>SW2 to $V_{OUT}$ Current = 0.5A |              | 32<br>20<br>8 | 36<br>24<br>12 | $\mu\text{A}$<br>$\mu\text{A}$<br>$\mu\text{A}$ |   |

| Maximum Duty Cycle                       | Buck (Switch A On)<br>Boost (Switch C On)                                                             | ● 80<br>● 75 | 87<br>82      |                | %                                               |   |

| Minimum Duty Cycle                       | Buck (Switch A On)<br>Boost (Switch C On)                                                             | ● 5          |               | 0              | %                                               |   |

| Frequency                                | PWM/SYNC = 5V, $V_{IN} = V_{OUT} = 12\text{V}$                                                        | ● 675        | 750           | 825            | kHz                                             |   |

| SYNC Frequency Range (Note 7)            |                                                                                                       | ● 300        |               | 1500           | kHz                                             |   |

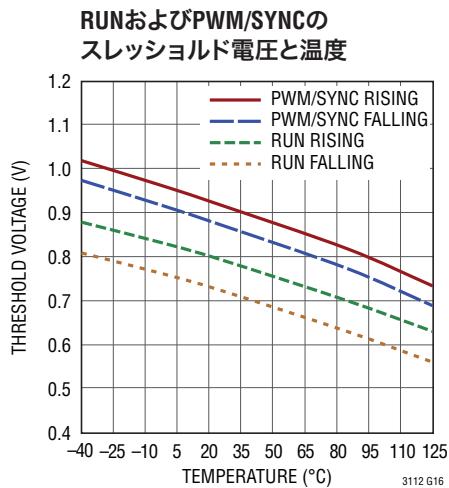

| PWM/SYNC Threshold                       | $V_{CC} = 2.7\text{V}$ or $5\text{V}$                                                                 | ● 0.5        | 0.9           | 1.5            | V                                               |   |

| RUN Threshold                            | $V_{IN} = 2.7\text{V}$ or $15\text{V}$                                                                | ● 0.35       | 0.75          | 1.5            | V                                               |   |

## 電気的特性

**Note 1 :** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2 :** LTC3112 は  $T_J$  が  $T_A$  にほぼ等しいパルス負荷条件でテストされる。LTC3112E は、 $0^\circ\text{C} \sim 85^\circ\text{C}$  の接合部温度で仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$  の動作接合部温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTC3112I は、 $-40^\circ\text{C} \sim 125^\circ\text{C}$  の接合部温度で仕様に適合することが保証されている。これらの仕様を満たす最大周囲温度は、基板レイアウト、パッケージの定格熱抵抗および他の環境要因と関連した特定の動作条件によって決まることに注意。

**Note 3 :** このデバイスには短時間の過負荷状態の間デバイスを保護するための過温度保護機能が備わっている。過温度保護機能がアクティブなとき接合部温度は  $125^\circ\text{C}$  を超える。規定された最高動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なうおそれがある。

**Note 4 :** デモボードに示されているような、またはデータシートおよびアプリケーションノートに説明されているような良好なレイアウト方法を使うと、絶対最大定格で規定されている DC リミットを超えるスイッチ・ピンの電圧過渡は通常動作を中断しない。

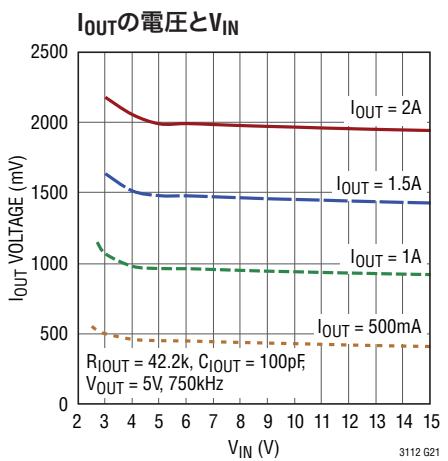

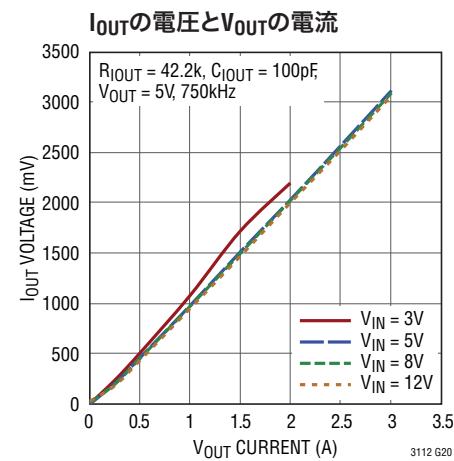

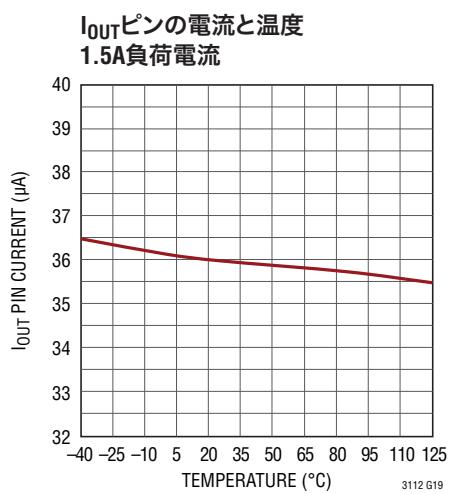

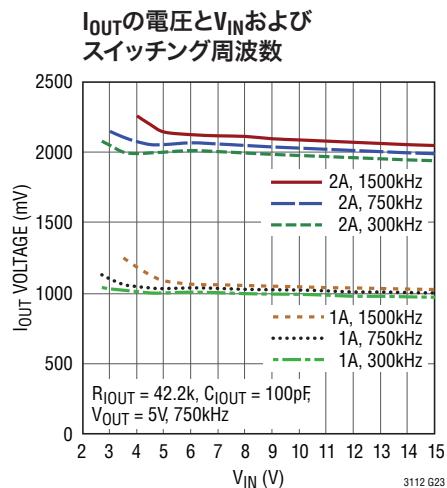

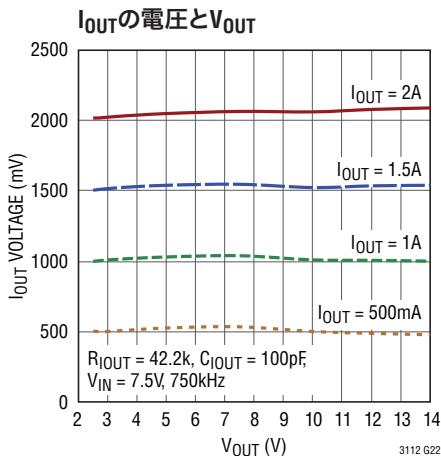

**Note 5 :**  $I_{\text{OUT}}$  電流はスイッチングを停止した DC 状態でテストされる。スイッチング環境では、 $I_{\text{OUT}}$  の精度はスイッチング周波数、負荷電流、入力 / 出力電圧、温度などの要因によって変化を示すことがある。予測される変動については、「標準的性能特性」の曲線を参照。

**Note 6 :** 接合部温度 ( $T_J$  ( $^\circ\text{C}$ )) は周囲温度 ( $T_A$  ( $^\circ\text{C}$ )) および電力損失 ( $P_D$  (W)) から次式に従って計算される。

$$T_J = T_A + (P_D \cdot \theta_{JA})$$

**Note 7 :** SYNC の周波数範囲は方形波を使ってテストされる。100ns の最小 “H” 時間または最小 “L” 時間による動作は設計によって確認されている。

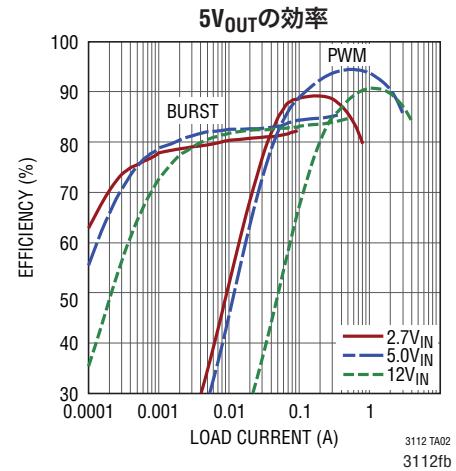

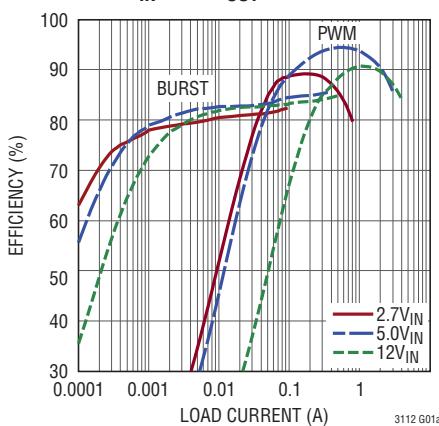

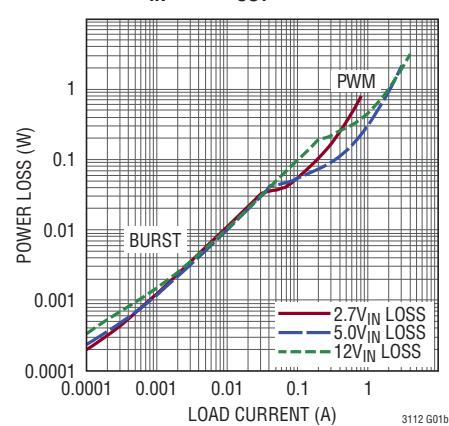

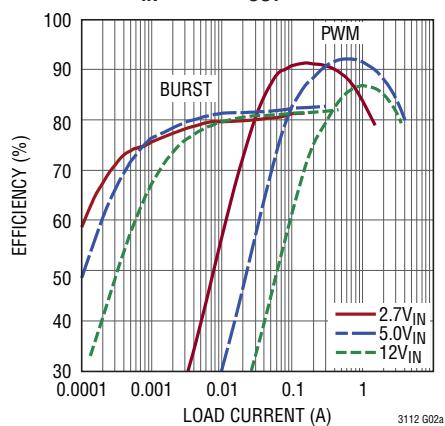

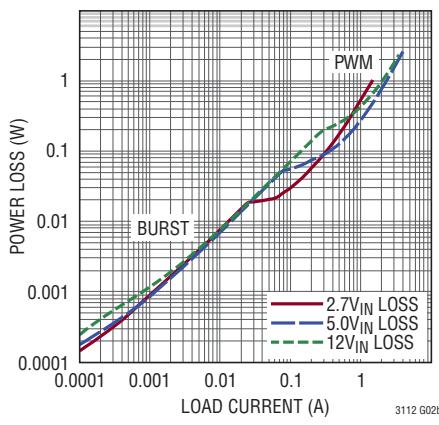

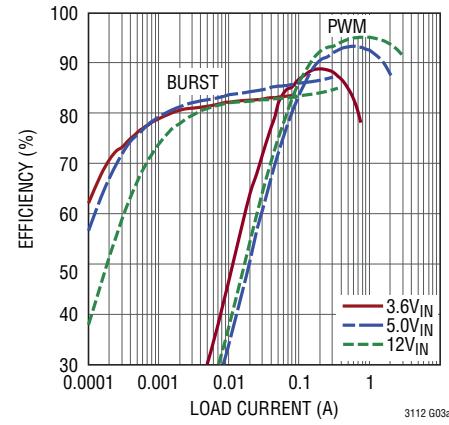

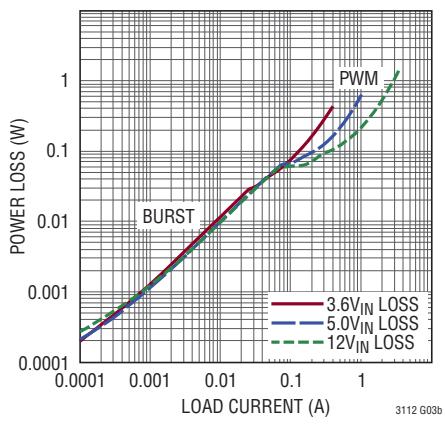

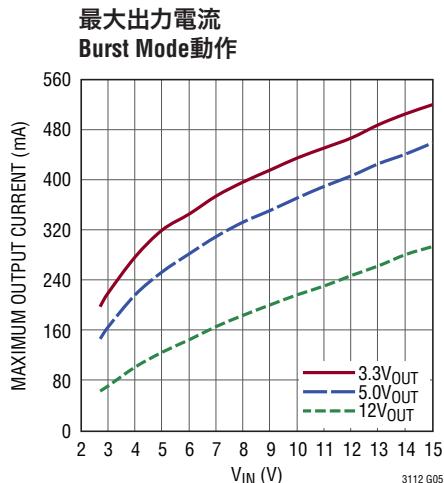

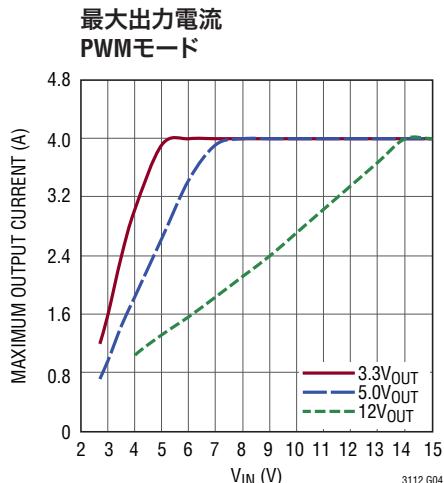

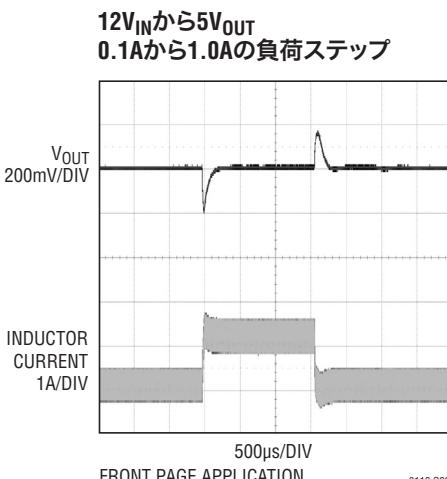

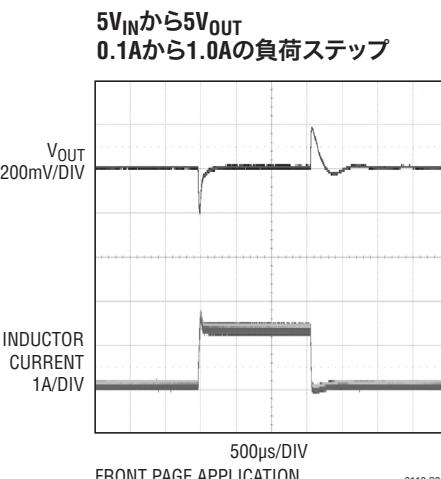

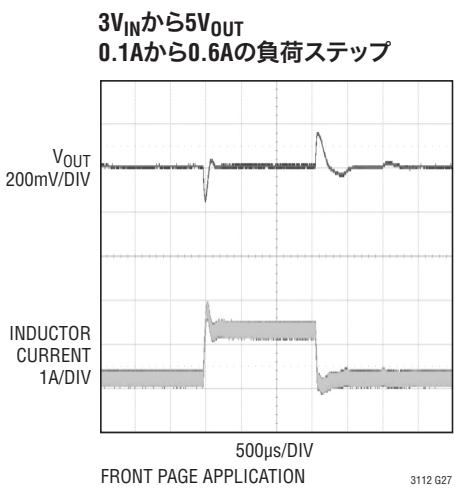

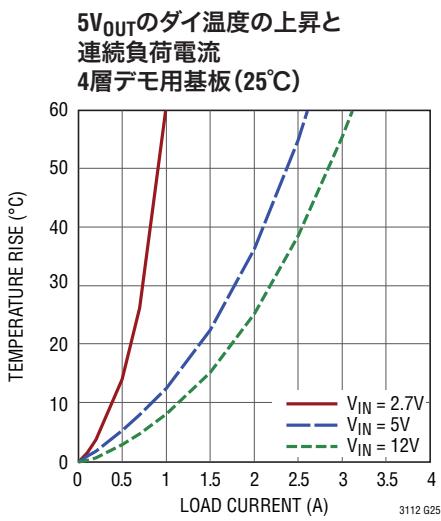

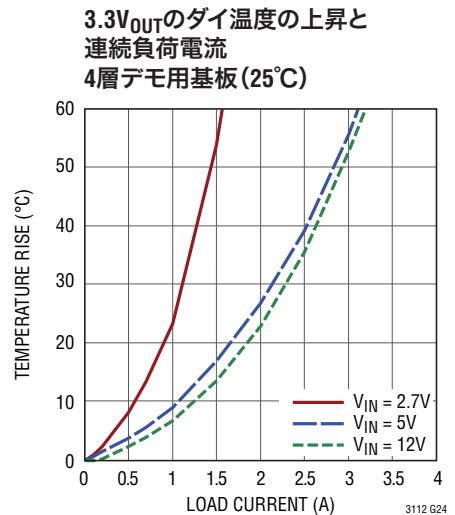

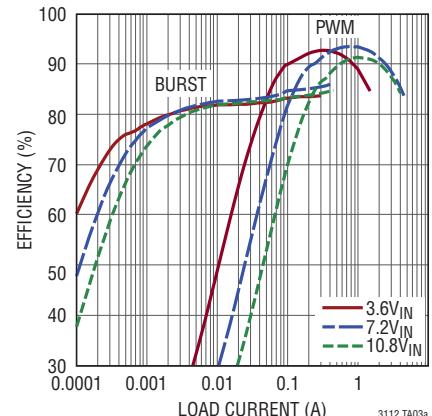

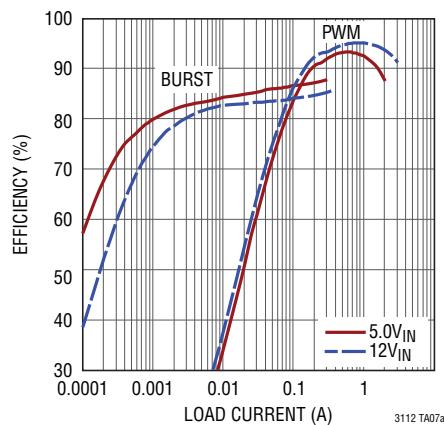

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{\text{IN}} = 5.0\text{V}$ 、 $V_{\text{OUT}} = 5.0\text{V}$

広い  $V_{\text{IN}}$  から  $5V_{\text{OUT}}$  の効率

広い  $V_{\text{IN}}$  から  $5V_{\text{OUT}}$  の電力損失

広い  $V_{\text{IN}}$  から  $3.3V_{\text{OUT}}$  の効率

広い  $V_{\text{IN}}$  から  $3.3V_{\text{OUT}}$  の電力損失

広い  $V_{\text{IN}}$  から  $12V_{\text{OUT}}$  の効率

広い  $V_{\text{IN}}$  から  $12V_{\text{OUT}}$  の電力損失

## 標準的性能特性

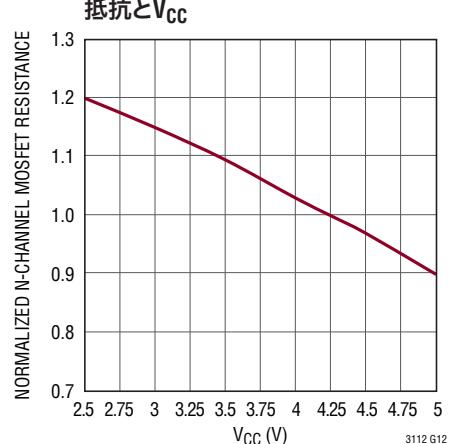

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 5.0\text{V}$ 、 $V_{OUT} = 5.0\text{V}$

## 標準的性能特性

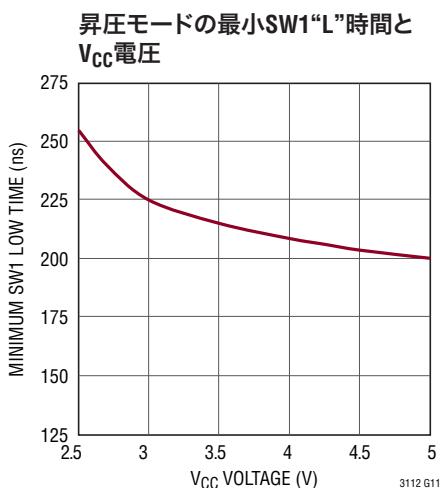

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 5.0\text{V}$ 、 $V_{OUT} = 5.0\text{V}$

## 標準的性能特性

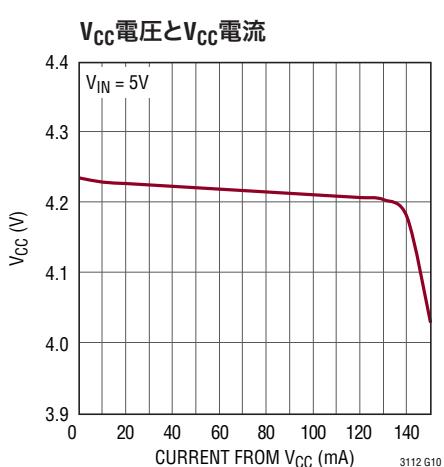

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 5.0\text{V}$ 、 $V_{OUT} = 5.0\text{V}$

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 5.0\text{V}$ 、 $V_{OUT} = 5.0\text{V}$

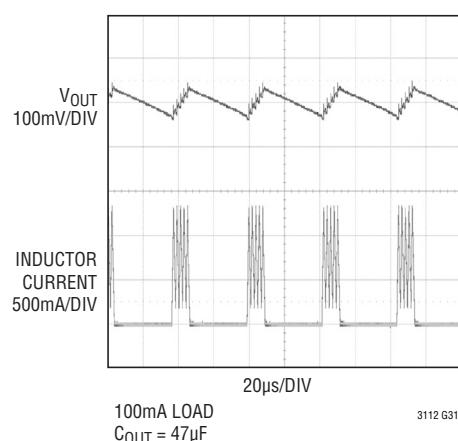

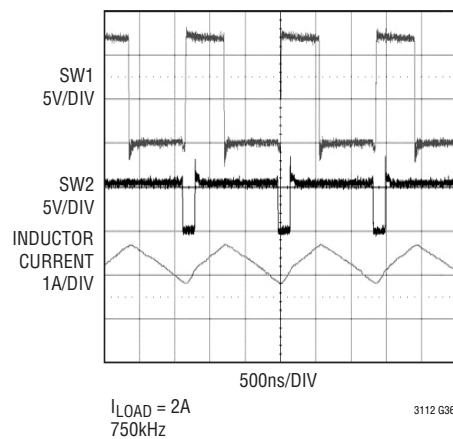

**12V<sub>IN</sub>から5V<sub>OUT</sub> Burst Mode動作の波形**

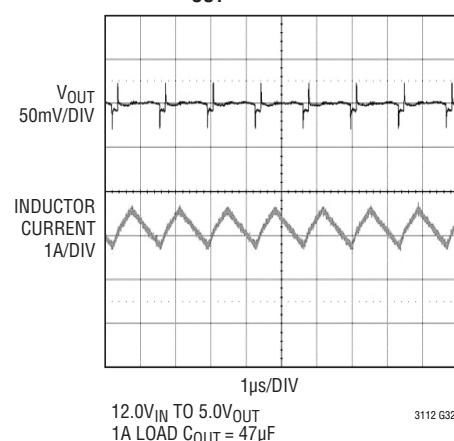

**PWMのV<sub>OUT</sub>のリップル**

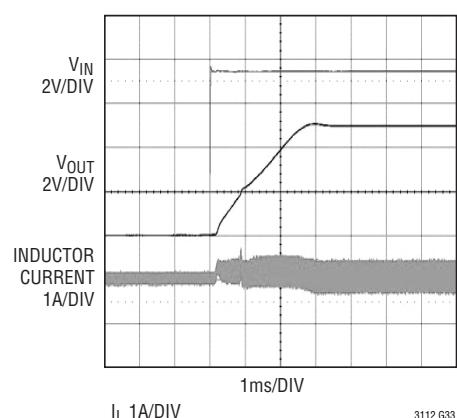

**7.5V<sub>IN</sub>から5.0V<sub>OUT</sub>のソフトスタートの波形**

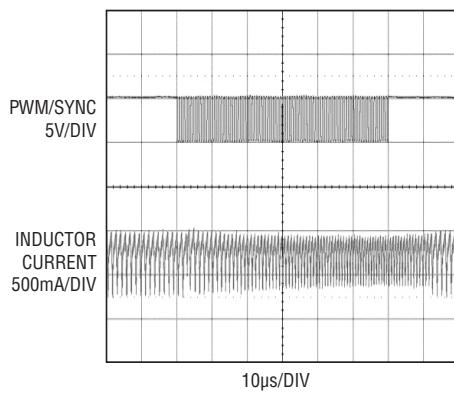

**1500kHz SYNC信号のキャプチャとリリース**

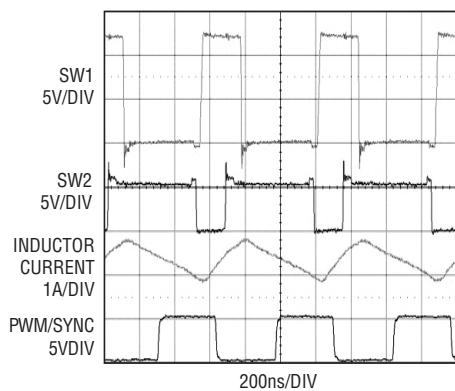

**12V<sub>IN</sub>から5.0V<sub>OUT</sub>のSW1およびSW2の波形**

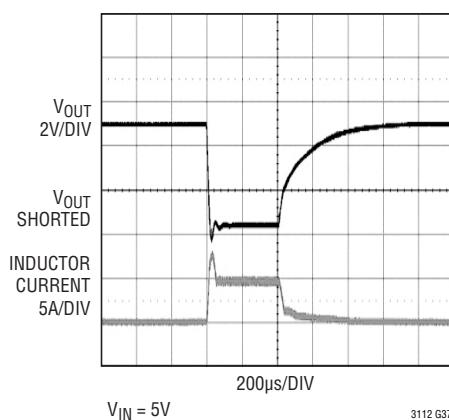

**V<sub>OUT</sub>の短絡に対する応答**

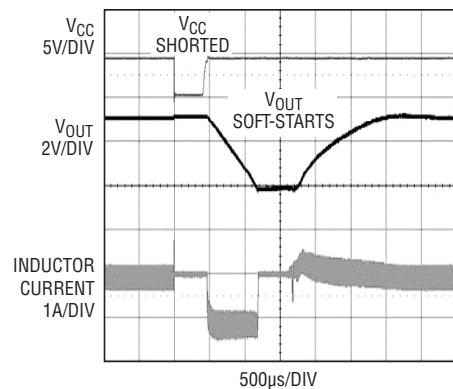

**V<sub>CC</sub>の短絡からの回復**

## ピン機能 (DFN/TSSOP)

**COMP (ピン 1/ピン 2)** : エラーアンプの出力。このピンから FB に接続された RC ネットワークにより、電圧コンバータのループ補償が設定されます。

**FB (ピン 2/ピン 3)** : 帰還電圧の入力。V<sub>OUT</sub> の抵抗分割器のタップをこのピンに接続します。出力電圧は、2.5V ~ 14V の範囲で次式に従って調整できます。

$$V_{\text{OUT}} = 0.8V \cdot \left( 1 + \frac{R_1}{R_2} \right)$$

ここで、R<sub>1</sub> は V<sub>OUT</sub> と FB の間の抵抗、R<sub>2</sub> は FB と GND の間の抵抗です。

**OVP (ピン 3/ピン 4)** : 過電圧保護入力。V<sub>OUT</sub> と GND の間の抵抗分割器の共通ポイントは、次式に従って過電圧保護を低い電圧にプログラムするのにも使用することができます。

$$V_{\text{OVP}} = 0.83V \cdot \left( 1 + \frac{R_3}{R_4} \right)$$

ここで、R<sub>3</sub> は V<sub>OUT</sub> と OVP の間の抵抗、R<sub>4</sub> は OVP と GND の間の抵抗です。

**V<sub>IN</sub> (ピン 4、5/ピン 5、6)** : 入力電源電圧。このピンは少なくとも 10μF の低 ESR、低 ESL のセラミック・コンデンサを使ってグランド・プレーンにバイパスします。このコンデンサはできるだけピンの近くに配置し、グランド・プレーンへのリターン経路をできるだけ短くします。

**RUN (ピン 6/ピン 7)** : シャットダウン制御入力。電圧を 0.75V (標準) より下に強制すると動作がディスエーブルされ、消費電流は 1μA 未満になります。

**I<sub>OUT</sub> (ピン 7/ピン 8)** : D スイッチの出力電流の 1A 当たり約 24μA の電流がこのピンからソースされます。RC 回路を使って平均出力電流を制御するか、またはアナログ出力電流モニタを与えることができます (「アプリケーション情報」のセクションを参照)。

**V<sub>OUT</sub> (ピン 8/ピン 9)** : 安定化された出力電圧。このピンは少なくとも 47μF の低 ESR セラミック・コンデンサに接続します。コンデンサはできるだけピンの近くに配置し、グランド・プレーンへのリターンを短くします。

**SW2 (ピン 9、10/ピン 12、13)** : 内部スイッチ C と D および外部インダクタがここに接続されます。

**BST2 (ピン 11/ピン 14)** : D スイッチ・ドライバ用の昇圧されたフロート・ドライバ電源。このピンから SW2 に 0.1μF のコンデンサを接続します。

**SW1 (ピン 12、13/ピン 15、16)** : 内部スイッチ A と B および外部インダクタがここに接続されます。

**BST1 (ピン 14/ピン 17)** : A スイッチ・ドライバ用の昇圧されたフロート・ドライバ電源。このピンから SW1 に 0.1μF のコンデンサを接続します。

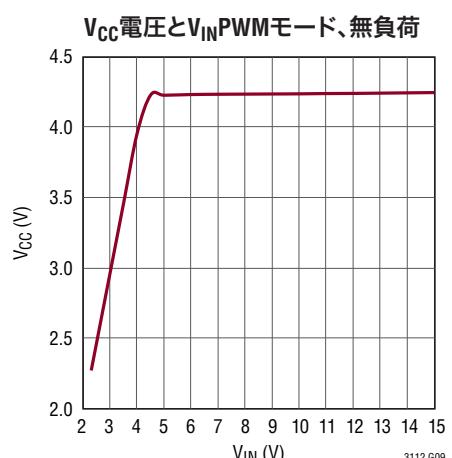

**V<sub>CC</sub> (ピン 15/ピン 18)** : 安定化された V<sub>CC</sub> 電源の外部コンデンサ接続。この電源は内部回路とスイッチ・ドライバを動作させるのに使われます。V<sub>CC</sub> は 4.2V まで V<sub>IN</sub> をトラッキングしますが、V<sub>IN</sub> が 4.2V を超えると 4.2V に留まります。1μF のセラミック・コンデンサをこのピンから GND に接続します。

**PWM/SYNC (ピン 16/ピン 19)** : Burst Mode の制御および同期入力。0.5V 未満の DC 電圧では Burst Mode 動作、1.5V を超えると 750kHz の固定周波数モードが指定されます。300kHz と 1500kHz の間のデジタル・パルス列をこのピンに与えると、内部発振器を無効にして動作周波数を設定します。パルス列の最小 “H” 時間と最小 “L” 時間は 100ns を超えるようにします (Note 7)。LTC3112 は Burst Mode 動作で動作するとき電力能力を下げていることに注意してください。詳細についてはこのデータシートの「動作」のセクションを参照してください。

**GND (露出パッドのピン 17/ピン 1、10、11、20、露出パッドのピン 21)** : グランド。小信号とデバイスの電源のグランド。露出パッドは PCB のグランドに半田付けし、できるだけ短く最低のインピーダンスの接続を介して電気的にグランドに接続する必要があります。熱流の大半はこのパッドを通るので、プリント回路のデザインがデバイスの熱性能に影響を与えます。詳細については「PCB レイアウト」と「熱に関する検討事項」のセクションを参照してください。

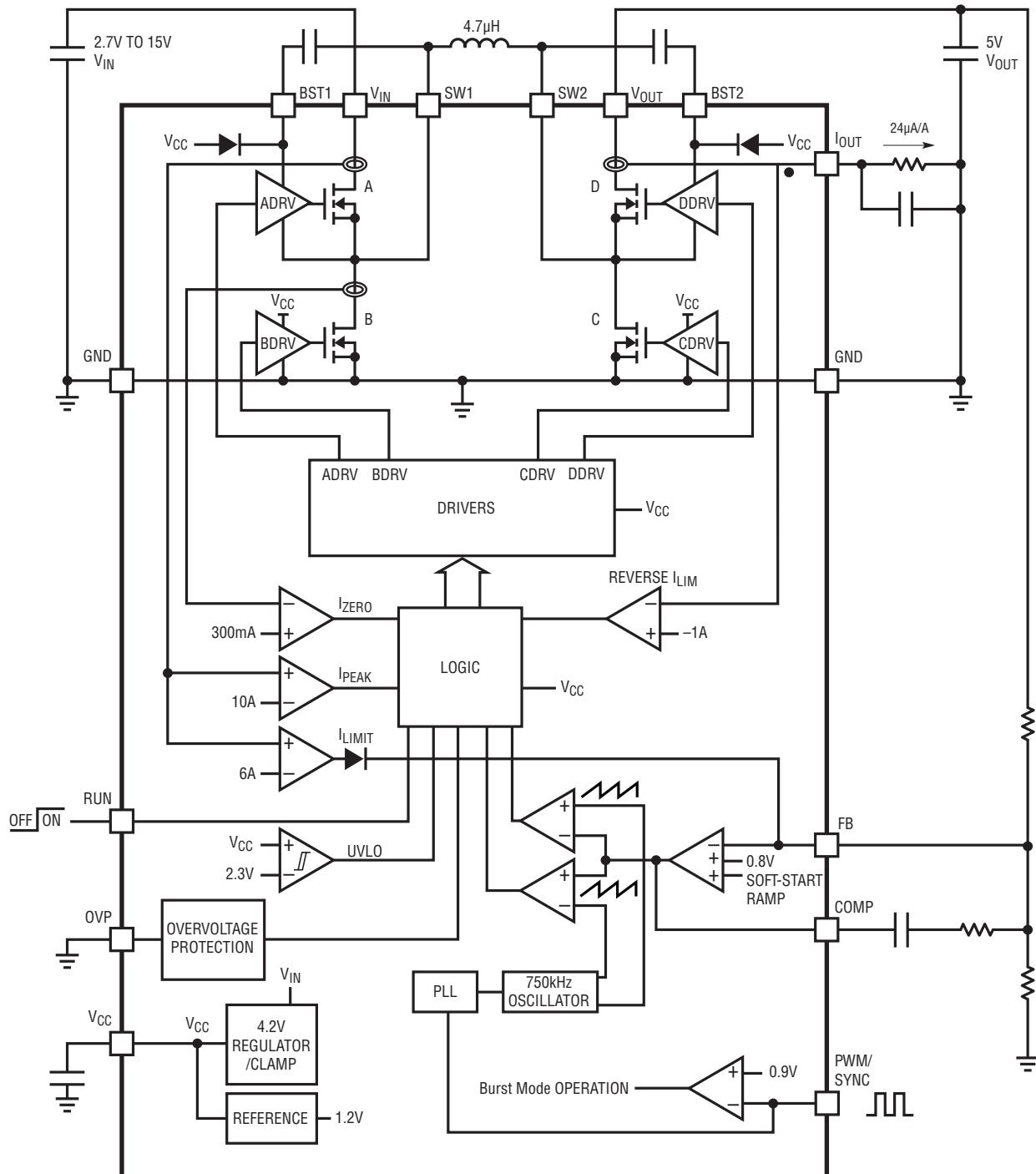

## ブロック図

## 動作

### はじめに

LTC3112 は、要求の厳しい様々なアプリケーション向けに最適化された、入力範囲と出力範囲が拡張された、高電流同期整流式昇降圧 DC/DC コンバータです。LTC3112 は、入力電圧に対して出力電圧を高く、低くまたは等しく安定化することができる独自のスイッチング・アルゴリズムを利用して います。COMP のエラーアンプの出力によりスイッチの出力 デューティ・サイクルが決まります。R<sub>DSON</sub> が小さくゲート電荷が少ない同期スイッチが、高効率でパルス幅変調制御を行 います。Burst Mode 動作を指示すると、軽負荷で高い効率 が実現されます。

### 低ノイズ固定周波数動作

#### 発振器、フェーズロック・ループ

内部発振器回路は通常の動作周波数を 750kHz に設定しま す。PWM/SYNC ピンに与えられるパルス列により、内部フェー ズロック・ループ回路を介して、動作周波数を 300kHz ~ 1.5MHz にプログラムすることができます。パルス列は、動作 を保証するため、最小 “H” 状態または最小 “L” 状態が少 なくとも 100ns 必要です (Note 7)。

#### エラーアンプ

エラーアンプは高利得の電圧モード・アンプです。コンバー タを安定化し、負荷過渡に高速で応答するため、ループ補 償用部品をこのアンプの周囲 (FB から COMP および V<sub>OUT</sub> から FB) に配置します。補償の種類および部品の選択の詳 細に関しては、このデータシートの「アプリケーション情報」 のセクションの「帰還ループを閉じる」を参照してください。

#### 電流制限動作

昇降圧コンバータには 2 つの電流制限回路が備わっています。主電流制限は平均電流制限回路で、スイッチ A の電流が標 準 6A を超える分に比例した電流を帰還分割器ネットワーク にソースします。この帰還ループは利得が高いので、注入さ

れた電流は、スイッチ A を流れる平均電流がほぼ電流制限 値に減少するまで誤差アンプの出力が減少するよう強制しま す。平均電流制限はアクティブ状態のエラーアンプを利用す るので、電流制限フォールト状態が解消するとほとんどオーバーシュートなしにスムーズに回復します。電流制限はスイッ チ A を流れる平均電流に基づいているので、電流制限時の ピーク・インダクタ電流はデューティ・サイクル (つまり過電流 状態の入力電圧と出力電圧) に依存します。この電流制限 機能が有効に働くには、FB からグランドへのテブナン抵抗 が 100kΩ を超えるようにします。

平均電流制限回路の速度はエラーアンプの動特性によって制 限されます。ハードな出力短絡では、平均電流制限回路が応 答する前にインダクタ電流が電流リミットを超えてかなり増 加する可能性があります。この理由で、2 つめの電流制限回 路があり、電流が平均電流制限値の約 160% を超えるとスイッ チ A をオフします。これにより、短時間のハードな出力短絡 に対する追加の保護が与えられます。

出力に短絡が生じると、平均電流制限が通常動作の電流制 限の約半分に減少します。

#### 逆電流制限

固定周波数動作の間、スイッチ D の逆電流コンパレータは V<sub>OUT</sub> ピンに入ってくる電流をモニタします。この電流が 1A (標準) を超えると、スイッチ D がスイッチング・サイクルの残り の時間オフします。この機能は、昇降圧の出力がレギュレー ション電圧より上のとき、昇降圧コンバータを過度の逆電流 から保護します。

#### 内部ソフトスタート時間

LTC3112 昇降圧コンバータは公称持続時間が 2ms の独立し た内部ソフトスタート回路を備えています。コンバータはソフ トスタートの間安定化状態に留まるので、この間に生じる出 力負荷過渡に応答します。さらに、起動時の出力電圧の立ち 上がり時間は出力コンデンサのサイズや負荷電流にはわずか しか依存しません。

## 動作

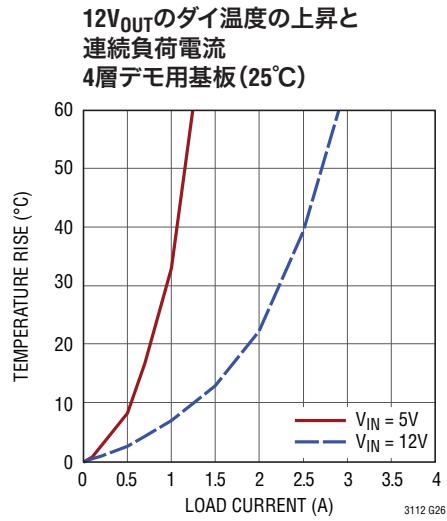

### 熱に関する検討事項

LTC3112 が最大出力電力を供給するには、パッケージ内部で発生した熱を放散するのに十分な熱経路を与えることが不可欠です。これはデバイス底部の熱パッドの利点を利用して実現することができます。プリント回路基板のビアを多数使って、できるだけ面積の大きな銅プレーンにデバイスの熱を逃がすことを推奨します。

コンバータが連続的に大きな電力を供給する必要があるとき、または高い周囲温度で動作する必要があるとき、LTC3112 の効率と最大出力電流能力が低下します。出力電流のディレーティングの大きさは、基板のグランド・プレーンやヒートシンクの面積、周囲動作温度、アプリケーションの入力電圧 / 出力電圧などの要因に依存します。熱設計が良くないと過度の熱が生じ、性能や信頼性が損なわれることがあります。

「標準的性能特性」のセクションに与えられている温度上昇曲線を一般的目安として使って、周囲温度を超える接合部温度の上昇を予測することができます。これらの曲線は図 3 に示されている 4 層 FR4 デモ用ボードのプリント回路基板のレイアウトに LTC3112 を実装して得られました。この曲線は室温の基板を使って得られており、上昇した周囲温度では、N チャネル MOSFET の初期  $R_{DS(ON)}$  が増加しているため熱上昇率が大きくなります。LTC3112 のダイ温度は 125°C の最大接合部温度定格より下に保つようにします。

接合部温度が高くなり過ぎると（約 150°C）、電流制限がその標準値から直線的に減少します。接合部温度が上昇を続けて約 170°C を超えると、LTC3112 はディスエーブルされます。全てのパワーデバイスがオフし、全てのスイッチ・ノードが高インピーダンス状態になります。コンバータのソフトスタート回路はサーマル・シャットダウンの間にリセットされ、過温度状態が解消するとスムーズに回復します。ダイの温度が約 160°C に下がると、LTC3112 は再起動します。

### 低電圧ロックアウト

LTC3112 昇降圧コンバータは  $V_{CC}$  電源が 2.35V（標準）に達するまでディスエーブルされ、全てのパワーデバイスはオフします。ソフトスタート回路は低電圧ロックアウト・スレッショルドより上に上昇するとスムーズに再起動します。 $V_{IN}$  が上昇方向 2.3V（標準）、下降方向 2.0V（標準）より下のとき、2 番目のUVLO 回路が全てのパワーデバイスをディスエーブルします。これにより、スタートアップ後に  $V_{CC}$  が代替ソースまたは  $V_{OUT}$  から給電されるアプリケーションの  $V_{IN}$  の動作範囲を下げることができます。

### インダクタの減衰

LTC3112 がディスエーブルされるか（ $RUN = 0V$ ）、Burst Mode 動作で（ $PWM/SYNC = 0V$ ）スリープに入ると、アクティブ回路が SW1 および SW2 から GND への  $250\Omega$ （標準）のインピーダンスを介してインダクタの電圧を「減衰」させてリングを最小に抑え、EMI を減らします。

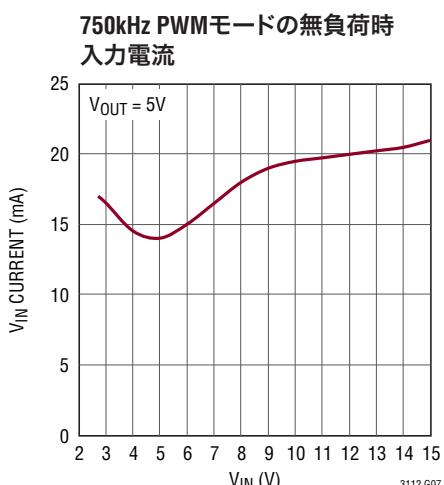

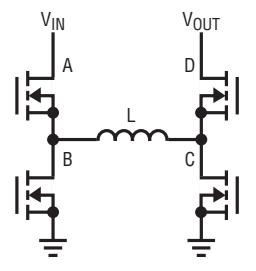

### PWM モードの動作

$PWM/SYNC$  ピンが “H” に保たれていると、LTC3112 昇降圧コンバータは電圧モード制御を使った固定周波数パルス幅変調（PWM）モードで動作します。最大出力電流能力は PWM モードでだけ与えられます。独自のスイッチング・アルゴリズムにより、コンバータは、インダクタ電流が不連続になることなしに、降圧、昇降圧および昇圧の各モードの間を移行することができます。昇降圧コンバータのスイッチ・トポロジーを図1に示します。

図1. 昇降圧用スイッチのトポロジー

入力電圧が output 電圧よりも大きいと、昇降圧コンバータは降圧モードで動作します。スイッチ D は最大デューティ・サイクルでオンし、スイッチ C はスイッチ D をドライブするのに使われる BST2 コンデンサの電圧をリフレッシュするのに

## 動作

ちょうど十分な時間オンします。スイッチ A とスイッチ B はパルス幅変調されて、出力レギュレーション電圧をサポートするのに必要なデューティ・サイクルを発生します。

入力電圧が出力電圧に近づくにつれ、スイッチ A とスイッチ D がスイッチング周期の長い部分オンし、VIN から VOUT への直接電流経路を与えます。スイッチ B とスイッチ C は適切なレギュレーションを行い、BST1 と BST2 のコンデンサを充電するのにちょうど十分なだけオンします。内部制御回路が全ての動作モードの（負荷電流によって変化する）適切なデューティ・サイクルを決めます。

入力電圧が出力電圧より十分下になると、コンバータは昇圧モードでだけ動作します。スイッチ A は最大デューティ・サイクルでオンし、スイッチ B は A をドライブするのに使われる BST1 コンデンサの電圧をリフレッシュするのにちょうど十分な時間オンします。スイッチ C とスイッチ D はパルス幅変調されて、出力電圧を安定化するのに必要なデューティ・サイクルを発生します。

このスイッチング・アルゴリズムにより、動作モード全てにわたって動作モード間をシームレスに移行し、平均インダクタ電流、インダクタ電流リップル、およびループの伝達関数の不連続性を除去します。これらの利点により、従来の 4 スイッチ昇降圧コンバータに比べて効率と安定性が向上します。

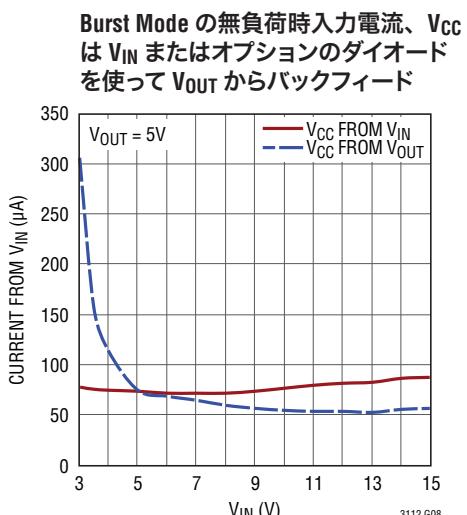

### 外部ソースによる V<sub>CC</sub> への給電

LTC3112 の V<sub>CC</sub> レギュレータは最大 5.5V の外部ソースから給電するかバックフィードすることができます。4.2V を超える電圧から V<sub>CC</sub> にバックフィードする利点は、低い入力電圧での効率の向上と最大デューティ・サイクルの改善です。これらの利点は「標準的性能特性」の「MOSFET の抵抗と V<sub>CC</sub>」および「SW 1 の “L” の最小時間」の曲線で示されています。5V<sub>OUT</sub> のアプリケーションでは、「標準的応用例」のセクションのいくつかの応用回路に示されているように、外部低電流ショットキー・ダイオードを使って V<sub>OUT</sub> から V<sub>CC</sub> に簡単に給電することができます。

また、V<sub>CC</sub> へのバックフィードは、インダクタがゼロ電流を通過するとき生じる軽負荷 PWM モードの出力電圧リップルを改善します。V<sub>CC</sub> にバックフィードすると、スイッチ・ピンのアンチクロス導通時間が減少し、この軽負荷状態での V<sub>OUT</sub> リップルを最小に抑えます。V<sub>OUT</sub> から V<sub>CC</sub> に給電する短所の 1 つは、「標準的性能特性」の曲線に示されている

ように、(VIN から V<sub>CC</sub> に給電するのに比べて) Burst Mode で低 VIN のとき無負荷時の消費電流が増加することです。

### 昇圧アプリケーションに関する検討事項

昇圧モードでは、V<sub>OUT</sub>/VIN の比率が高いほどサポート可能な最大出力電流が減少します。この影響は、「標準的性能特性」のセクションの「最大出力電流 (PWM モード)」の曲線に示されています。たとえば、12V<sub>OUT</sub> で 1A をサポートするには LTC3112 は 4V を超える VIN を必要とします。前に説明したように、(もし利用可能ならば) 5V ソースから V<sub>CC</sub> に給電すると低入力電圧で出力電流能力を改善することができます。

もっと低い入力電圧では (12V<sub>OUT</sub> の場合 3.6V より下)、LTC3112 はデューティ・サイクルの限界に達する可能性があります。これが生じるのは、SW1 と SW2 のそれぞれの最大デューティ・サイクルが乗算されて、公称 750kHz のスイッチング周波数では約 70% の最大デューティ・サイクルになるからです。PWM/SYNC ピンを使ってスイッチング周波数を下げると、最大デューティ・サイクルが増加するので、高い昇圧比を達成することができます。説明されているデューティ・サイクルの制限を超えて LTC3112 を動作させると動作が不安定になることがあるので、制限を超えて動作させようとしてください。

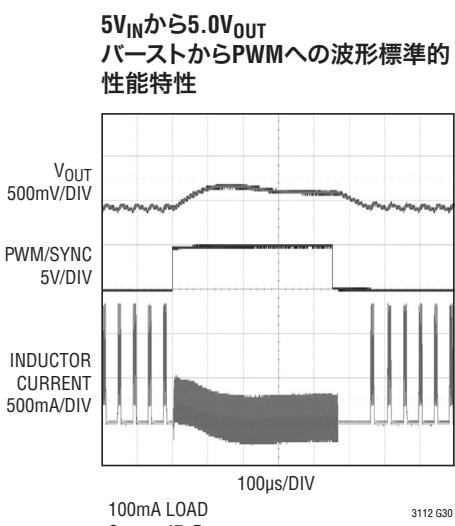

### Burst Mode 動作

PWM/SYNC ピンを “L” に保つと、昇降圧コンバータは、軽負荷で効率を改善し、ゼロ負荷でスタンバイ電流を減らすように設計された可変周波数スイッチング・アルゴリズムを使って動作します。Burst Mode 動作では、インダクタはピーク振幅が固定された電流パルスによって充電されるので、Burst Mode 動作のときは最大出力電流の一部分だけを供給することができます。

これらの電流パルスは出力レギュレーション電圧を維持するのに必要な頻度で繰り返されます。Burst Mode 動作で供給可能な最大出力電流 (I<sub>MAX</sub>) は次式で近似されるように入力電圧と出力電圧に依存します。

$$I_{MAX} = \frac{0.5 \cdot V_{IN}}{V_{IN} + V_{OUT}} (A)$$

昇降圧の負荷が最大 Burst Mode の電流能力を超えると、出力レールはレギュレーションから外れます。

Burst Mode 動作では、エラーアンプは低消費電力動作に設

## 動作

定され、補償ピン COMP をホールドするのに使われ、Burst Mode と PWM モード動作の間の移行時に生じる可能性のある過渡を減らします。

## 出力電流モニタ

LTC3112 は V<sub>OUT</sub> (つまり SWD) の電流を約 24μA/A の比率で反映するレプリカ電流をソースする回路を備えています。この電流は一般に I<sub>OUT</sub> から GND に接続された抵抗を流れ、filtrated されて平均負荷電流に比例する DC 電圧を発生しま

す。この電圧を A/D コンバータでモニタして負荷状態を追跡することができます。I<sub>OUT</sub> ピンの電圧は LTC3112 の帰還ループを制御して、V<sub>OUT</sub> 電圧の代わりに I<sub>OUT</sub> 電流を制御することができます。I<sub>OUT</sub> のレプリカ電流の精度は、デューティサイクル、V<sub>IN</sub> 電圧、V<sub>OUT</sub> 電圧、動作周波数などの要因に依存します。出力電流を正確に表すためには、I<sub>OUT</sub> ピンの DC 電圧は V<sub>CC</sub> - 1V より小さくなければなりません。

## アプリケーション情報

LTC3112 の基本的なアプリケーション回路がこのデータシートの最初のページに示されています。外部部品の選択は、PCB の面積、出力電圧、出力電流、リップル電圧、効率などのトレードオフにより、それぞれ特定のアプリケーションで必要とされるデバイスの性能に依存します。ここでは、外部部品の選択とアプリケーション回路の設計に役立ついくつかの基本的ガイドラインと検討事項について説明します。

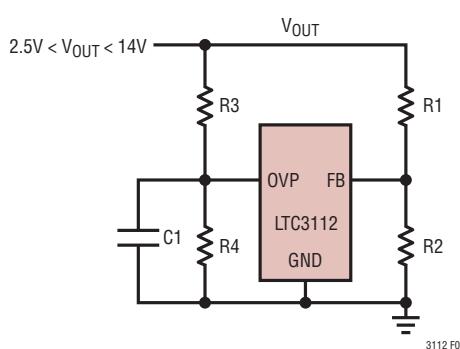

### V<sub>OUT</sub> と OVP のプログラミング

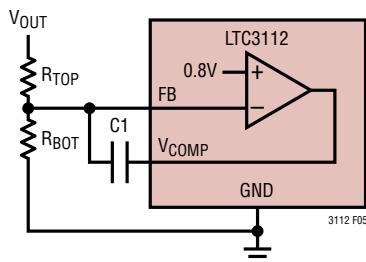

昇降圧の出力電圧は、図 2 に示されているように、FB ピンに接続された外部抵抗分割器で設定されます。

図2.出力電圧の設定

抵抗分割器の値は次式に従って昇降圧の出力電圧を決めます。

$$V_{OUT} = 0.8V \cdot \left( 1 + \frac{R1}{R2} \right)$$

精確な過電圧保護が必要であれば、2 番目の抵抗分割器 (R3 と R4) を OVP ピンに接続して、LTC3112 がスイッチングを停止する過電圧保護スレッショルドをプログラムすることができます。

$$V_{OVP} = 0.83V \cdot \left( 1 + \frac{R3}{R4} \right)$$

負荷ステップによる誤ったトリップを防ぐためのフィルタとして、R4 に並列に小さなコンデンサ (C1) が必要になることがあります。過電圧が発生するとソフトスタート・サイクルが開始されます。

### インダクタの選択

高効率を達成するには、昇降圧コンバータに低 ESR のインダクタを利用します。さらに、昇降圧のインダクタは飽和電流定格がワーストケースの平均インダクタ電流にリップル電流の半分を加えた電流を超えている必要があります。降圧または昇圧モード動作のピーク・トゥ・ピーク・インダクタ電流リップルは以下の式で計算することができます。

$$\Delta I_{L,P-P, BUCK} = \frac{V_{OUT}}{f \cdot L} \left( \frac{V_{IN} - V_{OUT}}{V_{IN}} \right) A$$

$$\Delta I_{L,P-P, BOOST} = \frac{V_{IN}}{f \cdot L} \left( \frac{V_{OUT} - V_{IN}}{V_{OUT}} \right) A$$

## アプリケーション情報

ここで、 $f$  は Hz を単位とするスイッチング周波数、 $L$  はヘンリーを単位とするインダクタの値です。

出力電流リップルへの影響に加えて、インダクタのサイズは帰還ループの安定性にも影響を与えます。昇圧モードでは、コンバータの伝達関数はインダクタの値に反比例する周波数で、右半平面のゼロを持ちます。その結果、インダクタ値が大きいと、このゼロが、帰還ループの位相マージンを減少させるだけ十分低い周波数に移動することがあります。コンバータを昇圧領域で使うつもりならば、15 $\mu$ H 未満のインダクタ値を選択することを推奨します。750kHz 動作では、5V<sub>OUT</sub> には 4.7 $\mu$ H のインダクタ、12V<sub>OUT</sub> には 10 $\mu$ H のインダクタを推奨します。

インダクタの DC 抵抗は、低い入力電圧で昇降圧コンバータの効率および最大出力電流能力に影響を与えることがあります。降圧モードでは、出力電流はインダクタ電流が電流制限値に達することによってだけ制限されます。ただし、昇圧モードでは、特に大きな昇圧比では、出力電流能力は電力段の合計抵抗損失によっても制限されます。これらにはスイッチ抵抗、インダクタ抵抗および PCB のトレース抵抗が含まれます。DC 抵抗の高いインダクタを使うと、出力電流能力が、このデータシートの「標準的性能特性」のセクションのグラフに示されているものから低下することがあります。

インダクタの異なったコア材と種類は、ある与えられた電流定格でのインダクタのサイズと価格に影響を与えます。シールドされた構造は他の回路との干渉の可能性を最小にするので一般に望ましいと言えます。インダクタの種類の選択は、特定のアプリケーションの価格、サイズおよび EMI に対する要件に依存します。LTC3112 の昇降圧コンバータの多くのアプリケーションに十分適したインダクタのサンプルを表 1 に示します。全てのインダクタの仕様は比較のために 4.7 $\mu$ H のインダクタンス値で示されていますが、これらのインダクタ・ファミリー内の他の値も一般にこのアプリケーションに十分適しています。各ファミリー内で（つまり、固定されたサイズで）、インダクタンスの増加とともに、DC 抵抗は一般に増加し、最大電流は一般に減少します。

表1. 昇降圧用の代表的な表面実装型インダクタ

| 製品番号                      | 値<br>( $\mu$ H) | DCR<br>(m $\Omega$ ) | MAX I<br>(A) | サイズ(mm)<br>W × L × H |

|---------------------------|-----------------|----------------------|--------------|----------------------|

| Coilcraft XPL7030-472ML   | 4.7             | 40.1                 | 6.8          | 7 × 7 × 3            |

| Coilcraft MSS1048-472NLB  | 4.7             | 12.3                 | 6.46         | 10 × 10 × 4.8        |

| Würth 744 311 470         | 4.7             | 24                   | 6            | 7 × 6.9 × 3.8        |

| Cooper Bussmann HC8-4R5-R | 4.5             | 18.6                 | 7.7          | 10.9 × 10.4 × 4      |

## 出力コンデンサの選択

出力電圧リップルを最小に抑えるため、昇降圧コンバータの出力には低 ESR の出力コンデンサを使います。多層セラミック・コンデンサは ESR が小さく、実装面積の小さいものが入手できるので最適です。十分大きなコンデンサを選択して出力電圧リップルを許容レベルに下げます。所与の出力電圧リップルに対して必要な最小出力コンデンサは (ESR と ESL を無視すると) 以下の式を使って計算することができます。

$$C_{\text{OUT}} = \frac{1}{\Delta V_{\text{P-P,BUCK}} 8 \cdot L \cdot f^2} \cdot \frac{(V_{\text{IN}} - V_{\text{OUT}}) V_{\text{OUT}}}{V_{\text{IN}}}$$

$$C_{\text{OUT}} = \frac{I_{\text{LOAD}} (V_{\text{OUT}} - V_{\text{IN}})}{\Delta V_{\text{P-P,BOOST}} V_{\text{OUT}} \cdot f}$$

ここで、 $f$  は MHz を単位とする周波数、 $C_{\text{OUT}}$  は  $\mu$ F を単位とする容量、 $L$  は  $\mu$ H を単位とするインダクタンス、 $I_{\text{LOAD}}$  はアンペアを単位とする出力電流です。

出力電流は昇圧モードでは不連続だと仮定すると、このモードのリップルは一般に降圧モードのリップルの大きさよりはるかに大きくなります。大部分のアプリケーションには、47 $\mu$ F 以上の出力コンデンサを推奨します。

## 入力コンデンサの選択

少なくとも 10 $\mu$ F の値の低 ESR セラミック・コンデンサができるだけ VIN ピンと GND ピンに近づけて配置することを推奨します。さらに、各ピンからグランド・プレーンへのリターン・トレースをできるだけ短くします。たとえば、（ベンチ電源のように）入力ソースがコンバータから遠く離れている場合、特に降圧モードで入力リップルを下げるため、100 $\mu$ F 以上のバルク・コンデンサを推奨します。

## アプリケーション情報

### コンデンサ・メーカーに関する情報

LTC3112 に使われる入力バイパス・コンデンサと出力コンデンサは両方とも低 ESR のもので、スイッチング・コンバータが発生する大きな AC 電流を扱うように設計されている必要があります。これはデバイスの適切な動作を維持し、入力と出力両方のリップルを減らすのに重要です。最近の低電圧セラミック・コンデンサの多くは、DC バイアス電圧が増加するにつれ、容量が定格値から大きく減少します。たとえば、小型表面実装セラミック・コンデンサがその定格電圧近くで動作するとき、その定格容量の 50% 以上を失うことは珍しくありません。その結果、最大動作電圧で意図する容量を実際に得るため、必要以上に大きな値の容量や電圧定格の高いコンデンサを使うことが必要になることがあります。詳細については、コンデンサ・メーカーの「容量と DC バイアス電圧」の曲線を参照してください。

表 2 に示されているコンデンサは、LTC3112 のアプリケーション回路に十分適した小型表面実装セラミック・コンデンサの例です。温度に対する容量低下を最小に抑えるため、示されている全てのコンデンサは X5R または X7R の誘電体のものです。

表2. 標準的バイパス・コンデンサおよび出力コンデンサ

| 製品番号                        | 値(μF) | 電圧(V) | サイズ(mm)<br>L × W × H |

|-----------------------------|-------|-------|----------------------|

| AVX LD103D226MAB2A          | 22    | 25    | 3.2 × 2.5 × 2.79     |

| Kemet C1210C476M4PAC7025    | 47    | 16    | 3.2 × 2.5 × 2.5      |

| Murata GRM32ER61E226KE15L   | 22    | 25    | 3.6 × 2.5 × 2.5      |

| Taiyo Yuden EMK325BJ476MM-T | 47    | 16    | 3.2 × 2.5 × 2.5      |

| TDK C5750X5RIC476M          | 47    | 16    | 5.7 × 5 × 2.3        |

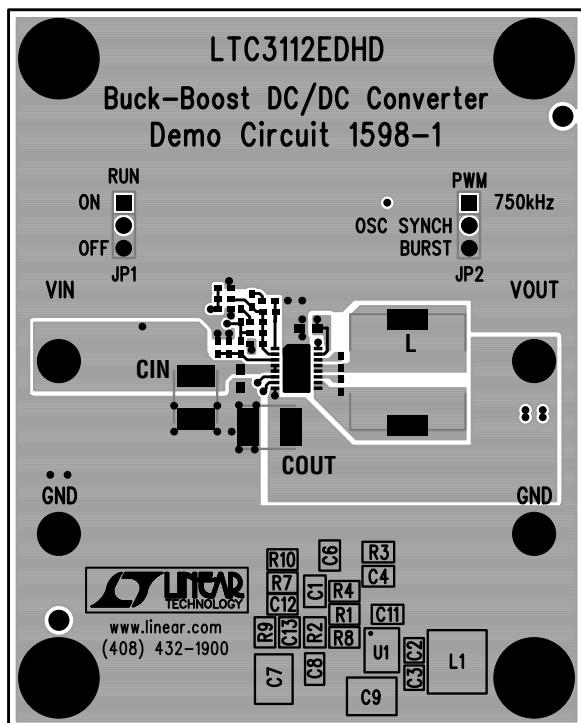

### PCB レイアウトの検討事項

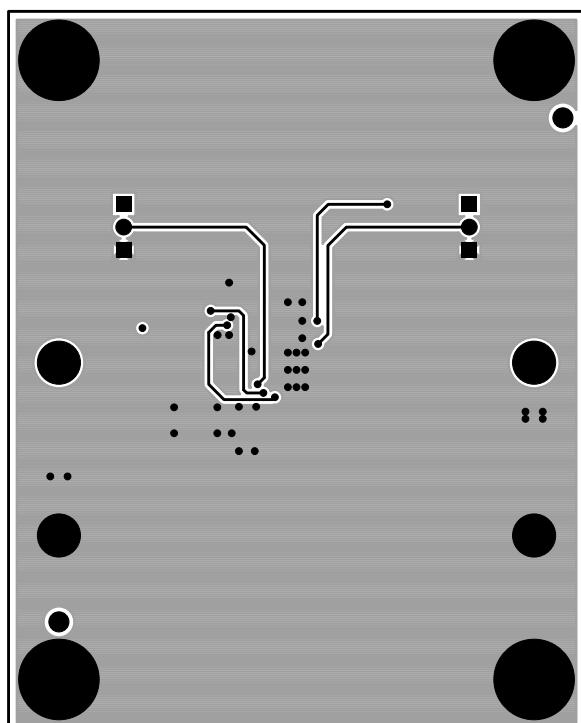

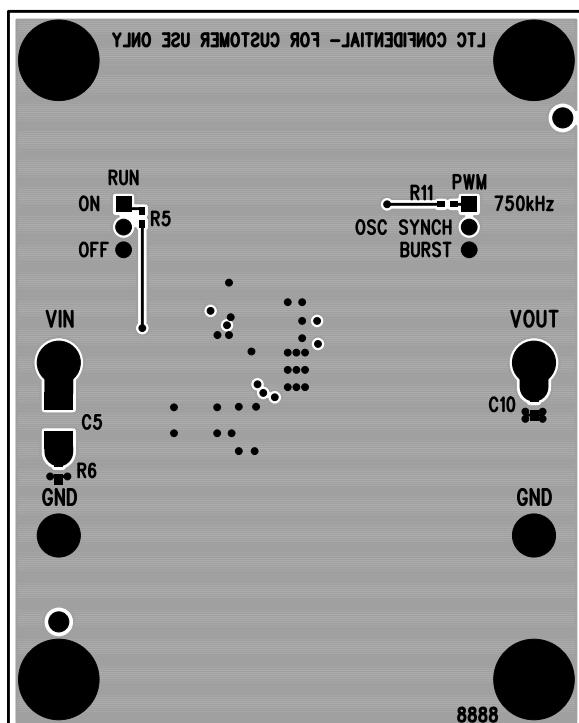

LTC3112 は大きな電流を高い周波数でスイッチングします。ノイズのない安定した効率の良いアプリケーション回路にするには、PCB のレイアウトに特別の注意が必要です。主要な検討事項のアウトラインを示すための代表的 4 層 PCB のレイアウトを図 3 に示します。主なガイドラインを以下にまとめます。

- 全動作電圧および電流範囲にわたって確実に動作を安定させるため、LTC3112 には 4 層基板を強く推奨します。専用の切れ目のないグランド・プレーンを、VIN、VOUT、SW1 および SW2 のトレースの直下に配置してミラー・プレーンを与える、dI/dt が高いエッジや dV/dt が高いエッジによるノイズ・ループを最小にします(図 3、第 2 層を参照)。

- 循環する全ての高電流経路をできるだけ短くします。コンデンサのグランドはできるだけ短い配線でビアを使ってグランド・プレーンに接続します。VIN のバイパス・コンデンサはできるだけデバイスの近くに配置し、グランドへの経路をできるだけ短くします(図 3 のトップ層を参照)。

- 露出パッドは LTC3112 の電力グランド接続です。多数のビアでバックパッドを直接グランド・プレーンに接続します。さらに、バックパッドに接続されるメタルを最大にすると熱環境が改善され、デバイスの電力処理能力が改善されます。

- 高電流部品とそれらの接続は全てグランド・プレーン上に配置し、ループの断面積を最小にします。これにより、EMI が最小になり、誘導性の電圧降下が減ります。

- 全ての高電流部品への接続をできるだけ幅広くして直列抵抗を減らします。これにより、効率が改善され、昇降圧コンバータの出力電流能力が最大化されます。

- 大きな循環電流が出力電圧検出を妨げないように、各抵抗分割器のグランドはデバイスの近くに電力接続から離して配置したビアを使ってグランド・プレーンに戻します。

- 抵抗分割器から帰還ピン FB への接続をできるだけ短くし、スイッチ・ピンの接続からできるだけ離します。

- 利用可能であれば内部の銅層で交差接続を行います。これらをグランド・プレーンに配置する必要があれば、グランド・プレーンのトレースをできるだけ短くして、グランド・プレーンへの搅乱を最小に抑えます(図 3 の第 3 層)。

## アプリケーション情報

トップ層

第2層

第3層

ボトム層(上面)

図3.PCB(例)のレイアウト

3112fb

## アプリケーション情報

### 降圧モードの小信号モデル

LTC3112 は電圧モード制御ループを使って出力電圧のレギュレーションを維持します。外部補償されたエラーアンプは COMP ピンをドライブして、パワースイッチの適切なデューティ・サイクルを発生します。外部補償ネットワークの使用により、広い範囲の出力電圧、スイッチング周波数、および LTC3112 がサポートする外部部品の値に対する閉ループ性能の最適化のための柔軟性が得られます。

昇降圧コンバータの小信号伝達関数は降圧モードと昇圧モードの動作で異なるので、両方の動作領域で確実に安定するように注意する必要があります。高い入力電圧から低い出力電圧に降圧するときコンバータは降圧モードで動作し、エラーアンプの出力 ( $V_{COMP}$ ) からコンバータの出力電圧への小信号伝達関数は次式で与えられます。

$$\left. \frac{V_0}{V_{COMP}} \right|_{BUCK\ MODE} = G_{BUCK} \frac{\left( 1 + \frac{s}{2\pi f_z} \right)}{1 + \frac{s}{2\pi f_0 Q} + \left( \frac{s}{2\pi f_0} \right)^2}$$

利得の項 ( $G_{BUCK}$ ) は 2 つの異なる成分からなります。以下の式で与えられるパルス幅変調器の利得と電力段の利得です。ここで、 $V_{IN}$  はボルトを単位とするコンバータの入力電圧、 $f$  は Hz を単位とするスイッチング周波数、 $R$  はオームを単位とする負荷抵抗、 $t_{LOW}$  はスイッチ・ピンの最小 “L” 時間です。スイッチ・ピンの最小 “L” 時間を示す曲線がこのデータシートの「標準的性能特性」のセクションに示されています。パラメータ  $R_S$  は電力段の平均直列抵抗を表しており、パワースイッチの抵抗の 2 倍とインダクタの DC 抵抗の和で近似することができます。

$$G_{BUCK} = G_{PWM} G_{POWER}$$

$$G_{PWM} = 2(1 - t_{LOW} f)$$

$$G_{POWER} = \frac{V_{IN} R}{(1 - t_{LOW} f)(R + R_S)}$$

降圧モードの利得は次式で十分近似されます。

$$G_{BUCK} = \frac{2 \cdot V_{IN} \cdot R}{R + R_S} \approx 2 \cdot V_{IN}$$

降圧モードの伝達関数は、出力コンデンサの ESR によって生じる单一のゼロを有します。ゼロの周波数 ( $f_Z$ ) は次式で与えられます。ここで、 $R_C$  と  $C_O$  はそれぞれ出力フィルタ・コンデンサの ESR(単位はオーム) と値(単位はファラッド) です。

$$f_Z = \frac{1}{2\pi R_C C_O}$$

ほとんどのアプリケーションで、出力電圧リップルを許容レベルに下げるため、ESR が非常に小さいコンデンサが使用されます。コンデンサの ESR のこのように低い値は非常に高い周波数のゼロを生じるので、このゼロは帰還ループの補償に大きな影響を与えるには一般に周波数が高すぎます。

降圧モードの伝達関数の分母は電力段の LC フィルタによって生じる 1 対の共振ポールを示しています。電力段の共振周波数 ( $f_0$ ) は次式で与えられます。ここで、 $L$  はヘンリーを単位とするインダクタの値です。

$$f_0 = \frac{1}{2\pi} \sqrt{\frac{R + R_S}{LC_0(R + R_C)}} \approx \frac{1}{2\pi} \sqrt{\frac{1}{LC_0}}$$

クオリティファクタ ( $Q$ ) は電圧ループの補償に大きく影響します。高い  $Q$  は共振周波数の近くで位相の急峻な減少を生じるからです。 $Q$  は電力段の減衰量に対して反比例の関係にあり、電力段の平均直列抵抗 ( $R_S$ ) によって大きく影響されます。 $R_S$  の値が小さいと  $Q$  が増加して共振周波数の近くで位相が鋭く減少するので、位相ブーストを強めるか、または適切な位相マージンを維持するために帯域幅を狭める必要があります。

$$Q = \frac{\sqrt{LC_0(R + R_C)(R + R_S)}}{RR_C C_0 + L + C_0 R_S(R + R_C)} \approx \frac{\sqrt{LC_0}}{\frac{L}{R} + C_0 R_S}$$

## アプリケーション情報

### 昇圧モードの小信号モデル

低い入力電圧から高い出力電圧に昇圧するとき昇降圧コンバータは昇圧モードで動作し、制御電圧 ( $V_{COMP}$ ) から出力電圧への小信号伝達関数は次式で与えられます。

$$\left. \frac{V_O}{V_{COMP}} \right|_{\text{BOOST MODE}} = G_{\text{BOOST}} \frac{\left(1 + \frac{s}{2\pi f_Z}\right) \left(1 - \frac{s}{2\pi f_{RHPZ}}\right)}{1 + \frac{s}{2\pi f_0 Q} + \left(\frac{s}{2\pi f_0}\right)^2}$$

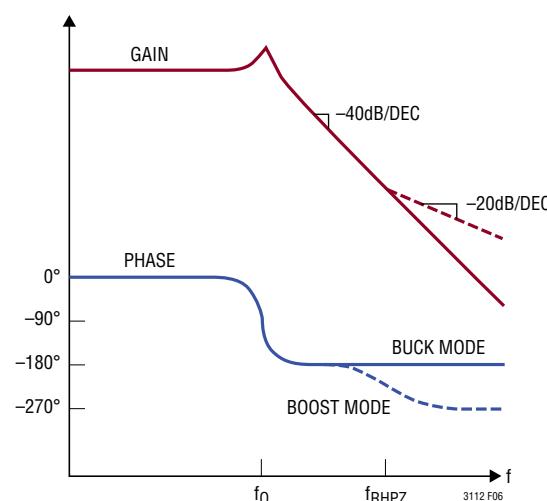

昇圧モード動作では、降圧モードと同様、出力コンデンサのESRによって生じる1対の共振ポールおよび1個のゼロによって伝達関数は特性が規定されます。ただし、これらに加えて右半平面にゼロがあり、高い周波数では利得が増加し、位相が減少します。その結果、十分な位相マージンを維持するため、昇圧モード動作のクロスオーバー周波数は一般に降圧モードの場合より低く設定する必要があります。

昇圧モードの利得 ( $G_{\text{BOOST}}$ ) は2つの成分からなります。パルス幅変調器と電力段です。昇圧モードの電力段の利得は次式で与えられます。

$$G_{\text{POWER}} \cong \frac{V_{\text{OUT}}^2}{(1-t_{\text{LOW}}f)V_{\text{IN}}}$$

個々の項を結合することにより、昇圧モードの総利得は次式に整理することができます。降圧モードの場合とは異なり、昇圧モードの利得は入力電圧と出力電圧両方の関数であることに注意してください。

$$G_{\text{BOOST}} \cong \frac{2 \cdot V_{\text{OUT}}^2}{V_{\text{IN}}}$$

昇圧モード動作では、右半平面のゼロ ( $f_Z$ ) の周波数は次式で与えられます。右半平面のゼロの周波数は高負荷および大きなインダクタでは減少します。

$$f_{RHPZ} = \frac{R(1-t_{\text{LOW}}f)^2 V_{\text{IN}}^2}{2\pi L V_{\text{OUT}}^2}$$

昇圧モードでは、次式で示されているように、電力段の共振周波数は入力電圧と出力電圧に依存します。

$$f_0 = \frac{1}{2\pi} \sqrt{\frac{R V_{\text{IN}}^2}{L C_0 (R + R_C)}} \cong \frac{1}{2\pi} \cdot \frac{V_{\text{IN}}}{V_{\text{OUT}}} \sqrt{\frac{1}{LC}}$$

最後に、昇圧モード動作の電力段のクオリティファクタの大きさは次式で与えられます。

$$Q = \frac{\sqrt{LC_0 R \left( R_S + \frac{RV_{\text{IN}}^2}{V_{\text{OUT}}^2} \right)}}{L + C_0 R_S R}$$

### 電圧ループの補償

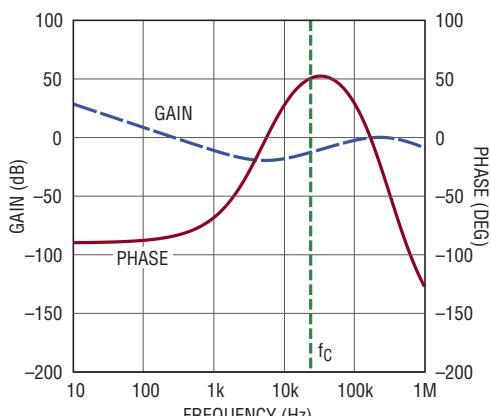

エラーアンプの出力 ( $V_{COMP}$ ) から出力電圧への伝達関数は、図4のボーデ線図に示されているように、1組の共振ポールおよび出力コンデンサのESRによって生じることのあるゼロによって特性が規定されることを、LTC3112の小信号モデルは明らかにしています。昇圧モード動作では、右半平面に追加のゼロがあり、高い周波数では位相遅れを生じて利得が増加します。一般に、ループのクロスオーバー周波数が十分低くて右半平面のゼロによる位相の減少が最小に抑えられるように、補償ネットワークは設計されます。降圧モードの低周波数利得は一定ですが、昇圧モードでは  $V_{\text{IN}}$  と  $V_{\text{OUT}}$  の両方にともなって変化します。

図4.昇降圧コンバータのボーデ線図

## アプリケーション情報

充電、LED 照明など、最適化された出力電圧の過渡応答を必要としないアプリケーションでは、図 5 に示されているような簡単なタイプ I の補償ネットワークを使って電圧ループを安定化することができます。十分な位相マージンを確保するため、制御ループのクロスオーバー周波数が共振周波数より十分下になるようにエラーアンプの利得を十分低くする必要があります。

図5. タイプIの補償を備えたエラーアンプ

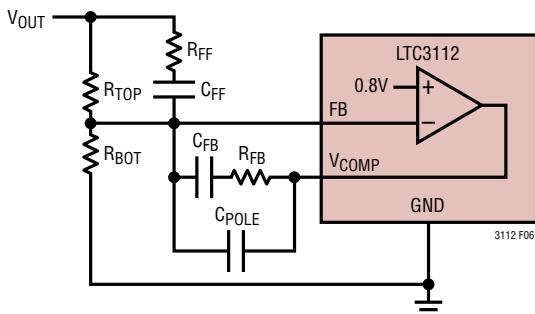

ほとんどのアプリケーションでは、タイプ I で補償されたループの帯域幅は低いので、十分な過渡応答性能が得られません。広い帯域幅の帰還ループを実現し、過渡応答を最適化し、出力コンデンサのサイズを最小に抑えるには、図 6 に示されているようなタイプ III の補償ネットワークが必要です。

図6. タイプ III の補償を備えたエラーアンプ

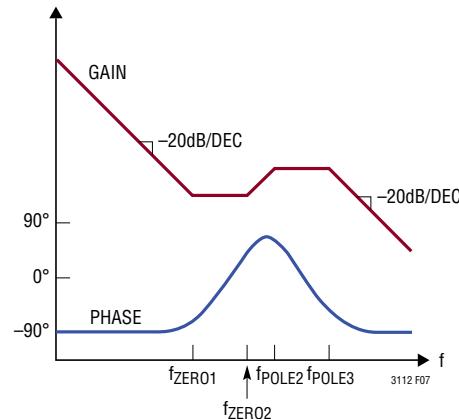

タイプ III の補償ネットワークのボーデ線図を図 7 に示します。タイプ III の補償ネットワークは原点近くのポールを与え、DC で非常に高いループ利得を生じ、安定化電圧の定常状態の誤差を最小に抑えます。 $f_{ZERO1}$  と  $f_{ZERO2}$  に位置する 2 個のゼロは十分な位相ブーストを与えるので、ループのクロスオーバー周波数を電力段の共振周波数 ( $f_O$ ) より上に設定することができます。タイプ III の補償ネットワークは 2 番目と 3 番目のポールも生じます。周波数  $f_{POLE2}$  に位置する 2 番目のポールはエラーアンプの利得をゼロ勾配に減少させて、ループのクロスオーバーが高すぎる周波数に拡張するのを防ぎます。周波数  $f_{POLE3}$  に位置する 3 番目のポールは高周波数スイッチング・ノイズを減衰させます。

図7. タイプIIIの補償のボーデ線図

補償されたタイプ III のエラーアンプの、抵抗分割器の入力からエラーアンプの出力 ( $V_{COMP}$ ) への伝達関数は次のとおりです。

$$\frac{V_{COMP}(s)}{V_{OUT}(s)} = G_{EA} \frac{\left(1 + \frac{s}{2\pi f_{ZERO1}}\right)\left(1 + \frac{s}{2\pi f_{ZERO2}}\right)}{s\left(1 + \frac{s}{2\pi f_{POLE1}}\right)\left(1 + \frac{s}{2\pi f_{POLE2}}\right)}$$

エラーアンプの利得は次式で与えられます。 $C_{FB}$  は一般に  $C_{POLE}$  よりはるかに値が大きいので、ほとんどの場合、簡単な近似値で十分精確です。

$$G_{EA} = \frac{1}{R_{TOP}(C_{FB} + C_{POLE})} \approx \frac{1}{R_{TOP}C_{FB}}$$

タイプ III の補償ネットワークのポールとゼロの周波数は以下の式を使って計算することができます。ここで、全ての周波数の単位は Hz、抵抗の単位はオーム、容量の単位はファラッドです。

## アプリケーション情報

$$f_{ZERO1} = \frac{1}{2\pi R_{FB} C_{FB}}$$

$$f_{ZERO2} = \frac{1}{2\pi(R_{TOP} + R_{FF})C_{FF}} \approx \frac{1}{2\pi R_{TOP} C_{FF}}$$

$$f_{POLE2} = \frac{C_{FB} + C_{POLE}}{2\pi C_{FB} C_{POLE} R_{FB}} \approx \frac{1}{2\pi C_{POLE} R_{FB}}$$

$$f_{POLE3} = \frac{1}{2\pi C_{FF} R_{FF}}$$

ほとんどのアプリケーションでは、ループのクロスオーバー周波数は電力段の共振周波数よりは上だが、昇圧モードの右半平面のゼロよりは下になるように補償ネットワークが設計され、追加の位相低下を最小に抑えます。クロスオーバー周波数が決定されると、位相マージンを最大にするため、補償ネットワークによって与えられる位相ブーストはそのポイントを中心にします。ゼロと高次のポールの周波数が大きく離れていると、高いピーク位相ブーストが与えられますが、エラーアンプの利得も増加して、ループのクロスオーバーを高い周波数に押しやすくなります。

電力段の Q はどれだけ急速に電力段の 180° の位相低下が生じるかを決定するので、この Q は補償ネットワークの設計に大きく影響する可能性があります。直列抵抗 ( $R_S$ ) の値が非常に小さいと Q が高くなり、鋭い位相低下が生じます。このような場合、共振周波数の上で電力段の位相は急速に -180° に低下し、総位相マージンは補償ネットワークによって与える必要があります。ただし、電力段の損失が大きいと (大きな  $R_S$ )、Q ファクタは下がり、位相低下は徐々に起きます。その結果、電力段の位相はクロスオーバー周波数で -180° にそれほど近づかず、補償ネットワークに要求される位相ブーストは小さくなります。

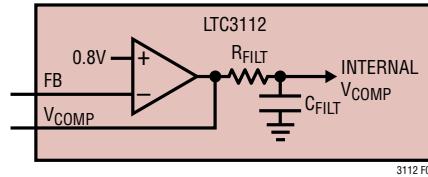

LTC3112 のエラーアンプは、スイッチング・ノイズを除去してそれが制御ループに干渉するのを防ぐため、固定最大帯域幅になるように設計されています。周波数領域の観点からは、図 8 に示されているように、これは追加のシングル・ポールと見ることができます。このポールの公称周波数は 400kHz です。約 60kHz より下の標準的ループのクロスオーバー周波

数の場合、この追加ポールが寄与する位相は微小です。ただし、クロスオーバー周波数の高いループでは、この追加の位相減少を考慮に入れて補償ネットワークを設計します。

図8.内部ループ・フィルタ

### ループ補償の例

このセクションでは、LTC3112 の標準的な応用回路の補償ネットワークの設計を例を使って説明します。この例では、3.5V ~ 15V の範囲の入力電力源から 1A の負荷に給電する能力のある 5V 安定化出力電圧を発生します。公称 750kHz のスイッチング周波数を選択しました。このアプリケーションでは、最大インダクタ電流リップルは最大入力電圧で発生します。ワーストケースのインダクタ電流リップルを約 1A に制限するため、4.7μH のインダクタの値が選択されました。値が 47μF の低 ESR 出力コンデンサが指定され、(ワーストケースの降圧比と最大負荷電流で生じる) 約 10mV のワーストケースの出力電圧リップルを生じます。まとめると、この LTC3112 の応用例の電力段の主要な仕様は以下のとおりです。

$$f = 0.75\text{MHz}, t_{LOW} = 0.2\mu\text{s}$$

$$V_{IN} = 3.5V \sim 15V$$

$$V_{OUT} = 5V/1A$$

$$C_{OUT} = 47\mu\text{F}, R_C = 5\text{m}\Omega$$

$$L = 4.7\mu\text{H}, R_L = 50\text{m}\Omega$$

電力段のパラメータが規定されたので、補償ネットワークを設計することができます。ほとんどのアプリケーションでは、最も補償の困難な箇所は最大の昇圧比および最高の負荷電流での昇圧モード動作です。この条件では、周波数が最低の右半平面のゼロが発生し、そのため位相が最も減少するからです。

## アプリケーション情報

したがって、妥当な方法として、このワーストケースの箇所で補償ネットワークを設計し、他の動作条件全体で十分な位相マージンが存在することを検証します。この応用例では ( $V_{IN} = 3.5V$ 、最大1Aの負荷電流)、右半平面のゼロは60kHzに位置し、これが制御ループの帯域幅を決定する支配的要因になります。

補償ネットワークの設計の最初のステップとして、補償されるループの目標クロスオーバー周波数を決定します。妥当な出発点として、補償ネットワークは約 60° のピーク位相ブーストを発生するとします。したがって、60° の位相マージンを得るために、ループのクロスオーバー周波数 ( $f_C$ ) を、そこで昇降圧コンバータの位相が -180° に達する周波数として選択します。その結果、ループのクロスオーバー周波数では、下に示すように、合計された位相は単にエラーアンプによって与えられる 60° の位相になります。

$$\begin{aligned}\text{位相マージン} &= \phi_{BUCK-BOOST} + \phi_{ERRORAMPLIFIER} + 180^\circ \\ &= -180^\circ + 60^\circ + 180^\circ = 60^\circ\end{aligned}$$

同様に、45° の位相マージンが必要であれば、目標とするクロスオーバー周波数は、そこで昇降圧コンバータの位相が -195° に達する周波数を選択して、クロスオーバー周波数での合計位相が望みの 45° の位相マージンになるようにします。

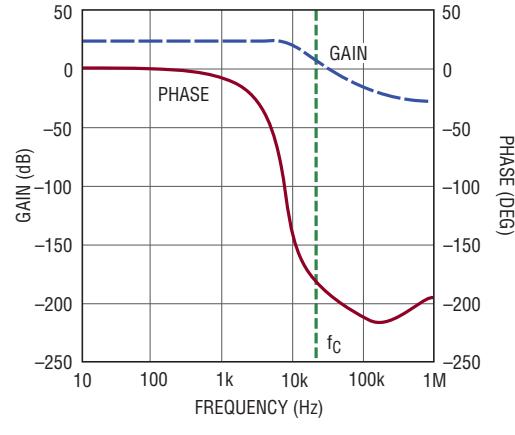

この例では、パラメータのばらつきや動作条件の変動にわたって適切な性能が得られるように、60° の位相マージンで設計します。その結果、目標クロスオーバー周波数 ( $f_C$ ) はそこで昇降圧コンバータが -180° に達するポイントになります。この周波数を解析的に求めることは、電力段の共振の Q ファクタに大きく影響されるため、一般に困難です。そのため、図 9 に示されているように、昇降圧コンバータのボーディングから求めるのが最善です。このボーディングは前に規定した電力段のパラメータを使った LTC3112 昇降圧コンバータのものであり、LTSpice® を使って小信号モデルの式から作成しました。この場合、位相は 35kHz で -180° に達するので、 $f_C = 35kHz$  が補償ループの目標クロスオーバー周波数になります。

図9.コンバータのボーディング、 $V_{IN} = 3.5V$ 、 $I_{LOAD} = 1A$

図 9 のボーディングから、目標クロスオーバー周波数での出力段の利得は 7dB です。したがって、この周波数を補償されたループのクロスオーバー周波数にするため、 $f_C$  での全ループ利得を 0dB に調整する必要があります。これを達成するため、補償ネットワークの利得を、クロスオーバー周波数で -7dB に設計する必要があります。

設計過程のこのポイントで、補償ネットワークに対して設定された 3 つの制約があります。その利得は  $f_C = 35kHz$  で -7dB、ピーク位相ブーストは 60°、位相ブーストの中心は  $f_C = 35kHz$  でなければなりません。これらの目標を満たす補償ネットワークを設計する 1 つの方法として、このデータシートの表紙に示されている標準的補償ネットワークの補償されたエラーアンプのボーディングを LTSpice でシミュレートします。次いで、要求される制約を満たすまで、利得、ポール周波数およびゼロ周波数を反復調整することができます。

代わりに、解析的手法を使って、望みの位相ブースト、中心周波数および利得を備えた補償ネットワークを設計することができます。この手順は、タイプ III の補償ネットワークは自由度が大きいため、一般に容易ではありません。ただし、両方の補償のゼロが同じ周波数 ( $f_Z$ ) で生じ、両方の高次ポール ( $fPOLE2$  と  $fPOLE3$ ) が共通の周波数 ( $f_P$ ) で生じると仮定することにより、設計過程を簡素化することができます。

## アプリケーション情報

ほとんどの場合、これは妥当な仮定です。ゼロは一般に 1kHz と 10kHz の間に位置し、ポールは一般にはるかに高い周波数で互いに近くに位置するからです。これを仮定すると、補償されたエラーアンプによって与えられる最大位相ブースト ( $\phi_{MAX}$ ) は、次式で示されるように、単にポールとゼロの間の開きによって決まります。

$$\phi_{MAX} = 4 \tan^{-1} \left( \sqrt{\frac{f_p}{f_z}} \right) - 270^\circ$$

妥当な選択として、ポールの周波数 ( $f_p$ ) がゼロの周波数 ( $f_z$ ) の約 50 倍になるように選択します。これにより、前に仮定したように、約  $\phi_{MAX} = 60^\circ$  のピーク位相ブーストが与えられます。次に、ピーク位相が目標のクロスオーバー周波数で生じるように位相ブーストの中心を定める必要があります。最大位相ブースト ( $f_{CENTER}$ ) は、下に示されているように、ポール周波数とゼロ周波数の幾何平均です。

$$f_{CENTER} = \sqrt{f_p f_z} = \sqrt{50} \cdot f_z \approx 7f_z$$

したがって、ポール周波数とゼロ周波数の間に 50 倍の開きがある場合に位相の中心を定めるには、以下の式で与えられているように、ゼロをクロスオーバー周波数の 1/7 に位置させ、ポールをクロスオーバー周波数の 7 倍に位置させます。

$$f_z = \frac{1}{7} f_C = \frac{1}{7} (35\text{kHz}) = 5\text{kHz}$$

$$f_p = 7f_C = 7(35\text{kHz}) = 250\text{kHz}$$

ポールとゼロのこの配置により、クロスオーバー周波数 ( $f_C$ ) に中心が置かれた  $60^\circ$  のピーク位相ブーストが生じます。次に、望みの目標クロスオーバー周波数を実現するため、最大位相ブースト・ポイントでの補償ネットワークの利得 ( $G_{CENTER}$ ) を  $-7\text{dB}$  に設定する必要があります。最大位相利得のポイントでの補償されたエラーアンプの利得は次式で与えられます。

$$G_{CENTER} = 10 \log \left[ \frac{2\pi f_p}{(2\pi f_z)^3 (R_{TOP} C_{FB})^2} \right] \text{dB}$$

ポール周波数とゼロ周波数の間の 50 倍の開きを仮定すると、上式は次式に整理されます。

$$G_{CENTER} = 20 \log \left[ \frac{50}{2\pi f_C R_{TOP} C_{FB}} \right] \text{dB}$$

この式は補償部品の値の決定に必要な 1 組の制約を全て満たします。特に、2 つのゼロ ( $f_{ZERO1}$  と  $f_{ZERO2}$ ) は 5kHz の近くに位置させます。2 つのポール ( $f_{POLE2}$  と  $f_{POLE3}$ ) は 250kHz の近くに位置させ、クロスオーバー周波数の利得  $G_{CENTER} = -7\text{dB}$  となるように利得を設定します。

補償部品の値を定める最初のステップとして、抵抗分割器を流れる静止電流を許容できる程度に低くする  $R_{TOP}$  の値を選択します。 $R_{TOP} = 845\text{k}\Omega$  の値は妥当な選択で、いくつかの応用回路で使用されます。次に、クロスオーバー周波数でのエラーアンプの利得を  $-7\text{dB}$  に設定するため、 $C_{FB}$  の値を次のように求めることができます。

$$G_{CENTER} = -7\text{dB} = 20 \log \left[ \frac{50}{2\pi(35\text{kHz})(845\text{k}\Omega)C_{FB}} \right]$$

$$C_{FB} = \frac{50}{0.185 \cdot 10^{12} \cdot \text{antilog}\left(\frac{-7}{20}\right)} \approx 680\text{pF}$$

前のセクションに与えられているポール周波数とゼロ周波数の式を使って、補償ポールを 250kHz に、ゼロを 5kHz に設定することができます。最初のゼロの周波数  $f_{ZERO1}$  を 5kHz に設定すると、 $R_{FB}$  は次の値になります。

$$R_{FB} = \frac{1}{2\pi(680\text{pF})(5\text{kHz})} \approx 45\text{k}\Omega$$

2 つのゼロをわずかに分離するため  $33\text{k}\Omega$  が選択され、高い方のゼロ周波数は 7kHz になります。これにより、自由なパラメータ ( $C_{POLE}$ ) が周波数  $f_{POLE1}$  を 250kHz の共通ポール周波数に設定します。

## アプリケーション情報

$$C_{POLE} = \frac{1}{2\pi(33k\Omega)(250\text{kHz})} \approx 22\text{pF}$$

次に、 $C_{FF}$  を選択して、2番目のゼロ ( $f_{ZERO2}$ ) を 5kHz の共通ゼロ周波数に設定することができます。

$$C_{FF} = \frac{1}{2\pi(845k\Omega)(5\text{kHz})} \approx 40\text{pF}$$

この場合、47pF の  $C_{FF}$  を選択して、2番目のゼロは低い方の 4kHz にしました。最後に、抵抗値  $R_{FF}$  を選択して 2番目のポールを配置することができます。

$$R_{FF} = \frac{1}{2\pi(47\text{pF})(250\text{kHz})} \approx 13k\Omega$$

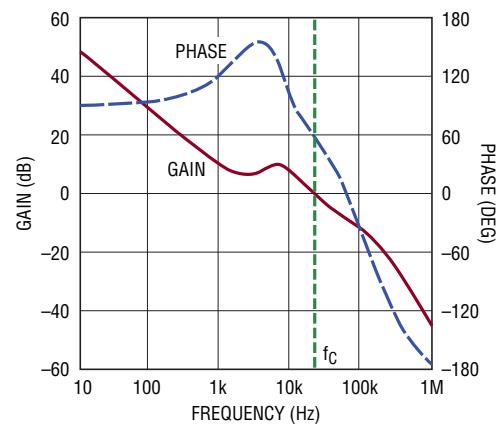

10kΩを選択して325kHzのポール周波数を与えます。補償ネットワークのポール周波数、ゼロ周波数および利得が確定したので、次のステップでは、補償されたエラーアンプのボーデ図を作成して利得と位相の特性を確認します。設計された補償部品の値を使ったエラーアンプのボーデ図を図10に示します。ボーデ図は、ピーク位相が30kHzの近くに生じ、そのポイントの位相ブーストが約60°であることを確認しています。さらに、ピーク位相周波数での利得は-10dBで、設計目標に近い値です。

設計過程の最後のステップとして、設計された補償ネットワークを使ってループ全体のボーデ図を計算し、その位相マージ

図10.補償されたエラーアンプのボーデ線図

ンとクロスオーバー周波数を確認します。この例の全ループのボーデ図を図11に示します。その結果、ループのクロスオーバー周波数は25kHz、位相マージンは約60°です。クロスオーバー周波数は設計目標の35kHzよりいくらか低いが、右半平面の厄介なゼロからは遠く離れています。

図11.全ループのボーデ線図

この帰還設計の例は、3.5V<sub>IN</sub>、5V<sub>OUT</sub>、1A負荷電流で設計されました。昇圧モードでの位相マージンは、V<sub>IN</sub>が低く、V<sub>OUT</sub>、負荷電流またはインダクタの値が高いほど、右半平面のゼロが低い周波数にシフトするため減少します。

注意点として、電力段のLC共振周波数でのQの大きさは、インダクタのESRおよびLTC3112のR<sub>ON</sub>の低いMOSFETを含むR<sub>S</sub>項(直列抵抗)に大きく依存します。全直列抵抗が低いとQが高くなるので、帰還設計が困難になります。直列抵抗が高いとQを下げる所以、ループのクロスオーバー周波数が低くなります。

ループ全体のボーデ図を全動作条件および部品の値のばらつきにわたってチェックして、全ての場合に十分な位相マージンが存在することを確認します。時間領域のシミュレーションによって、また実際の回路でコンバータの過渡応答を評価して、ループの安定性も確認します。

## 標準的応用例

1セル、2セルまたは3セル・リチウムイオン・バッテリから5V

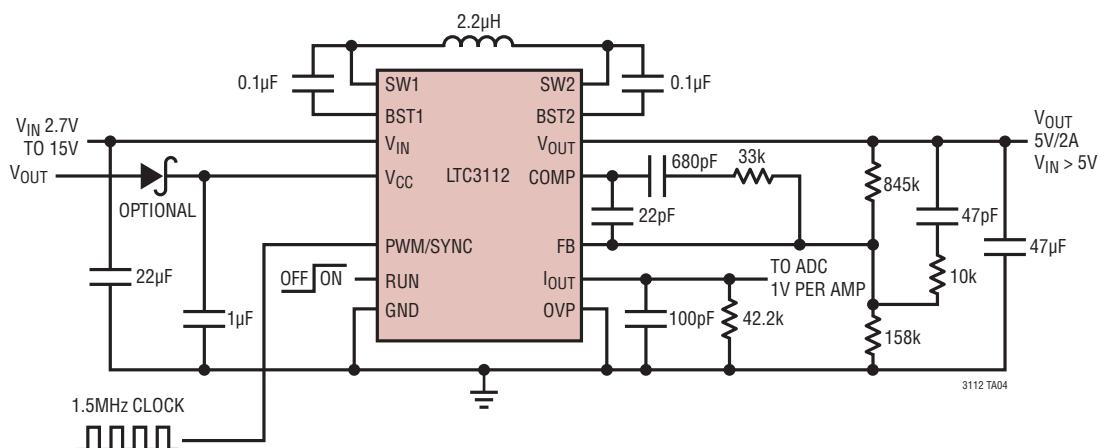

1.5MHzクロックに同期したLTC3112、5V/2A出力

3112 TA04a

## 標準的応用例

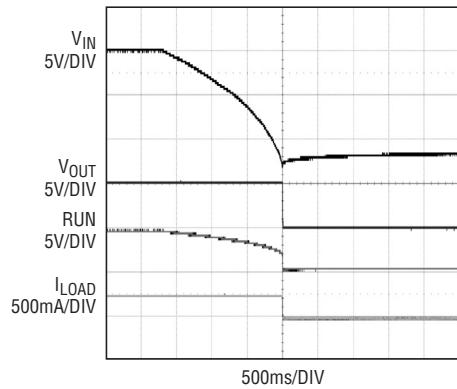

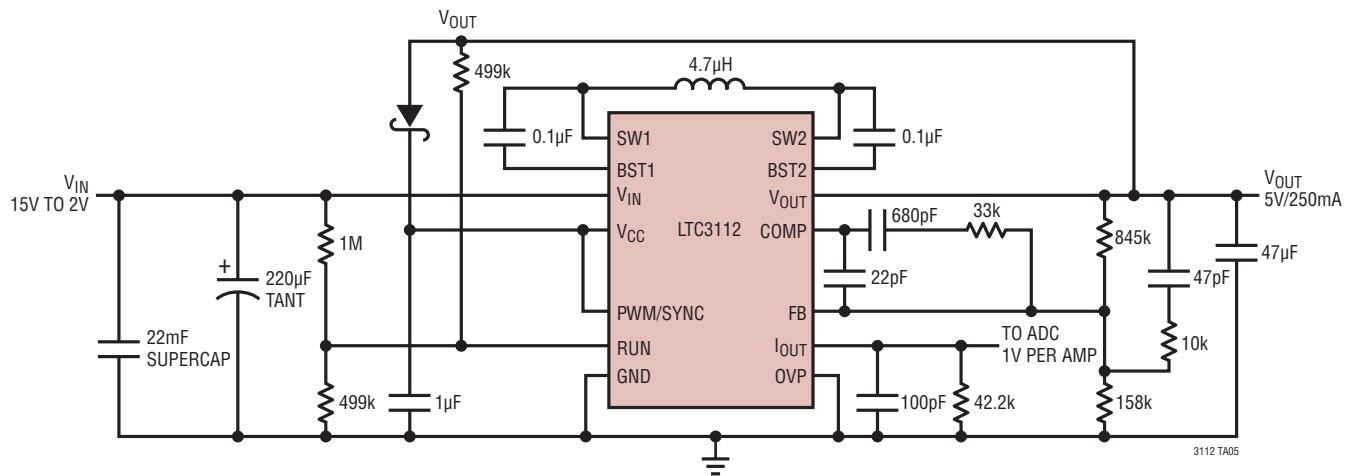

250mA負荷で $V_{IN} = 2V$ までスーパー・キャパシタから動作する5Vバックアップ電源

3112 TA05a

## 標準的応用例

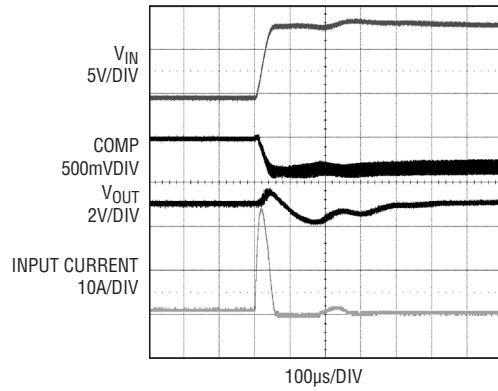

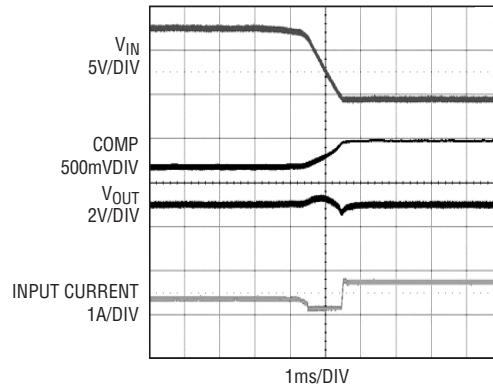

$V_{IN}$  フィードフォワード・ネットワークを使った、1セルまたは2セル・リチウムイオン・バッテリから12V ACアダプタ・ソースへのステップ応答

ACアダプタのプラグイン

3112 TA06a

ACアダプタの切断

3112 TA06b

3112fb

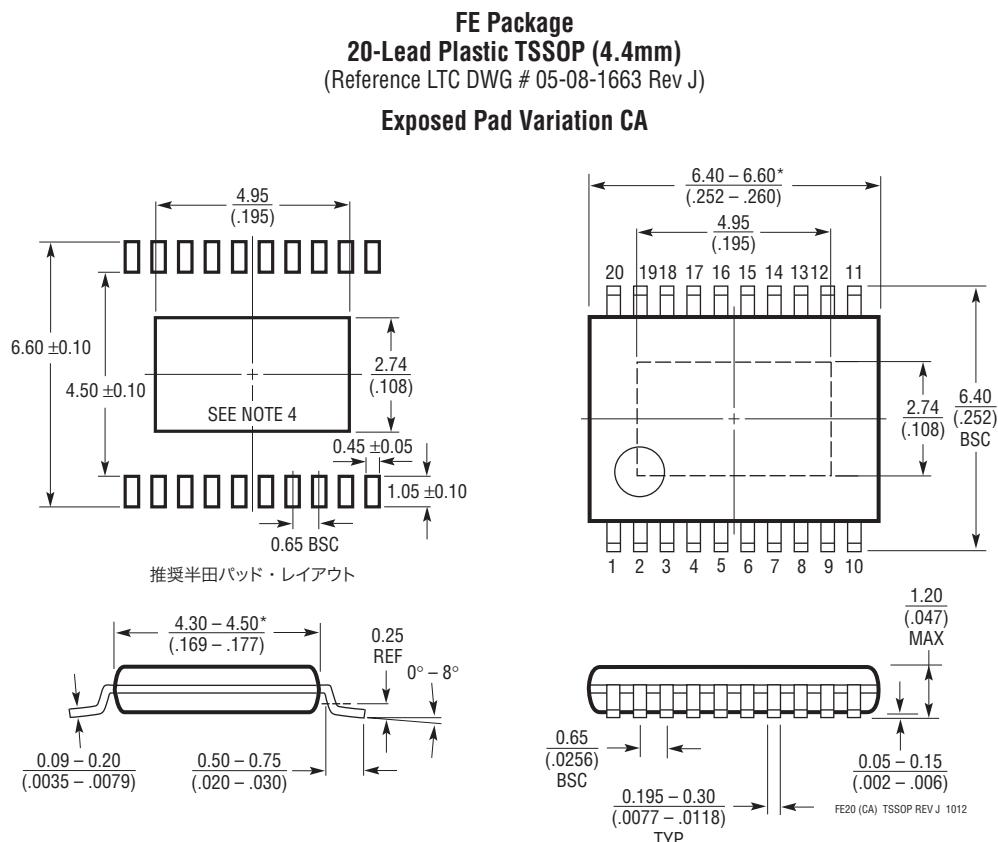

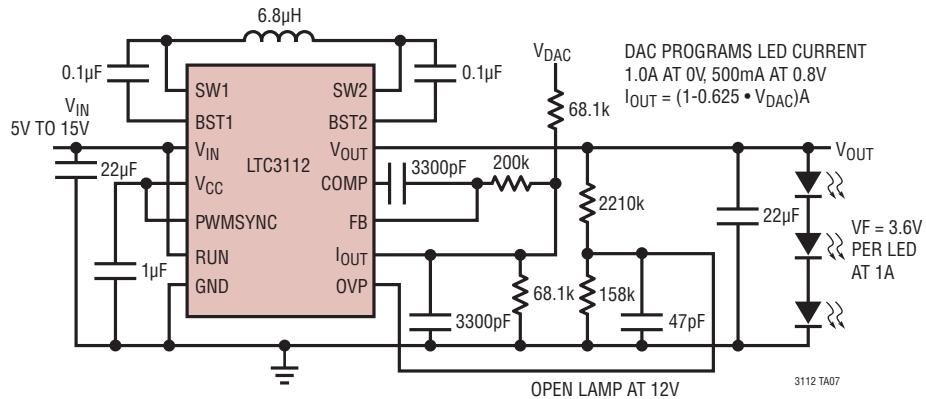

## 標準的応用例

広い入力電源範囲から安定化された12V出力

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> をご覧ください。

**DHD Package

16-Lead Plastic DFN (5mm x 4mm)**

(Reference LTC DWG # 05-08-1707)

推奨する半田パッドのピッチと寸法

NOTE:

1. 図はJEDECパッケージ・アウトラインMO-229のバージョンのバリエーション (WJGD-2) として提案。

2. 図は実寸とは異なる。

3. 全ての寸法はミリメートル。

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない。モールドのバリは（もしあれば）各サイドで0.15mmを超えないこと。

5. 露出パッドは半田メッキとする。

6. 網掛けの部分はパッケージの上面と底面のピン1の位置の参考に過ぎない。

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> をご覧ください。

## 改訂履歴

| REV | 日付    | 概要                                                                                                                    | ページ番号                    |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------|--------------------------|

| A   | 6/13  | 絶対最大定格: $I_{OUT}$ 電圧の仕様を明確化。<br>RUN thresholdの仕様を明確化。<br>「熱に関する検討事項」の最後の段落を明確化。<br>LTC4352の製品番号を明確化。<br>「関連製品」の表を明確化。 | 2<br>3<br>12<br>28<br>32 |

| B   | 10/13 | 「降圧モードの小信号モデル」の文章を明確化。<br>$C_{FB}$ の式を明確化。                                                                            | 18<br>23                 |

## 標準的応用例

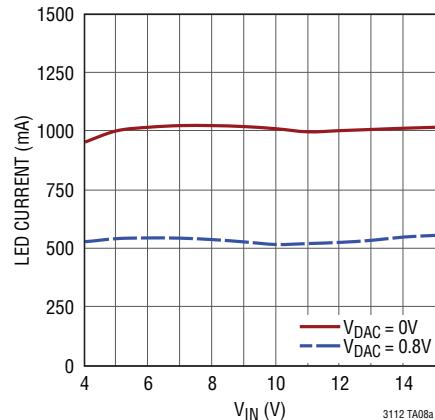

10W、10V高光度LEDドライバ、プログラム可能な電流および低損失検出

LED電流とV<sub>IN</sub>およびDAC電圧

## 関連製品

| 製品番号      | 説明                                                                     | 注釈                                                                                                                          |

|-----------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| LTC3531   | 200mA昇降圧同期整流式DC/DCコンバータ                                                | V <sub>IN</sub> :1.8V～5.5V, V <sub>OUT</sub> :3.3V, I <sub>Q</sub> = 16μA, I <sub>SD</sub> < 1μA, SOT23, DFNパッケージ           |

| LTC3129   | 15V、200mA同期整流式昇降圧DC/DCコンバータ                                            | V <sub>IN</sub> :2.42V～15V, V <sub>OUT</sub> :1.4V～15.75V, I <sub>Q</sub> = 11.3μA, I <sub>SD</sub> < 10nA, QFNおよびMSOPパッケージ |

| LTC3533   | 2A (I <sub>OUT</sub> )、2MHz同期整流式昇降圧DC/DCコンバータ                          | V <sub>IN</sub> :1.8V～5.5V, V <sub>OUT</sub> :1.8V～5.25V, I <sub>Q</sub> = 40μA, I <sub>SD</sub> < 1μA, DFNパッケージ            |

| LTC3113   | 3A、低ノイズの同期整流式昇降圧DC/DCコンバータ                                             | V <sub>IN</sub> 又はV <sub>OUT</sub> :1.8V～5.5V, I <sub>Q</sub> = 40μA, I <sub>SD</sub> < 1μA, DFNおよびTSSOPパッケージ               |

| LTC3534   | 7V、500mA同期整流式昇降圧DC/DCコンバータ                                             | V <sub>IN</sub> :2.4V～7V, V <sub>OUT</sub> :1.8V～7V, I <sub>Q</sub> = 25μA, I <sub>SD</sub> < 1μA, DFN, GNパッケージ             |

| LTC3538   | 800mA同期整流式昇降圧DC/DCコンバータ                                                | V <sub>IN</sub> :2.4V～5.5V, V <sub>OUT</sub> :1.8V～5.25V, I <sub>Q</sub> = 35μA, I <sub>SD</sub> < 5μA, DFNパッケージ            |

| LTC3440   | 600mA (I <sub>OUT</sub> )、2MHz同期整流式昇降圧DC/DCコンバータ                       | V <sub>IN</sub> :2.5V～5.5V, V <sub>OUT</sub> :2.5V～5.25V, I <sub>Q</sub> = 25μA, I <sub>SD</sub> < 1μA, MSOPおよびDFNパッケージ     |

| LTC3441   | 1.2A (I <sub>OUT</sub> )、1MHz同期整流式昇降圧DC/DCコンバータ                        | V <sub>IN</sub> :2.4V～5.5V, V <sub>OUT</sub> :2.4V～5.25V, I <sub>Q</sub> = 25μA, I <sub>SD</sub> < 1μA, DFNパッケージ            |

| LTC3442   | 1.2A (I <sub>OUT</sub> )、2MHz同期整流式昇降圧DC/DCコンバータ、プログラム可能なBurst Mode動作付き | V <sub>IN</sub> :2.4V～5.5V, V <sub>OUT</sub> :2.4V～5.25V, I <sub>Q</sub> = 35μA, I <sub>SD</sub> < 1μA, DFNパッケージ            |

| LTC3443   | 高電流マイクロパワー600kHz同期整流式昇降圧DC/DCコンバータ                                     | V <sub>IN</sub> :2.4V～5.5V, V <sub>OUT</sub> :1.5V～5.25V, I <sub>Q</sub> = 28μA, I <sub>SD</sub> < 1μA, DFNパッケージ            |

| LTC3115-1 | 2A (I <sub>OUT</sub> )、40V同期整流式昇降圧DC/DCコンバータ                           | V <sub>IN</sub> :2.7V～40V, V <sub>OUT</sub> :2.7V～40V, I <sub>Q</sub> = 30μA, I <sub>SD</sub> < 3μA, DFNおよびTSSOPパッケージ       |

| LTC3780   | 高効率、同期整流式4スイッチ昇降圧コンバータ                                                 | V <sub>IN</sub> :4V～36V, V <sub>OUT</sub> :0.8V～30V, I <sub>Q</sub> = 1500μA, I <sub>SD</sub> < 55μA, QFNパッケージ              |

| LTC3785   | 10V、高効率、同期整流式、No R <sub>SENSE</sub> ™、昇降圧コントローラ                        | V <sub>IN</sub> :2.7V～10V, V <sub>OUT</sub> :2.7V～10V, I <sub>Q</sub> = 86μA, I <sub>SD</sub> < 15μA, QFNパッケージ              |

| LTC3101   | 入力電圧範囲の広い複数出力DC/DCコンバータとPowerPath™コントローラ                               | V <sub>IN</sub> :1.8V～5.5V, V <sub>OUT</sub> :1.5V～5.25V, I <sub>Q</sub> = 38μA, I <sub>SD</sub> < 15μA, QFNパッケージ           |

| LTC3522   | 同期整流式400mA昇降圧および200mA降圧                                                | V <sub>IN</sub> :2.4V～5.5V, V <sub>OUT</sub> :2.2V～5.25V, I <sub>Q</sub> = 25μA, I <sub>SD</sub> < 1μA, QFNパッケージ            |

| LTC3530   | 入力電圧範囲の広い同期整流式昇降圧DC/DCコンバータ                                            | V <sub>IN</sub> :1.8V～5.5V, V <sub>OUT</sub> :1.8V～5.25V, I <sub>Q</sub> = 40μA, I <sub>SD</sub> < 1μA, DFNパッケージ            |