# 2A 双方向昇降圧 DC/DC レギュレータおよび チャージャ/バランサ

## 特長

- $V_{CAP}$  の動作範囲: 0.1V ~ 5.5V

- $V_{SYS}$  の動作範囲: 1.71V ~ 5.25V

- 充電モードからバックアップ・モードへの自動切り替え

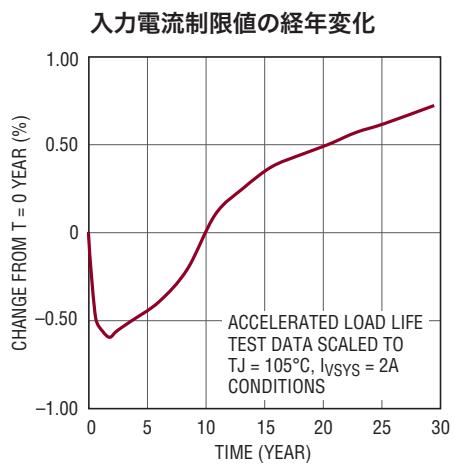

- $\pm 2\%$  精度のプログラム可能な充電入力電流制限: 125mA ~ 2A

- バックアップ電圧精度:  $\pm 1\%$

- バックアップ・コンデンサの自動バランス調整

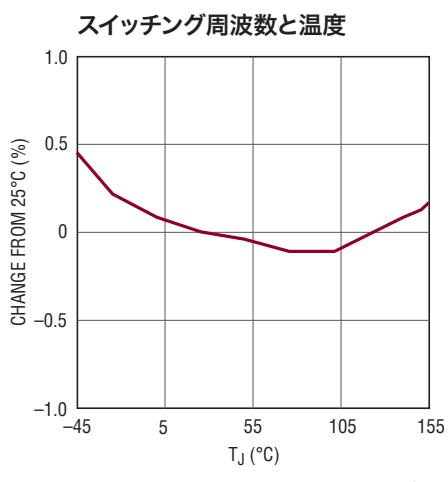

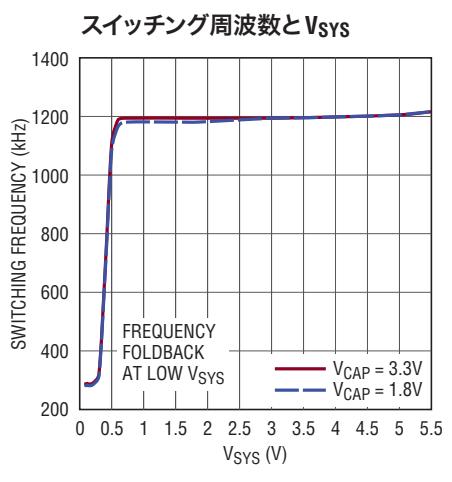

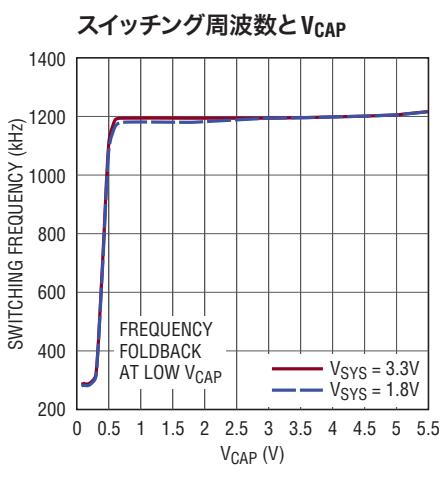

- 1.2MHz 固定スイッチング周波数

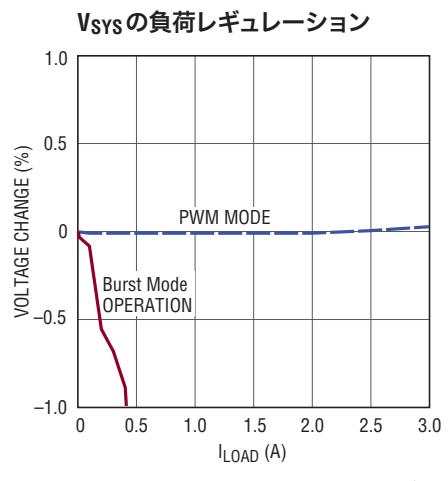

- Burst Mode<sup>®</sup>動作: 40μA の静止電流

- オープンコレクタ出力を備えたプログラム可能な多目的コンパレータ内蔵

- 動作の方向および充電の終了を示すオープンコレクタ出力

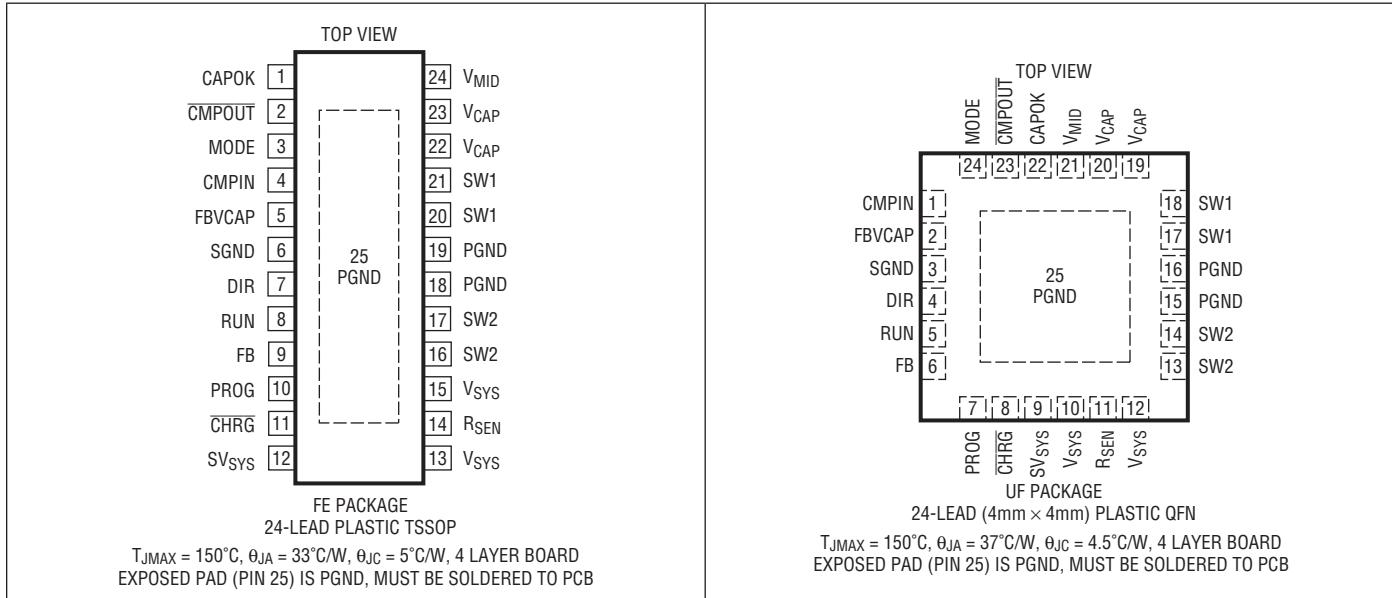

- 熱特性が改善されたTSSOP-24パッケージおよび4mm×4mm QFN-24パッケージ

## アプリケーション

- スーパーキャパシタのバックアップ・コンバータおよびチャージャ

- バッテリのバックアップ・コンバータおよびチャージャ

- サーバ、RAIDシステム

- バッテリ/コンデンサのバックアップ機能を内蔵したRFシステム

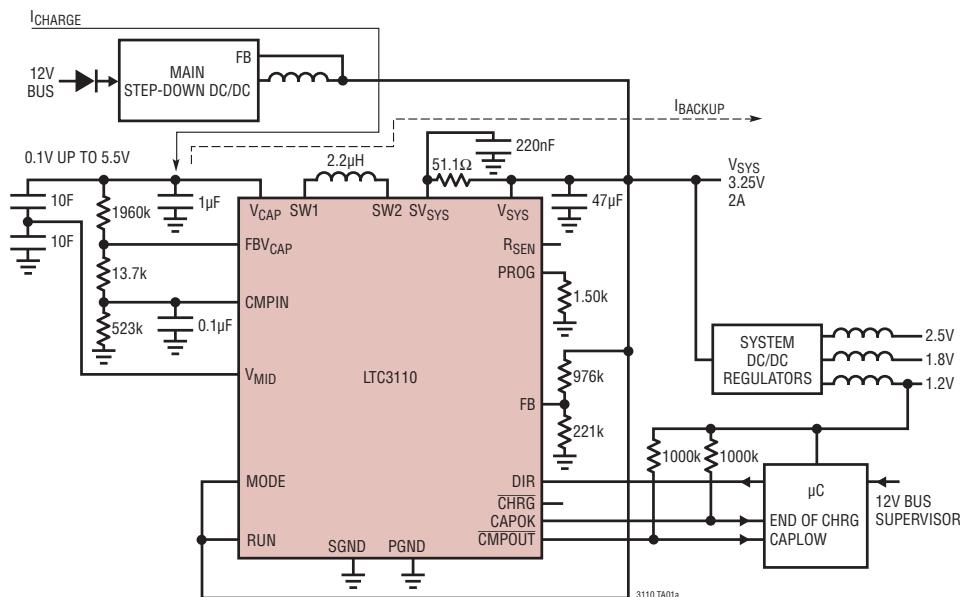

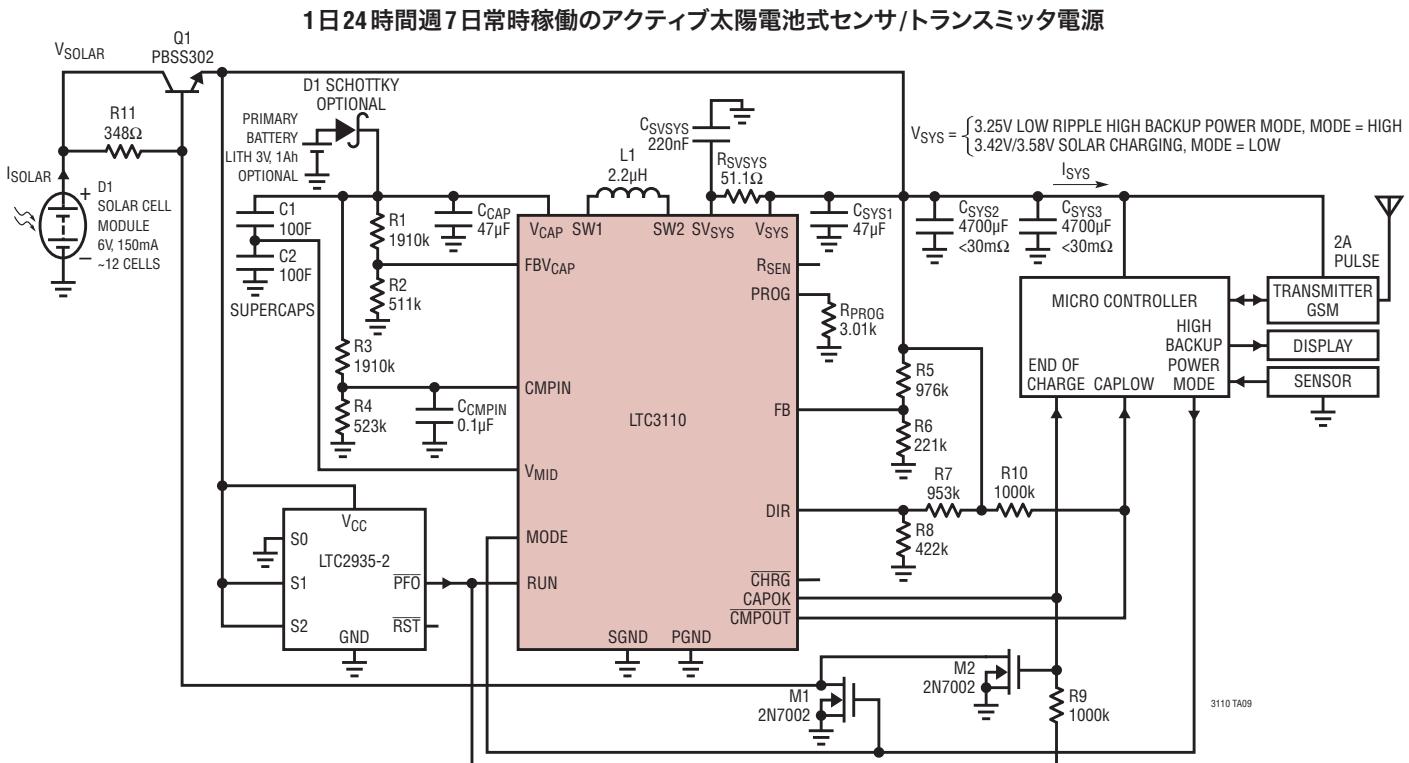

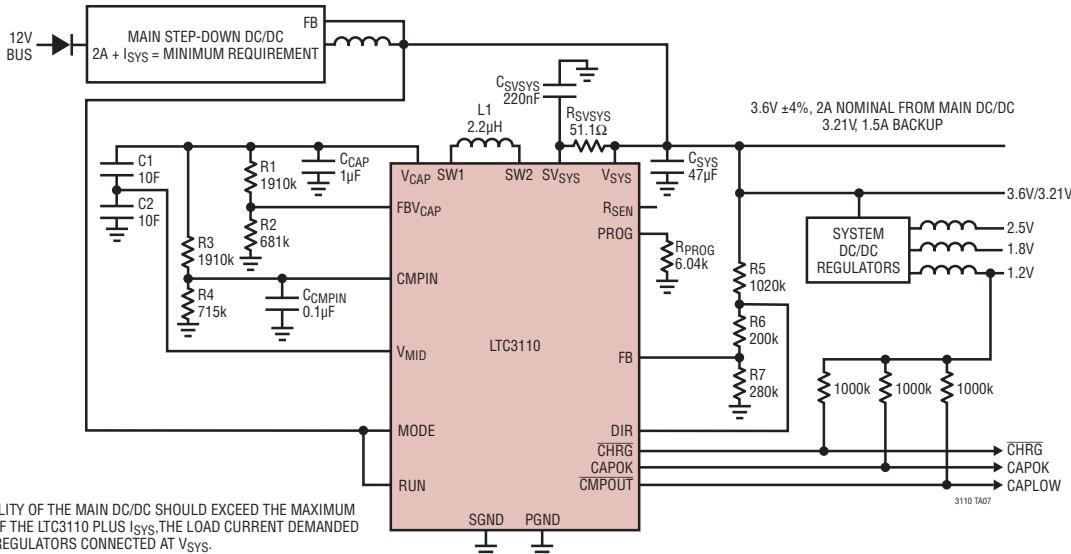

## 標準的応用例

## 絶対最大定格 (Note 1)

|                                                                                                                                                                                                                    |               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| V <sub>CAP</sub> 、V <sub>SYS</sub> 、S <sub>V</sub> <sub>SYS</sub> 、V <sub>MODE</sub> 、V <sub>CMPIN</sub> 、<br>V <sub>DIR</sub> 、V <sub>RUN</sub> 、V <sub>CAPOK</sub> 、V <sub>CMPOUT</sub> 、V <sub>CHRG</sub> ..... | -0.3V ~ 6V    |

| R <sub>SEN</sub> のDC電流.....                                                                                                                                                                                        | 1.6A          |

| 動作接合部温度範囲<br>(Note 2, 3).....                                                                                                                                                                                      | -40°C ~ 150°C |

|                            |               |

|----------------------------|---------------|

| 保存温度範囲.....                | -65°C ~ 150°C |

| リードの半田付け温度(半田付け、10秒).....  |               |

| TSSOP.....                 | 300°C         |

| リフローのピーク・ボディ温度(最大30秒)..... |               |

| QFN.....                   | 260°C         |

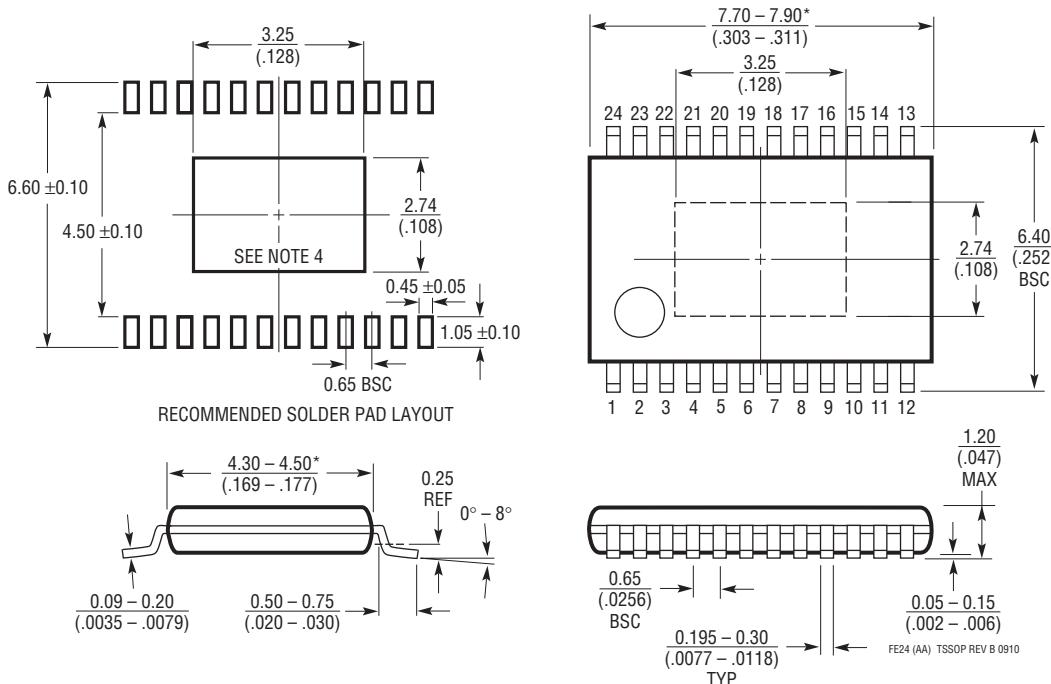

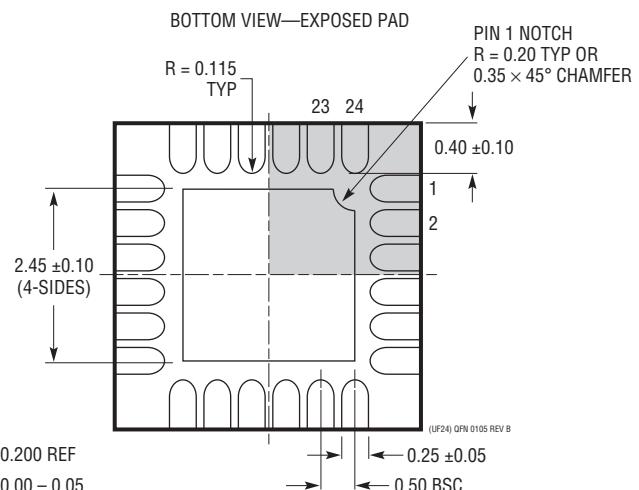

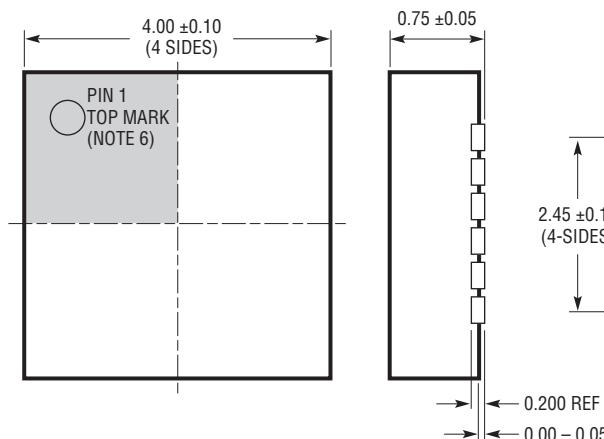

## ピン配置

## 発注情報

(<http://www.linear-tech.co.jp/product/LTC3110#orderinfo>)

| 無鉛仕上げ          | テープ・アンド・リール      | 製品マーキング*  | パッケージ                         | 温度範囲           |

|----------------|------------------|-----------|-------------------------------|----------------|

| LTC3110EFE#PBF | LTC3110EFE#TRPBF | LTC3110FE | 24-Lead Plastic TSSOP         | -40°C to 125°C |

| LTC3110IFE#PBF | LTC3110IFE#TRPBF | LTC3110FE | 24-Lead Plastic TSSOP         | -40°C to 125°C |

| LTC3110HFE#PBF | LTC3110HFE#TRPBF | LTC3110FE | 24-Lead Plastic TSSOP         | -40°C to 150°C |

| LTC3110EUF#PBF | LTC3110EUF#TRPBF | 3110      | 24-Lead (4mm×4mm) Plastic QFN | -40°C to 125°C |

| LTC3110IUF#PBF | LTC3110IUF#TRPBF | 3110      | 24-Lead (4mm×4mm) Plastic QFN | -40°C to 125°C |

| LTC3110HUF#PBF | LTC3110HUF#TRPBF | 3110      | 24-Lead (4mm×4mm) Plastic QFN | -40°C to 150°C |

更に広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/>をご覧ください。

テープ・アンド・リールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/>をご覧ください。

一部のパッケージは、#TRMPBF接尾部を付けることにより、指定の販売経路を通じて500個入りのリールで供給可能です。

## 電気的特性

●は規定動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ の値(Note 2)。

注記がない限り、 $V_{\text{CAP}} = 3.3\text{V}$ 、 $V_{\text{SYS}} = 3.3\text{V}$ 、 $V_{\text{DIR}} = V_{\text{SGND}}$ 、 $V_{\text{MODE}} = V_{\text{RUN}} = V_{\text{SYS}} = SV_{\text{SYS}}$ 。

| PARAMETER                                                                                          | CONDITIONS                                                                                                                  | MIN     | TYP   | MAX   | UNITS            |               |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|------------------|---------------|

| $V_{\text{CAP}}$ No-Load Operating Range in Backup Operation                                       | $V_{\text{SYS}} \geq 1.8\text{V}$                                                                                           | 0.1     |       | 5.5   | V                |               |

| $V_{\text{CAP}}$ Start-Up                                                                          | $V_{\text{SYS}} < \text{Undervoltage Lockout Threshold}$                                                                    | ● 1.8   |       |       | V                |               |

| $V_{\text{SYS}}$ Operating Range in Charge Operation                                               | $V_{\text{DIR}} = V_{\text{SYS}}$                                                                                           | ● 1.8   |       | 5.25  | V                |               |

| Undervoltage Lockout Threshold                                                                     | $V_{\text{SYS}}$ Ramping Down, $V_{\text{CAP}} = 0\text{V}$                                                                 |         | 1.55  |       | V                |               |

|                                                                                                    | $V_{\text{SYS}}$ Ramping Up, $V_{\text{CAP}} = 0\text{V}$                                                                   | ●       |       | 1.71  | V                |               |

| FB Feedback Voltage                                                                                | $V_{\text{CAP}}$ Ramping Down, $V_{\text{SYS}} = 0\text{V}$ , $V_{\text{RUN}} = V_{\text{CAP}}$                             |         | 1.55  |       | V                |               |

|                                                                                                    | $V_{\text{CAP}}$ Ramping Up, $V_{\text{SYS}} = 0\text{V}$ , $V_{\text{RUN}} = V_{\text{CAP}}$                               | ●       |       | 1.71  | V                |               |

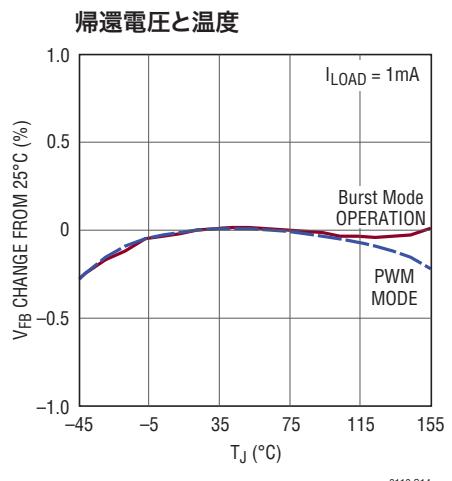

| FB Feedback Pin Input Current                                                                      | $0^\circ\text{C} < T_J < 85^\circ\text{C}$ (Note 5)                                                                         | 0.592   | 0.6   | 0.608 | V                |               |

|                                                                                                    | $-40^\circ\text{C} < T_J < 150^\circ\text{C}$                                                                               | ● 0.589 | 0.6   | 0.611 | V                |               |

| FB Feedback Pin Input Current                                                                      |                                                                                                                             |         | 0.1   | 50    | nA               |               |

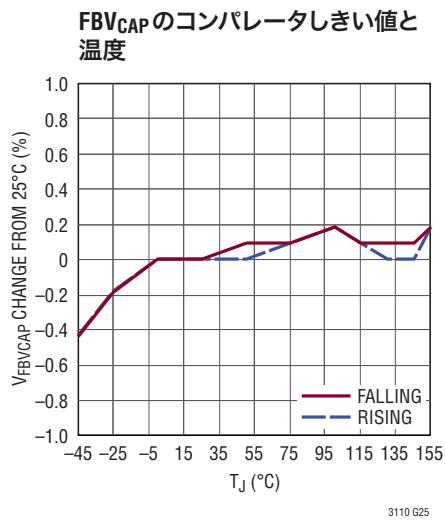

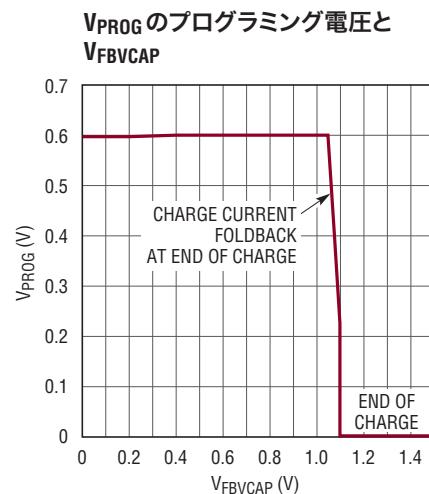

| FB $V_{\text{CAP}}$ End-of-Charge Threshold Rising                                                 | $\text{DIR} = V_{\text{SYS}}$                                                                                               | ●       | 1.095 | 1.117 | V                |               |

| FB $V_{\text{CAP}}$ End-of-Charge Threshold Falling                                                | $\text{DIR} = V_{\text{SYS}}$                                                                                               | ●       | 1.040 | 1.061 | V                |               |

| FB $V_{\text{CAP}}$ Input Current                                                                  | $V_{\text{FBVCAP}} = 1.1\text{V}$                                                                                           |         | 0.1   | 50    | nA               |               |

| FB $V_{\text{CAP}}$ Overcharge Threshold Rising                                                    |                                                                                                                             |         | 1.125 | 1.150 | 1.175            | V             |

| FB $V_{\text{CAP}}$ Overcharge Hysteresis                                                          |                                                                                                                             |         |       | 35    | mV               |               |

| Quiescent Current, Burst Mode Operation ( $I_{\text{VCAP}} + I_{\text{VSYS}} + I_{\text{SVSYS}}$ ) | $V_{\text{MODE}} = 0\text{V}$                                                                                               |         |       | 40    | $\mu\text{A}$    |               |

| Quiescent Current, End of Charge ( $I_{\text{VCAP}} + I_{\text{VSYS}} + I_{\text{SVSYS}}$ )        | $V_{\text{DIR}} = V_{\text{SYS}}$                                                                                           |         |       | 40    | $\mu\text{A}$    |               |

| Quiescent Current, Shutdown ( $I_{\text{VCAP}}$ )                                                  | $V_{\text{RUN}} = 0\text{V}$ , $V_{\text{SYS}} = SV_{\text{SYS}} = 0\text{V}$                                               |         |       | 0.05  | 1                | $\mu\text{A}$ |

| Peak Current Limit in Backup Operation                                                             | (Note 4)                                                                                                                    | 5       | 6     | 7     | A                |               |

| DC Current Limit in Backup Operation                                                               | (Note 4)                                                                                                                    | ● 3.5   | 4.5   |       | A                |               |

| Peak Current Limit in Charge Operation                                                             | (Note 4)                                                                                                                    | 5       | 6     | 7     | A                |               |

| Reverse Current Limit in Backup Operation                                                          | (Note 4)                                                                                                                    | 1       | 1.2   | 2     | A                |               |

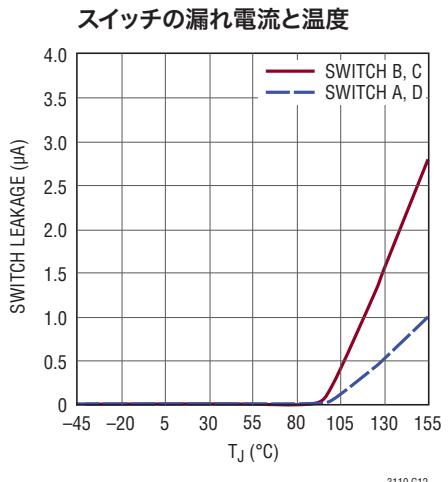

| Switch Leakage                                                                                     | Switch B, C: $V_{\text{CAP}} = V_{\text{SW1}} = 5.5\text{V}$ , $V_{\text{SYS}} = V_{\text{SW2}} = 5.25\text{V}$ ,           |         |       | 0.1   | $\mu\text{A}$    |               |

|                                                                                                    | Switch A, D: $V_{\text{CAP}} = 5.5\text{V}$ , $V_{\text{SYS}} = 5.25\text{V}$ $V_{\text{SW1}} = V_{\text{SW2}} = 0\text{V}$ |         |       | 0.1   | $\mu\text{A}$    |               |

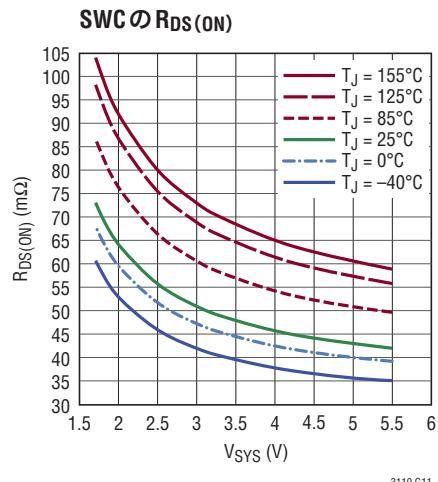

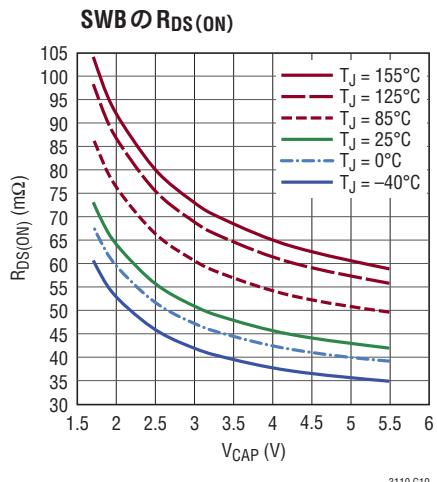

| Switch On-Resistance                                                                               | Switch A (Note 6)                                                                                                           |         |       | 64    | $\text{m}\Omega$ |               |

|                                                                                                    | Switch B (Note 6)                                                                                                           |         |       | 49    | $\text{m}\Omega$ |               |

|                                                                                                    | Switch C (Note 6)                                                                                                           |         |       | 49    | $\text{m}\Omega$ |               |

|                                                                                                    | Switch D Including Sense Resistor (Note 6)                                                                                  |         |       | 86    | $\text{m}\Omega$ |               |

| Oscillator Frequency                                                                               | $V_{\text{CAP}} = 0.2\text{V}$<br>$V_{\text{SYS}} = 0.2\text{V}$                                                            | ● 900   | 1200  | 1500  | kHz              |               |

|                                                                                                    |                                                                                                                             |         | 300   |       | kHz              |               |

|                                                                                                    |                                                                                                                             |         | 300   |       | kHz              |               |

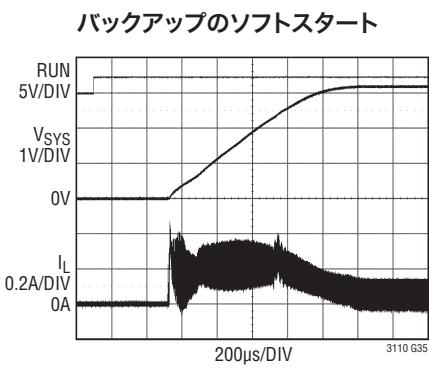

| Soft Start-Up Time in Backup Mode                                                                  | From $V_{\text{RUN}}$ rising to $V_{\text{FB}} = 90\%$                                                                      | 0.8     | 1.3   | 1.8   | ms               |               |

| Maximum Duty Cycle in Boost Mode                                                                   |                                                                                                                             | ● 91    | 93    | 96    | %                |               |

|                                                                                                    | $V_{\text{CAP}} = 0.2\text{V}$                                                                                              |         | 98    |       | %                |               |

| Minimum Duty Cycle in Buck Mode                                                                    |                                                                                                                             | ●       |       | 0     | %                |               |

| MODE Input Logic Threshold                                                                         | Enable Burst Mode Operation                                                                                                 |         |       | 0.3   | V                |               |

|                                                                                                    | Enable PWM Mode Operation                                                                                                   | 1       |       |       | V                |               |

| MODE Input Pull-Down Resistor                                                                      |                                                                                                                             |         |       | 6     | $\text{M}\Omega$ |               |

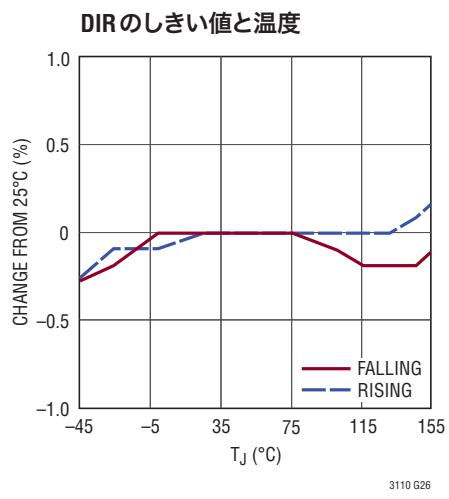

| DIR Threshold Rising                                                                               |                                                                                                                             | ● 1.073 | 1.095 | 1.117 | V                |               |

| DIR Threshold Falling                                                                              |                                                                                                                             | ● 1.024 | 1.045 | 1.066 | V                |               |

| DIR Hysteresis                                                                                     |                                                                                                                             | ● 30    | 50    | 70    | mV               |               |

| DIR Input Current                                                                                  | $V_{\text{DIR}} = 1.1\text{V}$                                                                                              |         | 0.1   | 50    | nA               |               |

## 電気的特性

●は規定動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ の値(Note 2)。

注記がない限り、 $V_{\text{CAP}} = 3.3\text{V}$ 、 $V_{\text{SYS}} = 3.3\text{V}$ 、 $V_{\text{DIR}} = V_{\text{SGND}}$ 、 $V_{\text{MODE}} = V_{\text{RUN}} = V_{\text{SYS}} = V_{\text{VPROG}}$ 。

| PARAMETER                                          | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MIN                                                                  | TYP                                                                  | MAX                                                                    | UNITS                                                    |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------|

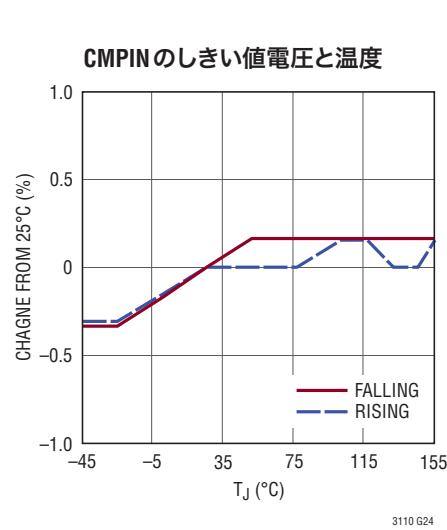

| CMPIN Threshold Rising                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.638                                                                | 0.65                                                                 | 0.662                                                                  | V                                                        |

| CMPIN Threshold Falling                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ● 0.575                                                              | 0.59                                                                 | 0.605                                                                  | V                                                        |

| CMPIN Input Current                                | $V_{\text{CMPIN}} = 5.5\text{V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                      | 0.1                                                                  | 50                                                                     | nA                                                       |

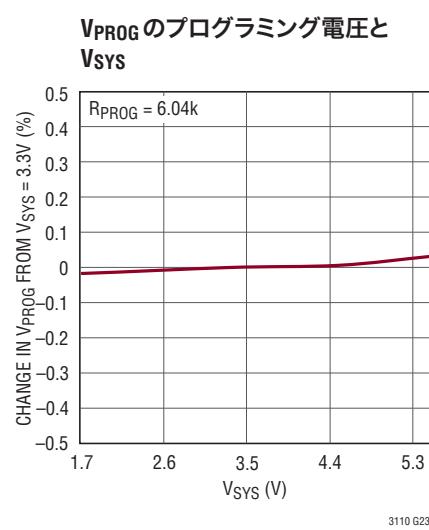

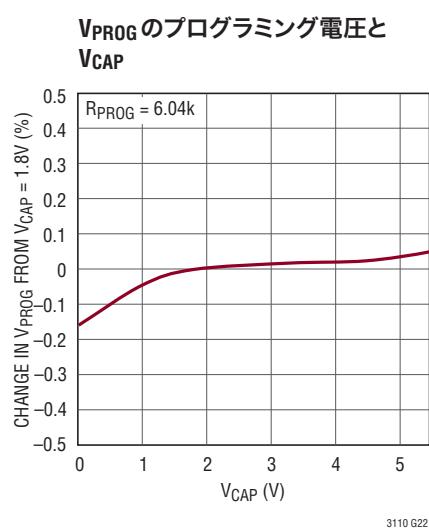

| PROG Voltage                                       | $V_{\text{FBVCAP}} = 1\text{V}$ , $\text{DIR} = V_{\text{SYS}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      | 0.6                                                                  |                                                                        | V                                                        |

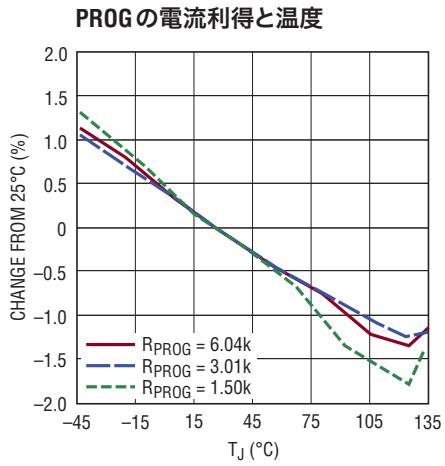

| PROG Current Gain                                  | $\text{DIR} = V_{\text{SYS}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      | 200                                                                  |                                                                        | $\mu\text{A}/\text{A}$                                   |

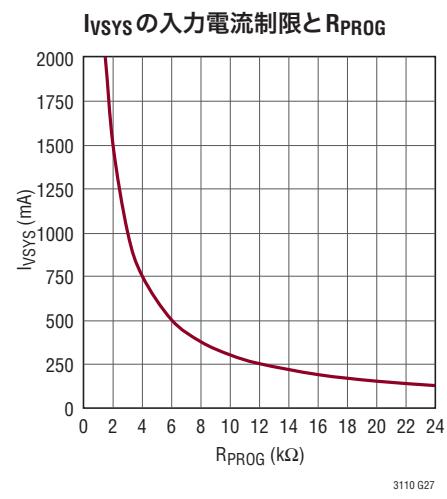

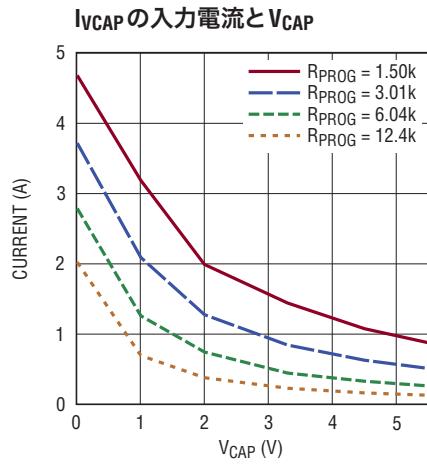

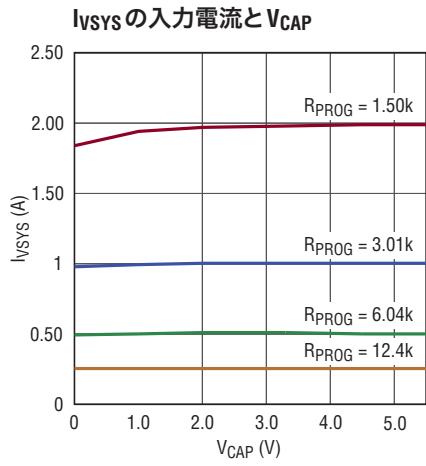

| $I_{\text{VSYs}}$ Input Current Limit              | $R_{\text{PROG}} = 24.3\text{k}$ (Notes 7, 8), $\text{DIR} = V_{\text{SYS}}$<br>$R_{\text{PROG}} = 24.3\text{k}$ (Notes 7, 8, 9), $\text{DIR} = V_{\text{SYS}}$ ,<br>$T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$<br>$R_{\text{PROG}} = 12.1\text{k}$ (Notes 7, 8), $\text{DIR} = V_{\text{SYS}}$<br>$R_{\text{PROG}} = 12.1\text{k}$ (Notes 7, 8, 9), $\text{DIR} = V_{\text{SYS}}$ ,<br>$T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$<br>$R_{\text{PROG}} = 6.04\text{k}$ (Notes 7, 8), $\text{DIR} = V_{\text{SYS}}$<br>$R_{\text{PROG}} = 6.04\text{k}$ (Notes 7, 8, 9), $\text{DIR} = V_{\text{SYS}}$ ,<br>$T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$<br>$R_{\text{PROG}} = 3.01\text{k}$ (Notes 7, 8), $\text{DIR} = V_{\text{SYS}}$<br>$R_{\text{PROG}} = 3.01\text{k}$ (Notes 7, 8, 9), $\text{DIR} = V_{\text{SYS}}$ ,<br>$T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$<br>$R_{\text{PROG}} = 1.5\text{k}$ (Notes 7, 8), $\text{DIR} = V_{\text{SYS}}$<br>$R_{\text{PROG}} = 1.5\text{k}$ (Notes 7, 8, 9), $\text{DIR} = V_{\text{SYS}}$ ,<br>$T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$ | 119<br>115<br>241<br>234<br>487<br>473<br>977<br>948<br>1960<br>1900 | 123<br>123<br>248<br>248<br>497<br>497<br>997<br>997<br>2000<br>2000 | 128<br>135<br>255<br>270<br>507<br>525<br>1017<br>1046<br>2040<br>2100 | mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA |

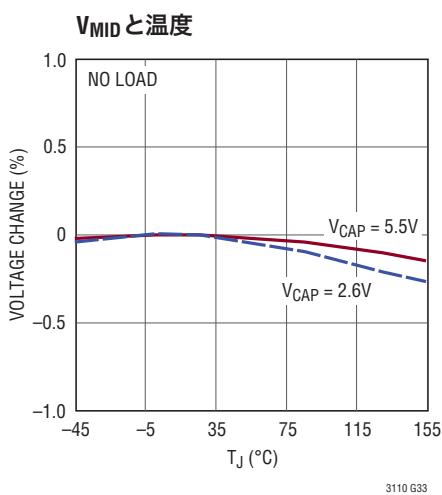

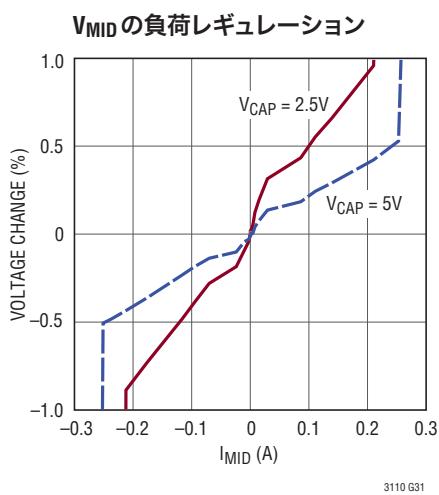

| $V_{\text{MID}}$ to $V_{\text{CAP}}$ Voltage Ratio | $V_{\text{MID}} = \text{Open Load}$ , $V_{\text{CAP}} = 5\text{V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.492                                                                | 0.5                                                                  | 0.508                                                                  |                                                          |

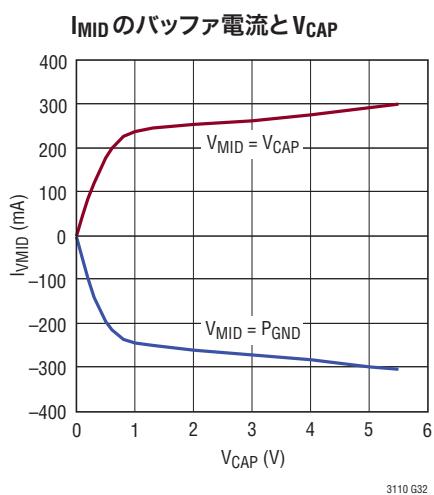

| $V_{\text{MID}}$ Balancing Current                 | $V_{\text{CAP}} = 5\text{V}$ , $V_{\text{MID}} = 5\text{V}$<br>$V_{\text{CAP}} = 5\text{V}$ , $V_{\text{MID}} = 0\text{V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ● 150<br>● 300<br>● -300<br>● -150                                   |                                                                      |                                                                        | mA<br>mA                                                 |

| $V_{\text{MID}}$ Current in Shutdown               | $V_{\text{RUN}} = 0\text{V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      | 0.1                                                                  | 1                                                                      | $\mu\text{A}$                                            |

| $V_{\text{MID}}$ Suspend Charging Threshold        | $V_{\text{MID}} \text{ Rising}$ , $V_{\text{CAP}} = 5\text{V}$<br>$V_{\text{MID}} \text{ Falling}$ , $V_{\text{CAP}} = 5\text{V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      | 2.6<br>2.38                                                          | 2.62<br>2.4                                                            | V<br>V                                                   |

| CHRG, CAPOK, CMPOUT Open-Drain Output Voltage      | $I = 10\text{mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ●                                                                    | 0.1                                                                  | 0.3                                                                    | V                                                        |

| RUN Input Logic Threshold                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ●                                                                    | 0.3                                                                  | 1                                                                      | V                                                        |

| RUN Pull-Down Resistor                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      | 6                                                                    |                                                                        | $\text{M}\Omega$                                         |

Note 1: 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与えるおそれがある。

Note 2: LTC3110は $T_J$ が $T_A$ にほぼ等しいパルス負荷条件でテストされる。LTC3110Eは、 $0^\circ\text{C}$ ～ $85^\circ\text{C}$ の接合部温度で性能仕様に適合することが保証されている。 $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の動作接合部温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTC3110Iは $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の動作接合部温度範囲で仕様に適合することが保証されている。LTC3110Hは $-40^\circ\text{C}$ ～ $150^\circ\text{C}$ の全動作接合部温度範囲で仕様に適合することが保証されている。温度が高いと動作寿命に悪影響を及ぼす。接合部温度が $125^\circ\text{C}$ を超えると、動作寿命はディレーティングされる。

これらの仕様を満たす最大周囲温度は、基板レイアウト、パッケージの定格熱インピーダンスおよび他の環境要因と関連した特定の動作条件によって決まるに注意。接合部温度( $T_J(\text{C})$ )は周囲温度( $T_A(\text{C})$ )および電力損失( $P_D(\text{W})$ )から次式に従って計算される。

$$T_J = T_A + (P_D \cdot \theta_{JA})$$

ここで、 $\theta_{JA}(\text{C/W})$ はパッケージの熱インピーダンス。

Note 3: このデバイスは短時間の過負荷状態の間デバイスを保護するための過熱保護機能を備えている。この保護が動作しているときは、最高定格接合部温度を超えられる。規定された絶対最大動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なうか、またはデバイスに永続的損傷を与える恐れがある。

Note 4: 電流の測定は、LTC3110がスイッチング動作を行っていないときに行われる。動作時に測定された電流制限値は、コンパレータの伝搬遅延のためにいくらか大き目の値となる。

Note 5: 設計、特性評価および統計的プロセス制御との相関によって保証されている。

Note 6: 設計、相関、およびベンチ測定により保証されている。

Note 7: 電流測定は出力がスイッチングしていないときに行われる。

Note 8: この仕様の精度は、パラメータを設定するために使用される抵抗の精度に直接関係している。

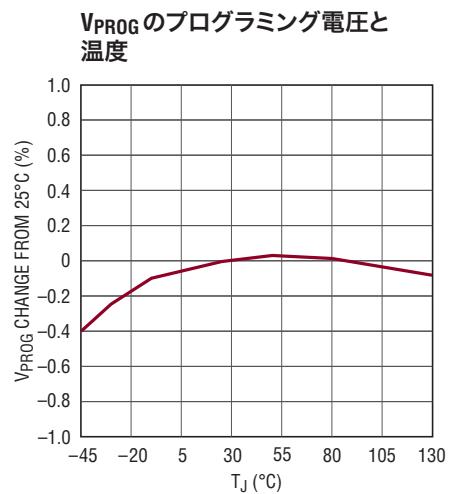

Note 9: 入力電流制限値は接合部温度が $125^\circ\text{C}$ を超えると減少する。「動作」セクションの「充電電流の熱フォールドバック」、および「標準的性能特性」セクションの「 $V_{\text{PROG}}$ のプログラミング電圧と温度」のグラフを参照。

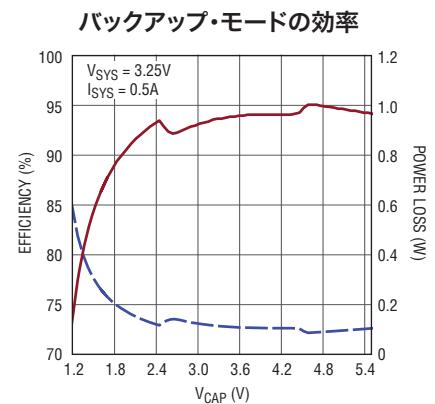

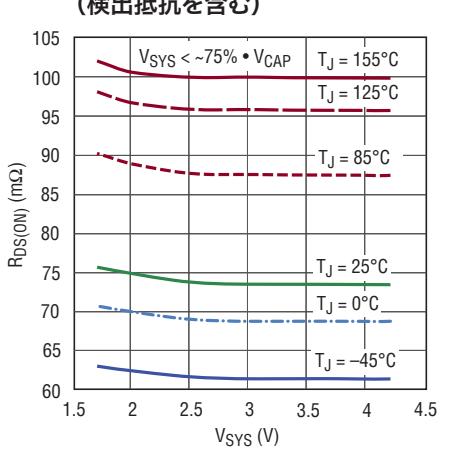

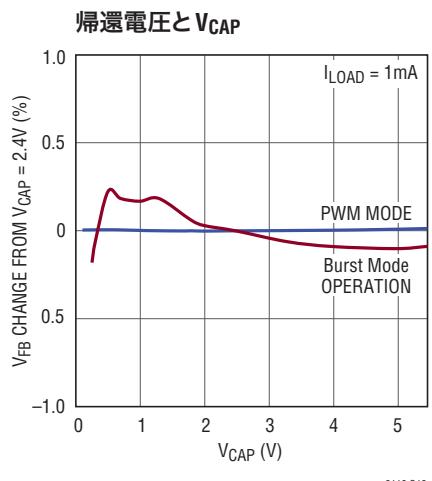

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$

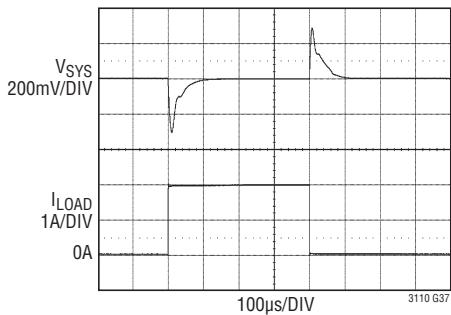

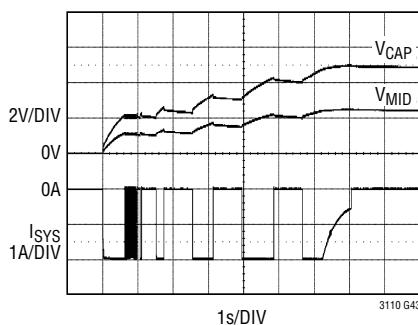

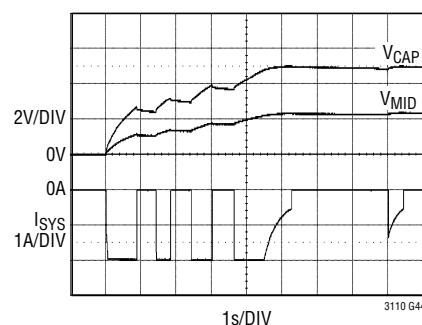

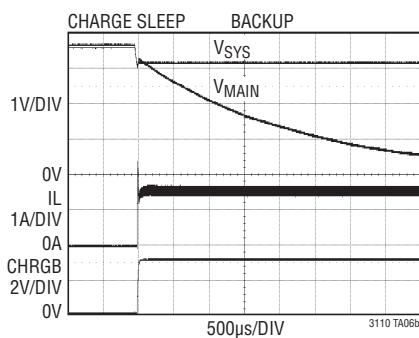

## 負荷ステップ(0Aから2A)

自律的アプリケーションでの

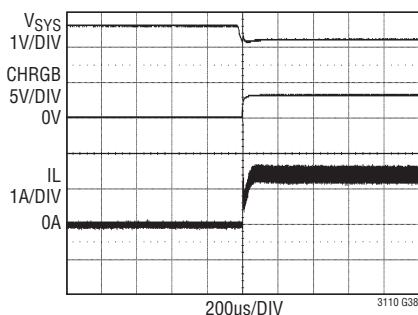

充電スリープ・モードからバックアップ

モードへのトランジエント応答

自律的アプリケーションでの

バックアップ・モードから

充電モードへのトランジエント応答

## Burst Mode動作

## PWM モードの動作

$V_{CAP}$  の過電圧障害状態での

PWM モード動作

充電バランサの動作

$C_1 > C_2$ 充電バランサの動作

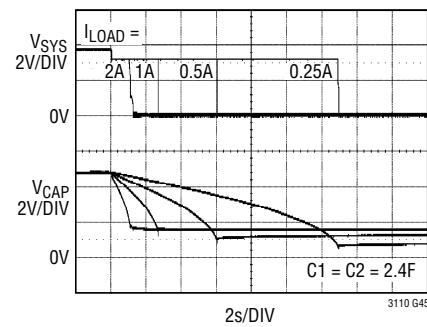

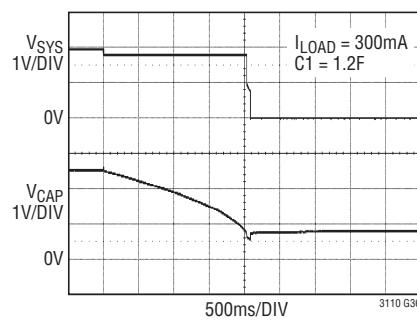

$C_1 < C_2$ コンデンサ1個でのバックアップ

電圧

## ピン機能 (FE/UFD)

**CAPOK(ピン1/ピン22)**:  $V_{CAP}$ 電圧のOKインジケータ出力。このオープンドレイン出力は、 $FBV_{CAP}$ の電圧が $FBV_{CAP}$ の立ち下がりしきい値より低いと“L”になります。この出力は、 $FBV_{CAP}$ の電圧が立ち上がりしきい値より高くなると解放されます。

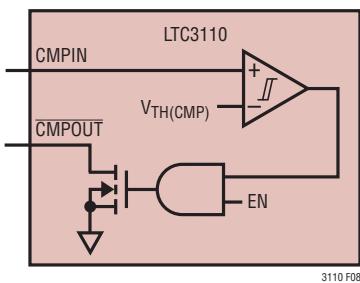

**CMPOUT(ピン2/ピン23)**: 汎用コンパレータの出力。このオープンドレイン出力は、 $CMPIN$ ピンの電圧がコンパレータの立ち上がりしきい値より高いときに“L”になります。この出力は、 $CMPIN$ ピンの電圧が立ち下がりしきい値より低くなると解放されます。

**MODE(ピン3/ピン24)**: Burst/PWMモード選択入力。MODEをロジック1の状態にすると、固定周波数、低ノイズのPWM動作が設定されます。MODEを“L”にすると、Burst Mode動作が設定されます。チャージャ・モードで動作しているときは、MODEピンに効力はありません。

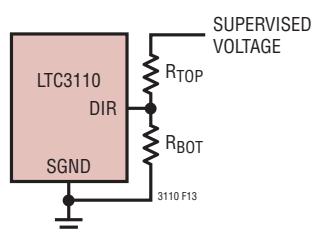

**CMPIN(ピン4/ピン1)**: ヒステリシスのある汎用コンパレータの正の入力。 $CMPIN$ の電圧は内部リファレンス電圧と比較されます。このピンは、抵抗分割器を外付けすることにより、デジタル式に駆動することや、電圧スーパーバイザとして構成することができます。抵抗分割器で駆動する場合や、インピーダンスが $200\Omega$ より高い電源で駆動する場合は、 $CMPIN$ とGNDの間に $0.1\mu F$ のコンデンサを接続して性能を最適にします。 $CMPIN$ の立ち上がりしきい値は $0.65V$ で、立ち下がりしきい値は $0.59V$ です。

**FBV<sub>CAP</sub>(ピン5/ピン2)**:  $V_{CAP}$ の充電終了電圧のプログラミング帰還抵抗分割器入力(ヒステリシスあり)。充電終了しきい値は $1.1V \sim 5.5V$ の範囲で調整することができます。 $FBV_{CAP}$ の立ち上がりしきい値は $1.095V$ で、立ち下がりしきい値は $1.061V$ です。

**SGND(ピン6/ピン3)**: 信号グランドの接続ピン。グランド・ブレーンを強く推奨します。グランドに終端している敏感なアナログ部品はケルビン接続でSGNDピンに接続し、PGNDの大電流経路から分離します。

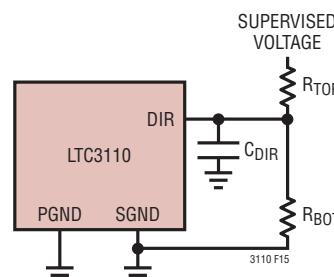

**DIR(ピン7/ピン4)**: ヒステリシスのある充電/バックアップ・モード・セレクタ入力。DIRの電圧が立ち下がりしきい値より高くなると、LTC3110のチャージャ・モードが有効になります。電圧が立ち下がりしきい値より低くなると、バックアップ・モードが有効になります。このピンはデジタル式に(つまり、マイクロコンピュータから)駆動することができます。このピンは、抵抗分割器を外付けすることにより、システム電圧をモニタする電圧スーパーバイザ入力として構成することができます。DIRの立ち上がりしきい値は $1.095V$ で、立ち下がりしきい値は $1.045V$ です。

**RUN(ピン8/ピン5)**: ロジックで制御されるシャットダウン入力。

$RUN \geq 1.0V$ : 通常動作

$RUN \leq 0.3V$ : シャットダウン

**FB(ピン9/ピン6)**:  $V_{SYS}$ のバックアップ電圧帰還ピン。抵抗分割器のタップをここに接続します。 $V_{SYS}$ の電圧は $1.8V \sim 5.25V$ の範囲で調整することができます。帰還リファレンス電圧は $0.6V$ です。

**PROG(ピン10/ピン7)**: チャージャ入力電流( $I_{V_{SYS}}$ )のプログラミング抵抗。充電モードで動作している場合は、PROGとSGNDの間に抵抗を接続することにより、 $V_{SYS}$ を流れる平均電流を設定することができます。

$$R_{PROG} = \frac{3k\Omega \cdot A}{I_{V_{SYS}}} \text{ for } 1.5k\Omega < R_{PROG} < 24.3k\Omega$$

$FBV_{CAP}$ を $1V$ 未満に保持するか接地することによって充電電流のフォールドバックを防ぐ場合は、 $R_{PROG}$ を $48.7k$ まで大きくしてもかまいません。

## ピン機能 (FE/UFD)

**CHRG(ピン11/ピン8)**: 充電/バックアップ・モード・インジケーターの出力。レギュレータが充電モードのとき、オープンドレイン出力は“L”になります。レギュレータがバックアップ・モードのとき、オープンドレイン出力は解放されます。

**V<sub>SYS</sub>(ピン12/ピン9)**: 降圧/昇圧コントローラ回路の信号電源電圧入力。このピンはV<sub>SYS</sub>に短絡するか、RCフィルタを介してV<sub>SYS</sub>から電源を供給する必要があります。詳細については、「アプリケーション情報」のセクションを参照してください。

**V<sub>SYS</sub>(ピン13、15/ピン10、12)**: システム・バックアップ出力電圧および充電電流入力電圧に対応する双方向電源ピン。V<sub>SYS</sub>とPGNDの間にバイパス・コンデンサを接続する必要があります。コンデンサ選択の詳細については、「標準的応用例」の回路図および「アプリケーション情報」セクションを参照してください。

**R<sub>SEN</sub>(ピン14/ピン11)**: 内部検出抵抗とスイッチDの接続部にある電流検出抵抗タップ。R<sub>SEN</sub>ピンは低インピーダンス経路を介して内部でV<sub>SYS</sub>ピンに短絡されています。R<sub>SEN</sub>を流れるDC電流は1.6Aに制限する必要があります。

**SW2(ピン16、17/ピン13、14)**: 昇降圧レギュレータの内部スイッチCおよびDに接続されているスイッチ・ピン。昇降圧インダクタの片側はSW2に接続します。インダクタとSW2の間に短い幅広のPCBトレースを配線して、電圧トランジエントおよびノイズを最小限に抑えます。

**PGND(ピン18、19、露出パッド・ピン25/ピン15、16、露出パッド・ピン25)**: 電源グランドの接続ピン。全ての大電流グランド経路はPGNDに終端します。露出パッドは定格熱性能を得るためPCBグランドに半田付けする必要があります。

**SW1(ピン20、21/ピン17、18)**: 昇降圧レギュレータの内部スイッチAおよびBに接続されているスイッチ・ピン。昇降圧インダクタの片側はSW1に接続します。インダクタとSW1の間に短い幅広のPCBトレースを配線して、電圧トランジエントおよびノイズを最小限に抑えます。

**V<sub>CAP</sub>(ピン22、23/ピン19、20)**: スーパーキャパシタのバックアップ・コンデンサまたはバックアップ・バッテリに接続するための双方向電源ピン。充電モードの場合はV<sub>CAP</sub>ピンから電流が流れ出し、V<sub>CAP</sub>とPGNDの間に接続されている蓄電素子を充電します。バックアップ・モードの場合はV<sub>CAP</sub>ピンに電流が流れ込み、蓄積エネルギーを使用してV<sub>SYS</sub>の負荷をバックアップします。

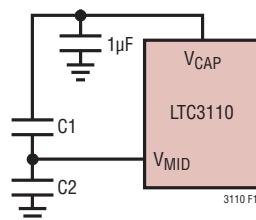

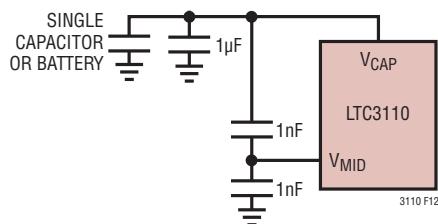

**V<sub>MID</sub>(ピン24/ピン21)**: アクティブな電圧バランス調整電源出力。このピンは2つの直列スーパーキャパシタの接続部に接続します。この出力を使用しない場合は、V<sub>MID</sub>ピンとPGNDの間に1nFの補償コンデンサを接続する必要があります。

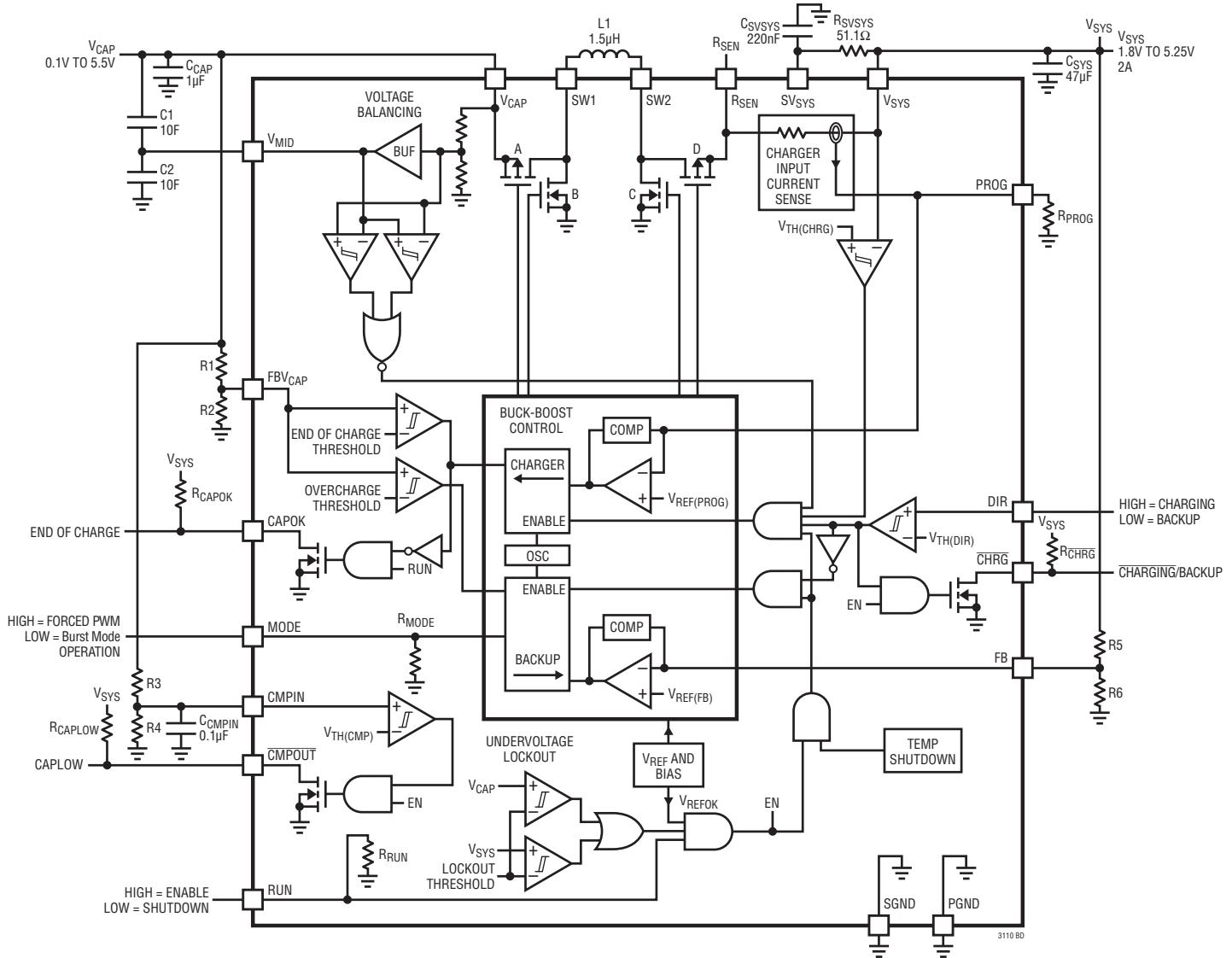

## ブロック図

## 動作

### はじめに

LTC3110は、モノリシックの昇降圧DC/DCレギュレータ/チャージャ複合デバイスで、ピンで選択可能な動作モードを備えており、1つのLTC3110デバイスを充電( $V_{DIR} = "H"$ )だけでなくシステム・バックアップ( $V_{DIR} = "L"$ )の用途にも利用することができます。充電時には、システム電源から流れる平均電流の制限値を外付け抵抗により正確に設定することができます。アクティブな電圧バランス調整バッファを $V_{MID}$ ピンに内蔵しているので、スーパーキャパシタ・スタックの充電中は、コンデンサの容量不整合に起因するコンデンサの過電圧状態を防止します。

昇降圧レギュレータは独自のスイッチング・アルゴリズムを使用しているので、インダクタ電流が途切れることも、バックアップ電圧 $V_{SYS}$ に大きな電圧リップルが発生することもなく、システム電圧 $V_{SYS}$ を蓄電素子の電圧 $V_{CAP}$ より高い、低い、または等しい電圧に安定化することができます。

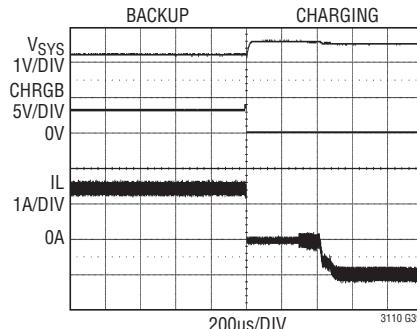

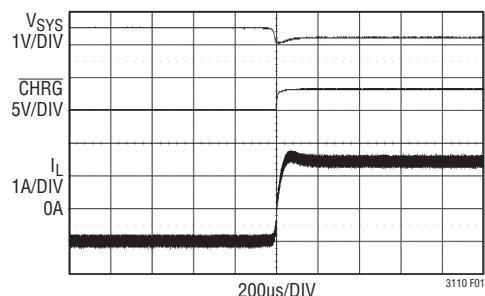

$DIR$ ピンの方向制御回路により、LTC3110はインダクタ電流を直ちに逆転して、充電動作モードとバックアップ動作モードを切り替え、バックアップ電圧をシステムに供給することにより、電源障害状態に対して素早く反応します(図1参照)。

図1. 充電動作からバックアップ動作への遷移

LTC3110は、システム電圧 $V_{SYS}$ または蓄電素子 $V_{CAP}$ から流れる静止電流に敏感なアプリケーションでは、シャットダウン時やスタンバイ時に静止電流を低減するよう最適化されています。充電動作時のスタンバイ電流はわずか40 $\mu$ Aです。バックアップ/Burst Mode動作時の無負荷時スタンバイ電流はわずか40 $\mu$ Aです。シャットダウン時には電源電流が1 $\mu$ A未満まで減少します。

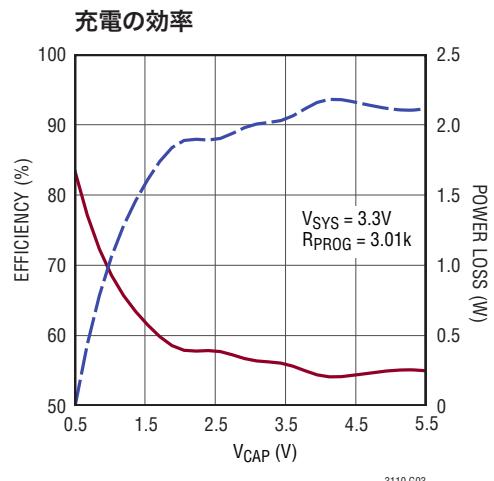

### 充電

システム電圧 $V_{SYS}$ から電力を供給する場合、昇降圧レギュレータは、通常は充電モード( $V_{DIR} = "H"$ )で動作するよう設定されます。つまり、 $V_{SYS}$ に接続される電圧源はLTC3110への電源入力であり、コンバータは $V_{CAP}$ ピンとPGNDピンの間に接続されているバックアップ蓄電素子を充電します。充電モードで動作する場合は、LTC3110の平均電流制限回路が動作します。PROGピンとSGNDピンの間に接続する抵抗により、 $V_{SYS}$ から流れる最大平均電流を正確に設定して電流の要求量を制限することができます。

図2. 充電電流のフォールドバックと充電終了

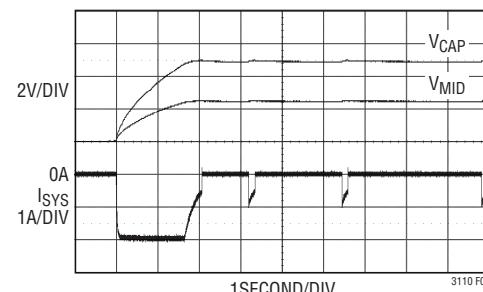

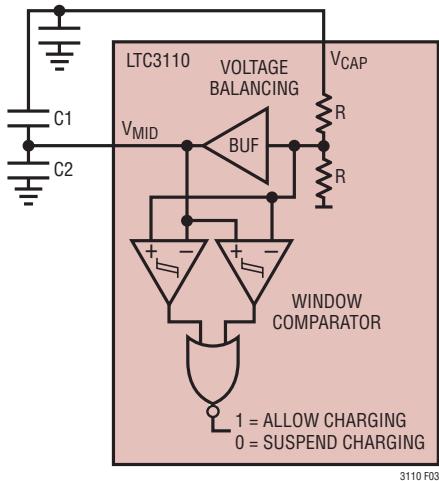

### アクティブ充電バランス

充電中、内蔵の線形充電バランス調整バッファは、コンデンサ・スタックの中間電圧 $V_{MID}$ を $V_{CAP}$ の半分の電圧に安定化するので、上側と下側のコンデンサの出力電圧の不一致をなくして等しくします。図3を参照してください。コンデンサ電圧の不一致が充電バランスの電流供給能力を超えている場合は、 $V_{MID}$ が $V_{CAP}$ の半分の電圧に戻るまで充電が一時停止します(「標準的性能特性」セクションの充電波形を参照)。充電の一時停止機能が作動するのは、 $V_{CAP} > 2.2V = V_{TH(CHRG)}$ +ヒステリシスが成立立つ場合だけです。 $V_{CAP} < 2V$ では、チャージャの動作が常に途切れません。

## 動作

図3. アクティブ充電バランサ

## 充電終了

$V_{CAP}$ ピンの最終充電電圧は、 $FBV_{CAP}$ に抵抗分割器を接続して設定します。「アプリケーション情報」セクションの図10を参照してください。

$FBV_{CAP}$ がその充電終了しきい値の95%（標準）を超えると、PROGのリファレンス電圧とそれによる充電電流レベルが折り返し始めます（図2参照）。充電終了前に、充電電流は最終的に設定値の30%（標準）のレベルまで折り返します（「標準的性能特性」セクションの充電波形を参照）。設定電圧レベルに達すると、コントローラは充電を終了してオフに切り替え、低静止電流状態になります。その間に $V_{MID}$ ピンの充電バランサがディスエーブルされて $CAPOK$ ピンが解放されます。低静止電流状態は、 $V_{CAP}$ の電圧が減衰して $FBV_{CAP}$ の立ち下がりしきい値より低くなるまで維持されます。この後、コントローラと充電バランサは $CAPOK$ ピンを“L”にした状態で動作を再開し、再びレギュレーション電圧に達するまでその状態を継続します。外部電源の漏れ電流がコンデンサに流れ込んでコンデンサが過電圧状態になるのを、デバイスが防ぐことはできないので注意してください。

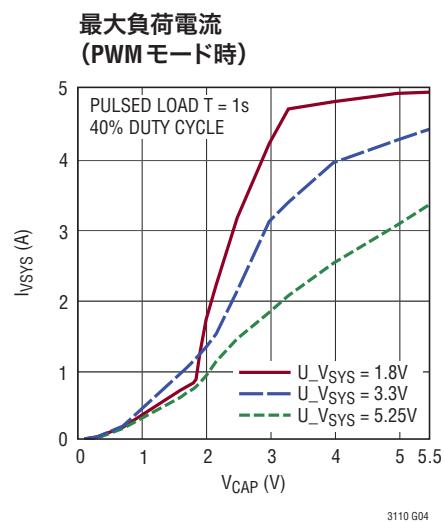

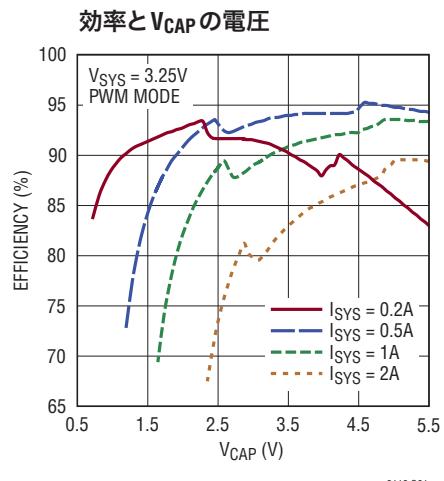

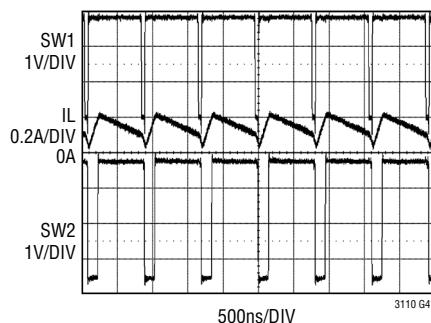

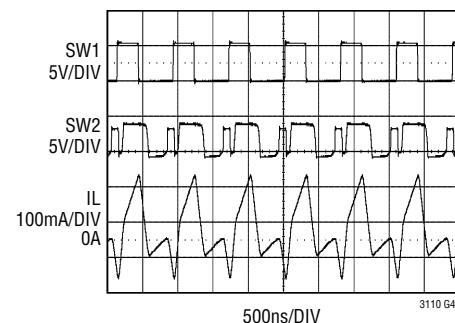

## 固定周波数 PWM モードでのバックアップ動作

$V_{DIR} = "L"$  のときにMODEピンを“H”に保持すると、LTC3110は、電圧モード制御ループを使用する固定周波数のパルス幅変調(PWM)モードで動作します。この動作モードでは、コンバータから供給することができる $V_{SYS}$ のバックアップ電流が最大になり、 $V_{SYS}$ の電圧リップルが減少し、固定周波数のスイッチング・スペクトラムが低ノイズになります。独自のスイッチング・アルゴリズムにより、すべての動作領域にわたって動作モード間をシームレスに移行し、平均インダクタ電流、インダクタ電流リップル、およびループの伝達関数の不連続性を除去します。これらの利点により、従来の4スイッチ昇降圧コンバータに比べて効率が向上し、ループの安定性が改善され、 $V_{SYS}$ の電圧リップルが小さくなります。

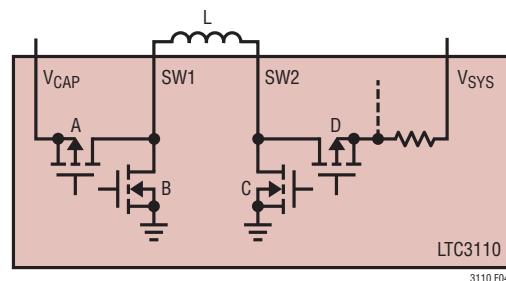

PチャネルMOSFETスイッチ2個とNチャネルMOSFETスイッチ2個、および対応するゲート・ドライバで構成されるLTC3110のパワー段の構成を図4に示します。エラーアンプの出力に応じて、内部のパルス幅変調器がスイッチの適正なデューティ・サイクルを生成し、 $V_{SYS}$ 電圧のレギュレーションを維持します。

$V_{CAP}$ の電圧が $V_{SYS}$ の電圧よりかなり高いと、昇降圧コンバータは降圧モードで動作します。スイッチDは引き続きオンしており、スイッチCはオフのままでです。スイッチAおよびBはパルス幅変調され、 $V_{SYS}$ のレギュレーション電圧をサポートするために必要なデューティ・サイクルを生成します。 $V_{CAP}$ の電圧が低下すると、スイッチAはスイッチング・サイクルの大部分でオンしたままになります。デューティ・サイクルが約90%に達すると、このスイッチ・ペアACはオンし始め、スイッチング周期のごく一部の時間オン状態になります。 $V_{SYS}$ の電圧が更に低下すると、スイッチ・ペアACはより長い時間オンのまになり、それに比例してBDの位相の時間が短くなります。この時点で、スイッチAは引き続きオンのままでですが、スイッチ・ペアCDは目的の $V_{SYS}$ 電圧を得るためにパルス幅変調されます。この時点では、コンバータは昇圧モードでだけ動作しています。

図4. 昇降圧用スイッチのトポロジ

## 動作

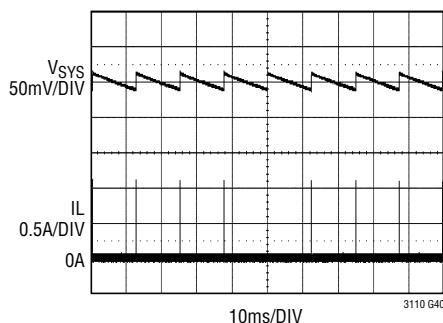

### Burst Mode動作でのバックアップ

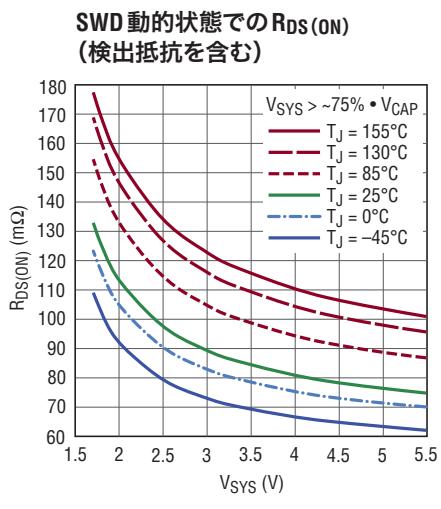

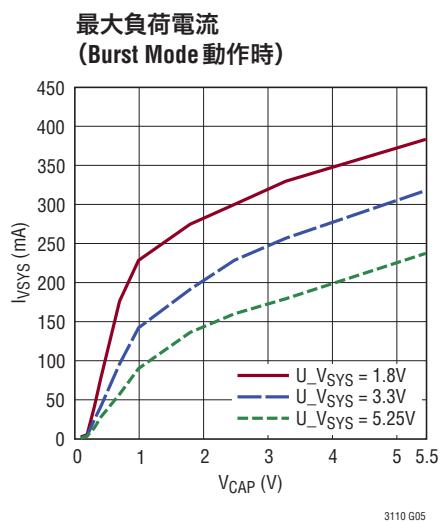

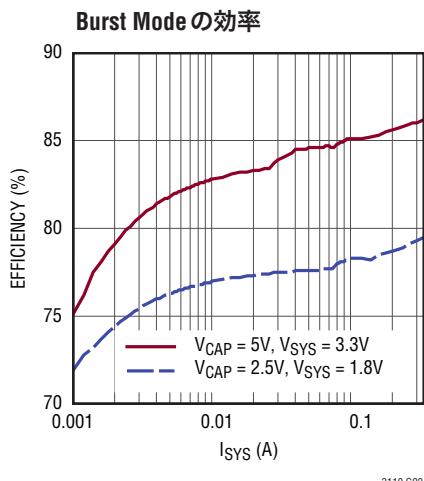

$V_{DIR} = "L"$ のときにMODEを“L”に保持すると、昇降圧コンバータは可変周波数スイッチング・アルゴリズムを使用してBurst Modeで動作します。このアルゴリズムは、無負荷時の入力静止電流を最小限に抑え、軽負荷時には、負荷をサポートするのに必要な最小限のレベルまでスイッチングの回数を低減することによって効率を改善します。Burst Mode動作時の $V_{SYS}$ の電流供給能力はPWMモード時よりもはるかに低く、スタンバイ時の軽負荷をサポートすることを目的にしています。Burst Modeの最大負荷電流を $V_{CAP}$ と $V_{SYS}$ の電圧の関数として示す曲線については、このデータシートの「標準的性能特性」のセクションを参照してください。Burst Mode動作時のコンバータの負荷がBurst Modeの最大電流供給能力を超えると、 $V_{SYS}$ はレギュレーション状態ではなくなります。スイッチAおよびCがオンすると、各Burst Modeサイクルが始まり、インダクタを流れる電流が直線的に増加します。インダクタ電流がBurst Modeのピーク電流制限値に達すると、スイッチAおよびCがオフしてスイッチBおよびDがオンし、インダクタに蓄積されたエネルギーが $V_{SYS}$ のコンデンサと負荷に放出されます。インダクタ電流がゼロに達すると、すべてのスイッチがオフしてサイクルが終了します。このようにして生成された電流パルスは必要に応じて繰り返し生成され、 $V_{SYS}$ の電圧のレギュレーションが維持されます。

### $V_{CAP}$ のピーク電流制限およびDC電流制限 (バックアップ・モード)

LTC3110は、ピーク・インダクタ電流を制限して、出力短絡状態や過負荷状態のときにスイッチ電流をデバイスの能力以内に抑えるように設計された、2つの電流制限回路を備えています。第1の電流制限回路は、次のとおりです。PWMモードでは、帰還ピン(FB)に電流を注入することによって $V_{CAP}$ のDC電流制限が動作します。この電流制限機能が最も有効に機能するには、FBとグランドの間のテブナン抵抗( $R_{BOT}/R_{TOP}$ )が100kΩを超えるようにします。

Burst Mode動作またはPWMモードが選択されている状態で $V_{SYS}$ が強固に短絡した場合は、インダクタ電流が増加してDC電流制限しきい値を超える可能性があります。この場合は、次のスイッチング・サイクルが始まるまで、ピーク電流制限(別の電流制限)回路がパワー・スイッチをオフします。

### 逆電流制限(バックアップ・モード)

PWMモードの動作では、レギュレーションを維持することが必要な場合、LTC3110には、 $V_{SYS}$ から流れ出す電流を能動的に導通させる能力があります。 $V_{SYS}$ をレギュレーション電圧より高い電圧に保持すると、大量の逆電流が流れる可能性があります。この状況が発生する可能性があるのは、LTC3110の $V_{SYS}$ を別の電源で動作状態に維持した場合です。この状態でデバイスが損傷しないようにするために、LTC3110は、負荷からパワー・スイッチDに流れ込む電流をモニタする逆電流コンパレータを備えています。この電流が1.2A(標準)を超えると、スイッチDはスイッチング・サイクルの残りの時間オフします。無負荷電流アプリケーションの場合は、インダクタ電流リップルを最小逆電流制限値の2倍( $1A \cdot 2 = 2A$ の最大インダクタ電流リップル)より低い値にする必要があります。インダクタ電流リップルの計算方法については、「インダクタの選択」のセクションを参照してください。

### 逆DC電流に起因する $V_{CAP}$ の過充電障害の防止 (バックアップ・モード)

PWMバックアップ動作(MODE = “H”かつ $DIR = "L"$ )時に、外部電源または別のDC/DCレギュレータが $V_{SYS}$ をバックアップ電圧の設定レベルより高い電圧まで誤って駆動すると、LTC3110はその $V_{SYS}$ 電流を逆転させ、同時に $V_{CAP}$ を充電する逆電流を発生させます。 $V_{SYS}$ が長時間誤った電圧レベルに保持されると、 $FBV_{CAP}$ が過充電しきい値を超えることがあります。LTC3110は逆充電を停止します。

$V_{DIR}$ が“L”的とき、逆DC電流による充電は $\overline{CHRG}$ ピンでは示されず、高インピーダンスのままでです。

$V_{SYS}$ を外部電源から駆動する場合、LTC3110を充電動作状態に設定すれば、通常はアプリケーションで過充電状態になることはありません。

外部電源を $DIR$ コンパレータから監視する場合、 $\overline{CHRG}$ 出力はPMOSのゲートを駆動して、バックアップ動作時に外部電源を切り離すことができます。29、30、31ページのPFETを使用したアプリケーションを参照してください。

$V_{SYS}$ を $DIR$ コンパレータから監視する場合は、バックアップ方向でのLTC3110の最大逆電流制限値より大きな電流を外部電源が供給できる必要があります。36ページの自律的アプリケーションを参照してください。外部電源が十分に強力である場合に限り、充電動作を確実に開始することができます。

## 動作

### FB<sub>V<sub>CAP</sub></sub>の障害状態

外付け部品が障害状態(例: 抵抗の開放または短絡、FB<sub>V<sub>CAP</sub></sub>ピンでの漏れ電流)になると、V<sub>CAP</sub>が不定の高電圧まで充電される可能性があります。V<sub>CAP</sub>が標準で5.95Vを超えると、LTC3110は充電を一時停止して、FB<sub>V<sub>CAP</sub></sub>がグランドに短絡した場合にLTC3110が実質的に絶対最大定格を超えないよう保護します。

スーパー・キャパシタやバッテリの最大電圧定格は、5.95Vより低いことがよくあります。これらの場合には、汎用コンパレータを構成してV<sub>CAP</sub>の過電圧を検出することができます(「アプリケーション情報」セクションの「冗長 V<sub>CAP</sub>スーパー・バイザとしての汎用コンパレータ構成による過電圧障害検出」の図を参照)。

### ソフトスタート(バックアップ・モード)

電源投入時にV<sub>CAP</sub>の電流トランジエントを最小限に抑えるため、LTC3110はソフトスタート回路を内蔵しています。ソフトスタートは、ソフトスタート時間の間にエラーアンプのリファレンス電圧がリニアに上昇することによって行われます。ソフトスタート期間中、レギュレータはMODEピンの設定に関係なく、常にPWMモードで動作します。起動時にV<sub>SYS</sub>の電圧が事前に充電され、既に目標値の80%より高い電圧になっている場合、ソフトスタートは省略され、LTC3110はMODEピンで設定されている動作モードに直ちに移行します。ソフトスタート期間は、サーマル・シャットダウンや低電圧ロックアウトが発生する限りセットされます。

### V<sub>SYS</sub>バックアップ電圧レギュレーションのエラーアンプと内部補償回路

昇降圧コンバータは、電圧モードのエラーアンプと内部補償回路網を使用します。

### V<sub>SYS</sub>平均電流制限レギュレーションのエラーアンプと内部補償回路

充電モード(DIR = "H")の昇降圧コンバータは、エラーアンプと内部補償回路網を使用して、V<sub>SYS</sub>ピンに流れ込む平均電流を安定化します。電流制限値はR<sub>PROG</sub>によって設定することができます。

### R<sub>SEN</sub>電流検出抵抗タップ

R<sub>SEN</sub>は、FET Dと内部検出抵抗の接続部に接続されています。R<sub>SEN</sub>ピンは未接続のままにしておいてください。そうしない場合は、負荷電流I<sub>RSEN</sub>により、V<sub>CAP</sub>ピンから流れ出す平均充電電流が同時に減少します。注記: R<sub>SEN</sub>に大容量のコンデンサを接続している場合にV<sub>SYS</sub>に高速の電圧ステップが発生すると、R<sub>SEN</sub>の内部抵抗に大量の突入電流が流れます。例えば、機械的な電源の接点を閉じてV<sub>SYS</sub>を供給する場合などが該当します。これらの場合には、R<sub>SEN</sub>とグランドの間に接続するコンデンサの値を最大10μFに制限します。

### V<sub>CAPOK</sub>充電終了インジケータおよびFB<sub>V<sub>CAP</sub></sub>コンパレータ

LTC3110はオープンドレインのコンパレータ出力ピンV<sub>CAPOK</sub>を備えており、これを使用してエネルギー蓄積素子の充電状態を示します。

コンパレータ入力FB<sub>V<sub>CAP</sub></sub>は、最終充電電圧を設定するため、標準ではV<sub>CAP</sub>とグランドの間の抵抗分割器に接続します。FB<sub>V<sub>CAP</sub></sub>の電圧が立ち上がりしきい値を超えると、コンパレータ出力V<sub>CAPOK</sub>は高インピーダンスになります。FB<sub>V<sub>CAP</sub></sub>の電圧が立ち下がりしきい値より低くなると、V<sub>CAPOK</sub>はグランド電位に低下します。RUNピンが"H"のとき、CAPOKは低い強度で引き込み続け、V<sub>CAP</sub>とV<sub>SYS</sub>が両方とも内部プルダウン・トランジスタのしきい値(最大1.4V)より低くなるまで継続します。

コンパレータは充電モードとバックアップ・モードの両方で動作し、RUNが"L"になってLTC3110がシャットダウン状態になると無条件に解放されます。

### CHRG動作モード・インジケータとDIRコンパレータ

LTC3110はオープンドレインのDIRコンパレータ出力ピンCHRGを備えており、通常はこれを使用してデバイスの動作モード(充電またはバックアップ)を表示します。プルアップ抵抗を接続することにより、この出力を使用してマイクロコントローラとインターフェースをとることや、入力分離スイッチとして使用するPチャネルMOSFETのゲートに接続することができます(「標準的応用例」セクションのUSBアプリケーションを参照)。

DIRコンパレータにはヒステリシスがあり、V<sub>DIR</sub>の電圧がDIRコンパレータの立ち上がりしきい値より高いときCHRGピンは"L"になり、V<sub>DIR</sub>の電圧がDIRコンパレータの立ち下がりしきい値より低いときCHRGは解放されます。

## 動作

図5. 汎用コンパレータ

RUNが“L”になってLTC3110がシャットダウンするか、低電圧状態時には、 $\overline{\text{CHRG}}$ ピンは無条件に解放されます。DIRピンの電圧は、絶対最大定格より低い値に制限されている限り、 $V_{\text{CAP}}$ または $V_{\text{SYS}}$ より高い値に駆動してもかまいません。

### 汎用コンパレータ

LTC3110は電圧コンパレータを内蔵しており、その入力にはCMPINピンからアクセス可能であり、また固定値の内部リファレンス電圧が加わっています。

このコンパレータを使用して、 $V_{\text{CAP}}$ 、 $V_{\text{SYS}}$ 、または任意の補助電源電圧をモニタすることができます。オープンドレイン出力 $\overline{\text{CMPOUT}}$ は、プルアップ抵抗を接続することにより、マイクロコントローラとインターフェースをとることができます。コンパレータの一般的な使用目的は、 $V_{\text{CAP}}$ を監視して、システムが消費電力を低減する必要が生じるまで、バックアップ・モードで許容される $V_{\text{CAP}}$ の最低電圧しきい値を設定することです。RUNが“L”になってLTC3110がシャットダウンするか、低電圧状態時には、 $\overline{\text{CMPOUT}}$ ピンは無条件に解放されます（「アプリケーション情報」のセクションも参照）。

### シャットダウン

RUNピンを0.3Vより下にするとLTC3110はシャットダウンし、RUNピンを1.0Vより上にするとICの動作がイネーブルされます。RUNピンにはプルダウン抵抗が内蔵されています。RUNの電圧は、絶対最大定格より低い値に制限されている限り、 $V_{\text{CAP}}$ または $V_{\text{SYS}}$ より高い値に駆動してもかまいません。

### 充電電流の熱フォールドバック

非常に大容量のコンデンサを充電しているときにLTC3110がサーマル・シャットダウンしないようにするために、LTC3110は温度レギュレータを備えています。ダイの温度が130°C（標準）を超えると、 $V_{\text{SYS}}$ の電流制限平均値が低下し、パッケージ内で消費される電力量を減らすのに役立ちます。電流制限値は、サーマル・シャットダウンの直前には設定制限値の約15%まで減少します。ダイ温度が標準で130°Cより低くなると、電流制限値は最大値まで戻ります。

### 低電圧ロックアウト

$V_{\text{CAP}}$ と $V_{\text{SYS}}$ のいずれかの電圧が低電圧ロックアウトの立ち上がりしきい値より低くなると、LTC3110は動作を停止して、SW1、SW2、 $V_{\text{MID}}$ 、 $\overline{\text{CMPOUT}}$ 、 $\overline{\text{CHRG}}$ 、PROGの各ピンは高インピーダンスになります。CAPOKは低い強度で引き込み続け、 $V_{\text{CAP}}$ と $V_{\text{SYS}}$ が両方とも内部プルダウン・トランジスタのしきい値（最大1.4V）より低くなるまで継続します。LTC3110は、 $V_{\text{CAP}}$ と $V_{\text{SYS}}$ のいずれか一方の電圧が低電圧ロックアウトの立ち上がりしきい値より高くなると動作を再開します。

### 熱に関する検討事項

LTC3110のパワー・スイッチは、内部電流制限しきい値までの電流で継続的に動作するように設計されています。ただし、高電流レベルで動作しているときは、デバイス内部でかなりの熱が発生する可能性があります。そのため、効率を最適化してLTC3110が最大定格出力電流を供給できるようにするために、デバイスの温度環境に関して注意深く検討する必要があります。特に、QFNパッケージとTSSOPパッケージのどちらの露出パッドもPC基板に半田付けし、PC基板はデバイスのパッケージからの放熱が最大になるように設計します。ダイ温度が約165°Cを超えると、デバイスは過熱シャットダウン状態になり、全てのスイッチングが停止して充電バランサがディスエーブルされます。注記：オープンドレイン出力ピンのCAPOK、 $\overline{\text{CMPOUT}}$ 、および $\overline{\text{CHRG}}$ は、サーマル・シャットダウン状態の間、引き続き“L”になっていることがあります。ダイが約10°C冷却されるまで、デバイスはディスエーブル状態のままになります。�ルト状態が解消されると、ソフトスタート回路が再起動され、過熱シャットダウン状態から滑らかに回復します。

## アプリケーション情報

LTC3110の標準的なアプリケーション回路を、このデータシートの表紙に「標準的応用例」として示します。外付け部品を適切に選択するには、PCBの面積、コスト、 $V_{SYS}$ と $V_{CAP}$ の電圧、許容リップル電圧、効率、熱に関する検討事項など、検討事項と交換条件から判断して、具体的なアプリケーションごとにデバイスに要求される性能に基づいて検討します。ここでは、外付け部品の選択とアプリケーション回路の設計に役立ついくつかの基本的ガイドラインと検討事項について説明します。

### インダクタの選択

LTC3110のアプリケーション回路に使用するインダクタをどう選択するかによって、供給可能な最大バックアップ電流および充電電流、インダクタ電流リップルの大きさ、および電力変換効率が決まります。インダクタのDC直列抵抗は小さくする必要があります。つまり、電流能力と効率は妥協することになります。インダクタンスの値を大きくするとインダクタの電流リップルは減少するので、バックアップ電流能力は一般に高くなります。DC抵抗が固定値の場合は、ピーク電流を低減して平均バックアップ電流に近づけることにより、インダクタンスの値が大きいほど効率が高くなるので、大量のRMS電流に起因する抵抗損失を最小限に抑えることができます。ただし、所定のインダクタ・ファミリ内のインダクタは、一般に値が大きいほど直列抵抗が大きいので、この効率の向上は抑えられます。LTC3110のアプリケーションで使用されるインダクタは、飽和電流定格がワーストケースの平均インダクタ電流にリップル電流の半分を加えた電流を超えている必要があります。動作モードごとのピーク・トゥ・ピーク・インダクタ電流リップルは、次式で計算できます。

$$\Delta I_{L(P-P)(BUCK)} = \frac{V_{SYS}}{1.2\text{MHz} \cdot L} \left( \frac{V_{CAP} - V_{SYS}}{V_{CAP}} \right)$$

$$\Delta I_{L(P-P)(BOOST)} = \frac{V_{CAP}}{1.2\text{MHz} \cdot L} \left( \frac{V_{SYS} - V_{CAP}}{V_{SYS}} \right)$$

$L$ はインダクタンス(単位: $\mu\text{H}$ )です。

電力変換効率に対する影響以外に、インダクタのDC抵抗は、特に $V_{CAP}$ の電圧が低いときに昇降圧コンバータの最大出力電流能力にも影響を与えることがあります。降圧モードでは、昇降圧コンバータの出力電流はインダクタ電流が電流制限しきい値に達することによってのみ制限されます。ただし、昇圧モードの場合、特に昇圧比が高いと、 $V_{SYS}$ のバックアップ電流能力はパワーモードの全抵抗損失によっても制限されます。これらにはスイッチ抵抗、インダクタ抵抗およびPCBのトレース抵抗が含まれます。DC抵抗が大きいインダクタを使用すると、

$V_{SYS}$ のバックアップ電流能力は、このデータシートの「標準的性能特性」のセクションに示す値より低下することがあります。ガイドラインとして、ほとんどのアプリケーションでは、インダクタのDC抵抗を  $60\text{m}\Omega$  の標準パワー・スイッチ抵抗より大幅に小さくします。

インダクタの最小値は、 $V_{CAP}$ ワーストケースの平均電流にリップル電流の半分を加えた値が $V_{CAP}$ の電流制限しきい値に達しないことを保証する必要があります。固定スイッチング周波数が  $1.2\text{MHz}$  の場合、標準的な推奨インダクタ値は  $1.5\mu\text{H}$  です。

インダクタのコア材と種類により、所定の電流定格でのインダクタのサイズと価格が異なります。シールドされた構造は、他の回路との干渉の可能性を最小限に抑えるので一般に適しています。インダクタの種類の選択は、価格、サイズ、および特定のアプリケーションのEMIに対する要件に依存します。LTC3110の多くのアプリケーションに最適なインダクタのサンプルを表1に示します。

表1. 推奨インダクタ

| VENDOR                                                                             | PART/STYLE                                                                                            |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Coilcraft<br><a href="http://www.coilcraft.com">www.coilcraft.com</a>              | XAL50xx Series (XAL5030-222ME_)<br>XAL60xx Series (XAL6030-222ME_)<br>EPL7040 Series (EPL7040-222ME_) |

| Würth Elektronik<br><a href="http://www.we-online.com">www.we-online.com</a>       | WE-HCI Series (744310150, 744314200)<br>WE-LHMI Series (74437346018, 74437349022)                     |

| Coiltronics www.<br><a href="http://cooperindustries.com">cooperindustries.com</a> | DR73 Series (DR73-2R2-R) DRQ74 Series (DR74-2R2-R)                                                    |

| Vishay<br><a href="http://www.vishay.com">www.vishay.com</a>                       | IHL-P-2525 Series (IHL-P-2525AH-01, IHL-P-2525CZ-01) IHL-P-2020 Series (IHL-P-2020CZ-A1)              |

| スミダ<br><a href="http://www.sumida.com">www.sumida.com</a>                          | CDEP6D31ME Series (CDEP6D31MENP-2R2MC)                                                                |

| 村田製作所<br><a href="http://www.murata.com">www.murata.com</a>                        | LQH66S Series (LQH66SN1R5M03)                                                                         |

| 太陽誘電<br><a href="http://www.yuden.co.jp/jp/">http://www.yuden.co.jp/jp/</a>        | NR6012T2R5NE NR8040T2RON                                                                              |

| TDK<br><a href="http://www.component.tdk.com">www.component.tdk.com</a>            | CLF Series                                                                                            |

## アプリケーション情報

### V<sub>SYS</sub>のコンデンサの選択

V<sub>SYS</sub>のバックアップ電圧リップルを最小限に抑えるため、V<sub>SYS</sub>ピンには低ESRのコンデンサを使用します。積層セラミック・コンデンサはESRが小さく、実装面積の小さいものが入手できるので最適です。十分大きな値のコンデンサを選択して、V<sub>SYS</sub>の電圧リップルを許容レベルまで低減します。コンデンサのESRおよびESLを無視すると、V<sub>SYS</sub>のピーク・トゥ・ピーク電圧リップルは、次式により計算することができます。ここで、C<sub>VSYS</sub>はV<sub>SYS</sub>に接続する容量であり、I<sub>LOAD</sub>はV<sub>SYS</sub>の負荷電流です。

$$\Delta V_{P-P(BUCK)} = \frac{V_{SYS}}{8 \cdot (1.2\text{MHz})^2 \cdot L \cdot C_{V_{SYS}}} \left( \frac{V_{CAP} - V_{SYS}}{V_{CAP}} \right)$$

$$\Delta V_{P-P(BOOST)} = \frac{I_{LOAD}}{1.2\text{MHz} \cdot C_{V_{SYS}}} \left( \frac{V_{SYS} - V_{CAP}}{V_{SYS}} \right)$$

昇圧モードではV<sub>SYS</sub>の電流が不連続であることを考慮すると、昇圧モードでのリップルは、降圧モードでのリップルの大きさよりも通常はかなり大きくなります。V<sub>SYS</sub>の容量の両端に生じるV<sub>SYS</sub>の電圧リップル以外に、V<sub>SYS</sub>のコンデンサの内部抵抗の両端にもV<sub>SYS</sub>の電圧リップルが生じます。ESRによって発生したV<sub>SYS</sub>の電圧リップルは、V<sub>SYS</sub>のコンデンサの直列抵抗に比例します。

### スーパーキャパシタの選択と追加のバイパス・コンデンサ

C<sub>V<sub>CAP</sub></sub>の全容量値が2mFより大きい場合や、各コンデンサ・スタックあたり4mFより大きい場合、LTC3110は安定しています。スーパーキャパシタはセラミック・コンデンサやタンタル・コンデンサより物理的にはるかに大きいので、一般に、チャージャのすぐ近くに配置することができません。レイアウトによるコンデンサのESRへの影響を最小に抑えるには、コンデンサ相互の接続およびICへの接続のためのトレースの幅をできるだけ大きくします。V<sub>MID</sub>ピンのトレースで伝送される平均電流は300mAなので、さほど厳しくはありません。ローカルのデカッピング・コンデンサをV<sub>CAP</sub>とグランドの間に接続し、できるだけデバイスに近づけて配置することを推奨します。積層セラミック・コンデンサはESRが極めて低く、実装面積の小さいものが入手できるので、電圧のデカッピングに最適です。ほとんどのアプリケーションには10μFのデカッピング・コンデンサで十分ですが、無制限にもっと大きな値のものを使用できます。

電圧リップルを最小限に抑えてデバイスの適切な動作を保証するため、値が100nFの低ESRバイパス・コンデンサと10μFの別の低ESRバイパス・コンデンサをV<sub>CAP</sub>ピンにできるだけ近づけて配置します。このコンデンサをV<sub>CAP</sub>とグランド・プレーンに接続する配線はできるだけ短くします。バランス調整が不要な状況でV<sub>SYS</sub>に1個のコンデンサを使用する場合は、100nF以上のコンデンサをV<sub>MID</sub>とPGNDの間に接続する必要があります。

### V<sub>CAP</sub>とV<sub>SYS</sub>の推奨バイパス・コンデンサ

コンデンサの種類の選択は、主にコスト、サイズ、漏れ電流の兼ね合いによって決まります。スイッチング・コンバータのアプリケーションには、小型、低ESR、および低リーク電流であることから、多くの場合セラミック・コンデンサが使用されます。ただし、パワー・アプリケーション向けに設計されたセラミック・コンデンサの多くは、DCバイアス電圧が上昇するにつれ、容量が定格値から大きく減少します。例えば、小型の表面実装セラミック・コンデンサをその定格電圧近くで動作させると、容量がその定格値から50%以上低下することも珍しくありません。そのため、場合によっては、最大動作電圧で所定の容量を実現するため、大きな値の容量や必要以上に電圧定格の高いコンデンサを使用する必要があります。アプリケーション回路で意図する容量を実現させるため、コンデンサ・メーカーの容量対DCバイアス電圧の曲線を必ず参照してください。表3に示すコンデンサは、LTC3110のアプリケーション回路に最適な小型表面実装セラミック・コンデンサの例です。全温度範囲での容量損失を最小限に抑えるため、記載されている全てのコンデンサはX5RまたはX7R誘電体です。

### コンデンサの最大電圧とバランス調整

スーパーキャパシタの使用寿命は、定格電圧、定格温度、定格寿命、実際の動作電圧、および動作温度によって決まります。スーパーキャパシタの寿命を延ばすには、動作電圧と温度を最大定格から下げます。Illinois Capacitor<sup>1</sup>とMaxwell<sup>2</sup>のWebサイトにはこれらのコンデンサの寿命計算のためのページが用意しております。

<sup>1</sup><http://www.illinoiscapacitor.com/tech-center/life-calculators.aspx>

<sup>2</sup>[http://www.maxwell.com/products/ultracapacitors/docs/APPLICATIONNOTE1012839\\_1.PDF](http://www.maxwell.com/products/ultracapacitors/docs/APPLICATIONNOTE1012839_1.PDF)

## アプリケーション情報

それぞれのコンデンサの推奨ディレーティング電圧を使うと、寿命が伸びます。V<sub>CAP</sub>の電圧が標準で2.2Vより高くなると、LTC3110は各コンデンサの電圧をV<sub>CAP</sub>/2に維持します。充電中、いずれかのスーパー・キャパシタに過電圧が発生しないようにするため、V<sub>MID</sub>の電圧は、標準で300mAの電流供給能力を持つ電圧バランス調整バッファ出力により絶えず駆動されます。

LTC3110がV<sub>CAP</sub>から流す電流が最小になるのは、充電終了時です。電流源を制限して、V<sub>CAP</sub>がそのレギュレーション設定値より高くならないよう注意する必要があります。設定値を超えると、LTC3110はレギュレーションを維持できないからです。

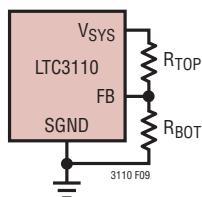

### V<sub>SYS</sub>電圧のプログラミング

V<sub>SYS</sub>の電圧は、図6に示すように、FBピンに接続した外付け抵抗分割器によって設定します。

V<sub>SYS</sub>のバックアップ電圧は、抵抗分割器の値により、次式に従って求められます。

$$V_{SYS} = 0.6V \cdot \left( 1 + \frac{R_{TOP}}{R_{BOT}} \right) \quad (1)$$

昇降圧コンバータは電圧モード制御を使用しており、V<sub>SYS</sub>電圧の設定以外に、R<sub>TOP</sub>は帰還ループの動特性において不可欠な役割を果たします。一般に、R<sub>TOP</sub>の値を大きくすると安定性が高まり、トランジエント応答の速度が低下します。R<sub>TOP</sub>の値を小さくすると安定性が低下し、トランジエント応答の速度が高まります。妥当な出発点は、R<sub>TOP</sub> = 1Mを選択してからR<sub>BOT</sub>に要求される値を計算し、式1に従って目的とするV<sub>SYS</sub>の電圧を設定します。V<sub>SYS</sub>に大容量のコンデンサを使用すると、コンバータの帯域幅が狭くなります。その場合には、R<sub>TOP</sub>を小さくしてトランジエント応答を改善します。値の大きなインダクタを使用するか、V<sub>SYS</sub>のコンデンサ容量を小さくすると、ループの安定性が低下します。また、R<sub>TOP</sub>の値を大きくすると、位相余裕を改善することができます。

図6. V<sub>SYS</sub>バックアップ電圧の設定

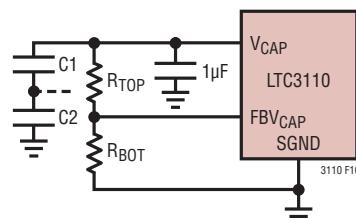

### V<sub>CAP</sub>電圧のプログラミング

V<sub>CAP</sub>の電圧は、図7に示すように、FBV<sub>CAP</sub>ピンに接続した外付け抵抗分割器によって設定します。

V<sub>CAP</sub>の最大電圧は、抵抗分割器の値により、次式に従って求められます。

$$V_{CAP} = 1.095V \cdot \left( 1 + \frac{R_{TOP}}{R_{BOT}} \right)$$

V<sub>CAP</sub>の電圧をその設定最大値より高くすることができる電流源を制限する場合は、注意が必要です。チャージャ・モードでは、LTC3110がV<sub>CAP</sub>のレギュレーションを維持する手段がないからです(図15、「μCに送信される過電圧エラー信号」を参照)。

図7. V<sub>CAP</sub>電圧のプログラミング

### V<sub>MID</sub>充電バランス出力

このピンは2つの直列スーパー・キャパシタの接続部に接続します。プッシュ/プル・バッファ出力は、V<sub>MID</sub>ピンの電圧を強制的にV<sub>CAP</sub>ピンの半分の電圧にします。出力を使用しない場合、例えば、1つのスーパー・キャパシタまたはバッテリを使用するアプリケーションでは、一般に、値が1nF以上のコンデンサをV<sub>CAP</sub>とV<sub>MID</sub>の間およびV<sub>MID</sub>とPGNDの間に接続します。

図8. V<sub>MID</sub>充電バランス出力

## アプリケーション情報

### DIRバックアップ・スーパーバイザのしきい値電圧のプログラミング

バックアップ・スーパーバイザのしきい値電圧は、図10に示すように、DIRピンに接続した外付け抵抗分割器によって設定します。

DIRスーパーバイザのしきい値電圧は、抵抗分割器の値により、次式に従って求められます。

$$V_{TH(DIR\_RISING)} = 1.095V \cdot \left( 1 + \frac{R_{TOP}}{R_{BOT}} \right)$$

$$V_{TH(DIR\_FALLING)} = 1.045V \cdot \left( 1 + \frac{R_{TOP}}{R_{BOT}} \right)$$

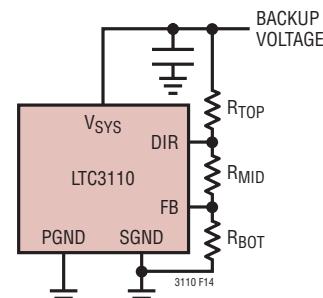

### バックアップ電圧およびDIRしきい値電圧の精度を高めたプログラミング

DIRピンの電圧とFBピンの電圧を、同じV<sub>SYS</sub>の電圧を分割して供給するアプリケーションでは、1列の抵抗分割器を使用することによって、抵抗の許容誤差の影響が小さくなり、抵抗を1本節約することができます。

$$V_{TH(DIR\_RISING)} = 1.095V \cdot \left( 1 + \frac{R_{TOP}}{R_{BOT} + R_{MID}} \right)$$

$$V_{TH(DIR\_FALLING)} = 1.045V \cdot \left( 1 + \frac{R_{TOP}}{R_{BOT} + R_{MID}} \right)$$

$$V_{SYS} = 0.6V \cdot \left( 1 + \frac{R_{TOP} + R_{MID}}{R_{BOT}} \right)$$

方向スーパーバイザのしきい値V<sub>TH</sub>(DIR\_RISING)は、バックアップ電圧V<sub>SYS</sub>より高く、十分な電圧差があることが必要であり、抵抗の許容誤差、リップル電圧、負荷電流ステップによる電圧低下に対応できる必要があることに注意してください。必要な場合は、DIRピンの前にRCフィルタを接続することにより、スーパーバイザの応答速度を低下させることができます。図12を参照してください。

要件に注意を払ってください。図11に示すように、または36ページの自律的アプリケーションの場合のように、V<sub>SYS</sub>をDIR入力で監視する場合は、充電動作に確実に切り替わるために、LTC3110の最大逆電流制限値である2Aより多くの電流を外部のV<sub>SYS</sub>電源が供給する必要があります。

図11. 許容誤差の小さい電圧

## アプリケーション情報

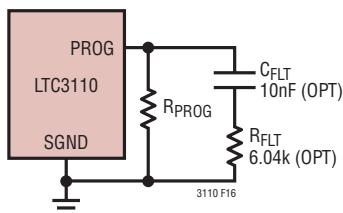

### チャージャ動作での $V_{SYS}$ 平均電流制限のプログラミング (DIR = "H")

$V_{SYS}$ の平均電流制限値は、図13に示すように、PROGピンと信号グランド(SGND)の間に接続した外付け抵抗によって設定します。

この抵抗値により、 $V_{SYS}$ に流れ込む平均電流を次式に従って求めます。

$$I_{V_{SYS}} = \frac{3k\Omega}{R_{PROG}}$$

温度範囲の広いアプリケーションでは、抵抗 $R_{PROG}$ の温度係数を考慮する必要があります。 $R_{PROG}$ が12.4kより大きい場合は、 $R_{FLT}$ と $C_{FLT}$ を追加してフィルタリングを行う必要があります。

図13.  $V_{SYS}$ の平均電流制限値の設定

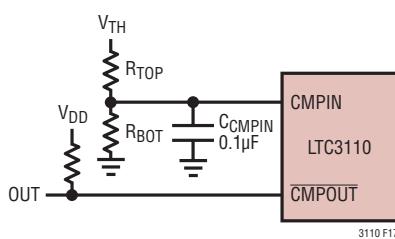

### ヒステリシスのある汎用電圧スーパーバイザとしてのCMPIN構成

立ち上がりと立ち下がりのしきい値電圧 $V_{TH}$ は、抵抗分割器の値(図14参照)により、次式に従って求められます。

$$V_{TH(RISING)} = 0.65V \cdot \left( 1 + \frac{R_{TOP}}{R_{BOT}} \right)$$

$$V_{TH(FALLING)} = 0.59V \cdot \left( 1 + \frac{R_{TOP}}{R_{BOT}} \right)$$

図14. 汎用電圧スーパーバイザ

CMPINを抵抗分割器で駆動する場合や、インピーダンスが $200\Omega$ より高い出力で駆動する場合は、CMPINとGNDの間に $0.1\mu F$ のコンデンサを接続して性能を最適にします(図14参照)。

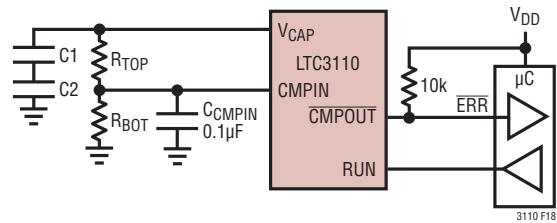

### 冗長 $V_{CAP}$ スーパーバイザとしての汎用コンパレータ構成による過電圧障害検出

部品が故障して $V_{CAP}$ の電圧帰還(FBV<sub>CAP</sub>)が遮断されると、充電中に $V_{CAP}$ が過電圧状態になる可能性があります。汎用コンパレータをスーパーバイザとして構成して、過電圧エラー信号をマイクロコントローラに送信することができます(図15参照)。

図15. μCに送信される過電圧エラー信号

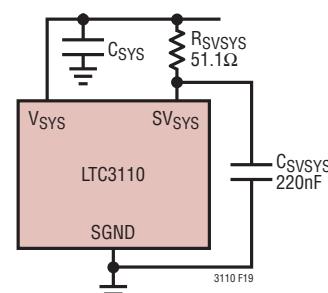

### $SV_{SYS}$ のフィルタリング

ノイズが重要な多くのアプリケーションでは、PCB上に小さなRCフィルタを配置して信号電源pin $SV_{SYS}$ にフィルタをかけるのが役立ちます(図16参照)。フィルタを追加した場合は、 $SV_{SYS}$ pinに接続された追加の負荷を調べて、抵抗のインピーダンスと比較して負荷が小さいかどうか、および $SV_{SYS}$ に不要な電圧降下が生じていないか確認する必要があります。

図16.  $SV_{SYS}$ のフィルタリング

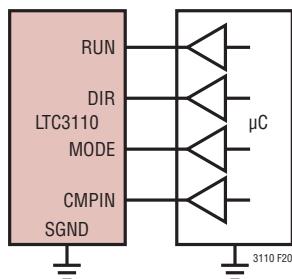

### RUN、DIR、MODE、CMPIN入力のデジタル制御

RUN、DIR、MODE、CMPINのコンパレータ入力は、外部マイクロコントローラからデジタルで駆動することができます。

## アプリケーション情報

図17. マイクロコントローラから駆動される

入力RUN、DIR、MODE、CMPIN

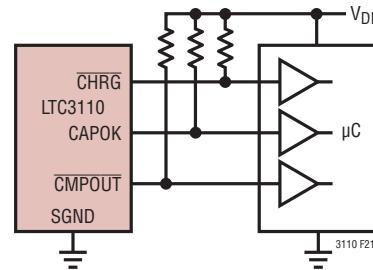

## オープンコレクタ出力

$\overline{\text{CHRG}}$ 、 $\overline{\text{CAPOK}}$ 、および $\overline{\text{CMPOUT}}$ のオープンコレクタ出力は他の外部信号線とワイヤードOR構成で互いに接続することができます。マイクロコントローラ入力とインターフェースをと

図18. μCとインターフェースをとる出力 $\overline{\text{CHRG}}$ 、 $\overline{\text{CAPOK}}$ 、 $\overline{\text{CMPOUT}}$

る場合は、レベルシフトのためプルアップ抵抗に接続することができます。

また、これらのオープンコレクタ出力を使用して、最大20mAの小負荷(例:豆ランプやLED)を駆動することもできます。

表2: 推奨されるスーパーキャパシタとウルトラキャパシタ

| メーカー               | 値(F) | ESR<br>(mΩ) | 電圧<br>(V)     | 温度範囲(°C)  | サイズ(mm)W×L×H   |

|--------------------|------|-------------|---------------|-----------|----------------|

| ムラタエレクトロニクス        |      |             |               |           |                |

| DMF3R5R5L334M3DTA0 | 0.33 | 60          | 4.2(5.5 Peak) | -30 to 70 | 14.0×21.0×2.5  |

| DMF3Z5R5H474M3DTA0 | 0.47 | 40          | 4.2(5.5 Peak) | -30 to 70 | 14.0×21.0×3.2  |

| Tecate             |      |             |               |           |                |

| TPL-10/10X30F      | 10   | 85          | 2.7           | -40 to 65 | 10.0×10.0×30.0 |

| TPL-25/16X26F      | 25   | 42          | 2.7           | -40 to 65 | 16.0×16.0×26.0 |

| TPL-100/22X45F     | 100  | 15          | 2.7           | -40 to 65 | 22.0×22.0×45.0 |

| TPLE-25/16X26F     | 25   | 42          | 2.3           | -40 to 85 | 16.0×16.0×26.0 |

| TPLE-100/22X45F    | 100  | 15          | 2.3           | -40 to 85 | 22.0×22.0×45.0 |

| TPLS-400/35X60F    | 400  | 12          | 2.7           | -40 to 65 | 35.0×35.0×60.0 |

| AVX                |      |             |               |           |                |

| BZ015A503Z_B       | 0.05 | 160         | 5.5           | -20 to 70 | 28.0×17.0×4.1  |

| BZ015A104Z_B       | 0.1  | 80          | 5.5           | -20 to 70 | 28.0×17.0×6.7  |

| CAP-XX             |      |             |               |           |                |

| HS206F             | 0.6  | 70          | 5.5           | -40 to 85 | 39.0×17.0×2.5  |

| HS230              | 1.2  | 50          | 5.5           | -40 to 85 | 39.0×17.0×3.8  |

| Cooper Bussmann    |      |             |               |           |                |

| A1635-2R5475-R     | 4.7  | 25          | 2.5           | -25 to 70 | 16.0×16.0×35.0 |

| M1325-2R5905-R     | 9    | 20          | 2.5           | -40 to 60 | 13.0×13.0×26.0 |

| HB1625-2R5256-R    | 25   | 36          | 2.5           | -25 to 70 | 16.0×16.0×25.0 |

| HV1860-2R7107-R    | 100  | 10          | 2.7           | -40 to 65 | 18.0×18.0×60.0 |

| Illinois Capacitor |      |             |               |           |                |

| 506DER2R55LZ       | 50   | 30          | 2.5           | -40 to 70 | 18.0×18.0×60.0 |

| 357DER2R55EZ       | 100  | 12          | 2.5           | -40 to 70 | 35.0×35.0×60.0 |

| Maxwell            |      |             |               |           |                |

| BCAP0005           | 5    | 170         | 2.7           | -40 to 65 | 10.0×10.0×20.0 |

| BCAP0100T01        | 100  | 15          | 2.7           | -40 to 65 | 22.0×22.0×45.0 |

| 太陽誘電               |      |             |               |           |                |

| PAS2026FR2R5504    | 0.5  | 55          | 2.5           | -25 to 60 | 26.0×20.0×0.9  |

| PAS0815LS2R5105    | 1    | 70          | 2.5           | -25 to 70 | 8.0×8.0×15.0   |

| LIC2540R3R8207     | 200  | 50          | 2.2 to 3.8    | -25 to 70 | 25.0×25.0×40.0 |

3110fa

## アプリケーション情報

表3. 代表的なバイパス・コンデンサおよびV<sub>SYS</sub>コンデンサ

| 製品番号                | 値(μF) | 電圧(V) | 実装面積 |

|---------------------|-------|-------|------|

| <b>AVX</b>          |       |       |      |

| 12066D106K          | 10    | 6.3   | 0603 |

| 12066D226K          | 22    | 6.3   | 0805 |

| 12066D476K          | 47    | 6.3   | 0805 |

| <b>Kemet</b>        |       |       |      |

| C0603C106M9PACTU    | 10    | 6.3   | 0603 |

| C0805C226M9PACTU    | 22    | 6.3   | 0805 |

| C0805C476M9PACTU    | 47    | 6.3   | 0805 |

| <b>村田製作所</b>        |       |       |      |

| GRM188D70J106MA73   | 10    | 6.3   | 0603 |

| GRM219B30J226ME47   | 22    | 6.3   | 0805 |

| GRM21BB30J476ME15   | 47    | 6.3   | 0805 |

| <b>TDK</b>          |       |       |      |

| C1608X7S0J106M080AC | 10    | 6.3   | 0603 |

| C2012X5R0J226M085AB | 22    | 6.3   | 0805 |

| C2012X5R0J476M125AC | 47    | 6.3   | 0805 |

| <b>太陽誘電</b>         |       |       |      |

| JMK107BJ106MA       | 10    | 6.3   | 0603 |

| JMK212ABJ226MD      | 22    | 6.3   | 0805 |

| JMK212BBJ476MG      | 47    | 6.3   | 0805 |

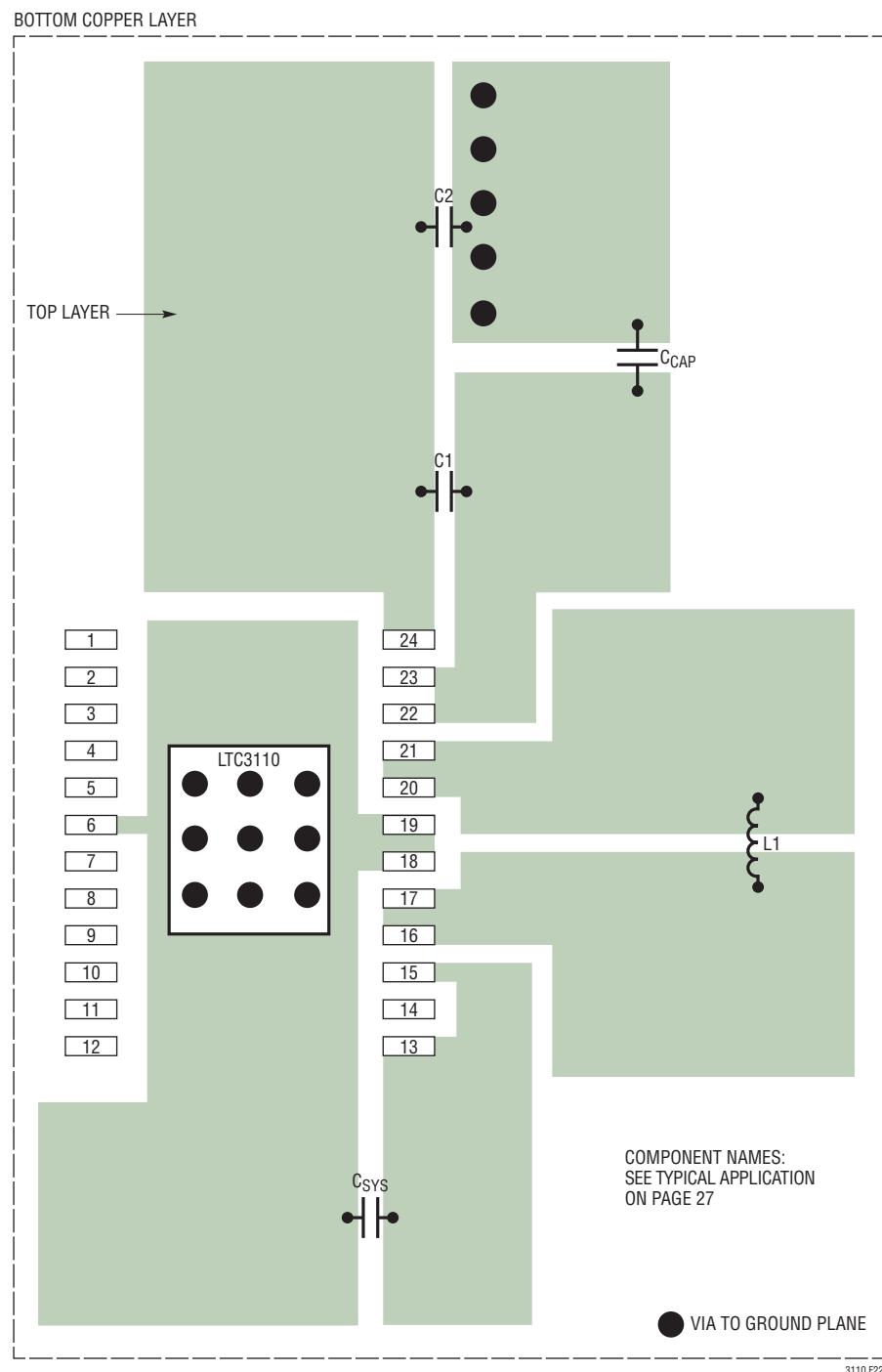

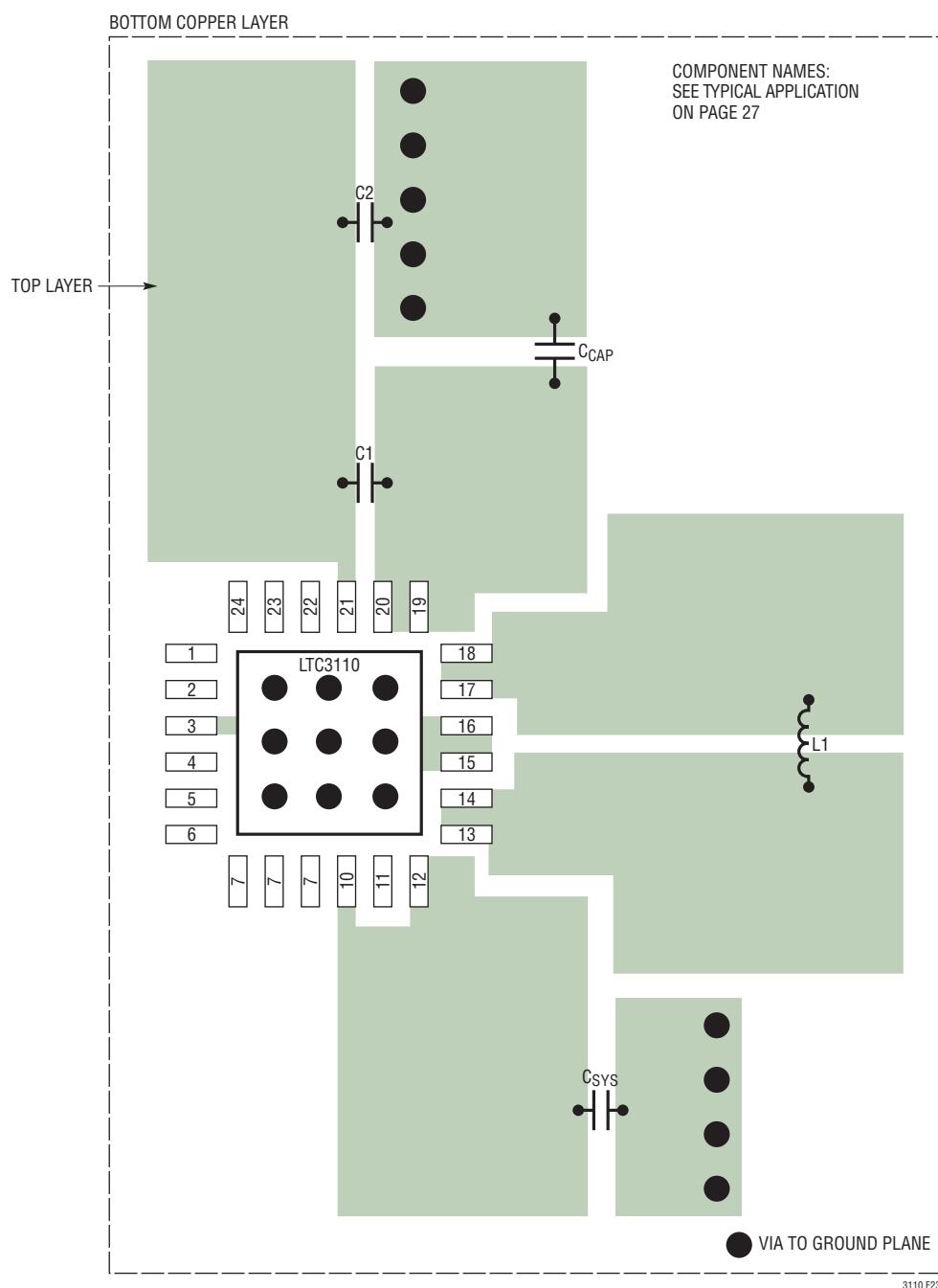

## PCB レイアウトに関する検討事項

LTC3110は大きな電流を高い周波数でスイッチングします。ノイズのない安定した動作を保証するには、PCB レイアウトに特別に注意が必要です。2層 PCB を使用する場合は、LTC3110に使用する推奨のPCB レイアウトを図19および20に示します。熱やノイズの理由から、4層 PCB レイアウトを推奨します。主なガイドラインは以下のとおりです。

1. 全ての循環する高電流経路をできるだけ短くします。これは図19と図20の部品への配線をできるだけ短くかつ幅広くすることによって実現できます。コンデンサのグランドは、できるだけ短い配線でビアによってグランド・プレーンに接続します。バイパス・コンデンサ CSYS および C<sub>CAP</sub> は、できるだけデバイスの近くに配置し、グランドまでの経路をできるだけ短くします。

2. 表示した部品とそれらの接続は全て完全なグランド・プレーン上に配置します。

3. ダイ・アタッチ・パッドにビアを使用すると、特に、ビアが PCB の露出した底面のグランド・プレーン領域まで伸びていると、チャージャの温度環境が改善されます。

4. FB、PROG、DIR、CMPIN、FBVCAPの各ピンへの接続はできるだけ短くし、スイッチ・ピンの接続点から離します。

## アプリケーション情報

図19. TSSOPパッケージのPCB部品配置

## アプリケーション情報

図20. QFNパッケージのPCB部品配置

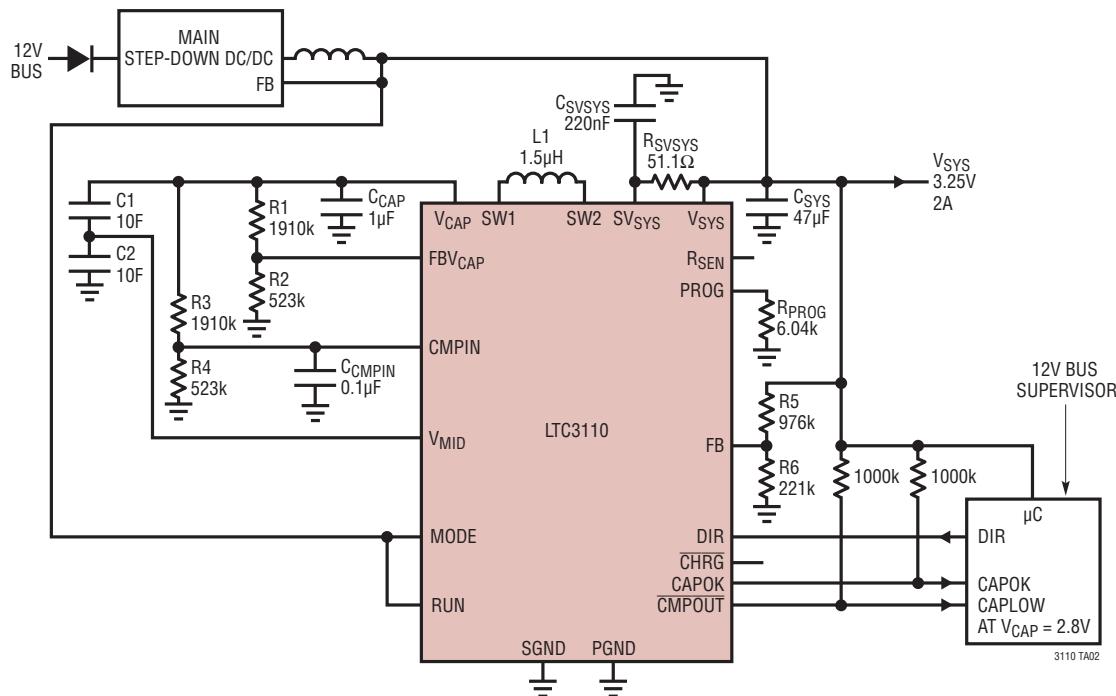

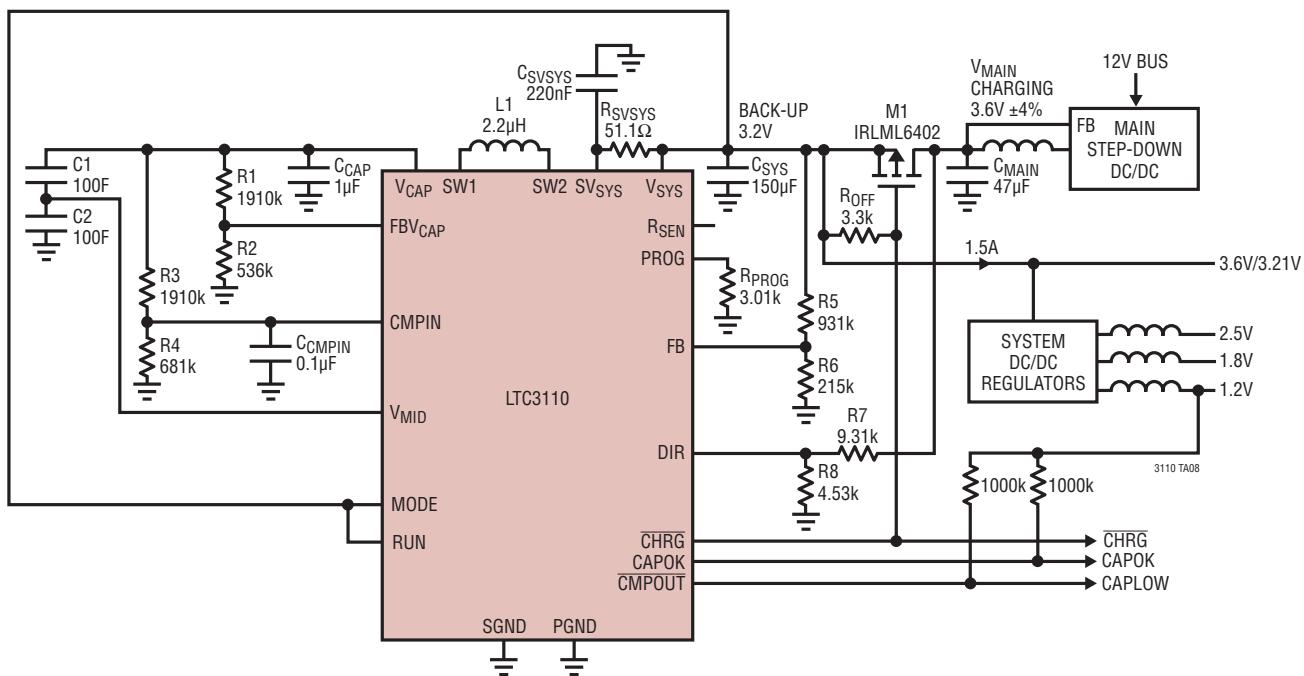

## 標準的応用例

アクティブな電圧バランス調整機能を備えたスーパー・キャパシタ・スタックからの3.3V/2A出力によるバックアップ/充電アプリケーション

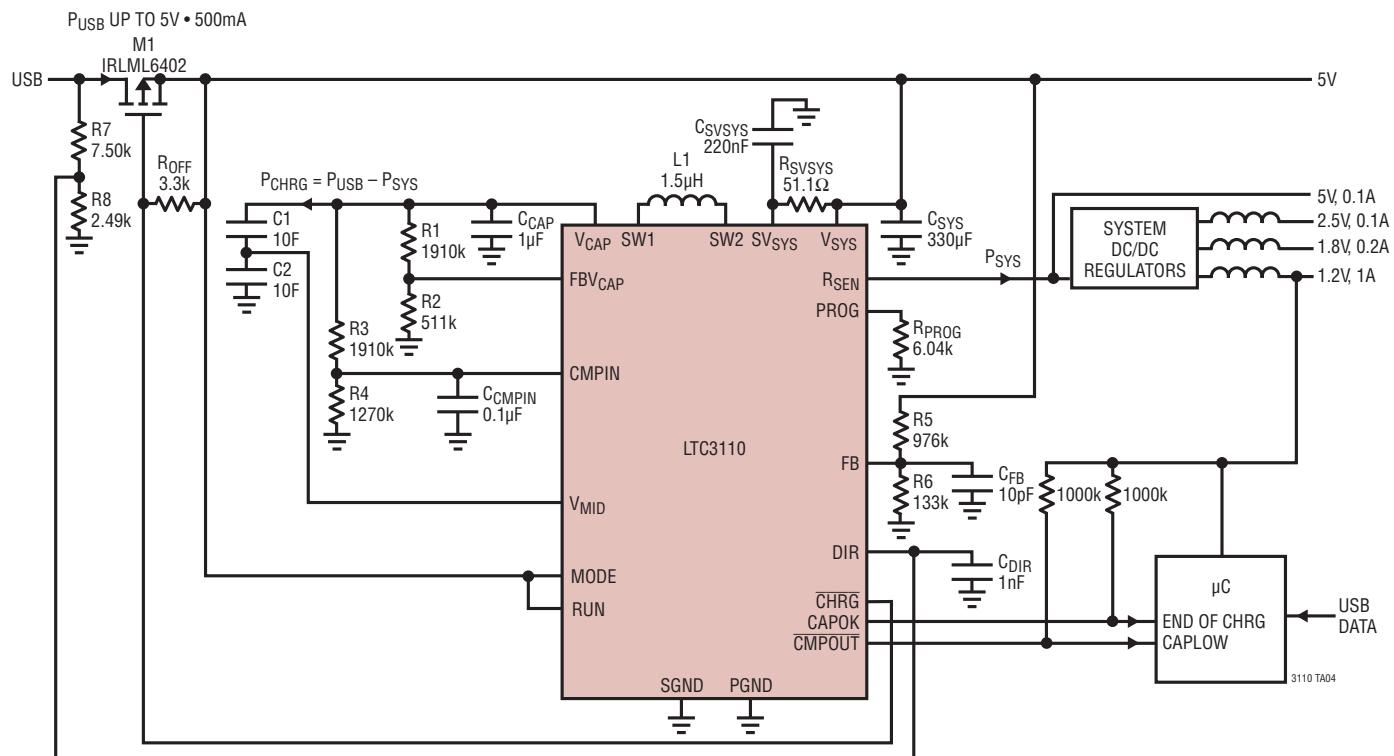

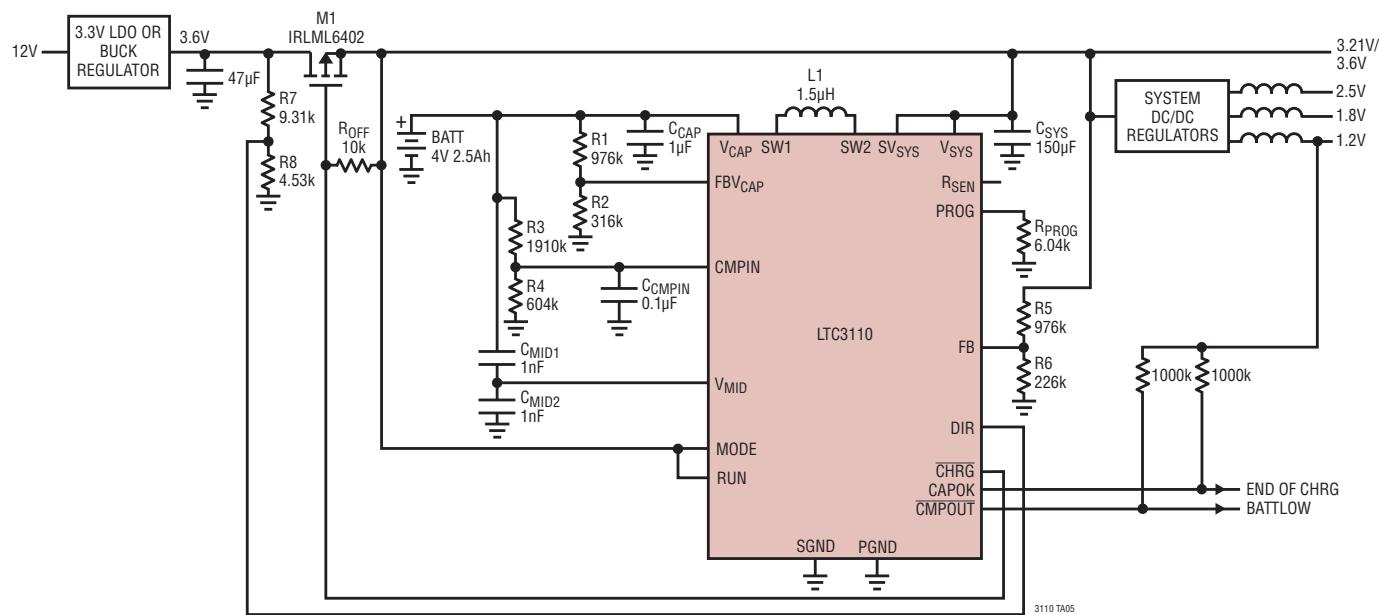

## 標準的応用例

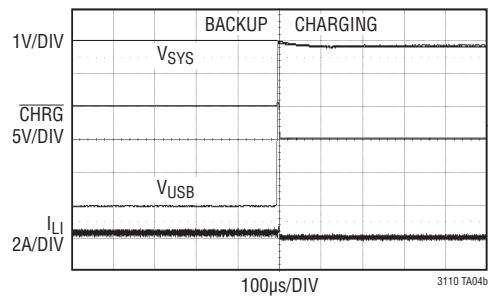

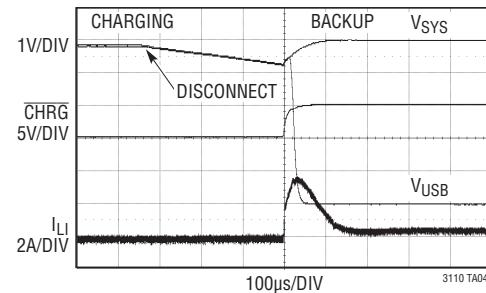

システム負荷に依存する可変充電電源  $P_{CHRG}$  を備えた 500mA USB 充電/バックアップ・アプリケーション

USB 接続時の過渡特性

USB 切断時の過渡特性

## 標準的応用例

入力分離スイッチを備えた自律的バックアップおよび充電アプリケーション

## 標準的応用例

鉛蓄電池のバックアップ/充電アプリケーション

3110fa

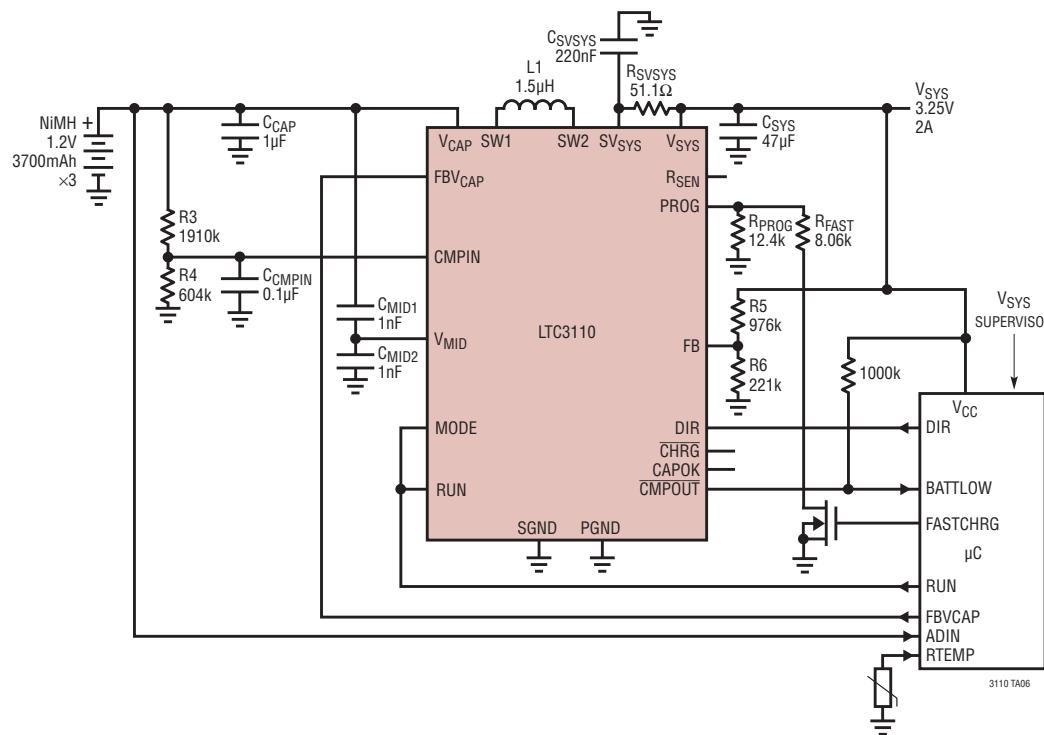

## 標準的応用例

## NiMHバッテリのバックアップ/充電アプリケーション

NOTE ON DIGITAL CONTROL SIGNALS IN NiMH BACKUP/RECHARGE APPLICATION:

CHARGING IS INITIATED BY PULLING DIR = HIGH AND FBVCAP = LOW.

CHARGING IS TERMINATED BY PULLING DIR = HIGH AND FBVCAP = HIGH (FBVCAP MUST BE  $\geq 1.2V$ ).

SYSTEM BACK-UP IS INITIATED BY FORCING FBVCAP = LOW, WAITING 5μs, THEN FORCING DIR = LOW.

GENERAL SAFETY NOTE: CHARGING MUST BE TERMINATED IF THE BATTERY VOLTAGE

OR CHARGE TIME HAVE REACHED THEIR MAXIMUM VALUES OR IF THE BATTERY

TEMPERATURE IS ABOVE OR BELOW THE SAVE OPERATING REGION OF THE BATTERY.

SEE DATASHEET OF THE BATTERY.

THE THERMISTOR, USED FOR MEASURING THE TEMPERATURE, MUST HAVE GOOD

THERMAL CONNECTION TO THE BATTERY PACK.

## 標準的応用例

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/product/LTC3110#packaging> を参照してください。

**FE Package

24-Lead Plastic TSSOP (4.4mm)

(Reference LTC DWG # 05-08-1771 Rev B)

Exposed Pad Variation AA**

注記 :

- 標準寸法 : ミリメートル

- 寸法は  $\frac{\text{ミリメートル}}{(\text{インチ})}$

- 図は実寸とは異なる

4. 露出パッド接着のための推奨最小 PCB メタルサイズ

\* 寸法にはモールドのバリを含まないモールドのバリは各サイドで 0.150mm (0.006") を超えないこと

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/product/LTC3110#packaging> を参照してください。

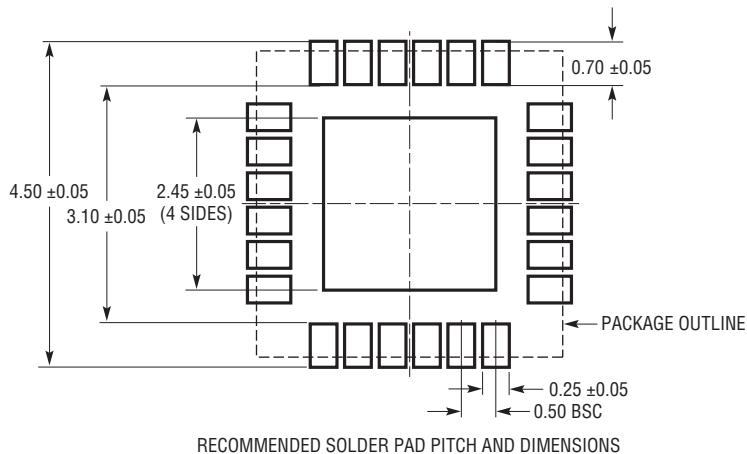

**UF Package

24-Lead Plastic QFN (4mm × 4mm)**

(Reference LTC DWG # 05-08-1697 Rev B)

注記:

1. 図はJEDECのパッケージ外形MO-220のバリエーション(WGGD-X)に含めるよう提案されている(承認待ち)

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで0.15mmを超えないこと

5. 露出パッドは半田メッキとする

6. 灰色の部分はパッケージの上面と底面のピン1の位置の参考に過ぎない

## 改訂履歴

| REV | 日付    | 概要                                                                                                                   | ページ番号                 |

|-----|-------|----------------------------------------------------------------------------------------------------------------------|-----------------------|

| A   | 03/16 | Hグレード・オプションの追加。<br>入力電流制限について条件およびNote 9を明示。<br>$V_{MID}$ のバッファ電流、バックアップ時間、充電バランスの曲線の軸ラベルを変更。<br>1.8V/300mA出力の回路を向上。 | 2、4<br>4<br>8、9<br>27 |

## 標準的応用例

自律的バックアップおよび充電アプリケーション(公称:3.6V、バックアップ電圧:3.2V)

## 関連製品

| 製品番号                                | 説明                                                           | 注釈                                                                                                                                         |

|-------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| LTC4040                             | 2.5A バッテリ・バックアップ・パワーマネージャ                                    | 昇圧バックアップ電源および降圧バッテリ・チャージャ、3.2Vのバッテリから2.5Aのバックアップ電源を得るための6.5Aスイッチ、バックアップ・モードへの切れ目のない自動切り替え                                                  |

| LTC3226                             | バックアップPowerPath™コントローラを内蔵した2セル・スーパー・キャパシタ・チャージャ              | 1×2×自動セル・バランスング付きマルチモード・チャージポンプ・スーパー・キャパシタ・チャージャ。<br>2A LDO バックアップ電源を内蔵(CPOとV <sub>OUT</sub> の間)。メイン/バックアップの自動切り替え、3mm×3mm QFN-16パッケージ     |

| LTC3625/<br>LTC3625-1               | 自動セル・バランスング付き、1A 高効率2セル・スーパー・キャパシタ・チャージャ                     | 直列に接続された2個のスーパー・キャパシタを高効率で昇圧/降圧充電、自動セル・バランスング。プログラム可能な充電電流:最大500mA(1個のインダクタ)、1A(2個のインダクタ)、3mm×4mm DFN-12パッケージ                              |

| LTC3128                             | 入力電流制限精度の高い3A モノリック昇降圧スーパー・キャパシタ・チャージャ/バランサ                  | 3Aまでプログラム可能な高精度(±2%)平均入力電流制限、アクティブな充電バランス調整、1個または2個のコンデンサを充電、V <sub>IN</sub> :1.73V～5.5V、V <sub>OUT</sub> :1.8V～5.5V                       |

| LTC3350                             | 大電流スーパー・キャパシタ・バックアップ・コントローラ/システム・モニタ                         | 最大4個の直列スーパー・キャパシタを同期整流式降圧モードで定電流/定電圧充電 V <sub>IN</sub> :4.5V～35V、システムの電圧/電流、容量、ESRをモニタする14ビットADC、アクティブ・バランサ内蔵、38ピン 5mm×7mm QFNパッケージ        |

| LTC4425                             | 電流制限付き理想ダイオードとV/Iモニタを備えたリニア・スーパー・キャパシタ・チャージャ                 | 2セルの直列スーパー・キャパシタ・スタックを充電する定電流/定電圧リニア・チャージャ、充電電流:2A、自動セル・バランスング、静止電流:20μA                                                                   |

| LTC3127                             | 入力電流制限をプログラム可能な1A 昇降圧DC/DCコンバータ                              | プログラム可能な±4% 精度の平均入力電流制限(0.2A～1A)、入力電圧範囲:1.8V～5.5V、出力電圧範囲:1.8V～5.25V                                                                        |

| LTC3125                             | 入力電流制限を調整可能な1.2A(I <sub>OUT</sub> )、1.6MHz 同期整流式昇圧DC/DCコンバータ | 94%の効率、V <sub>IN</sub> :1.8V～5.5V、V <sub>OUT</sub> (MAX) = 5.25V、I <sub>Q</sub> = 15μA、I <sub>SD</sub> < 1μA、2mm×3mm DFN-8パッケージ            |

| LTC3441/<br>LTC3441-2/<br>LTC3441-3 | I <sub>OUT</sub> が1.2Aの2MHz 同期整流式昇降圧DC/DCコンバータ               | 95%の効率、V <sub>IN</sub> :2.4V～5.5V、V <sub>OUT</sub> :2.4V～5.25V、I <sub>Q</sub> = 50μA、I <sub>SD</sub> < 1μA、3mm×4mm DFN-12パッケージ             |

| LTC3113                             | 低ノイズの3A 昇降圧DC/DCコンバータ                                        | 96%の効率、V <sub>IN</sub> :1.8V～5.5V、V <sub>OUT</sub> :1.8V～5.5V、I <sub>Q</sub> = 40μA、I <sub>SD</sub> < 1μA、4mm×5mm DFN-16および20ピン TSSOPパッケージ |

| LTC3355                             | SCAPチャージャとバックアップ・レギュレータを内蔵した20V/1A 降圧DC/DCシステム               | V <sub>IN</sub> の電圧範囲:3V～20V、V <sub>OUT</sub> の電圧範囲:2.7V～5V、1A電流モード降圧メイン・レギュレータ、最小0.5Vの1個のスーパー・キャパシタを電源とする5A 昇圧・バックアップ・レギュレータ、過電圧保護        |

| LTC3643                             | 2A 双方向電力バックアップ電源                                             | 双方の同期整流式昇圧コンデンサ・チャージャ/システム・バックアップ用降圧レギュレータ、広い入力電圧範囲:3V～17V、コンデンサの電圧:最大40V、コンデンサの充電電流:最大2A、高さの低い24ピン 3mm×5mm QFNパッケージ                       |

3110fa