# デュアル、シリアル18ビット SoftSpan電流出力D/Aコンバータ

## 特長

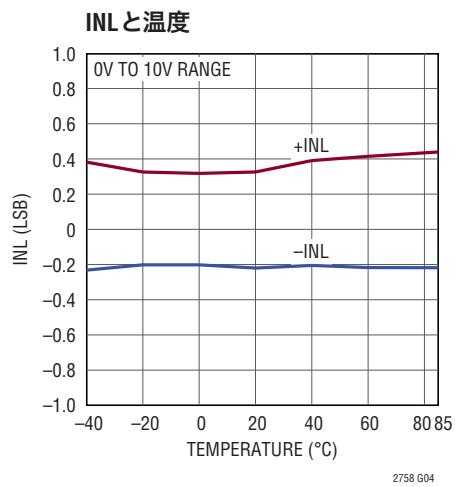

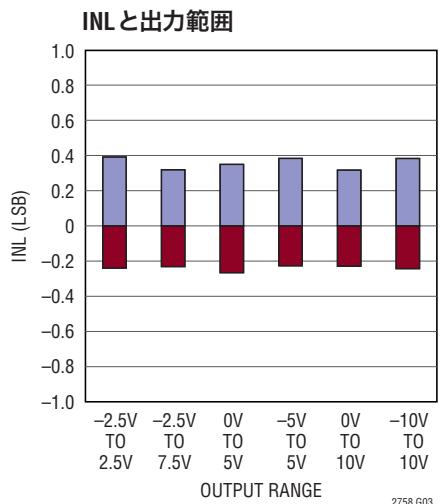

- 18ビットINL誤差の最大値:全温度範囲で $\pm 1\text{LSB}$

- 6つの出力範囲をプログラムまたはピン結線で設定:

0V~5V, 0V~10V, -2.5V~7.5V,  $\pm 2.5\text{V}$ ,  $\pm 5\text{V}$ ,  $\pm 10\text{V}$

- 全温度範囲で単調性を保証

- グリッチ・インパルス:0.4nV·s (3V)、2nV·s (5V)

- 18ビットのセトリング時間:2.1μs

- 単電源動作:2.7V~5.5V

- 電源電流:最大1μA

- 電圧制御によるオフセットと利得の調整

- すべてのレジスタの読み出しが可能なシリアル・インターフェース

- 出力範囲に関係なく出力を0Vにクリアおよびパワーオン・リセット

- 48ピン7mm×7mm LQFPパッケージ

## アプリケーション

- 計測器

- 医療機器

- 自動テスト装置

- プロセス制御および産業用自動制御

## 標準的応用例

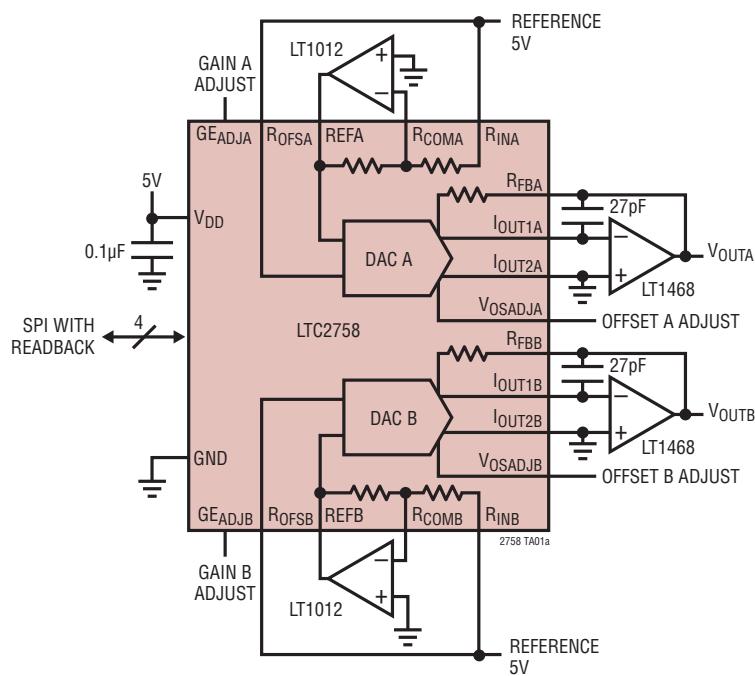

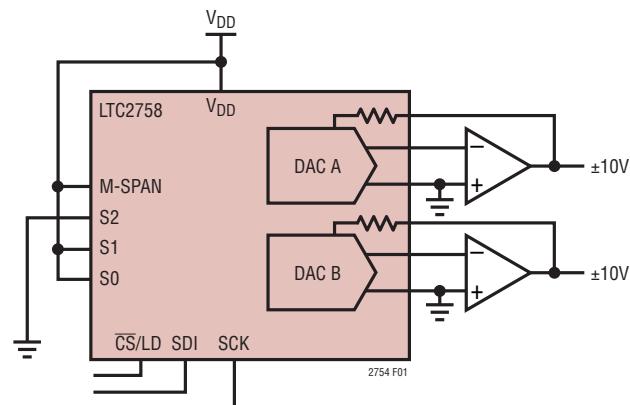

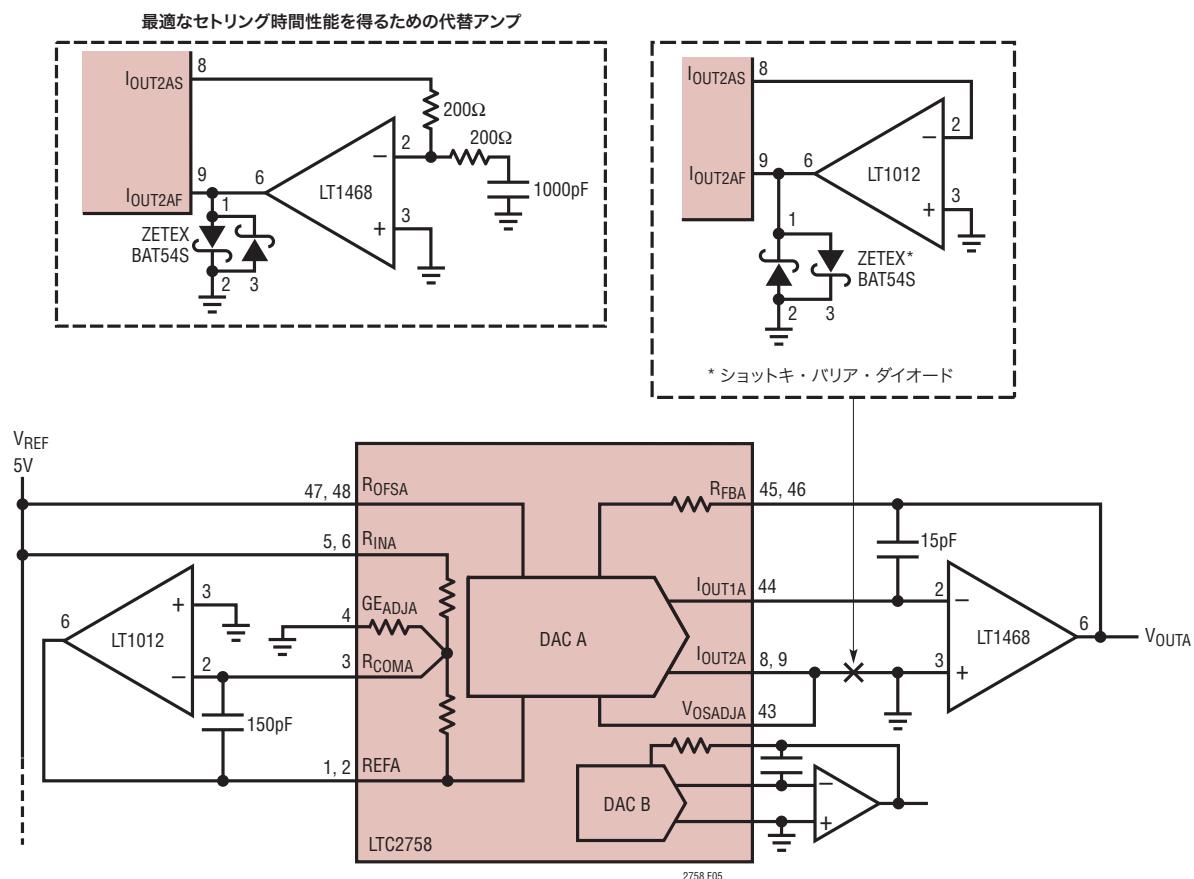

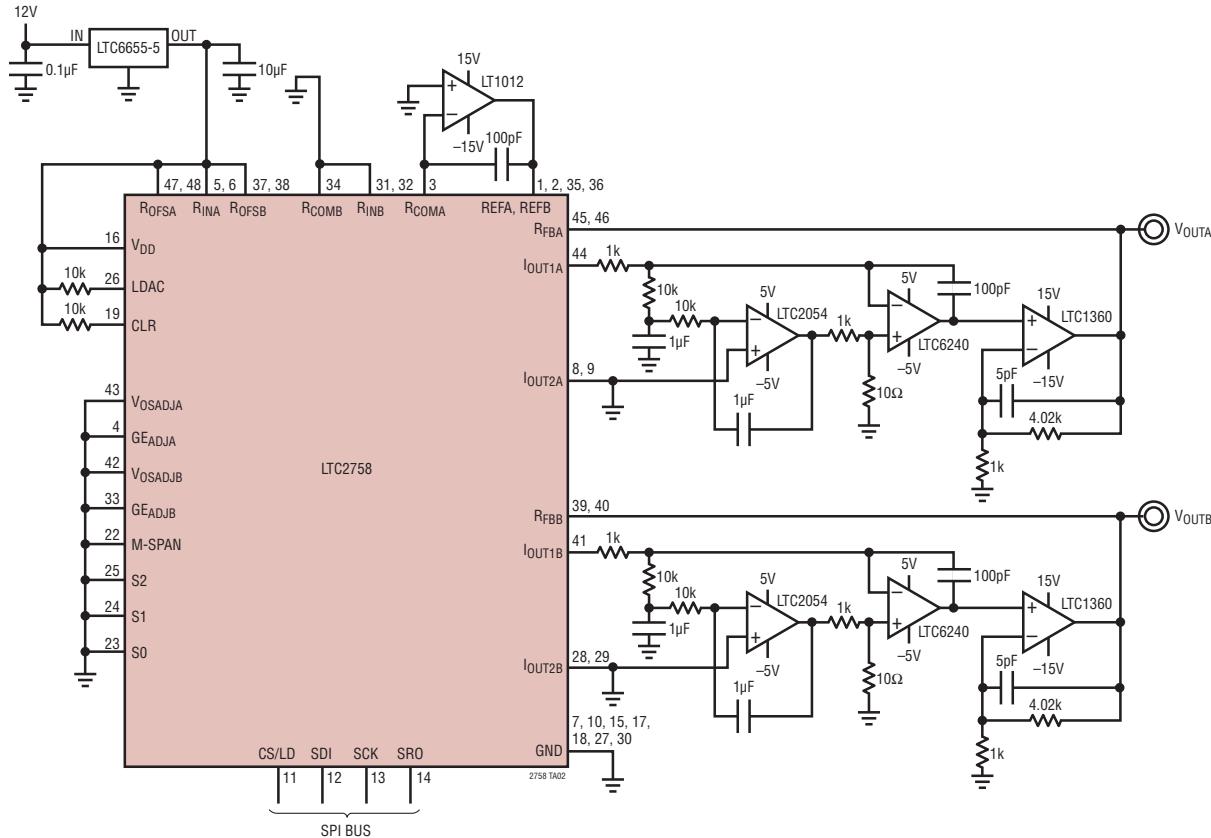

### 出力範囲をソフトウェアで選択可能なデュアル18ビットV<sub>OUT</sub> DAC

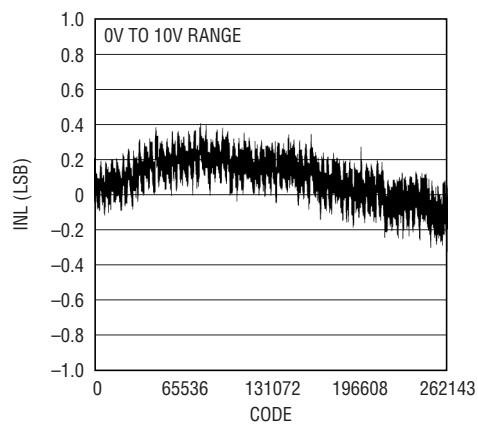

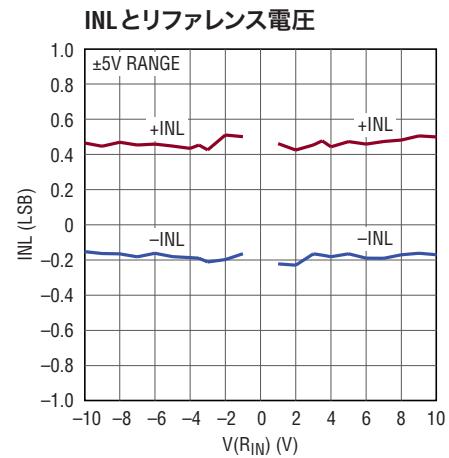

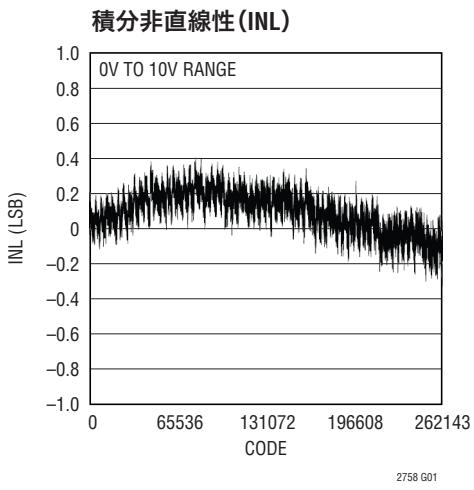

### LTC2758の積分非直線性

2758fa

# LTC2758

## 絶対最大定格

(Note 1, 2)

|I<sub>OUT1X</sub>、|I<sub>OUT2X</sub>からGND ..... ±0.3V

R<sub>INX</sub>、R<sub>COMX</sub>、REFX、R<sub>FBX</sub>、R<sub>OFSX</sub>、V<sub>OSADJX</sub>、

G<sub>EADJX</sub>からGND ..... ±18V

V<sub>DD</sub>からGND ..... -0.3V～7V

デジタル入力からGND ..... -0.3V～7V

デジタル出力からGND ..... -0.3V～V<sub>DD</sub>+0.3V(最大7V)

動作温度範囲

LTC2758C ..... 0°C～70°C

LTC2758I ..... -40°C～85°C

最大接合部温度 ..... 150°C

保存温度範囲 ..... -65°C～150°C

リード温度(半田付け、10秒) ..... 300°C

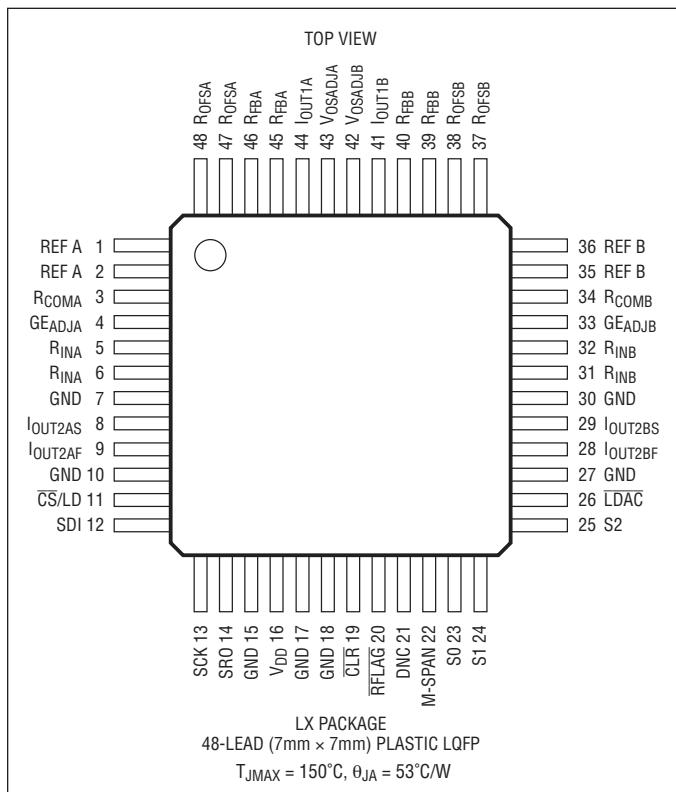

## ピン配置

## 発注情報

| 無鉛仕上げ           | 製品マーキング*  | パッケージ                            | 温度範囲          |

|-----------------|-----------|----------------------------------|---------------|

| LTC2758BCLX#PBF | LTC2758LX | 48-Lead (7mm x 7mm) Plastic LQFP | 0°C to 70°C   |

| LTC2758BILX#PBF | LTC2758LX | 48-Lead (7mm x 7mm) Plastic LQFP | -40°C to 85°C |

| LTC2758ACLX#PBF | LTC2758LX | 48-Lead (7mm x 7mm) Plastic LQFP | 0°C to 70°C   |

| LTC2758AILX#PBF | LTC2758LX | 48-Lead (7mm x 7mm) Plastic LQFP | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

この製品はトレイでのみ供給されます。詳細については、<http://www.linear-tech.co.jp/packaging/> をご覧ください。

## 電気的特性

注記がない限り、 $V_{DD} = 5V$ 、 $V(R_{INX}) = 5V$ 。●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ C$  の値。

| SYMBOL           | PARAMETER                            | CONDITIONS                                         | LTC2758B |       |            | LTC2758A |              |            | UNITS          |

|------------------|--------------------------------------|----------------------------------------------------|----------|-------|------------|----------|--------------|------------|----------------|

|                  |                                      |                                                    | MIN      | TYP   | MAX        | MIN      | TYP          | MAX        |                |

| <b>静特性</b>       |                                      |                                                    |          |       |            |          |              |            |                |

|                  | Resolution                           |                                                    | ●        | 18    |            | 18       |              |            | Bits           |

|                  | Monotonicity                         |                                                    | ●        | 18    |            | 18       |              |            | Bits           |

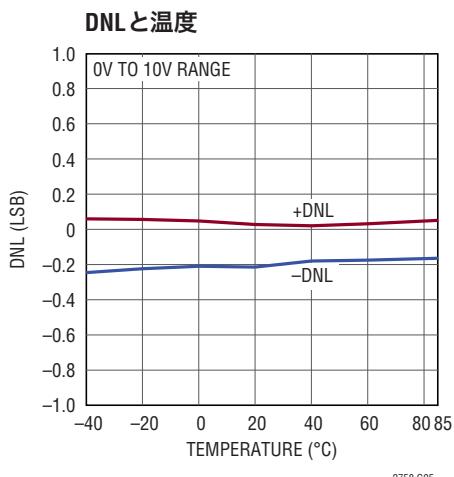

| DNL              | Differential Nonlinearity            |                                                    | ●        |       | ±1         |          | ±0.2         | ±1         | LSB            |

| INL              | Integral Nonlinearity                |                                                    | ●        |       | ±2         |          | ±0.5         | ±1         | LSB            |

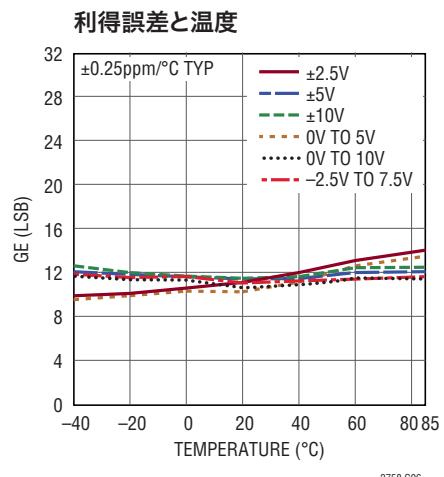

| GE               | Gain Error                           | All Output Ranges                                  | ●        |       | ±48        |          | ±6           | ±32        | LSB            |

|                  | Gain Error Temperature Coefficient   | $\Delta GAIN/\Delta TEMP$                          |          |       | ±0.25      |          | ±0.25        |            | ppm/°C         |

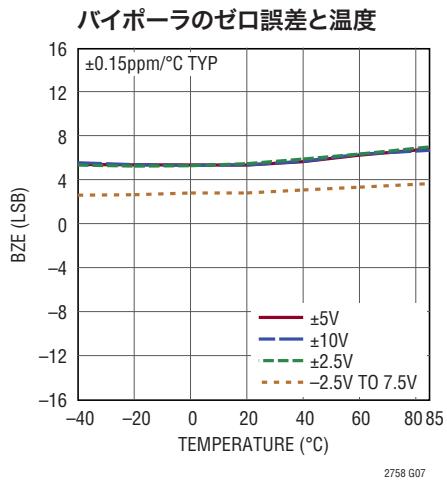

| BZE              | Bipolar Zero Error                   | All Bipolar Ranges                                 | ●        |       | ±36        |          | ±1           | ±24        | LSB            |

|                  | Bipolar Zero Temperature Coefficient |                                                    |          |       | ±0.2       |          | ±0.2         |            | ppm/°C         |

|                  | Unipolar Zero-Scale Error            | Unipolar Ranges (Note 3)                           | ●        | ±0.03 | ±3.2       |          | ±0.03        | ±3.2       | LSB            |

| PSR              | Power Supply Rejection               | $V_{DD} = 5V, \pm 10\%$<br>$V_{DD} = 3V, \pm 10\%$ | ●<br>●   |       | ±1.6<br>±4 |          | ±0.1<br>±0.3 | ±0.8<br>±2 | LSB/V<br>LSB/V |

| I <sub>LKG</sub> | I <sub>OUT1</sub> Leakage Current    | $T_A = 25^\circ C$<br>$T_{MIN}$ to $T_{MAX}$       | ●        | ±0.05 | ±2<br>±5   |          | ±0.05        | ±2<br>±5   | nA<br>nA       |

注記がない限り、 $V_{DD} = 5V$ 、 $V(R_{INX}) = 5V$ 。●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ C$  の値。

| SYMBOL              | PARAMETER                     | CONDITIONS               | MIN |      |      | TYP |     |     | MAX |     |     | UNITS |

|---------------------|-------------------------------|--------------------------|-----|------|------|-----|-----|-----|-----|-----|-----|-------|

|                     |                               |                          | MIN | TYP  | MAX  | MIN | TYP | MAX | MIN | TYP | MAX |       |

| <b>アナログ・ピン</b>      |                               |                          |     |      |      |     |     |     |     |     |     |       |

|                     | Reference Inverting Resistors | (Note 4)                 | ●   | 16   | 20   |     |     |     |     |     |     | kΩ    |

| R <sub>REF</sub>    | DAC Input Resistance          | (Note 5, 6)              | ●   | 8    | 10   |     |     |     |     |     |     | kΩ    |

| R <sub>FB</sub>     | Feedback Resistors            | (Note 6)                 | ●   | 8    | 10   |     |     |     |     |     |     | kΩ    |

| R <sub>OFS</sub>    | Bipolar Offset Resistors      | (Note 6)                 | ●   | 16   | 20   |     |     |     |     |     |     | kΩ    |

| R <sub>VOSADJ</sub> | Offset Adjust Resistors       |                          | ●   | 1024 | 1280 |     |     |     |     |     |     | kΩ    |

| R <sub>GEADJ</sub>  | Gain Adjust Resistors         |                          | ●   | 2048 | 2560 |     |     |     |     |     |     | kΩ    |

| C <sub>OUT1</sub>   | Output Capacitance            | Full-Scale<br>Zero-Scale |     |      |      | 90  |     |     |     |     |     | pF    |

## ダイナミック性能

|     |                                  |                                                              |  |  |      |  |  |  |  |  |  |              |

|-----|----------------------------------|--------------------------------------------------------------|--|--|------|--|--|--|--|--|--|--------------|

|     | Output Settling Time             | Span Code = 0000, 10V Step. To $\pm 0.0004\%$ FS<br>(Note 7) |  |  | 2.1  |  |  |  |  |  |  | μs           |

|     | Glitch Impulse                   | $V_{DD} = 5V$ (Note 8)<br>$V_{DD} = 3V$ (Note 8)             |  |  | 2    |  |  |  |  |  |  | nV·s<br>nV·s |

|     | Digital-to-Analog Glitch Impulse | $V_{DD} = 5V$ (Note 9)<br>$V_{DD} = 3V$ (Note 9)             |  |  | 2.6  |  |  |  |  |  |  | nV·s<br>nV·s |

|     | Reference Multiplying BW         | 0V to 5V Range,<br>Code = Full Scale, -3dB Bandwidth         |  |  | 1    |  |  |  |  |  |  | MHz          |

|     | Multiplying Feedthrough Error    | 0V to 5V Range, $V_{REF} = \pm 10V$ , 10kHz<br>Sine Wave     |  |  | 0.4  |  |  |  |  |  |  | mV           |

|     | Analog Crosstalk                 | (Note 10)                                                    |  |  | -109 |  |  |  |  |  |  | dB           |

| THD | Total Harmonic Distortion        | (Note 11) Multiplying                                        |  |  | -110 |  |  |  |  |  |  | dB           |

|     | Output Noise Voltage Density     | (Note 12) at I <sub>OUT1</sub>                               |  |  | 13   |  |  |  |  |  |  | nV/√Hz       |

## 電気的特性

注記がない限り、 $V_{DD} = 5V$ 、 $V(R_{INX}) = 5V$ 。●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ C$ での値。

| SYMBOL        | PARAMETER                  | CONDITIONS                                                | MIN    | TYP            | MAX        | UNITS   |

|---------------|----------------------------|-----------------------------------------------------------|--------|----------------|------------|---------|

| <b>電源</b>     |                            |                                                           |        |                |            |         |

| $V_{DD}$      | Supply Voltage             |                                                           | ●      | 2.7            | 5.5        | V       |

| $I_{DD}$      | $V_{DD}$ Supply Current    | Digital Inputs = 0V or $V_{DD}$                           | ●      | 0.5            | 2          | $\mu A$ |

| <b>デジタル入力</b> |                            |                                                           |        |                |            |         |

| $V_{IH}$      | Digital Input High Voltage | $3.3V \leq V_{DD} \leq 5.5V$<br>$2.7V \leq V_{DD} < 3.3V$ | ●<br>● | 2.4<br>2       |            | V       |

| $V_{IL}$      | Digital Input Low Voltage  | $4.5V \leq V_{DD} \leq 5.5V$<br>$2.7V \leq V_{DD} < 4.5V$ | ●<br>● |                | 0.8<br>0.6 | V       |

|               | Hysteresis Voltage         |                                                           |        | 0.1            |            | V       |

| $I_{IN}$      | Digital Input Current      | $V_{IN} = GND$ to $V_{DD}$                                | ●      |                | $\pm 1$    | $\mu A$ |

| $C_{IN}$      | Digital Input Capacitance  | $V_{IN} = 0V$ (Note 13)                                   | ●      |                | 6          | pF      |

| <b>デジタル出力</b> |                            |                                                           |        |                |            |         |

| $V_{OH}$      | $I_{OH} = 200\mu A$        | $2.7V \leq V_{DD} \leq 5.5V$                              | ●      | $V_{DD} - 0.4$ |            | V       |

| $V_{OL}$      | $I_{OH} = 200\mu A$        | $2.7V \leq V_{DD} \leq 5.5V$                              | ●      |                | 0.4        | V       |

## タイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ C$ での値。

| SYMBOL                                      | PARAMETER                                | CONDITIONS                  | MIN | TYP | MAX | UNITS |

|---------------------------------------------|------------------------------------------|-----------------------------|-----|-----|-----|-------|

| <b><math>V_{DD} = 4.5V \sim 5.5V</math></b> |                                          |                             |     |     |     |       |

| $t_1$                                       | SDI Valid to SCK Set-Up                  |                             | ●   | 7   |     | ns    |

| $t_2$                                       | SDI Valid to SCK Hold                    |                             | ●   | 7   |     | ns    |

| $t_3$                                       | SCK High Time                            |                             | ●   | 11  |     | ns    |

| $t_4$                                       | SCK Low Time                             |                             | ●   | 11  |     | ns    |

| $t_5$                                       | $\bar{CS}/LD$ Pulse Width                |                             | ●   | 9   |     | ns    |

| $t_6$                                       | LSB SCK High to $\bar{CS}/LD$ High       |                             | ●   | 4   |     | ns    |

| $t_7$                                       | $\bar{CS}/LD$ Low to SCK Positive Edge   |                             | ●   | 4   |     | ns    |

| $t_8$                                       | $\bar{CS}/LD$ High to SCK Positive Edge  |                             | ●   | 4   |     | ns    |

| $t_9$                                       | SRO Propagation Delay                    | $C_{LOAD} = 10pF$           | ●   |     | 18  | ns    |

| $t_{10}$                                    | $\bar{CLR}$ Pulse Width Low              |                             | ●   | 36  |     | ns    |

| $t_{11}$                                    | $\bar{LDA}$ Pulse Width Low              |                             | ●   | 15  |     | ns    |

| $t_{12}$                                    | $\bar{CLR}$ Low to $\bar{RFLAG}$ Low     | $C_{LOAD} = 10pF$ (Note 13) | ●   |     | 50  | ns    |

| $t_{13}$                                    | $\bar{CS}/LD$ High to $\bar{RFLAG}$ High | $C_{LOAD} = 10pF$ (Note 13) | ●   |     | 40  | ns    |

|                                             | SCK Frequency                            | 50% Duty Cycle (Note 14)    | ●   |     | 40  | MHz   |

## **$V_{DD} = 2.7V \sim 3.3V$**

|       |                           |              |   |    |  |    |

|-------|---------------------------|--------------|---|----|--|----|

| $t_1$ | SDI Valid to SCK Set-Up   |              | ● | 9  |  | ns |

| $t_2$ | SDI Valid to SCK Hold     | (Note 13)    | ● | 9  |  | ns |

| $t_3$ | SCK High Time             | $C_L = 10pF$ | ● | 15 |  | ns |

| $t_4$ | SCK Low Time              |              | ● | 15 |  | ns |

| $t_5$ | $\bar{CS}/LD$ Pulse Width |              | ● | 12 |  | ns |

## タイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

| SYMBOL   | PARAMETER                       | CONDITIONS                         | MIN | TYP | MAX | UNITS |

|----------|---------------------------------|------------------------------------|-----|-----|-----|-------|

| $t_6$    | LSB SCK High to CS/LD High      |                                    | ●   | 5   |     | ns    |

| $t_7$    | CS/LD Low to SCK Positive Edge  |                                    | ●   | 5   |     | ns    |

| $t_8$    | CS/LD High to SCK Positive Edge |                                    | ●   | 5   |     | ns    |

| $t_9$    | SRO Propagation Delay           | $C_{LOAD} = 10\text{pF}$           | ●   |     | 26  | ns    |

| $t_{10}$ | CLR Pulse Width Low             |                                    | ●   | 60  |     | ns    |

| $t_{11}$ | LDA $\bar{C}$ Pulse Width Low   |                                    | ●   | 20  |     | ns    |

| $t_{12}$ | CLR Low to RFLAG Low            | $C_{LOAD} = 10\text{pF}$ (Note 13) | ●   |     | 70  | ns    |

| $t_{13}$ | CS/LD High to RFLAG High        | $C_{LOAD} = 10\text{pF}$ (Note 13) | ●   |     | 60  | ns    |

|          | SCK Frequency                   | 50% Duty Cycle (Note 14)           | ●   |     | 25  | MHz   |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** 規定された最大動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なう恐れがある。

**Note 3:** 帰還抵抗および $I_{OUT1}$ 漏れ電流の仕様から計算。製造時のテストは行われない。ほとんどのアプリケーションで、ユニポーラのゼロスケール誤差は出力アンプからの寄与によって支配される。

**Note 4:** 入力抵抗は $R_{INX}$ から $R_{COMX}$ まで測定される。帰還抵抗は $R_{COMX}$ から $REFX$ まで測定される。

**Note 5:** DAC入力抵抗はコードに依存しない。

**Note 6:** 規定されたピンから $I_{OUT1X}$ および規定されたピンから $I_{OUT2X}$ への抵抗の並列組み合わせ。

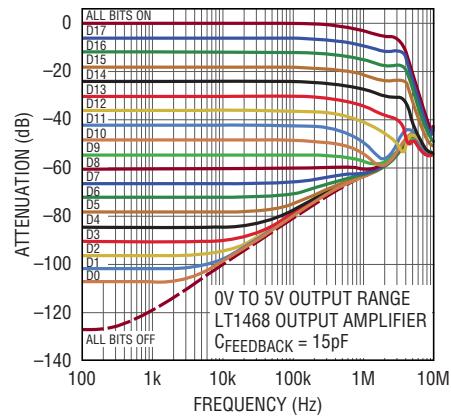

**Note 7:**  $C_{FEEDBACK} = 27\text{pF}$ でLT1468を使う。 $1.8\mu\text{s}$ の $\pm 0.0004\%$ セトリング時間は、個別に時定数を最適化して達成することができる。アプリケーション・ノート120「1ppm Settling Time Measurement for a Monolithic 18-Bit DAC (18ビットのモノリシックDACに対する1ppmでのセトリング時間測定)」を参照。

**Note 8:** メジャー・キャリーの遷移で測定される(0V～5V範囲)。出力アンプ: LT1468、 $C_{FB} = 50\text{pF}$ 。

**Note 9:** フルスケールの遷移、REF = 0V。

**Note 10:** Analog Crosstalk(アナログ・クロストーク)はdBで表したAC電圧比 $V_{OUTB}/V_{REFA}$ として定義されている。REFBは接地され、DAC Bは0V～5Vのスパンおよびゼロスケール、ミッドスケールまたはフルスケールのコードに設定される。 $V_{REFA}$ は3VRMS、1kHzの正弦波である。

**Note 11:** REF = 1kHzで6VRMS。0V～5V範囲。DACのコード = FS。出力アンプ = LT1468。

**Note 12:**  $V_n = \sqrt{4KTR_B}$ から計算。ここで、 $K = 1.38E-23 \text{ J/K}$ (ボルツマン定数)、 $R$  = 抵抗( $\Omega$ )、 $T$  = 温度( $^\circ\text{K}$ )、 $B$  = 帯域幅(Hz)。0V～5V範囲。ゼロスケール、ミッドスケール、またはフルスケール。

**Note 13:** 設計によって保証されているが、製造時にはテストされない。

**Note 14:** SROを使用するとき、最大SCK周波数 $f_{MAX}$ はSROの伝播遅延 $t_9$ によって次のように制限される。

$$f_{MAX} = \left( \frac{1}{2(t_9 + t_S)} \right) \quad \text{ここで、} t_S \text{は受信側デバイスのセットアップ時間。}$$

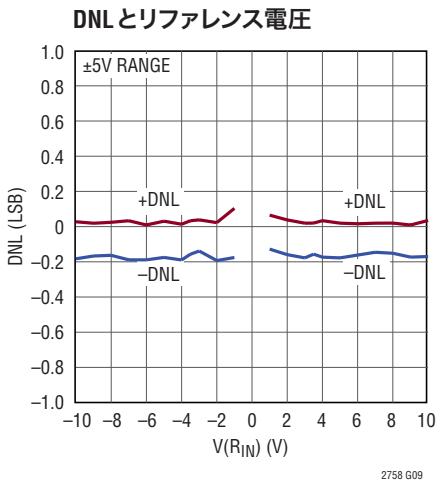

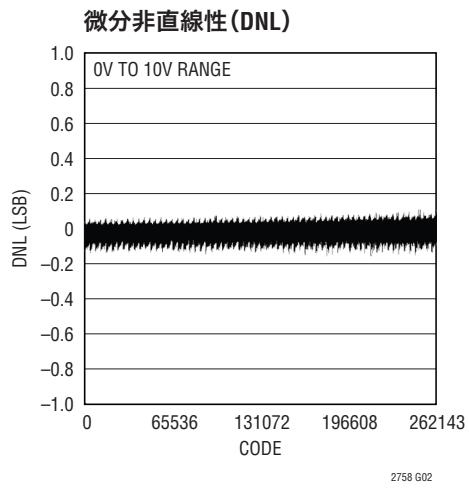

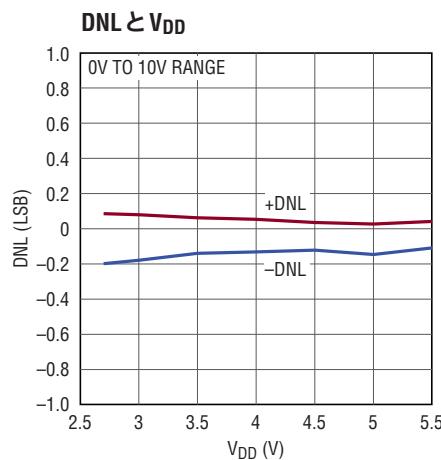

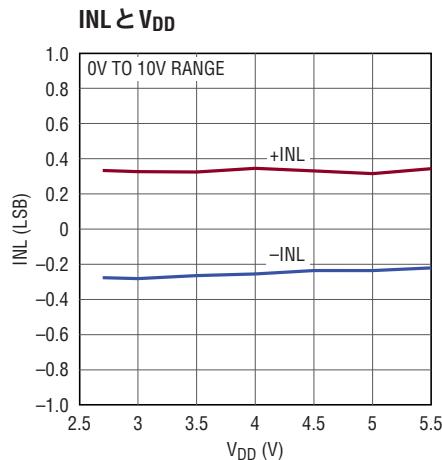

## 標準的性能特性

注記がない限り、 $V_{DD} = 5V$ 、 $V(R_{INX}) = 5V$ 、 $T_A = 25^\circ C$ 。

## 標準的性能特性

注記がない限り、 $V_{DD} = 5V$ 、 $V(R_{INX}) = 5V$ 、 $T_A = 25^\circ C$ 。

## 乗算周波数応答とデジタル・コード

## フルスケール・ステップのセトリング

LT1468 AMP;  $C_{FEEDBACK} = 20pF$

OV TO 10V STEP

$V_{REF} = -10V$ ; SPAN CODE = 0000

$t_{SETTLE} = 1.8\mu s$  to 0.0004% (18 BITS)

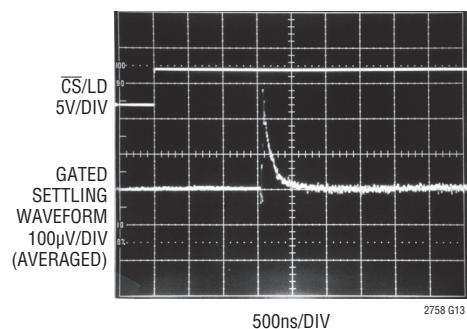

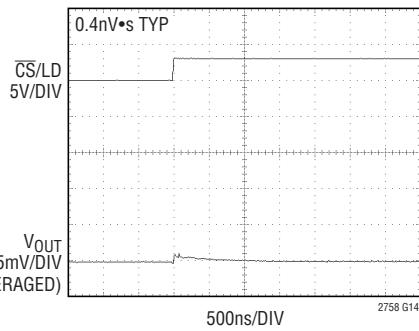

## ミッドスケール・グリッチ ( $V_{DD} = 3V$ )

0.4nV·s TYP

OV TO 5V RANGE

LT1468 OUTPUT AMPLIFIER

$C_{FEEDBACK} = 50pF$

RISING MAJOR CARRY TRANSITION.

FALLING TRANSITION IS SIMILAR OR BETTER.

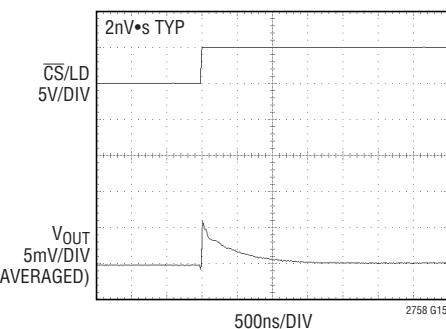

## ミッドスケール・グリッチ ( $V_{DD} = 5V$ )

2nV·s TYP

OV TO 5V RANGE

LT1468 OUTPUT AMPLIFIER

$C_{FEEDBACK} = 50pF$

RISING MAJOR CARRY TRANSITION.

FALLING TRANSITION IS SIMILAR OR BETTER.

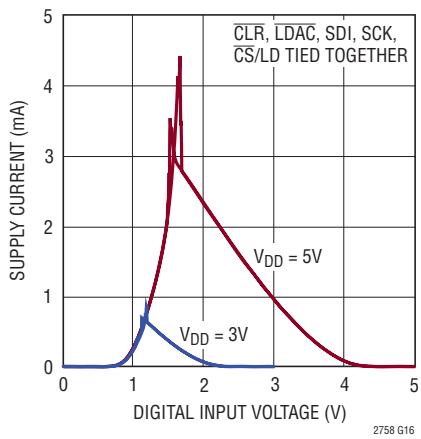

## 電源電流とロジック入力電圧

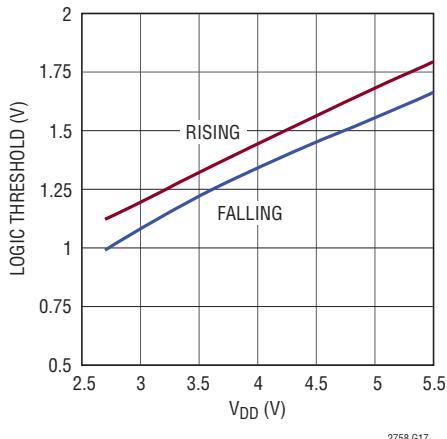

## ロジックしきい値と電源電圧

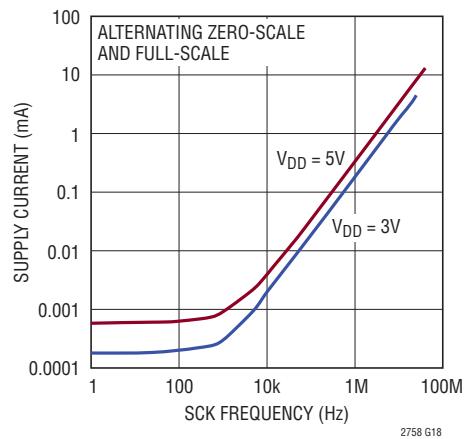

## 電源電流と更新周波数

## ピン機能

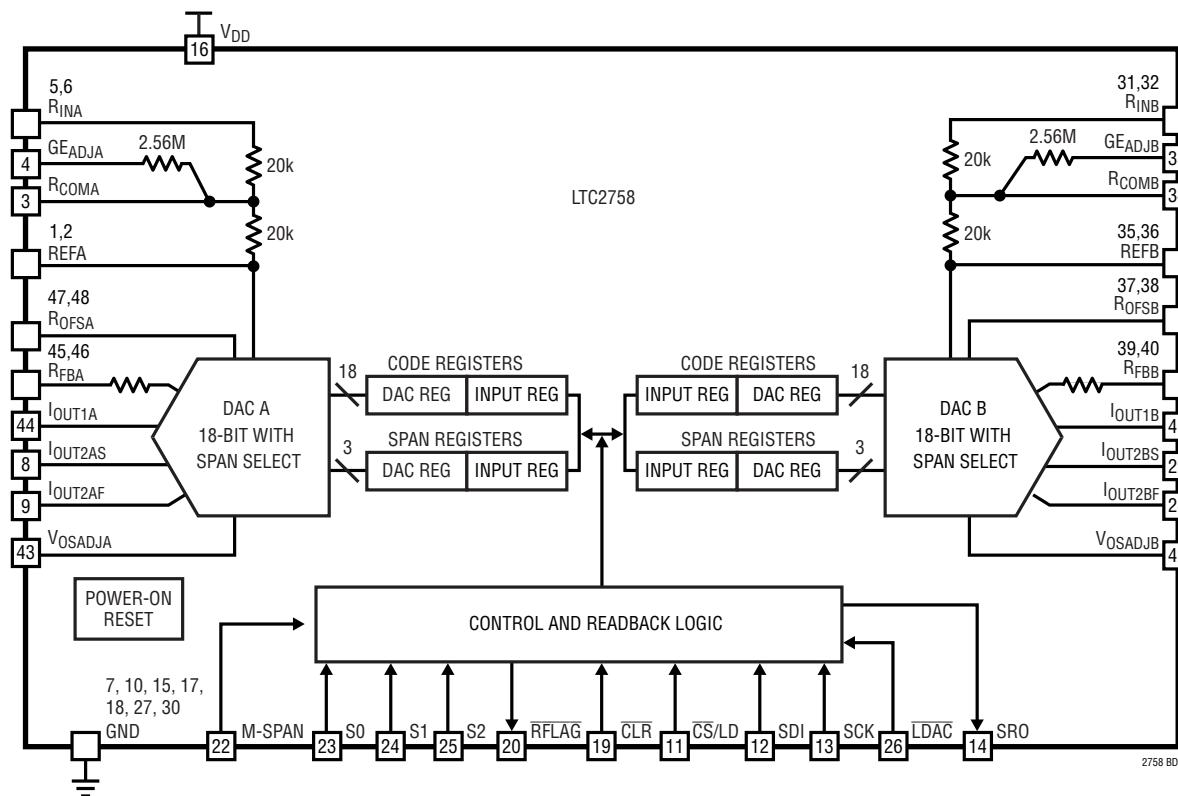

**REFA (ピン1、2)** : DAC A のリファレンスの反転アンプの帰還抵抗、および DAC A のリファレンス入力。20kの帰還抵抗が内部で REFA から R<sub>COMA</sub> に接続されています。通常動作では、このピンを DAC A のリファレンス反転アンプの出力に接続します（「標準的応用例」を参照）。標準 -5V ですが、±15V まで受け入れます。ピン1とピン2は内部で相互に短絡されています。

**R<sub>COMA</sub> (ピン3)** : DAC A のリファレンス・アンプの反転抵抗の仮想グランド・ポイント。20kのリファレンス反転抵抗が内部でそれぞれ R<sub>INA</sub> から R<sub>COMA</sub> および R<sub>COMA</sub> から REFA に接続されています（ブロック図を参照）。通常動作では、R<sub>COMA</sub> を外部リファレンス反転アンプの負入力に接続します（「標準的応用例」を参照）。

**G<sub>EADJA</sub> (ピン4)** : DAC A の利得調整ピン。この制御ピンを使って、利得誤差を除いたり、リファレンス誤差を補償することができます。LSB で表される利得の変化はどの出力範囲でも同じです。「動作」のセクションの「システムのオフセットおよび利得の調整」を参照してください。使用しない場合、グランドに接続します。

**R<sub>INA</sub> (ピン5、6)** : DAC A の外部リファレンス反転アンプの入力抵抗。20kの入力抵抗が内部で R<sub>INA</sub> から R<sub>COMA</sub> に接続されています。通常動作では、R<sub>INA</sub> を外部の正リファレンス電圧に接続します（「標準的応用例」を参照）。これらの精密整合抵抗セットのどちらかまたは両方（各セットは R<sub>INX</sub>、R<sub>COMX</sub> および R<sub>EFX</sub> で構成）を使って、正リファレンス電圧を反転し、DAC が必要とする負電圧を供給することができます。標準 5V ですが、±15V まで受け入れます。ピン5とピン6は内部で相互に短絡されています。

**GND (ピン7、10、15、17、18、27、30)** : グランド。グランドに接続します。

**I<sub>OUT2AS</sub>、I<sub>OUT2AF</sub> (ピン8、9)** : DAC A の電流出力のコンプリメントのセンス・ピンおよびフォース・ピン。クリーンな低インピーダンス経路を介してグランドに接続します。これらのピンは、ケルビンセンス・ペアとして、高精度グランド・バッファ・アンプと共に使用することができます（「アプリケーション情報」のセクションを参照）。

**CS/LD (ピン11)** : 同期チップセレクトおよびロード入力ピン。

**SDI (ピン12)** : シリアル・データ入力。データは、CS/LD が“L”的ときシリアル・クロック（SCK）の立ち上がりエッジで取り込まれます。

**SCK (ピン13)** : シリアル・クロック入力。

**SRO (ピン14)** : シリアル読み出し出力。SCK の立ち下がりエッ

ジでデータをクロックで送出します。読み出されるデータは、最後のアドレスビット A0 がクロックで取り込まれた後、クロックで送出され始めます。SRO はデバイスが選択されているとき（つまり、CS/LD が“L”的とき）だけアクティブな出力です。それ以外は、他のデバイスがバスを制御できるように、SRO は高インピーダンス出力になります。

**V<sub>DD</sub> (ピン16)** : 正電源入力 : 2.7V ≤ V<sub>DD</sub> ≤ 5.5V。0.1μF の低 ESR セラミック・コンデンサを使ってグランドにバイパスします。

**CLR (ピン19)** : 非同期クリア入力。このピンが“L”的とき、すべての DAC レジスタ（コードとスパンの両方）が 0 にクリアされます。DAC のすべての出力が 0V にクリアされます。

**RFLAG (ピン20)** : リセット・フラグ出力。パワーオン・リセットまたはクリアのイベントが生じると、アクティブ“L”的出力がアサートされます。更新コマンドが実行されると“H”に戻ります。

**DNC (ピン21)** : 接続しないでください。

**M-SPAN (ピン22)** : マニュアル・スパン制御ピン。M-SPAN は、ピン S2、S1 および S0（ピン 25、24 および 23）と連携して使われ、すべての DAC の単一固定出力範囲の動作を構成設定します。デバイスをマニュアル・スパンで使用するように構成設定するには、M-SPAN を直接 V<sub>DD</sub> に接続します。次いで、DAC の出力範囲を（SPI ポートではなく）ピン S2、S1 および S0 のハードウェア・ピン・ストラッピングによって設定します。書き込みと更新のコマンドはアクティブ出力スパンには影響を与えません。

デバイスを SoftSpan で使用するように構成設定するには、M-SPAN を直接 GND に接続します。これで、出力範囲は SPI ポートを介して個別に制御可能です。ピン S2、S1 および S0 は影響を与えません。

「動作」のセクションの「マニュアル・スパン構成」を参照してください。M-SPAN は GND（SoftSpan 構成）または V<sub>DD</sub>（マニュアル・スパン構成）のどちらかに直接接続する必要があります。

**S0 (ピン23)** : スパン・ビット 0 の入力。マニュアル・スパン・モード（M-SPAN を V<sub>DD</sub> に接続）で、ピン S0、S1 および S2 をピンストラップして、すべての DAC に単一の固定出力範囲を選択します。これらのピンは、使用しなくとも、GND または V<sub>DD</sub> に接続します。

**S1 (ピン24)** : スパン・ビット 1 の入力。マニュアル・スパン・モード（M-SPAN を V<sub>DD</sub> に接続）で、ピン S0、S1 および S2 をピンストラップして、すべての DAC に単一の固定出力範囲を選択します。これらのピンは、使用しなくとも、GND または V<sub>DD</sub> に接続します。

## ピン機能

**S2(ピン25)**: スパン・ビット2の入力。マニュアル・スパン・モード(M-SPANをV<sub>DD</sub>に接続)で、ピンS0、S1およびS2をピンスラップして、すべてのDACに单一の固定出力範囲を選択します。これらのピンは、使用しなくても、GNDまたはV<sub>DD</sub>に接続します。

**LDAC(ピン26)**: 非同期DAC負荷入力。 $\overline{LDAC}$ がロジック“L”的とき、すべてのDACが更新されます( $\overline{CS/LD}$ は“H”でなければなりません)。

**I<sub>OUT2BF</sub>、I<sub>OUT2BS</sub>(ピン28、29)**: DAC Bの電流出力のコンプリメントのフォース・ピンおよびセンス・ピン。クリーンな低インピーダンス経路を介してグランドに接続します。これらのピンは、ケルビンセンス・ペアとして、高精度グランド・バッファ・アンプと共に使用することができます(「標準的応用例」のセクションを参照)。

**R<sub>INB</sub>(ピン31、32)**: DAC Bの外部リファレンス反転アンプの入力抵抗。20kの入力抵抗が内部でR<sub>INB</sub>からR<sub>COMB</sub>に接続されています。通常動作では、R<sub>INB</sub>を外部の正リファレンス電圧に接続します(「標準的応用例」を参照)。これらの精密整合抵抗セットのどちらかまたは両方(各セットはR<sub>INX</sub>、R<sub>COMX</sub>およびREFXで構成)を使って、正リファレンス電圧を反転し、DACが必要とする負電圧を供給することができます。標準5Vですが、±15Vまで受け入れます。ピン31とピン32は内部で相互に短絡されています。

**G<sub>EADJB</sub>(ピン33)**: DAC Bの利得調整ピン。この制御ピンを使って、利得誤差を除いたり、リファレンス誤差を補償することができます。LSBで表される利得の変化はどの出力範囲でも同じです。「動作」のセクションの「システムのオフセットおよび利得の調整」を参照してください。使用しない場合、グランドに接続します。

**R<sub>COMB</sub>(ピン34)**: DAC Bのリファレンス・アンプの反転抵抗の仮想グランド・ポイント。20kのリファレンス反転抵抗が内部でそれぞれR<sub>INB</sub>からR<sub>COMB</sub>およびR<sub>COMB</sub>からREFBに接続されています(ブロック図を参照)。通常動作では、R<sub>COMB</sub>を外部リファレンス反転アンプの負入力に接続します(「標準的応用例」を参照)。

**REFB(ピン35、36)**: DAC Bのリファレンスの反転アンプの帰還抵抗、およびDAC Bのリファレンス入力。20kの帰還抵抗が内部でREFBからR<sub>COMB</sub>に接続されています。通常動作では、このピンをDAC Bのリファレンス反転アンプの出力に接続します(「標準的応用例」を参照)。標準-5Vですが、±15Vまで受け入れます。ピン35とピン36は内部で相互に短絡されています。

**R<sub>OFSB</sub>(ピン37、38)**: DAC Bのバイポーラ・オフセット抵抗。これらのピンはバイポーラ・スパンの出力電圧範囲を変換します。±15Vまで受け入れます。通常動作では、R<sub>INB</sub>(ピン31、32)の正リファレンス電圧に接続します。ピン37とピン38は内部で相互に短絡されています。

**R<sub>FBB</sub>(ピン39、40)**: DAC Bの帰還抵抗。通常動作では、DAC BのI/Vコンバータ・アンプの出力に接続します(「標準的応用例」を参照)。I<sub>OUT1B</sub>からのDACの出力電流は帰還抵抗を通ってR<sub>FBB</sub>ピンに流れます。ピン39とピン40は内部で相互に短絡されています。

**I<sub>OUT1B</sub>(ピン41)**: DAC Bの電流出力。このピンはDACが動作中は仮想グランドで、0Vになります。通常動作では、DAC BのI/Vコンバータ・アンプの負入力に接続します(「標準的応用例」を参照)。

**V<sub>OSADJB</sub>(ピン42)**: DAC Bのオフセット調整ピン。この電圧制御ピンを使って、ユニポーラ・オフセットまたはバイポーラ・ゼロ誤差を除くことができます。LSBで表されているオフセットの変化はどの出力範囲でも同じです。「動作」のセクションの「システムのオフセットおよび利得の調整」を参照してください。使用しない場合、グランドに接続します。

**V<sub>OSADJA</sub>(ピン43)**: DAC Aのオフセット調整ピン。この電圧制御ピンを使って、ユニポーラ・オフセットまたはバイポーラ・ゼロ誤差を除くことができます。LSBで表されているオフセットの変化はどの出力範囲でも同じです。「動作」のセクションの「システムのオフセットおよび利得の調整」を参照してください。使用しない場合、グランドに接続します。

**I<sub>OUT1A</sub>(ピン44)**: DAC Aの電流出力。このピンは、DACが動作中は仮想グランドで、0Vになります。通常動作では、DAC AのI/Vコンバータ・アンプの負入力に接続します(「標準的応用例」を参照)。

**R<sub>FBA</sub>(ピン45、46)**: DAC Aの帰還抵抗。通常動作では、DAC AのI/Vコンバータ・アンプの出力に接続します(「標準的応用例」を参照)。I<sub>OUT1A</sub>からのDACの出力電流は帰還抵抗を通ってR<sub>FBA</sub>ピンに流れます。ピン45とピン46は内部で相互に短絡されています。

**R<sub>OFSA</sub>(ピン47、48)**: DAC Aのバイポーラ・オフセット抵抗。これらのピンはバイポーラ・スパンの出力電圧範囲を変換します。±15Vまで受け入れます。通常動作では、R<sub>INA</sub>(ピン5、6)の正リファレンス電圧に接続します。ピン47とピン48は内部で相互に短絡されています。

## 機能ブロック図

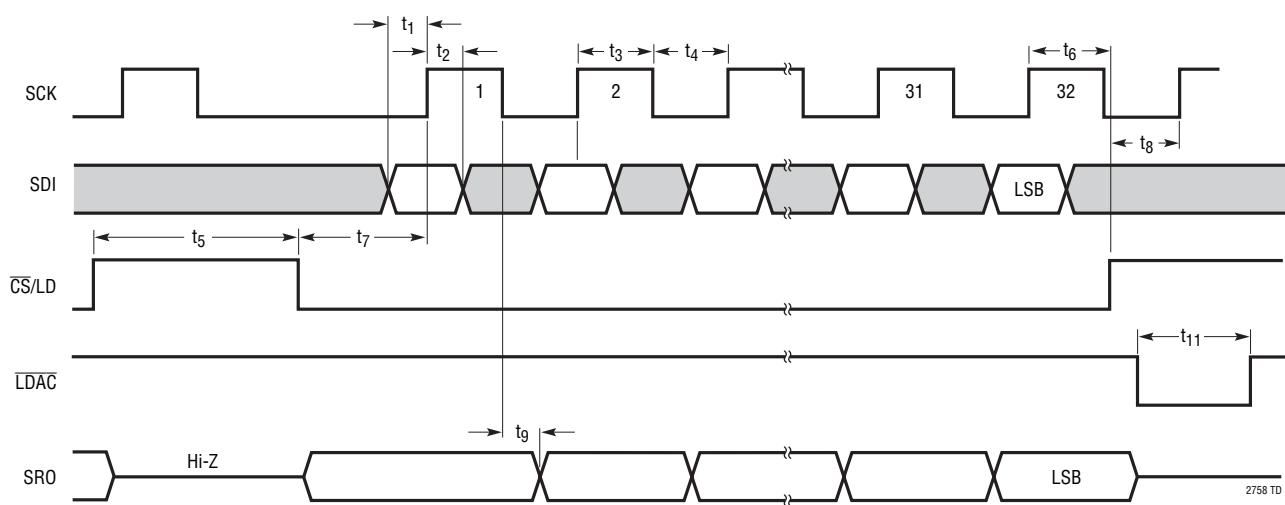

## タイミング図

## 動作

### 出力範囲

LTC2758はデュアル、電流出力、シリアル入力の高精度乗算型DACで、出力範囲を選択可能です。範囲は、最大の柔軟性を得るためにソフトウェアでプログラムするか(各DACを6種類の出力範囲のどれにでもプログラム可能)、またはピン・ストラッピングによってハードウェイ設定することができます。2つのユニポーラ範囲( $0V \sim 5V$ と $0V \sim 10V$ )および4つのバイポーラ範囲( $\pm 2.5V$ 、 $\pm 5V$ 、 $\pm 10V$ 、 $-2.5V \sim 7.5V$ )を利用するすることができます。これらの範囲は外部高精度5Vリファレンスを使う場合に得られます。他のリファレンス電圧の出力範囲は、各範囲が外部リファレンス電圧の倍数であることを見れば、容易に計算されます。したがって、範囲は次のように表すことができます。 $0 \sim 1$ 倍、 $0 \sim 2$ 倍、 $\pm 0.5$ 倍、 $\pm 1$ 倍、 $\pm 2$ 倍、および $-0.5$ 倍～ $1.5$ 倍。

### マニュアル・スパン構成

アプリケーションによっては複数の出力範囲は不要です。余計な動作負荷を加えずに单一スパンで動作するようにLTC2758を構成設定するには、M-SPANピンを直接V<sub>DD</sub>に接続します。次いで、全DACのアクティブ出力範囲を(SPIポートではなく)ピンS2、S1およびS0のハードウェア・ピン・ストラッピングによって設定します。書き込みと更新のコマンドはアクティブ出力スパンには影響を与えません。図1と表3を参照してください。

通常のSoftSpan動作ではM-SPANピンをグランドに接続します。

### 入力およびDACレジスタ

LTC2758には各DACに5個の内部レジスタがあり、合計10個のレジスタがあります(「ブロック図」を参照)。各DACチャネルには2組のダブル・バッファ付きレジスタ(1組はコード・データ用、1組はDACの出力範囲用)と1個の読み出しレジスタが備わっています。ダブル・バッファによりスパン(出力範囲)とコードを同時に更新可能なので、出力範囲の変更時に滑ら

図1. M-SPANを使用して LTC2758を単一スパン動作に構成(この図では、 $\pm 10V$ 範囲)

かに電圧を遷移させることができます。複数のDACの同時更新も可能です。

ダブル・バッファされたレジスタの各組は入力レジスタとDACレジスタで構成されています。

入力レジスタ：書き込み動作では、SDIピンから、選択された入力レジスタにデータをシフトさせます。入力レジスタは保持バッファなので、書き込み動作はDACの出力に影響を与えません。

DACレジスタ：更新動作では、入力レジスタの内容をそれに関連するDACレジスタにコピーします。他方、DACレジスタの内容は関連するDACの出力電圧または出力範囲を直接更新します。

更新には常にコードとスパンの両方のレジスタ・セットが含まれることに注意してください。ただし、DACレジスタの値は、関連した入力レジスタの値が書き込み動作によって先に変更されている場合だけ変化します。

## 動作

### シリアル・インターフェース

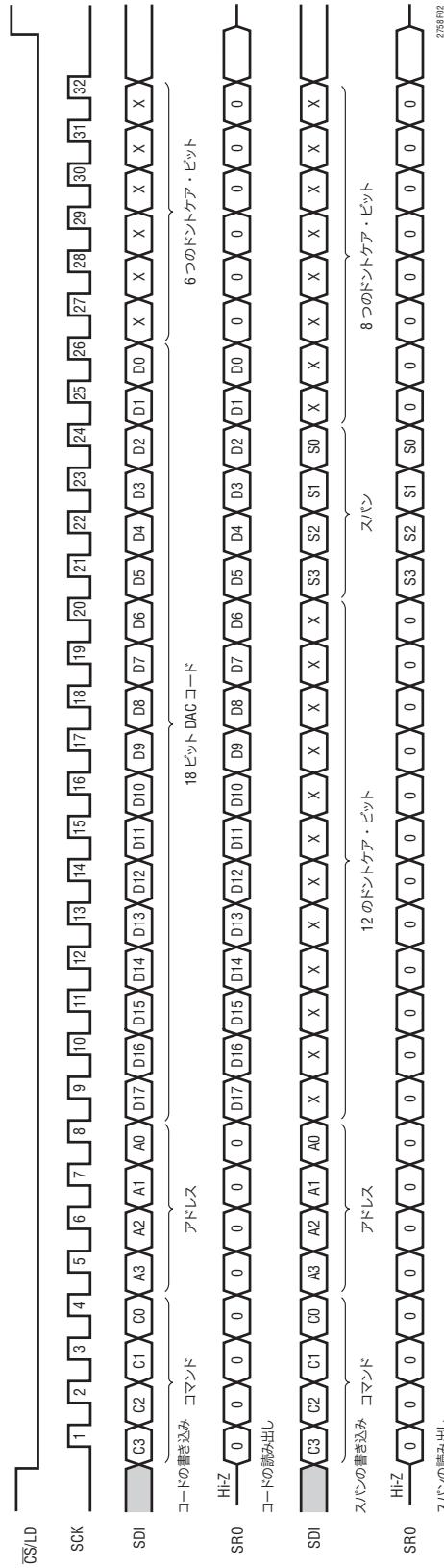

$\overline{CS}/LD$ ピンを“L”にすると、SDIピンのデータはクロック(SCKピン)の立ち上がりエッジでシフト・レジスタにロードされます。LTC2758に必要なロード・シーケンスは、4ビットのコマンド・ワード(C3 C2 C1 C0)と4ビットのアドレス・ワード(A3 A2 A1 A0)から成る1バイト、およびそれに続く3バイト(24ビット)のデータです。

コードを書き込むとき、コード・データは左(MSB)揃えにします。したがって、24ビットのデータ・フィールドは、18のコード・ビットと、それに続く6つのドントケア・ビットで構成されます。

出力範囲を書き込むとき、スパン・データは2つ目のデータ・バイトの最後の4ビットをS3からS0の順に使用します。書き込みに使うSDI入力ワードのシンタックスを図2に示します。

$\overline{CS}/LD$ が“L”的とき、SROピン(シリアル読み出し出力)はアクティブ出力です。データの読み出しは、コマンド(C3～C0)ワードとアドレス(A3～A0)ワードがSDIにシフトされた後に開始されます。 $\overline{CS}/LD$ の立ち下がりエッジからデータの読み出しが開始されるまで、SROはロジック“L”を出力します。

$\overline{CS}/LD$ が“H”的とき、SROピンは高インピーダンス(スリーステート)出力になります。

$\overline{LDAC}$ は非同期更新ピンです。 $\overline{LDAC}$ を“L”にすると、すべてのDACのコードおよびスパン・データが更新されます(入力バッファのデータがDACのバッファにコピーされます)。この動作中、 $\overline{CS}/LD$ は“H”でなければなりません。そうでないと、 $\overline{LDAC}$ がロックアウトされ、無効になります。 $\overline{LDAC}$ の使用は「全DACを更新」シリアル入力コマンドと機能的に同じです。

コマンド(C3～C0)のコードは表1で定義されています。表2では、アドレス(A3～A0)のコードが定義されています。

### 読み出し

コードとスパンのレジスタ・セットに加えて、各DACはそれに付随する1個の読み出しレジスタを備えています。命令サイクルごとに、内部レジスタの1つの内容が読み出しレジスタにコピーされ、SROピンを介してシリアルにシフトアウトされます。

読み出しデータは常に、最後のアドレス・ビットがSDIにシフトインされた直後のSCKの立ち下がりエッジで始まる24ビット・データ・フィールドに表示されます。コードを読み出すとき、コード・データには24ビット・フィールドの最初の18ビットが使用されます。また、出力範囲をチェックするときは、スパン・ビットは

2つ目のデータ・バイトの最後の4ビットです。どちらの場合も、24ビット・データ・フィールドの他のビットはすべて“0”になります。入力と読み出しのシーケンスを図2に示します。

SROによって出力されるデータの位置とシーケンスは、入力データと常に同じです。ただし、このため、SROのデータは対応するビットのSDIへのシフトインより1/2クロック・サイクル早くシフトアウトすることに注意してください。たとえば、SCKクロック17の立ち上がりエッジでSDIにシフトインされるコード・ビットD9は、クロック16の立ち下がりエッジでSROからクロックアウトされます。これにより、クロック17の立ち上がりエッジで、D9を外部のマイクロプロセッサにクロックすることができます。

読み出しコマンドでは、要求されたデータはコマンドおよびアドレス・バイトの直後の3バイト(24ビット)データ・フィールドでSROからシフトアウトされます。読み出しコマンドの場合、命令サイクルの待ち時間がないので、データは、要求されたのと同じ命令サイクル中にシフトアウトされます。

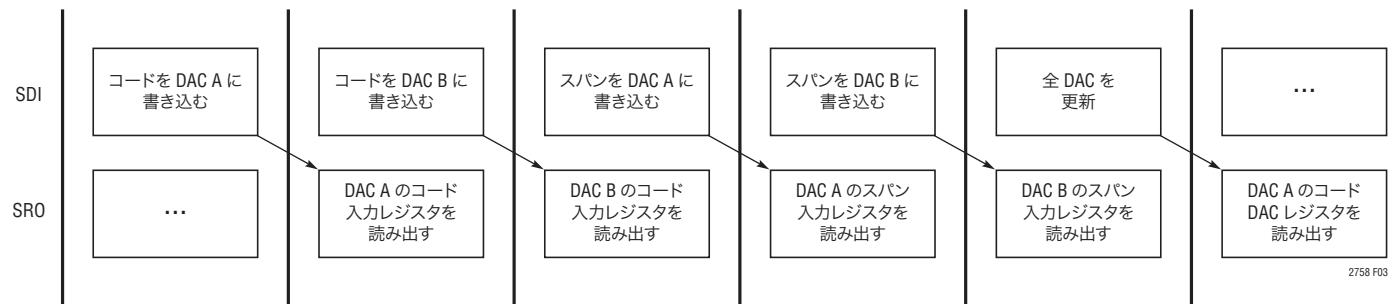

読み出し以外の(つまり、書き込みや更新)コマンドでは、SROは直前のコマンドで使用されたバッファの内容を自動的にシフトアウトします。この「ローリング読み出し」のデフォルト動作モードにより、後続のコマンド実行時に余計な負荷を加えずにはとんどのコマンドを検証できるので、必要な命令サイクル数を大幅に減らすことができます。概念的なフローチャートを図3に示します。先行する各コマンドに対して、次の命令サイクルの間にどのレジスタ(「読み出しポインタ」)が読み出しレジスタにコピーされてSROから出力されるかを表1に示します。

### マニュアル・スパン構成におけるスパンの読み出し

スパンDACレジスタが読み出しのために選択されると、SROが実際の出力スパンを出力して応答します。これは、LTC2758がSoftSpanに設定されているても(M-SPANはGNDに接続されている)、またはマニュアル・スパンが使われていても(M-SPANはV<sub>DD</sub>に接続されている)、当てはまります。

SoftSpan構成では、SROは(SPIポートを通してプログラムされた)スパンDACレジスタからスパン・コードを出力します。マニュアル・スパン構成では、アクティブ出力範囲は、ピンS2、S1およびS0によって制御されるので、SROはこれらのピンのロジック値を出力します。スパン・コード・ビットS2、S1およびS0は、SRO出力シーケンスで常に同じ順序と位置で現れます(図2を参照)。

## 動作

表1. コマンドのコード

| コード |    |                    |    | コマンド                             | 読み出しポインター-現在の入力ワード $W_0$ | 読み出しポインター-次の入力ワード $W_{+1}$ |

|-----|----|--------------------|----|----------------------------------|--------------------------|----------------------------|

| C3  | C2 | C1                 | C0 |                                  |                          |                            |

| 0   | 0  | 1                  | 0  | スパンをDAC $n$ に書き込む                | 前のコマンドによって設定             | DAC $n$ の入力スパン・レジスタ        |

| 0   | 0  | 1                  | 1  | コードをDAC $n$ に書き込む                | 前のコマンドによって設定             | DAC $n$ の入力コード・レジスタ        |

| 0   | 1  | 0                  | 0  | DAC $n$ を更新                      | 前のコマンドによって設定             | DAC $n$ のDACスパン・レジスタ       |

| 0   | 1  | 0                  | 1  | 全DACを更新                          | 前のコマンドによって設定             | DAC $n$ のDACコード・レジスタ       |

| 0   | 1  | 1                  | 0  | スパンをDAC $n$ に書き込む<br>DAC $n$ を更新 | 前のコマンドによって設定             | DAC $n$ のDACスパン・レジスタ       |

| 0   | 1  | 1                  | 1  | コードをDAC $n$ に書き込む<br>DAC $n$ を更新 | 前のコマンドによって設定             | DAC $n$ のDACコード・レジスタ       |

| 1   | 0  | 0                  | 0  | スパンをDAC $n$ に書き込む<br>全DACを更新     | 前のコマンドによって設定             | DAC $n$ のDACスパン・レジスタ       |

| 1   | 0  | 0                  | 1  | コードをDAC $n$ に書き込む<br>全DACを更新     | 前のコマンドによって設定             | DAC $n$ のDACコード・レジスタ       |

| 1   | 0  | 1                  | 0  | DAC $n$ の入力スパン・レジスタを読み出す         |                          | DAC $n$ の入力スパン・レジスタ        |

| 1   | 0  | 1                  | 1  | DAC $n$ の入力コード・レジスタを読み出す         |                          | DAC $n$ の入力コード・レジスタ        |

| 1   | 1  | 0                  | 0  | DAC $n$ のDACスパン・レジスタを読み出す        |                          | DAC $n$ のDACスパン・レジスタ       |

| 1   | 1  | 0                  | 1  | DAC $n$ のDACコード・レジスタを読み出す        |                          | DAC $n$ のDACコード・レジスタ       |

| 1   | 1  | 1                  | 1  | 動作なし                             | 前のコマンドによって設定             | DAC $n$ のDACコード・レジスタ       |

| -   |    | システム・クリア           |    |                                  | -                        | DAC AのDACスパン・レジスタ          |

| -   |    | 初期パワーアップまたはパワー割り込み |    |                                  | -                        | DAC AのDACスパン・レジスタ          |

示されていないコードは予備-使用しないでください

表2. アドレス・コード

| A3 | A2 | A1 | A0 | $n$             |

|----|----|----|----|-----------------|

| 0  | 0  | 0  | x  | DAC A           |

| 0  | 0  | 1  | x  | DAC B           |

| 1  | 1  | 1  | x  | 全てのDAC (Note 1) |

示されていないコードは予備-使用しないでください。ドントケアではありません。

Note 1:「全てのDAC」のアドレスを使って読み出しを行うと、LTC2758はデフォルトでDAC Aを選択する。

表3. スパン・コード

| S3 | S2 | S1 | S0 | スパン              |

|----|----|----|----|------------------|

| x  | 0  | 0  | 0  | ユニポーラ 0V～5V      |

| x  | 0  | 0  | 1  | ユニポーラ 0V～10V     |

| x  | 0  | 1  | 0  | バイポーラ -5V～5V     |

| x  | 0  | 1  | 1  | バイポーラ -10V～10V   |

| x  | 1  | 0  | 0  | バイポーラ -2.5V～2.5V |

| x  | 1  | 0  | 1  | バイポーラ -2.5V～7.5V |

示されていないコードは予備-使用しないでください。ドントケアではありません。

## 動作

### 例

- DAC Aに0～10Vの範囲、0Vの出力をロードし、DAC Bに±10Vの範囲、0Vの出力をロードします。DACの出力が同時に変化することに注意してください。

a)  $\overline{CS}/LD\downarrow$  クロックでSDI:

00101111 00000000 00000011 00000000をシフト

b)  $\overline{CS}/LD\uparrow$

スパン入力レジスタ - DACの範囲をバイポーラ±10Vに設定

c)  $\overline{CS}/LD\downarrow$  クロックでSDI:

00100000 00000000 00000001 00000000をシフト

d)  $\overline{CS}/LD\uparrow$

スパン入力レジスタ - DAC Aの範囲をユニポーラ0V～10Vに設定

e)  $\overline{CS}/LD\downarrow$  クロックでSDI:

00111111 10000000 00000000 00XXXXXXをシフト

f)  $\overline{CS}/LD\uparrow$

コード入力レジスタ - 全DACのコードをミッドスケールに設定

g)  $\overline{CS}/LD\downarrow$  クロックでSDI:

00110000 00000000 00000000 00XXXXXXをシフト

h)  $\overline{CS}/LD\uparrow$

コード入力レジスタ - DAC Aのコードをゼロに設定

i)  $\overline{CS}/LD\downarrow$  クロックでSDI:

01001111 XXXXXXXX XXXXXXXX XXXXXXXXをシフト

j)  $\overline{CS}/LD\uparrow$

全DACのコードと範囲の両方を更新

k) または、ステップiおよびjを $\overline{LDAC}$ 「」で置き換え可能

- DAC Bに±2.5Vの範囲、その出力に0Vをロードします。DACの出力を更新する前に(つまり、入力レジスタの内容をDACレジスタにコピーする前に)、読み出しを使って入力レジスタの内容をチェックします。パワーオン後、入力レジスタのコードはゼロであることに注意してください。

a)  $\overline{CS}/LD\downarrow$  クロックでSDI:

00110010 10000000 00000000 00XXXXXXをシフト

b)  $\overline{CS}/LD\uparrow$

コード入力レジスタ - DAC Bをミッドスケールに設定

c)  $\overline{CS}/LD\downarrow$  クロックでSDI:

00100010 00000000 00000100 00000000をシフト

SROの出力データ:

10000000 00000000 00000000により、コード入力レジスタ - DAC Bがミッドスケールに設定されていることを確認

d)  $\overline{CS}/LD\uparrow$

スパン入力レジスタ - DAC Bの範囲をバイポーラ±2.5V範囲に設定

e)  $\overline{CS}/LD\downarrow$  クロックでSDI:

10100010 XXXXXXXX XXXXXXXX XXXXXXXXをシフト

SROの出力データ:

00000000 00000100 00000000により、スパン入力レジスタ - DAC Bが±2.5Vのバイポーラ範囲に設定されていることを確認 $\overline{CS}/LD\uparrow$

f)  $\overline{CS}/LD\downarrow$  クロックでSDI:

01000010 XXXXXXXX XXXXXXXX XXXXXXXXをシフト

g)  $\overline{CS}/LD\uparrow$

DAC Bのコードと範囲の両方を更新

h) または、ステップfおよびgを $\overline{LDAC}$ 「」で置き換え可能

## 動作

### システムのオフセットとリファレンスの調整

多くのシステムがシステム全体のオフセットの補償を必要とします。このシステムのオフセットは、LTC2758のオフセットより1桁以上大きいことがあります。LTC2758のオフセットは非常に小さく、最も高精度なオペアンプを使っていても外部出力アンプの誤差に大きく影響されるほどです。

オフセット調整ピン V<sub>OSADJX</sub> を使って、ユニポーラ・オフセットまたはバイポーラ・ゼロ誤差を除くことができます。LSB で表されているオフセットの変化はどの出力範囲でも同じです。

$$\Delta V_{OS}[\text{ LSB}] = \frac{-V(V_{OSADJX})}{V(R_{INX})} \cdot 2048$$

R<sub>INX</sub> に 5V リファレンスが与えられていると仮定すると、V<sub>OSADJX</sub> に加えられる 5V 制御電圧はどの出力範囲でも  $\Delta V_{OS} = -2048 \text{ LSB}$  を生じます。

電圧で表すと、オフセットのデルタは、出力範囲に応じて、32、64 または 128 分の 1 に減衰します。(これらの関数はリファレンス電圧に関係なく有効です。)

$$\Delta V_{OS} = -(1/128)V_{OSADJX} \quad [0V \sim 5V, \pm 2.5V \text{ のスパン}]$$

$$\Delta V_{OS} = -(1/64)V_{OSADJX} \quad [0V \sim 10V, \pm 5V, -2.5V \sim 7.5V \text{ のスパン}]$$

$$\Delta V_{OS} = -(1/32)V_{OSADJX} \quad [\pm 10V \text{ のスパン}]$$

利得誤差調整ピン GE<sub>ADJX</sub> を使って、利得誤差を除いたり、リファレンス誤差を補償することができます。LSB で表される利得誤差の変化はどの出力範囲でも同じです。

$$\Delta GE = \frac{V(GE_{ADJX})}{V(R_{INX})} \cdot 2048$$

正リファレンス電圧では、利得誤差のデルタは非反転です。

このピンは、反転したリファレンス電圧 V(REFX) を変えることによって利得を補償することに注意してください。電圧で表すと、V(REFX) のデルタは反転されて 128 分の 1 に減衰されます。

$$\Delta V(REFX) = -(1/128)GE_{ADJX}$$

これらのピンの公称入力範囲は  $\pm 5V$  です。必要ならば、 $\pm 15V$  までの他の電圧を使用することができます。ただし、電源を分圧した電圧は使わないでください。DAC の最良の性能を維持するには、リファレンスの品質をもった低ノイズの入力が必要です。

V<sub>OSADJX</sub> ピンの入力インピーダンスは  $1.28M\Omega$  です。LTC2758 のセトリング性能を維持するには、これらのピンを  $10k$  以下のテブナン等価インピーダンスでドライブします。これらのピンを使わない場合、GND に短絡します。

GE<sub>ADJX</sub> ピンの入力インピーダンスは  $2.56M\Omega$  で、固定リファレンス電圧でのみ使用することが意図されています。これらのピンを使わない場合、GND に短絡します。

### パワーオン・リセットとクリア

LTC2758 に最初に電源が投入されると、すべての DAC がユニポーラ 5V モードでパワーアップします (S3 S2 S1 S0 = 0000)。全ての内部 DAC レジスタが 0 にリセットされ、DAC 出力は 0V に初期化されます。

デバイスがマニュアル・スパン動作に構成設定されると、全ての DAC が最初の更新コマンドでピンストラップされた範囲に設定されます。これにより、ユーザーは、選択された出力範囲に電圧が滑らかに遷移するようにスパンとコードを同時に更新することができます。

$\overline{CLR}$  ピンを “L” にすると、システムがクリアされます。DAC バッファは 0 にリセットされ、DAC 出力は全て 0V にリセットされます。入力バッファはそのままなので、それ以降の ( $\overline{LDAC}$  の使用を含む) 更新コマンドは呼び出された DAC をそれぞれの前の状態に復元します。

命令の間に (つまり  $\overline{CS}/\overline{LD}$  が “L” のときに)  $\overline{CLR}$  がアサートされると、命令は中止されます。これらの条件では、関連した入力バッファの完全性は保証されないので、内容を読み出してチェックするか置き換えます。

$\overline{RFLAG}$  ピンは、データの完全性が失われたことをシステムに通知するフラグとして使われます。 $\overline{RFLAG}$  出力は、パワーアップ時、システム・クリア時、または電源 V<sub>DD</sub> が約 2V より下になると “L” にアサートされ、有効な更新コマンドが実行されるまでアサートされたままになります。

## 動作

## 動作

図3. ローリング読み出し

## アプリケーション情報

### オペアンプの選択

18ビットのLTC2758は精度が非常に高いので、このデバイスのもつている並外れた性能を十分引き出すには、慎重に検討してオペアンプを選択する必要があります。幸いにも、オペアンプのオフセットに対するINLとDNLの感度は、前の世代の乗算型DACに比べて大幅に低下しています。

ユニポーラまたはバイポーラの出力範囲でプログラムされたときの、LTC2758の精度に対するオペアンプのパラメータの影響を評価するための式を、表4と表5に示します。これらは、オペアンプが原因で生じることがある、INL、DNL、ユニポーラのオフセット、ユニポーラの利得誤差、バイポーラのゼロ誤差およびバイポーラの利得誤差の変化です。

表4. 表5の式の係数

| 出力範囲       | A1  | A2 | A3   | A4  | A5  |

|------------|-----|----|------|-----|-----|

| 5V         | 1.1 | 2  | 1    |     | 1   |

| 10V        | 2.2 | 3  | 0.5  |     | 1.5 |

| ±5V        | 2   | 2  | 1    | 1   | 1.5 |

| ±10V       | 4   | 4  | 0.83 | 1   | 2.5 |

| ±2.5V      | 1   | 1  | 1.4  | 1   | 1   |

| -2.5V~7.5V | 1.9 | 3  | 0.7  | 0.5 | 1.5 |

LTC2758との併用を推奨するリニアテクノロジーの高精度オペアンプのリストの一部を表6に示します。設計時に簡単に使える式により、システムの規定の誤差範囲に適合するオペアンプを容易に選択できます。表6からアンプを選択し、オペアンプの規定されたパラメータを表5に代入します。カテゴリーごとの誤差をすべて加算してデバイスの精度に対するオペアンプの影響を求めます。算術和は(可能性の低い)ワーストケースの影響を与えます。根二乗和(RSS)はもっと現実的な推定値を与えます。

表5. すべての出力範囲でDACの精度に対するオペアンプの影響を求める使いやすい式(p.1の回路)。

添字の1は出力アンプを指し、添字の2はリファレンス反転アンプを指す。

| OP AMP            | INL (LSB)                                                   | DNL (LSB)                                                    | UNIPOLAR OFFSET (LSB)                                               | BIPOLAR ZERO ERROR (LSB)                                            | UNIPOLAR GAIN ERROR (LSB)                                   | BIPOLAR GAIN ERROR (LSB)                                    |

|-------------------|-------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|

| $V_{OS1}$ (mV)    | $V_{OS1} \cdot 12.1 \cdot \left(\frac{5V}{V_{REF}}\right)$  | $V_{OS1} \cdot 3.1 \cdot \left(\frac{5V}{V_{REF}}\right)$    | $A3 \cdot V_{OS1} \cdot 52.4 \cdot \left(\frac{5V}{V_{REF}}\right)$ | $A3 \cdot V_{OS1} \cdot 78.6 \cdot \left(\frac{5V}{V_{REF}}\right)$ | $V_{OS1} \cdot 52.4 \cdot \left(\frac{5V}{V_{REF}}\right)$  | $V_{OS1} \cdot 52.4 \cdot \left(\frac{5V}{V_{REF}}\right)$  |

| $I_{B1}$ (nA)     | $I_{B1} \cdot 0.0012 \cdot \left(\frac{5V}{V_{REF}}\right)$ | $I_{B1} \cdot 0.00032 \cdot \left(\frac{5V}{V_{REF}}\right)$ | $I_{B1} \cdot 0.524 \cdot \left(\frac{5V}{V_{REF}}\right)$          | $I_{B1} \cdot 0.524 \cdot \left(\frac{5V}{V_{REF}}\right)$          | $I_{B1} \cdot 0.0072 \cdot \left(\frac{5V}{V_{REF}}\right)$ | $I_{B1} \cdot 0.0072 \cdot \left(\frac{5V}{V_{REF}}\right)$ |

| $A_{VOL1}$ (V/mV) | $A1 \cdot \left(\frac{66}{A_{VOL1}}\right)$                 | $A2 \cdot \left(\frac{6}{A_{VOL1}}\right)$                   | 0                                                                   | 0                                                                   | $A5 \cdot \left(\frac{524}{A_{VOL1}}\right)$                | $A5 \cdot \left(\frac{524}{A_{VOL1}}\right)$                |

| $V_{OS2}$ (mV)    | 0                                                           | 0                                                            | 0                                                                   | $A4 \cdot V_{OS2} \cdot 52.4 \cdot \left(\frac{5V}{V_{REF}}\right)$ | $V_{OS2} \cdot 104.8 \cdot \left(\frac{5V}{V_{REF}}\right)$ | $V_{OS2} \cdot 104.8 \cdot \left(\frac{5V}{V_{REF}}\right)$ |

| $I_{B2}$ (nA)     | 0                                                           | 0                                                            | 0                                                                   | $A4 \cdot I_{B2} \cdot 0.524 \cdot \left(\frac{5V}{V_{REF}}\right)$ | $I_{B2} \cdot 1.048 \cdot \left(\frac{5V}{V_{REF}}\right)$  | $I_{B2} \cdot 1.048 \cdot \left(\frac{5V}{V_{REF}}\right)$  |

| $A_{VOL2}$ (V/mV) | 0                                                           | 0                                                            | 0                                                                   | $A4 \cdot \left(\frac{262}{A_{VOL2}}\right)$                        | $\left(\frac{524}{A_{VOL2}}\right)$                         | $\left(\frac{524}{A_{VOL2}}\right)$                         |

表6. LTC2758との併用を推奨するリニアテクノロジーの高精度アンプの一部とその仕様のリスト

| アンプ     | アンプの仕様           |          |                |                      |                      |                   |            |                                 |         |

|---------|------------------|----------|----------------|----------------------|----------------------|-------------------|------------|---------------------------------|---------|

|         | $V_{OS}$ $\mu$ V | $I_B$ nA | $A_{VOL}$ V/mV | 電圧ノイズ $nV/\sqrt{Hz}$ | 電流ノイズ $pA/\sqrt{Hz}$ | スルーレート V/ $\mu$ s | 利得帯域幅積 MHz | LTC2758の $t_{SETTLING}$ $\mu$ s | 電力損失 mW |

| LTC1150 | 10               | 0.05     | 5600           | 90                   | 0.0018               | 3                 | 2.5        | 10ms                            | 24      |

| LT1001  | 25               | 2        | 800            | 10                   | 0.12                 | 0.25              | 0.8        | 120                             | 46      |

| LT1012  | 25               | 0.1      | 2000           | 14                   | 0.02                 | 0.2               | 1          | 120                             | 11.4    |

| LT1097  | 50               | 0.35     | 2500           | 14                   | 0.008                | 0.2               | 0.7        | 120                             | 11      |

| LT1468  | 75               | 10       | 5000           | 5                    | 0.6                  | 22                | 90         | 2.1                             | 117     |

## アプリケーション情報

オペアンプのオフセットは大部分がDACの出力オフセットと利得誤差に寄与し、INLとDNLに対する影響はごくわずかです。たとえば、LTC2758の出力範囲がユニポーラ5Vの場合を考えてみます。(この例では、LSBのサイズが $19\mu\text{V}$ であることに注意。)オペアンプのオフセットが $35\mu\text{V}$ である場合、1.8LSBの出力オフセットと1.8LSBの利得誤差を生じますが、INLは0.4LSBで、DNLはわずか0.1LSBです。

表4と表5の簡単な式では直接扱ってはいませんが、ユニポーラとバイポーラのアプリケーションに対する温度の影響も同様に簡単に処理することができます。まず、オペアンプのデータシートを調べて、全温度範囲でのワーストケースの $V_{OS}$ と $I_B$ を見つけます。次に、これらの数値を表5の $V_{OS}$ と $I_B$ の式に代入して温度による影響を計算します。

高速セトリング時間が重要なアプリケーションの場合、アプリケーション・ノート120「1ppm Settling Time Measurement for a Monolithic 18-Bit DAC (18ビットのモノリシックDACに対する1ppmでのセトリング時間測定)」で、18ビットDACのセトリング時間とオペアンプの選択について詳細に説明されています。

### 推奨事項

DCまたは低周波数アプリケーションでは、LTC1150が最もシンプルな18ビットの高精度出力アンプです。オートゼロ・アンプはオフセット(最大 $10\mu\text{V}$ )とオフセット・ドリフト( $0.01\mu\text{V}/^\circ\text{C}$ )が非常に小さいので、これらの除去は不要です。振幅が8Vを超えるときは、負荷電流能力を高めるためにLT1010を使用します。オートゼロ・アンプをセトリングさせるのは特別な場合です。詳細については、アプリケーション・ノート120「1ppm Settling Time Measurement for a Monolithic 18-Bit DAC (18ビットのモノリシックDACに対する1ppmでのセトリング時間測定)」のAppendix Eを参照してください。

LT1012とLT1001は、適度な速度と高精度を実現する優れた中間的な出力アンプ・ソリューションです。また、固定リファレンス・アプリケーションでは、リファレンス反転アンプにも最適です。

高速アプリケーションでは、LTC1468は $2.1\mu\text{s}$ でセトリングします。オフセットが最大 $75\mu\text{V}$ なので、DAC出力時にINLが最大0.9LSB低下することに注意してください。高い精度が求められる高速アプリケーションでは、アンプのオフセットはデジタル・ポテンショメータを使って除去することができます。

オフセットをゼロにせずに高速セトリング( $8\mu\text{s}$ )を達成しオフセットを非常に小さく抑える(最大 $3\mu\text{V}$ )複合出力アンプを最終頁の「標準的応用例」に示します。この回路は高い開ループ利得(最小 $1000\text{V/mV}$ )、小さい入力バイアス電流(最大 $0.15\text{nA}$ )、高速スルーレート(最小 $25\text{V}\mu\text{V}/\text{s}$ )、高い利得帯域幅積(標準 $30\text{MHz}$ )を実現します。高速経路は、 $18\text{MHz}$ の超低バイアス電流アンプ LTC6240と、追加利得を提供し、 $\pm 10\text{V}$ までの出力振幅が可能な $50\text{MHz}$ の高速スルー・アンプ LT1360で構成されています。補償はLTC6240の出力を使って行われるので、利得5の段の後補償を行う場合よりもはるかに大きい補償コンデンサを使用できます。オートゼロ・アンプ LTC2054は、高速経路のオフセットを除去するために、I<sub>OUT1</sub>で電圧を検出して LTC6240 の非反転入力をドライブします。 $100:1$ 減衰器と入力フィルタにより、低いDCオフセットを維持しながらこの段の低周波数ノイズを低減します。

### 高精度電圧リファレンスの検討事項

LTC2758に使用するオペアンプの選択がシステムの性能にとって非常に重要なと同様に、高精度電圧リファレンスの選択にもそれ相応の配慮が必要です。LTC2758の出力電圧は電圧リファレンスの影響を直接受けるので、電圧リファレンスの誤差は全てDACの出力電圧誤差として現れます。

18ビットのアプリケーション用の高精度電圧リファレンスの選択時に検討すべき主な誤差源が3つあります。つまり、出力電圧の初期許容誤差、出力電圧の温度係数、および出力電圧ノイズです。

リファレンスの出力電圧の初期許容誤差が修正されないと、フルスケールの誤差項を生じます。LT1236のような出力電圧の初期許容誤差が低い( $\pm 0.05\%$ )リファレンスを選択すると、リファレンスによって生じる利得誤差を小さくできます。ただし、システムのゼロ誤差とフルスケール誤差を修正する較正手順を必ず実行することを推奨します。

リファレンスの出力電圧の温度係数は、フルスケール誤差だけでなく、回路のINLとDNLの性能にも影響します。出力電圧の温度係数が大きいリファレンスを選択すると、DACの出力電圧とその伝達特性が周囲条件に大きく依存するようになります。リファレンスの温度係数による誤差を小さく抑えるには、出力電圧の温度係数が小さい高精度リファレンスを選択するか、回路の周囲温度を厳密に制御して温度勾配を小さくします。

## アプリケーション情報

表7. LTC2758との併用を推奨するリニアテクノロジーの高精度リファレンスの一部とその仕様のリスト

| リファレンス                     | 初期許容誤差      | 温度ドリフト       | 0.1Hz～10Hzノイズ          |

|----------------------------|-------------|--------------|------------------------|

| LT1019A-5,<br>LT1019A-10   | ±0.05% max  | 5ppm/°C max  | 12µV <sub>P-P</sub>    |

| LT1236A-5,<br>LT1236A-10   | ±0.05% max  | 5ppm/°C max  | 3µV <sub>P-P</sub>     |

| LT1460A-5,<br>LT1460A-10   | ±0.075% max | 10ppm/°C max | 20µV <sub>P-P</sub>    |

| LT1790A-2.5                | ±0.05% max  | 10ppm/°C max | 12µV <sub>P-P</sub>    |

| LTC6652A-5                 | ±0.05% max  | 5ppm/°C max  | 2.8ppm <sub>P-P</sub>  |

| LTC6655A-2.5<br>LTC6655A-5 | ±0.025% max | 2ppm/°C max  | 0.25ppm <sub>P-P</sub> |

高精度DACのアプリケーションが18ビット性能に移行するにつれ、リファレンスの出力電圧ノイズがシステムのノイズフロアの支配的部を占める可能性があります。その結果、システムのダイナミックレンジとSN比を低下させる可能性があります。望みのシステム分解能に対して、できるだけ出力ノイズ電圧が低い電圧リファレンスを選択するように注意が必要です。LT1236やLTC6655のような高精度電圧リファレンスは0.1Hz～10Hzの領域で低い出力ノイズを発生しますが、フルスケールが5Vまたは10Vのシステムの18ビット LSB レベルより十分小さいレベルです。ただし、回路の帯域幅が増加すると、リファレンスの出力にフィルタをかけて出力ノイズを抑える必要があるかもしれません。

## 接地

どんな高分解能のコンバータの場合でもそうですが、クリーンな接地が重要です。低インピーダンスのアナログ・グランド・プレーンが必要であり、スター・グランドの手法も必要です。スターグランドに使用する基板層を連続に保ってグランド抵抗を最小に抑えます。つまり、別々のスタートレースを使わずにスターグランドのコンセプトを使います。IOUT2ピンは特に注意が必要です。グランドへの電圧低下が生じることが許容されていると、IOUT2XFピンとIOUT2XSピンに流れるコードに依存する電流によってINLが劣化します。この場合の最良の戦略は、デバイスの直下に配置した多数のビアによって、これらのピンをスターグランドプレーンに接続することです。また、必要であれば、これらのピンをスターグランド・ポイントに配線することができます。フォース・ピンとセンス・ピンをデバイスのところで相互に接続し、30平方を超えない1オンス銅の1本のトレースで各チャネルを配線します。

これらの選択肢のどちらも実行できない稀なケースでは、フォース/センス・アンプをグランド・バッファとして使います(図4を参照)。ただし、グランド・バッファ・アンプの電圧オフセットは、表5のVOS1で規定された精度の効果に直接影響します。オフセットの結合された効果は、式の中のVOS1を、IOUT1からIOUT2XSへの全オフセットで置き換えて計算することができます。

## アプリケーション情報

図4. フォース/センス・アンプを使ってGNDからI<sub>OUT2</sub>をドライブするオプション回路

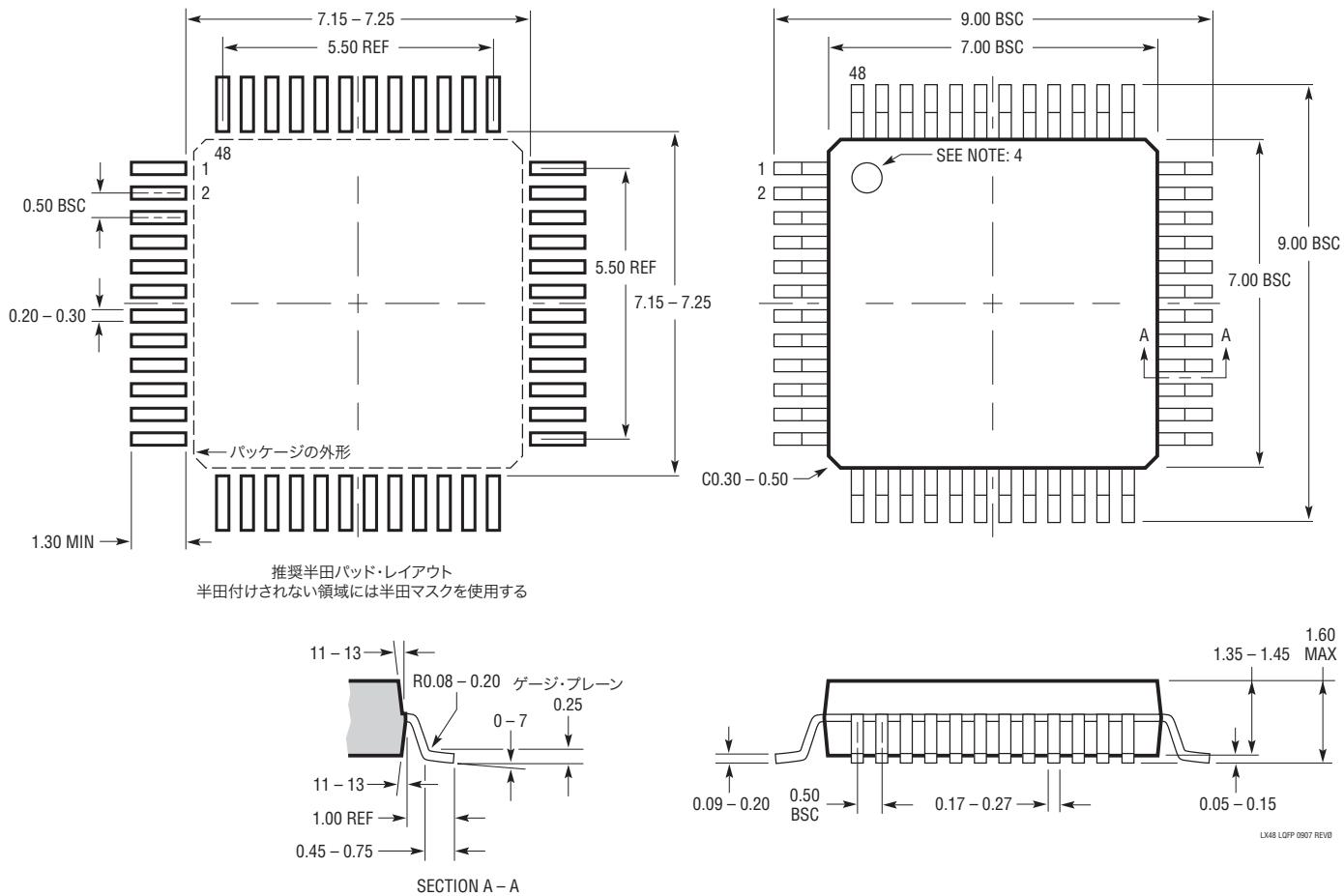

## パッケージ

**LX Package

48-Lead Plastic LQFP (7mm × 7mm)**

(Reference LTC DWG # 05-08-1760 Rev 0)

- NOTE:**

1. パッケージ寸法は JEDEC のパッケージ外形 #MS-026 に適合

2. 寸法はミリメートル

3. パッケージの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで 0.25mm を超えないこと

4. ピン 1 の識別マークはモールドのくぼみ(直径 0.50mm)

5. 図は実寸とは異なる

LX48 LQFP 0907 REV0

## 改訂履歴

| REV | 日付   | 概要                               | ページ番号   |

|-----|------|----------------------------------|---------|

| A   | 9/13 | R COMA(ピン3)の説明を修正。<br>標準的応用例を更新。 | 8<br>24 |

# LTC2758

## 標準的応用例

調整なしで高速セトリングと18ビット精度の両方を実現する複合アンプ回路

## 関連製品

| 製品番号       | 説明                                   | 注釈                                                  |

|------------|--------------------------------------|-----------------------------------------------------|

| LTC2757    | シングル・パラレル18ビット電流出力SoftSpan DAC       | INL/DNL:±1LSB、ソフトウェアで選択可能な出力範囲、7mm×7mm LQFP-48パッケージ |

| LTC1592    | シングル・シリアル16/14/12ビット電流出力SoftSpan DAC | INL/DNL:±1LSB、ソフトウェアで選択可能な出力範囲、16ピン SSOPパッケージ       |

| LTC2752    | デュアル・シリアル16ビット電流出力SoftSpan DAC       | INL/DNL:±1LSB、ソフトウェアで選択可能な出力範囲、7mm×7mm LQFP-48パッケージ |

| LTC2754-12 | クワッド・シリアル16/12ビット電流出力SoftSpan DAC    | INL/DNL:±1LSB、ソフトウェアで選択可能な出力範囲、7mm×8mm QFN-52パッケージ  |

| LTC2704-12 | クワッド・シリアル16/14/12ビット電圧出力SoftSpan DAC | INL/DNL:±1LSB、ソフトウェアで選択可能な出力範囲、アンプ内蔵                |

## リファレンス

|         |                             |                                                    |

|---------|-----------------------------|----------------------------------------------------|

| LTC6655 | 低ドリフトの高精度バッファ付きリファレンス       | 最大許容誤差:0.025%、2ppm/°C(最大)、0.1Hz～10Hzノイズ:0.25ppmp-p |

| LT1236  | 高精度リファレンス                   | 最大許容誤差:0.05%、5ppm/°C(最大)、0.1Hz～10Hzノイズ:3μVp-p      |

| LT1460  | マイクロパワー高精度シリーズ・リファレンス       | 最大許容誤差:0.075%、10ppm/°C(最大)、0.1Hz～10Hzノイズ:20μVp-p   |

| LT1790  | マイクロパワー低損失リファレンス            | 最大許容誤差:0.05%、10ppm/°C(最大)、0.1Hz～10Hzノイズ:12μVp-p    |

| LTC6652 | 高精度、低ドリフト、低ノイズのバッファ付きリファレンス | 最大許容誤差:0.05%、5ppm/°C(最大)、0.1Hz～10Hzノイズ:2.8ppmp-p   |

## アンプ

|         |                      |                                                        |

|---------|----------------------|--------------------------------------------------------|

| LTC1150 | コンデンサ内蔵のゼロドリフト・オペアンプ | 最大オフセット電圧:10μV、高電圧動作:±16V、ノイズ:1.8μVp-p                 |

| LT1012  | 高精度オペアンプ             | 最大オフセット電圧:25μV、最大入力電流:100pA、ノイズ:0.5μVp-p、電源電流:380μA    |

| LT1001  | 高精度オペアンプ             | 最大オフセット電圧:25μV、ノイズ:0.3μVp-p、高出力ドライブ                    |

| LT1468  | シングル16ビット高精度オペアンプ    | セトリング時間:900ns、利得帯域幅:90MHz、スルーレート:22V/μs、最大オフセット電圧:75μV |

2758fa