# 最大10ppm/°Cのリファレンスを内蔵したクワッド16ビット/12ビット±10V電圧出力SoftSpan D/Aコンバータ

## 特長

- 最大10ppm/°Cの高精度リファレンス

- 出力範囲を個別にプログラム可能:

0V～5V、0V～10V、±2.5V、±5V、±10V

- 全ての範囲で完全な16ビット/12ビット分解能

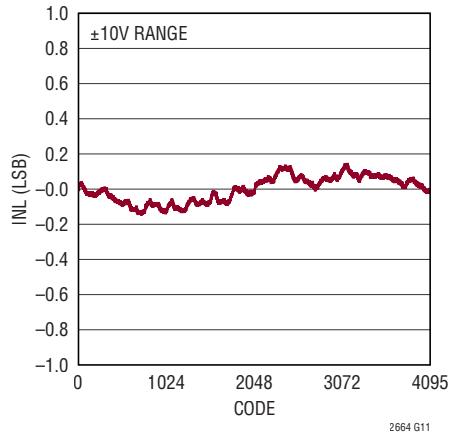

- 最大INL誤差:±4LSB(16ビット)

- ソフトウェアまたは専用のピンを介してA/Bを切り替え

- 補助入力付きのアナログ・マルチプレクサ

- 全温度範囲で単調性を保証

- 内部リファレンスまたは外部リファレンス

- ±10mAの出力駆動電流を保証

- 1.8V～5VのSPIシリアル・インターフェース

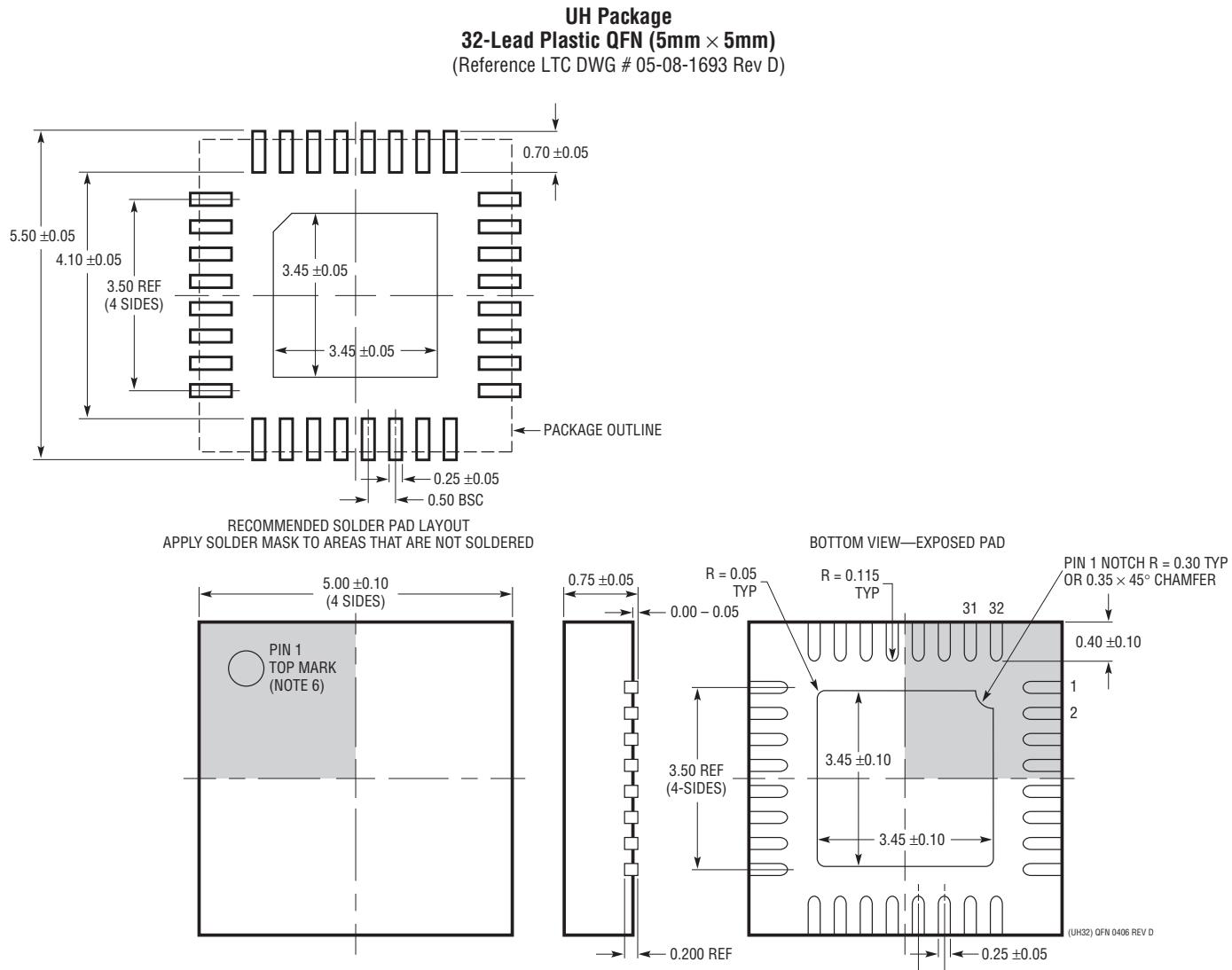

- 32ピン(5mm×5mm)QFNパッケージ

## アプリケーション

- 光通信

- 計測機器

- データ収集

- 自動テスト装置

- プロセス制御および産業用オートメーション

## 概要

LTC<sup>®</sup>2664は、高精度リファレンスを内蔵した、4チャネル、16/12ビット±10Vデジタル/アナログ・コンバータ・ファミリです。これらのデバイスは単調性が保証されており、レール・トゥ・レールの出力バッファを内蔵しています。これらのSoftSpan<sup>TM</sup> D/Aコンバータの出力電圧範囲は、±10Vまでの5種類です。各チャネルの範囲は個別にプログラム可能です。あるいは、デバイスをハードウェアで構成して固定電圧範囲で動作させることもできます。

内蔵の2.5Vリファレンスは各チャネルとは別個にバッファされます。外部リファレンスは追加の範囲オプションとして使用できます。また、LTC2664は専用ピンまたはソフトウェアの切り替えコマンドによるA/Bの切り替え機能も内蔵しています。

SPI/Microwire互換の3線式シリアル・インターフェースは、最小1.71Vのロジック・レベル、最大50MHzのクロック・レートで動作します。

**L**、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。SoftSpanはリニアテクノロジー社の商標です。その他全ての商標の所有権は、それぞれの所有者に帰属します。6891433、5859606、5936245、7671770をはじめとする米国特許によって保護されています。

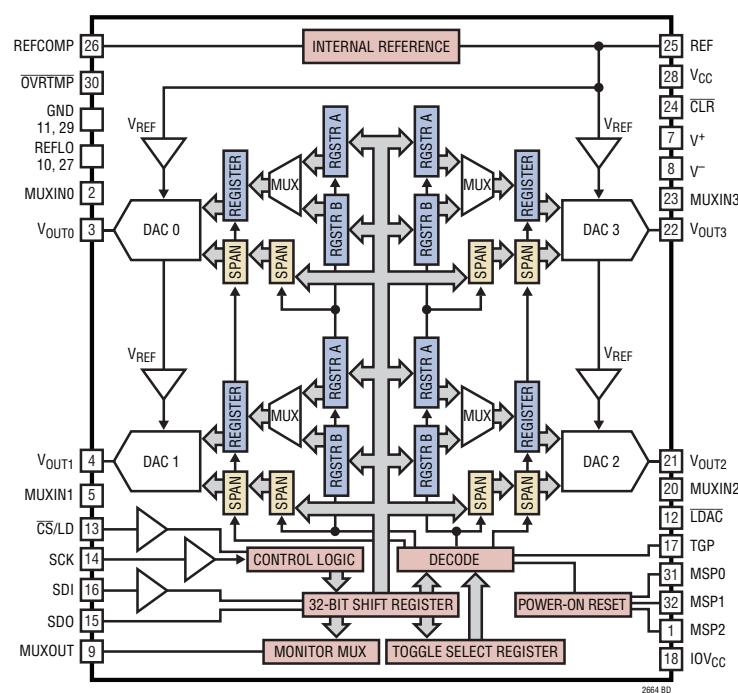

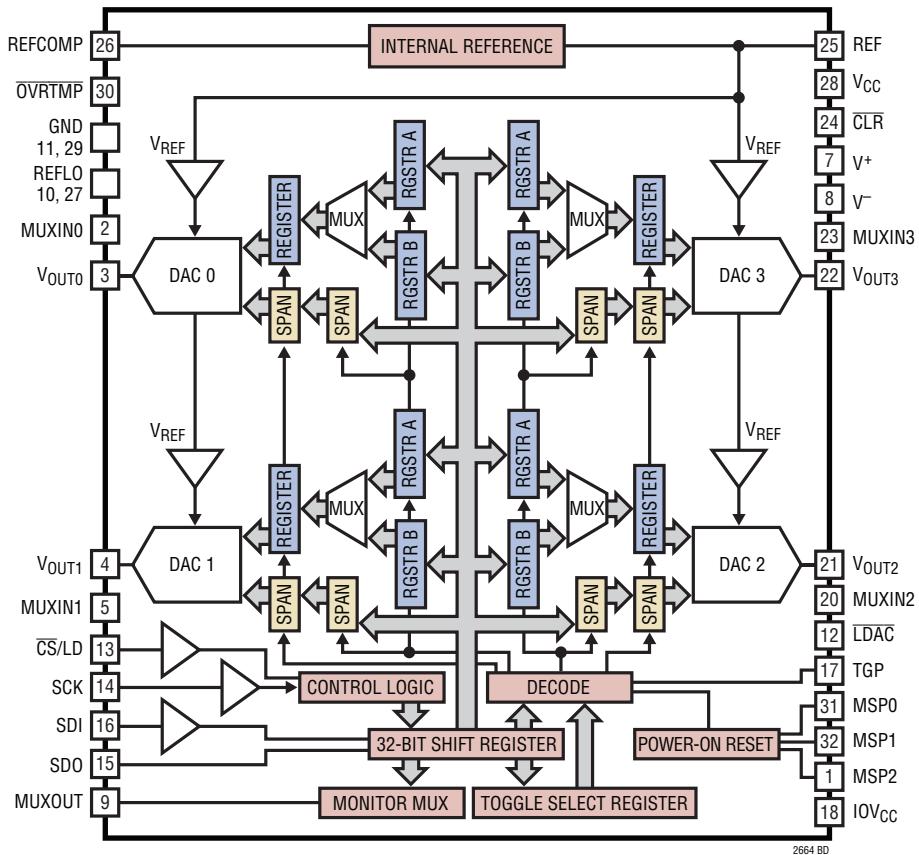

## ブロック図

2664fa

# LTC2664

## 絶対最大定格

(Note 1, 2)

|                                                                        |                                               |

|------------------------------------------------------------------------|-----------------------------------------------|

| アナログ電源電圧( $V_{CC}$ )                                                   | -0.3V ~ 6V                                    |

| デジタルI/O電圧( $IOV_{CC}$ )                                                | -0.3V ~ 6V                                    |

| REFLO                                                                  | -0.3V ~ 0.3V                                  |

| $V^+$                                                                  | -0.3V ~ 16.5V                                 |

| $V^-$                                                                  | -16.5V ~ 0.3V                                 |

| $\overline{CS}/LD$ 、 $SCK$ 、 $SDI$ 、 $\overline{LDAC}$ 、 $CLR$ 、 $TGP$ | -0.3V ~ 6V                                    |

| $MSP0$ 、 $MSP1$ 、 $MSP2$                                               | -0.3V ~ 最小( $V_{CC} + 0.3V$ 、6V)              |

| $V_{OUT0}$ ~ $V_{OUT3}$ 、 $MUXINO$ ~ $MUXIN3$ 、 $MUXOUT$               | $V^- - 0.3V$ ~ $V^+ + 0.3V$ (最大 $\pm 16.5V$ ) |

| REF、REFCOMP                                                            | -0.3V ~ 最小( $V_{CC} + 0.3V$ 、6V)              |

| SDO                                                                    | -0.3V ~ 最小( $IOV_{CC} + 0.3V$ 、6V)            |

| $\overline{OVRTMP}$                                                    | -0.3V ~ 6V                                    |

## 動作温度範囲

|          |               |

|----------|---------------|

| LTC2664C | 0°C ~ 70°C    |

| LTC2664I | -40°C ~ 85°C  |

| LTC2664H | -40°C ~ 125°C |

| 最大接合部温度  | 150°C         |

| 保存温度範囲   | -65°C ~ 150°C |

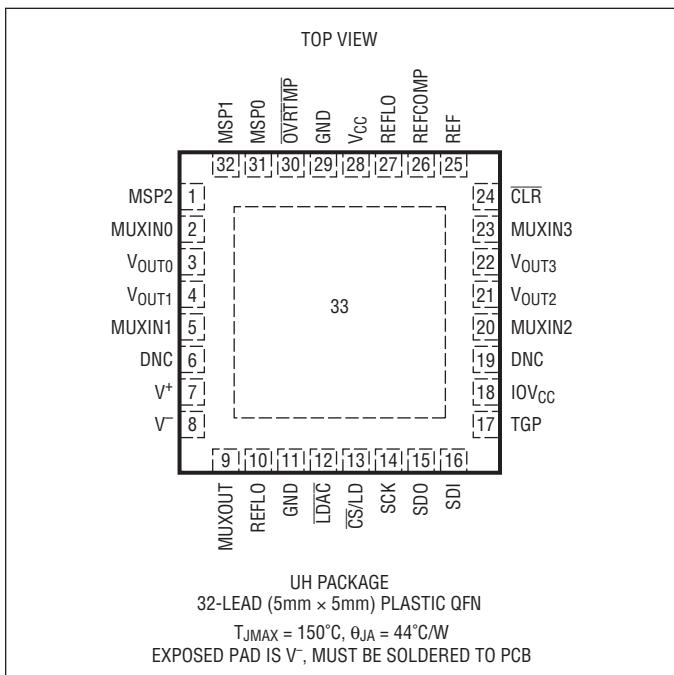

## ピン配置

発注情報 <http://www.linear-tech.co.jp/product/LTC2664#orderinfo>

|         |   |    |    |     |     |                             |

|---------|---|----|----|-----|-----|-----------------------------|

| LTC2664 | C | UH | 16 | #TR | PBF |                             |

|         |   |    |    |     |     | 無鉛指定                        |

|         |   |    |    |     |     | PBF = 無鉛                    |

|         |   |    |    |     |     | テープ・アンド・リール                 |

|         |   |    |    |     |     | TR = 2500個入りテープ・アンド・リール     |

|         |   |    |    |     |     | 分解能                         |

|         |   |    |    |     |     | 16 = 16ビット                  |

|         |   |    |    |     |     | 12 = 12ビット                  |

|         |   |    |    |     |     | パッケージの種類                    |

|         |   |    |    |     |     | UH = 32ピンQFN                |

|         |   |    |    |     |     | 温度グレード                      |

|         |   |    |    |     |     | C = 民生用温度範囲(0°C ~ 70°C)     |

|         |   |    |    |     |     | I = 産業用温度範囲(-40°C ~ 85°C)   |

|         |   |    |    |     |     | H = 自動車用温度範囲(-40°C ~ 125°C) |

|         |   |    |    |     |     | 製品番号                        |

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/>をご覧ください。

テープ・アンド・リールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/>をご覧ください。

一部のパッケージは、#TRMPBF接尾部を付けることにより、指定の販売経路を通じて500個入りのリールで供給可能です。

## 製品選択ガイド

| 無鉛仕上げ             | テープ・アンド・リール         | 製品マーキング* | パッケージ                 | 温度範囲           |

|-------------------|---------------------|----------|-----------------------|----------------|

| LTC2664CUH-16#PBF | LTC2664CUH-16#TRPBF | 266416   | 32-Lead (5mm×5mm) QFN | 0°C ~ 70°C     |

| LTC2664IUH-16#PBF | LTC2664IUH-16#TRPBF | 266416   | 32-Lead (5mm×5mm) QFN | -40°C to 85°C  |

| LTC2664HUH-16#PBF | LTC2664HUH-16#TRPBF | 266416   | 32-Lead (5mm×5mm) QFN | -40°C to 125°C |

| LTC2664CUH-12#PBF | LTC2664CUH-12#TRPBF | 266412   | 32-Lead (5mm×5mm) QFN | 0°C ~ 70°C     |

| LTC2664IUH-12#PBF | LTC2664IUH-12#TRPBF | 266412   | 32-Lead (5mm×5mm) QFN | -40°C to 85°C  |

| LTC2664HUH-12#PBF | LTC2664HUH-12#TRPBF | 266412   | 32-Lead (5mm×5mm) QFN | -40°C to 125°C |

\* 温度グレードは出荷時のコンテナのラベルで識別されます。

**電気的特性** ●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

注記がない限り、 $V_{CC} = 5\text{V}$ 、 $IOV_{CC} = 5\text{V}$ 、 $V^+ = 15\text{V}$ 、 $V^- = -15\text{V}$ 、 $V_{REF} = 2.5\text{V}$ 、 $V_{OUT}$ は無負荷。

## LTC2664-16/LTC2664-12

| SYMBOL       | PARAMETER                                    | CONDITIONS                                 | LTC2664-12 |         |            | LTC2664-16 |         |            | UNITS                 |

|--------------|----------------------------------------------|--------------------------------------------|------------|---------|------------|------------|---------|------------|-----------------------|

|              |                                              |                                            | MIN        | TYP     | MAX        | MIN        | TYP     | MAX        |                       |

| <b>DC 性能</b> |                                              |                                            |            |         |            |            |         |            |                       |

|              | Resolution                                   |                                            | ●          | 12      |            | 16         |         |            | Bits                  |

|              | Monotonicity                                 | All Ranges (Note 3)                        | ●          | 12      |            | 16         |         |            | Bits                  |

| DNL          | Differential Nonlinearity                    | All Ranges (Note 3)                        | ●          |         | $\pm 0.05$ | $\pm 0.5$  |         | $\pm 0.35$ | $\pm 1$               |

| INL          | Integral Nonlinearity<br>All Ranges (Note 3) | $V^+/V^- = \pm 15\text{V}$                 | ●          |         | $\pm 0.2$  | $\pm 1$    |         | $\pm 2.2$  | $\pm 4$               |

|              |                                              | $V^- = \text{GND}$ (Note 3)                | ●          |         | $\pm 0.2$  | $\pm 1$    |         | $\pm 2.2$  | $\pm 4$               |

|              |                                              | C-Grade, I-Grade<br>H-Grade                | ●          |         | $\pm 0.2$  | $\pm 1$    |         | $\pm 2.2$  | $\pm 5$               |

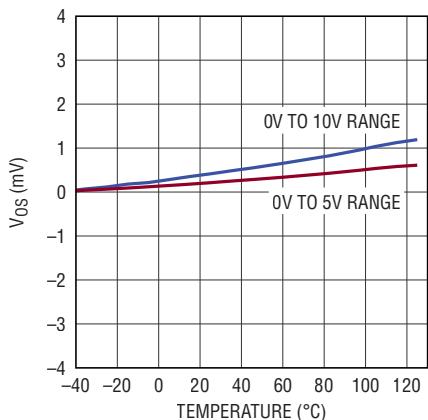

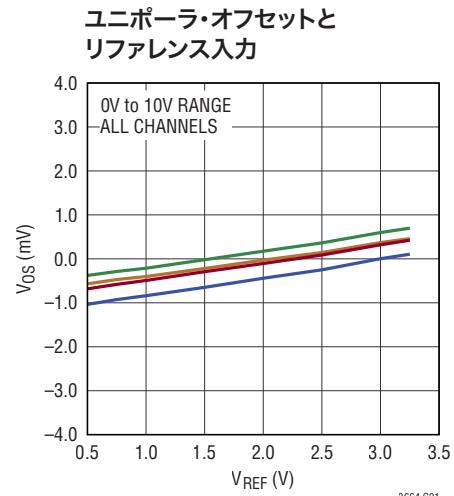

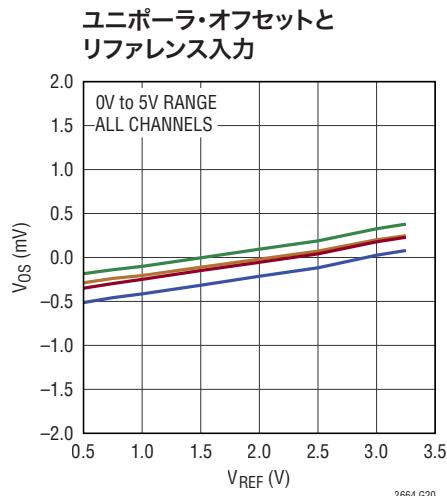

| Vos          | Unipolar Offset Error                        | 0V to 5V Range                             | ●          | $\pm 1$ | $\pm 2$    |            | $\pm 1$ | $\pm 2$    | mV                    |

|              |                                              | 0V to 10V Range                            | ●          | $\pm 2$ | $\pm 4$    |            | $\pm 2$ | $\pm 4$    | mV                    |

|              | Vos Temperature Coefficient                  | All Unipolar Ranges                        |            |         | 1          |            | 1       |            | ppm/ $^\circ\text{C}$ |

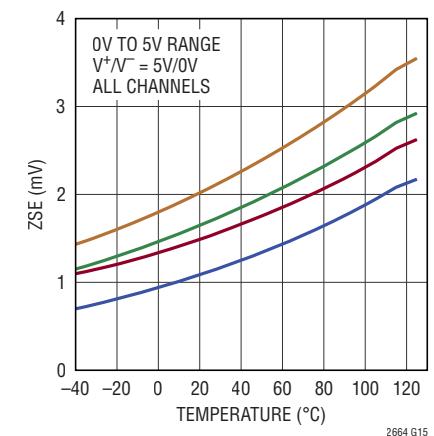

| ZSE          | Single-Supply Zero-Scale Error               | All Unipolar Ranges,<br>$V^- = \text{GND}$ | ●          | 2       | 6          |            | 2       | 6          | mV                    |

| BZE          | Bipolar Zero Error                           | All Bipolar Ranges                         | ●          |         | $\pm 0.02$ | $\pm 0.08$ |         | $\pm 0.02$ | $\pm 0.08$            |

|              | BZE Temperature Coefficient                  | All Bipolar Ranges                         |            |         | 1          |            | 1       |            | ppm/ $^\circ\text{C}$ |

| GE           | Gain Error                                   | All Ranges, External Reference             | ●          |         | $\pm 0.02$ | $\pm 0.08$ |         | $\pm 0.02$ | $\pm 0.08$            |

|              | Gain Temperature Coefficient                 |                                            |            |         | 2          |            | 2       |            | ppm/ $^\circ\text{C}$ |

| PSR          | Power Supply Rejection<br>All Ranges         | $V_{CC} = 5\text{V}, \pm 10\%$             |            |         | 0.1        |            | 1       |            | LSB/V                 |

|              |                                              | $V^+/V^- = \pm 15\text{V}, \pm 5\%$        |            |         | 0.001      |            | 0.01    |            | LSB/V                 |

| SYMBOL           | PARAMETER                                          | CONDITIONS                                                                                                                                                                                              | MIN | TYP           | MAX                           | UNITS                                                     |

|------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------|-------------------------------|-----------------------------------------------------------|

| V <sub>OUT</sub> | Output Voltage Swing                               | To $V^-$ (Unloaded, $V^- = \text{GND}$ )                                                                                                                                                                | ●   | $V^- + 0.004$ | $V^- - 0.004$                 | V                                                         |

|                  |                                                    | To $V^+$ (Unloaded, $V^+ = 5\text{V}$ )                                                                                                                                                                 |     |               |                               |                                                           |

|                  |                                                    | To $V^- (-10\text{mA} \leq I_{OUT} \leq 10\text{mA})$                                                                                                                                                   | ●   | $V^+ - 1.4$   | V                             | V                                                         |

|                  |                                                    | To $V^+ (-10\text{mA} \leq I_{OUT} \leq 10\text{mA})$                                                                                                                                                   | ●   |               |                               |                                                           |

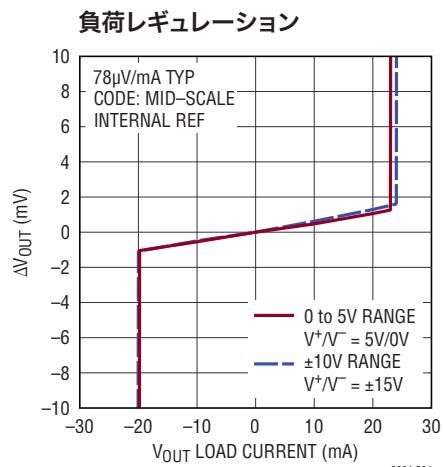

|                  | Load Regulation                                    | $-10\text{mA} \leq I_{OUT} \leq 10\text{mA}$<br>(Note 4)                                                                                                                                                | ●   | 78            | 150                           | $\mu\text{V}/\text{mA}$                                   |

| R <sub>OUT</sub> | DC Output Impedance                                | $-10\text{mA} \leq I_{OUT} \leq 10\text{mA}$<br>(Note 4)                                                                                                                                                | ●   | 0.078         | 0.15                          | $\Omega$                                                  |

|                  |                                                    | DC Crosstalk (Note 5)<br>0V to 5V Range                                                                                                                                                                 |     |               | $\pm 1$<br>$\pm 2$<br>$\pm 4$ | $\mu\text{V}$<br>$\mu\text{V}/\text{mA}$<br>$\mu\text{V}$ |

| I <sub>SC</sub>  | $V^+/V^-$ Short-Circuit Output Current<br>(Note 6) | Due to Full-Scale Output Change<br>Due to Load Current Change<br>Due to Powering Down (per Channel)                                                                                                     |     |               |                               |                                                           |

|                  |                                                    | $V_{CC} = 5.5\text{V}$ , $V^+/V^- = \pm 15.75\text{V}$ , $V_{REF} = 2.5\text{V}$ ,<br>$\pm 10\text{V}$ Output Range<br>Code:Zero-Scale; Forcing Output to GND<br>Code:Full-Scale; Forcing Output to GND | ●   | 16<br>-40     | 42<br>-14.5                   | $\text{mA}$<br>$\text{mA}$                                |

## リファレンス

|                                   |                                                |       |         |          |                        |

|-----------------------------------|------------------------------------------------|-------|---------|----------|------------------------|

| Reference Output Voltage          |                                                | 2.495 | 2.5     | 2.505    | V                      |

| Reference Temperature Coefficient | (Note 7)                                       |       | $\pm 2$ | $\pm 10$ | ppm/ $^\circ\text{C}$  |

| Reference Line Regulation         | $V_{CC} \pm 10\%$                              |       | 50      |          | $\mu\text{V}/\text{V}$ |

| Reference Short-Circuit Current   | $V_{CC} = 5.5\text{V}$ , Forcing Output to GND |       | 2.6     |          | $\text{mA}$            |

| REFCOMP Pin Short-Circuit Current | $V_{CC} = 5.5\text{V}$ , Forcing Output to GND |       | 65      |          | $\mu\text{A}$          |

**電気的特性** ●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

注記がない限り、 $V_{CC} = 5\text{V}$ 、 $IOV_{CC} = 5\text{V}$ 、 $V^+ = 15\text{V}$ 、 $V^- = -15\text{V}$ 、 $V_{REF} = 2.5\text{V}$ 、 $V_{OUT}$ は無負荷。

| SYMBOL | PARAMETER                              | CONDITIONS                                                          | MIN | TYP   | MAX             | UNITS                        |

|--------|----------------------------------------|---------------------------------------------------------------------|-----|-------|-----------------|------------------------------|

|        | Reference Load Regulation              | $V_{CC} = 5\text{V} \pm 10\%$ , $I_{OUT} = 100\mu\text{A}$ Sourcing |     | 140   |                 | $\text{mV}/\text{mA}$        |

|        | Reference Output Voltage Noise Density | $C_{REFCOMP} = C_{REF} = 0.1\mu\text{F}$ , at $f = 10\text{kHz}$    |     | 32    |                 | $\text{nV}/\sqrt{\text{Hz}}$ |

|        | Reference Input Range                  | External Reference Mode (Note 8)                                    | ●   | 0.5   | $V_{CC} - 1.75$ | V                            |

|        | Reference Input Current                | External Reference                                                  | ●   | 0.001 | 1               | $\mu\text{A}$                |

|        | Reference Input Capacitance (Note 9)   |                                                                     | ●   | 40    |                 | $\text{pF}$                  |

## 電源

|               |                                     |                                                                                                     |        |             |                |               |

|---------------|-------------------------------------|-----------------------------------------------------------------------------------------------------|--------|-------------|----------------|---------------|

| $V_{CC}$      | Analog Supply Voltage               |                                                                                                     | ●      | 4.5         | 5.5            | V             |

| $V^+$         | Analog Positive Supply              |                                                                                                     | ●      | 4.5         | 15.75          | V             |

| $V^-$         | Analog Negative Supply              | $V^-$ Not Tied to GND<br>$V^-$ Tied to GND                                                          | ●      | -15.75<br>0 | -4.5           | V             |

| $IOV_{CC}$    | Digital I/O Supply Voltage          |                                                                                                     | ●      | 1.71        | $V_{CC} + 0.3$ | V             |

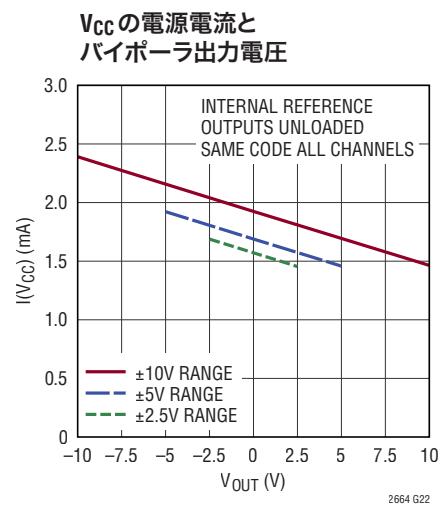

| $I(V_{CC})$   | Supply Current $V_{CC}$             | $V_{CC} = 5\text{V}$ , Unipolar Ranges (Note 10)<br>$V_{CC} = 5\text{V}$ , Bipolar Ranges (Note 10) | ●<br>● | 1.6<br>2.7  | 2.1<br>3.2     | $\text{mA}$   |

| $I_s$         | Supply Current $V^+/V^-$            | Unipolar Ranges (Code = 0)<br>Bipolar Ranges (Note 11)                                              | ●<br>● | 1.3<br>2.3  | 1.8<br>2.7     | $\text{mA}$   |

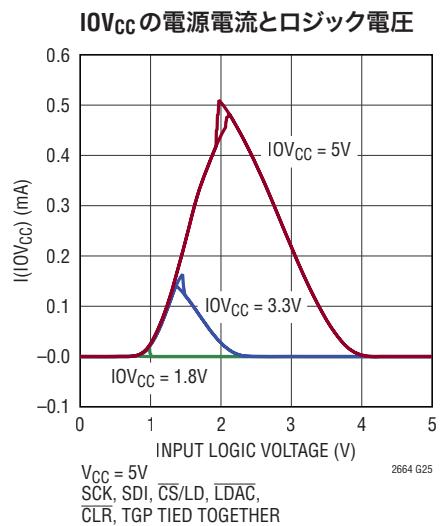

| $I(IOV_{CC})$ | Supply Current $IOV_{CC}$ (Note 12) | $IOV_{CC} = 5\text{V}$                                                                              | ●      | 0.02        | 1              | $\mu\text{A}$ |

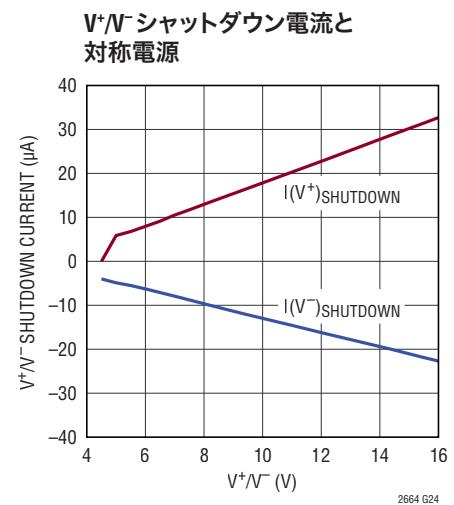

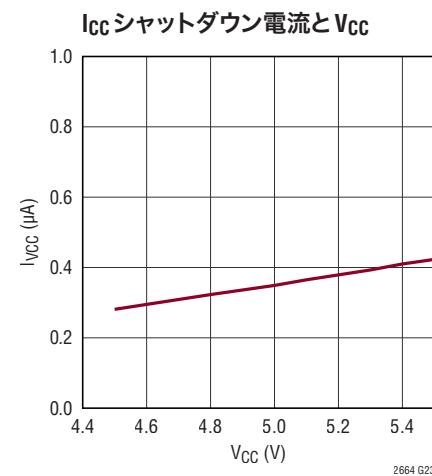

|               | $V_{CC}$ Shutdown Supply Current    | $IOV_{CC} = V_{CC} = 5\text{V}$ , $V^+/V^- = \pm 15\text{V}$                                        | ●      | 1           | 10             | $\mu\text{A}$ |

|               | $V^+$ Shutdown Supply Current       | $IOV_{CC} = V_{CC} = 5\text{V}$ , $V^+/V^- = \pm 15\text{V}$                                        | ●      | 35          | 70             | $\mu\text{A}$ |

|               | $V^-$ Shutdown Supply Current       | $IOV_{CC} = V_{CC} = 5\text{V}$ , $V^+/V^- = \pm 15\text{V}$                                        | ●      | -60         | -27            | $\mu\text{A}$ |

## アナログ・マルチプレクサ

|  |                                        |                                      |   |       |                  |               |

|--|----------------------------------------|--------------------------------------|---|-------|------------------|---------------|

|  | Analog Mux DC Output Impedance         |                                      |   | 2.2   | $\text{k}\Omega$ |               |

|  | Analog Mux Leakage Current             | Analog Mux Disabled (High Impedance) | ● | 0.02  | 1                | $\mu\text{A}$ |

|  | Analog Mux Output Voltage Range        | Analog Mux Selected to DAC Channel   | ● | $V^-$ | $V^+ - 1.4$      | V             |

|  | Analog Mux Continuous Current (Note 9) |                                      | ● |       | $\pm 1$          | $\text{mA}$   |

## 温度モニタ

|  |                         |                        |  |      |                            |

|--|-------------------------|------------------------|--|------|----------------------------|

|  | Initial Voltage         | $T = 25^\circ\text{C}$ |  | 1.4  | V                          |

|  | Temperature Coefficient |                        |  | -3.7 | $\text{mV}/^\circ\text{C}$ |

## AC性能

|           |                                                                                         |                                                                                                                                           |  |                       |                                                                                                      |

|-----------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|-----------------------|------------------------------------------------------------------------------------------------------|

| $t_{SET}$ | Settling Time (Notes 9, 13)<br>0V to 5V or $\pm 2.5\text{V}$ Span, $\pm 5\text{V}$ Step | $\pm 0.024\%$ ( $\pm 1\text{LSB}$ at 12 Bits)<br>$\pm 0.0015\%$ ( $\pm 1\text{LSB}$ at 16 Bits)                                           |  | 4.5<br>9              | $\mu\text{s}$                                                                                        |

|           | Settling Time (Notes 9, 13)<br>0V to 10V or $\pm 5\text{V}$ Span, $\pm 10\text{V}$ Step | $\pm 0.024\%$ ( $\pm 1\text{LSB}$ at 12 Bits)<br>$\pm 0.0015\%$ ( $\pm 1\text{LSB}$ at 16 Bits)                                           |  | 8<br>9.5              | $\mu\text{s}$                                                                                        |

|           | Settling Time (Notes 9, 13)<br>$\pm 10\text{V}$ Span, $\pm 20\text{V}$ Step             | $\pm 0.024\%$ ( $\pm 1\text{LSB}$ at 12 Bits)<br>$\pm 0.0015\%$ ( $\pm 1\text{LSB}$ at 16 Bits)                                           |  | 15.5<br>20            | $\mu\text{s}$                                                                                        |

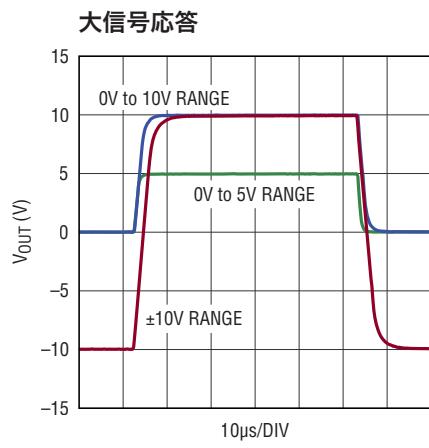

| $SR$      | Voltage Output Slew Rate                                                                |                                                                                                                                           |  | 5                     | $\text{V}/\mu\text{s}$                                                                               |

|           | Capacitive Load Driving                                                                 | No Oscillation                                                                                                                            |  | 1000                  | $\text{pF}$                                                                                          |

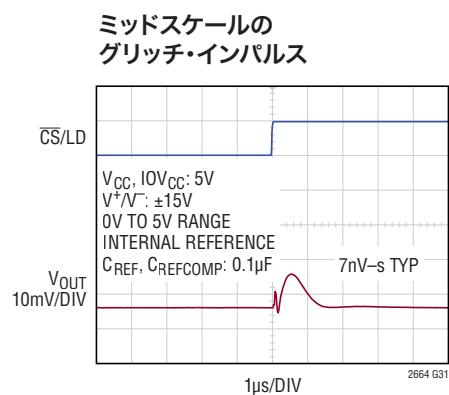

|           | Glitch Impulse (Note 14)                                                                | At Mid-Scale Transition, 0V to 5V Range                                                                                                   |  | 7                     | $\text{nV} \cdot \text{s}$                                                                           |

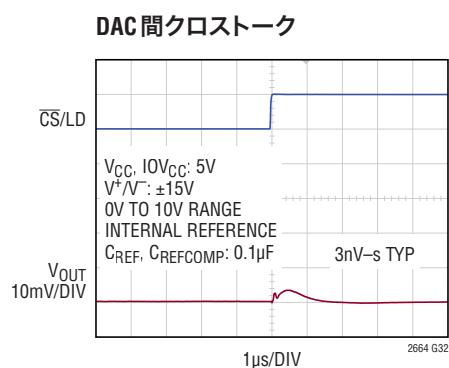

|           | DAC-to-DAC Crosstalk (Note 15)                                                          | Due to Full-Scale Output Change                                                                                                           |  | 3.5                   | $\text{nV} \cdot \text{s}$                                                                           |

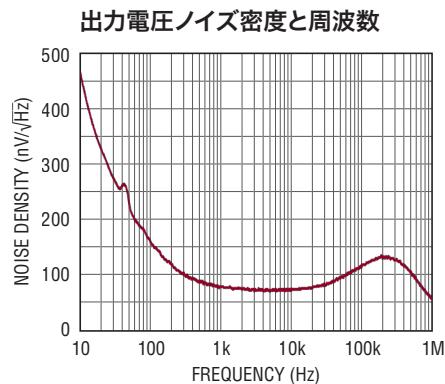

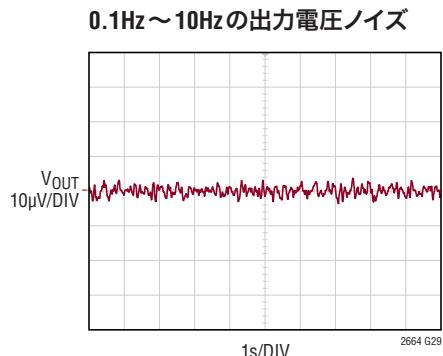

| $e_n$     | Output Voltage Noise<br>0V to 5V Output Span,<br>Internal Reference                     | Density at $f = 1\text{kHz}$<br>Density at $f = 10\text{kHz}$<br>0.1Hz to 10Hz, Internal Reference<br>0.1Hz to 200kHz, Internal Reference |  | 90<br>80<br>1.7<br>55 | $\text{nV}/\sqrt{\text{Hz}}$<br>$\text{nV}/\sqrt{\text{Hz}}$<br>$\mu\text{VRMS}$<br>$\mu\text{VRMS}$ |

2664fa

**電気的特性** ●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

注記がない限り、 $V_{CC} = 5\text{V}$ 、 $IOV_{CC} = 5\text{V}$ 、 $V^+ = 15\text{V}$ 、 $V^- = -15\text{V}$ 、 $V_{REF} = 2.5\text{V}$ 、 $V_{OUT}$ は無負荷。

| SYMBOL                                                                          | PARAMETER                             | CONDITIONS                                                                                                    | MIN    | TYP                  | MAX          | UNITS                          |

|---------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------|--------|----------------------|--------------|--------------------------------|

| <b>デジタルI/O</b>                                                                  |                                       |                                                                                                               |        |                      |              |                                |

| $V_{CC} = 4.5\text{V} \sim 5.5\text{V}$ 、 $IOV_{CC} = 1.71\text{V} \sim V_{CC}$ |                                       |                                                                                                               |        |                      |              |                                |

| $V_{OH}$                                                                        | Digital Output High Voltage           | SDO Pin.Load Current = $-100\mu\text{A}$                                                                      | ●      | $IOV_{CC} - 0.2$     |              | V                              |

| $V_{OL}$                                                                        | Digital Output Low Voltage            | SDO Pin.Load Current = $100\mu\text{A}$<br>$\overline{OVR TMP}$ Pin.Load Current = $100\mu\text{A}$           | ●<br>● |                      | 0.2<br>0.2   | V<br>V                         |

| $I_{OZ}$                                                                        | Digital Hi-Z Output Leakage           | SDO Pin Leakage Current ( $\overline{CS}/LD$ High)<br>$\overline{OVR TMP}$ Pin Leakage Current (Not Asserted) | ●<br>● |                      | $\pm 1$<br>1 | $\mu\text{A}$<br>$\mu\text{A}$ |

| $I_{ILK}$                                                                       | Digital Input Leakage                 | $V_{IN} = \text{GND}$ to $IOV_{CC}$                                                                           | ●      |                      | $\pm 1$      | $\mu\text{A}$                  |

| $C_{IN}$                                                                        | Digital Input Capacitance<br>(Note 9) |                                                                                                               | ●      |                      | 8            | pF                             |

| <b><math>IOV_{CC} = 2.7\text{V}</math> to <math>V_{CC}</math></b>               |                                       |                                                                                                               |        |                      |              |                                |

| $V_{IH}$                                                                        | Digital Input High Voltage            |                                                                                                               | ●      | $0.8 \cdot IOV_{CC}$ |              | V                              |

| $V_{IL}$                                                                        | Digital Input Low Voltage             |                                                                                                               | ●      |                      | 0.5          | V                              |

| <b><math>IOV_{CC} = 1.71\text{V} \sim 2.7\text{V}</math></b>                    |                                       |                                                                                                               |        |                      |              |                                |

| $V_{IH}$                                                                        | Digital Input High Voltage            |                                                                                                               | ●      | $0.8 \cdot IOV_{CC}$ |              | V                              |

| $V_{IL}$                                                                        | Digital Input Low Voltage             |                                                                                                               | ●      |                      | 0.3          | V                              |

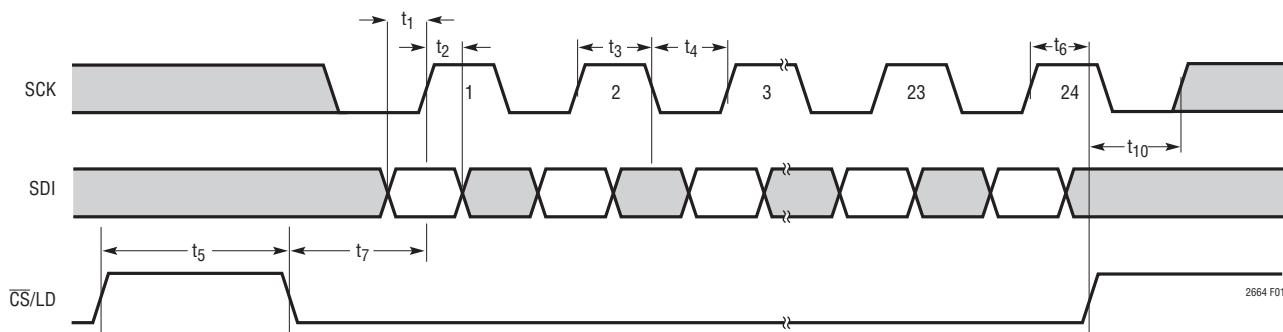

**タイミング特性** ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

デジタル入力の“L”電圧と“H”電圧はそれぞれ0Vと $IOV_{CC}$ 。

## LTC2664-16/LTC2664-12

| SYMBOL                                                                                                    | PARAMETER                                              | CONDITIONS                                                                                                    | MIN    | TYP | MAX      | UNITS         |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------|-----|----------|---------------|

| <b><math>V_{CC} = 4.5\text{V} \sim 5.5\text{V}</math>、<math>IOV_{CC} = 2.7\text{V} \sim V_{CC}</math></b> |                                                        |                                                                                                               |        |     |          |               |

|                                                                                                           |                                                        |                                                                                                               |        |     |          |               |

| $t_1$                                                                                                     | SDI Valid to SCK Setup                                 |                                                                                                               | ●      | 6   |          | ns            |

| $t_2$                                                                                                     | SDI Valid to SCK Hold                                  |                                                                                                               | ●      | 6   |          | ns            |

| $t_3$                                                                                                     | SCK HIGH Time                                          |                                                                                                               | ●      | 9   |          | ns            |

| $t_4$                                                                                                     | SCK LOW Time                                           |                                                                                                               | ●      | 9   |          | ns            |

| $t_5$                                                                                                     | $\overline{CS}/LD$ Pulse Width                         |                                                                                                               | ●      | 10  |          | ns            |

| $t_6$                                                                                                     | LSB SCK High to $\overline{CS}/LD$ High                |                                                                                                               | ●      | 7   |          | ns            |

| $t_7$                                                                                                     | $\overline{CS}/LD$ Low to SCK High                     |                                                                                                               | ●      | 7   |          | ns            |

| $t_8$                                                                                                     | SDO Propagation Delay from SCK Falling Edge            | $C_{LOAD} = 10\text{pF}$<br>$IOV_{CC} = 4.5\text{V}$ to $V_{CC}$<br>$IOV_{CC} = 2.7\text{V}$ to $4.5\text{V}$ | ●<br>● |     | 20<br>30 | ns            |

| $t_9$                                                                                                     | CLR Pulse Width                                        |                                                                                                               | ●      | 20  |          | ns            |

| $t_{10}$                                                                                                  | $\overline{CS}/LD$ High to SCK Positive Edge           |                                                                                                               | ●      | 7   |          | ns            |

| $t_{12}$                                                                                                  | LDAC Pulse Width                                       |                                                                                                               | ●      | 15  |          | ns            |

| $t_{13}$                                                                                                  | $\overline{CS}/LD$ High to LDAC High or Low Transition |                                                                                                               | ●      | 15  |          | ns            |

|                                                                                                           | SCK Frequency                                          | 50% Duty Cycle                                                                                                | ●      |     | 50       | MHz           |

| $t_{14}$                                                                                                  | TGP High Time (Note 9)                                 |                                                                                                               | ●      | 1   |          | $\mu\text{s}$ |

| $t_{15}$                                                                                                  | TGP Low Time (Note 9)                                  |                                                                                                               | ●      | 1   |          | $\mu\text{s}$ |

## タイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

デジタル入力の“L”電圧と“H”電圧はそれぞれ0Vと $\text{IOV}_{\text{CC}}$ 。

## LTC2664-16/LTC2664-12

| SYMBOL                                                                                                           | PARAMETER                                                 | CONDITIONS                      | MIN | TYP | MAX | UNITS         |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------|-----|-----|-----|---------------|

| $\text{V}_{\text{CC}} = 4.5\text{V} \sim 5.5\text{V}$ 、 $\text{IOV}_{\text{CC}} = 1.71\text{V} \sim 2.7\text{V}$ |                                                           |                                 |     |     |     |               |

| t1                                                                                                               | SDI Valid to SCK Setup                                    |                                 | ●   | 7   |     | ns            |

| t2                                                                                                               | SDI Valid to SCK Hold                                     |                                 | ●   | 7   |     | ns            |

| t3                                                                                                               | SCK HIGH Time                                             |                                 | ●   | 30  |     | ns            |

| t4                                                                                                               | SCK LOW Time                                              |                                 | ●   | 30  |     | ns            |

| t5                                                                                                               | $\bar{CS}/LD$ Pulse Width                                 |                                 | ●   | 15  |     | ns            |

| t6                                                                                                               | LSB SCK High to $\bar{CS}/LD$ High                        |                                 | ●   | 7   |     | ns            |

| t7                                                                                                               | $\bar{CS}/LD$ Low to SCK High                             |                                 | ●   | 7   |     | ns            |

| t8                                                                                                               | SDO Propagation Delay from SCK Falling Edge               | $C_{\text{LOAD}} = 10\text{pF}$ | ●   |     | 60  | ns            |

| t9                                                                                                               | CLR Pulse Width                                           |                                 | ●   | 30  |     | ns            |

| t10                                                                                                              | $\bar{CS}/LD$ High to SCK Positive Edge                   |                                 | ●   | 7   |     | ns            |

| t12                                                                                                              | $\bar{LDAC}$ Pulse Width                                  |                                 | ●   | 15  |     | ns            |

| t13                                                                                                              | $\bar{CS}/LD$ High to $\bar{LDAC}$ High or Low Transition |                                 | ●   | 15  |     | ns            |

|                                                                                                                  | SCK Frequency                                             | 50% Duty Cycle                  | ●   |     | 15  | MHz           |

| t14                                                                                                              | TGP High Time (Note 9)                                    |                                 | ●   | 1   |     | $\mu\text{s}$ |

| t15                                                                                                              | TGP Low Time (Note 9)                                     |                                 | ●   | 1   |     | $\mu\text{s}$ |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与えるおそれがある。

**Note 2:** 全ての電圧値はGNDを基準にしている。

**Note 3:**  $V^* = \text{GND}$ の場合、直線性はコード $k_L$ からコード $2^N - 1$ まで定義される。ここで、Nは分解能。 $k_L$ は出力制限が生じない下端のコード。 $V_{\text{REF}} = 2.5\text{V}$ およびN = 16の場合、 $k_L = 128$ となり、直線性はコード128からコード65,535まで定義される。 $V_{\text{REF}} = 2.5\text{V}$ およびN = 12の場合、 $k_L = 8$ となり、直線性はコード8からコード4095まで定義される。

**Note 4:**  $4.5\text{V} \leq V^* \leq 16.5\text{V}$ 、 $-16.5\text{V} \leq V^* \leq -4.5\text{V}$ または $V^* = \text{GND}$ 。 $V_{\text{OUT}}$ は少なくとも $V^*$ より1.4Vより低く、 $V^*$ より1.4V高い。

**Note 5:** DCクロストークは、 $\text{V}_{\text{CC}} = 5\text{V}$ で内部リファレンスを使って測定される。1つのDACチャネルの状態は規定どおりに変化し、隣接するチャネルのミッドスケールでの出力は変化の前後で測定される。

**Note 6:** このデバイスは短時間の過負荷状態の間デバイスを保護するための電流制限回路を内蔵している。電流制限時には接合部温度が最大定格を超えることがある。規定された最大動作接合部温度を超えた状態で動作が継続すると、デバイスの信頼性を損なう恐れがある。

**Note 7:** 温度係数は、まず、出力電圧の最大変化と公称出力電圧の比を計算することによって求められる。次に、この比を規定温度範囲で割る。

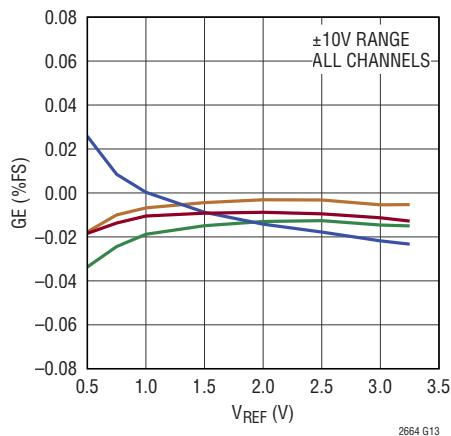

**Note 8:** 利得誤差およびバイポーラ・ゼロ誤差の仕様は、1.25Vより低いリファレンス入力電圧ではグレードが下がることがある。「標準的性能特性」のセクションの「利得誤差とリファレンス入力」と「バイポーラ・ゼロとリファレンス入力」の曲線を参照。

**Note 9:** 設計によって保証されているが、製造時にはテストされない。

**Note 10:** 内部リファレンス。

**Note 11:**  $(V^*)$ は $\pm 10\text{V}$ スパンで測定、出力無負荷、全てのチャネルはフルスケール。 $I(V^*)$ は $\pm 10\text{V}$ スパンで測定、出力無負荷、全てのチャネルは負のフルスケール。各DACのアンプは内部に $40\text{k}\Omega$ の帰還回路網の負荷があるので、出力電圧が0Vから変化するにつれて電源電流が増加する。

**Note 12:** 0Vまたは $\text{IOV}_{\text{CC}}$ でのデジタル入力。

**Note 13:** 内部リファレンス。負荷は $2\text{k}$ で $100\text{pF}$ と並列にGNDに接続する。

**Note 14:**  $\text{V}_{\text{CC}} = 5\text{V}$ 、 $0\text{V} \sim 5\text{V}$ の範囲、内部リファレンス・モード。DACは、ハーフスケールとハーフスケール-1LSBの間を $\pm 1\text{LSB}$ でステップさせる。負荷は $2\text{k}$ で $200\text{pF}$ と並列にGNDに接続する。

**Note 15:** DAC間のクロストークは、あるDACの出力のフルスケールの変化によって別のDACの出力に現れるグリッチである。 $0\text{V} \sim 10\text{V}$ の範囲で内部リファレンスを使用し、ミッドスケールのDACで測定される。

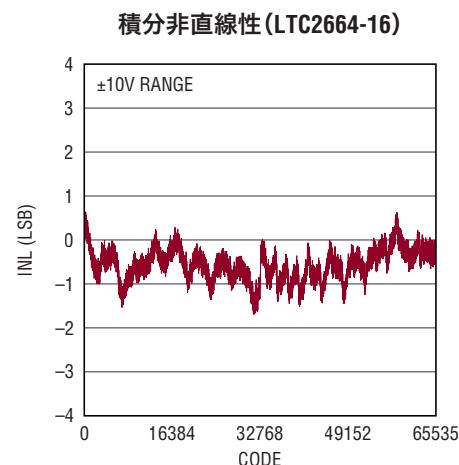

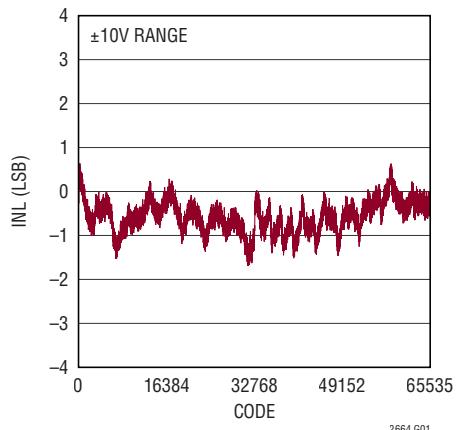

## 標準的性能特性 注記がない限り、TA = 25°C。

LTC2664-16

### 積分非直線性 (INL)

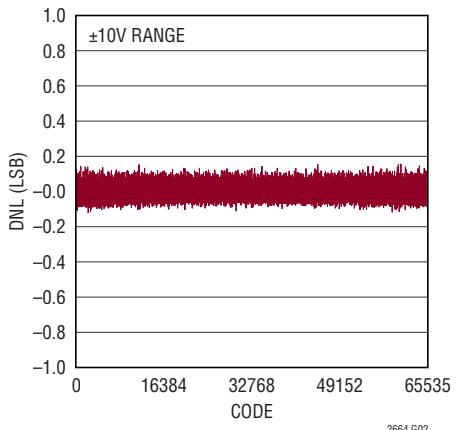

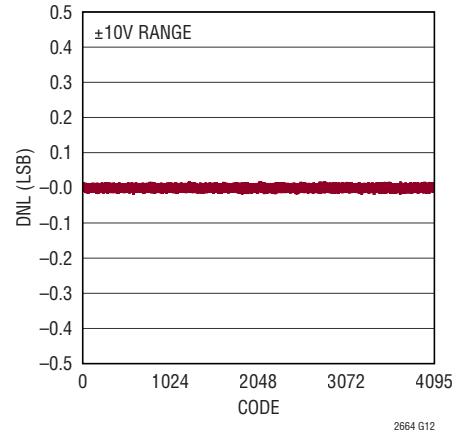

### 微分非直線性 (DNL)

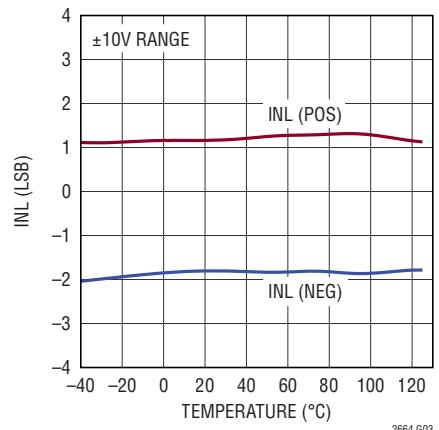

### INL と 温度

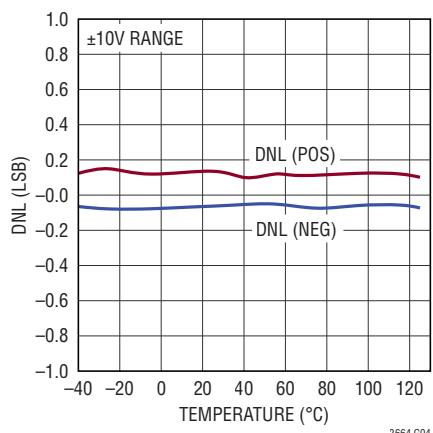

### DNL と 温度

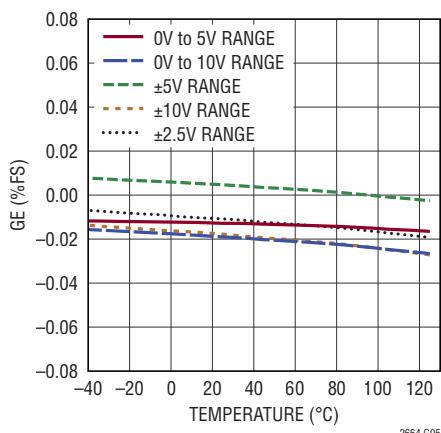

### 利得誤差と 温度

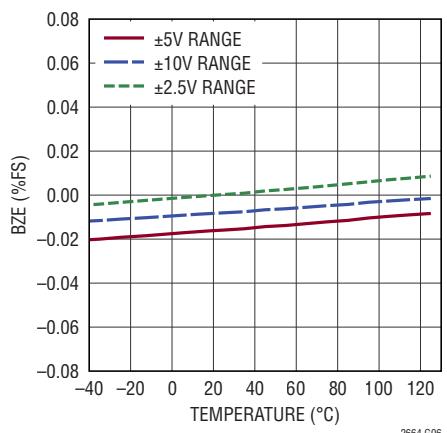

### バイポーラ・ゼロ誤差と 温度

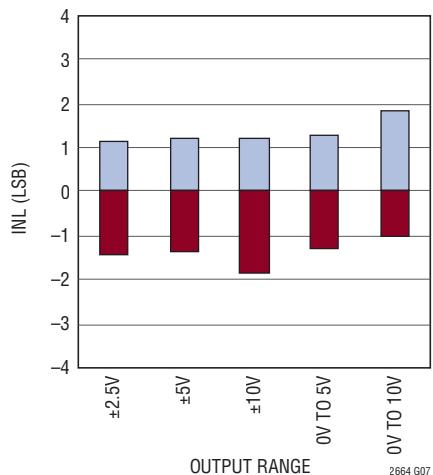

### INL と 出力範囲

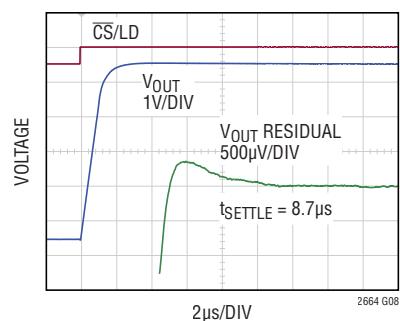

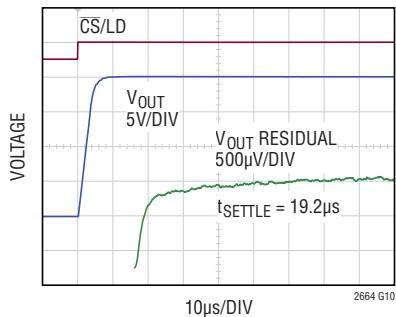

### 5Vステップのセッティング

OV TO 5V RANGE; INTERNAL REFERENCE RISING 5V STEP; AVERAGE OF 128 EVENTS FALLING SETTLING IS SIMILAR OR BETTER RESIDUAL WAVEFORM INCLUDES 100ns FIXTURE DELAY

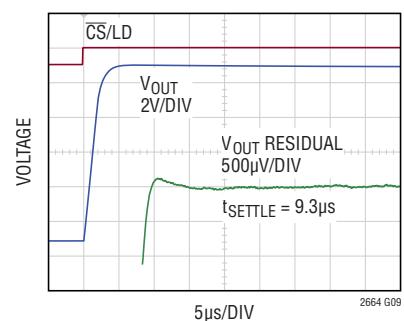

### 10Vステップのセッティング

OV TO 10V RANGE; INTERNAL REFERENCE RISING 10V STEP; AVERAGE OF 128 EVENTS FALLING SETTLING IS SIMILAR OR BETTER RESIDUAL WAVEFORM INCLUDES 100ns FIXTURE DELAY

2664fa

標準的性能特性 注記がない限り、TA = 25°C。

## 20Vステップのセッティング

±10V RANGE; INTERNAL REFERENCE

RISING 20V STEP; AVERAGE OF 64 EVENTS

FALLING SETTLING IS SIMILAR OR BETTER

RESIDUAL WAVEFORM INCLUDES

100ns FIXTURE DELAY

## LTC2664-16/LTC2664-12

## 利得誤差とリファレンス入力

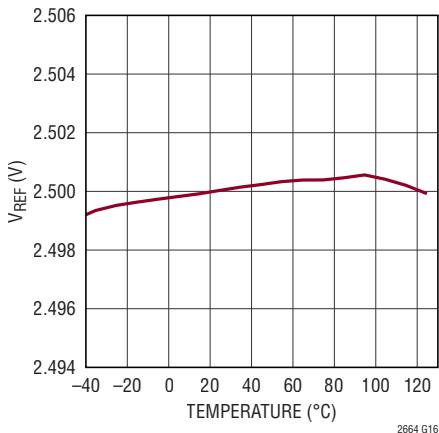

## リファレンス出力と温度

積分非直線性(INL)

(LTC2664-12)微分非直線性(DNL)

(LTC2664-12)

## 単電源のゼロスケール誤差と温度

## ユニポーラ・オフセットと温度

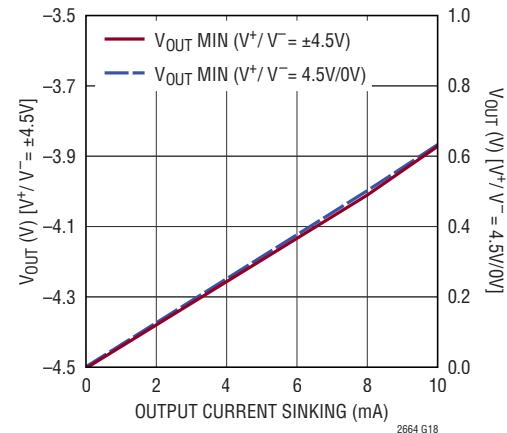

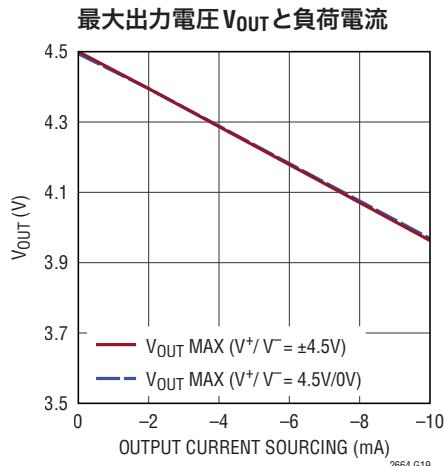

最小出力電圧V<sub>OH</sub>と負荷電流

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 。

LTC2664-16/LTC2664-12

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 。

LTC2664-16/LTC2664-12

$V_{CC} = 5\text{V}$ ;  $V^+/V^- = \pm 15\text{V}$

0V TO 5V RANGE

CODE = MID-SCALE

INTERNAL REFERENCE

$C_{REF} = C_{REFCOMP} = 0.1\mu\text{F}$

$V_{CC} = 5\text{V}$ ;  $V^+/V^- = \pm 15\text{V}$

0V TO 5V RANGE

CODE = MID-SCALE

INTERNAL REFERENCE

$C_{REF} = C_{REFCOMP} = 0.1\mu\text{F}$

$V_{CC} = 5\text{V}$ ;  $V^+/V^- = \pm 15\text{V}$

$V_{REF} = 2.5\text{V}$  (INTERNAL REFERENCE)

$C_{REF} = C_{REFCOMP} = 0.1\mu\text{F}$

RISING MAJOR CARRY TRANSITION

FALLING TRANSITION IS SIMILAR OR BETTER

ALL CHANNELS ARE SIMILAR OR BETTER

10V TO 0V FALLING STEP:  $V_{OUT1}$

MEASURED CHANNEL:  $V_{OUT0}$

RISING STEP IS SIMILAR OR BETTER

ALL CHANNELS ARE SIMILAR OR BETTER

2664fa

## ピン機能

**MSP2(ピン1)** : MSPANビット2。このピンをV<sub>CC</sub>またはGNDに接続して、4チャネル全てのパワーオン・スパンとパワーオンリセット・コードを選択します(表4を参照)。

**MUXIN0～MUXIN3(ピン2、5、20、23)** : アナログ・マルチプレクサの補助入力。このピンを使用して、外部電圧が適合範囲内(V<sup>-</sup>～V<sup>+</sup> - 1.4V)に入っていることをモニタすることができます。使用しない場合は、GNDに接続します。

**V<sub>OUT0</sub>～V<sub>OUT3</sub>(ピン3、4、21、22)** : DACのアナログ電圧出力。

**DNC(ピン6、19)** : 何も接続しないでください。

**V<sup>+</sup>(ピン7)** : アナログ正電源。標準で15V (4.5V～15.75Vの範囲)。1μFのコンデンサを使ってGNDにバイパスします。

**V<sup>-</sup>(ピン8)** : アナログ負電源。標準で-15V (-4.5V～-15.75Vの範囲)、またはGNDに接続可。V<sup>-</sup>がGNDに接続されていない限り、1μFのコンデンサを使ってGNDにバイパスします。

**MUXOUT(ピン9)** : アナログ・マルチプレクサ出力。V<sub>OUT0</sub>～V<sub>OUT3</sub>、MUXIN0～MUXIN3、REFLO、REF、V<sup>+</sup>、V<sup>-</sup>、および温度モニタ出力は内部でMUXOUTピンに配線することができます。マルチプレクサがディスエーブルされると、このピンは高インピーダンスになります。

**REFLO(ピン10、27)** : リファレンス“L”ピン。リファレンスおよびDAC出力の信号グランド。これらのピンはGNDに接続してください。

**GND(ピン11、29)** : アナログ・グランド。ノイズのないアナログ・グランド・プレーンに接続します。

**LDAC(ピン12)** : アクティブ“L”的非同期DAC更新ピン。CS/LDが“H”的とき、LDACの立ち下がりエッジにより、全てのDACレジスタが入力レジスタAからのデータに更新されます(ソフトウェアの更新と同様)。CS/LDが“L”的ときにLDACが“L”になると、CS/LDが“H”に戻った後にDACレジスタが更新されます。LDACピンが“L”になると、DACがシワーラップします。LDACが“L”的場合、ソフトウェアのパワーダウン・コマンドは無視されます。ロジック・レベルはIOV<sub>CC</sub>によって決まります。

LDACを使用しない場合は“H”に(IOV<sub>CC</sub>に)接続します。この場合、更新はSPIコマンドによって実行できます(表1を参照)。

**CS/LD(ピン13)** : シリアル・インターフェースのチップ・セレクト/負荷入力。CS/LDが“L”的とき、SCKがイネーブルされ、SDIのデータをレジスタにシフトします。CS/LDを“H”にすると、SCKはディスエーブルされ、指定されたコマンド(表1を参照)が実行されます。ロジック・レベルはIOV<sub>CC</sub>によって決まります。

**SCK(ピン14)** : シリアル・インターフェースのクロック入力。ロジック・レベルはIOV<sub>CC</sub>によって決まります。

**SDO(ピン15)** : シリアル・インターフェースのデータ出力。32ビット・シフトレジスタのシリアル出力はSDOピンから出力されます。SDIピンを介してデバイスに転送されたデータは、SCKの32の立ち上がりエッジだけ遅れてから、次の立ち下がりエッジで出力されます。データのエコー読み出しままたはデイジーチェーン動作に使用することができます(プルアップ/プルダウン抵抗が必要)。CS/LDが“H”的とき、SDOピンは高インピーダンスになります。ロジック・レベルはIOV<sub>CC</sub>によって決まります。

**SDI(ピン16)** : シリアル・インターフェースのデータ入力。SDIのデータはSCKの立ち上がりエッジでDACにクロックインされます。LTC2664は24ビットまたは32ビットの入力ワード長を受け入れます。ロジック・レベルはIOV<sub>CC</sub>によって決まります。

**TGP(ピン17)** : 非同期切り替えピン。立ち下がりエッジでは、DACレジスタは入力レジスタAからのデータに更新されます。立ち上がりエッジでは、DACレジスタは入力レジスタBからのデータに更新されます。切り替え操作が影響するのは、切り替え選択ビット(Tx)が1に設定されているDACチャネルだけです。ソフトウェアによって切り替え操作を行う場合は、TGPピンをIOV<sub>CC</sub>に接続します。切り替え操作を行わない場合、TGPピンはGNDに接続します。ロジック・レベルはIOV<sub>CC</sub>によって決まります。

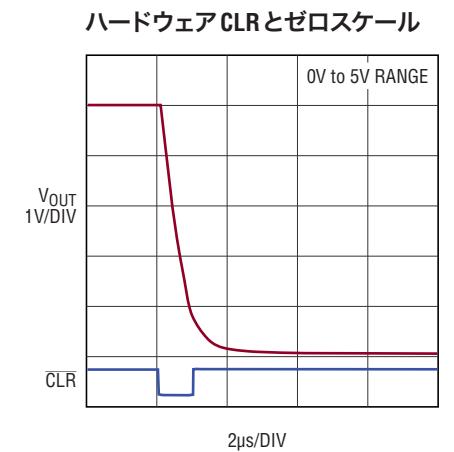

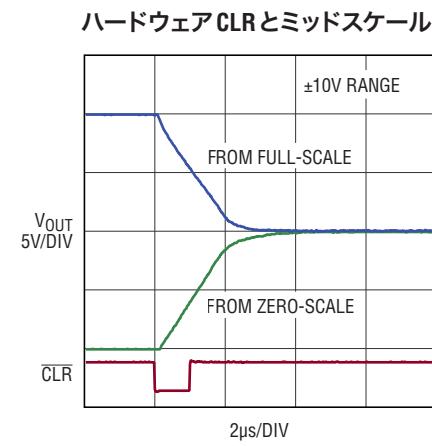

**CLR(ピン24)** : アクティブ“L”的非同期クリア入力。このレベルトリガ入力がロジック“L”になると、デバイスがクリアされ、MSPANピンと表4の規定値を使って選択するハードワイヤ接続のオプションによって設定されるリセット・コードと範囲になります。制御レジスタはゼロにクリアされます。ロジック・レベルはIOV<sub>CC</sub>によって決まります。

**IOV<sub>CC</sub>(ピン18)** : デジタル入力/出力電源電圧。1.71V ≤ IOV<sub>CC</sub> ≤ V<sub>CC</sub> + 0.3V。0.1μFのコンデンサを使用してGNDにバイパスします。

**REF(ピン25)** : リファレンス入力/出力。REFピンの電圧により、全てのチャネルのフルスケール電圧範囲が設定されます。デフォルトで、内部リファレンスはこのピンに接続されます。外部DC負荷電流を駆動するときはバッファを付加する必要があります。リファレンスがディスエーブルされると(「動作」のセクションの「リファレンス・モード」を参照)、リファレンスの出力が切断されてREFピンは高インピーダンス入力になり、REFピンには高精度の外部リファレンスを接続することができます。ノイズを小さくしてリファレンスを安定化させるため、このピ

## ピン機能

ンからGNDにコンデンサを接続します。この値はCREFCOMP以下にする必要があります。ここで、CREFCOMPはREFCOMPピンに接続する容量です。許容される外部リファレンス入力電圧範囲は、0.5V～VCC - 1.75Vです。

**REFCOMP(ピン26)**：内部リファレンス補償ピン。ノイズを小さくしてリファレンスを安定化させるため、GNDとの間に0.1 $\mu$ Fコンデンサを接続します。REFCOMPをGNDに接続すると内部リファレンスがディスエーブルされた状態でデバイスがパワーアップするので、起動時に外部リファレンスを使用することができます。

**V<sub>CC</sub>(ピン28)**：アナログ電源電圧入力。4.5V ≤ V<sub>CC</sub> ≤ 5.5V。1 $\mu$ Fのコンデンサを使ってGNDにバイパスします。

**OVRTEMP(ピン30)**：過熱保護割り込みピン。チップ温度が160°Cを超えると、このオープンドレインのNチャネル出力は“L”になります。このピンはCS/LDの次の立ち上がりエッジで解放されます。プルアップ抵抗が必要です。

**MSP0(ピン31)**：MSPANビット0。このピンをVCCまたはGNDに接続して、4チャネル全てのパワーオン・スパンとパワーオンリセット・コードを選択します(表4を参照)。

**MSP1(ピン32)**：MSPANビット1。このピンをVCCまたはGNDに接続して、4チャネル全てのパワーオン・スパンとパワーオンリセット・コードを選択します(表4を参照)。

**露出パッド(ピン33)**：アナログ負電源(V-)。PCBに半田付けする必要があります。

## ブロック図

## タイミング図

図1. シリアル・インターフェースのタイミング

## 動作

LTC2664は、出力範囲を選択可能で高精度リファレンスを内蔵した、4チャネル、 $\pm 10V$ デジタル/アナログ・コンバータ(DAC)ファミリです。DACは正の5V電源とバイポーラの $\pm 15V$ 電源で動作します。バイポーラの電源は最小 $\pm 4.5V$ で動作可能で、対称である必要はありません。更に、負の $V^-$ 電源はグランドで動作可能なので、デバイスに単電源システムとの互換性を持たせています。出力はバイポーラの電源レールによって駆動されます。

出力アンプは真のレール・トゥ・レール動作を行います。 $V^+$ レールまたは $V^-$ レールから負荷電流が流れる場合、レールに対する出力電圧のヘッドルームは、出力デバイスの $60\Omega$ の標準チャネル抵抗によって制限されます。「標準的性能特性」のセクションの「レールに対するヘッドルームと出力電流」のグラフを参照してください。

LTC2664は、エコー読み出し機能を備えた、カスケード接続可能な3線式SPI/Microwire互換インターフェースを使って制御されます。

### パワーオン・リセット

電源が最初に入れられたときに出力がリセットされるので、システムの初期設定が一定に保たれ、再現可能になります。MSPANピン(MSP2、MSP1、MSP0)をGNDまたは $V_{CC}$ に接続することにより、初期出力範囲とリセット・コード(ゼロスケールまたはミッドスケール)の選択、ならびに手動(固定)範囲の動作とSoftSpan動作の選択を行うことができます。ピン配置と利用可能なオプションについては、表4を参照してください。

### 電源シーケンシングと起動

電源( $V_{CC}$ 、 $IOV_{CC}$ 、 $V^+$ 、および $V^-$ )は都合の良い順序で投入してかまいません。

外部リファレンスを使用する場合は、電源投入時シーケンスおよび電源切断時シーケンスの間にREFの入力電圧を $V_{CC} + 0.3V$ より高くすることはできません(「絶対最大定格」のセクションを参照)。起動後は、DCリファレンス電圧を $0.5V \sim V_{CC} - 1.75V$ の範囲にしても問題ありません。

可能な最大性能を実現するには、電源のバイパスが非常に重要になります。 $V_{CC}$ 、 $V^+$ 、および $V^-$ の各電源にはグランドとの間に少なくとも $1\mu F$ の容量を取り付け、各電源には $0.1\mu F$ 以上の低ESR容量をできるだけデバイスの近くに取り付けてください。 $IOV_{CC}$ では、容量の大きい方のコンデンサを省略してもかまいません。

ベンチ電源が注意深く電流/電圧制限されている場合、電源ケーブルやトレースのインダクタンスがバイパス容量と組み合わされることによって絶対最大定格を超える電源電圧トランジエントが生じる可能性があるので、電源の活線挿入や急激な切り替えは避けるようにしてください。起動時には、電源の突入電流を $5A$ 以下に、電源のスルーレートを $5V/\mu s$ 以下に制限します。これらの要件が満たされないと、内部保護回路が損傷して長期信頼性に悪影響を与える可能性があります。

## 動作

表1. コマンドのコード

| コマンド |    |    |    |                                               |

|------|----|----|----|-----------------------------------------------|

| C3   | C2 | C1 | C0 |                                               |

| 0    | 0  | 0  | 0  | Write Code to $n$                             |

| 1    | 0  | 0  | 0  | Write Code to All                             |

| 0    | 1  | 1  | 0  | Write Span to $n$                             |

| 1    | 1  | 1  | 0  | Write Span to All                             |

| 0    | 0  | 0  | 1  | Update $n$ (Power Up)                         |

| 1    | 0  | 0  | 1  | Update All (Power Up)                         |

| 0    | 0  | 1  | 1  | Write Code to $n$ , Update $n$ (Power Up)     |

| 0    | 0  | 1  | 0  | Write Code to $n$ , Update All (Power Up)     |

| 1    | 0  | 1  | 0  | Write Code to All, Update All (Power Up)      |

| 0    | 1  | 0  | 0  | Power Down $n$                                |

| 0    | 1  | 0  | 1  | Power Down Chip (All DACs, Mux and Reference) |

| 1    | 0  | 1  | 1  | Analog Mux                                    |

| 1    | 1  | 0  | 0  | Toggle Select                                 |

| 1    | 1  | 0  | 1  | Global Toggle                                 |

| 0    | 1  | 1  | 1  | Config                                        |

| 1    | 1  | 1  | 1  | No Operation                                  |

表2. DACアドレス、 $n$

| アドレス |    |    |    |       |

|------|----|----|----|-------|

| A3   | A2 | A1 | A0 |       |

| 0    | 0  | 0  | 0  | DAC 0 |

| 0    | 0  | 0  | 1  | DAC 1 |

| 0    | 0  | 1  | 0  | DAC 2 |

| 0    | 0  | 1  | 1  | DAC 3 |

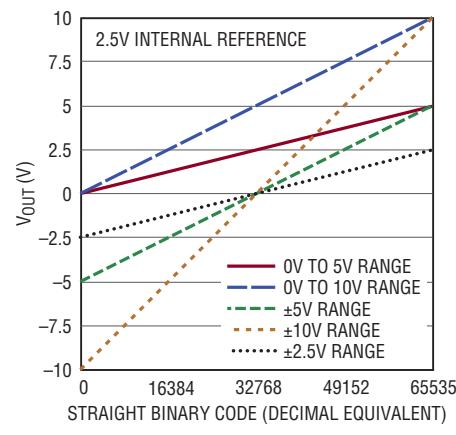

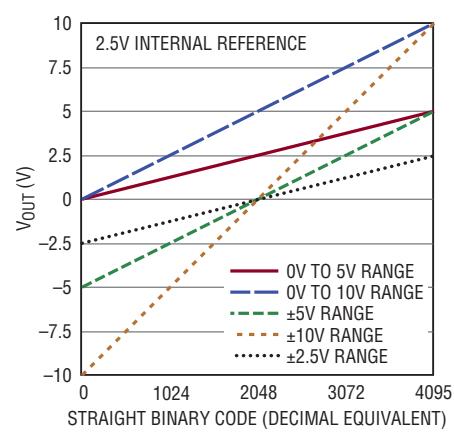

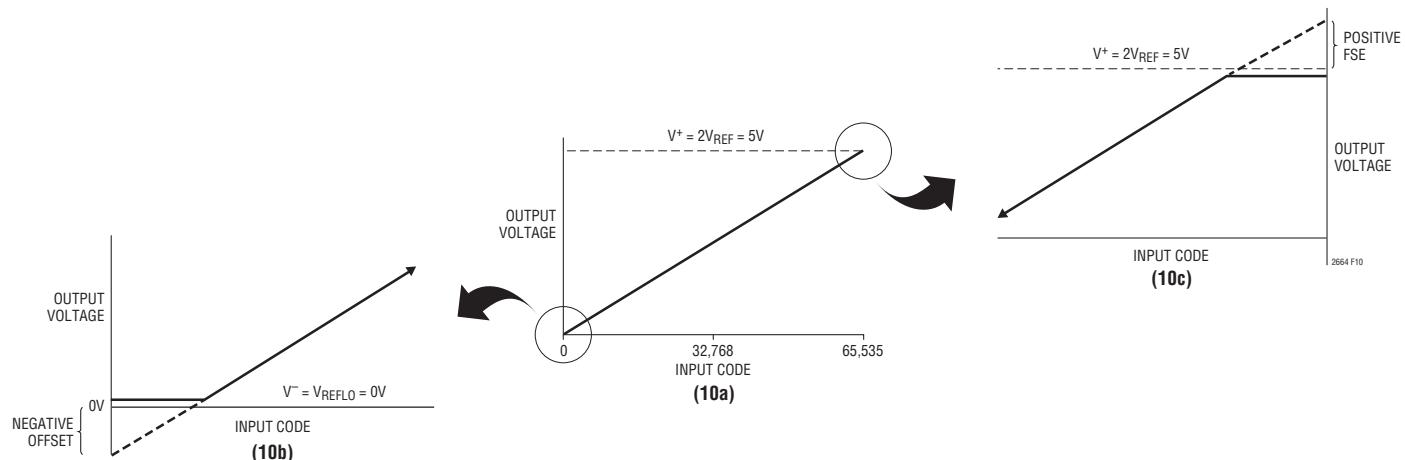

## 伝達関数

全ての出力範囲および分解能に対するDACの入力-出力間伝達関数を図2aと図2bに示します。全ての範囲に対する入力コードはストレート・バイナリ形式です。

## シリアル・インターフェース

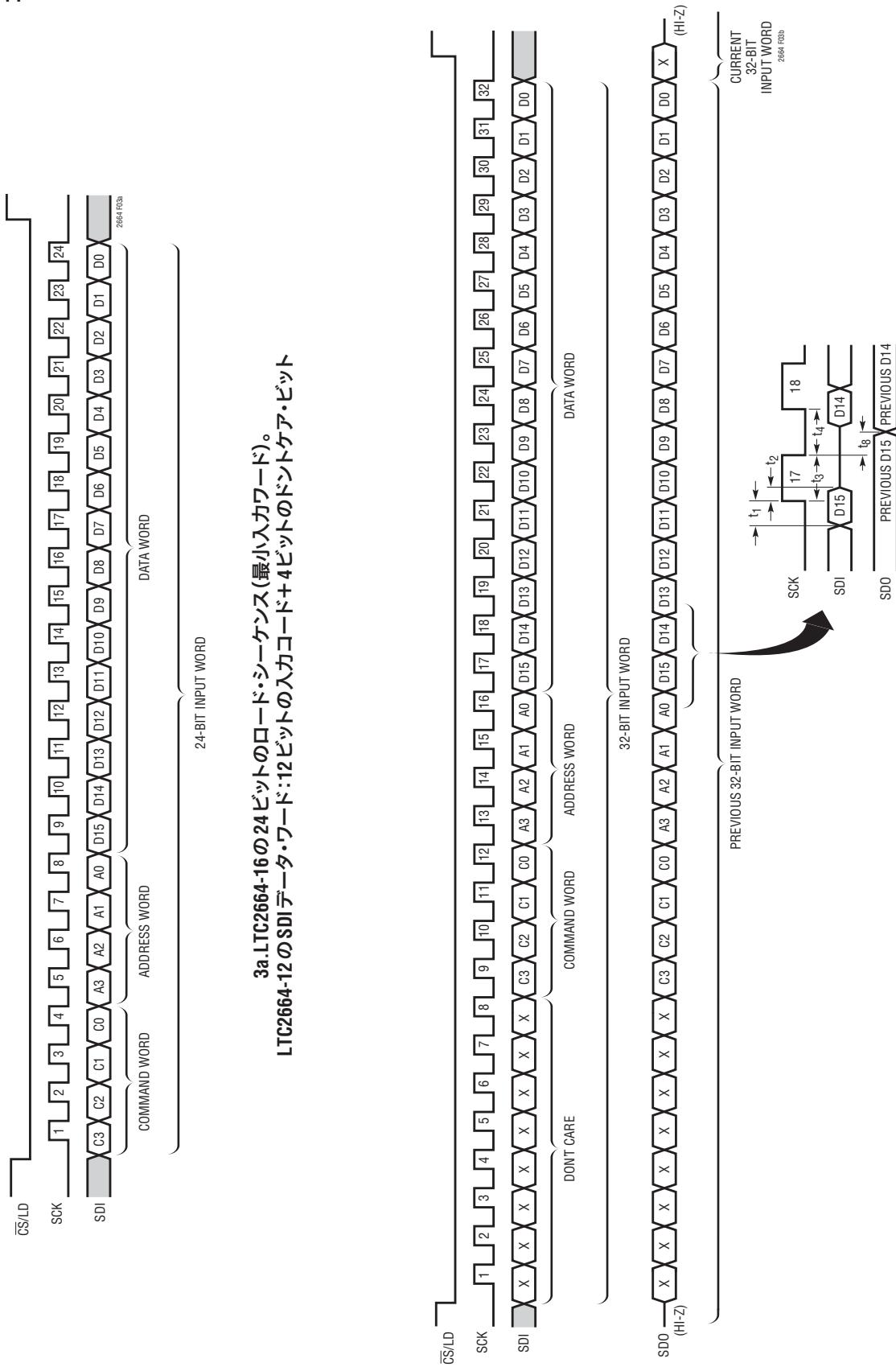

CS/LDピンを“L”にすると、SDIピンのデータがクロック(SCKピン)の立ち上がりエッジでシフト・レジスタに読み込まれます。最初に4ビットのコマンド(C3～C0)、次に4ビットのDACアドレス(A3～A0)、そして最後に16ビットのデータ・ワードがストレート・バイナリ形式で読み込まれます。LTC2664-16では、データ・ワードはMSBからLSBへと並んだ16ビットの入力コードで構成されます。LTC2664-12では、データ・ワードはMSBからLSBへと並んだ12ビットの入力コードと、それに続く4ビットのドントケア・ビットで構成されます。データはCS/LD信号が“L”的ときだけLTC2664に転送することができます。CS/LDの立ち上がりエッジでデータ転送が終了し、24ビットの入力ワードで指定された動作がデバイスによって実行されます。全てのシーケンスを図3aに示します。

図2a. LTC2664-16の伝達関数

図2b. LTC2664-12の伝達関数

## 動作

図3. LTC2664のロード・シーケンス

## 動作

最小入力ワードは24ビットですが、オプションで32ビットに拡張することができます。32ビットのワード幅を使用するには、8ビットのドントケア・ビットを最初にデバイスに転送し、続いて上記の24ビットのワードを転送する必要があります。32ビットのシーケンスを図3bに示します。32ビット・ワードはエコード読み出しとデイジーチェーン動作に必要で、最小ワード幅が16ビット以上のプロセッサに対応させるためにも有効です。

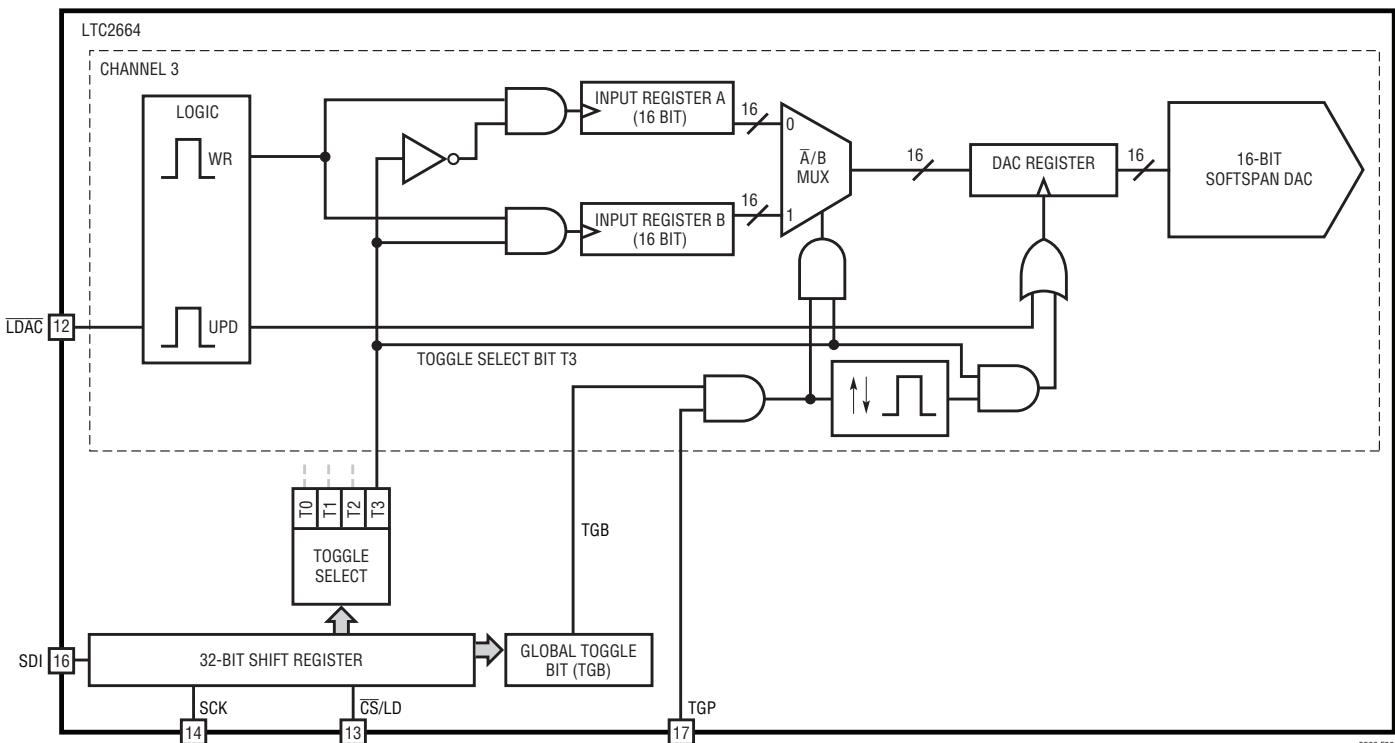

### 入力レジスタおよびDACレジスタ

LTC2664には、メインのシフトレジスタに加えて、各DACに5個の内部レジスタがあります（「ブロック図」を参照）。各DACチャネルには2組のダブル・バッファ・レジスタが備わっています。1組はコード・データ用、1組はDACのスパン（出力範囲）用です。ダブル・バッファによりスパンとコードを同時に更新可能なので、出力範囲の変更時に滑らかに電圧を遷移させることができます。複数のDACを同時に更新することも可能です。

ダブル・バッファ・レジスタの各組は、入力レジスタとDACレジスタで構成されます。

- 入力レジスタ**：書き込み操作では、選択された入力レジスタにSDIピンからデータがシフトします。入力レジスタは保持バッファなので、書き込み操作によってDAC出力が影響を受けることはありません。

コードのデータ・パスには、各DACレジスタに2個の入力レジスタAおよびBがあります。レジスタBは切り替え操作のときのみ使用される代替の入力レジスタですが、レジスタAはデフォルトの入力レジスタです（「ブロック図」を参照）。

- DACレジスタ**：更新操作では、入力レジスタの内容がそれに対応するDACレジスタにコピーされます。DACレジスタの内容はDACの出力電圧または出力範囲を直接制御します。また、選択されたDACがパワーダウン・モードであれば、更新操作によってパワーアップされます。データ・パスとレジスタは「ブロック図」に示されています。

更新では、コードとスパンの両方のデータが常にリフレッシュされますが、対応する入力レジスタの値が書き込み操作によって変更されていない限り、DACレジスタに保持された値は変更されないことに注意してください。例えば、新しいコードを書き込んでチャネルを更新すると、コードは更新されますが、スパンは変更されずにリフレッシュされます。チャネルの更新は、シリアル更新コマンド、 $\overline{LDAC}$ の負パルス、または切り替え操作で実行できます。

表3.スパン書き込みのコード

| S2 | S1 | S0 | 出力範囲       |                      |

|----|----|----|------------|----------------------|

|    |    |    | 内部リファレンス   | 外部リファレンス             |

| 0  | 0  | 0  | 0V～5V      | 0V～2V <sub>REF</sub> |

| 0  | 0  | 1  | 0V～10V     | 0V～4V <sub>REF</sub> |

| 0  | 1  | 0  | $\pm 5V$   | $\pm 2V_{REF}$       |

| 0  | 1  | 1  | $\pm 10V$  | $\pm 4V_{REF}$       |

| 1  | 0  | 0  | $\pm 2.5V$ | $\pm V_{REF}$        |

### 出力範囲

LTC2664は、出力範囲が選択可能な4チャネルDACです。出力範囲はソフトウェアまたはピンの結線によるハードワイヤ接続で設定することができます。

### SoftSpan動作

出力範囲がシリアル・インターフェースを介して制御されるSoftSpan動作は、3つ全てのMSPANピン（MSP2、MSP1、およびMSP0）をV<sub>CC</sub>に接続することによって行われます（表4を参照）。SoftSpanの設定では、パワーオン時に全てのチャネルが0V～5Vの範囲のゼロスケールに初期化されます。次いで、各チャネルの範囲とコードが全てプログラム可能になります。

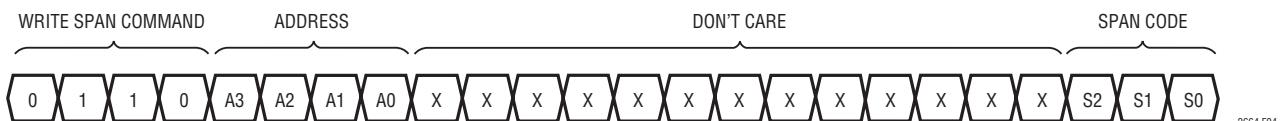

各チャネルには範囲情報用に1組のダブルバッファ・レジスタが備わっています（「ブロック図」を参照）。**Write Span n**または**Write Span All**コマンド（それぞれ、0110bと1110b）を使ってスパン入力レジスタをプログラムします。図4にそのシンタックスを、表3にスパン・コードと出力範囲を示します。

ダブルバッファ付きコード・レジスタ同様、更新操作ではスパン入力レジスタを対応するスパンDACレジスタにコピーします。

図4. スパン書き込みのシンタックス

## 動作

### 手動によるスパン操作

どのアプリケーションにも複数の出力範囲は必要ありません。MSPANピン(MSP2、MSP1、およびMSP0)をGNDまたはV<sub>CC</sub>に接続することにより、付帯的な操作なしに任意の出力範囲をハードウェアで設定することができます。ユニポーラ・モードでは、ゼロスケールおよびミッドスケールのリセット・オプションも利用可能です(表4を参照)。

表4. MSPANピンの設定

| MSP2            | MSP1            | MSP0            | 出力範囲   | リセット・コード   | 手動によるスパン | ソフトウェアによるスパン |

|-----------------|-----------------|-----------------|--------|------------|----------|--------------|

| 0               | 0               | 0               | ±10V   | Mid-Scale  | X        |              |

| 0               | 0               | V <sub>CC</sub> | ±5V    | Mid-Scale  | X        |              |

| 0               | V <sub>CC</sub> | 0               | ±2.5V  | Mid-Scale  | X        |              |

| 0               | V <sub>CC</sub> | V <sub>CC</sub> | 0V~10V | Zero-Scale | X        |              |

| V <sub>CC</sub> | 0               | 0               | 0V~10V | Mid-Scale  | X        |              |

| V <sub>CC</sub> | 0               | V <sub>CC</sub> | 0V~5V  | Zero-Scale | X        |              |

| V <sub>CC</sub> | V <sub>CC</sub> | 0               | 0V~5V  | Mid-Scale  | X        |              |

| V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | 0V~5V  | Zero-Scale |          | X            |

### アナログ・マルチプレクサ

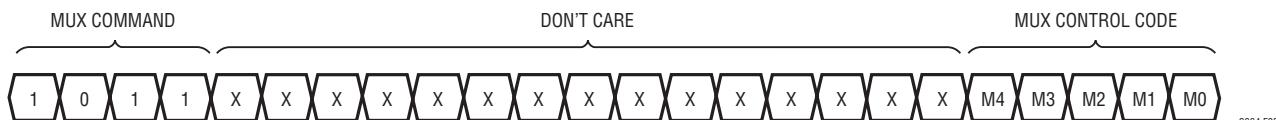

LTC2664は、選択されたデバイスの電圧を調べるためにアナログ・マルチプレクサ(mux)を内蔵しています。個々のDAC出力以外に、REF、REFLO、V<sup>+</sup>電源とV<sup>-</sup>電源、内部温度モニタ、および4つの補助入力(MUXIN0~MUXIN3)をマルチプレクサの入力として使用することができます。muxコマンド(1011b)と、表5に規定されている制御コードを組み合わせて使用することにより、マルチプレクサのいづれかの入力をMUXOUTピンに結合することができます。

補助入力(MUXIN0~MUXIN3)を使用して、外部電圧が適合範囲内(V<sup>-</sup>~V<sup>+</sup> - 1.4V)に入っていることをモニタすることができます。入力ピンはイネーブルされるまでは高インピーダンス状態であり、イネーブルされると、MUXOUTでの外部負荷インピーダンスと直列に、約2.2kの駆動源が負荷になります。

マルチプレクサの適合範囲はV<sup>-</sup>~V<sup>+</sup> - 1.4Vですが、V<sup>+</sup>電源を供給するチャネル(制御コード11011b)は例外で、V<sup>+</sup>まで達します。MUXOUTは電源投入時にディスエーブルされます(高インピーダンス)。

MUXOUTは高インピーダンス負荷のみを駆動するように設計されているので、MUXOUTでの出力電流が±1mAを超えると、内部回路が損傷する可能性があります。

Muxコマンドのシンタックスとコードをそれぞれ図5と表5に示します。

表5. アナログ・マルチプレクサの制御コード

| M4 | M3 | M2 | M1 | M0 | MUXピン出力           |

|----|----|----|----|----|-------------------|

| 0  | 0  | 0  | 0  | 0  | ディスエーブル(Hi-Z)     |

| 1  | 0  | 0  | 0  | 0  | MUXIN0            |

| 1  | 0  | 0  | 0  | 1  | V <sub>OUT0</sub> |

| 1  | 0  | 0  | 1  | 0  | V <sub>OUT1</sub> |

| 1  | 0  | 0  | 1  | 1  | MUXIN1            |

| 1  | 0  | 1  | 0  | 0  | MUXIN2            |

| 1  | 0  | 1  | 0  | 1  | V <sub>OUT2</sub> |

| 1  | 0  | 1  | 1  | 0  | V <sub>OUT3</sub> |

| 1  | 0  | 1  | 1  | 1  | MUXIN3            |

| 1  | 1  | 0  | 0  | 0  | REFLO             |

| 1  | 1  | 0  | 0  | 1  | REF               |

| 1  | 1  | 0  | 1  | 0  | 温度モニタ             |

| 1  | 1  | 0  | 1  | 1  | V <sup>+</sup>    |

| 1  | 1  | 1  | 0  | 0  | V <sup>-</sup>    |

### 温度モニタ

バイアスされた温度モニタ・ダイオード・スタックを備えているので、Muxコマンドと制御コード11010bを組み合わせて使用することにより、このダイオード・スタックをMUXOUTまで配線することができます。通常、V<sub>MUXOUT</sub> = 1.4V - 3.7mV/°C • (T<sub>J</sub> - 25 °C) です。接合部温度はT<sub>J</sub> = 25 °C + (1.4V - V<sub>MUXOUT</sub>) / (3.7mV/°C) のように計算することができます。最高の精度を得るには、マルチプレクサを使用してダイオードの下側でREFLOを検出し、既知の温度で電圧を較正します。標準的な未較正精度は±5°Cです。

図5. マルチプレクサ・コマンド

## 動作

### 切り替え操作

システムによっては、DACスイッチを2つの電圧レベルの間で繰り返し切り替える必要があります。この例として、小さなACバイアスの付加、オン状態とオフ状態の個別の切り替えなどがあります。LTC2664の切り替え機能は、DACチャネルあたり2個の入力レジスタ(AとB)を備えることにより、この種の操作を可能にします。

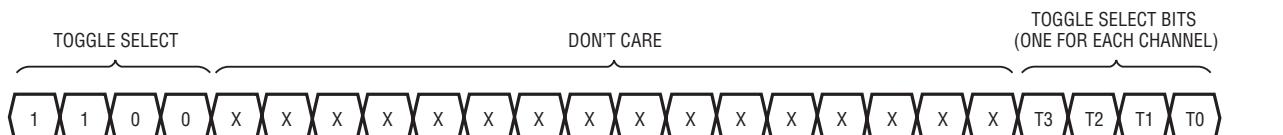

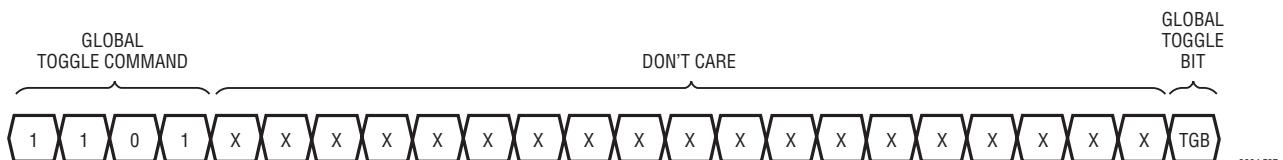

AとBの切り替えは3つの信号によって制御されます。これらの信号の1つ目は切り替え選択コマンドで、それぞれが1つのチャネルを制御する4ビットのデータ・フィールドに作用します(図6を参照)。2つ目はグローバル切り替えコマンドで、グローバル切り替えビットTGBを使用し、選択された全てのチャネルを制御します(図7を参照)。最後に、TGPピンにより、外部クロックまたはロジック信号を使用して、DAC出力をAとBの間で切り替えることができます。これらの制御回路からの信号は、図8に示すように合成されます。

切り替え機能が不要な場合、TGP(ピン17)をグランドに接続し、切り替え選択レジスタをパワーオン・リセット状態(ゼロにクリア)のままにします。すると、入力レジスタAが単独の入力レジスタとして機能し、レジスタBは使用されません。

### 切り替え選択レジスタ(TSR)

切り替え選択コマンド(1100b)のシンタックスを図6に示します。4ビットのTSRデータ・フィールドの各ビットにより、同じ名称のDACチャネルが制御されます。T0によってチャネル0が、T1によってチャネル1が制御されます。つまりTxによってチャネルTxが制御されます。

切り替え選択ビット(T0、T1、T2、T3)には2つの機能があります。まず、各切り替え選択ビットにより、コード書き込み操作によるデータをAまたはBのどちらの入力レジスタが受け取る

かが制御されます。所定のチャネルの切り替え選択ビットが“H”的場合、コード書き込み操作はアドレス指定されたチャネルの入力レジスタBに対して行われます。このビットが“L”的場合、コード書き込み操作は入力レジスタAに対して行われます。

次に、各切り替え選択ビットにより、切り替え操作に対応するチャネルがイネーブルされます。

### 入力レジスタAおよびBへの書き込み

切り替えるチャネルを選択したら、選択したチャネルの入力レジスタAに必要なコードを書き込みます。次に、切り替え選択コマンドを使ってそのチャネルの切り替え選択ビットを設定します。最後に、入力レジスタBに必要なコードを書き込みます。これらの手順が完了すると、チャネルが切り替えられるようになります。例えば、チャネル3がコード4096と4200の間で切り替わるように設定するには以下のようにします。

- 1) コード・チャネル3(コード = 4096)をレジスタAに書き込む

00000011 00010000 00000000

- 2) 選択を切り替える(ビットT3をセット)

11000000 00000000 00001000

- 3) コード・チャネル3(コード = 4200)をレジスタBに書き込む

00000011 00010000 01101000

ステップ(3)のコード書き込みでは、ステップ(2)のビットT3が1に設定されているため、レジスタBに指定されています。この時点では、チャネル3は2つの必要なコードを保持する入力レジスタAとBを備えており、切り替え操作ができる状態になっています。

図6. 切り替え選択のシンタックス

図7. グローバル切り替えのシンタックス

## 動作

### レジスタAとBの切り替え

入力レジスタAとBが、上記の例のように、必要な全てのチャネルと対応する切り替え選択ビットが“H”に設定されるように書き込まれている場合、そのチャネルは切り替えのための準備ができます。

LTC2664は3つのタイプの切り替え操作をサポートします。1つ目は、選択された全てのチャネルをSPIポートを使って同時に切り替えるタイプ、2つ目は、選択された全てのチャネルを外部クロックまたはロジック信号を使って同時に切り替えるタイプ、3つ目は、チャネルの任意の組み合せを入力レジスタAまたはBから更新するように指定できるタイプです。

内部の切り替え/更新回路はエッジで作動するので、それぞれの入力レジスタからの更新の引き金となるのは、(切り替えビットTGBまたは切り替えピンTGP)の遷移だけです。

選択された全てのチャネルをSPIポートを使って同時に切り替えるには、TGPピンが“H”になるようにし、望みのチャネルに対応する切り替え選択レジスタのビットも“H”になるようにします。グローバル切り替えコマンド(1101b)を使ってコードを交互に切り替えることにより、グローバル切り替えビット

(TGB)を順次変化させます(図7を参照)。TGBを1から0に変更すると、DACレジスタはそれぞれの入力レジスタAを基に更新されます。TGBを0から1に変更すると、DACレジスタはそれぞれの入力レジスタBを基に更新されます。この方法では、1回のシリアル・コマンドだけで最大4チャネルを切り替えることができることに注意してください。

選択された全てのチャネルを外部ロジック信号を使って切り替えるには、グローバル切り替えレジスタのTGBビットが“H”になるようにし、切り替え選択レジスタ内で、望みのチャネルに対応する切り替え選択レジスタのビットも“H”になるようにします。コードを交互に切り替えるには、TGPピンにクロックまたはロジック信号を入力します。TGPの立ち下がりエッジでは、DACレジスタは関連の入力レジスタAのデータを基に更新されます。TGPの立ち上がりエッジでは、DACレジスタは関連の入力レジスタBのデータを基に更新されます。入力レジスタが更新されると、全ての切り替えはTGPピンに入力された信号によって実行され、SPI命令を追加する必要はありません。

チャネルの任意の組み合せで入力レジスタAまたはBからの更新をさせるには、TGPピンが“H”になるようにし、グローバル切り替えレジスタのTGBビットも“H”になるようにします。

図8. 切り替えの簡略ブロック図。概念のみ(実際の回路は異なる)

## 動作

切り替え選択コマンドを使用することにより、必要に応じて切り替え選択ビットを設定して入力レジスタ(AまたはB)を選択することで、各チャネルが更新されます。次に、シリアル・コマンド(1001b)を使用するか、またはLDACピンに負のパルスを入力することにより、全てのチャネルが更新されます。切り替え選択ビットが0のチャネルでは入力レジスタAからの更新が行われ、切り替え選択ビットが1のチャネルでは入力レジスタBからの更新が行われます(図8を参照)。切り替え/選択および更新操作を交互に切り替えることにより、必要に応じて最大4チャネルをAまたはBに同時に切り替えることができます。

### デイジーチェーン動作

シフトレジスタのシリアル出力はSDOピンから出力されます。SDI入力からデバイスに転送されたデータは、SCKの32の立ち上がりエッジだけ遅れてから、次のSCKの立ち下がりエッジで出力されることにより、SCKの次の32の立ち上がりエッジでのマイクロプロセッサへのクロック入力に対応します。

SDO出力を使って、単一の3線式シリアル・ポート(つまり、SCK、SDIおよび $\overline{\text{CS}}/\text{LD}$ )から複数のシリアル・デバイスを制御しやすくすることができます。このようなデイジーチェーンの直列接続は、チェーンの上流に位置する各デバイスのSDOを次に位置するデバイスのSDIに接続することによって構成されます。これらのデバイスのシフトレジスタはこのように直列に接続され、実質的に、チェーン全体にわたる単一入力のシフトレジスタを形成します。このため、これらのデバイスは、それらへの入力ワードを単に連結することにより、個別にアドレス指定して制御することができます(最初の命令はチェーンの最後のデバイスをアドレス指定し、以下同様)。SCK信号と $\overline{\text{CS}}/\text{LD}$ 信号はチェーンの全てのデバイスに共通です。

使用時には、最初に $\overline{\text{CS}}/\text{LD}$ を“L”にします。次に、最初のデバイスのSDIをデータ入力として使用して、連結された入力データをチェーンに転送します。データの転送が完了すると、 $\overline{\text{CS}}/\text{LD}$ は“H”になり、全てのデバイスの命令シーケンスが同時に完了します。チェーン内の他の全てのデバイスに対しては**No-Operation**コマンド(1111)を使用することにより、単一のデバイスだけを制御することができます。

$\overline{\text{CS}}/\text{LD}$ が“H”になると、SDOピンが高インピーダンス出力になるので、デイジーチェーン動作をさせるには各デバイスのSDOにプルアップ抵抗が必要です(最後のデバイスを除く)。

### エコー読み出し

SDOピンを使ってデバイスへのデータ転送を検証することができます。32ビットの各命令サイクルの間、SDOは検証のため前の32ビットの命令を出力します。

$\overline{\text{CS}}/\text{LD}$ が“H”的場合、SDOは高インピーダンスになり、他のSPIデバイスが使用できるようにバスを解放します。

### パワーダウン・モード

電力が制限されているアプリケーションの場合、必要なDAC出力の数が4より少ないとときは、パワーダウン・モードを使用して電源電流を低減することができます。パワーダウン時には、出力アンプとリファレンス・バッファがディスエーブルされます。DAC出力は高インピーダンス状態になり、出力ピンはそれぞれ42k(最小)抵抗によって受動的にグランドに引き下げられます。レジスタの内容はパワーダウンの間に影響を受けることはありません。

どのチャネルまたは複数のチャネルの組み合わせでも、適切なDACアドレスと組み合わせたコマンド0100bを使ってパワーダウン・モードにすることができます。更に、全てのDACチャネルと内蔵リファレンスはともに、**Power-Down Chip**コマンド0101bを使ってパワーダウン・モードにすることができます。全てのパワーダウン・コマンドでは16ビットのデータワードが無視されます。

表1に示されているDAC更新を含むいづれかのコマンドを実行する、非同期のLDACピンを“L”にする、または切り替え操作を行うことにより、通常動作が再開します(「切り替え操作」のセクションを参照)。選択されたDACはその電圧出力が更新されるとパワーアップされます。パワーダウンしたDACを更新する場合、待機時間を付加して追加のパワーダウン遅延に対応します。更新コマンドの前にチャネルがパワーダウンされている場合(コマンド0100b)、パワーアップ遅延時間は30 $\mu\text{s}$ になります。それに対して、チップがパワーダウンされている場合(コマンド0101b)、パワーアップ遅延時間は35 $\mu\text{s}$ になります。

### LDACを使用したDACの非同期更新

表1に示す更新コマンドの他、非同期でアクティブ“L”的LDACピンによっても、4個のDACレジスタが全て入力レジスタの内容に更新されます。

$\overline{\text{CS}}/\text{LD}$ が“H”的場合、LDACピンを“L”にすると、全てのDACレジスタが入力レジスタの内容に更新されます。

$\overline{\text{CS}}/\text{LD}$ が“L”的場合には、CS/LDの立ち上がりエッジの前のLDACピンの“L”に立ち下がるパルスで全てのDAC出力がパ

## 動作

ワーアップしますが、その出力は更新されません。 $\overline{CS}/LD$ の立ち上がりエッジの後でLDACが“L”を維持すると、LDACが認識され、24ビットのワードで指定されたコマンドが実行されてDAC出力が更新されます。

LDACが“L”になると、 $\overline{CS}/LD$ の状態に関係なくDAC出力がパワーアップします。

$\overline{CS}/LD$ が“H”になる時点の $\overline{LDAC}$ が“L”的場合、入力ワードで指定された全てのソフトウェア・パワーダウン・コマンド(パワーダウンn、パワーダウン・チップ、設定/選択リファレンス)が禁止されます。

### リファレンス・モード

LTC2664は2つのリファレンス・モード(内部および外部)を備えており、これによってリファレンス・ソースを選択することができます。どちらのモードでも、REFピンの電圧および出力範囲の設定値により、各チャネルのフルスケール電圧が決まります。

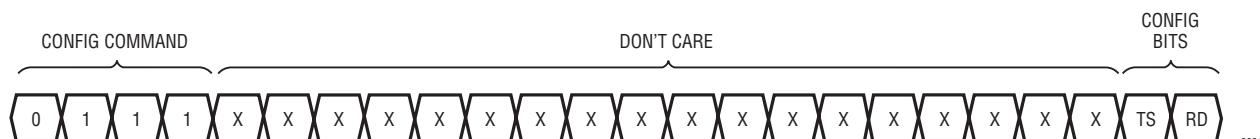

このデバイスは、温度ドリフトの標準値が $2\text{ppm}/^\circ\text{C}$ の $2.5\text{V}$ リファレンスを内蔵しています。内部リファレンスを使用するには、REFCOMPピンをフロート状態(グランドへのDC経路がない状態)にしておきます。更に、設定レジスタのRDビットの値を0にする必要があります。この値は、パワーアップ時にリセットするか、または**Config**コマンド0111bを使ってリセットすることで0になります。図9にコマンドのシンタックスを示します。

内部リファレンスで外部回路を駆動するのであれば、バッファが必要です。リファレンスを安定化させてノイズを小さくするため、REFCOMPとGNDの間に $0.1\mu\text{F}$ のコンデンサを接続する必要があります。この構成では、内部リファレンスが最大 $0.1\mu\text{F}$ を非常に安定して駆動することができます。安定した動作をさせるため、REFピンの容量性負荷がREFCOMPピンの容量性負荷を超えないようにします。

外部リファレンスを使用するには、REFCOMPピンをグランドに接続します。これにより、起動時の内部リファレンスの出力がディスエーブルされ、REFピンは高インピーダンス入力になります。パワーアップ後、REFピンに必要なリファレンス電圧を印加し、**Config**コマンド(0111b)を使ってRDビットを1に設定します。これにより、V<sub>CC</sub>の電源電流が約 $200\mu\text{A}$ 減少します。

許容可能な外部リファレンス電圧の範囲は $0.5\text{V} \leq V_{\text{REF}} \leq V_{\text{CC}} - 1.75\text{V}$ です。

### 内蔵リファレンス・バッファ

各チャネルには、独自の高性能リファレンス・バッファが内蔵されています。これらのバッファは入力インピーダンスが非常に大きいので、リファレンス電圧源の負荷になりません。これらのバッファは、DACの切り替えによって生じるグリッチからリファレンス電圧を保護するので、動作時のDAC間クロストークを最小限に抑えます。標準的なDAC間クロストークは $3.5\text{nV}\cdot\text{s}$ 未満です( $0\text{V} \sim 10\text{V}$ の範囲)。「標準的性能特性」のセクションの「DAC間クロストーク」のグラフを参照してください。

### 電圧出力

アンプが広範囲の負荷条件で定格電圧精度を維持する能力は、アンプの負荷レギュレーションの仕様で特性が評価されます。出力電圧の変化は、負荷電流を強制的に $1\text{mA}$ 変化させることによって測定されます。LTC2664の高電圧、レール・トゥ・レール出力アンプのそれぞれは、電源のヘッドルームが最小 $1.4\text{V}$ で最大 $10\text{mA}$ をソースまたはシンクするときの負荷レギュレーションが保証されています。更に、このアンプは、有効なヘッドルームが $2.2\text{V}$ 以上に増加すると、最大 $\pm 14\text{mA}$ を駆動することができます。

DC出力インピーダンスは負荷レギュレーションと同等であり、 $\mu\text{V}/\text{mA}$ から $\Omega$ への単位変換を計算するだけで求めることができます。負荷をレールから十分に離して駆動した場合、アンプのDC出力インピーダンスは標準で $0.08\Omega$ です。

どちらかのレールから負荷電流が流れているとき、そのレールに対する出力電圧のヘッドルームは出力デバイスの $60\Omega$ の標準チャネル抵抗によって制限されます。たとえば、 $1\text{mA}$ をシンクしているとき、最小出力電圧( $V^-$ より上)は $60\Omega \cdot 1\text{mA} = 60\text{mV}$ になります。「標準的性能特性」のセクションの「レールに対するヘッドルームと出力電流」のグラフを参照してください。

このアンプは最大 $1000\text{pF}$ の容量性負荷を安定して駆動します。

図9. 設定コマンドのシンタックス—サーマル・シャットダウン(TS)とリファレンス・ディスエーブル(RD)

## 動作

### 熱過負荷保護

LTC2664は、ダイ温度が160°Cを超えると、デバイス自体を保護します。全てのチャネルの電源が遮断され、オープンドレンの $\overline{OVRTMP}$ 割り込みピンは“L”になります。リファレンス回路とバイアス回路はパワーオン状態に保たれます。この保護機能がトリガされると、デバイスはダイが冷えた後でもシャットダウン状態を維持します。

チャネルが通常動作に戻ることが可能になるには、ダイの温度を約150°Cまで下げる必要があります。デバイスが十分に冷却されると、 $\overline{LDAC}$ や切り替えの操作を含む有効な更新操作により、シャットダウン状態を解除することができます。 $\overline{CS/LD}$ の立ち上がりエッジにより、ダイ温度に関係なく $\overline{OVRTMP}$ ピンが解放されます。

デバイスの総負荷電流は容易に50mAを超える可能性があるので、システム設計における加熱の可能性について慎重に評価する必要があります。最小1kの接地された負荷を使用可能で、この場合、過度の熱は発生しません。

**Config** コマンドを使ってTSビットを設定することにより、過熱保護をディスエーブルすることができます(図9を参照)。

### 基板レイアウト

これらのデバイスの優れた負荷レギュレーションおよびDCクロストークの性能は、信号グランドと電源グランドの同相抵抗を最小限に抑えることによってある程度実現されます。

どのような高分解能のコンバータの場合でもそうですが、ノイズのない基板の接地が重要です。スター・グランド手法などの、低インピーダンスのアナログ・グランド・プレーンが必要です。スター・グランドに使用する基板層を連続に保ってグランド抵抗を最小限に抑えます。つまり、別々のスター・トレースを使用せずにスター・グランドのコンセプトを使用します。REFLOピンからスター・ポイントまでの抵抗はできるだけ小さくします。

最高の性能を得るには、グランド・プレーンに150~200ミルの間隔のビアの配列を取付け、他の基板層からのグランド・ブロードと接続します。これにより、全グランド抵抗が減少し、グランド・ループの面積が最小限に抑えられます。

### 5V単電源システムにLTC2664を使用

LTC2664を単電源システムで使用するには、V-ピンをグランドの他にREFLOとGNDに接続し、V<sup>+</sup>とV<sub>CC</sub>を5V電源に接続するだけで済みます。IOV<sub>CC</sub>は5V電源に接続するか、またはロジック電源電圧(5Vより低い場合)に接続することができます。

内部リファレンスでは、0V~5Vの出力範囲を使用します。他のレール・トゥ・レール・デバイスと同様に、出力は電源電圧範囲内に制限されます。デバイスの出力はグランドを下回ることができないので、10bに示すように、これらの出力によって最小コードに制限が生じる可能性があります。同様に、フルスケール誤差(FSE = V<sub>OS</sub> + GE)が正の場合、またはV<sup>+</sup> < 2 • V<sub>REF</sub>の場合、フルスケールに近くで制限が生じる可能性があります。図10cを参照してください。

マルチプレクサを使用可能であり、十分に機能します。マルチプレクサによってグランドまで引き下げることができますですが、上側のヘッドルームに制限があるので、3.6V以下の出力電圧にのみ有効です(V<sup>+</sup> = 5V)。

外部リファレンスを使用することにより、更なる柔軟性を得ることができます。例えば、LTC6655などの1.25Vリファレンスを使用することにより、0倍~2倍の範囲と0倍~4倍の範囲の選択が可能になり、それぞれ2.5Vと5Vのフルスケール電圧が得られます。更に、このデバイスは、ゼロスケール・コードまたはミッドスケール・コードにリセットするように設定することができます(「出力範囲」のセクションを参照)。

## 動作

図10. 単電源動作での0V～5Vの出力範囲への影響。(10a)全体の伝達関数 (10b)ゼロスケール近くのコードに対する負のオフセットの影響 (10c)フルスケール近くのコードに対する正のフルスケール誤差の影響

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/product/LTC2664#packaging> を参照してください。

## 改訂履歴

| REV | 日付    | 概要           | ページ番号 |

|-----|-------|--------------|-------|

| A   | 06/16 | 上面マークの情報を修正。 | 3     |

# LTC2664

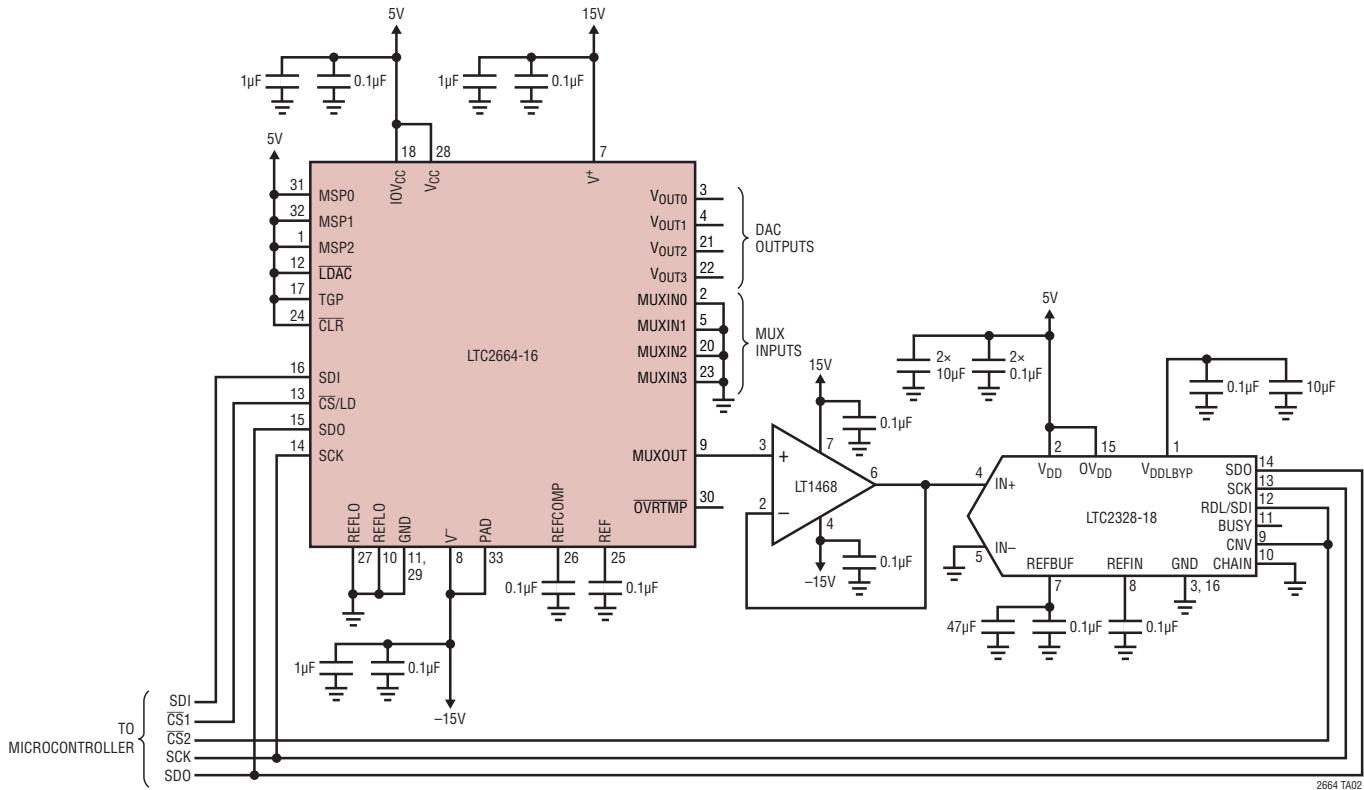

## 標準的応用例

アナログ・マルチプレクサを使って最大 $\pm 10.24V$ のDACの出力電圧を測定する。

独立したADCリファレンスでLTC2664の内部リファレンスをクロスチェック

## 関連製品

| 製品番号          | 概要                                                                                   | 注釈                                                                         |

|---------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| LTC2666       | $\pm 10\text{ppm}/^\circ\text{C}$ のリファレンスを内蔵した8チャネルのシリアル16/12ビット電圧出力SoftSpan DAC     | ソフトウェアでプログラム可能な出力範囲:最大 $\pm 10\text{V}$ 、5mm×5mm QFNパッケージ                  |

| LTC2668       | $\pm 10\text{ppm}/^\circ\text{C}$ のリファレンスを内蔵した16チャネルのシリアル16/12ビット電圧出力SoftSpan DAC    | ソフトウェアでプログラム可能な出力範囲:最大 $\pm 10\text{V}$ 、6mm×6mm QFNパッケージ                  |

| LTC2704       | クワッド・シリアル16/14/12ビット電圧出力SoftSpan DAC、 $\pm 2\text{LSB}$ のINL、 $\pm 1\text{LSB}$ のDNL | ソフトウェアでプログラム可能な出力範囲:最大 $\pm 10\text{V}$ 、SPIインターフェース、外付けアンプ不要              |

| LTC2754       | クワッド・シリアル16/12ビット電流出力SoftSpan DAC、 $\pm 1\text{LSB}$ のINL、 $\pm 1\text{LSB}$ のDNL    | ソフトウェアでプログラム可能な出力範囲:最大 $\pm 10\text{V}$ 、SPIインターフェース、7mm×8mm QFNパッケージ      |

| LTC2654       | リファレンスを内蔵したクワッド・シリアル16/12ビット電圧出力DAC                                                  | 内部リファレンス: $\pm 10\text{ppm}/^\circ\text{C}$ 、4mm×4mm QFNおよび16ピン細型SSOPパッケージ |

| LTC2634       | リファレンスを内蔵したクワッド12/10/8ビットSPI電圧出力DAC                                                  | 内部リファレンス: $\pm 10\text{ppm}/^\circ\text{C}$ 、3mm×3mm QFNおよび10ピンMSOPパッケージ   |

| <b>リファレンス</b> |                                                                                      |                                                                            |

| LTC6655A      | 低ドリフトの高精度バッファ付きリファレンス                                                                | 最大許容誤差:0.025%、2ppm/ $^\circ\text{C}$ (最大)、0.1Hz～10Hzでのノイズ:0.25ppm-p        |