## 特長

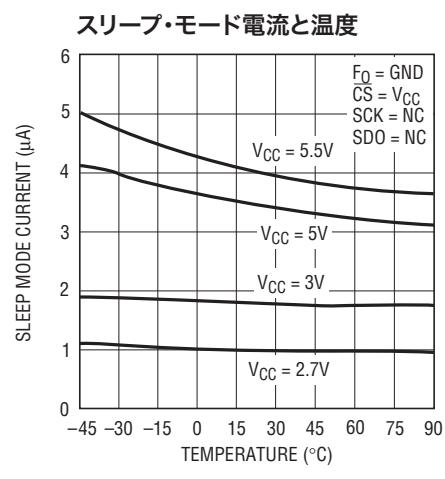

- 低消費電流

(変換モードで $200\mu\text{A}$ 、オートスリープ・モードで $4\mu\text{A}$ )

- GND～V<sub>CC</sub>の同相範囲をもつ差動入力と

差動リファレンス

- INL:3ppm、ミッシング・コードなし

- 10ppmのフルスケール誤差と1ppmのオフセット

- ノイズ:0.56ppm、ENOB(有効ビット数):20.8

- 待ち時間なし:デジタル・フィルタが1サイクルで安定

入力ステップ後も各変換は正確

- 2.7V～5.5Vの単一電源動作

- 内部発振器—外付け部品が不要

- 最小110dB、50Hz/60Hzのノッチ・フィルタ

- 24ビットのLTC2410/LTC2411とピン・コンパチブル

## アプリケーション

- ダイレクト・センサ・デジタイザ

- 秤

- 直接温度測定

- ガス分析器

- 歪みゲージ・トランスジューサ

- 計測

- データ収集

- 産業用プロセス制御

- DVMおよびメータ

## 概要

LTC®2430/LTC2431は2.7V～5.5Vで動作するマイクロパワー20ビット差動デルタシグマ・アナログ-デジタル・コンバータで、発振器を内蔵しており、INLが3ppm、RMSノイズが0.56ppmです。デルタシグマ技術を採用し、マルチプレクス・アプリケーションに対応する1サイクルでのセッティングを実現します。LTC2430/LTC2431は50Hzまたは60Hz±2%で110dB以上の差動モード除去比を達成するように構成できます。また、外部発振器によって、ユーザが定義した除去周波数にドライブすることも可能です。内部発振器には、周波数設定用の部品を外付けする必要はありません。

このコンバータは0.1V～V<sub>CC</sub>のあらゆる外部リファレンス電圧を使用できるので、柔軟なレシオメトリックおよびリモート・センス測定構成が可能です。フルスケール差動入力範囲は、 $-0.5\text{V}_{\text{REF}}\sim 0.5\text{V}_{\text{REF}}$ です。リファレンス同相電圧V<sub>REFCM</sub>と入力同相電圧V<sub>INCM</sub>は、GND～V<sub>CC</sub>の範囲で個別に設定可能です。DC同相入力除去比は120dB以上です。

LTC2430/LTC2431はSPIおよびMICROWIRE™プロトコル適合の柔軟な3線デジタル・インターフェースを介して通信を行います。

、LTC、LTはリニアテクノロジー社の登録商標です。

No Latency ΔΣはリニアテクノロジー社の商標です。

MICROWIREはナショナルセミコンダクタ社の商標です。

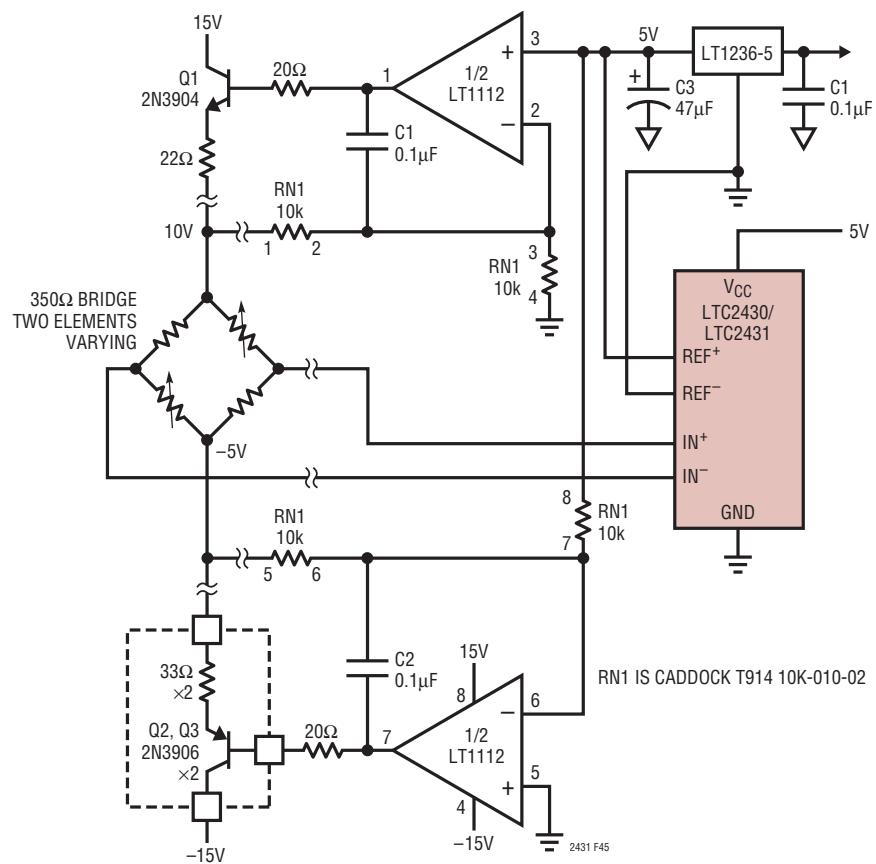

## 標準的応用例

# LTC2430/LTC2431

## 絶対最大定格 (Note 1,2)

|                       |                         |                             |                         |

|-----------------------|-------------------------|-----------------------------|-------------------------|

| 電源電圧( $V_{CC}$ )からGND | -0.3V~7V                | GNDへのデジタル出力電圧               | -0.3V~( $V_{CC}+0.3V$ ) |

| アナログ入力ピンの電圧<br>GNDへ   | -0.3V~( $V_{CC}+0.3V$ ) | 動作温度範囲<br>LTC2430C/LTC2431C | 0°C~70°C                |

| リファレンス入力ピンの電圧<br>GNDへ | -0.3V~( $V_{CC}+0.3V$ ) | LTC2430I/LTC2431I           | -40°C~85°C              |

| GNDへのデジタル入力電圧         | -0.3V~( $V_{CC}+0.3V$ ) | 保存温度範囲                      | -65°C~150°C             |

| GNDへのデジタル入力電圧         | -0.3V~( $V_{CC}+0.3V$ ) | リード温度(半田付け、10秒)             | 300°C                   |

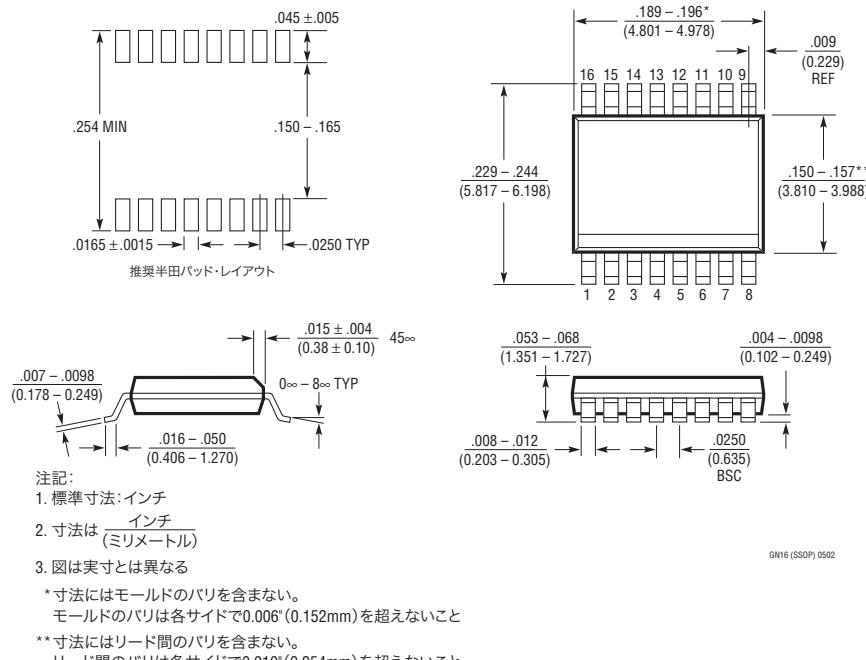

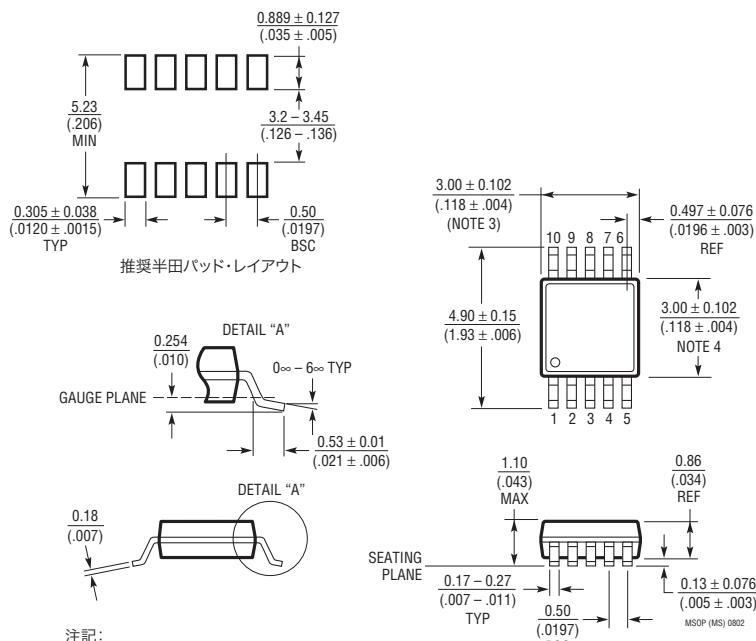

## パッケージ/発注情報

| TOP VIEW                                             | ORDER PART NUMBER        | TOP VIEW                                             | ORDER PART NUMBER        |

|------------------------------------------------------|--------------------------|------------------------------------------------------|--------------------------|

|                                                      |                          |                                                      |                          |

|                                                      | LTC2430CGN<br>LTC2430IGN |                                                      | LTC2431CMS<br>LTC2431IMS |

| GN PACKAGE<br>16-LEAD PLASTIC SSOP                   | GN PART MARKING          | MS PACKAGE<br>10-LEAD PLASTIC MSOP                   | MS PART MARKING          |

| T <sub>JMAX</sub> = 125°C, θ <sub>JA</sub> = 110°C/W | 2430<br>2430I            | T <sub>JMAX</sub> = 125°C, θ <sub>JA</sub> = 120°C/W | LTxD<br>LTxE             |

より広い動作温度範囲で規定されるデバイスについては、弊社へお問い合わせください。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値。(Note 3, 4)

| PARAMETER                       | CONDITIONS                                                                                                                                                                                                                                                                                                                 | MIN | TYP          | MAX          | UNITS                                                                         |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|--------------|-------------------------------------------------------------------------------|

| Resolution (No Missing Codes)   | 0.1V ≤ V <sub>REF</sub> ≤ V <sub>CC</sub> , -0.5 • V <sub>REF</sub> ≤ V <sub>IN</sub> ≤ 0.5 • V <sub>REF</sub> (Note 5)                                                                                                                                                                                                    | ●   | 20           |              | Bits                                                                          |

| Integral Nonlinearity           | 4.5V ≤ V <sub>CC</sub> ≤ 5.5V, REF <sup>+</sup> = 2.5V, REF <sup>-</sup> = GND, V <sub>INCM</sub> = 1.25V (Note 6)<br>5V ≤ V <sub>CC</sub> ≤ 5.5V, REF <sup>+</sup> = 5V, REF <sup>-</sup> = GND, V <sub>INCM</sub> = 2.5V (Note 6)<br>REF <sup>+</sup> = 2.5V, REF <sup>-</sup> = GND, V <sub>INCM</sub> = 1.25V (Note 6) | ●   | 2<br>3<br>10 | 20           | ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub> |

| Offset Error                    | 2.5V ≤ REF <sup>+</sup> ≤ V <sub>CC</sub> , REF <sup>-</sup> = GND,<br>GND ≤ IN <sup>+</sup> = IN <sup>-</sup> ≤ V <sub>CC</sub> (Note 14)                                                                                                                                                                                 | ●   | 5            | 20           | μV                                                                            |

| Offset Error Drift              | 2.5V ≤ REF <sup>+</sup> ≤ V <sub>CC</sub> , REF <sup>-</sup> = GND,<br>GND ≤ IN <sup>+</sup> = IN <sup>-</sup> ≤ V <sub>CC</sub>                                                                                                                                                                                           |     |              | 50           | nV/°C                                                                         |

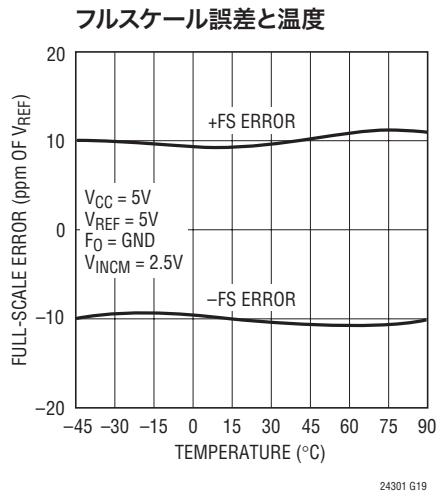

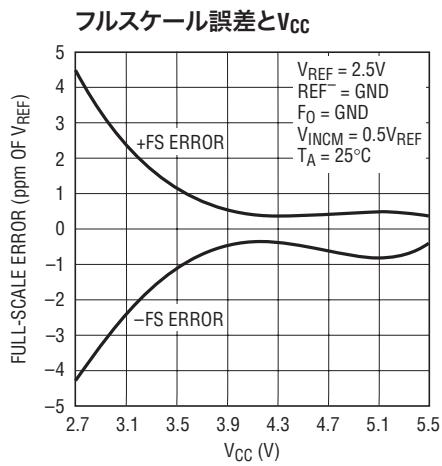

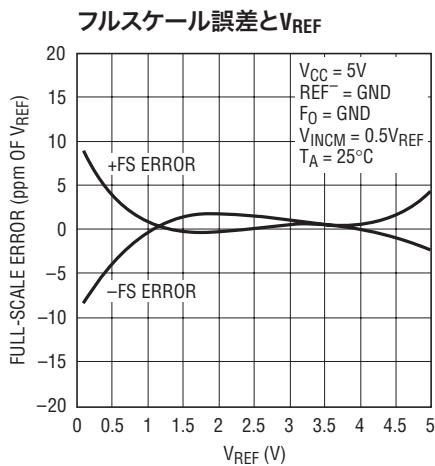

| Positive Full-Scale Error       | 2.5V ≤ REF <sup>+</sup> ≤ V <sub>CC</sub> , REF <sup>-</sup> = GND,<br>IN <sup>+</sup> = 0.75REF <sup>+</sup> , IN <sup>-</sup> = 0.25 • REF <sup>+</sup>                                                                                                                                                                  | ●   | 10           | 20           | ppm of V <sub>REF</sub>                                                       |

| Positive Full-Scale Error Drift | 2.5V ≤ REF <sup>+</sup> ≤ V <sub>CC</sub> , REF <sup>-</sup> = GND,<br>IN <sup>+</sup> = 0.75REF <sup>+</sup> , IN <sup>-</sup> = 0.25 • REF <sup>+</sup>                                                                                                                                                                  |     |              | 0.1          | ppm of V <sub>REF</sub> /°C                                                   |

| Negative Full-Scale Error       | 2.5V ≤ REF <sup>+</sup> ≤ V <sub>CC</sub> , REF <sup>-</sup> = GND,<br>IN <sup>+</sup> = 0.25 • REF <sup>+</sup> , IN <sup>-</sup> = 0.75 • REF <sup>+</sup>                                                                                                                                                               | ●   | 10           | 20           | ppm of V <sub>REF</sub>                                                       |

| Negative Full-Scale Error Drift | 2.5V ≤ REF <sup>+</sup> ≤ V <sub>CC</sub> , REF <sup>-</sup> = GND,<br>IN <sup>+</sup> = 0.25 • REF <sup>+</sup> , IN <sup>-</sup> = 0.75 • REF <sup>+</sup>                                                                                                                                                               |     |              | 0.1          | ppm of V <sub>REF</sub> /°C                                                   |

| Total Unadjusted Error          | 4.5V ≤ V <sub>CC</sub> ≤ 5.5V, REF <sup>+</sup> = 2.5V, REF <sup>-</sup> = GND, V <sub>INCM</sub> = 1.25V<br>5V ≤ V <sub>CC</sub> ≤ 5.5V, REF <sup>+</sup> = 5V, REF <sup>-</sup> = GND, V <sub>INCM</sub> = 2.5V<br>REF <sup>+</sup> = 2.5V, REF <sup>-</sup> = GND, V <sub>INCM</sub> = 1.25V                            |     |              | 3<br>6<br>15 | ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub> |

| Output Noise                    | 5V ≤ V <sub>CC</sub> ≤ 5.5V, REF <sup>+</sup> = 5V, V <sub>REF-</sub> = GND,<br>GND ≤ IN <sup>+</sup> = IN <sup>-</sup> ≤ 5V, (Note 13)                                                                                                                                                                                    |     |              | 2.8          | μVRMS                                                                         |

24301f

## コンバータ特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3、4)

| PARAMETER                               | CONDITIONS                                                                                                                                                |   | MIN | TYP | MAX | UNITS |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|-----|-------|

| Input Common Mode Rejection DC          | $2.5V \leq \text{REF}^+ \leq V_{CC}$ , $\text{REF}^- = \text{GND}$ ,<br>$\text{GND} \leq \text{IN}^- = \text{IN}^+ \leq 5V$ (Note 5)                      | ● | 110 | 120 |     | dB    |

| Input Common Mode Rejection<br>60Hz ±2% | $2.5V \leq \text{REF}^+ \leq V_{CC}$ , $\text{REF}^- = \text{GND}$ ,<br>$\text{GND} \leq \text{IN}^- = \text{IN}^+ \leq 5V$ , (Notes 5, 7)                | ● | 140 |     |     | dB    |

| Input Common Mode Rejection<br>50Hz ±2% | $2.5V \leq \text{REF}^+ \leq V_{CC}$ , $\text{REF}^- = \text{GND}$ ,<br>$\text{GND} \leq \text{IN}^- = \text{IN}^+ \leq 5V$ , (Notes 5, 8)                | ● | 140 |     |     | dB    |

| Input Normal Mode Rejection<br>60Hz ±2% | (Notes 5, 7)                                                                                                                                              | ● | 110 | 140 |     | dB    |

| Input Normal Mode Rejection<br>50Hz ±2% | (Notes 5, 8)                                                                                                                                              | ● | 110 | 140 |     | dB    |

| Reference Common Mode<br>Rejection DC   | $2.5V \leq \text{REF}^+ \leq V_{CC}$ , $\text{GND} \leq \text{REF}^- \leq 2.5V$ ,<br>$V_{REF} = 2.5V$ , $\text{IN}^- = \text{IN}^+ = \text{GND}$ (Note 5) | ● | 130 | 140 |     | dB    |

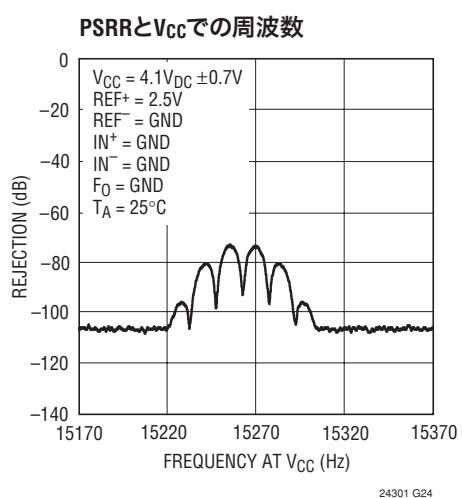

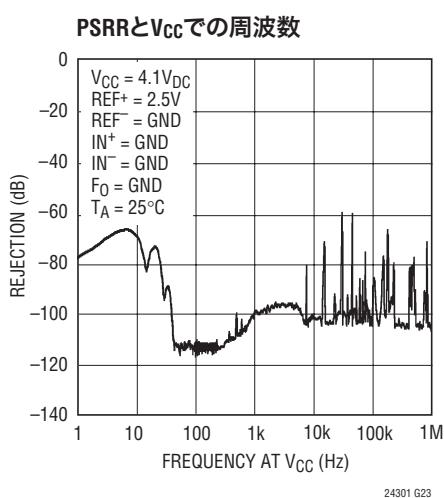

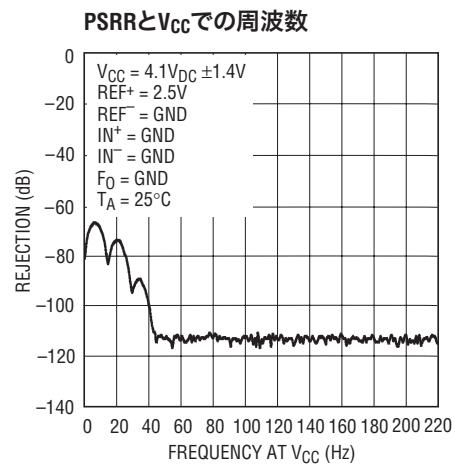

| Power Supply Rejection, DC              | $\text{REF}^+ = 2.5V$ , $\text{REF}^- = \text{GND}$ , $\text{IN}^- = \text{IN}^+ = \text{GND}$                                                            |   |     | 110 |     | dB    |

| Power Supply Rejection, 60Hz ±2%        | $\text{REF}^+ = 2.5V$ , $\text{REF}^- = \text{GND}$ , $\text{IN}^- = \text{IN}^+ = \text{GND}$ , (Note 7)                                                 |   |     | 120 |     | dB    |

| Power Supply Rejection, 50Hz ±2%        | $\text{REF}^+ = 2.5V$ , $\text{REF}^- = \text{GND}$ , $\text{IN}^- = \text{IN}^+ = \text{GND}$ , (Note 8)                                                 |   |     | 120 |     | dB    |

## アナログ入力とリファレンス

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL                       | PARAMETER                                                                 | CONDITIONS                                        |   | MIN          | TYP | MAX             | UNITS |

|------------------------------|---------------------------------------------------------------------------|---------------------------------------------------|---|--------------|-----|-----------------|-------|

| $\text{IN}^+$                | Absolute/Common Mode $\text{IN}^+$ Voltage                                |                                                   | ● | GND – 0.3V   |     | $V_{CC} + 0.3V$ | V     |

| $\text{IN}^-$                | Absolute/Common Mode $\text{IN}^-$ Voltage                                |                                                   | ● | GND – 0.3V   |     | $V_{CC} + 0.3V$ | V     |

| $V_{IN}$                     | Input Differential Voltage Range<br>( $\text{IN}^+ - \text{IN}^-$ )       |                                                   | ● | $-V_{REF}/2$ |     | $V_{REF}/2$     | V     |

| $\text{REF}^+$               | Absolute/Common Mode $\text{REF}^+$ Voltage                               |                                                   | ● | 0.1          |     | $V_{CC}$        | V     |

| $\text{REF}^-$               | Absolute/Common Mode $\text{REF}^-$ Voltage                               |                                                   | ● | GND          |     | $V_{CC} - 0.1V$ | V     |

| $V_{REF}$                    | Reference Differential Voltage Range<br>( $\text{REF}^+ - \text{REF}^-$ ) |                                                   | ● | 0.1          |     | $V_{CC}$        | V     |

| $C_s(\text{IN}^+)$           | $\text{IN}^+$ Sampling Capacitance                                        |                                                   |   |              | 1.5 |                 | pF    |

| $C_s(\text{IN}^-)$           | $\text{IN}^-$ Sampling Capacitance                                        |                                                   |   |              | 1.5 |                 | pF    |

| $C_s(\text{REF}^+)$          | $\text{REF}^+$ Sampling Capacitance                                       |                                                   |   |              | 1.5 |                 | pF    |

| $C_s(\text{REF}^-)$          | $\text{REF}^-$ Sampling Capacitance                                       |                                                   |   |              | 1.5 |                 | pF    |

| $I_{DC\_LEAK}(\text{IN}^+)$  | $\text{IN}^+$ DC Leakage Current                                          | $\bar{CS} = V_{CC}$ , $\text{IN}^+ = \text{GND}$  | ● | -10          | 1   | 10              | nA    |

| $I_{DC\_LEAK}(\text{IN}^-)$  | $\text{IN}^-$ DC Leakage Current                                          | $\bar{CS} = V_{CC}$ , $\text{IN}^- = V_{CC}$      | ● | -10          | 1   | 10              | nA    |

| $I_{DC\_LEAK}(\text{REF}^+)$ | $\text{REF}^+$ DC Leakage Current                                         | $\bar{CS} = V_{CC}$ , $\text{REF}^+ = V_{CC}$     | ● | -10          | 1   | 10              | nA    |

| $I_{DC\_LEAK}(\text{REF}^-)$ | $\text{REF}^-$ DC Leakage Current                                         | $\bar{CS} = V_{CC}$ , $\text{REF}^- = \text{GND}$ | ● | -10          | 1   | 10              | nA    |

# LTC2430/LTC2431

## デジタル入力とデジタル出力

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL   | PARAMETER                                         | CONDITIONS                                                                     | MIN                 | TYP             | MAX        | UNITS         |

|----------|---------------------------------------------------|--------------------------------------------------------------------------------|---------------------|-----------------|------------|---------------|

| $V_{IH}$ | High Level Input Voltage<br>$\overline{CS}, F_0$  | $2.7V \leq V_{CC} \leq 5.5V$<br>$2.7V \leq V_{CC} \leq 3.3V$                   | ●<br>2.7V<br>2.0    | 2.5<br>2.0      | 0.8<br>0.6 | V<br>V        |

| $V_{IL}$ | Low Level Input Voltage<br>$\overline{CS}, F_0$   | $4.5V \leq V_{CC} \leq 5.5V$<br>$2.7V \leq V_{CC} \leq 5.5V$                   | ●<br>4.5V<br>2.7V   | 2.5<br>2.0      | 0.8<br>0.6 | V<br>V        |

| $V_{IH}$ | High Level Input Voltage<br>SCK                   | $2.7V \leq V_{CC} \leq 5.5V$ (Note 9)<br>$2.7V \leq V_{CC} \leq 3.3V$ (Note 9) | ●<br>2.7V<br>2.0    | 2.5<br>2.0      | 0.8<br>0.6 | V<br>V        |

| $V_{IL}$ | Low Level Input Voltage<br>SCK                    | $4.5V \leq V_{CC} \leq 5.5V$ (Note 9)<br>$2.7V \leq V_{CC} \leq 5.5V$ (Note 9) | ●<br>4.5V<br>2.7V   | 2.5<br>2.0      | 0.8<br>0.6 | V<br>V        |

| $I_{IN}$ | Digital Input Current<br>$\overline{CS}, F_0$     | $0V \leq V_{IN} \leq V_{CC}$                                                   | ●<br>0V             | -10             | 10         | $\mu\text{A}$ |

| $I_{IN}$ | Digital Input Current<br>SCK                      | $0V \leq V_{IN} \leq V_{CC}$ (Note 9)                                          | ●<br>0V             | -10             | 10         | $\mu\text{A}$ |

| $C_{IN}$ | Digital Input Capacitance<br>$\overline{CS}, F_0$ |                                                                                |                     | 10              |            | $\text{pF}$   |

| $C_{IN}$ | Digital Input Capacitance<br>SCK                  | (Note 9)                                                                       |                     | 10              |            | $\text{pF}$   |

| $V_{OH}$ | High Level Output Voltage<br>SDO                  | $I_O = -800\mu\text{A}$                                                        | ●<br>I <sub>O</sub> | $V_{CC} - 0.5V$ |            | V             |

| $V_{OL}$ | Low Level Output Voltage<br>SDO                   | $I_O = 1.6\text{mA}$                                                           | ●<br>I <sub>O</sub> | 0.4             |            | V             |

| $V_{OH}$ | High Level Output Voltage<br>SCK                  | $I_O = -800\mu\text{A}$ (Note 10)                                              | ●<br>I <sub>O</sub> | $V_{CC} - 0.5V$ |            | V             |

| $V_{OL}$ | Low Level Output Voltage<br>SCK                   | $I_O = 1.6\text{mA}$ (Note 10)                                                 | ●<br>I <sub>O</sub> | 0.4             |            | V             |

| $I_{OZ}$ | Hi-Z Output Leakage<br>SDO                        |                                                                                | ●<br>I <sub>O</sub> | -10             | 10         | $\mu\text{A}$ |

## 電源条件

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL   | PARAMETER                         | CONDITIONS                                                        | MIN      | TYP | MAX | UNITS         |

|----------|-----------------------------------|-------------------------------------------------------------------|----------|-----|-----|---------------|

| $V_{CC}$ | Supply Voltage                    |                                                                   | ●<br>2.7 | 2.7 | 5.5 | V             |

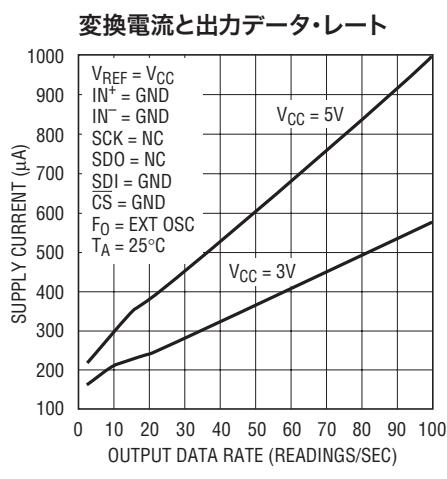

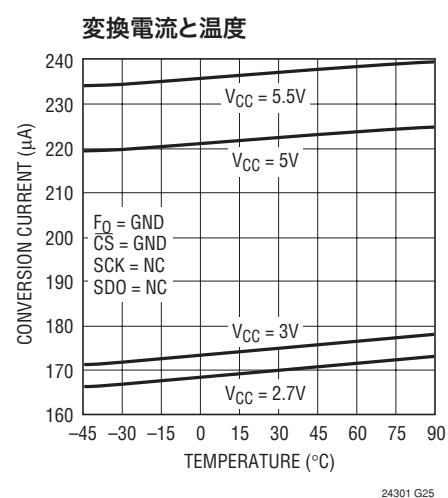

| $I_{CC}$ | Supply Current<br>Conversion Mode | $\overline{CS} = 0V$ (Note 12)                                    |          | 200 | 300 | $\mu\text{A}$ |

|          | Sleep Mode                        | $\overline{CS} = V_{CC}$ (Note 12)                                |          | 4   | 10  | $\mu\text{A}$ |

|          | Sleep Mode                        | $\overline{CS} = V_{CC}, 2.7V \leq V_{CC} \leq 3.3V$<br>(Note 12) |          | 2   | 2   | $\mu\text{A}$ |

## タイミング特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL          | PARAMETER                                             | CONDITIONS                                                               | MIN         | TYP                                            | MAX                                  | UNITS          |

|-----------------|-------------------------------------------------------|--------------------------------------------------------------------------|-------------|------------------------------------------------|--------------------------------------|----------------|

| $f_{EOSC}$      | External Oscillator Frequency Range                   |                                                                          | ●           | 5                                              | 2000                                 | kHz            |

| $t_{THEO}$      | External Oscillator High Period                       |                                                                          | ●           | 0.25                                           | 200                                  | μs             |

| $t_{LEO}$       | External Oscillator Low Period                        |                                                                          | ●           | 0.25                                           | 200                                  | μs             |

| $t_{CONV}$      | Conversion Time                                       | $F_0 = 0\text{V}$<br>$F_0 = V_{CC}$<br>External Oscillator (Note 11)     | ●<br>●<br>● | 130.86<br>157.03<br>20510/ $f_{EOSC}$ (in kHz) | 133.53<br>160.23<br>136.20<br>163.44 | ms<br>ms<br>ms |

| $f_{ISCK}$      | Internal SCK Frequency                                | Internal Oscillator (Note 10)<br>External Oscillator (Notes 10, 11)      |             |                                                | 19.2<br>$f_{EOSC}/8$                 | kHz<br>kHz     |

| $D_{ISCK}$      | Internal SCK Duty Cycle                               | (Note 10)                                                                | ●           | 45                                             | 55                                   | %              |

| $f_{ESCK}$      | External SCK Frequency Range                          | (Note 9)                                                                 | ●           |                                                | 2000                                 | kHz            |

| $t_{LESCK}$     | External SCK Low Period                               | (Note 9)                                                                 | ●           | 250                                            |                                      | ns             |

| $t_{HESCK}$     | External SCK High Period                              | (Note 9)                                                                 | ●           | 250                                            |                                      | ns             |

| $t_{DOUT_ISCK}$ | Internal SCK 24-Bit Data Output Time                  | Internal Oscillator (Notes 10, 12)<br>External Oscillator (Notes 10, 11) | ●<br>●      | 1.22<br>192/ $f_{EOSC}$ (in kHz)               | 1.25<br>1.28                         | ms<br>ms       |

| $t_{DOUT_ESCK}$ | External SCK 24-Bit Data Output Time                  | (Note 9)                                                                 | ●           |                                                | 24/ $f_{ESCK}$ (in kHz)              | ms             |

| $t_1$           | $\overline{\text{CS}} \downarrow$ to SDO Low Z        |                                                                          | ●           | 0                                              | 200                                  | ns             |

| $t_2$           | $\overline{\text{CS}} \uparrow$ to SDO High Z         |                                                                          | ●           | 0                                              | 200                                  | ns             |

| $t_3$           | $\overline{\text{CS}} \downarrow$ to SCK $\downarrow$ | (Note 10)                                                                | ●           | 0                                              | 200                                  | ns             |

| $t_4$           | $\overline{\text{CS}} \downarrow$ to SCK $\uparrow$   | (Note 9)                                                                 | ●           | 50                                             |                                      | ns             |

| $t_{KQMAX}$     | SCK $\downarrow$ to SDO Valid                         |                                                                          | ●           |                                                | 220                                  | ns             |

| $t_{KQMIN}$     | SDO Hold After SCK $\downarrow$                       | (Note 5)                                                                 | ●           | 15                                             |                                      | ns             |

| $t_5$           | SCK Set-Up Before $\overline{\text{CS}} \downarrow$   |                                                                          | ●           | 50                                             |                                      | ns             |

| $t_6$           | SCK Hold After $\overline{\text{CS}} \downarrow$      |                                                                          | ●           |                                                | 50                                   | ns             |

Note 1: 絶対最大定格はそれを超えるとデバイスの寿命に影響を及ぼす値。

Note 2: 全ての電圧値はGNDを基準にしている。

Note 3: 注記がない限り、 $V_{CC} = 2.7\text{V} \sim 5.5\text{V}$ 。

$V_{REF} = \text{REF}^+ - \text{REF}^-$ ,  $V_{REFCM} = (\text{REF}^+ + \text{REF}^-)/2$ ;

$V_{IN} = \text{IN}^+ - \text{IN}^-$ ,  $V_{INCM} = (\text{IN}^+ + \text{IN}^-)/2$ .

Note 4: 注記がない限り、 $F_0$ ピンはGNDまたは $V_{CC}$ または $f_{EOSC} = 153600\text{Hz}$ の外部変換クロック・ソースに接続する。

Note 5: 設計によって保証されているが、テストされない。

Note 6: 積分非直線性は、実際の伝達曲線のエンドポイントを通る直線からのコードの偏差として定義されている。偏差は測定されたコードから期待値を差し引いた値として計算される。

Note 7:  $F_0 = 0\text{V}$  (内部発振器) または  $f_{EOSC} = 153600\text{Hz} \pm 2\%$  (外部発振器)

Note 8:  $F_0 = V_{CC}$  (内部発振器) または  $f_{EOSC} = 128000\text{Hz} \pm 2\%$  (外部発振器)

Note 9: コンバータは外部SCKモードで動作しているので、SCKピンはデジタル入力として使用されている。データの出力時にSCKをドライブするクロック信号の周波数は $f_{ESCK}$ であり、kHzで表されている。

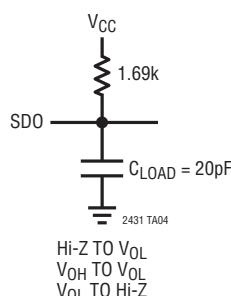

Note 10: コンバータは内部SCKモードで動作しているので、SCKピンはデジタル出力として使用されている。この動作モードでは、SCKピンの全等価負荷容量は $C_{LOAD} = 20\text{pF}$ である。

Note 11: 外部発振器は $F_0$ ピンに接続される。外部発振器の周波数 ( $f_{EOSC}$ ) はkHzで表されている。

Note 12: コンバータは内部発振器を使用する。

$F_0 = 0\text{V}$ または $F_0 = V_{CC}$ 。

Note 13: 出力ノイズには内部較正動作によって生じる分が含まれる。

Note 14: 設計およびテストの相関により保証されている。

# LTC2430/LTC2431

## 標準的性能特性

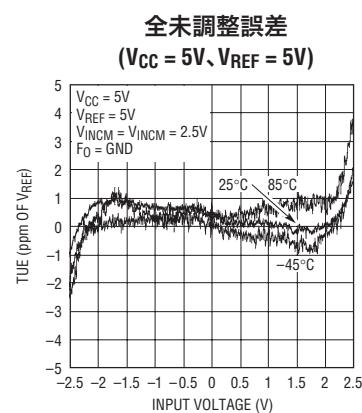

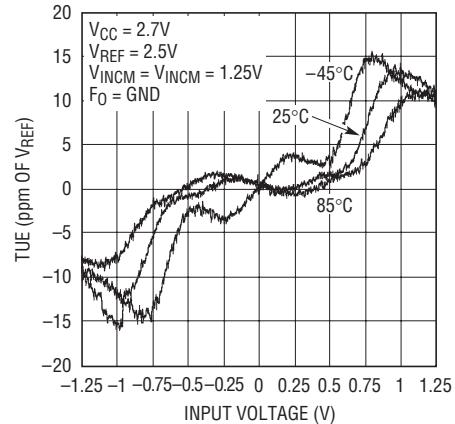

### 全未調整誤差

( $V_{CC} = 5V$ ,  $V_{REF} = 5V$ )

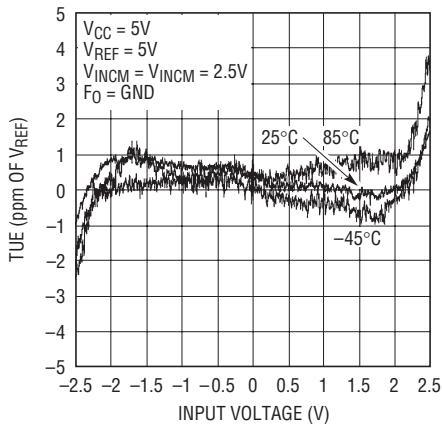

### 全未調整誤差

( $V_{CC} = 5V$ ,  $V_{REF} = 2.5V$ )

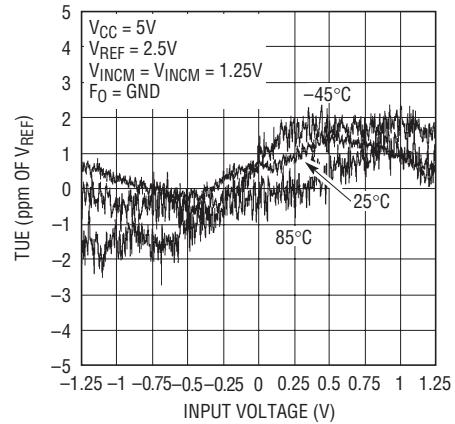

### 全未調整誤差

( $V_{CC} = 2.7V$ ,  $V_{REF} = 2.5V$ )

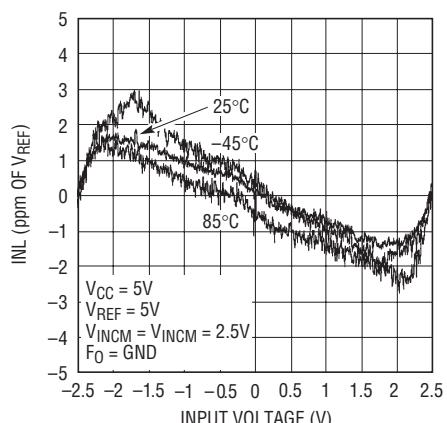

### 積分非直線性

( $V_{CC} = 5V$ ,  $V_{REF} = 5V$ )

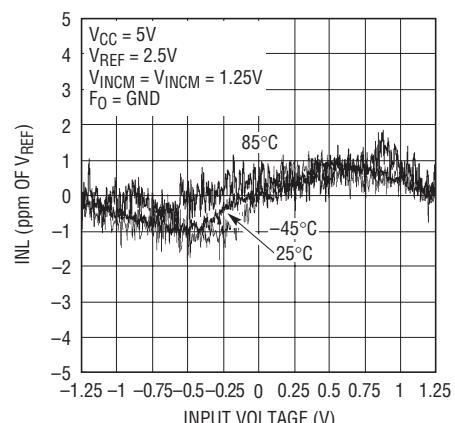

### 積分非直線性

( $V_{CC} = 5V$ ,  $V_{REF} = 2.5V$ )

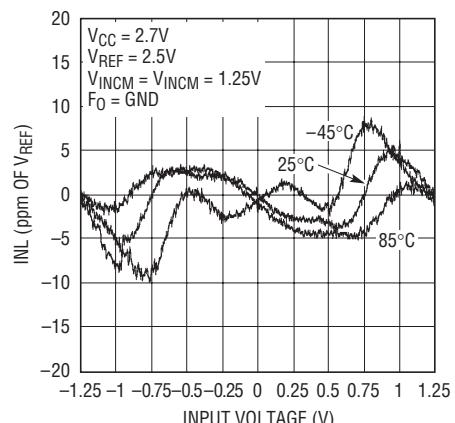

### 積分非直線性

( $V_{CC} = 2.7V$ ,  $V_{REF} = 2.5V$ )

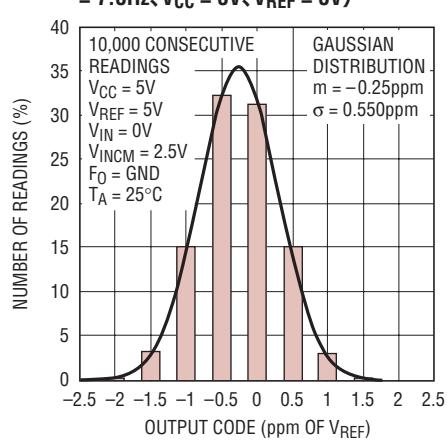

### ノイズのヒストグラム(出力レート = 7.5Hz, $V_{CC} = 5V$ , $V_{REF} = 5V$ )

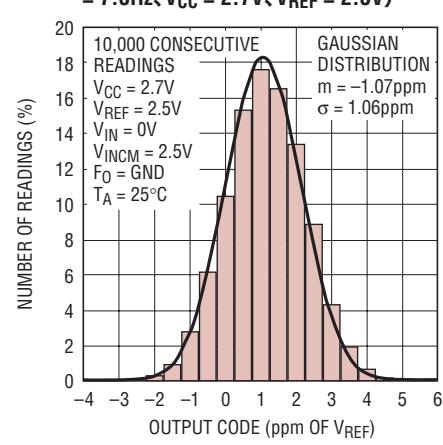

### ノイズのヒストグラム(出力レート = 7.5Hz, $V_{CC} = 2.7V$ , $V_{REF} = 2.5V$ )

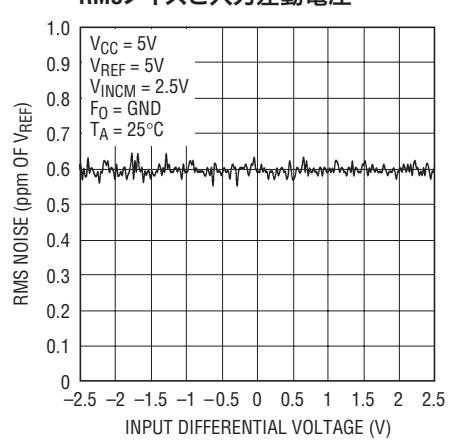

### RMSノイズと入力差動電圧

24301f

## 標準的性能特性

# LTC2430/LTC2431

## 標準的性能特性

## ピン機能 (LTC2430)

**GND(ピン1、7、8、9、10、15、16)**: グランド。グランド電流の流れとV<sub>CC</sub>のデカッピングを最適にするため、内部で結合されている複数のグランド・ピン。これらのピンのそれぞれを1つのグランド・プレーンに低インピーダンスで接続します。適正な動作のためには7つのピン全てをグランドに接続する必要があります。

**V<sub>CC</sub>(ピン2)**: 正電源電圧。10μFのタンタル・コンデンサと0.1μFのセラミック・コンデンサを並列に使って、デバイスのできるだけ近くでGNDにバイパスします。

**REF<sup>+</sup>(ピン3)、REF<sup>-</sup>(ピン4)**: 差動リファレンス入力。これらのピンの電圧は、リファレンスの正入力REF<sup>+</sup>がリファレンスの負入力REF<sup>-</sup>より少なくとも0.1Vだけ高く保たれる限り、GND～V<sub>CC</sub>の範囲の任意の電圧することができます。

**IN<sup>+</sup>(ピン5)、IN<sup>-</sup>(ピン6)**: 差動アナログ入力。これらのピンの電圧はGND-0.3V～V<sub>CC</sub>+0.3Vの範囲の任意の値にすることができます。これらのリミット内では、コンバータのバイポーラ入力範囲(V<sub>IN</sub> = IN<sup>+</sup>-IN<sup>-</sup>)は-0.5 • (V<sub>REF</sub>) ~ 0.5 • (V<sub>REF</sub>)となります。この入力範囲の外側では、コンバータは固有のオーバーレンジとアンダーレンジの出力コードを発生します。

**CS(ピン11)**: アクティブ“L”的デジタル入力。このピンを“L”にすると、SDOデジタル出力が有効になり、ADCが覚醒します。各変換の後、ADCは自動的にスリープ・モードに入り、CSが“H”に留まる限りこの省電力状態に保たれます。「データ出力」の転送中にCSが“L”から“H”に遷移すると、データ転送が中止され、新たに変換が開始されます。

## (LTC2431)

**V<sub>CC</sub>(ピン1)**: 正電源電圧。10μFのタンタル・コンデンサと0.1μFのセラミック・コンデンサを並列に使って、デバイスのできるだけ近くでGND(ピン6)にバイパスします。

**REF<sup>+</sup>(ピン2)、REF<sup>-</sup>(ピン3)**: 差動リファレンス入力。これらのピンの電圧は、リファレンスの正入力REF<sup>+</sup>がリファレンスの負入力REF<sup>-</sup>より少なくとも0.1Vだけ高く保たれる限り、GND～V<sub>CC</sub>の範囲の任意の電圧することができます。

**IN<sup>+</sup>(ピン4)、IN<sup>-</sup>(ピン5)**: 差動アナログ入力。これらのピンの電圧はGND-0.3V～V<sub>CC</sub>+0.3Vの範囲の任意の値にすることができます。これらのリミット内では、コンバータのバイポーラ入力範囲(V<sub>IN</sub> = IN<sup>+</sup>-IN<sup>-</sup>)は-0.5 • (V<sub>REF</sub>) ~ 0.5 • (V<sub>REF</sub>)となります。

**SDO(ピン12)**: スリーステートのデジタル出力。データ出力の期間中、このピンはシリアル・データの出力として使われます。チップ・セレクトCSが“H”的とき(CS = V<sub>CC</sub>)、SDOピンは高インピーダンス状態になります。変換とスリープの間、このピンは変換状態出力として使われます。変換状態はCSを“L”に引き下げるとき観察することができます。

**SCK(ピン13)**: 双方向デジタル・クロック・ピン。内部シリアル・クロック動作モードでは、SCKはデータ出力期間中は内部シリアル・インターフェース・クロックのデジタル出力として使われます。外部シリアル・クロック動作モードでは、SCKはデータ出力期間中は外部シリアル・インターフェース・クロックのデジタル入力として使われます。内部シリアル・クロック動作モードでは、弱い内部プルアップが自動的に動作状態になります。シリアル・クロック動作モードは電源立上げ時またはCSの最新の立ち下りエッジの間SCKピンに与えられるロジック・レベルによって決まります。

**F<sub>O</sub>(ピン14)**: 周波数制御ピン。ADCのノッチ周波数と変換時間を制御するデジタル入力。F<sub>O</sub>ピンがV<sub>CC</sub>に接続されると(F<sub>O</sub> = V<sub>CC</sub>)、コンバータはその内部発振器を使い、デジタル・フィルタの最初のヌルは50Hzに位置します。F<sub>O</sub>ピンがGNDに接続されると(F<sub>O</sub> = 0V)、コンバータはその内部発振器を使い、デジタル・フィルタの最初のヌルは60Hzに位置します。F<sub>O</sub>が外部クロック信号によって周波数f<sub>EOSC</sub>でドライブされると、コンバータはこの信号をそのシステム・クロックとして使い、デジタル・フィルタの最初のヌルは周波数f<sub>EOSC</sub>/2560に位置します。

この入力範囲の外側では、コンバータは固有のオーバーレンジとアンダーレンジの出力コードを発生します。

**GND(ピン6)**: グランド。このピンを1つのグランド・プレーンに低インピーダンスで接続します。

**CS(ピン7)**: アクティブ“L”的デジタル入力。このピンを“L”にすると、SDOデジタル出力が有効になり、ADCが覚醒します。各変換の後、ADCは自動的にスリープ・モードに入り、CSが“H”に留まる限りこの省電力状態に保たれます。「データ出力」の転送中にCSが“L”から“H”に遷移すると、データ転送が中止され、新たに変換が開始されます。

# LTC2430/LTC2431

## ピン機能 (LTC2431)

**SDO(ピン8) :**スリーステートのデジタル出力。「データ出力」の期間中、このピンはシリアル・データ出力として使われます。チップ・セレクト $\overline{CS}$ が“H”的とき( $\overline{CS} = V_{CC}$ )、SDOピンは高インピーダンス状態になります。変換とスリープの間、このピンは変換状態出力として使われます。変換状態は $\overline{CS}$ を“L”に引き下げるとき観察することができます。

**SCK(ピン9) :**双方向デジタル・クロック・ピン。内部シリアル・クロック動作モードでは、SCKはデータ出力期間中は内部シリアル・インターフェース・クロックのデジタル出力として使われます。外部シリアル・クロック動作モードでは、SCKはデータ出力期間中は外部シリアル・インターフェース・クロックのデジタル入力として使われます。内部シリアル・クロック動作モードでは、弱い内部プルアップが自動的に動作状態になります。シリアル・クロック動

作モードは電源立ち上げ時または $\overline{CS}$ の最新の立下りエッジの間にSCKピンに与えられるロジック・レベルによって決まります。

**F<sub>0</sub>(ピン10) :**周波数制御ピン。ADCのノッチ周波数と変換時間を制御するデジタル入力。F<sub>0</sub>ピンがV<sub>CC</sub>に接続されているとき(F<sub>0</sub> = V<sub>CC</sub>)、コンバータはその内部発振器を使い、デジタル・フィルタの最初のヌルは50Hzに位置します。F<sub>0</sub>ピンがGNDに接続されているとき(F<sub>0</sub> = 0V)、コンバータはその内部発振器を使い、デジタル・フィルタの最初のヌルは60Hzに位置します。F<sub>0</sub>が外部クロック信号によって周波数f<sub>EOSC</sub>でドライブされると、コンバータはこの信号をそのシステム・クロックとして使い、デジタル・フィルタの最初のヌルは周波数f<sub>EOSC</sub>/2560に位置します。

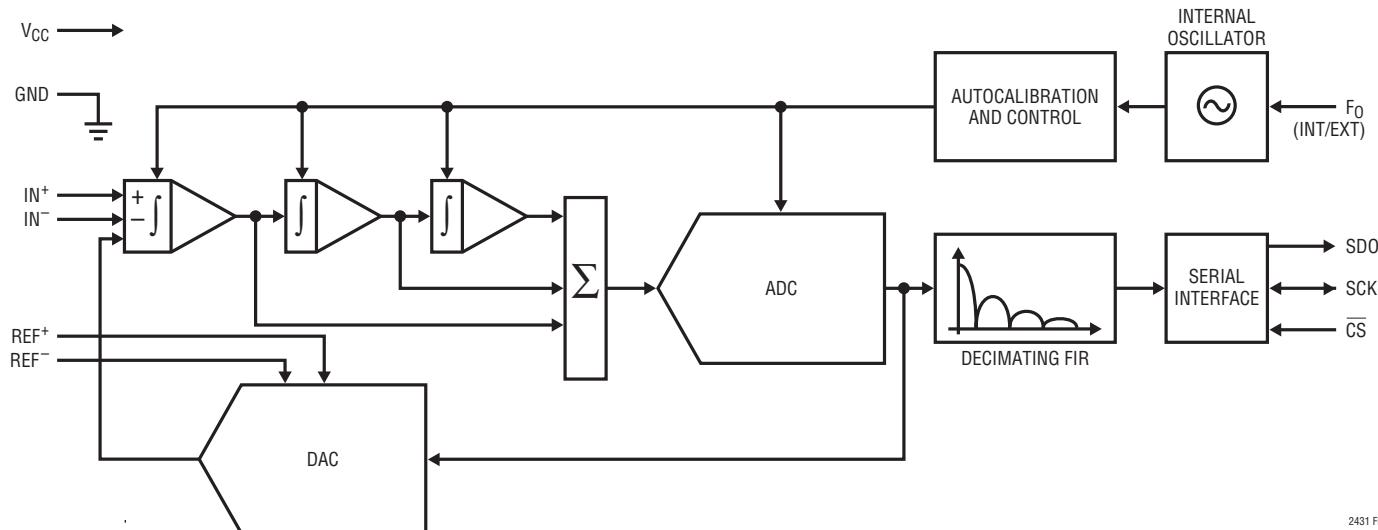

## 機能を示すブロック図

図. 1

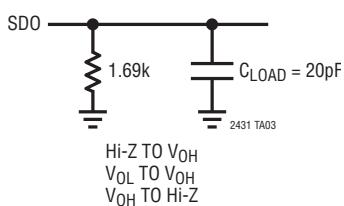

## テスト回路

24301f

## アプリケーション情報

### コンバータの動作

#### コンバータの動作サイクル

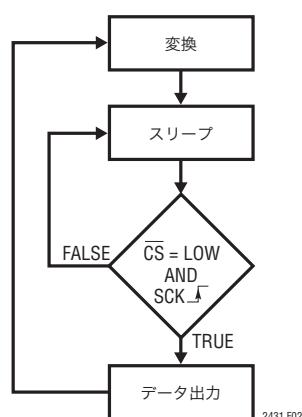

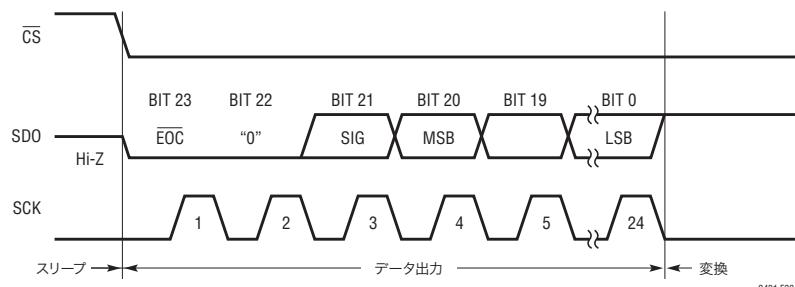

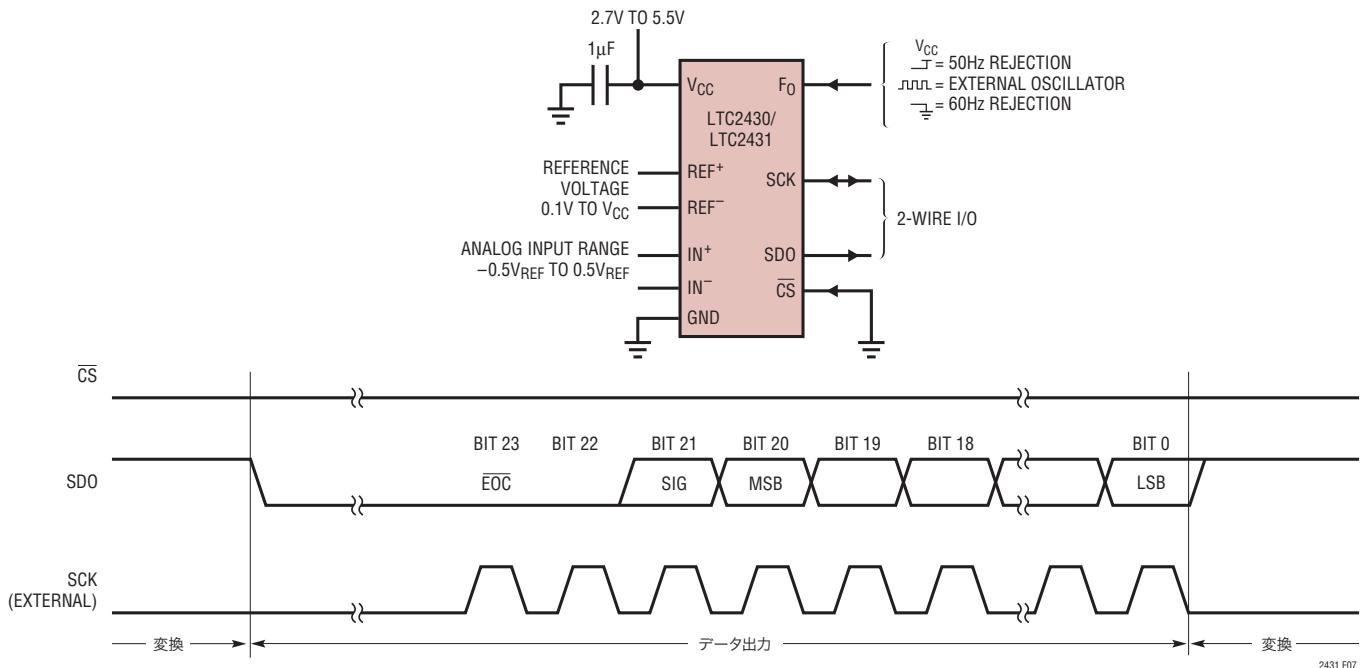

LTC2430/LTC2431は低消費電力デルタシグマADコンバータで、使いやすい3線シリアル・インターフェースを備えています(図1を参照)。その動作は3つのステートで構成されています。コンバータの動作サイクルは変換ステートから始まり、省電力のスリープ・ステートがそれに続き、データ出力ステートで終了します(図2を参照)。3線式のインターフェースはシリアル・データ出力(SDO)、シリアル・クロック(SCK)およびチップ・セレクト(CS)で構成されています。

LTC2430/LTC2431は最初に変換をおこないます。変換が完了すると、デバイスはスリープ・ステートに入ります。CSが“H”に保たれている限り、デバイスはスリープ・ステートに留まります。このスリープ・ステートの間、電力消費は2桁近く減少します。コンバータがスリープ・ステートの間、変換結果はスタチック・シフトレジスタ内に無期限に保存されます。

CSが“L”に引き下げられると、デバイスは省電力モードから出て、データ出力ステートに入ります。SCKの最初の立上りエッジの前に $\overline{\text{CS}}$ が“H”に引き上げられると、デバイスは省電力のスリープ・モードに戻り、変換結果は内部のスタチック・シフトレジスタ内に依然として保たれます。SCKの最初の立上りエッジの後 $\overline{\text{CS}}$ が“L”的ままだと、デバイスは変換結果を出し始めます。この時点でCSを“H”にすると、データの出力状態が終了し、新しい変換が開始されます。変換結果には待ち時間がありません。データの出力は直前に終了した変換に対応して

図2. LTC2430/LTC2431の状態遷移図

います。この結果はシリアル・クロック(SCK)によって制御されて、シリアル・データ出力ピン(SDO)からシフトされて出力されます。

データはSCKの立下りエッジによって更新されるので、ユーザーはSCKの立上りエッジを使って確実にデータをラッチすることができます(図3を参照)。データ出力ステートは24ビットがADCから読み出されるか、CSが“H”に引き上げられると終了します。デバイスは自動的に新しい変換を開始し、このサイクルが繰り返されます。

$\overline{\text{CS}}$ ピンとSCKピンのタイミング制御によって、LTC2430/LTC2431はいくつかの動作モード(内部または外部のSCKと自走変換の各モード)を柔軟に提供します。これらの多様なモードはプログラミング用構成レジスタを必要としません。さらに、上記の周期動作を乱すことがありません。これらの動作モードについては「シリアル・インターフェースのタイミング・モード」のセクションで詳しく説明します。

#### 変換クロック

従来型のコンバータに較べてデルタシグマ・コンバータが与える主な利点は(一般に同期フィルタまたは櫛形フィルタとして実装される)内蔵デジタル・フィルタです。高分解能で低周波数のアプリケーションの場合、このフィルタは一般に50Hzまたは60Hzのライン周波数およびそれらの高調波を除去するように設計されます。フィルタの除去性能はコンバータのシステム・クロックの精度に直接関係します。LTC2430/LTC2431には高精度の発振器が内蔵されています。したがって、水晶や発振器など外部で周波数を設定する部品は不要です。LTC2430/LTC2431は内蔵発振器でクロック信号が与えられ、ライン周波数(50Hzまたは60Hz)で最小110dBの除去を達成します。

#### 使いやすさ

LTC2430/LTC2431のデータ出力には、待ち時間、フィルタのセトリング遅延、または変換サイクルに関連した冗長データがありません。変換と出力データの間には1対1対応の関係があります。したがって、複数のアナログ入力の多重化が容易です。

LTC2430/LTC2431は変換サイクルごとにオフセットとフルスケールの較正を行います。この較正はユーザーからは見えず、上記のサイクル動作には影響を与えません。連続較正の利点は、時間経過、電源電圧の変化、および温度ドリフトに対してオフセットとフルスケールの測定値がきわめて安定していることです。

# LTC2430/LTC2431

## アプリケーション情報

### パワーアップ・シーケンス

LTC2430/LTC2431は電源電圧V<sub>CC</sub>が約2Vより下に下がると自動的に内部リセット状態になります。この機能により、変換結果とシリアル・インターフェースによるモード選択の一貫性が保証されます（「シリアル・インターフェースのタイミング・モード」のセクションの「2線式I/O」のセクションを参照）。

V<sub>CC</sub>電圧がこの臨界スレッショルドを超えると、LTC2430またはLTC2431は約1msの長さの内部パワーオン・リセット（POR）信号を発生します。このPOR信号により、全ての内部レジスタがクリアされます。POR信号に続き、コンバータは通常の変換サイクルを開始し、上述のステートが継起します。PORに続く最初の変換結果の精度は、PORの時間間隔が経過する前に電源電圧が動作範囲（2.7V～5.5V）内に回復していれば、デバイスの仕様を満たします。

### リファレンス電圧範囲

LTC2430/LTC2431は差動の外部リファレンス電圧を受け入れます。REF<sup>+</sup>ピンとREF<sup>-</sup>ピンの絶対/同相電圧の仕様はGND～V<sub>CC</sub>の全範囲を含みます。コンバータが正しく動作するには、REF<sup>+</sup>ピンはREF<sup>-</sup>ピンよりも常に高い電位でなければなりません。

LTC2430/LTC2431は0.1V～V<sub>CC</sub>の差動リファレンス電圧を受け入れることができます。コンバータ（LTC2430/LTC2431）の出力ノイズはフロントエンド回路の熱ノイズによって決まるので、マイクロボルトで表したその値はリファレンス電圧に対してほぼ一定です。リファレンス電圧を下げても、コンバータの実効分解能は大きくは改善されません。他方、リファレンス電圧を下げると、コンバータの全体のINL性能が改善されます。リファレンス電圧が減少すると、かなり高い出力データ・レートで外部変換クロック（外部F<sub>O</sub>信号）を使って動作させると、コンバータの性能も改善されます。

### 入力電圧範囲

アナログ入力は真に差動で、IN<sup>+</sup>とIN<sup>-</sup>の入力ピンの絶対/同相範囲はGND−0.3VからV<sub>CC</sub>+0.3Vまでです。これらのリミットの外側では、ESD保護用デバイスがオンし始め、入力のリーク電流による誤差が急速に増加します。これらのリミット内では、LTC2430またはLTC2431はバイポーラ差動入力信号（V<sub>IN</sub>=IN<sup>+</sup>−IN<sup>-</sup>）を−FS=−0.5•V<sub>REF</sub>から+FS=0.5•V<sub>REF</sub>に変換します。ここで、V<sub>REF</sub>=REF<sup>+</sup>−REF<sup>-</sup>です。この範囲の外側では、コンバータは固有の出力コードを使ってオーバーレンジまたはアンダーレンジの状態を表示します。

IN<sup>+</sup>ピンとIN<sup>-</sup>ピンに与えられる入力信号は、グランドより300mV下およびV<sub>CC</sub>より300mV上まで達することができます。どんなフォールト電流も制限するため、デバイスの性能に影響を与えることなく、最大5kの抵抗をIN<sup>+</sup>ピンとIN<sup>-</sup>ピンに直列に追加することができます。物理的レイアウトでは、これらの直列抵抗と対応するピンの間の接続の寄生容量をできるだけ低く保つのが重要です。したがって、抵抗はできるだけピンに近づけて配置します。さらに、直列抵抗は入力リーク電流により、温度に依存したオフセット誤差を生じます。V<sub>REF</sub>=5Vのとき、1nAの入力リーク電流により、5kの抵抗には1ppmのオフセット誤差が生じます。この誤差は非常に大きく温度に依存します。

### 出力データのフォーマット

LTC2430/LTC2431のシリアル出力のデータ・ストリームは24ビット長です。次の21ビットは変換結果で、MSBが最初にきます。3番目と4番目のビットは一緒にになってアンダーレンジ状態（差動入力電圧が−FSより下）またはオーバーレンジ状態（差動入力電圧が+FSより上）を示すのにも使われます。

ビット23（最初の出力ビット）は変換終了（EOC）のインジケータです。このビットは、変換ステートおよびスリープ・ステートの間、CSピンが“L”的ときSDOピンから読み出せます。このビットは変換中は“H”で、変換が完了すると“L”になります。

ビット22（2番目の出力ビット）はダミービット（DMY）で、常に“L”です。

ビット21（3番目の出力ビット）は変換結果の符合のインジケータ（SIG）です。V<sub>IN</sub>が>0ならば、このビットは“H”になります。V<sub>IN</sub>が<0ならば、このビットは“L”になります。

ビット20（4番目の出力ビット）は結果の最上位ビット（MSB）です。このビットはビット21と組み合わされてアンダーレンジまたはオーバーレンジも表示します。ビット21とビット20が両方とも“H”的場合、差動入力電圧が+FSを越えています。

ビット21とビット20が両方とも“L”的場合、差動入力電圧が−FSよりも下に下がっています。

## アプリケーション情報

これらのビットの機能を表1にまとめています。

表1. LTC2430/LTC2431の状態ビット

| Input Range                           | Bit 23<br>EOC | Bit 22<br>DMY | Bit 21<br>SIG | Bit 20<br>MSB |

|---------------------------------------|---------------|---------------|---------------|---------------|

| $V_{IN} \geq 0.5 \cdot V_{REF}$       | 0             | 0             | 1             | 1             |

| $0V \leq V_{IN} < 0.5 \cdot V_{REF}$  | 0             | 0             | 1             | 0             |

| $-0.5 \cdot V_{REF} \leq V_{IN} < 0V$ | 0             | 0             | 0             | 1             |

| $V_{IN} < -0.5 \cdot V_{REF}$         | 0             | 0             | 0             | 0             |

ビット20からビット0までは21ビットの変換結果で、MSBが先にきます。

ビット0は最下位ビット(LSB)です。

データはシリアル・クロック(SCK)によって制御されてSDOピンからシフトされて出力されます(図3を参照)。 $\overline{CS}$ が“H”的ときは常にSDOは高インピーダンスに保たれ、外部で発生させたSCKクロック・パルスは全て内部のデータ出力シフトレジスタによって無視されます。

変換結果をデバイスからシフトして出力するには、最初に $\overline{CS}$ を“L”にドライブする必要があります。 $\overline{CS}$ が“L”に引き下げられると、デバイスのSDOピンに $\overline{EOC}$ が現われます。 $\overline{EOC}$ は変換完了時にリアルタイムで“H”から“L”に変化します。この信号は外部のマイクロコントローラへの割り込み信号として使うことができます。ビット23( $\overline{EOC}$ )はSCKの最初の立上りエッジで捕捉することができます。ビット22はSCKの最初の立下りエッジでシフトされてデバイスから出力されます。最後のデータ・ビット(ビット0)は23番目のSCKの立下りエッジでシフトされて出力され、24番目のSCKパルスの立上りエッジでラッチすることができます。24番目のSCKパルスの立下りエッジでSDOは“H”になり、新しい変換サイクルの開始を示します。このビットは次の変換サイクルの $\overline{EOC}$ (ビット22)として機能します。出力データのフォーマットが表2にまとめています。

IN<sup>+</sup>ピンとIN<sup>-</sup>ピンの電圧が $-0.3V \sim (V_{CC}+0.3V)$ の絶対最大動作範囲に留まる限り、 $-FS = -0.5 \cdot V_{REF}$ から $+FS = 0.5 \cdot V_{REF}$ までの任意の差動入力電圧 $V_{IN}$ に対して変換結果が生成されます。

図3. 出力データのタイミング

表2. LTC2430/LTC2431の出力データのフォーマット

| Differential Input Voltage<br>$V_{IN}^*$ | Bit 23<br>EOC | Bit 22<br>DMY | Bit 21<br>SIG | Bit 20<br>MSB | Bit 19 | Bit 18 | Bit 17 | ... | Bit 0<br>LSB |

|------------------------------------------|---------------|---------------|---------------|---------------|--------|--------|--------|-----|--------------|

| $V_{IN}^* \geq 0.5 \cdot V_{REF}^{**}$   | 0             | 0             | 1             | 1             | 0      | 0      | 0      | ... | 0            |

| $0.5 \cdot V_{REF}^{**} - 1LSB$          | 0             | 0             | 1             | 0             | 1      | 1      | 1      | ... | 1            |

| $0.25 \cdot V_{REF}^{**}$                | 0             | 0             | 1             | 0             | 1      | 0      | 0      | ... | 0            |

| $0.25 \cdot V_{REF}^{**} - 1LSB$         | 0             | 0             | 1             | 0             | 0      | 1      | 1      | ... | 1            |

| 0                                        | 0             | 0             | 1             | 0             | 0      | 0      | 0      | ... | 0            |

| -1LSB                                    | 0             | 0             | 0             | 1             | 1      | 1      | 1      | ... | 1            |

| $-0.25 \cdot V_{REF}^{**}$               | 0             | 0             | 0             | 1             | 1      | 0      | 0      | ... | 0            |

| $-0.25 \cdot V_{REF}^{**} - 1LSB$        | 0             | 0             | 0             | 1             | 0      | 1      | 1      | ... | 1            |

| $-0.5 \cdot V_{REF}^{**}$                | 0             | 0             | 0             | 1             | 0      | 0      | 0      | ... | 0            |

| $V_{IN}^* < -0.5 \cdot V_{REF}^{**}$     | 0             | 0             | 0             | 0             | 1      | 1      | 1      | ... | 1            |

\*差動入力電圧 $V_{IN} = IN^+ - IN^-$ 。

\*\*差動リファレンス電圧 $V_{REF} = REF^+ - REF^-$ 。

## アプリケーション情報

+FSを超える差動入力電圧の場合、変換結果は+FS+1 LSBに相当する値にクランプされます。-FSより低い差動入力電圧の場合、変換結果は-FS-1 LSBに相当する値にクランプされます。

### 周波数除去の選択 ( $F_O$ )

LTC2430/LTC2431の内部発振器は50Hz±2%または60Hz±2%のライン周波数およびその高調波での通常モードの除去が110dBより優れています。60Hz除去では $F_O$ ピンをGNDに接続し、50Hz除去では $F_O$ ピンをV<sub>CC</sub>に接続します。

50Hz除去または60Hz除去の選択は $F_O$ を適切なロジック・レベルにドライブすることによっても行うことができます。スリープ・ステートまたはデータ出力ステートの間の選択の変更がコンバータの動作を乱すことはありません。変換ステートの間に選択が行われると、進行中の変換結果は仕様から外れることがあります。それに続く変換は影響を受けません。

50Hzまたは60Hzと異なる基本除去周波数が要求される場合、またはコンバータを外部ソースに同期させる必要がある場合、外部の変換クロックを使ってLTC2430またはLTC2431を動作させることができます。コンバータは $F_O$ ピンに外部クロック信号が与えられていることを自動的に検知し、内部発振器をオフします。外部信号が検出されるには、その周波数 $f_{EOSC}$ は少なくとも5kHzあることが必要です。外部クロック信号のデューティ・サイクルは、“H”と“L”的期間( $t_{H0}$ と $t_{L0}$ )の最小と最大の規定値が守られる限り重要ではありません。

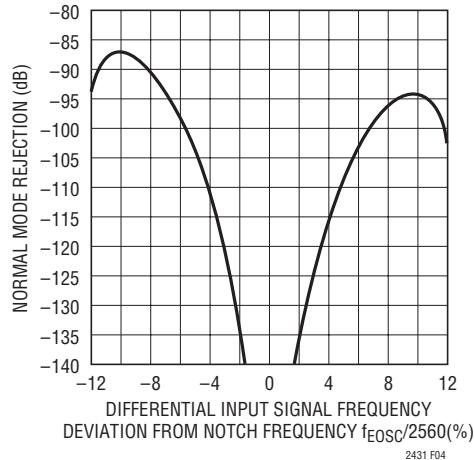

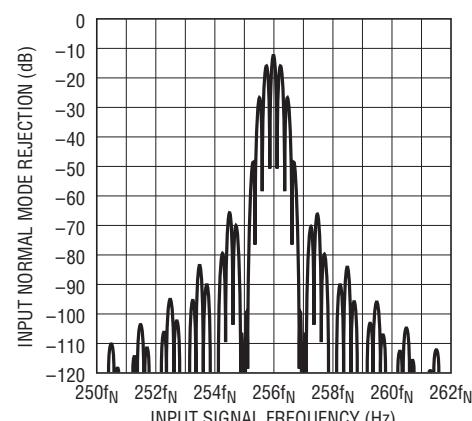

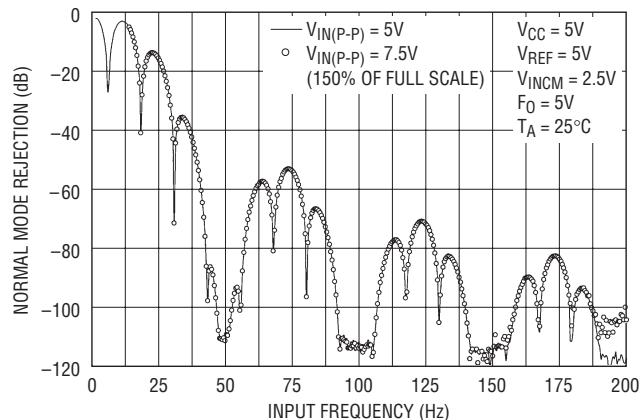

周波数が $f_{EOSC}$ の外部変換クロックを使って動作しているとき、 $f_{EOSC}/2560\pm4\%$ の周波数範囲およびその高調波に対し、LTC2430またはLTC2431は110dBを超える通常モードの除去率を与えます。 $f_{EOSC}/2560$ からの入力周波数の偏差の関数としての通常モードの除去率を図4に示します。

$F_O$ ピンに外部クロックが与えられていないとき、コンバータ(LTC2430/LTC2431)は内部発振器を自動的に起動して、「内部変換クロック」モードに入ります。コンバータが外部のシリアル・クロックを使っているとき、スリープ・ステートまたはデータ出力ステートの間に変換クロック・ソースが変更された場合、その動作は乱されません。

変換ステートの間に変更されると、進行中の変換結果は仕様から外れることがあります。それに続く変換は影響を受けません。データ出力ステートの間に変更が起き、コンバータが内

図4. 周波数が $f_{EOSC}$ の内部発振器使用時の

LTC2430/LTC2431の通常モードの除去率

部SCKモードだと、シリアル・クロックのデューティ・サイクルが影響を受けることがあります。シリアル・データ・ストリームは有効なままであります。

$F_O$ の関数としての各ステートの持続時間と実現可能な出力データ・レートを表3にまとめてあります。

### シリアル・インターフェース・ピン

LTC2430/LTC2431は、3線同期式インターフェースを介して、変換結果を伝送し、変換開始コマンドを受け取ります。変換中やスリープ状態では、このインターフェースを使ってコンバータの状態にアクセスすることができます。データの出力状態では、このインターフェースは変換結果を読み出すのに使います。

### シリアル・クロックの入力/出力(SCK)

SCKのシリアル・クロック信号はデータ転送の同期に使われます。データの各ビットはシリアル・クロックの立下りエッジでシフトされてSDOピンから出力されます。

内部SCKモード動作では、SCKピンは出力であり、コンバータ(LTC2430またはLTC2431)は内部変換クロックを8で割って、それ自身のシリアル・クロックを発生します。外部SCKモード動作では、SCKピンは入力として使われます。内部SCKモードまたは外部SCKモードは起動時に選択され、次いで、 $\overline{CS}$ ピンに“H”から“L”への遷移が検出されるたびに再度選択されます。

## アプリケーション情報

表3. LTC2430/LTC2431のステートの持続時間

| ステート  | 動作モード                           |                                                                             | 持続時間                                                                    |

|-------|---------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 変換    | 内部発振器                           | $F_0 = "L"$<br>(60Hzの除去)                                                    | 133ms、出力データ・レート $\leq 7.5$ の読み出し/s                                      |

|       |                                 | $F_0 = "H"$<br>(50Hzの除去)                                                    | 160ms、出力データ・レート $\leq 6.2$ の読み出し/s                                      |

|       | 外部発振器                           | $F_0 = \text{周波数が } f_{EOSC} \text{ kHzの外部発振器} (f_{EOSC}/2560 \text{ の除去})$ | $20510/f_{EOSC}$ 、出力データ・レート $\leq f_{EOSC}/20510$ 読み出し/s                |

| スリープ  |                                 |                                                                             | $\overline{CS} = "H"$ である間                                              |

| データ出力 | 内部シリアル・クロック                     | $F_0 = "L"/"H"$<br>(内部発振器)                                                  | $\overline{CS} = "L"$ である間、<br>ただし 1.25ms (24 SCK サイクル) は超えない           |

|       |                                 | $F_0 = \text{周波数が } f_{EOSC} \text{ kHzの外部発振器}$                             | $\overline{CS} = "L"$ である間、<br>ただし $192/f_{EOSC}ms$ (24 SCK サイクル) は超えない |

|       | 周波数が $f_{SCK}$ kHz の外部シリアル・クロック |                                                                             | $\overline{CS} = "L"$ である間、<br>ただし $24/f_{SCK}ms$ (24 SCK サイクル) は超えない   |

起動時またはこの遷移の間 SCK が “H” またはフロート状態ならば、コンバータは内部 SCK モードに入ります。起動時またはこの遷移の間 SCK が “L” ならば、コンバータは外部 SCK モードに入ります。

### シリアル・データ出力 (SDO)

シリアル・データ出力ピン SDO は、データ出力ステートの間に最後の変換の結果をシリアル・ビット・ストリームとして (MSB を最初に) 出力します。さらに、SDO ピンは変換ステートおよびスリープ・ステートの間、変換終了インジケータとして使われます。

$\overline{CS}$  が “H” のとき、SDO ドライバは高インピーダンス状態に切り替わります。これにより、シリアル・インターフェースを他のデバイスと共有することができます。変換ステートまたはスリープ・ステートのとき  $\overline{CS}$  が “L” ならば、SDO は EOC を出力します。変換時に  $\overline{CS}$  が “L” ならば、EOC ビットが SDO ピンに “H” として現われます。変換が完了すると、EOC は “L” に下がります。

### チップ・セレクト入力 ( $\overline{CS}$ )

アクティブ “L” のチップ・セレクト  $\overline{CS}$  は、変換ステートをテストし、前のセクションで説明されているように、データ出力の転送をイネーブルするのに使われます。

さらに、 $\overline{CS}$  信号を使って、シリアル・データ転送が完了する前に、新しい変換サイクルをトリガすることができます。コンバータ (LTC2430 または LTC2431) は、コンバータがデータ出力ステートに入った後 (つまり、 $\overline{CS} = "L"$  で SCK の 1 番目の立上り

エッジが生じた後)  $\overline{CS}$  ピンの “L” から “H” への遷移が検出されるといつでも、進行中のシリアル・データ転送を中止して新しい変換サイクルを開始します。

最後に、 $\overline{CS}$  を使って自走モードの動作を制御することができます (「シリアル・インターフェースのタイミング・モード」のセクションを参照)。 $\overline{CS}$  を接地すると、ADC は  $F_0$  で選択された最大出力レートで連続して変換を行うように強制されます。

### シリアル・インターフェースのタイミング・モード

LTC2430/LTC2431 の 3 線インターフェースは SPI および MICROWIRE と互換性があります。このインターフェースにより、いくつかの動作モードを柔軟に実現できます。これらには内部/外部シリアル・クロック、2 線または 3 線の I/O、シングル・サイクル変換が含まれます。以下のセクションではこれらのシリアル・インターフェースのそれぞれのタイミング・モードを詳細に説明します。これら全ての場合に、コンバータは内部発振器 ( $F_0 = "L"$  または  $F_0 = "H"$ ) または  $F_0$  ピンに接続された外部発振器を使うことができます。表 4 にまとめられていますので参照してください。

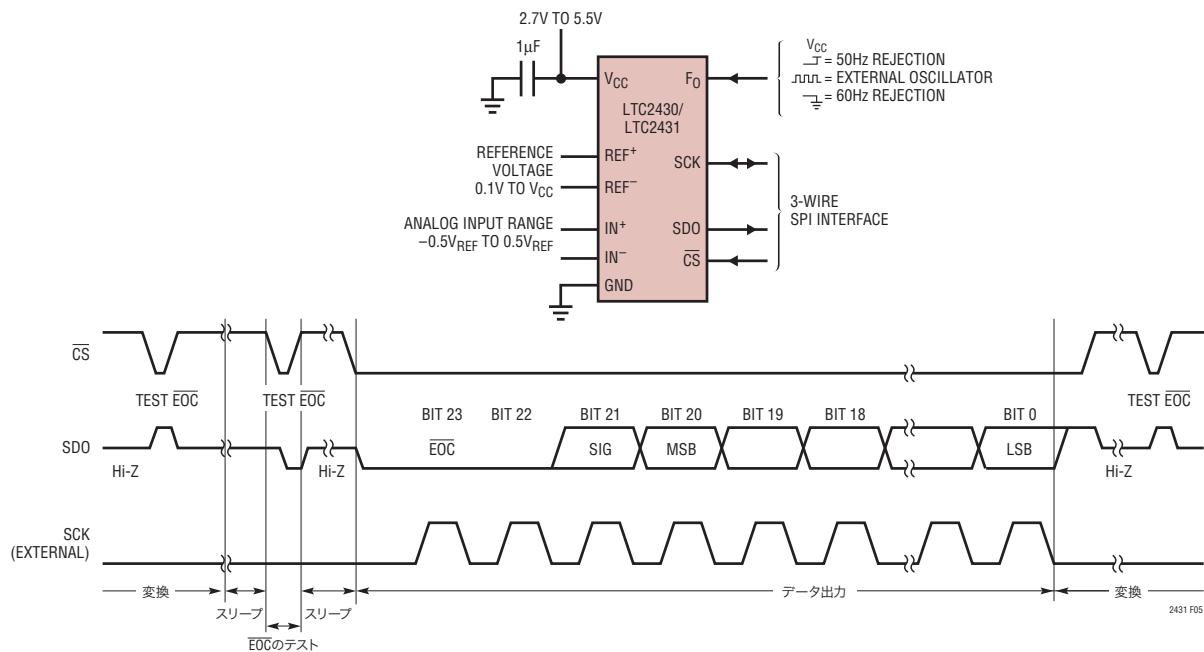

### 外部シリアル・クロック、シングル・サイクル動作 (SPI/MICROWIRE と互換)

このタイミング・モードでは、外部シリアル・クロックを使って変換結果をシフトして出力し、 $\overline{CS}$  信号を使って変換サイクルの状態をモニタして制御します (図 5 を参照)。

# LTC2430/LTC2431

## アプリケーション情報

表4. LTC2430/LTC2431のインターフェースのタイミング・モード

| 構成設定              | SCK<br>信号源 | 変換サイクルの<br>制御              | データ出力<br>制御                | 接続と波形 |

|-------------------|------------|----------------------------|----------------------------|-------|

| 外部SCK、シングル・サイクル変換 | 外部         | $\overline{CS}$ およびSCK     | $\overline{CS}$ およびSCK     | 図5、図6 |

| 外部SCK、2線式I/O      | 外部         | SCK                        | SCK                        | 図7    |

| 内部SCK、シングル・サイクル変換 | 内部         | $\overline{CS} \downarrow$ | $\overline{CS} \downarrow$ | 図8、図9 |

| 内部SCK、2線式I/O、連続変換 | 内部         | 連続                         | 内部                         | 図10   |

図5. 外部シリアル・クロック、シングル・サイクル動作

シリアル・クロック・モードは $\overline{CS}$ の立下りエッジで選択されます。外部シリアル・クロック・モードを選択するには、 $\overline{CS}$ の各立下りエッジの間シリアル・クロック・ピン (SCK) を“L”にする必要があります。

シリアル・データ出力ピン (SDO) は、 $\overline{CS}$ が“H”的間は高インピーダンスになります。変換サイクル中はいつでも、コンバータの状態をモニタするために $\overline{CS}$ を“L”に引き下げるることができます。 $\overline{CS}$ が“L”に引き下げられている間、 $\overline{EOC}$ がSDOピンに出力されます。変換中は $\overline{EOC} = 1$ となり、変換が終了すると $\overline{EOC} = 0$ となります。 $\overline{CS}$ が“H”的場合、変換が完了するとデバイスは自動的に省電力のスリープ・ステートに入ります。

$\overline{CS}$ が“L”的ときは、デバイスはデータ出力モードに入れます。 $\overline{CS}$ が“L”的間にSCKの最初の立上りエッジが現れるまで、結果は内部スタチック・シフトレジスタに保持されます。データはSCKの各立下りエッジでシフトされてSDOピンから出力されます。このため、外部回路はSCKの立上りエッジを使って出力

をラッチすることができます。 $\overline{EOC}$ はSCKの最初の立上りエッジを使ってラッチすることができ、変換結果の最後のビットはSCKの24番目の立上りエッジを使ってラッチすることができます。SCKの24番目の立下りエッジで、デバイスは新しい変換を開始します。SDOが“H”( $\overline{EOC} = 1$ )になり、変換中であることを示します。

データ・サイクルの完了時に $\overline{CS}$ を“L”的ままにしておき、 $\overline{EOC}$ を変換終了時の割り込み信号としてモニタすることができます。代わりに、 $\overline{CS}$ を“H”にドライブしてSDOをHi-Zに設定することができます。上述のように、変換状態をモニタするために、 $\overline{CS}$ をいつでも“L”に引き下げることができます。

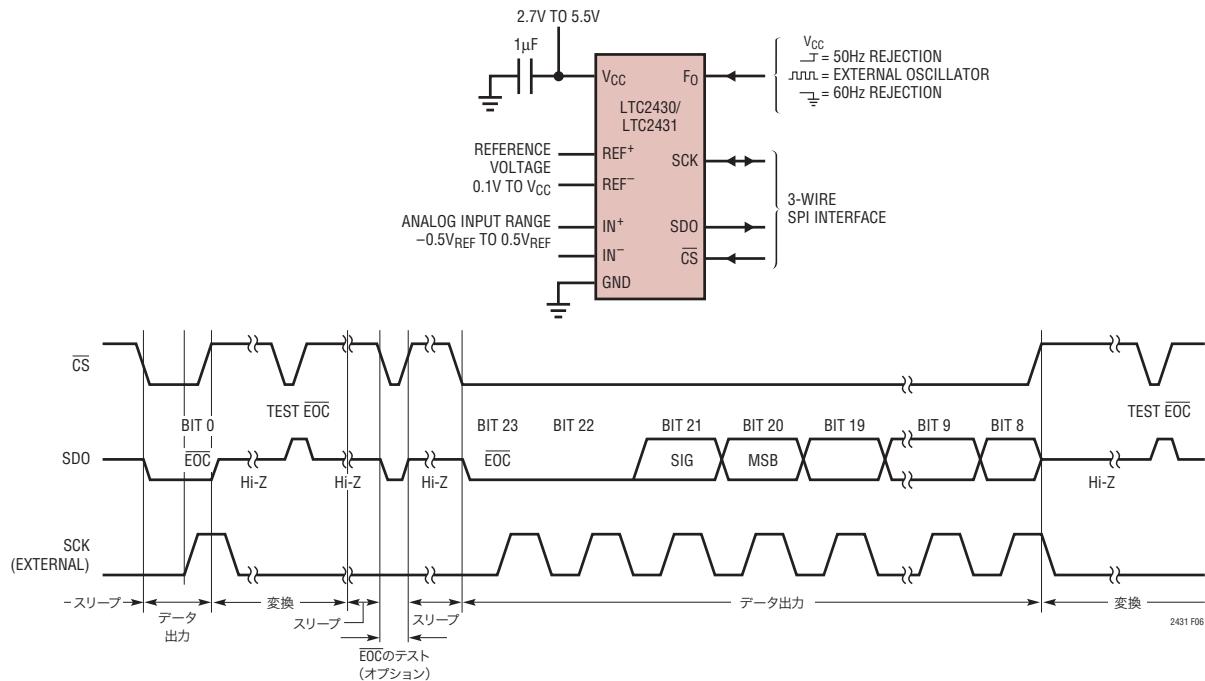

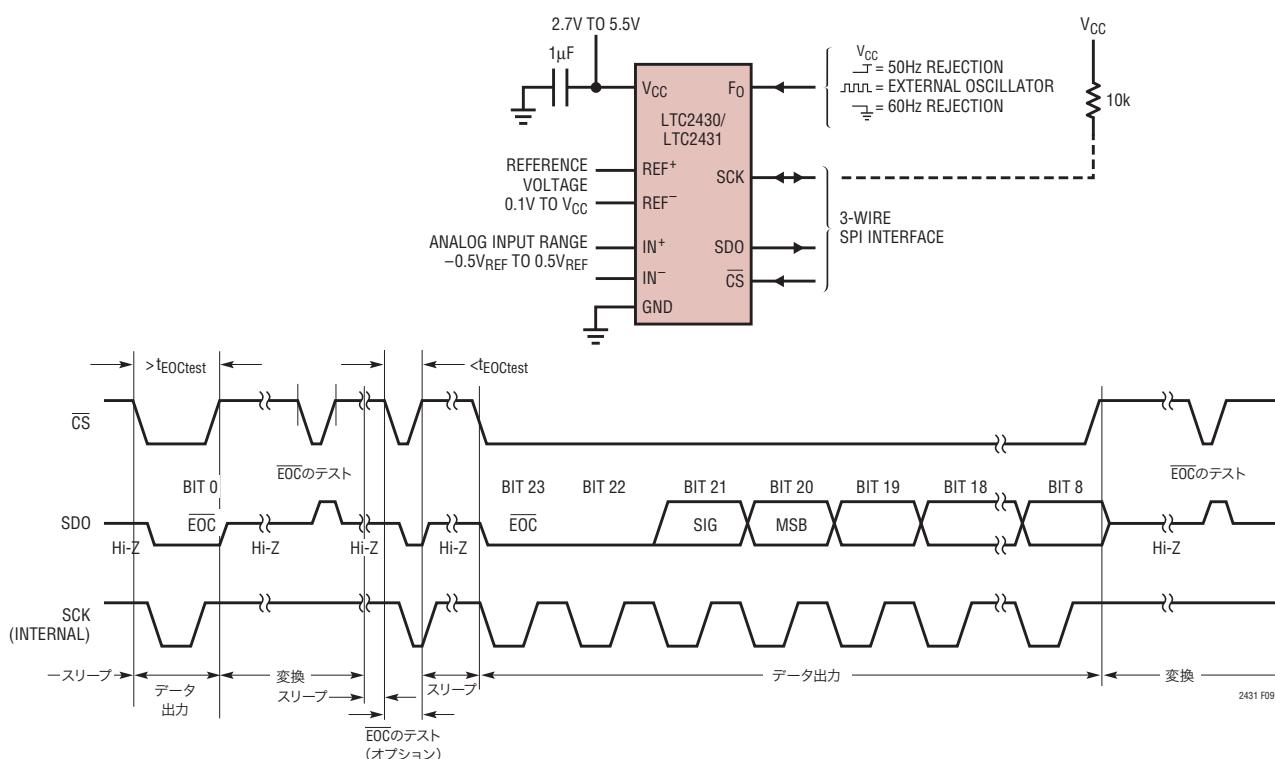

通常、 $\overline{CS}$ はデータ出力ステートの間“L”に保たれます。ただし、SCKの最初の立上りエッジと24番目の立下りエッジの間に、いつでも $\overline{CS}$ を“H”に引き上げてデータ出力ステートを中止することができます(図6を参照)。

## アプリケーション情報

図6. 外部シリアル・クロック、短縮されたデータ出力長

**CS**の立上りエッジでデバイスはデータ出力ステートを中止し、直ちに新しい変換を開始します。これは出力データの24ビット全ては必要としないシステムでは有用で、無効の変換サイクルを中止するか、変換の開始点を同期させます。

### 外部シリアル・クロック、2線式I/O

このタイミング・モードでは2線式シリアルI/Oインターフェースを利用します。変換結果は外部で作られたシリアル・クロック(SCK)信号によってシフトされてデバイスから出力されます(図7参照)。

外部シリアル・クロック・モードが起動時リセット(POR)サイクルの終りに選択されます。PORサイクルはV<sub>CC</sub>が3Vを超えてから約1ms後に終了します。この時点でSCKに与えられたレベルによってSCKが内部であるか外部であるかが決まります。外部シリアル・クロックのタイミング・モードに入るには、PORの終了前にSCKを”L”にドライブする必要があります。

**CS**が”L”に固定されているので、変換ステートおよびスリープ・ステートの間、変換終了(**EOC**)をSDOピンで連続してモニタすることができます。**EOC**は外部コントローラへの割込み信号として使うことができ、変換結果が用意できていることを示します。変換中は**EOC** = 1となり、変換が終了すると**EOC** =

0となります。**EOC**の立下りエッジで、変換結果が内部のスタチック・シフトレジスタにロードされます。データはSCKの各立下りエッジでシフトされてSDOピンから出力されるので、外部回路はSCKの立上りエッジでデータをラッチすることができます。**EOC**はSCKの最初の立上りエッジでラッチすることができます。SCKの24番目の立下りエッジで、SDOは”H”になります(**EOC** = 1)、新しい変換サイクルが開始されたことを示します。

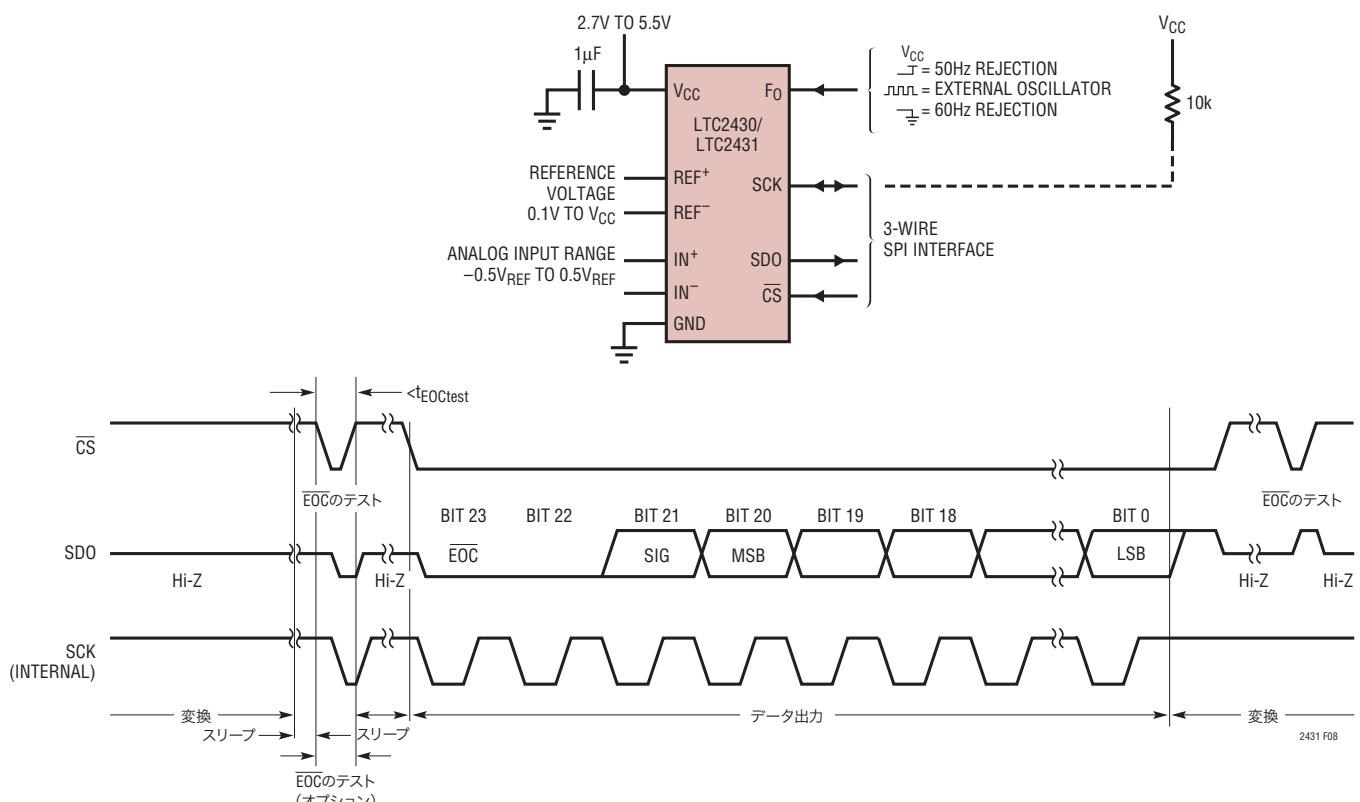

### 内部シリアル・クロック、シングル・サイクル動作

このタイミング・モードでは、内部シリアル・クロックを使って変換結果をシフトして出力し、**CS**信号を使って変換サイクルの状態をモニタして制御します(図8を参照)。

内部シリアル・クロック・タイミング・モードを選択するには、**CS**の立下りエッジより前にシリアル・クロック・ピン(SCK)をフロー(Hi-Z)にするか、または”H”に引き上げる必要があります。SCKが**CS**の立下りエッジで”L”にドライブされると、デバイスは内部シリアル・クロック・モードに入りません。内部の弱いプルアップ抵抗が**CS**の立下りエッジの間SCKピンに対して働くので、SCKが外部からドライブされないと内部シリアル・クロック・タイミング・モードが自動的に選択されます。

## LTC2430/LTC2431

## アプリケーション情報

図7. 外部シリアル・クロック、 $\overline{CS} = 0$ の動作

図8 内部シリアル・クロック、シングル・サイクル動作

## アプリケーション情報

シリアル・データ出力ピン(SDO)は、 $\overline{CS}$ が“H”的間は高インピーダンスになります。変換サイクル中はいつでも、コンバータの状態をモニタするために $\overline{CS}$ を“L”に引き下げることができます。 $\overline{CS}$ が“L”に引き下げられると、SCKが“L”になり、 $\overline{EOC}$ がSDOピンに出力されます。変換中は $EOC = 1$ となり、デバイスがスリープ・ステートに入ると $\overline{EOC} = 0$ となります。

$EOC$ をテストするとき、変換が完了していると( $EOC = 0$ )、 $CS$ が“L”的ままであればデバイスはスリープ・ステートから出て、データ出力ステートに入ります。デバイスが省電力スリープ・ステートに戻れるようにするには、SCKの最初の立上りエッジより前に $\overline{CS}$ を“H”に引き上げる必要があります。内部SCKタイミング・モードでは、SCKは“H”になり、デバイスは( $EOC = 0$ ならば) $CS$ の立下りエッジ後、 $t_{EOCtest}$ の時点でデータを出力し始め、( $EOC$ の立下りエッジで $CS$ が“L”ならば) $\overline{EOC}$ が“L”になった後、 $t_{EOCtest}$ の時点でデータを出力し始めます。デバイスが内部発振器を使用している場合、 $t_{EOCtest}$ の値は23μsです( $F_0$  = ロジック“L”または“H”)。周波数が $f_{EOSC}$ の外部発振器が $F_0$ をドライブしていると、 $t_{EOCtest}$ は3.6/ $f_{EOSC}$ となります。 $t_{EOCtest}$ の時点より前に $\overline{CS}$ が“H”に引き上げられると、デバイスはスリープ・ステートに戻ります。変換結果は内部のスタチック・シフト・レジスタに保存されます。

$\overline{CS}$ が $t_{EOCtest}$ より長く“L”に留まると、SCKの最初の立上りエッジが生じ、変換結果がシリアルにシフトされSDOピンから出力されます。データ出力サイクルはSCKのこの最初の立上りエッジで始まり、24番目の立上りエッジの後終了します。データはSCKの各立下りエッジでシフトされてSDOピンから出力されます。内部で作られたシリアル・クロックはSCKピンに出力されます。この信号を使って変換結果を外部回路にシフトすることができます。 $EOC$ はSCKの最初の立上りエッジを使ってラッチすることができます。変換結果の最後のビットはSCKの24番目の立上りエッジを使ってラッチすることができます。24番目の立上りエッジの後、SDOは“H”になり( $EOC = 1$ )、SCKは“H”的まま留まり、新しい変換が始まります。

通常、 $CS$ はデータ出力ステートの間“L”に保たれます。ただし、SCKの最初の立上りエッジと24番目の立上りエッジの間のいつでも $\overline{CS}$ を“H”に引き上げてデータ出力ステートを中止することができます(図9を参照)。これは24ビット出力データの全ては必要としないシステムでは有用で、無効の変換サイクルを中止したり、変換の開始点を同期させます。コンバータがSCKを“L”にドライブしている状態で $CS$ が“H”に引き上げられると、SCKをロジック“H”的状態に戻すのに内部プルアップが使えなくなります。

図9. 内部シリアル・クロック、短縮されたデータ出力長

24301f

# LTC2430/LTC2431

## アプリケーション情報

このため、デバイスは $\overline{CS}$ の次の立下りエッジで内部シリアル・クロック・モードから抜け出します。これは、外付けの10kプルアップ抵抗をSCKピンに追加するか、SCKが“L”的き決して $\overline{CS}$ を“H”に引き上げないようにして、避けることができます。

SCKが“L”的きはいつもLTC2430/LTC2431のSCKピンの内部プルアップはディスエーブルされます。通常、デバイスが内部SCKタイミング・モードだと、SCKは外部からドライブされません。ただし、特定のアプリケーションでは、SCKに外部ドライバが必要なことがあります。このドライバが“L”信号を出力した後Hi-Zになると、LTC2430/LTC2431の内部プルアップはディスエーブルされたままになります。したがって、SCKは“L”的きになります。 $\overline{CS}$ の次の立下りエッジで、デバイスは外部SCKタイミング・モードに切り替わります。10kプルアップ抵抗をSCKに外付けすると、このピンは外部ドライバがHi-Zになると“H”的きになります。 $\overline{CS}$ の次の立下りエッジで、デバイスは内部SCKタイミング・モードのまま留まります。

変換状態をテストするために $\overline{CS}$ を“H - L - H”とトグルするとき、スリープ・ステートで同様の状況が起きることがあります。デバイスがスリープ・ステート ( $\overline{EOC} = 0$ ) ならば、SCKは“L”的きになります。 $\overline{CS}$ が( $t_{EOCtest}$ として上で定義された時間内に)“H”的きになると、内部プルアップがアクティブになります。SCKピンに大きな容量性負荷があると、内部プルアップでは $\overline{CS}$ が再度“L”的きになる前にSCKを“H”レベルに戻すのに十分ではない

ことがあります。これは、 $\overline{CS}$ が $\overline{EOC} = 0$ を検出した後“L”的きに留まる通常の場合は問題ありません。この状況は10kプルアップ抵抗をSCKピンに外付けすることにより簡単に克服されます。

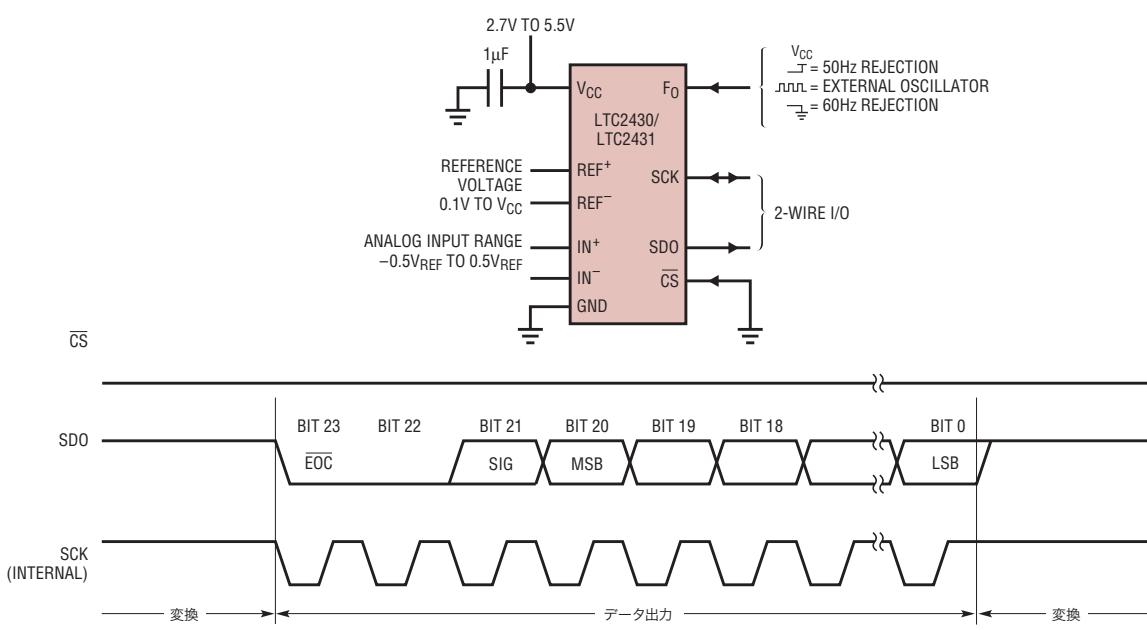

### 内部シリアル・クロック、2線式I/O、連続変換

このタイミング・モードでは2線とも出力の(SCKとSDO)インターフェースを使います。変換結果は内部で作られたシリアル・クロック(SCK)信号によってシフトされてデバイスから出力されます(図10を参照)。

内部シリアル・クロック・モードは起動時リセット(POR)サイクルの終りに選択されます。PORサイクルは $V_{CC}$ が2Vを超えてから約1ms後に終了します。内部の弱いプルアップはPORサイクルの間アクティブなので、SCKが外部で“L”的きにドライブされないと、内部シリアル・クロック・タイミング・モードが自動的に選択されます(内部プルアップがピンを“H”的きに引き上げられないほどSCKに負荷がかかっていると、外部SCKモードが選択されます)。

変換中、SCKとシリアル・データ出力ピン(SDO)は“H”的きになります( $\overline{EOC} = 1$ )。変換が完了すると、SCKとSDOは“L”的きになります( $\overline{EOC} = 0$ )、変換が終了してデバイスが省電力のスリープ・ステートに入ったことを示します。

図10. 内部シリアル・クロック、 $\overline{CS} = 0$  連続動作

24301f

## アプリケーション情報

デバイスは最小時間(内部SCKの周期の1/2)の間スリープ・ステートに留まってから、直ちにデータを出力し始めます。データ出力サイクルはSCKの最初の立上りエッジで始まり、24番目の立上りエッジの後に終了します。データはSCKの各立下りエッジでシフトされてSDOピンから出力されます。内部で作られたシリアル・クロックはSCKピンに出力されます。この信号を使って変換結果を外部回路にシフトすることができます。 $\overline{\text{EOC}}$ はSCKの最初の立上りエッジを使ってラッチすることができ、変換結果の最後のビットはSCKの24番目の立上りエッジを使ってラッチすることができます。24番目の立上りエッジの後、SDOは“H”になり( $\text{EOC} = 1$ )、新しい変換が進行中であることを示します。変換中、SCKは“H”的ままでです。

### コンバータの精度の維持

デバイスのデカップリング、PCBのレイアウト、アンチエイリアシング回路、ライン周波数の乱れなどの影響を変換結果ができるだけ受けないようにLTC2430/LTC2431は設計されています。にもかかわらず、このデバイスの並外れた精度を維持するには、いくつか配慮をしておくのが賢明です。

### デジタル信号レベル

LTC2430/LTC2431のデジタル・インターフェースは使うのが簡単です。そのデジタル入力( $\text{F}_0$ 、 $\text{CS}$ 、および外部SCKモード動作のSCK)は標準TTL/CMOSロジック・レベルを受け入れ、内部ヒステリシス・レシーバは100 $\mu\text{s}$ までの低速エッジ・レートを許容します。ただし、このコンバータの並外れた精度と低電源電流の利点を活かすには、いくらか配慮が必要です。

デジタル出力信号(SDOと内部SCKモード動作のSCK)は変換ステートの間一般にアクティブではないので、それほど心配いりません。

デジタル信号が0.5V～(V<sub>CC</sub>-0.5V)の範囲にある間は、CMOS入力レシーバに電源から追加電流が流れます。デジタル入力信号( $\text{F}_0$ 、 $\text{CS}$ 、および外部SCKモード動作のSCK)のどれかがこの範囲内のとき、問題の信号が有効なロジック・レベルであっても、LTC2430/LTC2431の電源電流が増加する可能性があることに注意してください。マイクロパワー動作では、全てのデジタル入力信号をフルCMOSレベル( $\text{V}_{IL} < 0.4\text{V}$ および $\text{V}_{OH} > (\text{V}_{CC}-0.4\text{V})$ )にドライブすることを推奨します。

変換周期の間、LTC2430/LTC2431のピンに接続されている高速デジタル信号のアンダーシュートやオーバーシュートがAD変換過程を大きく乱すことがあります。アンダーシュートとオーバーシュートは、外部制御信号の遷移時間がドライバからLTC2430/LTC2431までの伝播遅延の2倍より短いとき、コンバータのピンのところのインピーダンスの不整合によって生じることができます。参考までに、普通のFR-4基板の場合、信号の伝播速度は内部トレースで約183ps/インチ、表面トレースで170ps/インチです。したがって、1nsの最小遷移時間で制御信号を発生しているドライバは、2.5インチより短いトレースでコンバータに接続する必要があります。この問題は、共通制御ラインが使用され、多数の反射が起きる可能性があるとき特に困難になります。解決策は全ての伝送ラインをそれらの特性インピーダンスに近い値で注意深く終端することです。

LTC2430/LTC2431のピンの近くで並列終端するとこの問題が解決されますが、ドライバの電力消費が増加します。ドライバまたはLTC2431のピンの近くに27Ω～56Ωの直列抵抗を接続しても、追加の電力消費なしにこの問題が解決されます。実際の抵抗値はトレースのインピーダンスと接続トポロジーに依存します。

代わりの解決策は制御信号のエッジレートを下げることです。エッジを非常に遅くすると、遷移時間の間のコンバータの電源電流が増加することに注意が必要です。差動入力と差動リファレンスのアーキテクチャでは、グランド電流に対するコンバータの敏感さが大幅に減少します。

コンバータ(LTC2430またはLTC2431)を外部変換クロックで使用するとき、 $\text{F}_0$ 信号の接続には特に注意が必要です。このクロックは変換時間の間アクティブで、内部デジタル・フィルタが与える通常モードの除去率はこの周波数ではありません。コンバータのリファレンス端子のこの周波数の通常モード信号はDC利得とINL誤差を生じることがあります。コンバータの入力端子のこの周波数の通常モード信号はDCオフセット誤差を生じことがあります。このような乱れは、 $\text{F}_0$ 信号のトレースとコンバータの入力やリファレンスの接続トレースの間の非対称の容量性結合によって生じことがあります。直接的解決法は $\text{F}_0$ 信号のトレースと入力/リファレンス信号の間の間隔をできるだけ大きく保つことです。

# LTC2430/LTC2431

## アプリケーション情報

F<sub>O</sub>信号がコンバータの近くで並列に終端されていると、F<sub>O</sub>接続トレース、終端、およびグランド・リターン経路によって形成されるループにかなりのAC電流が流れます。したがって、コンバータの入力やリファレンスに乱された信号の誘導性結合を生じることがあります。このような状況では、ユーザーは差動入力とリファレンス接続のループ面積だけでなく、F<sub>O</sub>信号のループ面積も最小に抑える必要があります。

### 入力とリファレンスのドライブ

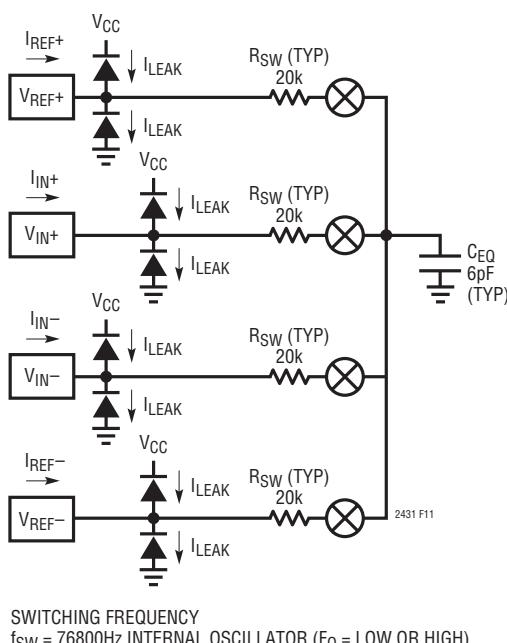

コンバータ(LTC2430またはLTC2431)の入力ピンとリファレンス・ピンはサンプリング・コンデンサのネットワークに直接接続されています。差動入力電圧と差動リファレンス電圧の関係に依存して、これらのコンデンサはこれらの4つのピンの間で切り替わり、その過程で少量の電荷を転送します。簡略等価回路を図11に示します。

簡単な近似法として、アナログ入力ピン (IN<sup>+</sup>、IN<sup>-</sup>、REF<sup>+</sup> またはREF<sup>-</sup>) をドライブしているソース・インピーダンスR<sub>S</sub>は (R<sub>SW</sub>およびC<sub>EQ</sub>(図11を参照)と一緒に) 時定数τ = (R<sub>S</sub> + R<sub>SW</sub>) • C<sub>EQ</sub>の1次受動ネットワークを形成していると考えることができます。コンバータは、サンプリング周期が入力回路の時定数τより少なくとも14倍大きいと、1ppmより高い精度で入力信号をサンプリングすることができます。4つのアナログ入力ピンのサンプリング過程は半分独立しているので、各時定数

は個別に考慮すべきで、最悪の状況では誤差が加算されることがあります。

内部発振器を使っているとき(F<sub>O</sub> = “L”または“H”)、LTC2430/LTC2431のフロントエンド・スイッチトキャパシタ・ネットワークは13μsのサンプリング周期に対応する76800Hzのクロックで駆動されます。したがって、セトリング誤差を1ppm未満にするには、τ ≤ 13μs/14 = 920nsとなるようにドライブ・ソースのインピーダンスを選択します。周波数がf<sub>EOSC</sub>の外部発振器を使うと、サンプリング周期は2/f<sub>EOSC</sub>で、1ppm未満のセトリング誤差の場合、τ ≤ 0.14/f<sub>EOSC</sub>です。

### 入力電流

入力が完全にセトリングすれば、変換結果は動的入力電流の影響を受けません。入力信号サンプリング過程が完全にセトリングしないと、利得誤差とオフセット誤差が生じることがありますが、コンバータのINL性能を劣化させることはありません。IN<sup>+</sup>ピンとIN<sup>-</sup>ピンを通じて流れる平均バイアス電流を、(64内部クロック・サイクルより長い)長時間にわたって積分したときのサンプリング電荷の移動の結果として表す式を図11に示します。

SWITCHING FREQUENCY

f<sub>SW</sub> = 76800Hz INTERNAL OSCILLATOR (F<sub>O</sub> = LOW OR HIGH)

f<sub>SW</sub> = 0.5 • f<sub>EOSC</sub> EXTERNAL OSCILLATOR

$$\begin{aligned} I_{(IN^+)}_{AVG} &= \frac{V_{IN} + V_{INCM} - V_{REFCM}}{0.5 \cdot R_{EQ}} \\ I_{(IN^-)}_{AVG} &= \frac{-V_{IN} + V_{INCM} - V_{REFCM}}{0.5 \cdot R_{EQ}} \\ I_{(REF^+)}_{AVG} &= \frac{1.5 \cdot V_{REF} - V_{INCM} + V_{REFCM}}{0.5 \cdot R_{EQ}} - \frac{V_{IN}^2}{V_{REF} \cdot R_{EQ}} \\ I_{(REF^-)}_{AVG} &= \frac{-1.5 \cdot V_{REF} - V_{INCM} + V_{REFCM}}{0.5 \cdot R_{EQ}} + \frac{V_{IN}^2}{V_{REF} \cdot R_{EQ}} \\ \text{WHERE} \\ V_{REF} &= REF^+ - REF^- \\ V_{REFCM} &= \left( \frac{REF^+ + REF^-}{2} \right) \\ V_{IN} &= IN^+ - IN^- \\ V_{INCM} &= \left( \frac{IN^+ - IN^-}{2} \right) \\ R_{EQ} &= 43.2M\Omega \text{ INTERNAL OSCILLATOR } 60Hz \text{ Notch } (F_O = \text{LOW}) \\ R_{EQ} &= 52.0M\Omega \text{ INTERNAL OSCILLATOR } 50Hz \text{ Notch } (F_O = \text{HIGH}) \\ R_{EQ} &= (6.66 \cdot 10^{12}) / f_{EOSC} \text{ EXTERNAL OSCILLATOR} \end{aligned}$$

図11. LTC2430/LTC2431の等価アナログ入力回路

24301f

## アプリケーション情報

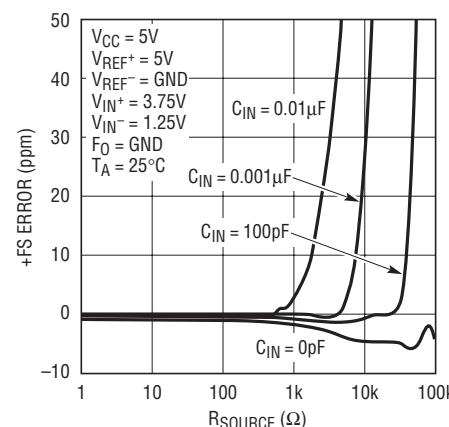

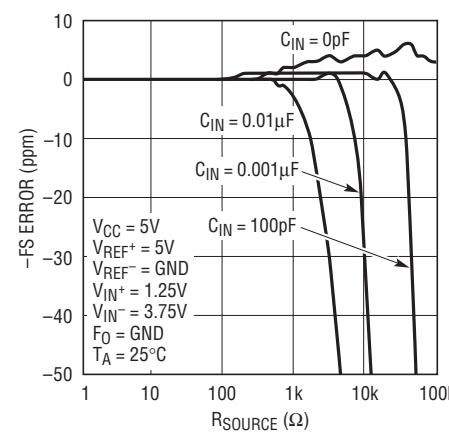

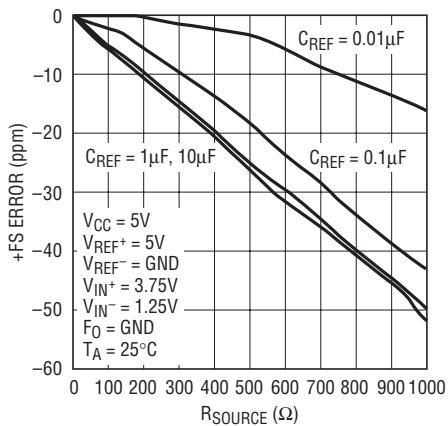

この入力の動的電流の効果は図12のテスト回路を使って解析することができます。C<sub>PAR</sub>コンデンサは、LTC2430/LTC2431のピン容量(標準5pF)と、図13および図14に示されている結果を得るのに使われたテスト装置の容量を含んでいます。注意深く実装すると、総入力容量(C<sub>IN</sub>+C<sub>PAR</sub>)を5pFに近づけることができ、図13と図14で予測される性能より良い性能を実現することができます。簡単のため、2つの異なった状況について検討することができます。

入力容量の値が比較的小さいと(C<sub>IN</sub> < 0.01μF)、サンプリング・コンデンサの電圧はほとんど完全にセトリングし、ソース・インピーダンスの値が比較的大きくても、小さな誤差が生じるだけです。C<sub>IN</sub>のこのような値はコンバータのオフセットと利得性能を悪くし、信号のフィルタ処理の大きな利点は得られないで避けた方が良いでしょう。それでも、入力のマルチプレクサ、ワイヤ、コネクタ、センサなどの寄生容量として小さな値のC<sub>IN</sub>を避けられないとき、LTC2430またはLTC2431は図13および図14に示されているように、比較的大きな値のソース抵抗で動作しながら、並外れた精度を維持することができます。これらの測定結果は前に示された1次近似とはわずかに異なることがあります。なぜなら、これらの測定結果には入力アンプの非線形セトリング過程とともに、実際の2次入力ネットワークの影響が含まれているからです。C<sub>IN</sub>の値が小さい場合、IN<sup>+</sup>とIN<sup>-</sup>はほとんど独立にセトリングしますので、2つのピンのソース・インピーダンスを整合させようと試みても、得るところはほとんどありません。

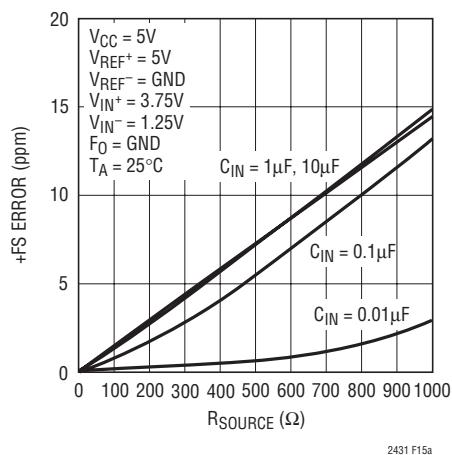

構成設定によっては、アンチエイリアシングや一般的な入力信号のフィルタ処理のために、もっと大きな値の入力コンデンサ(C<sub>IN</sub> > 0.01μF)が必要になることがあります。このようなコンデンサは入力サンプリング電荷を平均化するので、外部ソース抵抗からは擬似的に一定の入力差動インピーダンスに見えます。F<sub>O</sub> = “L”的とき(内部発振器と60Hzノッチ)、差動入力抵抗は標準21.6MΩであり、これにより、IN<sup>+</sup>またはIN<sup>-</sup>をドライブしているソース抵抗1Ωごとに0.023ppmの利得誤差が生じます。F<sub>O</sub> = “H”的とき(内部発振器と50Hzノッチ)、差動入力抵抗は標準26MΩであり、これにより、IN<sup>+</sup>またはIN<sup>-</sup>をドライブしているソース抵抗1Ωごとに0.019ppmの利得誤差が生じます。周波数がf<sub>EOSC</sub>の外部発振器によってF<sub>O</sub>がドライブされるとき(外部変換クロック動作)、差動入力抵抗は標準3.3 • 10<sup>12</sup>/f<sub>EOSC</sub>Ωであり、IN<sup>+</sup>またはIN<sup>-</sup>をドライブしているソース抵抗1Ωごとに1.15 • 10<sup>-6</sup> • f<sub>EOSC</sub>ppmの利得誤差を生じます。2つの入力ピンのソース抵抗の影響はこの利得誤差に関しては加算されます。

図12. IN<sup>+</sup>とIN<sup>-</sup>のRCネットワーク

図13. +FS誤差とIN<sup>+</sup>またはIN<sup>-</sup>のR<sub>SOURCE</sub>(小さなC<sub>IN</sub>)

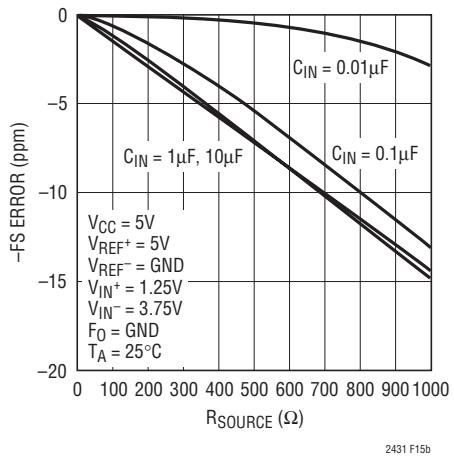

図14. -FS誤差とIN<sup>+</sup>またはIN<sup>-</sup>のR<sub>SOURCE</sub>(小さなC<sub>IN</sub>)

## アプリケーション情報

$C_{IN}$ の値が大きい場合の $IN^+$ と $IN^-$ から見たソース抵抗の和の関数としての標準的+FS誤差と-FS誤差を図15に示します。

この利得誤差に加えて、オフセット誤差の項も現れることがあります。オフセット誤差は2つの入力ピン $IN^+$ と $IN^-$ をドライブするソース・インピーダンスの間の不整合および入力同相電圧とリファレンス同相電圧の間の差に比例します。入力ドライブ回路のゼロではないソース・インピーダンスはコンバータの平均入力電流と一緒にになってINL性能を下げますが、入力信号の同相成分によるオフセット誤差の変調から間接的な歪みが生じることがあります。したがって、大きな値の $C_{IN}$ コンデンサを使う場合、 $IN^+$ ピンと $IN^-$ ピンから見たソース・インピーダンスを注意深く整合させることを推奨します。

図15a. +FS誤差と $IN^+$ または $IN^-$ の $R_{SOURCE}$ (大きな $C_{IN}$ )

図15b. -FS誤差と $IN^+$ または $IN^-$ の $R_{SOURCE}$ (大きな $C_{IN}$ )

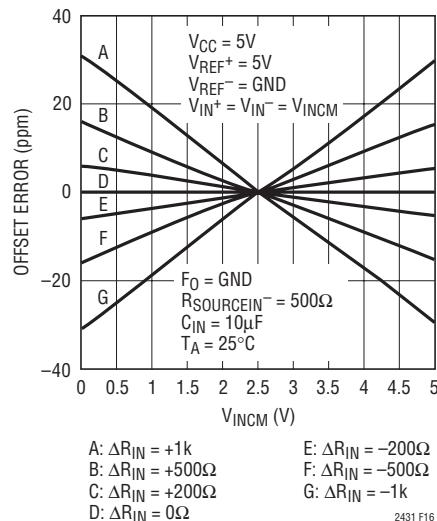

$F_0 = "L"$ のとき(内部発振器と60Hzノッチ)、ソース・インピーダンスの $1\Omega$ の不整合ごとにフルスケール同相入力信号が0.023ppmの差動入力信号に変換されます。 $F_0 = "H"$ のとき(内部発振器と50Hzノッチ)、ソース・インピーダンスの $1\Omega$ の不整合ごとにフルスケール同相入力信号が $\pm 0.019ppm$ の差動入力信号に変換されます。周波数が $f_{EOSC}$ の外部発振器によって $F_0$ がドライブされるとき、ソース・インピーダンスの $1\Omega$ の不整合ごとにフルスケール同相入力信号が $0.15 \cdot 10^{-6} \cdot f_{EOSC} ppm$ の差動入力信号に変換されます。大きな値の $C_{IN}$ が使われるときの、 $IN^+$ ピンと $IN^-$ ピンの間の様々な値のソース抵抗の不平衡の入力同相電圧による標準的オフセット誤差を図16に示します。

可能なら、対称ブリッジのレシオメトリックな測定の場合そうであるように、リファレンス信号の同相電圧に非常に近い入力信号の同相電圧で動作させるのが望ましいといえます。この構成設定はソース・インピーダンスの不整合によって生じるオフセット誤差を除去します。

ダイナミック入力電流の大きさは非常に安定した内部サンプリング・コンデンサのサイズとコンバータのサンプリング・クロックの精度に依存します。全温度範囲と電源範囲で、内部クロックの精度は標準で1%より良くなります。

図16. 値の大きな $C_{IN}$ の場合の( $C_{IN} \geq 1\mu F$ )オフセット誤差と同相電圧( $V_{INCM} = V_{IN^+} = V_{IN^-}$ )および入力ソース抵抗の不平衡( $\Delta R_{IN} = R_{SOURCEIN^+} - R_{SOURCEIN^-}$ )

## アプリケーション情報

この仕様は外部クロックでも簡単に実現できます。比較的安定した(50ppm/ $^{\circ}\text{C}$ )抵抗が $\text{IN}^+$ と $\text{IN}^-$ から見た外部ソース・インピーダンスに使われると、ダイナミック電流の予想ドリフト、オフセットおよび利得誤差は無視できるほど小さくなります(全温度範囲と電圧範囲でそれぞれの値の約1%)。要求の非常に厳しいアプリケーションであっても、一度較正しておけば十分でしょう。

入力サンプリング電荷に加えて、入力ESD保護ダイオードには温度に依存したリーク電流が流れます。公称1nA(最大 $\pm 10\text{nA}$ )のこの電流により、オフセットがわずかにシフトします。100 $\Omega$ のソース抵抗により、標準1 $\mu\text{V}$ 、最大10 $\mu\text{V}$ のオフセット電圧が生じます。

### リファレンス電流

同様に、LTC2430またはLTC2431は差動リファレンス・ピン $\text{REF}^+$ と $\text{REF}^-$ をサンプリングして、少量の電荷を外部のドライブ回路とやり取りしますので、ダイナミックなリファレンス電流が生じます。この電流はコンバータのオフセットは変化させませんが、利得とINL性能を下げることがあります。この電流の影響は同じ明確に区別される2つの状況で分析することができます。

外部リファレンス・コンデンサの値が比較的小さいと( $C_{\text{REF}} < 0.01\mu\text{F}$ )、サンプリング・コンデンサの電圧はほとんど完全にセトリングし、ソース・インピーダンスの値が比較的大きくても、小さな誤差が生じるだけです。 $C_{\text{REF}}$ のこのような値はコンバータのオフセットと利得性能を悪くし、リファレンスのフィルタの大きな利点は得られないので避けた方が良いでしょう。

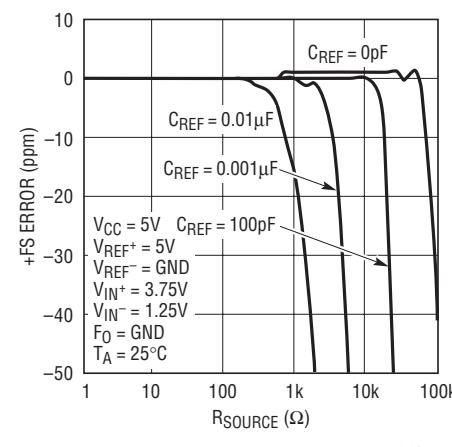

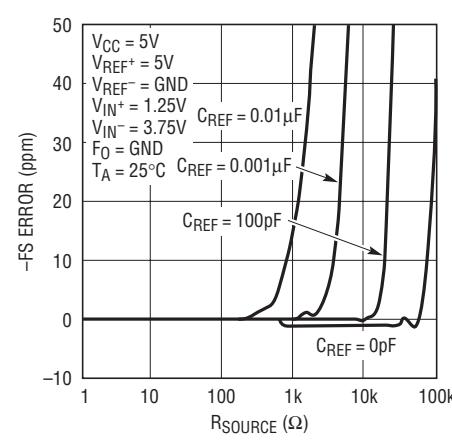

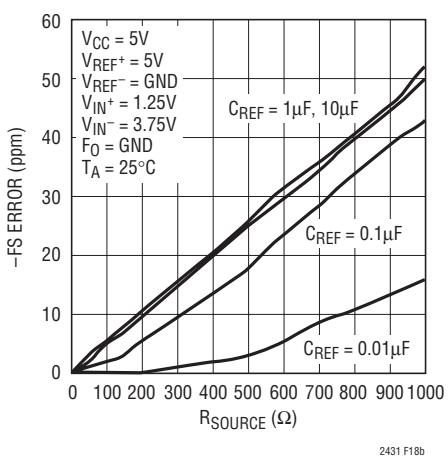

特定の構成ではリファレンス・フィルタとして、もっと大きな値( $C_{\text{REF}} > 0.01\mu\text{F}$ )のリファレンス・コンデンサが必要になることがあります。このようなコンデンサはリファレンス・サンプリング電荷を平均化するので、外部ソース抵抗は擬似的に一定のリファレンス差動インピーダンスを見ることになります。 $F_O = \text{"L"}$ のとき(内部発振器と60Hzノッチ)、差動リファレンス抵抗は標準15.6M $\Omega$ であり、これにより、 $\text{REF}^+$ または $\text{REF}^-$ をドライブしているソース抵抗1 $\Omega$ ごとに0.032ppmの利得誤差が生じます。 $F_O = \text{"H"}$ のとき(内部発振器と50Hzノッチ)、差動リファレンス抵抗は標準18.7M $\Omega$ であり、これにより、 $\text{REF}^+$ または $\text{REF}^-$ をドライブしているソース抵抗1 $\Omega$ ごとに0.027ppmの利得誤差が生じます。周波数が $f_{\text{EOSC}}$ の外部発振器によって $F_O$ がドライブされるとき(外部変換クロック動作)、標準的差動リファレンス抵抗は $2.4 \cdot 10^{12}/f_{\text{EOSC}}\Omega$ であり、 $\text{REF}^+$

または $\text{REF}^-$ をドライブしているソース抵抗1 $\Omega$ ごとに0.206 $\cdot 10^{-6} \cdot f_{\text{EOSC}}\text{ppm}$ の利得誤差を生じます。2つのリファレンス・ピンのソース抵抗の影響はこの利得誤差に関しては加算されます。 $\text{REF}^+$ ピンと $\text{REF}^-$ ピンから見たソース抵抗とこれらのピンに接続された外部容量 $C_{\text{REF}}$ の様々な組合せに対する標準的FS誤差を図17と図18に示します。標準的-FS誤差は極性を反対にした+FS誤差に似ています。

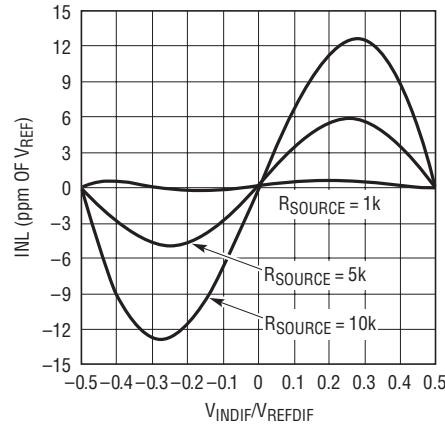

この利得誤差に加えて、コンバータのINL性能はリファレンスのソース・インピーダンスによって低下します。 $F_O = \text{"L"}$ のとき(内部発振器と60Hzノッチ)、 $\text{REF}^+$ または $\text{REF}^-$ をドライブするソース抵抗100 $\Omega$ ごとに約0.11ppmのINL誤差が追加されます。

図17a. +FS誤差と $\text{REF}^+$ または $\text{REF}^-$ の $R_{\text{SOURCE}}$ (小さな $C_{\text{IN}}$ )

図17b. -FS誤差と $\text{REF}^+$ または $\text{REF}^-$ の $R_{\text{SOURCE}}$ (小さな $C_{\text{IN}}$ )

# LTC2430/LTC2431

## アプリケーション情報

図18a. +FS誤差とREF<sup>+</sup>またはREF<sup>-</sup>のR<sub>SOURCE</sub>(大きなC<sub>REF</sub>)

図18b. -FS誤差とREF<sup>+</sup>またはREF<sup>-</sup>のR<sub>SOURCE</sub>(大きなC<sub>REF</sub>)

$F_O = "H"$ のとき(内部発振器と50Hzノッチ)、REF<sup>+</sup>またはREF<sup>-</sup>をドライブするソース抵抗100Ωごとに約0.092ppmのINL誤差が追加されます。周波数が $f_{EOSC}$ の外部発振器によって $F_O$ がドライブされるとき、REF<sup>+</sup>ピンまたはREF<sup>-</sup>ピンをドライブしているソース抵抗の100Ωごとに約 $0.73 \cdot 10^{-6} \cdot f_{EOSC}$ ppmのINL誤差が追加されます。大きなC<sub>REF</sub>値が使われるとREF<sup>+</sup>ピンまたはREF<sup>-</sup>ピンをドライブしているソース抵抗によって生じる標準的INL誤差を図19に示します。2つのリファレンス・ピンのソース抵抗の影響はこのINL誤差に関しては加算されます。一般に、REF<sup>+</sup>ピンとREF<sup>-</sup>ピンのソース・インピーダンスの整合は利得やINL誤差には役立ちません。

$V_{CC} = 5V$

$F_O = GND$

$C_{REF} = 10\mu F$

$V_{REF^+} = 5V$

$V_{REF^-} = GND$

$T_A = 25^\circ C$

$V_{INCM} = 0.5(V_{IN^+} + V_{IN^-}) = 2.5V$

図19. 値の大きなC<sub>REF</sub>の場合(C<sub>REF</sub> ≥ 1μF)のINLと

差動入力電圧(V<sub>IN</sub> = IN<sup>+</sup> - IN<sup>-</sup>)および

リファレンス・ソース抵抗(REF<sup>+</sup>とREF<sup>-</sup>のR<sub>SOURCE</sub>)

したがって、ユーザーがREF<sup>+</sup>ピンとREF<sup>-</sup>ピンをドライブするソース・インピーダンスを整合させることを試みるより、それらの和を最小にすることを推奨します。

ダイナミック・リファレンス電流の大きさは非常に安定した内部サンプリング・コンデンサのサイズとコンバータのサンプリング・クロックの精度に依存します。全温度範囲と電源範囲で、内部クロックの精度は標準で1%より良くなります。この仕様は外部クロックでも簡単に実現できます。比較的安定した(50ppm/°C)抵抗がREF<sup>+</sup>とREF<sup>-</sup>から見た外部ソース・インピーダンスに使われると、ダイナミック電流の利得誤差の予想ドリフトは無視できるほど小さくなります(全温度範囲と電圧範囲でその値の約1%)。要求の非常に厳しいアプリケーションであっても、一度較正しておけば十分でしょう。

入力サンプリング電荷に加えて、リファレンス・ピンのESD保護ダイオードには温度に依存したリーク電流が流れます。公称1nA(最大±10nA)のこのリーク電流により小さな利得誤差が生じます。100Ωのソース抵抗により、標準0.05μV、最大0.5μVのフルスケール誤差が生じます。

## アプリケーション情報

### 出力データ・レート

内部発振器を使っているとき、LTC2430/LTC2431は60Hz( $F_O = "L"$ )のノッチ周波数で1秒間に最高7.5回の読み出しを行うことができ、50Hz( $F_O = "H"$ )のノッチ周波数で1秒間に6.25回の読み出しを行うことができます。実際の出力データ・レートはスリープとデータ出力のフェーズの長さに依存しますが、これらはユーザーによって制御され、ほとんど無視できるほど短くすることができます。外部変換クロックを使って動作させると( $F_O$ を外部発振器に接続)、LTC2430/LTC2431の出力データ・レートを望むように増加させることができます。変換フェーズの持続時間は20510/f<sub>EOSC</sub>です。f<sub>EOSC</sub> = 153600Hzならば、コンバータは、まるで内部発振器が使われ、ノッチが60Hzに設定されているかのように動作します。これら2つの動作モードの間でLTC2430/LTC2431の性能に大きな差はありません。

f<sub>EOSC</sub>を公称153600Hzを超えて増加させると、最大出力データ・レートが比例して増加します。ただし、この大きな利点は3つの潜在的影響を伴いますので、それらについて注意深く検討する必要があります。

第一に、f<sub>EOSC</sub>が変化すると、内部のノッチの位置が比例して変化し、コンバータの電源ライン周波数の差動モード除去が減少します。多くのアプリケーションで、その結果生じる性能低下は、LTC2430/LTC2431の並外れた同相除去に依存することにより、また入力回路の同相モードから差動モードへの変換ソースを注意深く除去することにより、大きく減らすことができます。ユーザーはシングルエンド入力フィルタを避け、IN<sup>+</sup>ピンとIN<sup>-</sup>ピンをドライブする回路内で非常に高い整合性と対称性を維持すべきです。

第二に、クロック周波数の増加により、入力ピンとリファレンス・ピンを通って転送されるサンプリング電荷の量が比例して増加します。大きな外部入力コンデンサやリファレンス・コンデンサ(C<sub>IN</sub>, C<sub>REF</sub>)が使われる場合、f<sub>EOSC</sub>の任意の値でのコンバータの性能に対するソース抵抗の影響の評価のための式が前のセクションに与えられています。小さな外部入力コンデンサやリファレンス・コンデンサ(C<sub>IN</sub>, C<sub>REF</sub>)が使われる場合、LTC2430/LTC2431の標準的性能に対する外部ソース抵抗の影響を図13、図14および図17から推測することができます。これらの図で、横軸は153600/f<sub>EOSC</sub>で目盛られています。

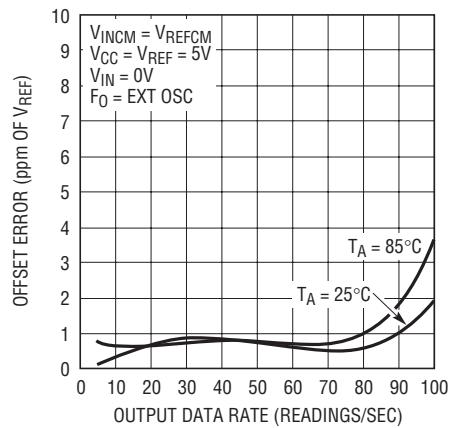

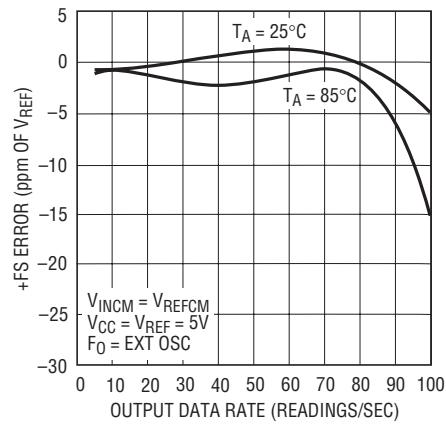

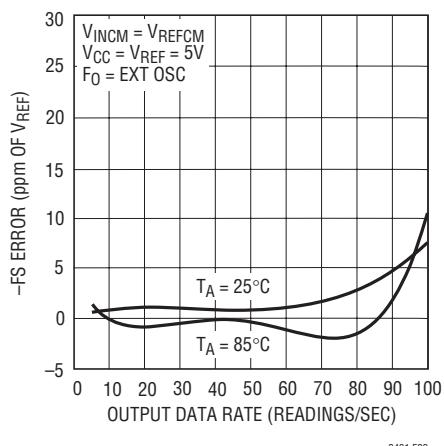

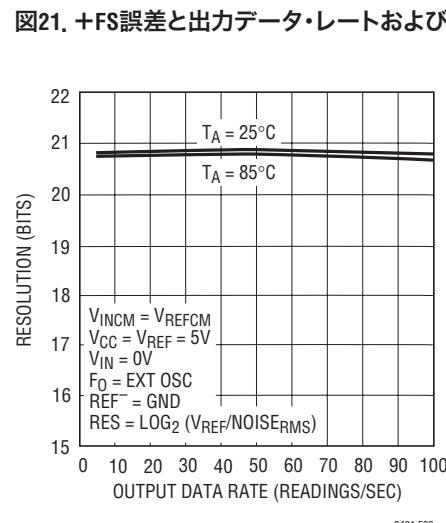

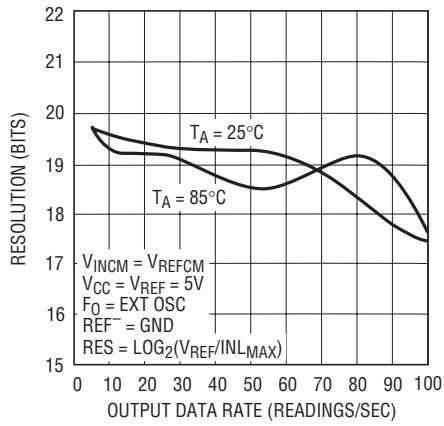

第三に、外部発振器の周波数が1.6MHzを超えて増加すると(10倍以上の出力データ・レートの増加)、内部の自動較正回路の効果が低下し始めます。このため、コンバータの精度と直線性が次第に低下します。1秒当たり最大100までの読み取りの出力データ・レートの標準的な測定性能曲線を図20～図27に示します。1秒当たり50の読み取りを超える出力データ・レートで、このコンバータで可能な最高レベルの精度を得るには、使用する電源電圧を最大にし、最高周囲動作温度を制限することを推奨します。「デジタル信号レベル」のセクションで説明したように、精度はクロック信号レベルとエッジ・レートにも敏感です。状況によっては、差動リファレンス電圧を下げた方が良いことがあります。

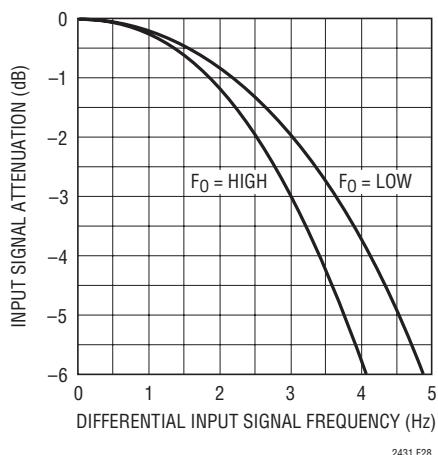

### 入力帯域幅

内部SINC<sup>4</sup>デジタル・フィルタとアナログおよびデジタルの自動較正回路を結合した効果により、LTC2430/LTC2431の入力帯域幅が決まります。内部発振器が使われると、LTC2430/LTC2431の3dB入力帯域幅は60Hzのノッチ周波数( $F_O = "L"$ )では3.63Hz、50Hzのノッチ周波数( $F_O = "H"$ )では3.02Hzです。周波数がf<sub>EOSC</sub>の外部変換クロック発生器をF<sub>O</sub>ピンに接続すると、3dB入力帯域幅は $2.36 \cdot 10^{-5} \cdot f_{EOSC}$ になります。

複雑なフィルタリングと較正アルゴリズムが利用されているため、コンバータの入力帯域幅はポールが3dB周波数に位置する1次フィルタではありません正確にモデル化できません。内部発振器が使われる場合のLTC2430/LTC2431の入力帯域幅の形を図28に示します。周波数がf<sub>EOSC</sub>の外部発振器が使われる場合のLTC2430/LTC2431の入力帯域幅の形は、図28のLTC2411のF<sub>O</sub> = "L"の曲線から得ることができます。この図の横軸はf<sub>EOSC</sub>/153600で目盛られています。

変換ノイズ(V<sub>REF</sub> = 5Vでは標準2.8μV<sub>RMS</sub>)は、ノイズの無いコンバータの入力に接続された白色ノイズ源によってモデル化することができます。

# LTC2430/LTC2431

## アプリケーション情報

2431 F20

2431 F21

図20. オフセット誤差と出力データ・レートおよび温度

2431 F22

図22. -FS誤差と出力データ・レートおよび温度

2431 F23

図23. 分解能(RMS雑音  $\leq 1\text{LSB}$ )と出力データ・レートおよび温度

2430 F24

図24. 分解能( $\text{INL}_{\text{RMS}} \leq 1\text{LSB}$ )と出力データ・レートおよび温度

2431 F25

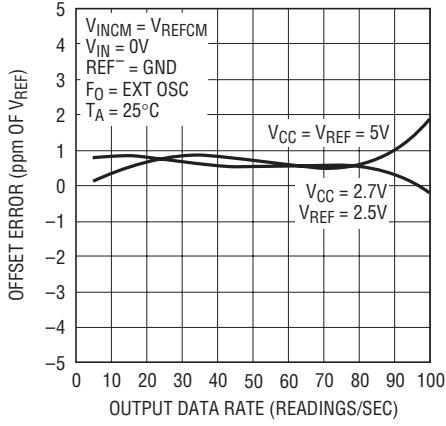

図25. オフセット誤差と出力データ・レートおよび $V_{CC}$

## アプリケーション情報

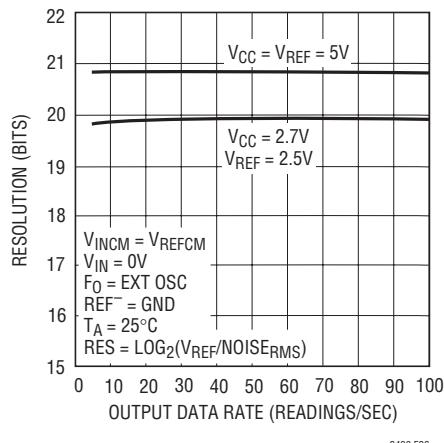

図26. 分解能(RMS雑音  $\leq$  1 LSB)と

出力データ・レートおよび $V_{CC}$

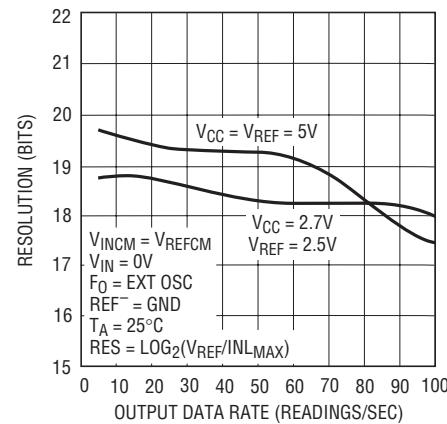

図27. 分解能( $INL_{MAX} \leq 1$  LSB)と

出力データ・レートおよび $V_{CC}$

図28. 内部発振器を使ったときの入力信号の帯域幅

帯域幅が無限のノイズ源のノイズ・スペクトル密度は  $67nV\sqrt{Hz}$ 、0.5MHzの単一ポールのノイズ源では  $216nV\sqrt{Hz}$  です。これらの数字から、外部増幅回路の設計には特に注意する必要があることは明らかです。このような回路は、出力を基準にしたノイズを減らすための非常に低い帯域幅(わずか数Hz)と、入力のスイッチトキャパシタ・ネットワークをドライブするのに必要な比較的高い帯域幅(少なくとも500kHz)の両方の必要条件に直面します。可能な解決法は、高利得で低帯域幅のアンプ段の後ろに高帯域幅のユニティゲインのバッファを置くことです。

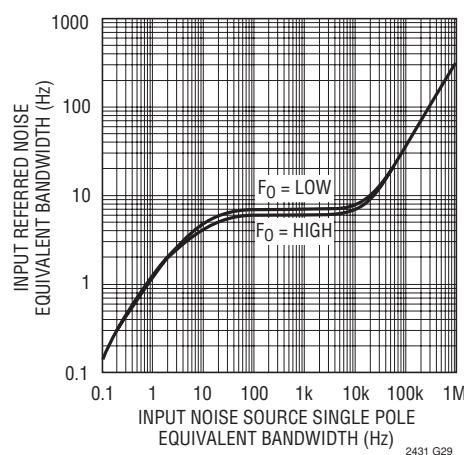

外部のアンプがLTC2430/LTC2431をドライブする場合、ADCの入力を基準にしたシステム・ノイズの計算は、図29を使うと簡単になります。LTC2430/LTC2431の入力ピンをドライブしているアンプのノイズは帯域を制限されたホワイトノイズ源としてモデル化することができます。

図29. 入力を基準にしたノイズに等価な、

入力に接続されたホワイトノイズ源の帯域幅

その帯域幅はコーナー周波数が $f_i$ の単一ポール・ローパス・フィルタの帯域幅によって近似することができます。アンプのノイズ・スペクトル密度は $n_i$ です。図29から、x軸の値の選択に $f_i$ を使って、入力をドライブしているアンプのノイズに相当する帯域幅 $freq_i$ をy軸上に見つけることができます。この帯域幅には、ADCの内部較正とフィルタリングの帯域制限効果が含まれています。これらの効果を含む、コンバータの入力を基準にしたドライビング・アンプのノイズは、 $N = n_i \cdot \sqrt{freq_i}$ として計算することができます。このように、(LTC2430/LTC2431の入力を基準にした)全システム・ノイズは、ADCの入力を基準にする3つのノイズ源(LTC2430/LTC2431の内部ノイズ( $2.8\mu V$ )、IN<sup>+</sup>をドライブするアンプのノイズ、IN<sup>-</sup>をドライブするアンプのノイズ)を2乗の和の平方根として合計することにより求めることができます。

## アプリケーション情報

周波数が $f_{EOSC}$ の外部発振器で $F_O$ ピンをドライブする場合、 $x$ 軸が $f_{EOSC}/153600$ で目盛られていれば、ノイズの計算に図29をそのまま使うことができます。 $f_{EOSC}/153600$ の比の値が大きくなると、図29の曲線の精度が低下し始めますが、同時に、LTC2430/LTC2431のノイズフロアが上がる所以、ドライブするアンプのノイズの寄与分が重要ではなくなります。

### 通常モードの除去率とアンチエイリアシング

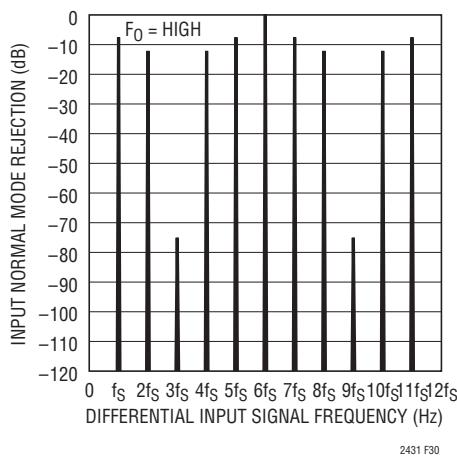

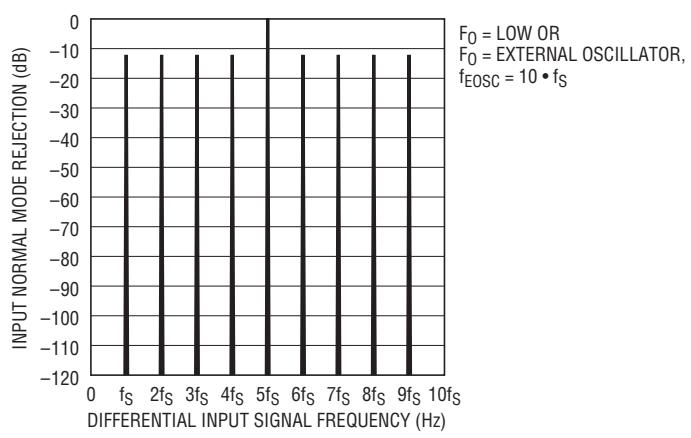

従来のADCに比べたデルタシグマADCの利点の1つは、デバイスに内蔵されたデジタル・フィルタです。大きなオーバーサンプリング率と組み合わせることにより、LTC2430/LTC2431はアンチエイリアシング・フィルタの必要条件を大幅に簡素化します。

SINC<sup>4</sup>デジタル・フィルタにより、DCと変調器のサンプリング周波数( $f_S$ )の整数倍を除く全ての周波数で通常モードの除去が120dBを超えます。LTC2430/LTC2431の自動較正回路は、アナログとデジタルの両方の領域での追加の通常モード信号フィルタリングにより、アンチエイリアシングの必要条件をさらに簡単にします。動作モードには無関係に、 $f_S = 256 \cdot f_N = 2048 \cdot f_{OUTMAX}$ です。ただし、 $f_N$ はノッチ周波数、 $f_{OUTMAX}$ は最大出力データ・レートです。内部発振器モードでは、50Hzのノッチ設定で $f_S = 12,800\text{Hz}$ 、60Hzのノッチ設定で $f_S = 15,360\text{Hz}$ です。外部発振器モードでは、 $f_S = f_{EOSC}/10$ です。

図30. 入力通常モードの除去率、

内部発振器と50Hzノッチ

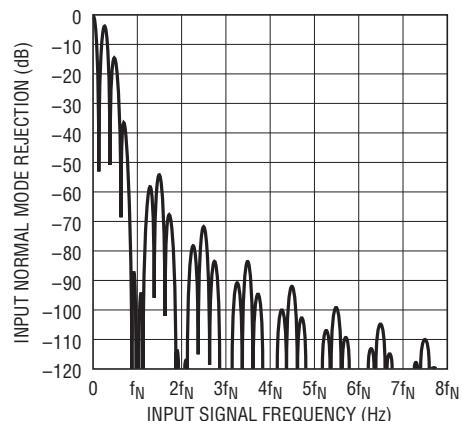

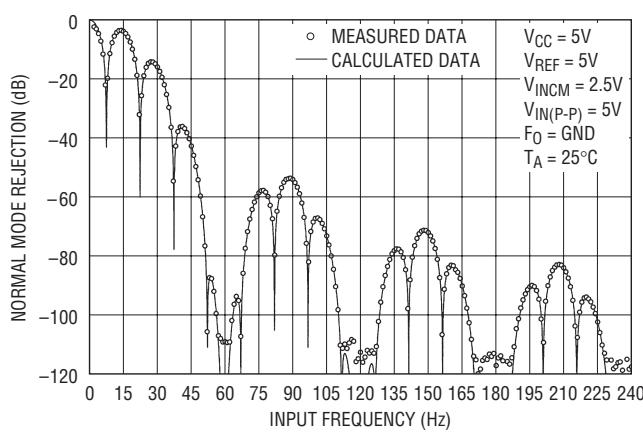

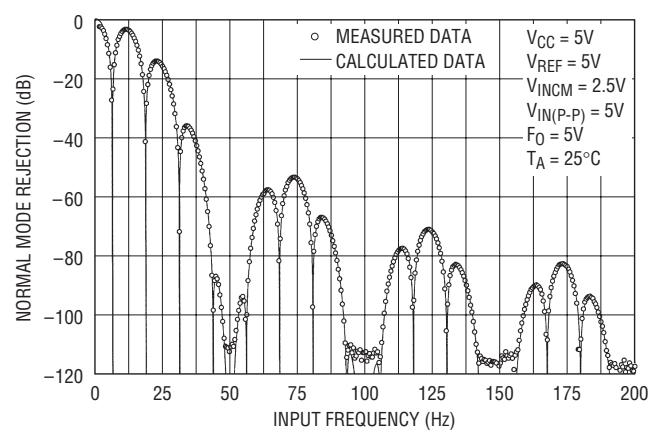

50Hzのノッチ設定( $F_O = "H"$ )の場合の結合された通常モードの除去性能を図30に示し、 $F_O = "L"$ の内部発振器の場合と外部発振器モードの場合を図31に示します。 $f_S$ の整数倍で生じる低除去領域の帯域幅は非常に狭くなります。通常モードの除去率曲線の拡大した細部を図32(DCの近くでの除去)と図33( $f_S = 256f_N$ での除去)に示します。ただし、 $f_N$ はノッチ周波数を表します。これらの曲線は外部発振器モードで得られましたが、それらは $f_N$ の値を適切に選択することにより全ての動作モードで使えます。

図34～図36に示されているように、ユーザーは内部発振器を使ってこのレベルの性能の実現を期待することができます。内部発振器を使い、60Hzのノッチ設定で動作しているLTC2430/LTC2431の通常モードの除去率の標準的測定値を、計算された理論曲線に重ね合わせて図34に示します。同様に、内部発振器と50Hzのノッチ設定で動作しているLTC2430/LTC2431の通常モード除去の標準的測定値を、理論的計算による曲線に重ね合わせて図35に示します。

これらの並外れた通常モードの仕様のおかげで、LTC2430/LTC2431の前段のアンチエイリアシングのフィルタリングは(もし必要だとしても)最小のもので十分です。LTC2430/LTC2431の前に受動RC部品を置く場合、入力のダイナミック電流について検討します(「入力電流」のセクションを参照)。大きな実効RC時定数が使われる場合、動的入力電流の影響を最小に抑えるため外部バッファ・アンプが必要になることがあります。

図31. 入力通常モードの除去率、

内部発振器と $F_O = "L"$ または外部発振器

## アプリケーション情報

図32. 入力通常モードの除去率

図33. 入力通常モードの除去率

図34. 入力通常モードの除去率と入力周波数

図35. 入力通常モードの除去率と入力周波数

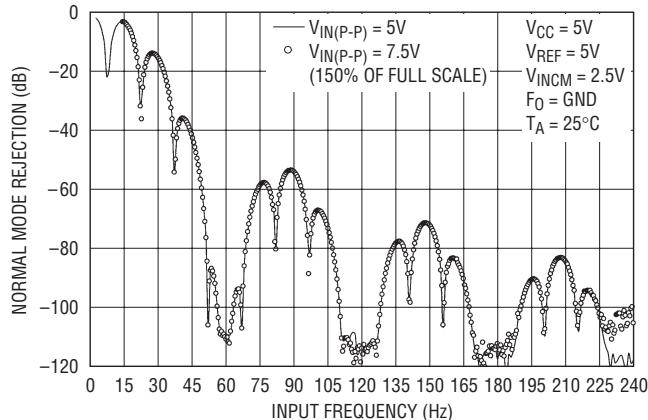

従来の高次デルタシグマ変調器は非常に良い直線性と分解能を与えますが、大きな入力信号レベルでは潜在的に不安定です。LTC2430/LTC2431の3次変調器に使われている独自アーキテクチャはこの問題を解決し、フルスケールの最大150%の入力信号レベルで予測可能な安定動作を保証します。多くの産業用アプリケーションでは、ボルト・レベルの乱れに重ねられたマイクロボルト・レベルの信号を測定しなければならないことが珍しくありませんが、LTC2430/LTC2431は並外れてこのような課題に適しています。乱れが差動のとき、関係する仕様は大きな入力信号レベルに対する通常レベルの除去率です。リファレンス電圧 $V_{REF} = 5V$ のとき、LTC2430/

LTC2431のフルスケール差動入力範囲は5Vピーク・トゥ・ピークです。5Vピーク・トゥ・ピーク(フルスケール)入力信号を使って得られた従来の通常モードの除去率の結果に重ね合わせた、7.5Vピーク・トゥ・ピーク(フルスケールの150%)入力信号を使った、LTC2430/LTC2431の通常モードの除去率の測定結果を図36と図37に示します。LTC2430/LTC2431の除去性能はこの極端な状況でも低下せずに保たれていることが明らかです。大きな入力信号レベルで動作しているとき、ユーザーはこのような信号がデバイスの絶対最大定格を超えないよう注意する必要があります。

# LTC2430/LTC2431

## アプリケーション情報

2431 F36

図36. 入力の通常モードの測定された除去率と入力周波数

2431 F37

図37. 入力の通常モードの測定された除去率と入力周波数

## ブリッジ・アプリケーション

標準的歪みゲージをベースにしたブリッジは2mV/ボルトの励起電圧しか与えません。LTC2430/LTC2431の最大リファレンス電圧は5Vですから、与えられた励起を追加回路なしでリモート検出するには、励起を5Vに制限する必要があります。このため、フルスケールはわずか10mVになり、これは平均化処理なしで3500分の1に分解することができます。多くのソリッドステート・センサの場合、これはセンサと同等です。ただし、128サンプルを平均化するとノイズ・レベルは8分の1に減少し、分解能が40000分の1になります。もっと良い計量システムと同等になります。ロードセルのヒステリシスとクリープ効果は一般にこれよりはるかに大きくなります。このレベルの精度の歪み測定を必要とするほとんどのアプリケーションは低速で変化する現象の測定です。したがって、多数の読み取り値の平均化が必要な時間は通常問題ではありません。大きな風袋重量上の小さなインクリメンタルな変化の精確な測定を必要とするシステムの場合、履歴効果の無いLTC2430/LTC2431ファミリは大きな利点を与えます。

LTC2430/LTC2431だけでは要件を満たせないアプリケーションの場合、LTC2430/LTC2431の「待ち時間なし」の特長により、外部アンプの誤差を効果的に補償することができます。待ち時間なしの動作により、アンプのオフセットと利得のサンプルを重量測定の間隙に挟み込むことが可能になります。相関を取ったダブル・サンプリングを使うと、ブリッジ内の1/fノイズ、オフセットおよび熱電対効果を抑止することができます。相関を取ったダブル・サンプリングには、励起の極性の反転と

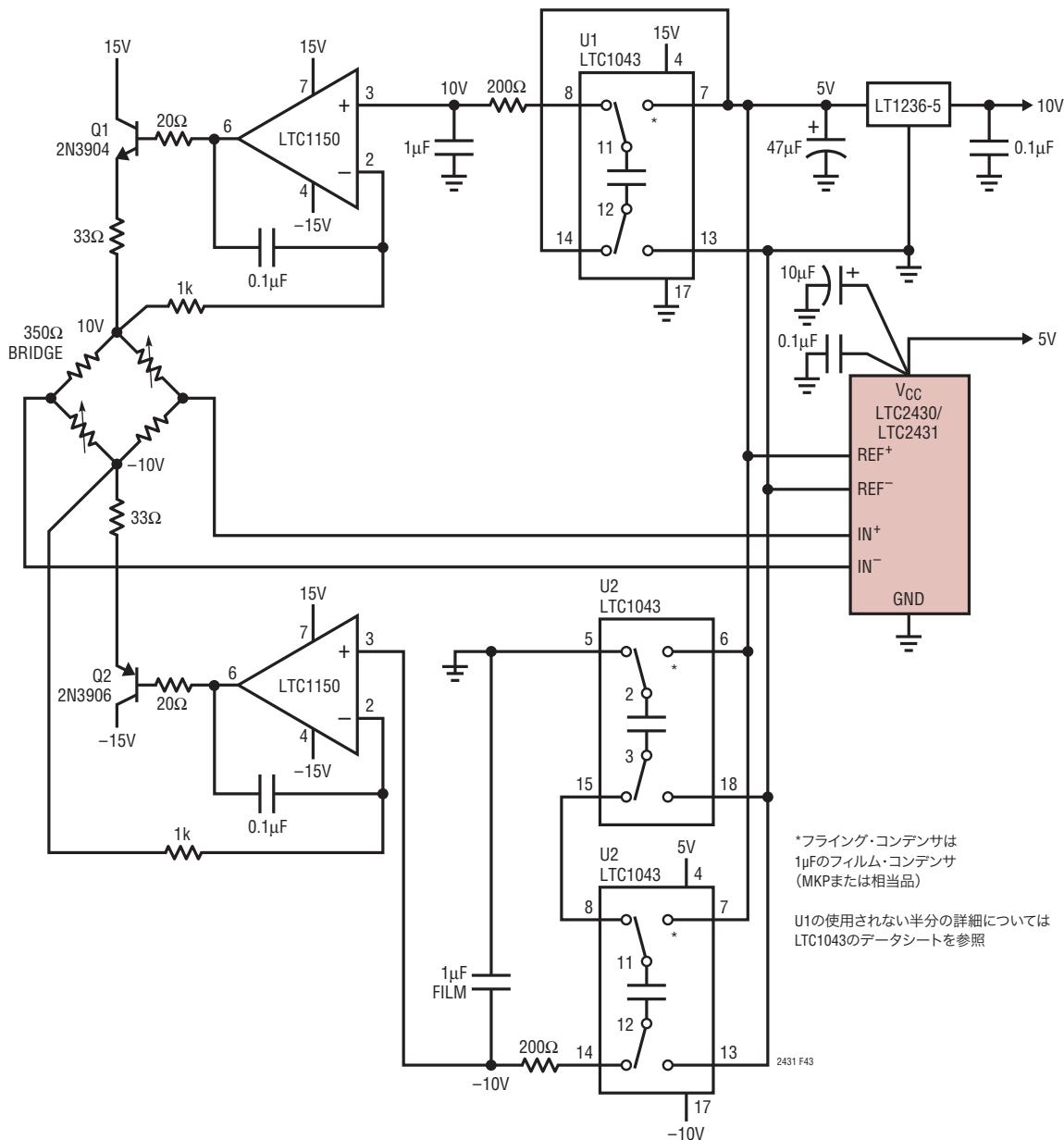

入力の極性の数学的反転の扱いが含まれます。代わりに、いくつかの高精度減衰手法の1つを使ってリファレンス信号の高精度分割を行うと、ブリッジの励起を最大 $\pm 10V$ に増加させることができます。別のオプションとして、図43と図45に示されているように、励起アンプのリモート・フィードバックとともに、LTC2430/LTC2431の5V入力範囲内のリファレンスを使って固定利得を介して励起を発生するか、またはLTC1043ベースの電圧乗算を使います。

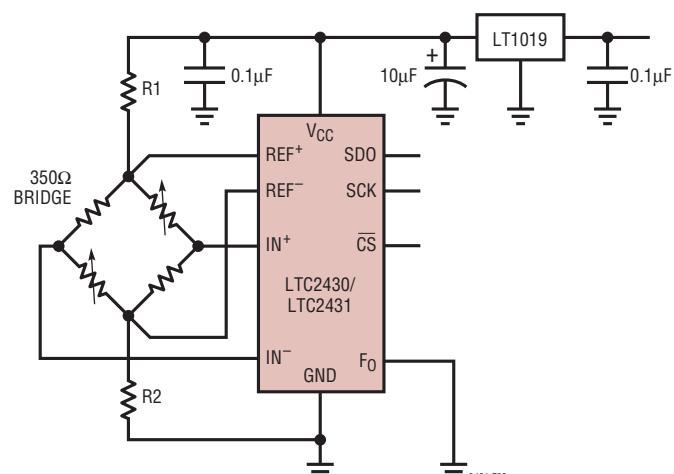

簡単なブリッジ接続の例を図38に示します。これは測定速度が最優先されるのではなくどんなブリッジ・アプリケーションにも適していることに注意してください。

R1とR2を使って、REF信号の許容AC成分を増やすことができる

図38. 簡単なブリッジ接続

24301f

## アプリケーション情報

大きな容器の重量計測が行われる多くのアプリケーションでは、長時間にわたる平均重量に関心があり、内容物の動きや機械的共振のため短時間の重量はすぐには決定されません。多くの場合、大きな重量の測定アプリケーションでは、各負荷保持ポイントに配置されたロードセルが使われ、それらの出力は信号処理回路の前に受動素子で和を取るか、ADCの前にアクティブに増幅して和を取るか、または複数のADCチャネルを介してデジタル化してから数学的に和を取ることができます。複数のLTC2430/LTC2431の出力の数学的加算はノイズの平方根減少の利点を与えます。LTC2430/LTC2431は低消費電力なので、ADCがロードセルの筐体内部に配置されているマルチドロップ通信方式に最適です。

ロードセルへの直接接続はロードセルのボディに組み込むのがおそらく最善でしょう。センサへの距離を最小にすると、保護デバイス、RFIサプレッション、配線などが不要になるからです。LTC2430/LTC2431の示す温度ドリフトはきわめて微小です。その結果、外部の周囲温度範囲に置いても性能が損なわれません。増幅機能を組み込むと熱的安定性が大きく低下します。入力オフセット電圧と電流、利得設定抵抗の温度係数の全てが要因になるからです。

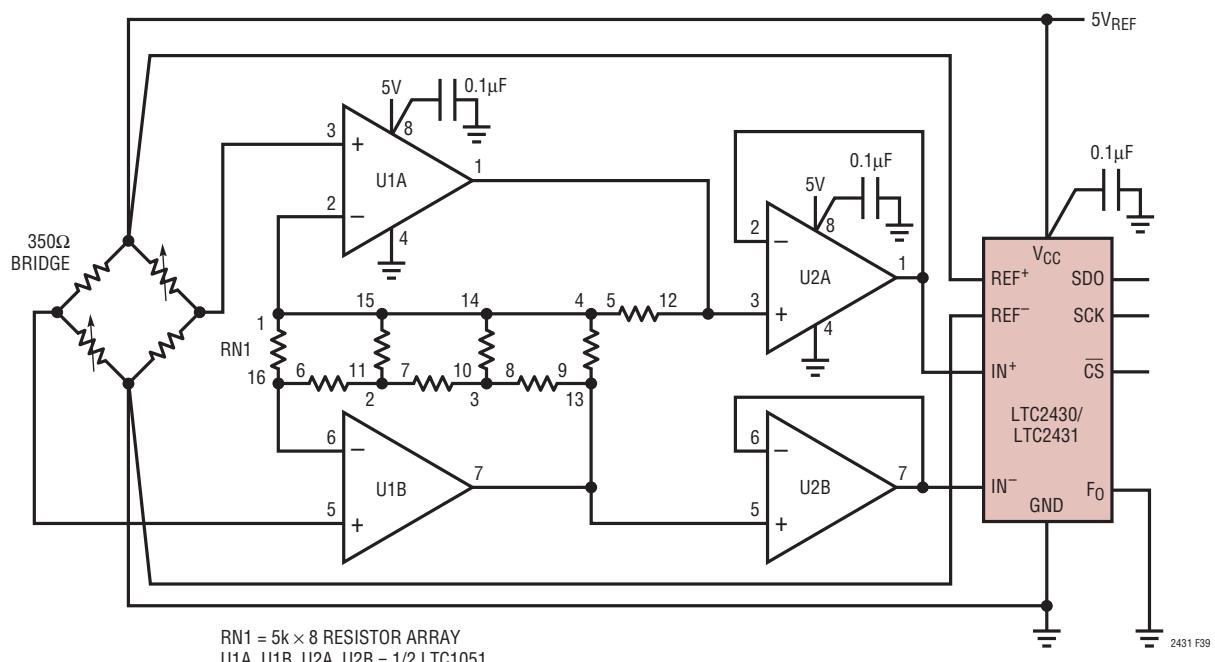

図39の回路は簡単な増幅方式の一例を示しています。この例は、ブリッジによって決定されるように、同相電圧が2.5Vの差動出力を与えます。3個のアンプで構成される真の計装アンプを使う必要はありません。LTC2430/LTC2431の同相除去はほとんどのアンプを大きく凌いでいるからです。LTC1051はデュアルのオートゼロ・アンプで、その入力基準のノイズがLTC2430/LTC2431のノイズを支配する前に10の利得を与えるのに使うことができます。この例は34の利得を示しており、8個の個別抵抗を含む抵抗アレイを使って作られた帰還ネットワークによって決定されます。抵抗は熱勾配が存在するとき温度トラッキングを最適化するように配置されています。2番目のLTC1051は変換時に発生する過渡負荷ステップから低ノイズ入力段をバッファします。

個々の誤差要因を減らすことにより抵抗の整合が統計的に改善されるので、この手法の利得の安定性と精度は非常に良いになります。

図39. オートゼロ・アンプを使った入力リファレンス・ノイズの削減

## LTC2430/LTC2431

## アプリケーション情報

ロードセルのインターフェースの以前の世代で一般的に行われていたのと比べると、34の利得は低く見えるかもしれません。LTC2430/LTC2431の精度は考えを変えます。高い利得で高い利得精度と直線性を達成するのは困難なことがあります。ノイズの削減の点では利点がほとんど無いことがあります。

100の利得では、160dBの標準的開ループ利得から生じる利得誤差は-1ppmですが、ワーストケースでは116dBの最小利得で利得誤差が-158ppmになります。34の利得でのワーストケースの利得誤差は-54ppmです。LTC1051Aを使うとワーストケースの利得誤差は-33ppmに減少します。34より高い利得の利点はあやしくなります。入力基準のノイズはほとんど改善されず、利得精度は潜在的に低下するからです。

この4アンプ・トポロジーには(計装アンプが低利得で使われるとき通常支配的な)出力段に一般的な高いノイズ・レベルがないという意味で、このトポロジーには標準的な集積化された3アンプ計装アンプより利点があることに注意してください。このアンプが10の利得で使われると利得誤差はわずか10ppmで、入力基準のノイズは0.28 $\mu$ V<sub>RMS</sub>に減少します。バッファ段は高い利得安定性と直線性で最大50の利得を与えるように構成設定することもできます。

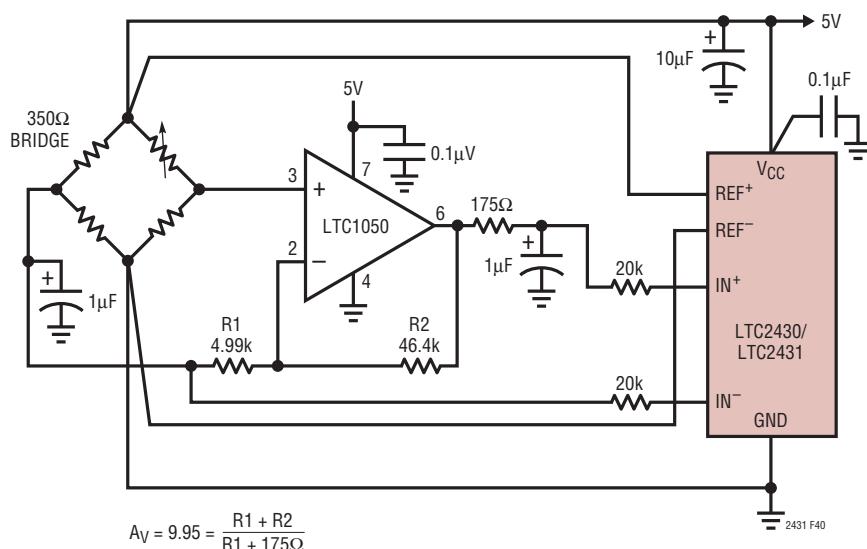

シングルエンドの利得を与えるのに使われている1個のアンプの例を図40に示します。このトポロジーは、利得設定抵抗を歪みゲージの温度係数に整合させることができるアプリケーションに最適です。ブリッジがわずか1つか2つの可変素子と一緒に精密抵抗で構成されている場合、ブリッジのリファレンスの部分が帰還抵抗と一緒に動作するようにして利得を決めることができます。帰還抵抗がロードセルのデザインに組み込まれている場合、ロードセルの素子の温度係数に合致した抵抗を使うと、絶対精度の高い抵抗を使う必要なしに良い結果を得ることができます。この場合の同相電圧はここでもブリッジの出力の関数です。 $350\Omega$ のブリッジで使われた差動利得は次のとおりです。

$$A_V = 9.95 = \frac{R_1 + R_2}{R_1 + 175\Omega}$$

同相利得は差動利得の半分です。利用可能な最大差動信号は $1/4 V_{REF}$ であり、上述の2アンプ・トポロジーの場合の $1/2 V_{REF}$ とは異なります。

## リモート・ハーフブリッジ・インターフェース

フルブリッジ・アプリケーションとは異なり、標準的ハーフブリッジ・アプリケーションは信号振幅がずっと大きいことが多いので、ブリッジの出力の非直線性に対処する必要があります。アプリケーションには、それぞれのスパンで大きく変化するRTD、サーミスタ、その他の抵抗性素子が含まれます。

図40. 1個のアンプを使うブリッジ・アプリケーション

## アプリケーション情報

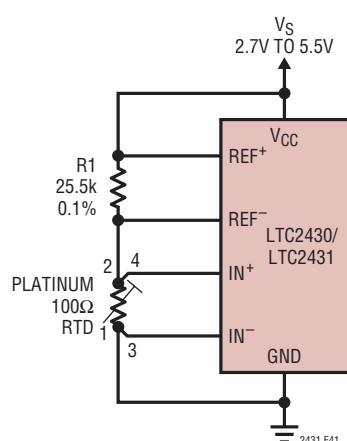

可変素子が1個のブリッジの場合、図41に示されているように、ブリッジのリファレンス部分がADCのリファレンスとして使われていると、ハーフブリッジの出力の非直線性は完全に除去できます。LTC2430/LTC2431は $1/2 V_{REF}$ までの入力を受け入れることができます。したがって、リファレンス抵抗R1は可変抵抗の最大値の少なくとも2倍の値が必要です。

これは、 $100\Omega$  プラチナRTDの場合、R1の値が $800\Omega$ となることを意味します。このように低い値のR1は、自己発熱効果のため推奨できません。R1には $25.5k$ の値が示されており、自己発熱効果はほとんどのセンサにとって許容できるレベルに減少します。

図41. リモート・ハーフブリッジ・インターフェース

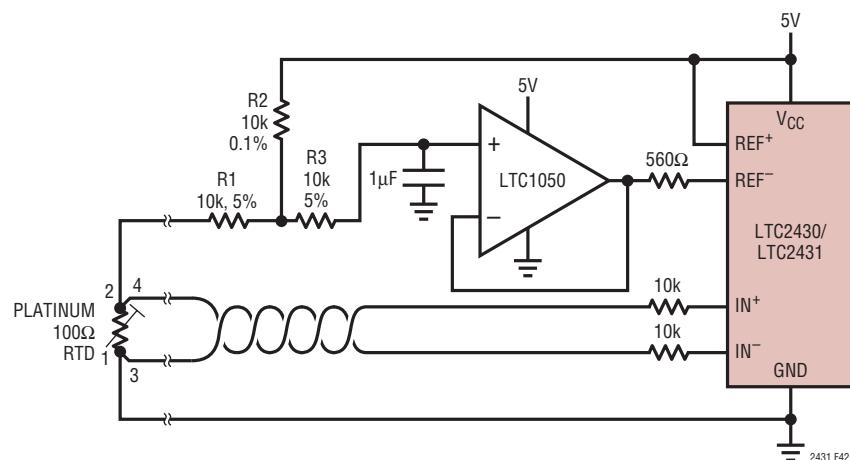

図41に示されている基本回路はセンサへの完全な4線接続を示しており、センサは遠くに配置することができます。差動入力接続は、誘起された、またはカップリングした $60Hz$ の干渉を除去しますが、リファレンス入力には同じ除去性能はありません。 $60Hz$ ノイズや他のノイズがRTDに現れる場合、図42に示されているようなローパス・フィルタを推奨します。R1とR2の接続部分に大きなコンデンサを直接配置することはできないことに注意してください。このコンデンサはサンプリング過程の電荷を保存するからです。もっと良い方法は、値の大きな抵抗(R3)を使って入力ラインからデカップリングされたローパス・フィルタを作ることです。

ハーフブリッジで(可変素子と固定素子の間に)3番目の抵抗を使うと、2抵抗のバージョンと本質的に同じ結果を与えますが、いくつかの利点が得られます。たとえば、 $25k$ のリファレンス抵抗を使って $100\Omega$  RTDの励起電流を設定すると、負リファレンス入力は正入力と同じ外部ノードをサンプリングしていますが、長いケーブルと一緒に使われると誤差を生じことがあります。ケーブルが短いアプリケーションでは、誤差は小さく許容できるでしょう。代わりに、1個の $25k$ 抵抗を $10k\ 5\%$ および $10k\ 0.1\%$ のリファレンス抵抗で置き換えると、リファレンスに入り込むノイズ・レベルは(少なくとも高い周波数では)減少します。サンプリング・パルスが誤差に変換されない限り、1個または複数のコンデンサ、またはフェライト・ビーズの形で、フィルタをネットワークに導入することができます。リファレンス電圧も減少しますが、これは望ましくありません。それは、入力基準のノイズ・レベルではなく、LSBの値を減らすからです。

図42. リファレンスのノイズ・サプレッション付きリモート・ハーフブリッジ検出

## LTC2430/LTC2431

## アプリケーション情報

図42に示されている回路は図41のもっと厳しい例を示しており、ノイズ・サプレッションが増加し、リモート・アプリケーションの保護が強化されています。

励起回路の利得とブリッジからのリモート・フィードバックの例を図43に示します。LTC1043は電圧乗算機能を備えており、5Vリファレンスからわずか1ppmの誤差で±10Vを発生します。アンプはユニティゲインで使われているので、利得誤差やオフセット電圧によって生じる誤差は微小です。 $1\mu\text{V}/^\circ\text{C}$ のオフセット

ト電圧ドリフトは0.05ppm/°Cの利得誤差に変換されます。同様の代替方式は、フィードバックに抵抗アレイを使って利得を与えるアンプを使って、減衰器を介したプリッジ検出方式に似た結果を与えることができます。アンプの開ループ利得が高くなければならず、そうでないと利得誤差が誤差の原因になることに注意してください。入力オフセット電圧は全体の誤差に比較的影響を与えないで、このアプリケーションには性能の低いアンプを使いたくなるかもしれません。

図43. 励起電圧に精密4×リファレンスを与えるLTC1043

## アプリケーション情報

LF156のようなデバイスの利得(全温度範囲で25V/mV)は、(5Vリファレンスから-10Vを発生するための2の反転利得で経験するように)3のノイズ利得で-180ppmのワーストケース誤差を生じることに注意してください。

10Vの励起に関連した誤差は-80ppmとなるでしょう。したがって、全体のリファレンス誤差は130ppm(2つの平均)に達することができます。

精密利得を与えるため抵抗アレイを使って励起を与える同様の方式を図45に示します。回路は10Vと-5Vの励起をブリッジに与えるように構成設定され、LTC2430/LTC2431の入力に2.5Vの同相電圧を生じ、誘起された60Hzの振幅が最大2VRMSに達することがあるアプリケーションのAC入力範囲を最大にします。

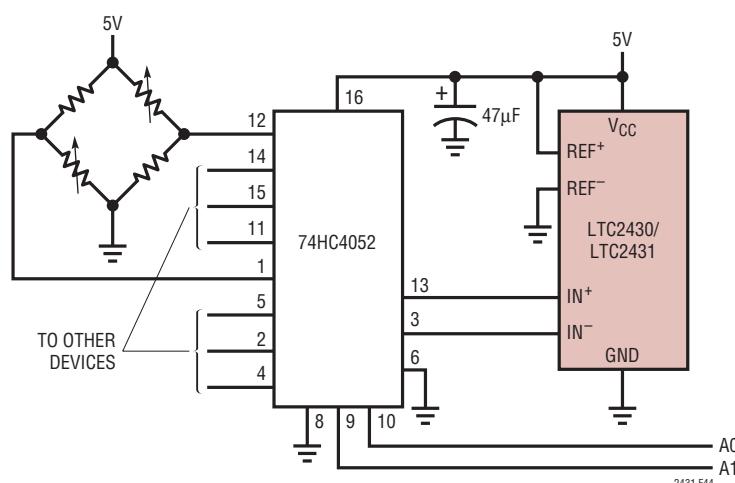

図43と図45の回路は、複数のブリッジ回路を備え、ブリッジ出力を(74HC4052のような安価なマルチプレクサを介して)1個のLTC2430/LTC2431に多重化することができる場合に使うことができます。

LTC2430/LTC2431を差動マルチプレクサと一緒に使う方法を図44に示します。これは安価なマルチプレクサで、ブリッジの出力に直接使うと、または過電圧に対する保護メカニズムとし

て抵抗が挿入されると、リークのためいくらかの誤差が加わります。通常動作ではブリッジの出力はA/Dおよびマルチプレクサの入力範囲内にあるでしょうが、マルチプレクサまたはADCへの入力に最大励起電圧を生じる可能性のあるフォールト状態について考えておきます。マルチプレクサの前にアンプを使用すると、ソース・インピーダンスに誤差電圧を生じるチャネルのリーク電流に関連した誤差の大部分を除去します。

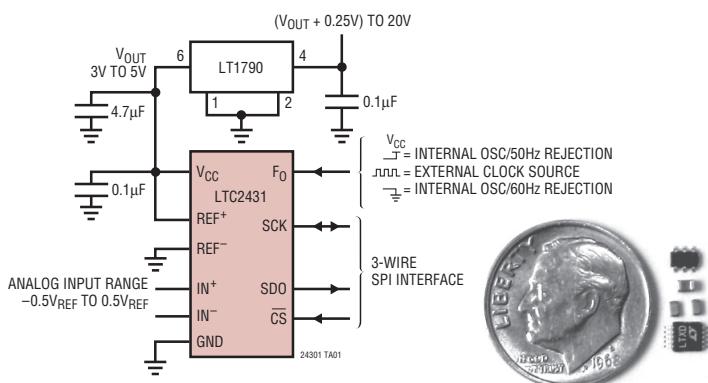

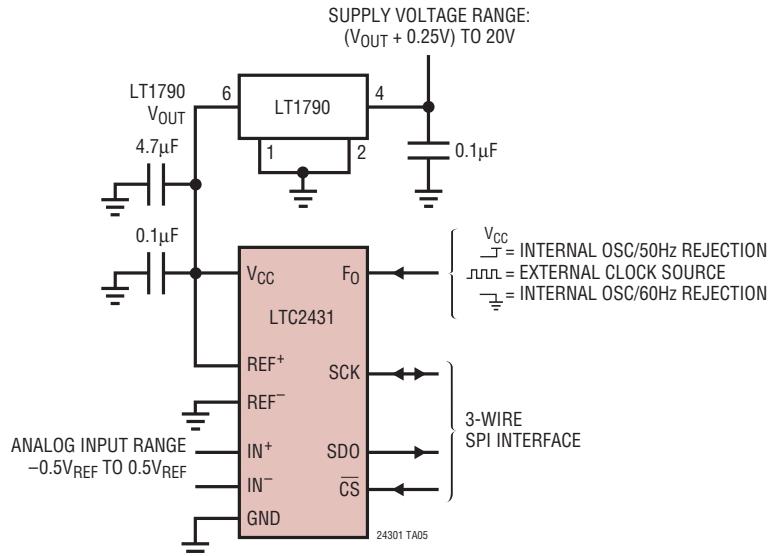

### 0.1平方インチの完全な20ビットデータ収集システム

LTC2430/LTC2431は20ビットの精度があり、最大300µAを消費します。LTC2431はMSパッケージなので、利用できるスペースが非常に限られているアプリケーションには特に適しています。0.1平方インチの完全な20ビット・データ収集システムを図46に示します。このシステムでは、LTC2431はS6パッケージのLT1790リファレンス・ファミリによって給電されます。LT1790の出力レベルより0.25V上から20Vまでの電源電圧であれば、LT1790は最大1mAを供給し、LTC2431の安定した性能を保証することができます。

LT1790の3V、3.3V、4.096Vおよび5Vのバージョンは直接 LTC2430/LTC2431に給電することができます。もっと低い電圧バージョンは、LTC2430/LTC2431のために2.7V～5.5Vの別のVCC電源が必要です。

図44. 差動マルチプレクサを使ってチャネル能力を拡張

# LTC2430/LTC2431

## アプリケーション情報

図45. 抵抗アレイを使って励起アンプの精密整合を実現

## パッケージ寸法

**GNパッケージ

16ピン・プラスチックSSOP(細型0.150インチ)

(Reference LTC DWG # 05-08-1641)**

MSパッケージ

10ピン・プラスチックMSOP

(Reference LTC DWG # 05-08-1661)

注記：

1. 寸法はミリメートル/(インチ)

2. 図は実寸とは異なる

3. 寸法にはモールドのバリ、突出部、またはゲートのバリを含まない。

モールドのバリ、突出部、またはゲートのバリは、各サイドで $0.152\text{mm}(0.006")$ を超えないこと

4. 寸法には、リード間のバリまたは突出部を含まない。

リード間のバリまたは突出部は、各サイドで $0.152\text{mm}(0.006")$ を超えないこと

5. リードの平坦度(整形後のリードの底面)は最大 $0.102\text{mm}(0.004")$ であること

# LTC2430/LTC2431

## 標準的応用例

デバイスのサイズの比較

LT1790は1.25V、2.048V、2.5V、3V、3.3V、4.096Vおよび5Vの各出力のものが提供されている

LTC2431はLT1790の3V、3.3V、4.096Vおよび5Vの各バージョンから給電することができる

図46. 0.1平方インチの完全な20ビットデータ収集システム

## 関連製品

| 製品番号                 | 説明                                          | 注釈                                         |

|----------------------|---------------------------------------------|--------------------------------------------|

| LT <sup>®</sup> 1019 | 高精度バンドギャップ・リファレンス、2.5V、5V                   | ドリフト:3ppm/ $^{\circ}$ C、初期精度:最大0.05%       |

| LT1025               | 熱電対用マイクロパワー冷接点補償器                           | 電源電流:80μA、初期精度:0.5 $^{\circ}$ C            |

| LTC1050              | 高精度チオッパ安定オペアンプ                              | 外付け部品不要、オフセット:5μV、ノイズ:1.6μV <sub>P-P</sub> |

| LT1236A-5            | 高精度バンドギャップ・リファレンス、5V                        | 初期精度:最大0.05%、ドリフト:5ppm/ $^{\circ}$ C       |

| LT1460               | マイクロパワー・シリーズのリファレンス                         | 初期精度:最大0.075%、ドリフト:最大10ppm/ $^{\circ}$ C   |

| LT1790               | マイクロパワーSOT23低ドロップアウト・リファレンス・ファミリ            | 初期精度:最大0.05%、ドリフト:最大10ppm/ $^{\circ}$ C    |

| LTC2400              | 24ビット、No Latency ΔΣ ADC、SO-8                | ノイズ:0.3ppm、INL:4ppm、全未調整誤差:200μA           |

| LTC2401/LTC2402      | 1チャネル/2チャネル、24ビット、No Latency ΔΣ ADC、MSOP    | ノイズ:0.6ppm、INL:4ppm、全未調整誤差:10ppm、200μA     |

| LTC2404/LTC2408      | 4チャネル/8チャネル、24ビット、No Latency ΔΣ ADC         | ノイズ:0.3ppm、INL:4ppm、全未調整誤差:10ppm、200μA     |

| LTC2410              | 24ビット、完全差動、No Latency ΔΣ ADC                | ノイズ:0.16ppm、INL:2ppm、全未調整誤差:10ppm、200μA    |

| LTC2411              | 24ビット、完全差動、No Latency ΔΣ ADC、MS10           | ノイズ:0.29ppm、INL:2ppm、全未調整誤差:10ppm、200μA    |

| LTC2413              | 24ビット、完全差動、No Latency ΔΣ ADC                | 50Hzと60Hzを同時除去、ノイズ:800nV <sub>RMS</sub>    |

| LTC2414/LTC2418      | 8チャネル/16チャネル、24ビット、差動、No Latency ΔΣ ADC     | ノイズ:0.2ppm、INL:2ppm、全未調整誤差:10ppm           |

| LTC2415              | 24ビット、No Latency ΔΣ ADC、15Hz出力レート           | LTC2410とピン・コンパチブル                          |

| LTC2420              | 20ビット、No Latency ΔΣ ADC、SO-8                | ノイズ:1.2ppm、INL:8ppm、LTC2400とピン・コンパチブル      |

| LTC2421/LTC2422      | 1チャネル/2チャネル、20ビット、No Latency ΔΣ ADC、MSOP-10 | ノイズ:1.2ppm、ローパワー2.7V~5.5V電源、200μA          |

| LTC2424/LTC2428      | 4チャネル/8チャネル、20ビット、No Latency ΔΣ ADC         | ノイズ:1.2ppm、LTC2404/LTC2408とピン・コンパチブル       |

| LTC2440              | 24ビット、高速、低ノイズ、ΔΣ ADC                        | ノイズ:200nV <sub>RMS</sub> 、出力レート:4000Hz     |

24301f