SNRが94.7dBの16ビット、

250ksps、単極性疑似差動

SAR A/Dコンバータ

## 特長

- スループット・レート: 250ksps

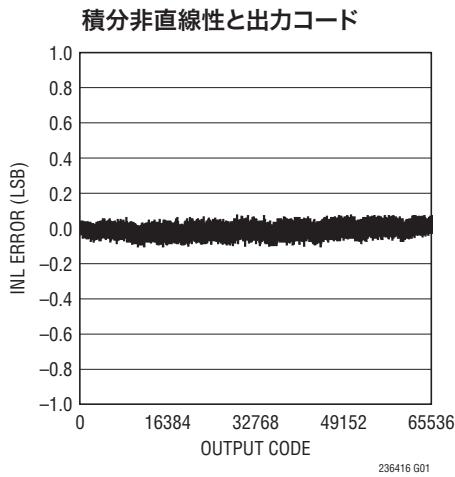

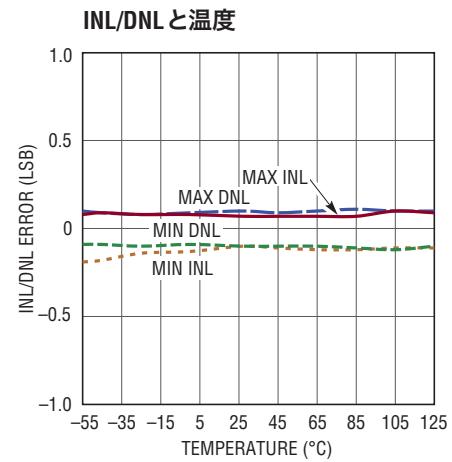

- INL:  $\pm 0.75$ LSB(最大)

- 欠落コードのない16ビット分解能を保証

- 低消費電力: 250ksps で 3.4mW、250spS で 3.4 $\mu$ W

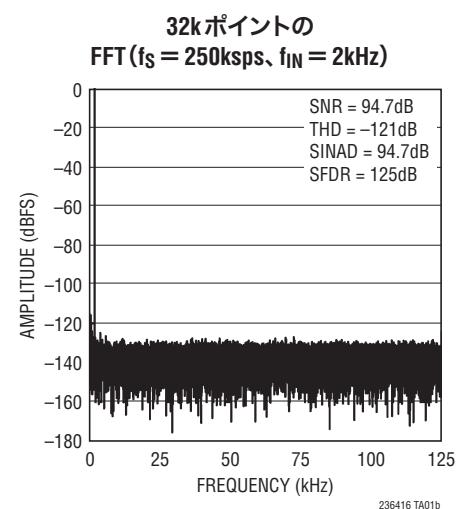

- SNR(標準): 94.7dB ( $f_{IN} = 2$ kHz)

- THD(標準): -120dB ( $f_{IN} = 2$ kHz)

- 125°Cまでの動作を保証

- 2.5V電源

- 単極性の疑似差動入力範囲: 0V ~  $V_{REF}$

- $V_{REF}$ 入力範囲: 2.5V ~ 5.1V

- パイプライン遅延なし、サイクル待ち時間なし

- 入出力の電圧: 1.8V ~ 5V

- デイジーチェーン・モードを備えたSPI互換シリアルI/O

- 内部変換クロック

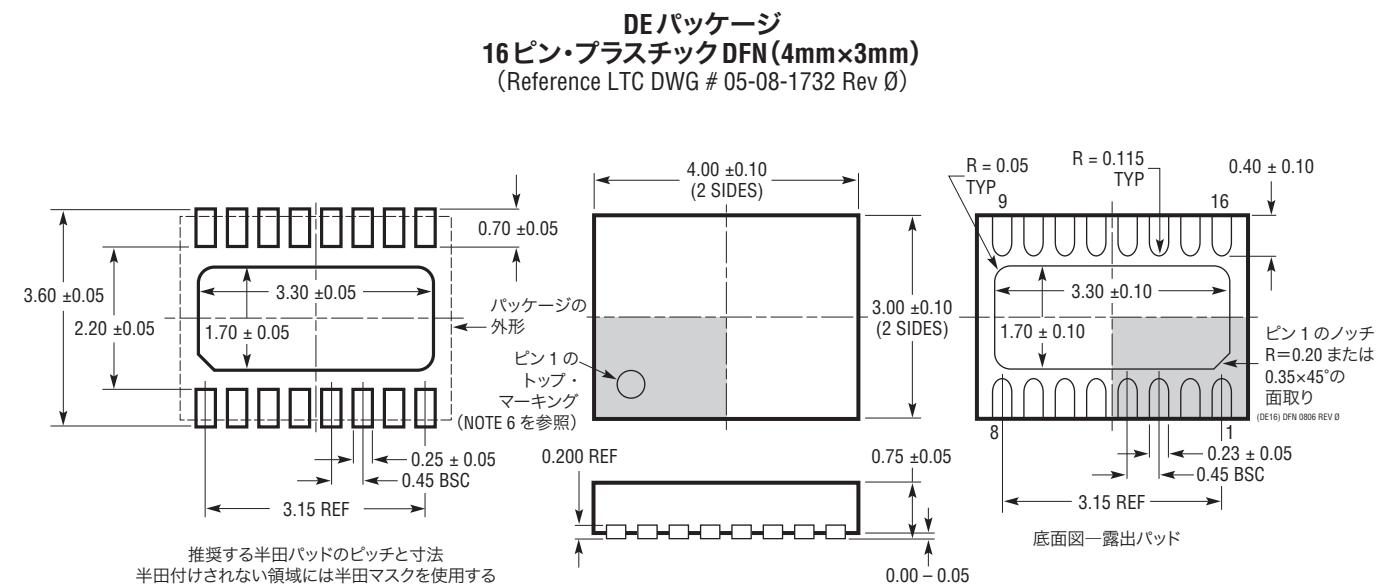

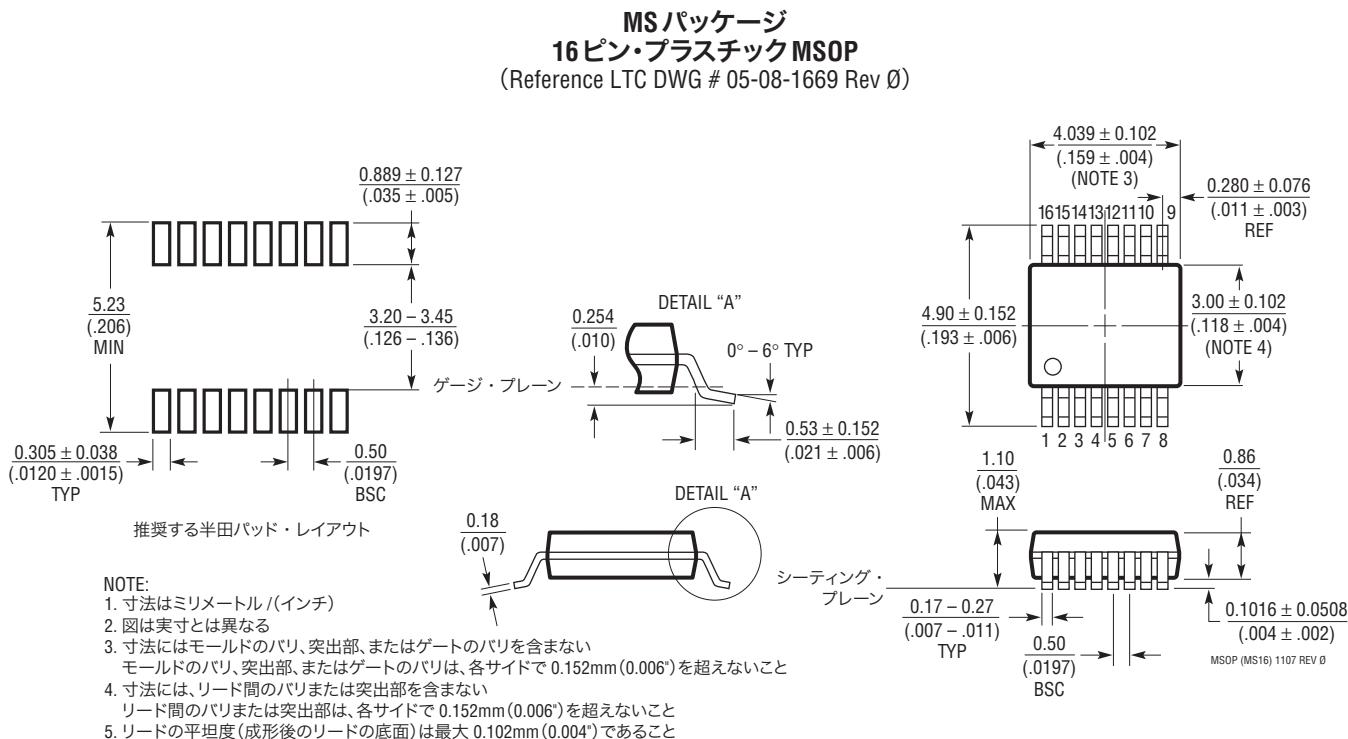

- 16ピンMSOPおよび4mm×3mm DFNパッケージ

## アプリケーション

- 医療用画像処理

- 高速データ収集

- 携帯型または小型計測器

- 産業用プロセス制御

- 低消費電力のバッテリ駆動計測器

- ATE

## 概要

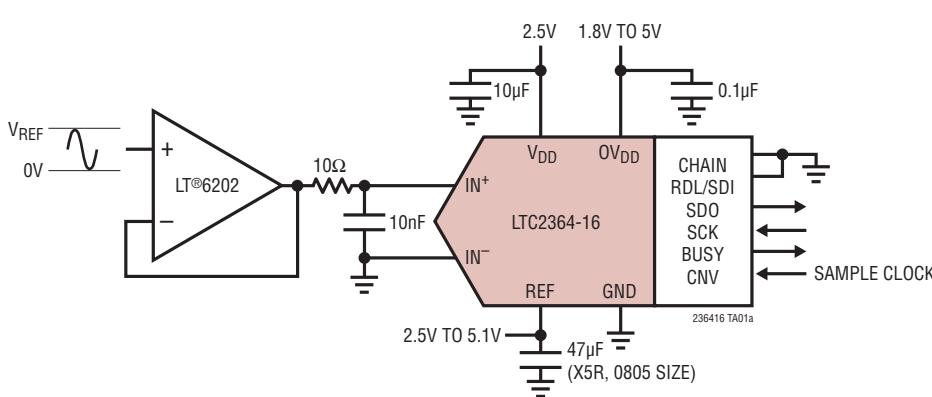

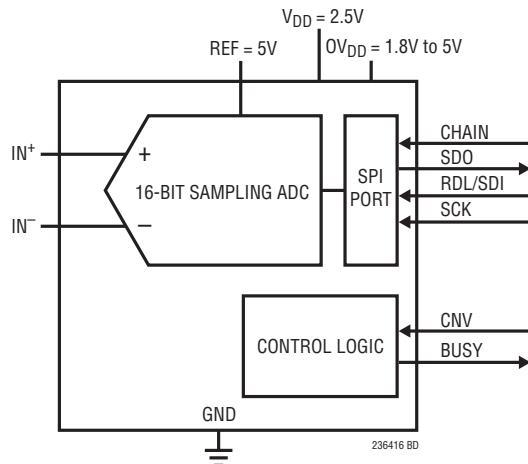

LTC<sup>®</sup>2364-16は、低ノイズ、低消費電力の高速16ビット逐次比較レジスタ(SAR)A/Dコンバータです。LTC2364-16は2.5V電源で動作し、 $V_{REF}$ の範囲が2.5V～5.1Vの場合、単極性の疑似差動入力範囲は0V～ $V_{REF}$ です。LTC2364-16は、わずか3.4mWの消費電力、 $\pm 0.75$ LSBのINL(最大)、16ビット分解能で欠落コードなし、および94.7dBのSNRを実現します。

LTC2364-16には、1.8V、2.5V、3.3Vおよび5VのロジックをサポートするSPI互換の高速シリアル・インターフェースがあり、デイジーチェーン・モードも備えています。サイクル待ち時間がなく、スループットが250kspsと速いので、さまざまな高速アプリケーションに最適です。内部発振器が変換時間を設定するので、外部のタイミングに対する配慮は少なくて済みます。LTC2364-16は、変換と変換の間は消費電力が自動的に低下するので、サンプリング・レートに比例して電力損失が減ります。

LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。SoftSpanはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。7705765を含む米国特許によって保護されています。

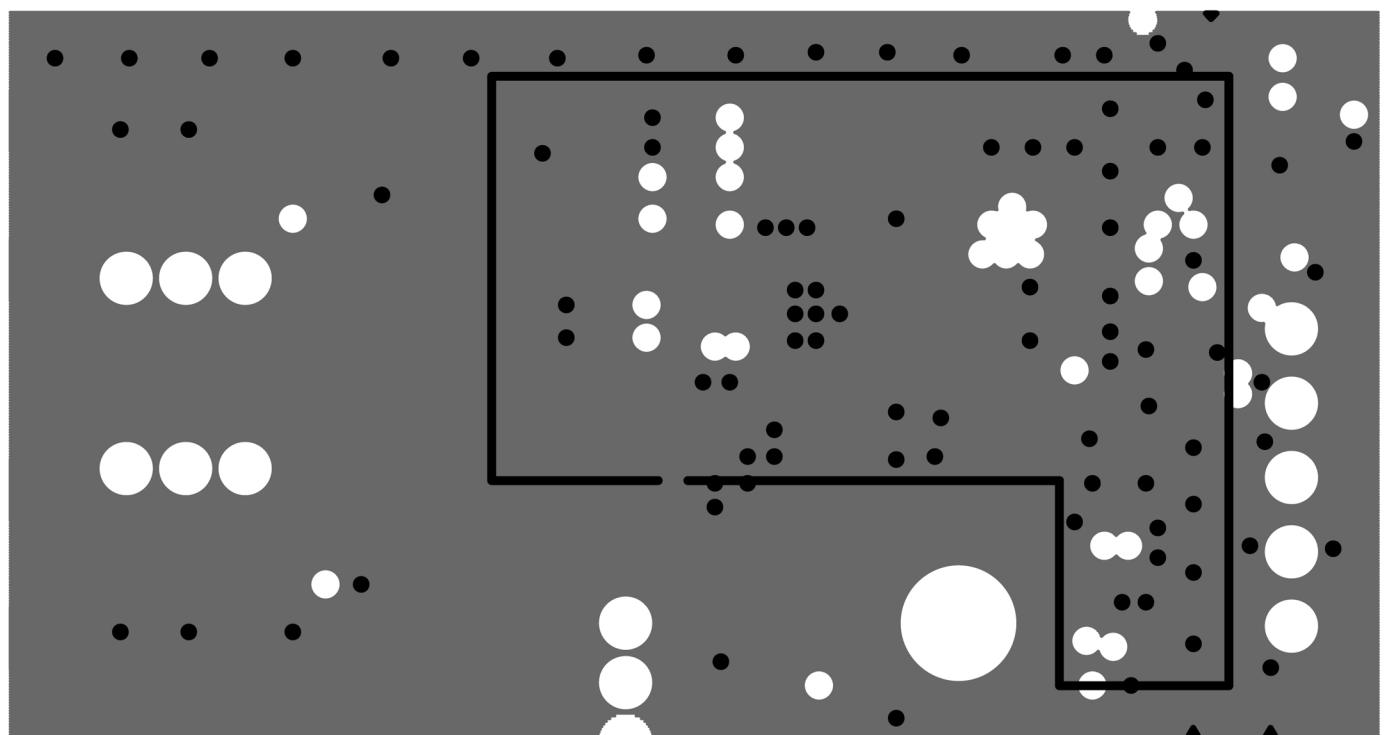

## 標準的応用例

## 絶対最大定格 (Note 1, 2)

|                                  |                                          |

|----------------------------------|------------------------------------------|

| 電源電圧 (V <sub>DD</sub> )          | 2.8V                                     |

| 電源電圧 (0V <sub>DD</sub> )         | 6V                                       |

| リファレンス入力 (REF)                   | 6V                                       |

| アナログ入力電圧 (Note 3)                |                                          |

| IN <sup>+</sup> 、IN <sup>-</sup> | (GND - 0.3V) ~ (REF + 0.3V)              |

| デジタル入力電圧                         |                                          |

| (Note 3)                         | (GND - 0.3V) ~ (0V <sub>DD</sub> + 0.3V) |

| デジタル出力電圧                         |                                          |

| (Note 3)                         | (GND - 0.3V) ~ (0V <sub>DD</sub> + 0.3V) |

|           |               |

|-----------|---------------|

| 電力損失      | 500mW         |

| 動作温度範囲    |               |

| LTC2364C  | 0°C ~ 70°C    |

| LTC2364I  | -40°C ~ 85°C  |

| LTC2364 H | -40°C ~ 125°C |

| 保存温度範囲    | -65°C ~ 150°C |

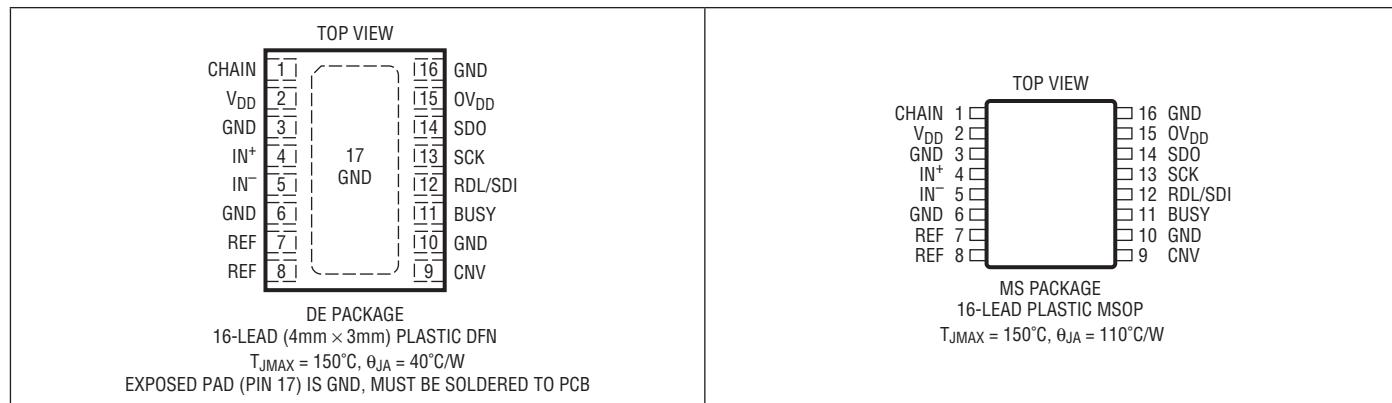

## ピン配置

## 発注情報

| 無鉛仕上げ             | テープアンドリール           | 製品マーキング* | パッケージ                           | 温度範囲           |

|-------------------|---------------------|----------|---------------------------------|----------------|

| LTC2364CMS-16#PBF | LTC2364CMS-16#TRPBF | 236416   | 16-Lead Plastic MSOP            | 0°C to 70°C    |

| LTC2364IMS-16#PBF | LTC2364IMS-16#TRPBF | 236416   | 16-Lead Plastic MSOP            | -40°C to 85°C  |

| LTC2364HMS-16#PBF | LTC2364HMS-16#TRPBF | 236416   | 16-Lead Plastic MSOP            | -40°C to 125°C |

| LTC2364CDE-16#PBF | LTC2364CDE-16#TRPBF | 23646    | 16-Lead (4mm x 3mm) Plastic DFN | 0°C to 70°C    |

| LTC2364IDE-16#PBF | LTC2364IDE-16#TRPBF | 23646    | 16-Lead (4mm x 3mm) Plastic DFN | -40°C to 85°C  |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

電気的特性 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL                | PARAMETER                           | CONDITIONS                     | MIN | TYP     | MAX             | UNITS                      |

|-----------------------|-------------------------------------|--------------------------------|-----|---------|-----------------|----------------------------|

| $V_{IN^+}$            | Absolute Input Range ( $V_{IN^+}$ ) | (Note 5)                       | ●   | -0.1    | $V_{REF} + 0.1$ | V                          |

| $V_{IN^-}$            | Absolute Input Range ( $V_{IN^-}$ ) | (Note 5)                       | ●   | -0.1    | 0.1             | V                          |

| $V_{IN^+} - V_{IN^-}$ | Input Differential Voltage Range    | $V_{IN} = V_{IN^+} - V_{IN^-}$ | ●   | 0       | $V_{REF}$       | V                          |

| $I_{IN}$              | Analog Input Leakage Current        |                                | ●   |         | $\pm 1$         | $\mu\text{A}$              |

| $C_{IN}$              | Analog Input Capacitance            | Sample Mode<br>Hold Mode       |     | 45<br>5 |                 | $\text{pF}$<br>$\text{pF}$ |

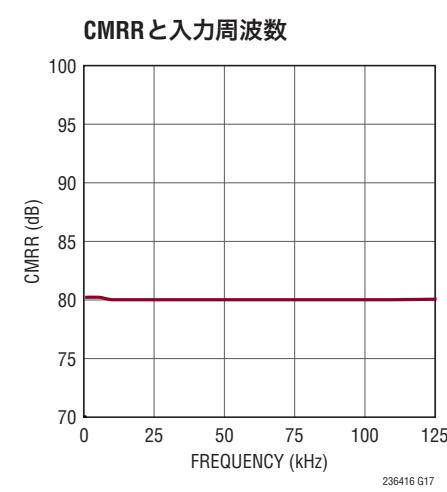

| CMRR                  | Input Common Mode Rejection Ratio   | $f_{IN} = 125\text{kHz}$       |     |         | 80              | dB                         |

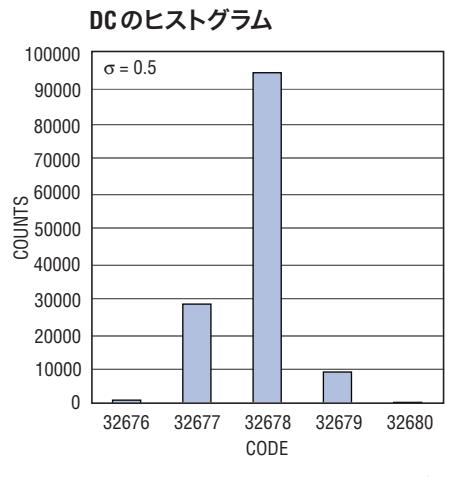

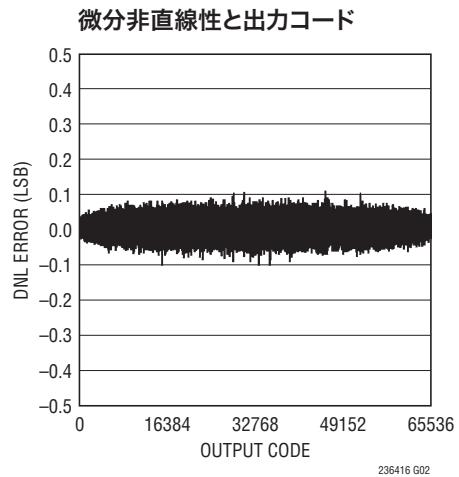

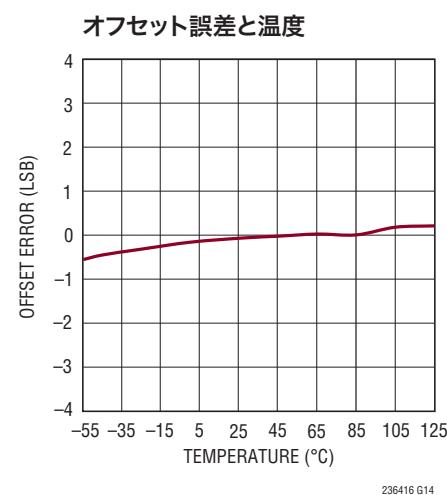

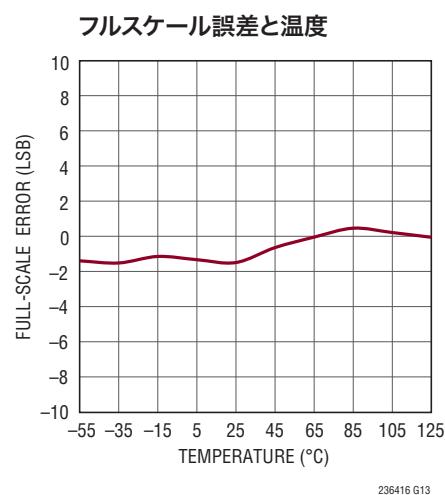

コンバータの特性 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL | PARAMETER                    | CONDITIONS | MIN | TYP   | MAX       | UNITS                       |

|--------|------------------------------|------------|-----|-------|-----------|-----------------------------|

|        | Resolution                   |            | ●   | 16    |           | Bits                        |

|        | No Missing Codes             |            | ●   | 16    |           | Bits                        |

|        | Transition Noise             |            |     | 0.5   |           | $\text{LSBRMS}$             |

| INL    | Integral Linearity Error     | (Note 6)   | ●   | -0.75 | $\pm 0.1$ | 0.75                        |

| DNL    | Differential Linearity Error |            | ●   | -0.5  | $\pm 0.1$ | 0.5                         |

| ZSE    | Zero-Scale Error             | (Note 7)   | ●   | -4    | 0         | 4                           |

|        | Zero-Scale Error Drift       |            |     | 4     |           | $\text{mLSB}^\circ\text{C}$ |

| FSE    | Full-Scale Error             | (Note 7)   | ●   | -20   | $\pm 2$   | 20                          |

|        | Full-Scale Error Drift       |            |     |       | $\pm 0.1$ | $\text{ppm}^\circ\text{C}$  |

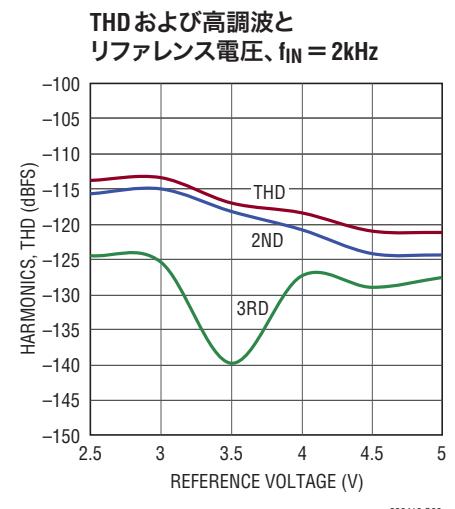

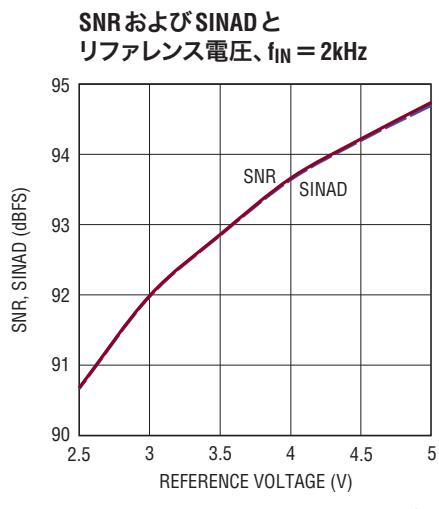

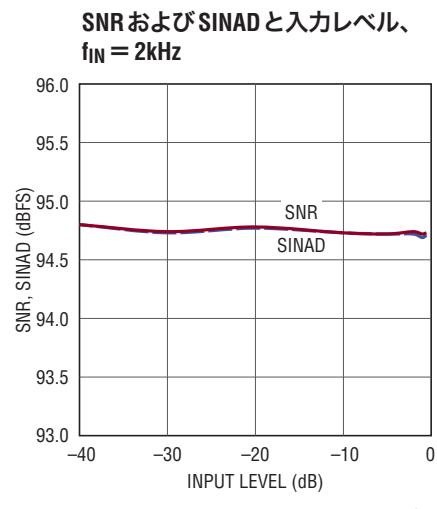

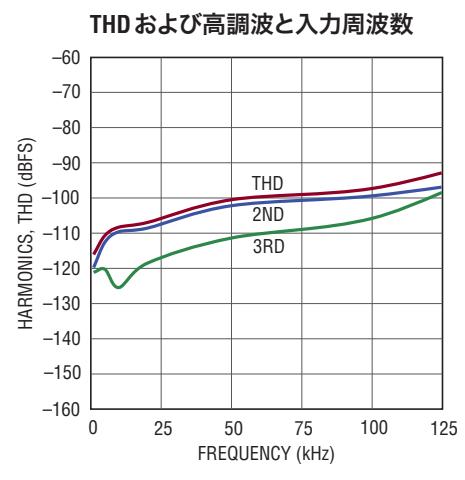

ダイナミック精度 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ 、 $A_{IN} = -1\text{dBFS}$ での値。(Note 4、8)

| SYMBOL | PARAMETER                            | CONDITIONS                                                   | MIN | TYP  | MAX  | UNITS         |

|--------|--------------------------------------|--------------------------------------------------------------|-----|------|------|---------------|

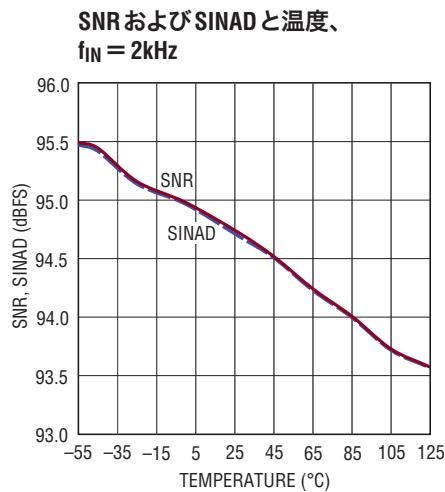

| SINAD  | Signal-to-(Noise + Distortion) Ratio | $f_{IN} = 2\text{kHz}$ , $V_{REF} = 5\text{V}$               | ●   | 91.9 | 94.7 | dB            |

|        |                                      | $f_{IN} = 2\text{kHz}$ , $V_{REF} = 5\text{V}$ , (H-Grade)   | ●   | 91.7 | 94.7 | dB            |

| SNR    | Signal-to-Noise Ratio                | $f_{IN} = 2\text{kHz}$ , $V_{REF} = 5\text{V}$               | ●   | 92.5 | 94.7 | dB            |

|        |                                      | $f_{IN} = 2\text{kHz}$ , $V_{REF} = 2.5\text{V}$             | ●   | 87.7 | 90.7 | dB            |

|        |                                      | $f_{IN} = 2\text{kHz}$ , $V_{REF} = 5\text{V}$ , (H-Grade)   | ●   | 92.2 | 94.7 | dB            |

|        |                                      | $f_{IN} = 2\text{kHz}$ , $V_{REF} = 2.5\text{V}$ , (H-Grade) | ●   | 87.3 | 90.7 | dB            |

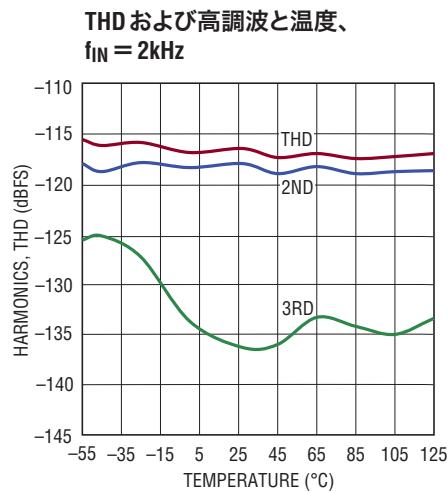

| THD    | Total Harmonic Distortion            | $f_{IN} = 2\text{kHz}$ , $V_{REF} = 5\text{V}$               | ●   | -120 | -102 | dB            |

|        |                                      | $f_{IN} = 2\text{kHz}$ , $V_{REF} = 2.5\text{V}$             | ●   | -120 | -102 | dB            |

| SFDR   | Spurious Free Dynamic Range          | $f_{IN} = 2\text{kHz}$ , $V_{REF} = 5\text{V}$               | ●   | 103  | 122  | dB            |

|        |                                      | -3dB Input Bandwidth                                         |     |      | 34   | MHz           |

|        | Aperture Delay                       |                                                              |     |      | 500  | ps            |

|        |                                      |                                                              |     |      | 4    | ps            |

|        |                                      | Transient Response                                           |     |      | 3.46 | $\mu\text{s}$ |

# LTC2364-16

リファレンスの入力 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL           | PARAMETER               | CONDITIONS | MIN | TYP  | MAX | UNITS |

|------------------|-------------------------|------------|-----|------|-----|-------|

| $V_{\text{REF}}$ | Reference Voltage       | (Note 5)   | ●   | 2.5  | 5.1 | V     |

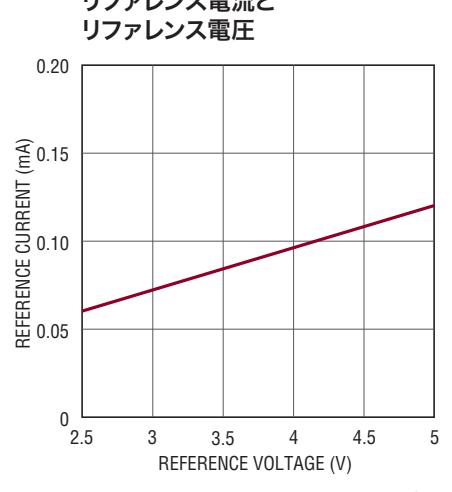

| $I_{\text{REF}}$ | Reference Input Current | (Note 9)   | ●   | 0.12 | 0.2 | mA    |

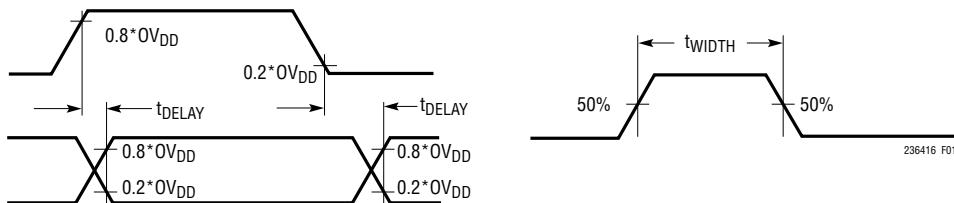

デジタル入力とデジタル出力 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL              | PARAMETER                   | CONDITIONS                                       | MIN | TYP                     | MAX                     | UNITS         |

|---------------------|-----------------------------|--------------------------------------------------|-----|-------------------------|-------------------------|---------------|

| $V_{\text{IH}}$     | High Level Input Voltage    |                                                  | ●   | 0.8 • 0 $V_{\text{DD}}$ |                         | V             |

| $V_{\text{IL}}$     | Low Level Input Voltage     |                                                  | ●   |                         | 0.2 • 0 $V_{\text{DD}}$ | V             |

| $I_{\text{IN}}$     | Digital Input Current       | $V_{\text{IN}} = 0\text{V}$ to $0V_{\text{DD}}$  | ●   | -10                     | 10                      | $\mu\text{A}$ |

| $C_{\text{IN}}$     | Digital Input Capacitance   |                                                  |     | 5                       |                         | pF            |

| $V_{\text{OH}}$     | High Level Output Voltage   | $I_{\text{O}} = -500\mu\text{A}$                 | ●   | 0 $V_{\text{DD}}$ - 0.2 |                         | V             |

| $V_{\text{OL}}$     | Low Level Output Voltage    | $I_{\text{O}} = 500\mu\text{A}$                  | ●   |                         | 0.2                     | V             |

| $I_{\text{OZ}}$     | Hi-Z Output Leakage Current | $V_{\text{OUT}} = 0\text{V}$ to $0V_{\text{DD}}$ | ●   | -10                     | 10                      | $\mu\text{A}$ |

| $I_{\text{SOURCE}}$ | Output Source Current       | $V_{\text{OUT}} = 0\text{V}$                     |     |                         | -10                     | mA            |

| $I_{\text{SINK}}$   | Output Sink Current         | $V_{\text{OUT}} = 0V_{\text{DD}}$                |     |                         | 10                      | mA            |

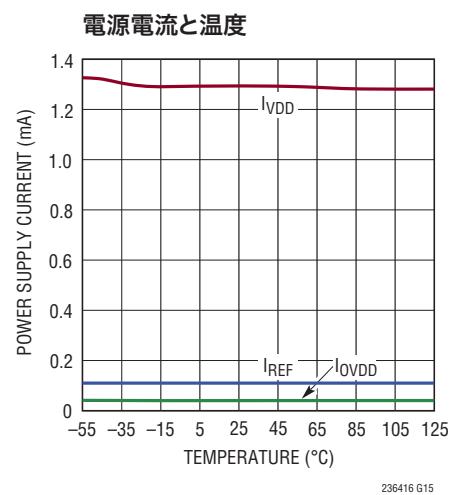

電源要件 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 4)。

| SYMBOL            | PARAMETER         | CONDITIONS                                                                                                      | MIN | TYP   | MAX  | UNITS         |   |

|-------------------|-------------------|-----------------------------------------------------------------------------------------------------------------|-----|-------|------|---------------|---|

| $V_{\text{DD}}$   | Supply Voltage    |                                                                                                                 | ●   | 2.375 | 2.5  | 2.625         | V |

| $0V_{\text{DD}}$  | Supply Voltage    |                                                                                                                 | ●   | 1.71  |      | 5.25          | V |

| $I_{\text{VDD}}$  | Supply Current    | 250ksps Sample Rate                                                                                             | ●   | 1.36  | 1.7  | mA            |   |

| $I_{\text{OVDD}}$ | Supply Current    | 250ksps Sample Rate ( $C_L = 20\text{pF}$ )                                                                     | ●   | 0.1   |      | mA            |   |

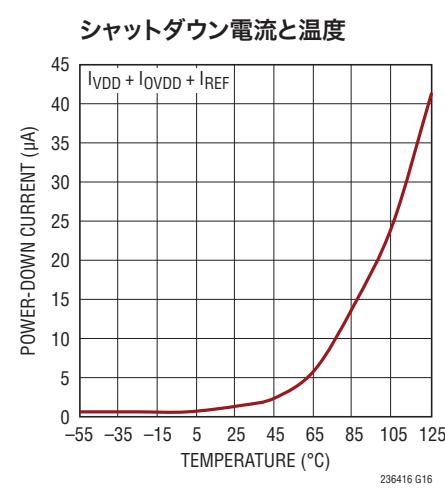

| $I_{\text{PD}}$   | Power Down Mode   | Conversion Done ( $I_{\text{VDD}} + I_{\text{OVDD}} + I_{\text{REF}}$ , $V_{\text{REF}} > 2\text{V}$ )          | ●   | 0.9   | 90   | $\mu\text{A}$ |   |

| $I_{\text{PD}}$   | Power Down Mode   | Conversion Done ( $I_{\text{VDD}} + I_{\text{OVDD}} + I_{\text{REF}}$ , $V_{\text{REF}} > 2\text{V}$ , H-Grade) | ●   | 0.9   | 140  | $\mu\text{A}$ |   |

| $P_{\text{D}}$    | Power Dissipation | 250ksps Sample Rate                                                                                             |     | 3.4   | 4.25 | $\text{mW}$   |   |

|                   | Power Down Mode   | Conversion Done ( $I_{\text{VDD}} + I_{\text{OVDD}} + I_{\text{REF}}$ , $V_{\text{REF}} > 2\text{V}$ )          |     | 2.25  | 225  | $\mu\text{W}$ |   |

|                   | Power Down Mode   | Conversion Done ( $I_{\text{VDD}} + I_{\text{OVDD}} + I_{\text{REF}}$ , $V_{\text{REF}} > 2\text{V}$ , H-Grade) |     | 2.25  | 315  | $\mu\text{W}$ |   |

ADCのタイミング特性 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL              | PARAMETER                          | CONDITIONS                                                    | MIN | TYP   | MAX | UNITS         |

|---------------------|------------------------------------|---------------------------------------------------------------|-----|-------|-----|---------------|

| $f_{\text{SMPL}}$   | Maximum Sampling Frequency         |                                                               | ●   |       | 250 | ksps          |

| $t_{\text{CONV}}$   | Conversion Time                    |                                                               | ●   | 1.9   | 3   | $\mu\text{s}$ |

| $t_{\text{ACQ}}$    | Acquisition Time                   | $t_{\text{ACQ}} = t_{\text{CYC}} - t_{\text{HOLD}}$ (Note 10) | ●   | 3.460 |     | $\mu\text{s}$ |

| $t_{\text{HOLD}}$   | Maximum Time Between Acquisitions  |                                                               | ●   |       | 540 | ns            |

| $t_{\text{CYC}}$    | Time Between Conversions           |                                                               | ●   | 4     |     | $\mu\text{s}$ |

| $t_{\text{CNVH}}$   | CNV High Time                      |                                                               | ●   | 20    |     | ns            |

| $t_{\text{BUSYLH}}$ | CNV $\uparrow$ to BUSY Delay       | $C_L = 20\text{pF}$                                           | ●   |       | 13  | ns            |

| $t_{\text{CNVL}}$   | Minimum Low Time for CNV           | (Note 11)                                                     | ●   | 20    |     | ns            |

| $t_{\text{QUIET}}$  | SCK Quiet Time from CNV $\uparrow$ | (Note 10)                                                     | ●   | 20    |     | ns            |

ADCのタイミング特性 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL         | PARAMETER                              | CONDITIONS                                     | MIN    | TYP | MAX | UNITS |

|----------------|----------------------------------------|------------------------------------------------|--------|-----|-----|-------|

| $t_{SCK}$      | SCK Period                             | (Note 11, 12)                                  | ● 10   |     |     | ns    |

| $t_{SCKH}$     | SCK High Time                          |                                                | ● 4    |     |     | ns    |

| $t_{SCKL}$     | SCK Low Time                           |                                                | ● 4    |     |     | ns    |

| $t_{SSDISCK}$  | SDI Setup Time From SCK↑               | (Note 11)                                      | ● 4    |     |     | ns    |

| $t_{HSDISCK}$  | SDI Hold Time From SCK↑                | (Note 11)                                      | ● 1    |     |     | ns    |

| $t_{SCKCH}$    | SCK Period in Chain Mode               | $t_{SCKCH} = t_{SSDISCK} + t_{DSDO}$ (Note 11) | ● 13.5 |     |     | ns    |

| $t_{DSDO}$     | SDO Data Valid Delay from SCK↑         | $C_L = 20\text{pF}$ (Note 11)                  | ●      |     | 9.5 | ns    |

| $t_{HSDO}$     | SDO Data Remains Valid Delay from SCK↑ | $C_L = 20\text{pF}$ (Note 10)                  | ● 1    |     |     | ns    |

| $t_{DSDOBUSY}$ | SDO Data Valid Delay from BUSY↓        | $C_L = 20\text{pF}$ (Note 10)                  | ●      |     | 5   | ns    |

| $t_{EN}$       | Bus Enable Time After RDL↓             | (Note 11)                                      | ●      |     | 16  | ns    |

| $t_{DIS}$      | Bus Relinquish Time After RDL↑         | (Note 11)                                      | ●      |     | 13  | ns    |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** すべての電圧値はグランドを基準にしている。

**Note 3:** これらのピンの電圧がグランドを下回るか、REFまたは $0V_{DD}$ を上回ると、内部のダイオードによってクランプされる。この製品は、グランドを下回るか、REFまたは $0V_{DD}$ を上回った場合でも、ラッチアップを生じることなく最大100mAの入力電流を処理することができる。

**Note 4:**  $V_{DD} = 2.5\text{V}$ ,  $0V_{DD} = 2.5\text{V}$ ,  $REF = 5\text{V}$ ,  $f_{SMPL} = 250\text{kHz}$

**Note 5:** 推奨動作条件。

**Note 6:** 積分非直線性は、実際の伝達曲線のエンドポイントを通る直線からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

**Note 7:** ゼロスケール誤差は、出力コードが0000 0000 0000 0000と0000 0000 0000 0001の間を行ったり来たりするとき、0.5LSBから測定されたオフセット電圧である。フルスケール誤差は、最後のコード遷移の理想値からの偏差であり、オフセット誤差の影響を含む。

**Note 8:** dB表示のすべての規格値は、5Vのリファレンス電圧の場合、フルスケールの5V入力を基準にしている。

**Note 9:**  $f_{SMPL} = 250\text{kHz}$ ,  $I_{REF}$ はサンプル・レートに比例して変化する。

**Note 10:** 設計によって保証されているが、テストされない。

**Note 11:** パラメータは $0V_{DD} = 1.71\text{V}$ ,  $0V_{DD} = 2.5\text{V}$ および $0V_{DD} = 5.25\text{V}$ でテストされ、保証されている。

**Note 12:** 立ち上がりで捕捉する場合、最大10nsの $t_{SCK}$ により最大100MHzのシフトクロック周波数が可能である。

図1. タイミングの仕様の電圧レベル

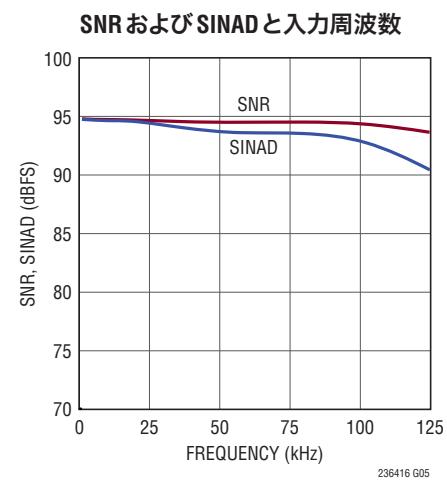

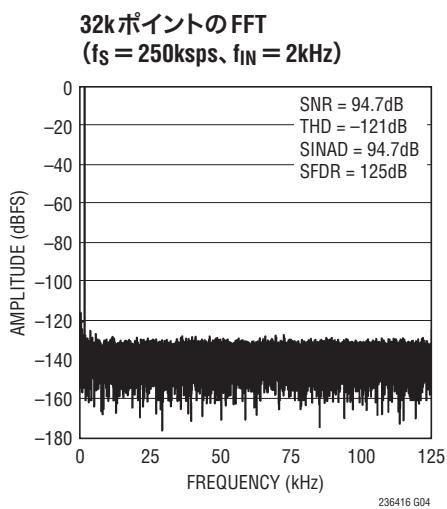

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 2.5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、 $REF = 5\text{V}$ 、 $f_{SMPL} = 250\text{ksps}$ 。

**標準的性能特性** 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 2.5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、 $\text{REF} = 5\text{V}$ 、 $f_{\text{SMPL}} = 250\text{ksps}$ 。

## ピン機能

**CHAIN (ピン1)** : チェーン・モード選択ピン。“L”的とき、LTC2364-16は通常モードで動作し、RDL/SDI入力ピンはSDOをイネーブルまたはディスエーブルします。“H”的とき、LTC2364-16はチェーン・モードで動作し、RDL/SDIピンはSDI(デイジーチェーンのシリアル・データ入力)として機能します。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**V<sub>DD</sub>(ピン2)** : 2.5V電源。V<sub>DD</sub>の範囲は2.375V～2.625Vです。V<sub>DD</sub>ピンは10μFのセラミック・コンデンサを使ってGNDにバイパスします。

**GND(ピン3、6、10、16)** : グランド。

**IN<sup>+</sup>(ピン4)** : アナログ入力。IN<sup>+</sup>-IN<sup>-</sup>の範囲が0V～V<sub>REF</sub>の条件で、IN<sup>+</sup>はIN<sup>-</sup>に対して差動で動作します。

**IN<sup>-</sup>(ピン5)** : アナログ・グランド検出。IN<sup>-</sup>の入力範囲はGNDを基準にして±100mVであり、グランド・プレーンまたは離れた場所のグランド検出箇所に接続する必要があります。

**REF(ピン7、8)** : リファレンス入力。REFの範囲は2.5V～5.1Vです。このピンはGNDピンを基準にしており、47μFのセラミック・コンデンサ(X5R、0805のサイズ)を使ってピンの近くでデカッピングします。

**CNV(ピン9)** : 変換入力。この入力の立ち上がりエッジによってデバイスがパワーアップされ、新しい変換が開始されます。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**BUSY(ピン11)** : BUSYのインジケータ。新しい変換が開始されると“H”になり、変換が終了すると“L”に戻ります。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**RDL/SDI(ピン12)** : CHAINが“L”的とき、デバイスは通常モードになり、RDL/SDIピンはバス・イネーブル入力として扱われます。CHAINが“H”的とき、デバイスはチェーン・モードになり、RDL/SDIピンはシリアル・データ入力ピンとして扱われ、デイジーチェーン内の別のADCからのデータが入力されます。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**SCK(ピン13)** : シリアル・データ・クロック入力。SDOがイネーブルされていると、変換結果または別のADCからのデイジーチェーン・データが、このクロックの立ち上がりエッジで、MSBを先頭にしてシフトアウトされます。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**SDO(ピン14)** : シリアル・データ出力。変換結果またはデイジーチェーン・データは、SCKの各立ち上がりエッジでMSBを先頭にしてこのピンから出力されます。出力データはストレート・バイナリ形式です。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**OV<sub>DD</sub>(ピン15)** : I/Oインターフェースのデジタル電源。OV<sub>DD</sub>の範囲は1.71V～5.25Vです。この電源の公称値は、ホストのインターフェースと同じ電源電圧に設定されます(1.8V、2.5V、3.3V、または5V)。OV<sub>DD</sub>ピンは、0.1μFのコンデンサを使ってGNDにバイパスします。

**GND(露出パッド・ピン17、DFNパッケージのみ)** : グランド。露出パッドはグランド・プレーンに直接半田付けする必要があります。

## 機能ブロック図

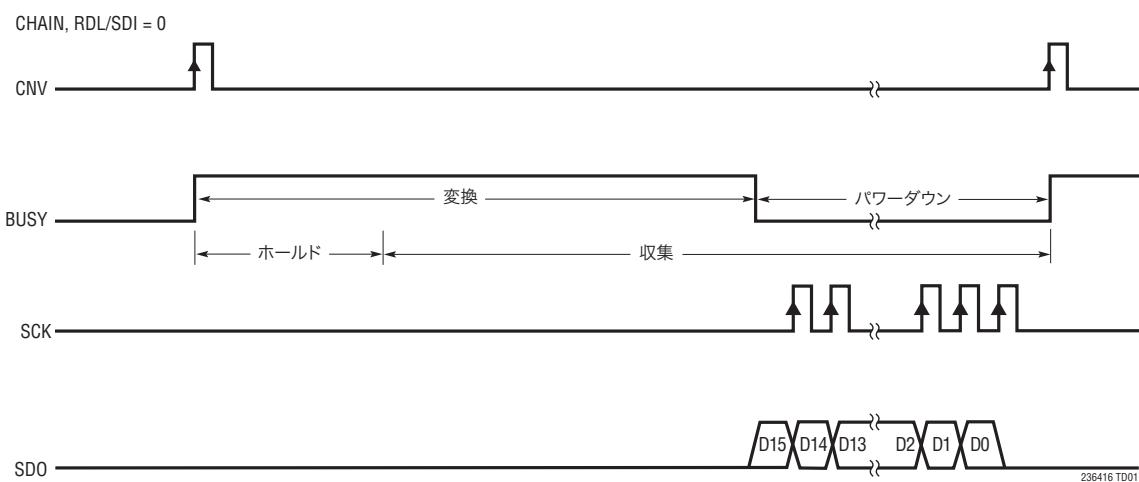

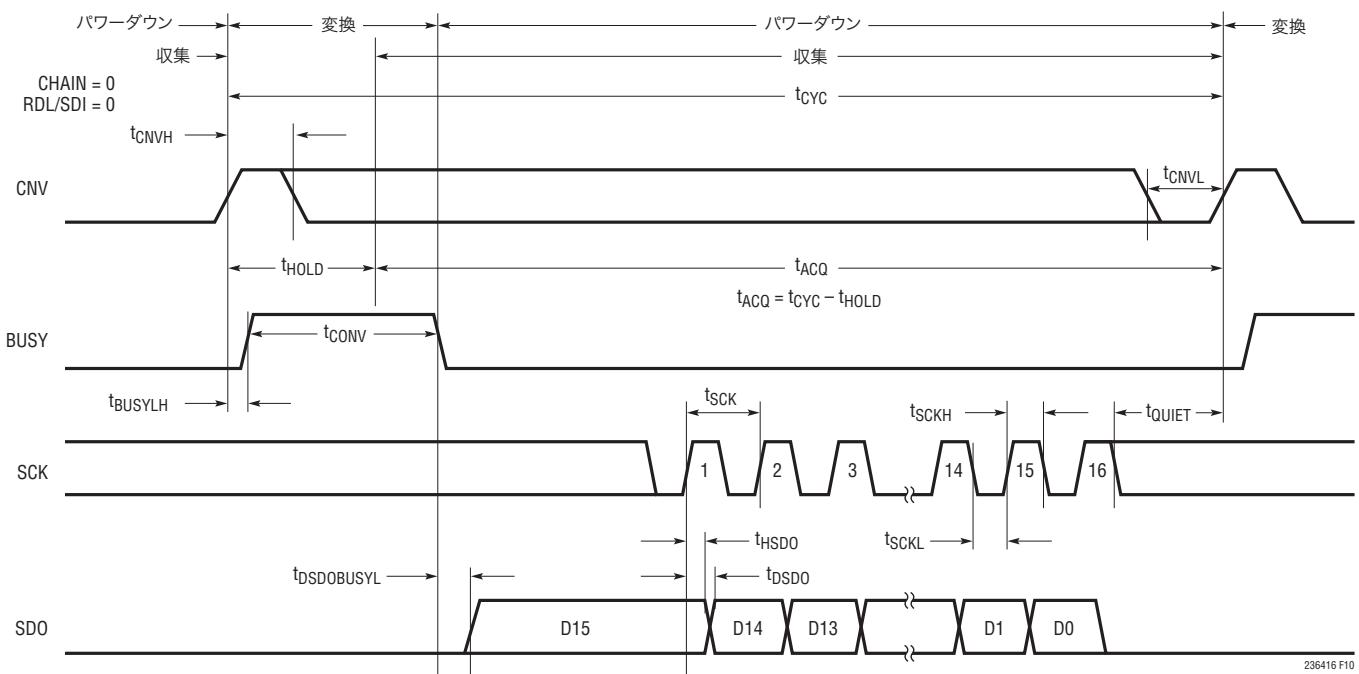

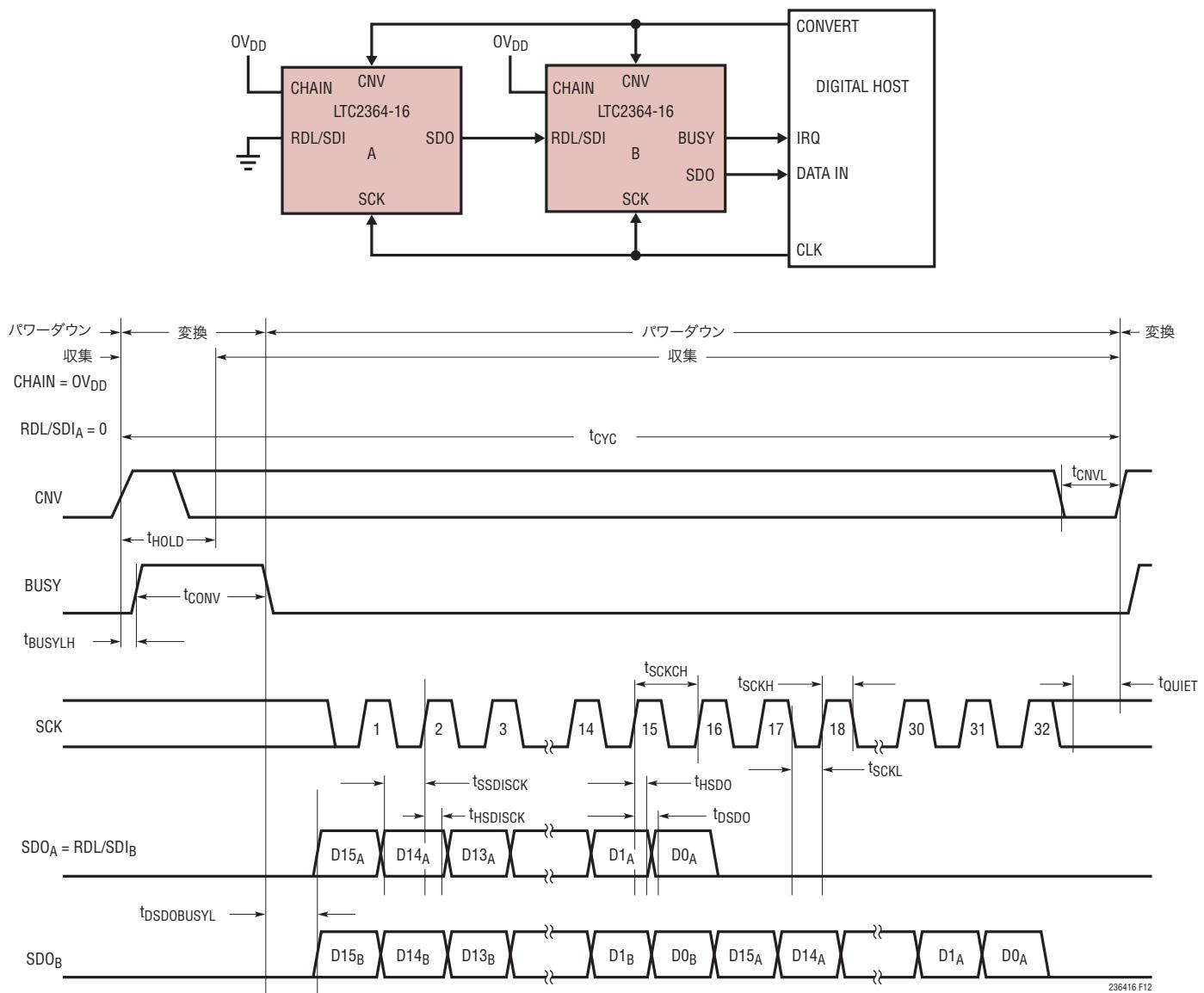

## タイミング図

シリアル・インターフェースを使った変換タイミング

## アプリケーション情報

### 概要

LTC2364-16は低ノイズ、低消費電力の高速16ビット逐次比較レジスタ(SAR)ADCです。LTC2364-16は単一2.5V電源で動作し、2.5V～5.1Vの範囲のV<sub>REF</sub>に対して0V～V<sub>REF</sub>の疑似差動ユニポーラ入力範囲をサポートしているので、広いダイナミックレンジを必要とする高性能アプリケーションに最適です。LTC2364-16は最大±0.75 LSBのINLと94.7dBのSNRを達成し、16ビット分解能でミッシング・コードはありません。

サイクル待ち時間がなく、スループットが250kspsと高速なので、様々な高速アプリケーションに最適です。内部発振器が変換時間を設定するので、外部のタイミングの問題が緩和されます。LTC2364-16が250kspsで消費する電力は3.4mWに過ぎない上に、自動パワーダウン機能を備えており、アクティブでない期間の電力損失はさらに減少します。

### コンバータの動作

LTC2364-16は2フェーズで動作します。収集フェーズでは、疑似差動アナログ入力電圧をサンプリングするために、IN<sup>+</sup>ピンとIN<sup>-</sup>ピンに電荷再配分コンデンサD/Aコンバータ(CDAC)が接続されます。CNVピンの立ち上がりエッジにより変換が開始されます。変換フェーズでは、16ビットCDACが逐次比較アルゴリズムを通じてシーケンス制御され、差動コンパレータを使用してサンプル入力とリファレンス電圧のバイナリ加重した部分(例:V<sub>REF</sub>/2、V<sub>REF</sub>/4...V<sub>REF</sub>/65536)を効率的に比較します。変換の最後には、CDACの出力はサンプリングされたアナログ入力に近似します。次に、ADC制御ロジックが、シリアル転送用の16ビット・デジタル出力コードを準備します。

### 伝達関数

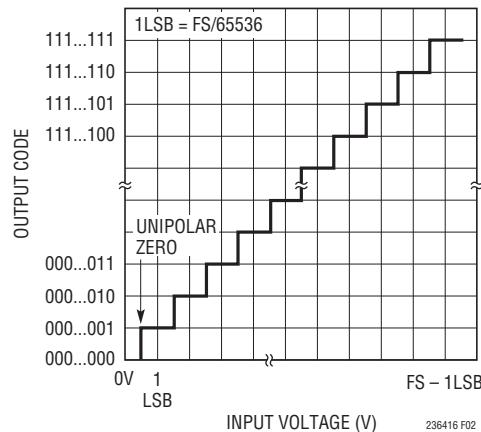

LTC2364-16はREFのフルスケール電圧を2<sup>16</sup>レベルにデジタル化するので、REF = 5Vでは1LSBの大きさが76μVになります。理想的な伝達関数を図2に示します。出力データはストレート・バイナリ形式です。

図2. LTC2364-16の伝達関数

### アナログ入力

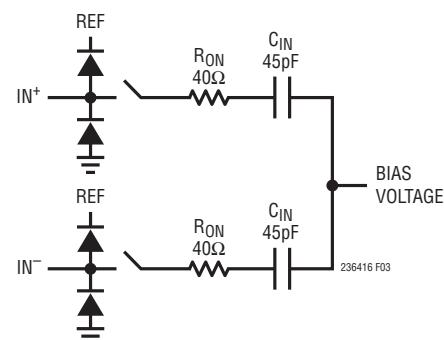

LTC2364-16のアナログ入力は、両方の入力に共通する不要な信号を低減するために疑似差動となっています。このアナログ入力は、図3に示す等価回路によってモデル化できます。入力のダイオードはESD保護機能を提供します。収集フェーズでは、サンプリングCDACに起因する約45pF(C<sub>IN</sub>)と、サンプリング・スイッチのオン抵抗に起因する40Ω(R<sub>ON</sub>)が各入力に直列に存在します。収集時にC<sub>IN</sub>コンデンサを充電するとき、IN<sup>+</sup>入力には電流スパイクが流れます。変換時にアナログ入力に流れるのはわずかなリーク電流だけです。

図3. LTC2364-16の差動アナログ入力の等価回路

## アプリケーション情報

### 入力ドライブ回路

低インピーダンスのソースは、利得誤差なしに、LTC2364-16の高インピーダンス入力を直接ドライブすることができます。高インピーダンス・ソースは、収集時のセトリング時間を最小にするためとADCの歪み性能を最適化するために、バッファする必要があります。収集を開始するときADCの入力に電流スパイクが流れるので、DC入力であっても、セトリング時間の最小化は重要です。

最良の性能を得るには、バッファ・アンプを使用してLTC2364-16のアナログ入力をドライブする必要があります。このアンプの出力インピーダンスは低いので、収集フェーズでアナログ信号の高速セトリングを実現できます。また、このアンプは、信号源を、ADCの入力に流れる電流スパイクから絶縁します。

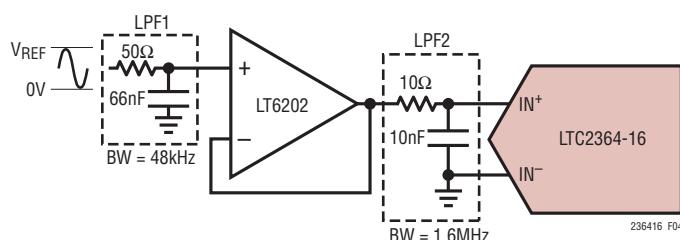

### 入力フィルタリング

バッファ・アンプと信号源のノイズと歪みはADCのノイズと歪みに加わるので、これらについても考慮しなければなりません。ノイズの多い入力信号は、バッファ・アンプの入力の前で適切なフィルタを使ってノイズを最小に抑える必要があります。多くのアプリケーションでは、図4に示されている簡単な1ポールのRCローパス・フィルタ(LPF1)で十分です。

図4. 入力信号チェーン

LPF2で構成される別のフィルタ・ネットワークをバッファとADCの入力の間に使って、ノイズに対するバッファの影響を最小に抑え、同時にサンプリング過渡変動からバッファに反射される搅乱を最小に抑えます。アナログ入力のRC時定数が大きいと、アナログ入力のセトリング時間が長くなります。したがって、LPF2はLPF1より広い帯域幅を必要とします。ノイズ密度の低いバッファ・アンプを選択して、SNRの劣化を最小に抑える必要があります。

RCフィルタのコンデンサと抵抗は歪みを大きくする可能性があるので、これらの部品は高品質のものを使用します。NPOタイプやシルバーマイカ・タイプの誘電体コンデンサはすぐれた直線性を示します。表面実装カーボン抵抗は、自己発熱や半田工程で生じる損傷により歪みを生じることがあります。表面実装金属皮膜抵抗は、両方の問題に対してはるかに耐性があります。

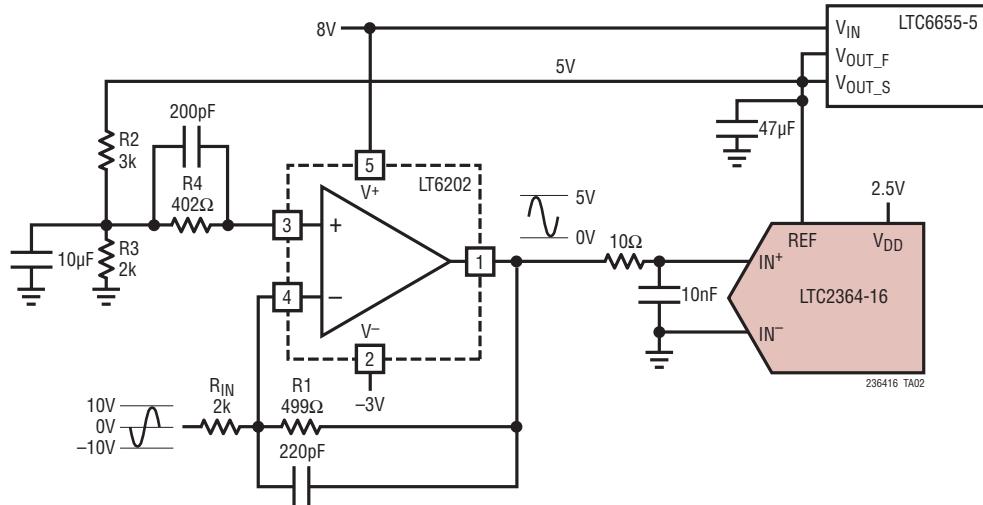

### 疑似差動ユニポーラ入力

ほとんどのアプリケーションでは、低消費電力のADCドライバであるLT6202でLTC2364-16をドライブすることを推奨します。LT6202はノイズ密度が $1.9\text{nV}/\sqrt{\text{Hz}}$ と低く、電源電流が3mAと小さいので、柔軟性があり、さまざまな振幅の信号をLTC2364-16の0V～5Vの入力範囲に変換するように構成できます。

LTC2364-16の最大限の歪み性能を実現するために、図4に示すようにユニティゲイン・バッファとして構成されたLT6202を介してドライブされる低歪みのシングルエンド信号源を使って、データシートで規定された-120dBのTHDを達成することができます。

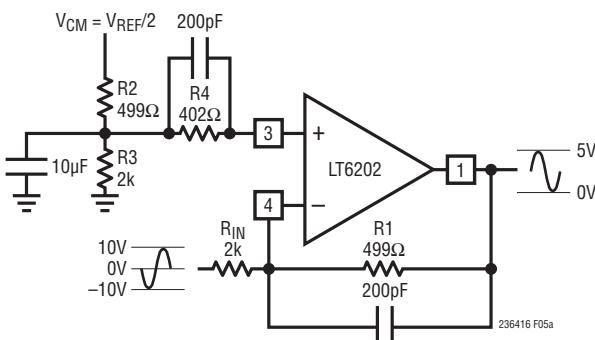

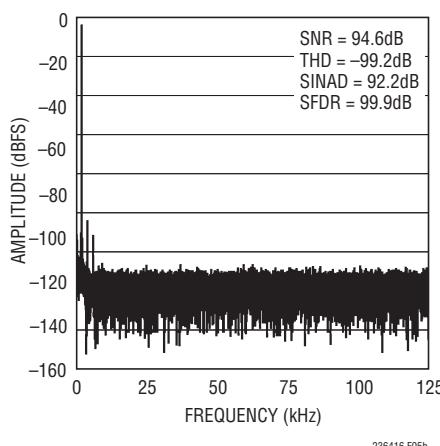

LT6202を使用すると、グランドより低い電位まで振幅する大きな真のバイポーラ信号をバッファして、LTC2364-16の入力範囲である0V～5Vに変換することもできます。 $\pm 10\text{V}$ の真のバイポーラ信号をLTC2364-16で使えるように変換する目的で使用されるLT6202を図5aに示します。この場合、LT6202は反転アンプ段として構成され、入力信号をLTC2364-16の0V～5Vの入力範囲まで減衰させてレベルシフトする役割を果たします。反転構成では、シングルエンドの入力信号源が高インピーダンス入力を直接ドライブすることはありません。代わりに、入力インピーダンスは抵抗 $R_{IN}$ によって設定されます。 $R_{IN}$ は、信号源のソース・インピーダンスに基づいて、注意して選択する必要があります。 $R_{IN}$ の値が高いと、システムとしてのLT6202とLTC2364-16のノイズと歪みの両方が悪化する傾向があります。この構成の $R_{IN}$ 、 $R1$ 、 $R2$ 、 $R3$ および $R4$ のいくつかの値に対するSNRとTHDを表1に示します。図5aに示されているようにLT6202を使用したときのFFTを図5bに示します。

## アプリケーション情報

図5a.  $\pm 10V$ のバイポーラ信号を

$0V \sim 5V$ の入力信号に変換するLT6202

図5b. 図5aに示されている回路の

32kポイントのFFTプロット ( $f_{IN} = 2\text{kHz}$ )

表1. 入力信号が $\pm 10\text{V}$ の場合のSNRおよびTHDと $R_{IN}$

| R <sub>IN</sub><br>(Ω) | R1<br>(Ω) | R2<br>(Ω) | R3<br>(Ω) | R4<br>(Ω) | SNR<br>(dB) | THD<br>(dB) |

|------------------------|-----------|-----------|-----------|-----------|-------------|-------------|

| 2k                     | 499       | 499       | 2k        | 402       | 94.6        | -99.2       |

| 10k                    | 2.49k     | 2.49k     | 10k       | 2k        | 94.4        | -93.8       |

| 100k                   | 24.9k     | 24.9k     | 100k      | 20k       | 92.4        | -93.7       |

## ADCのリファレンス

LTC2364-16はその入力範囲を定めるのに外部リファレンスを必要とします。このADCのデータシートで規定されている性能を完全に実現するには、低ノイズ、低温度ドリフトのリファレンスが不可欠です。リニアテクノロジーは多くのアプリケーションの要求を満たすように設計された高性能リファレンスの品揃えを提供しています。LTC6655-5は小型、低消費電力、高精度なので、LTC2364-16と一緒に使用するのに特に適しています。LTC6655-5の初期精度は0.025%（最大）、温度係数は2ppm/°C（最大）で、高精度アプリケーションに適しています。LTC6655-5はHグレードの温度範囲で完全に規定されており、LTC2364-16の最大125°Cの拡張温度範囲での動作を補完します。47µFのセラミック・コンデンサ（X5R、0805のサイズ）をREFピンの近くに配置して、LTC6655-5をバイパスすることを推奨します。

LTC2364-16のREFピンには、各変換サイクルの間 $47\mu\text{F}$ のバイパス・コンデンサから電荷( $Q_{\text{CONV}}$ )が流れます。リファレンスはこの電荷をDC電流( $I_{\text{REF}} = Q_{\text{CONV}}/t_{\text{CYC}}$ )で補充します。REFピンのDC電流( $I_{\text{REF}}$ )はサンプリング・レートと出力コードに依存します。LTC2364-16を使って信号を一定のレートで連続的にサンプリングする場合、LTC6655-5は全コード範囲でリファレンス電圧の偏差を $0.5\text{LSB}$ 未満に保ちます。

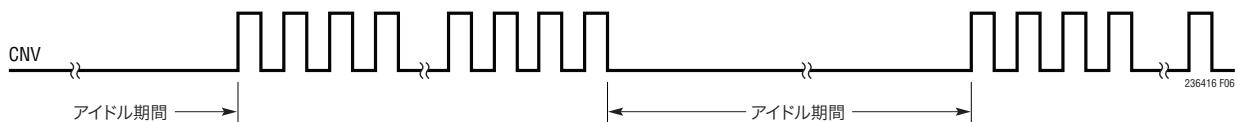

アイドル時には、LTC2364-16のREFピンには微小なリーク電流(1 $\mu$ A未満)が流れるだけです。図6に示すように、長時間のアイドル状態の後、バースト状にサンプリングされるアプリケーションでは、 $I_{REF}$ は短時間で約0 $\mu$ Aから最大0.2mA(250ksps)になります。このDC電流のステップによりリファレンスの過渡応答がトリガされます。リファレンスの出力電

図6. バースト・サンプリングを示すCNVの波形

## アプリケーション情報

圧のどんな偏差も出力コードの精度に影響を与えるので、この過渡応答を考慮する必要があります。リファレンスの過渡応答が重要なアプリケーションでは、高速でセトリングする LTC6655-5 リファレンスを推奨します。

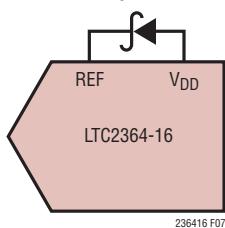

パワーマネージメントが不可欠で、外部リファレンスがパワーダウンされる可能性のあるアプリケーションでは、140 $\mu$ A の最大シャットダウン電流を保証するために、REF の電圧を 2V より高くしておくことを推奨します。このようなアプリケーションでは、図7に示すように、ショットキ・ダイオードを REF と V<sub>DD</sub> の間に配置することができます。

図7. リファレンスがパワーダウンされる可能性のあるアプリケーションでは、REF と V<sub>DD</sub> 間のショットキ・ダイオードにより REF > 2V を維持する

## ダイナミック性能

ADC の定格スループットでの周波数応答、歪み、およびノイズをテストするには、高速フーリエ変換(FFT)の手法が使われます。低歪みの正弦波を与えてそのデジタル出力をFFTアルゴリズムを用いて解析することにより、基本波の外側の周波数に関して ADC のスペクトルの内容を調べることができます。LTC2364-16 の AC 歪みの測定値とノイズの測定値は、保証されたテスト済みの限界値です。

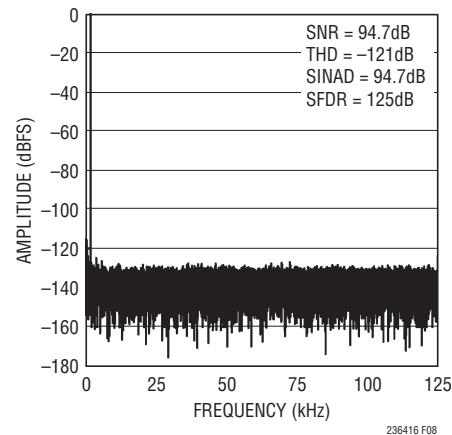

### 信号対ノイズ+歪み比(SINAD)

信号対ノイズ+歪み比(SINAD)は、基本入力周波数の RMS 振幅と ADC の出力の他のすべての周波数成分の RMS 振幅の比です。出力の帯域は、DC より高くサンプリング周波数の半分より低い周波数に制限されます。図8は、LTC2364-16 が 2kHz の入力、250kHz のサンプリング・レートで 94.7dB の標準 SINAD を達成していることを示しています。

### 信号対ノイズ比(SNR)

信号対ノイズ比(SNR)は、基本入力周波数の RMS 振幅と、最初の 5 つの高調波と DC を除く他のすべての周波数成分の RMS 振幅の比です。図8は、LTC2364-16 が 2kHz の入力、

250kHz のサンプリング・レートで 94.7dB の標準 SNR を達成していることを示しています。

図8. LTC2364-16 の 32k ポイントの FFT ( $f_{IN} = 2\text{kHz}$ )

## 全高調波歪み(THD)

全高調波歪み(THD)は、入力信号のすべての高調波の二乗和平方根と基本波の RMS 値との比です。帯域外高調波は、DC とサンプリング周波数の半分 ( $f_{SAMPL}/2$ ) の間の周波数帯域でエイリアスを生じます。THD は次のように表されます。

$$\text{THD} = 20 \log \frac{\sqrt{V2^2 + V3^2 + V4^2 + \dots + V_N^2}}{V1}$$

ここで、V1 は基本周波数の RMS 振幅で、V2 ~ V<sub>N</sub> は 2 次 ~ N 次の高調波の振幅です。

## 電力に関する検討事項

LTC2364-16 は 2 つの電源ピンを備えています。2.5V 電源 (V<sub>DD</sub>) とデジタル入力/出力インターフェースの電源 (OV<sub>DD</sub>) です。柔軟性の高い OV<sub>DD</sub> 電源により、LTC2364-16 は、2.5V と 3.3V のシステムを含む、1.8V ~ 5V で動作するどんなデジタル・ロジックとも通信することができます。

### 電源シーケンス制御

LTC2364-16 には電源シーケンス制御に関する特別な要件はありません。「絶対最大定格」のセクションに記載されている最大電圧の関係を遵守するよう注意する必要があります。LTC2364-16 はパワーオン・リセット(POR)回路を備えています。

## アプリケーション情報

これにより、LTC2364-16は最初の電源投入時か、または電源電圧が1Vを下回るたびにリセットされます。電源電圧が公称電源電圧範囲に戻ると、PORはADCを再度初期化します。再初期化の期間が確実に終了するように、PORイベントの20 $\mu$ s後までは変換を開始しないようにします。この時点より前に変換を開始すると、結果が無効になります。

## タイミングと制御

### CNVのタイミング

LTC2364-16の変換はCNVによって制御されます。CNVの立ち上がりエッジで変換が開始され、LTC2364-16がパワーアップします。一度変換が開始されると、変換が完了するまで再度開始することはできません。最適性能を得るには、CNVをクリーンな低ジッタ信号でドライブします。コンバータの状態はBUSY出力で示され、変換の進行中はこの出力が“H”に保たれます。デジタル化された結果にエラーが生じないようにするには、CNVのどんな追加の遷移も、変換開始後40ns以内または変換完了後に発生するようにします。変換が完了すると、LTC2364-16はパワーダウンして入力信号の収集を開始します。

## 収集

独自のサンプリング・アーキテクチャにより、LTC2364-16は現在の変換の開始から527ns後に次の変換のための入力信号の収集を開始することができます。これにより、収集時間が3.460 $\mu$ sに延びるので、セトリング要件が緩和され、非常に低消費電力のADCドライバを使用することができます。（「タイミング図」を参照）

## 内部変換クロック

LTC2364-16には内部クロックが備わっており、最大変換時間が3 $\mu$ sになるように調整されています。

## 自動パワーダウン

LTC2364-16は変換完了後自動的にパワーダウンし、CNVの立ち上がりエッジで新しい変換が開始されるとパワーアップします。パワーダウンの間に、最後の変換のデータをクロックアウトすることができます。パワーダウンの間の電力損失を最小に抑えるには、SDOをディスエーブルし、SCKをオフします。

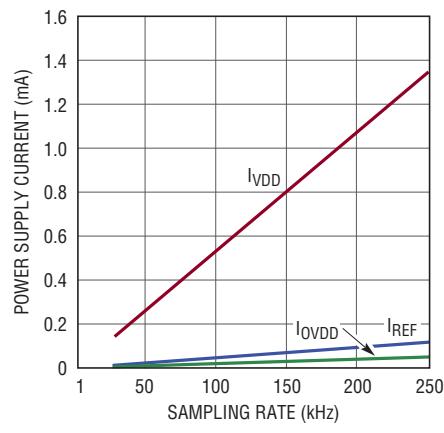

自動パワーダウン機能により、サンプリング周波数が低下するのに伴って、LTC2364-16の電力損失が減少します。電力が消費されるのは変換中だけなので、サンプリング・レートが低いほど、変換サイクル(tcYCY)の大きな部分でパワーダウン状態に留まることができます。そのため平均電力損失は図9に示すようにサンプリング・レートに比例して減少します。

図9. LTC2364-16の電源電流とサンプリング・レート

## デジタル・インターフェース

LTC2364-16はシリアル・デジタル・インターフェースを備えています。柔軟性の高いOV<sub>DD</sub>電源により、LTC2364-16は、2.5Vと3.3Vのシステムを含む、1.8V～5Vで動作するどんなデジタル・ロジックとも通信することができます。

SDOがイネーブルされているとき、外部クロックがSCKピンに与えられると、シリアル出力データがSDOピンからクロックアウトされます。変換後にデータをクロックアウトすると、最良の性能が得られます。少なくとも20MHzのシフトクロック周波数では、250kspsのスループットが依然達成されます。シリアル出力データはSCKの立ち上がりエッジで状態を変え、SCKの立ち下がりエッジまたは次の立ち上がりエッジで捕捉することができます。D15はSCKの最初の立ち上がりエッジまで有効なまま保たれます。

LTC2364-16のシリアル・インターフェースはシンプルで使うのが簡単です。以下のセクションでは、LTC2364-16の動作について説明します。単一のADCが使用されているか、それとも複数

## タイミング図

のADCがSPIバスを共有しているか、またはデイジーチェーン接続されているかにより、いくつかのモードが用意されています。

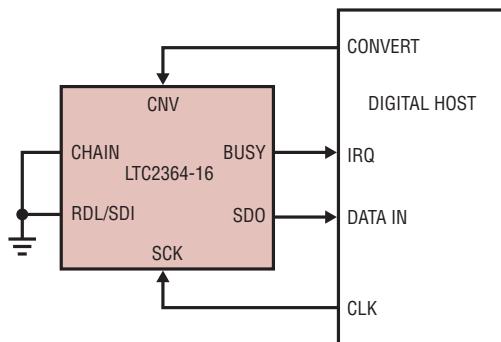

### 通常モード、單一デバイス

CHAIN = 0のとき、LTC2364-16は通常モードで動作します。通常モードでは、RDL/SDIはシリアル・データ出力ピン SDO をイネーブルまたはディスエーブルします。RDL/SDIが“H”だと、SDOは高インピーダンスになります。RDL/SDIが“L”だと、SDOはドライブされます。

CHAINとRDL/SDIがグランドに接続されている状態で通常モードで動作している単一のLTC2364-16を図10に示します。RDL/SDIが接地されると、SDOはイネーブルされ、新しい変換データのMSB (D15)がBUSYの立ち下がりエッジで利用可能になります。これがLTC2364-16を動作させる最も簡単な方法です。

図10. 1個のLTC2364-16を通常モードで使用

## タイミング図

### 通常モード、複数デバイス

CNV、SCK および SDO を共有して、通常モード (CHAIN = 0) で動作している複数の LTC2364-16 デバイスを図11 に示します。CNV、SCK および SDO を共有することにより、複数の ADC を並列で動作させるのに必要な信号数が減少します。SDO が共有されているので、バスの競合を防ぐため、各 ADC

の RDL/SDI 入力をを使って、一度に 1 個の LTC2364-16 だけが SDO をドライブできるようにする必要があります。図11 に示すように、RDL/SDI 入力はアイドル状態では “H” であり、個別に “L” にして変換と変換の間に各デバイスからデータを読み出します。RDL/SDI を “L” にすると、選択されたデバイスの MSB が SDO に出力されます。

図11. 複数のデバイスが CNV、SCK および SDO を共有する通常モード

## タイミング図

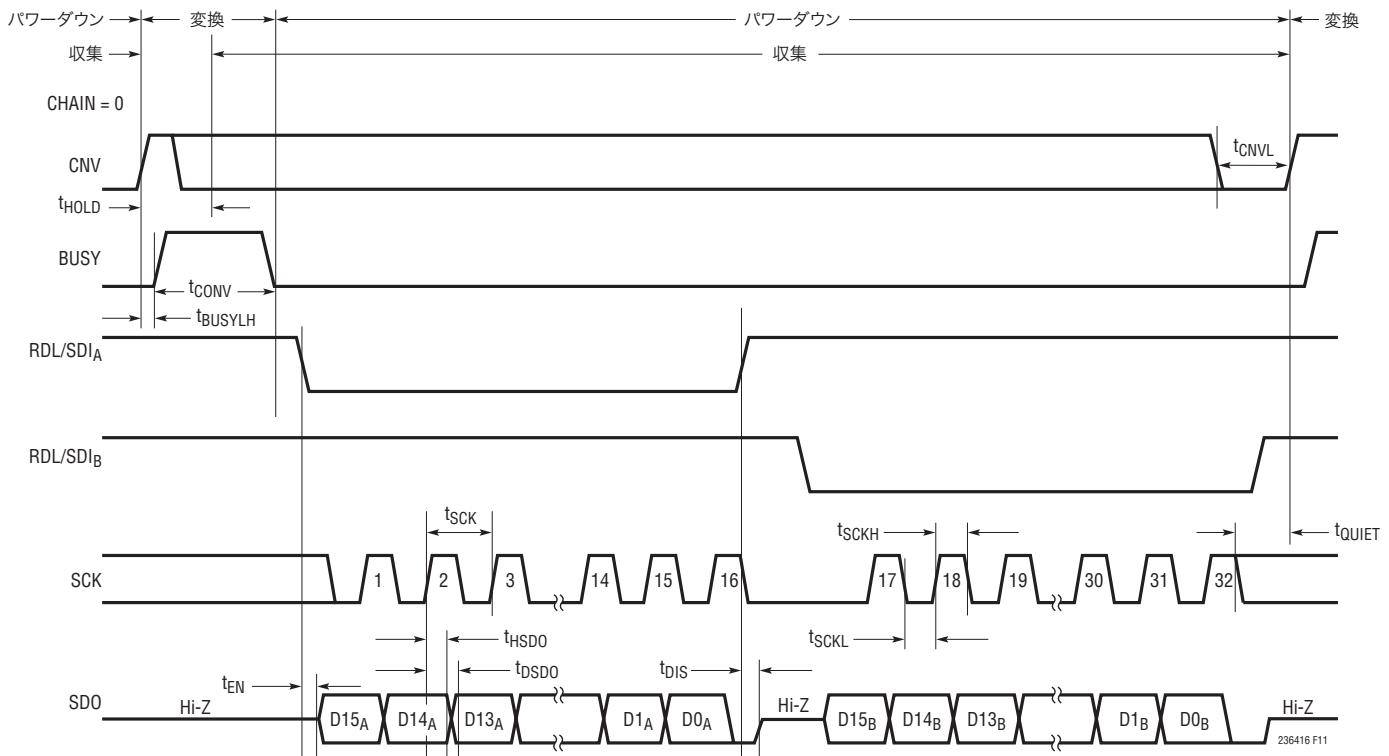

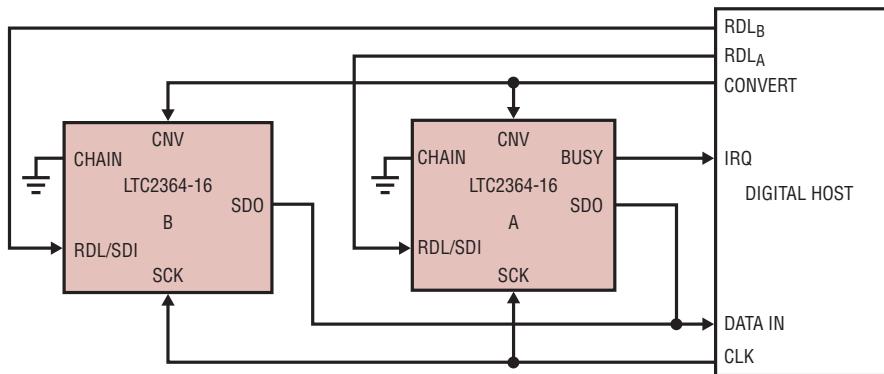

### チェーン・モード、複数デバイス

CHAIN = OV<sub>DD</sub> のとき、LTC2364-16 はチェーン・モードで動作します。チェーン・モードでは、SDO は常にインエーブルされており、RDL/SDI はシリアル・データ入力ビン (SDI) として機能し、別の ADC からのデジタル・チェーン・データ出力を入力することができます。

これは、多数のコンバータにインターフェースするのに必要なライン数がハードウェアの制約によって制限されるアプリケーションに便利です。デジタル・チェーン接続された 2 個のデバイスの例を図 12 に示します。コンバータ A の MSB は、16 SCK サイクル後にコンバータ B の SDO に現れます。コンバータ A の MSB は、最初の SCK の立ち上がりエッジで、コンバータ B の SDI/RDL ピンにクロックインされます。

図12. チェーン・モードのタイミング図

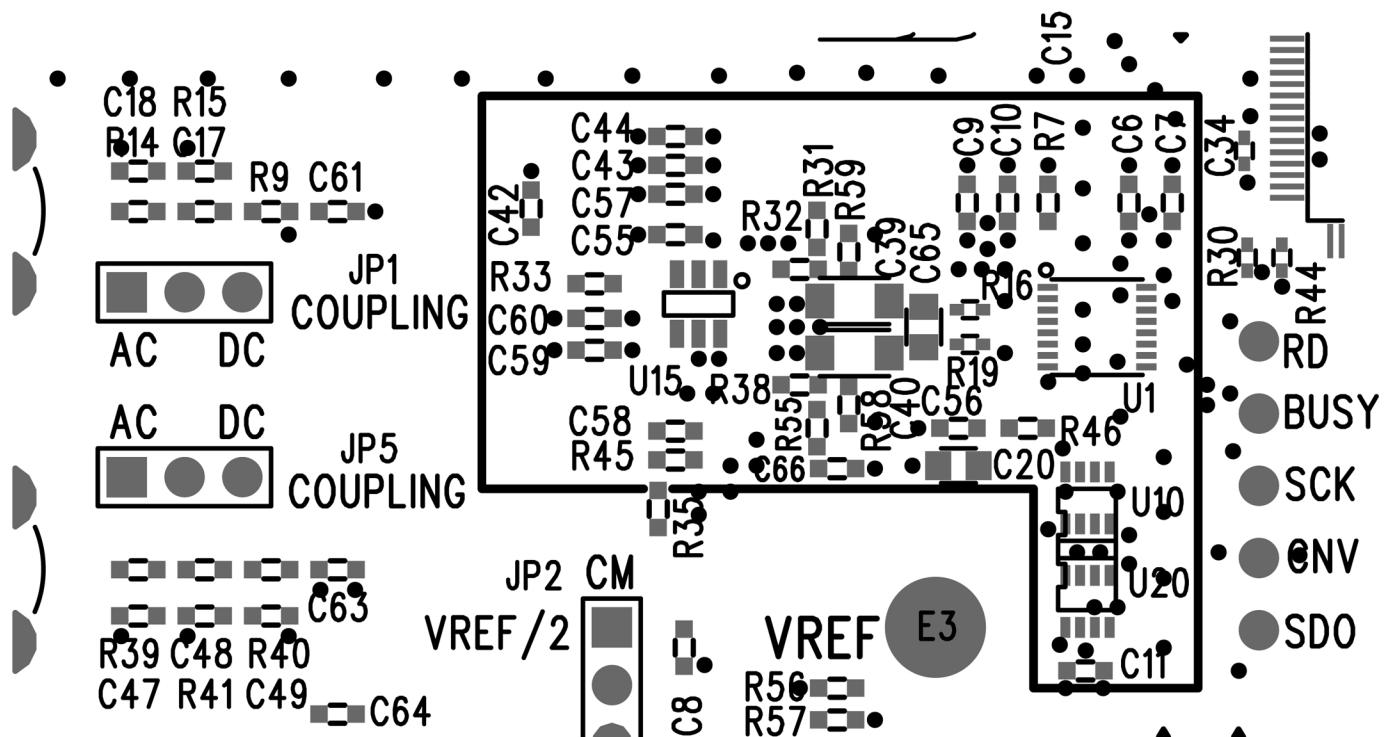

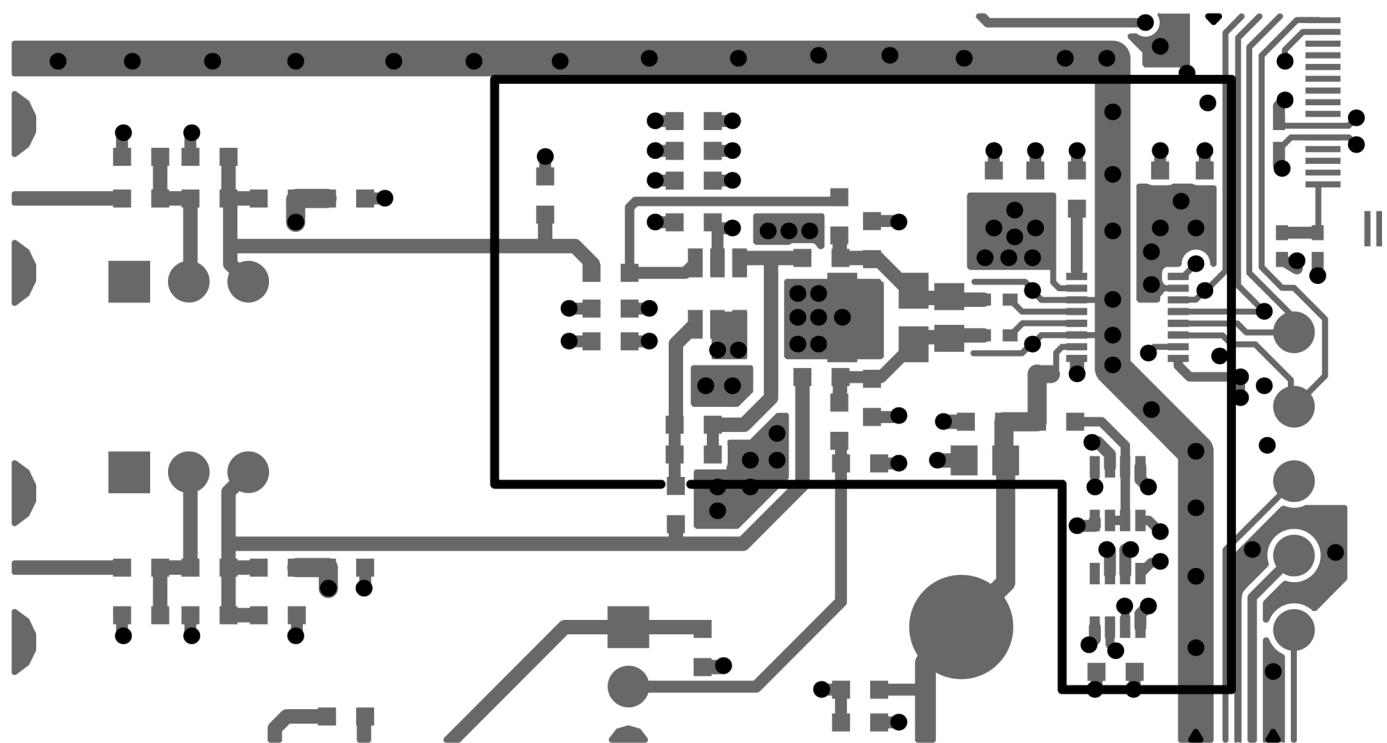

## 基板のレイアウト

LTC2364-16 から最大限の性能を引き出すには、プリント回路基板を推奨します。プリント回路基板(PCB)のレイアウトでは、デジタル信号ラインとアナログ信号ラインをできるだけ離すようにします。特に、どのデジタル・クロックやデジタル信号も、アナログ信号に沿って配置したり、ADCの下を通したりしないでください。

## 推奨レイアウト

以下に推奨PCBレイアウトの一例を示します。切れ目のない単一のグランド・プレーンを使用します。電源へのバイパス・コンデンサは電源ピンのできるだけ近くに配置します。これらのバイパス・コンデンサの低インピーダンスの共通リターンが、ADCの低ノイズ動作には不可欠です。アナログ入力のトレースはグランドを使ってシールドします。詳細に関しては、LTC2364-16用評価キットDC1813Aを参照してください。

シルクスクリーンの上面(一部)

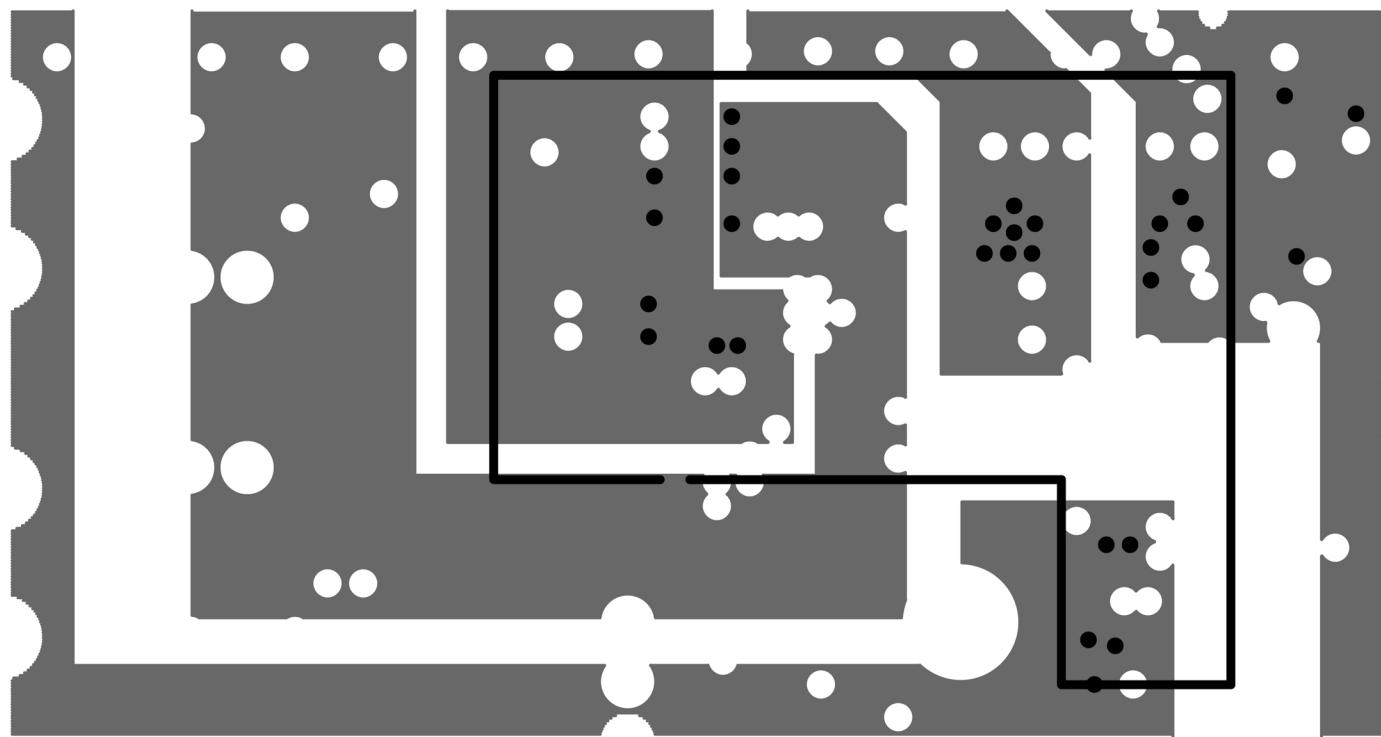

基板のレイアウト

第1層、部品面(一部)

第2層、グランド・プレーン(一部)

236416fa

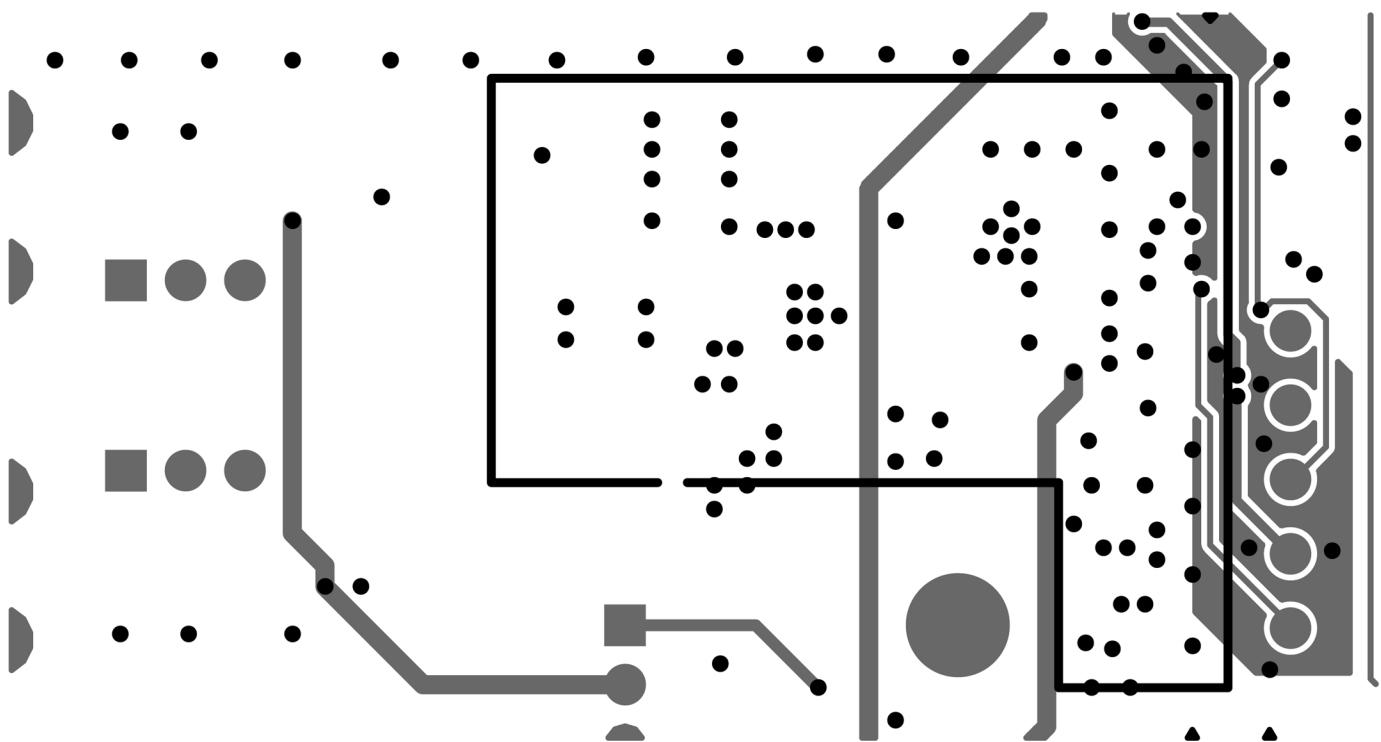

## 基板のレイアウト

第3層、電源プレーン(一部)

第4層、最下層(一部)

236416fa

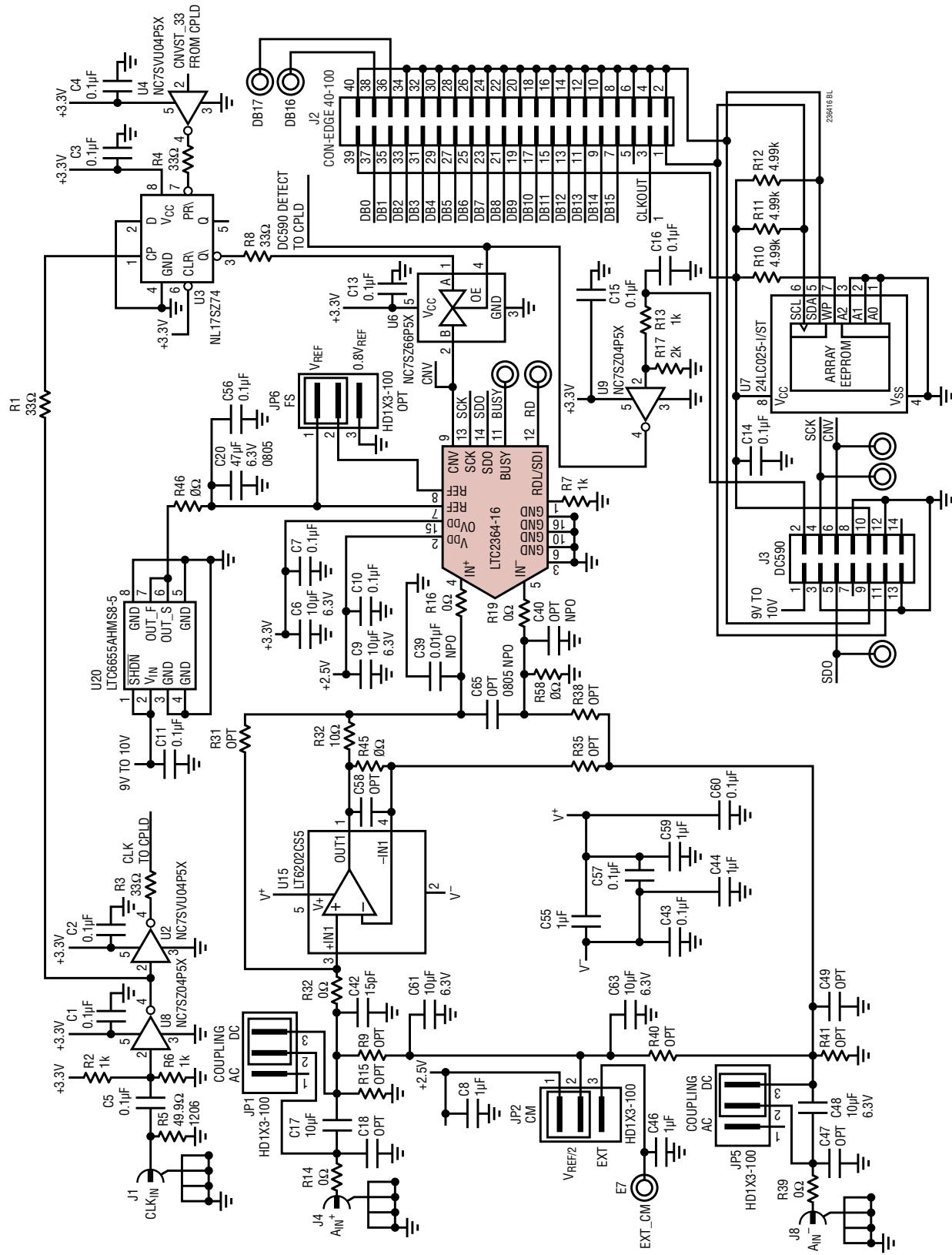

## 基板のレイアウト

## デモボードの回路図(一部)

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

## 改訂履歴

| REV | 日付   | 概要                            | ページ番号 |

|-----|------|-------------------------------|-------|

| A   | 8/12 | 「概要」セクションの分解能を18ビットから16ビットに修正 | 1     |

LTC2364-16

## 標準的應用例

±10Vのバイポーラ信号を LTC2364-16への0V～5Vの入力信号に変換する LT6202

## 関連製品

| 製品番号                                 | 説明                                               | 注釈                                                                          |

|--------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------|

| <b>ADC</b>                           |                                                  |                                                                             |

| LTC2379-18/LTC2378-18                | 18ビット、1.6Msps/1Msps/500ksps/250kspsシリアル、低消費電力ADC | 2.5V電源、差動入力、SNR:101.2dB、入力範囲:±5V、DGC、MSOP-16および4mm×3mm DFN-16パッケージのピン互換ファミリ |

| LTC2377-18/LTC2376-18                |                                                  |                                                                             |

| LTC2380-16/LTC2378-16                | 16ビット、2Msps/1Msps/500ksps/250kspsシリアル、低消費電力ADC   | 2.5V電源、差動入力、SNR:96.2dB、入力範囲:±5V、DGC、MSOP-16および4mm×3mm DFN-16パッケージのピン互換ファミリ  |

| LTC2377-16/LTC2376-16                |                                                  |                                                                             |

| LTC2383-16/LTC2382-16/<br>LTC2381-16 | 16ビット、1Msps/500ksps/250kspsシリアル、低消費電力ADC         | 2.5V電源、差動入力、SNR:92dB、入力範囲:±2.5V、MSOP-16および4mm×3mm DFN-16パッケージのピン互換ファミリ      |

| LTC2393-16/LTC2392-16/<br>LTC2391-16 | 16ビット、1Msps/500ksps/250kspsパラレル/シリアルADC          | 5V電源、差動入力、SNR:94dB、入力範囲:±4.096V、7mm×7mm LQFP-48およびQFN-48パッケージのピン互換ファミリ      |

| LTC1864/LTC1864L                     | 16ビット、250ksps/150ksps、1チャネル・マイクロパワーADC           | 5V/3V電源、1チャネル、4.3mW/1.5mW、MSOP-8パッケージ                                       |

| LTC1865/LTC1865L                     | 16ビット、250ksps/150ksps、2チャネル・マイクロパワーADC           | 5V/3V電源、2チャネル、4.3mW/1.3mW、MSOP-10パッケージ                                      |

---

DAC

|         |                                                  |                                                        |

|---------|--------------------------------------------------|--------------------------------------------------------|

| LTC2757 | 18ビット、シングル・パラレル I <sub>OUT</sub> SoftSpan™ DAC   | INL/DNL:±1LSB、ソフトウェアで選択可能な範囲、7mm×7mm LQFP-48パッケージ      |

| LTC2641 | 16ビット/14ビット/12ビットのシングル・シリアル V <sub>OUT</sub> DAC | INL/DNL:±1LSB、MSOP-8、3mm×3mm DFN および SO-8パッケージ、0V～5V出力 |

| LTC2630 | 12ビット/10ビット/8ビットのシングル V <sub>OUT</sub> DAC       | 6ピン SC70パッケージ、内部リファレンス、INL:±1LSB(12ビット)                |

## リファレンス

|         |                                  |                                                                          |

|---------|----------------------------------|--------------------------------------------------------------------------|

| LTC6655 | バッファ付き、高精度、低ドリフト、<br>低ノイズ・リファレンス | 5V/2.5V、2ppm/ $^{\circ}\text{C}$ 、ピーク・トゥ・ピーク・ノイズ:0.25ppm、<br>MSOP-8パッケージ |

| LTC6652 | バッファ付き、高精度、低ドリフト、<br>低ノイズ・リファレンス | 5V/2.5V、5ppm/ $^{\circ}\text{C}$ 、ピーク・トゥ・ピーク・ノイズ:2.1ppm、<br>MSOP-8パッケージ  |

## アンプ

|                               |                                                          |                                                                                     |

|-------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------|

| LT6202/LT6203                 | シングル/デュアル 100MHz、レール・トゥ・レール入力/出力、超低ノイズ、低消費電力アンプ          | 1.9nV/ $\sqrt{\text{Hz}}$ 、3mA(最大)、利得帯域幅積:100MHz                                    |

| LT6200/LT6200-5/<br>LT6200-10 | 165MHz/800MHz/1.6GHz オペアンプ、ユニティゲイン/ $AV = 5$ / $AV = 10$ | 低ノイズ電圧:0.95nV/ $\sqrt{\text{Hz}}$ (100kHz)、低歪み:1MHz で -80dB、TSOT23-6 および SO-8 パッケージ |