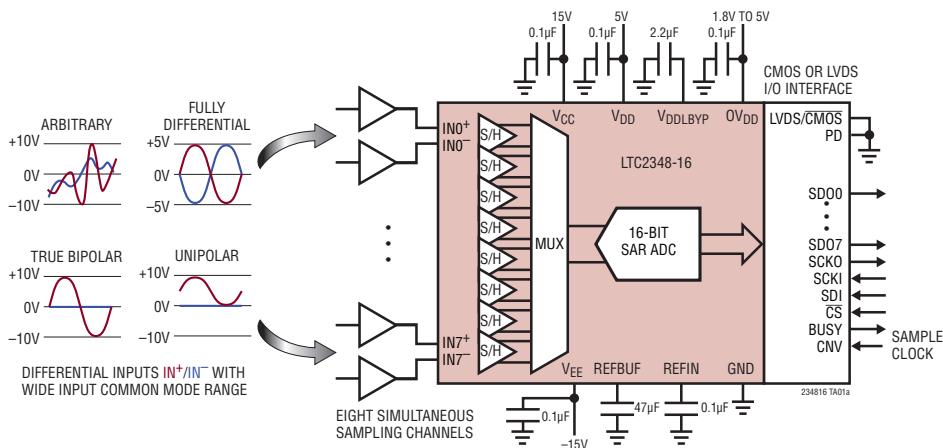

入力同相電圧範囲が広い、

オクタル、16ビット、200ksps の

$\pm 10.24V$  差動入力 SoftSpan A/D コンバータ

## 特長

- 各チャネルのスループット: 200ksps

- 8つの同時サンプリング・チャネル

- INL(最大):  $\pm 1\text{ LSB}$

- 欠落コードのない16ビットを保証

- 同相電圧範囲の広い差動入力

- チャネルごとのSoftSpan入力電圧レンジ:

$\pm 10.24V$ ,  $0V \sim 10.24V$ ,  $\pm 5.12V$ ,  $0V \sim 5.12V$

$\pm 12.5V$ ,  $0V \sim 12.5V$ ,  $\pm 6.25V$ ,  $0V \sim 6.25V$

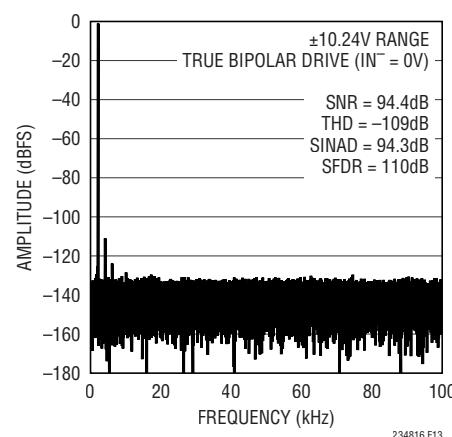

- シングル・コンバージョンのSNR: 94.4dB(標準)

- THD: -109dB(標準,  $f_{IN} = 2\text{kHz}$ )

- CMRR: 118dB(標準,  $f_{IN} = 200\text{Hz}$ )

- レール・トゥ・レールのオーバードライブ耐性

- $125^\circ\text{C}$ までの動作を保証

- リファレンスとバッファを内蔵(4.096V)

- SPI CMOS(1.8V ~ 5V)とLVDSのシリアルI/O

- 内部変換クロック、サイクル待ち時間なし

- 電力損失: 140mW(標準)

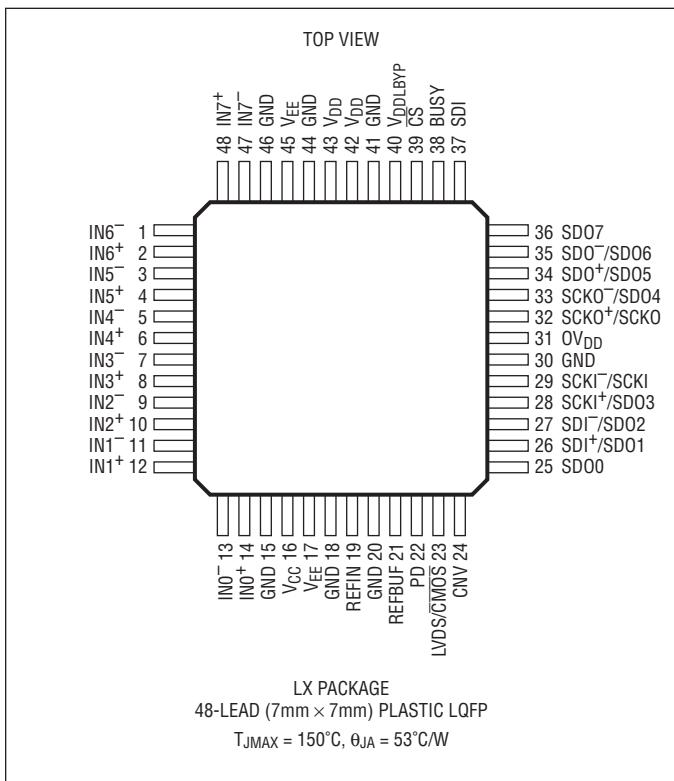

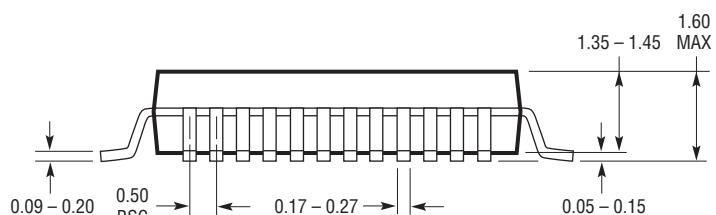

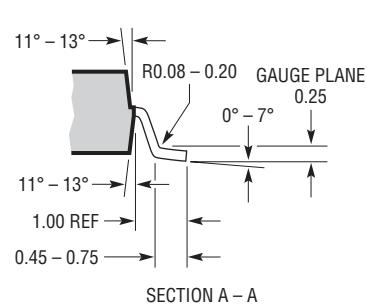

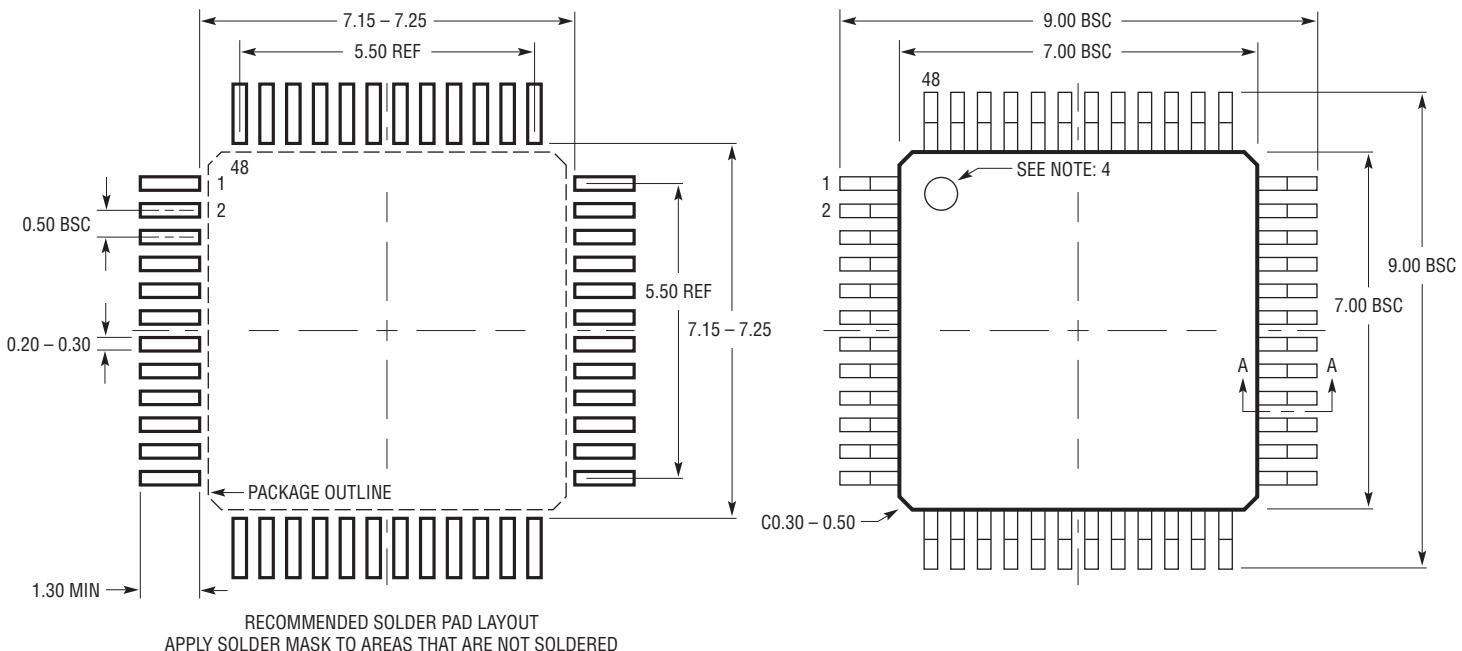

- 48ピン(7mm×7mm)LQFPパッケージ

## アプリケーション

- プログラマブル・ロジック・コントローラ

- 産業用プロセス制御

- 電源系統の監視

- テストと測定

## 標準的応用例

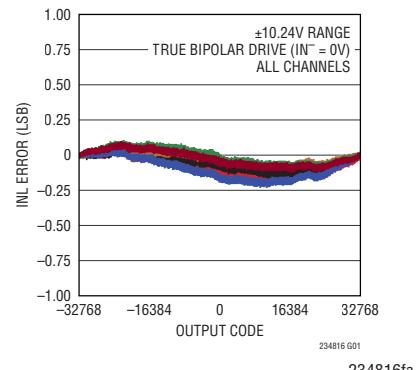

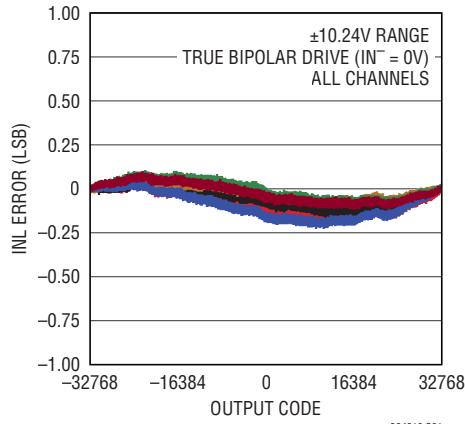

積分非直線性と出力コードと

チャネル

# LTC2348-16

## 絶対最大定格

(Note 1, 2)

|                             |                            |

|-----------------------------|----------------------------|

| 電源電圧 ( $V_{CC}$ )           | -0.3V ~ ( $V_{EE} + 40V$ ) |

| 電源電圧 ( $V_{EE}$ )           | -17.4V ~ 0.3V              |

| 電源電圧差 ( $V_{CC} - V_{EE}$ ) | 40V                        |

| 電源電圧 ( $V_{DD}$ )           | 6V                         |

| 電源電圧 ( $OV_{DD}$ )          | 6V                         |

内蔵の安定化電源をバイパス ( $V_{DDLBYP}$ ) (Note 3)

アナログ入力電圧

|                             |                                           |

|-----------------------------|-------------------------------------------|

| $IN0^+ \sim IN7^+$ ,        |                                           |

| $IN0^- \sim IN7^-$ (Note 4) | ( $V_{EE} - 0.3V$ ) ~ ( $V_{CC} + 0.3V$ ) |

| REFIN                       | -0.3V ~ 2.8V                              |

| REFBUF, CNV (Note 5)        | -0.3V ~ ( $V_{DD} + 0.3V$ )               |

デジタル入力電圧 (Note 5) (-0.3V) ~ ( $OV_{DD} + 0.3V$ )

デジタル出力電圧 (Note 5) (-0.3V) ~ ( $OV_{DD} + 0.3V$ )

電力損失 ..... 500mW

動作温度範囲

LTC2348C ..... 0°C ~ 70°C

LTC2348I ..... -40°C ~ 85°C

LTC2348H ..... -40°C ~ 125°C

保存温度範囲 ..... -65°C ~ 150°C

## ピン配置

## 発注情報

| 鉛フリー仕様            | トレイ               | 製品マーキング*     | パッケージ                          | 温度範囲           |

|-------------------|-------------------|--------------|--------------------------------|----------------|

| LTC2348CLX-16#PBF | LTC2348CLX-16#PBF | LTC2348LX-16 | 48-Lead (7mm×7mm) Plastic LQFP | 0°C to 70°C    |

| LTC2348ILX-16#PBF | LTC2348ILX-16#PBF | LTC2348LX-16 | 48-Lead (7mm×7mm) Plastic LQFP | -40°C to 85°C  |

| LTC2348HLX-16#PBF | LTC2348HLX-16#PBF | LTC2348LX-16 | 48-Lead (7mm×7mm) Plastic LQFP | -40°C to 125°C |

より広い動作温度範囲で規定されるデバイスについては、弊社へお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/>

## 電氣的特性

- は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 6)

| 記号                  | パラメータ                                          | 条件                                                                                                                                                                                                                                                                                                                                                                                                                                  | 最小値                                                                                                                   | 標準値                                                                                                                                                                                                     | 最大値 | 単位           |

|---------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|

| $V_{IN+}$           | Absolute Input Range<br>( $IN0^-$ to $IN7^+$ ) | (Note 7)                                                                                                                                                                                                                                                                                                                                                                                                                            | $V_{EE}$                                                                                                              | $V_{CC} - 4$                                                                                                                                                                                            |     | V            |

| $V_{IN-}$           | Absolute Input Range<br>( $IN0^-$ to $IN7^-$ ) | (Note 7)                                                                                                                                                                                                                                                                                                                                                                                                                            | $V_{EE}$                                                                                                              | $V_{CC} - 4$                                                                                                                                                                                            |     | V            |

| $V_{IN+} - V_{IN-}$ | Input Differential Voltage Range               | SoftSpan 7: $\pm 2.5 \cdot V_{REFBUF}$ Range (Note 7)<br>SoftSpan 6: $\pm 2.5 \cdot V_{REFBUF}/1.024$ Range (Note 7)<br>SoftSpan 5:0V to $2.5 \cdot V_{REFBUF}$ Range (Note 7)<br>SoftSpan 4:0V to $2.5 \cdot V_{REFBUF}/1.024$ Range (Note 7)<br>SoftSpan 3: $\pm 1.25 \cdot V_{REFBUF}$ Range (Note 7)<br>SoftSpan 2: $\pm 1.25 \cdot V_{REFBUF}/1.024$ Range (Note 7)<br>SoftSpan 1:0V to $1.25 \cdot V_{REFBUF}$ Range (Note 7) | -2.5 • $V_{REFBUF}$<br>-2.5 • $V_{REFBUF}/1.024$<br>0<br>0<br>-1.25 • $V_{REFBUF}$<br>-1.25 • $V_{REFBUF}/1.024$<br>0 | $2.5 \cdot V_{REFBUF}$<br>$2.5 \cdot V_{REFBUF}/1.024$<br>$2.5 \cdot V_{REFBUF}$<br>$2.5 \cdot V_{REFBUF}/1.024$<br>$1.25 \cdot V_{REFBUF}$<br>$1.25 \cdot V_{REFBUF}/1.024$<br>$1.25 \cdot V_{REFBUF}$ |     | V            |

| $V_{CM}$            | Input Common Mode Voltage Range                | (Note 7)                                                                                                                                                                                                                                                                                                                                                                                                                            | $V_{EE}$                                                                                                              | $V_{CC} - 4$                                                                                                                                                                                            |     | V            |

| $V_{IN+} - V_{IN-}$ | Input Differential Overdrive Tolerance         | (Note 8)                                                                                                                                                                                                                                                                                                                                                                                                                            | $-(V_{CC} - V_{EE})$                                                                                                  | $(V_{CC} - V_{EE})$                                                                                                                                                                                     |     | V            |

| $I_{IN}$            | Analog Input Leakage Current                   |                                                                                                                                                                                                                                                                                                                                                                                                                                     | -1                                                                                                                    | 1                                                                                                                                                                                                       |     | $\mu A$      |

| $C_{IN}$            | Analog Input Capacitance                       | Sample Mode<br>Hold Mode                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                       | 50<br>10                                                                                                                                                                                                |     | $pF$<br>$pF$ |

| CMRR                | Input Common Mode Rejection Ratio              | $V_{IN+} = V_{IN-} = 18V_{P-P}$ 200Hz Sine                                                                                                                                                                                                                                                                                                                                                                                          | 100                                                                                                                   | 118                                                                                                                                                                                                     |     | dB           |

| $V_{IHCV}$          | CNV High Level Input Voltage                   |                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.3                                                                                                                   |                                                                                                                                                                                                         |     | V            |

| $V_{ILCNV}$         | CNV Low Level Input Voltage                    |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                       | 0.5                                                                                                                                                                                                     |     | V            |

| $I_{INCNV}$         | CNV Input Current                              | $V_{IN} = 0V$ to $V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                           | -10                                                                                                                   | 10                                                                                                                                                                                                      |     | $\mu A$      |

## コンバータの特性

- は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 9)

| 記号  | パラメータ                        | 条件                                                                                                                                                                          | 最小値 | 標準値                        | 最大値    | 単位                                   |        |

|-----|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------|--------|--------------------------------------|--------|

|     | Resolution                   |                                                                                                                                                                             | ●   | 16                         |        | Bits                                 |        |

|     | No Missing Codes             |                                                                                                                                                                             | ●   | 16                         |        | Bits                                 |        |

|     | Transition Noise             | SoftSpans 7 and 6:±10.24V and ±10V Ranges<br>SoftSpans 5 and 4:0V to 10.24V and 0V to 10V Ranges<br>SoftSpans 3 and 2:±5.12V and ±5V Ranges<br>SoftSpan 1:0V to 5.12V Range |     | 0.33<br>0.65<br>0.5<br>1.0 |        | LSBRMS<br>LSBRMS<br>LSBRMS<br>LSBRMS |        |

| INL | Integral Linearity Error     | (Note 10)                                                                                                                                                                   | ●   | -1                         | ±0.3   | 1                                    | LSB    |

| DNL | Differential Linearity Error | (Note 11)                                                                                                                                                                   | ●   | -0.9                       | ±0.2   | 0.9                                  | LSB    |

| ZSE | Zero-Scale Error             | (Note 12)                                                                                                                                                                   | ●   | -550                       | ±160   | 550                                  | µV     |

|     | Zero-Scale Error Drift       |                                                                                                                                                                             |     | ±2                         |        |                                      | µV/°C  |

| FSE | Full-Scale Error             | (Note 12)                                                                                                                                                                   | ●   | -0.1                       | ±0.025 | 0.1                                  | %FS    |

|     | Full-Scale Error Drift       |                                                                                                                                                                             |     | ±2.5                       |        |                                      | ppm/°C |

# LTC2348-16

## ダイナミック精度

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $A_{IN} = -1\text{dBFS}$ 。(Note 9、13)

| 記号                      | パラメータ                                | 条件                                                                                                                                                                                                                                                                                                                            |                  | 最小値                          | 標準値                          | 最大値                          | 単位    |

|-------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------|------------------------------|------------------------------|-------|

| SINAD                   | Signal-to-(Noise + Distortion) Ratio | SoftSpans 7 and 6: $\pm 10.24\text{V}$ and $\pm 10\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$<br>SoftSpans 5 and 4:0V to 10.24V and 0V to 10V Ranges, $f_{IN} = 2\text{kHz}$<br>SoftSpans 3 and 2: $\pm 5.12\text{V}$ and $\pm 5\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$<br>SoftSpan 1:0V to 5.12V Range, $f_{IN} = 2\text{kHz}$ | ●<br>●<br>●<br>● | 91.8<br>87.2<br>89.3<br>84.0 | 94.3<br>90.1<br>92.0<br>87.0 |                              | dB    |

| SNR                     | Signal-to-Noise Ratio                | SoftSpans 7 and 6: $\pm 10.24\text{V}$ and $\pm 10\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$<br>SoftSpans 5 and 4:0V to 10.24V and 0V to 10V Ranges, $f_{IN} = 2\text{kHz}$<br>SoftSpans 3 and 2: $\pm 5.12\text{V}$ and $\pm 5\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$<br>SoftSpan 1:0V to 5.12V Range, $f_{IN} = 2\text{kHz}$ | ●<br>●<br>●<br>● | 92.3<br>87.3<br>89.5<br>84.1 | 94.4<br>90.1<br>92.0<br>87.0 |                              | dB    |

| THD                     | Total Harmonic Distortion            | SoftSpans 7 and 6: $\pm 10.24\text{V}$ and $\pm 10\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$<br>SoftSpans 5 and 4:0V to 10.24V and 0V to 10V Ranges, $f_{IN} = 2\text{kHz}$<br>SoftSpans 3 and 2: $\pm 5.12\text{V}$ and $\pm 5\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$<br>SoftSpan 1:0V to 5.12V Range, $f_{IN} = 2\text{kHz}$ | ●<br>●<br>●<br>● |                              | -109<br>-111<br>-113<br>-114 | -101<br>-104<br>-104<br>-103 | dB    |

| SFDR                    | Spurious Free Dynamic Range          | SoftSpans 7 and 6: $\pm 10.24\text{V}$ and $\pm 10\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$<br>SoftSpans 5 and 4:0V to 10.24V and 0V to 10V Ranges, $f_{IN} = 2\text{kHz}$<br>SoftSpans 3 and 2: $\pm 5.12\text{V}$ and $\pm 5\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$<br>SoftSpan 1:0V to 5.12V Range, $f_{IN} = 2\text{kHz}$ | ●<br>●<br>●<br>● | 101<br>105<br>105<br>105     | 110<br>112<br>114<br>115     |                              | dB    |

|                         | Channel-to-Channel Crosstalk         | One Channel Converting 18V <sub>P-P</sub> 200Hz Sine in $\pm 10.24\text{V}$ Range, Crosstalk to All Other Channels                                                                                                                                                                                                            |                  |                              | -109                         |                              | dB    |

| -3dB Input Bandwidth    |                                      |                                                                                                                                                                                                                                                                                                                               |                  |                              | 7                            |                              | MHz   |

| Aperture Delay          |                                      |                                                                                                                                                                                                                                                                                                                               |                  |                              | 1                            |                              | ns    |

| Aperture Delay Matching |                                      |                                                                                                                                                                                                                                                                                                                               |                  |                              | 150                          |                              | ps    |

| Aperture Jitter         |                                      |                                                                                                                                                                                                                                                                                                                               |                  |                              | 3                            |                              | psRMS |

| Transient Response      | Full-Scale Step, 0.005% Settling     |                                                                                                                                                                                                                                                                                                                               |                  |                              | 360                          |                              | ns    |

## 内部リファレンスの特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 9)

| 記号          | パラメータ                                      | 条件                                        |   | 最小値   | 標準値   | 最大値   | 単位                    |

|-------------|--------------------------------------------|-------------------------------------------|---|-------|-------|-------|-----------------------|

| $V_{REFIN}$ | Internal Reference Output Voltage          |                                           |   | 2.043 | 2.048 | 2.053 | V                     |

|             | Internal Reference Temperature Coefficient | (Note 14)                                 | ● |       | 5     | 20    | ppm/ $^\circ\text{C}$ |

|             | Internal Reference Line Regulation         | $V_{DD} = 4.75\text{V}$ to $5.25\text{V}$ |   |       | 0.1   |       | mV/V                  |

|             | Internal Reference Output Impedance        |                                           |   |       | 20    |       | k $\Omega$            |

| $V_{REFIN}$ | REFIN Voltage Range                        | REFIN Overdriven (Note 7)                 |   | 1.25  |       | 2.2   | V                     |

## リファレンス・バッファ特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 9)

| 記号           | パラメータ                           | 条件                                                                                                                           |   | 最小値         | 標準値   | 最大値         | 単位         |

|--------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------|---|-------------|-------|-------------|------------|

| $V_{REFBUF}$ | Reference Buffer Output Voltage | REFIN Overdriven, $V_{REFIN} = 2.048\text{V}$                                                                                | ● | 4.091       | 4.096 | 4.101       | V          |

|              | REFBUF Voltage Range            | REFBUF Overdriven (Notes 7, 15)                                                                                              | ● | 2.5         |       | 5           | V          |

|              | REFBUF Input Impedance          | $V_{REFIN} = 0\text{V}$ , Buffer Disabled                                                                                    |   |             | 13    |             | k $\Omega$ |

| $I_{REFBUF}$ | REFBUF Load Current             | $V_{REFBUF} = 5\text{V}$ , 8 Channels Enabled (Notes 15, 16)<br>$V_{REFBUF} = 5\text{V}$ , Acquisition or Nap Mode (Note 15) | ● | 1.5<br>0.39 | 1.9   | 1.9<br>0.39 | mA<br>mA   |

234816fa

## デジタル入力とデジタル出力

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 9)

| 記号                        | パラメータ                                | 条件                                                                                 | ● | 最小値              | 標準値              | 最大値 | 単位            |

|---------------------------|--------------------------------------|------------------------------------------------------------------------------------|---|------------------|------------------|-----|---------------|

| <b>CMOS デジタル入力とデジタル出力</b> |                                      |                                                                                    |   |                  |                  |     |               |

| $V_{IH}$                  | High Level Input Voltage             |                                                                                    | ● | 0.8 • 0 $V_{DD}$ |                  |     | V             |

| $V_{IL}$                  | Low Level Input Voltage              |                                                                                    | ● |                  | 0.2 • 0 $V_{DD}$ |     | V             |

| $I_{IN}$                  | Digital Input Current                | $V_{IN} = 0\text{V}$ to $0V_{DD}$                                                  | ● | -10              | 10               |     | $\mu\text{A}$ |

| $C_{IN}$                  | Digital Input Capacitance            |                                                                                    |   |                  | 5                |     | $\text{pF}$   |

| $V_{OH}$                  | High Level Output Voltage            | $I_{OUT} = -500\mu\text{A}$                                                        | ● | 0 $V_{DD}$ - 0.2 |                  |     | V             |

| $V_{OL}$                  | Low Level Output Voltage             | $I_{OUT} = 500\mu\text{A}$                                                         | ● |                  | 0.2              |     | V             |

| $I_{OZ}$                  | Hi-Z Output Leakage Current          | $V_{OUT} = 0\text{V}$ to $0V_{DD}$                                                 | ● | -10              | 10               |     | $\mu\text{A}$ |

| $I_{SOURCE}$              | Output Source Current                | $V_{OUT} = 0\text{V}$                                                              |   |                  | -50              |     | $\text{mA}$   |

| $I_{SINK}$                | Output Sink Current                  | $V_{OUT} = 0V_{DD}$                                                                |   |                  | 50               |     | $\text{mA}$   |

| <b>LVDS デジタル入力とデジタル出力</b> |                                      |                                                                                    |   |                  |                  |     |               |

| $V_{ID}$                  | Differential Input Voltage           |                                                                                    | ● | 200              | 350              | 600 | mV            |

| $R_{ID}$                  | On-Chip Input Termination Resistance | $\overline{CS} = 0\text{V}$ , $V_{ICM} = 1.2\text{V}$<br>$\overline{CS} = 0V_{DD}$ | ● | 90               | 106              | 125 | $\Omega$      |

|                           |                                      |                                                                                    |   |                  | 10               |     | $M\Omega$     |

| $V_{ICM}$                 | Common-Mode Input Voltage            |                                                                                    | ● | 0.3              | 1.2              | 2.2 | V             |

| $I_{ICM}$                 | Common-Mode Input Current            | $V_{IN+} = V_{IN-} = 0\text{V}$ to $0V_{DD}$                                       | ● | -10              | 10               |     | $\mu\text{A}$ |

| $V_{OD}$                  | Differential Output Voltage          | $R_L = 100\Omega$ Differential Termination                                         | ● | 275              | 350              | 425 | mV            |

| $V_{OCM}$                 | Common-Mode Output Voltage           | $R_L = 100\Omega$ Differential Termination                                         | ● | 1.1              | 1.2              | 1.3 | V             |

| $I_{OZ}$                  | Hi-Z Output Leakage Current          | $V_{OUT} = 0\text{V}$ to $0V_{DD}$                                                 | ● | -10              | 10               |     | $\mu\text{A}$ |

## 電源要件

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 9)

| 記号                | パラメータ                     | 条件                                                                                         | ●                | 最小値                         | 標準値                        | 最大値  | 単位                                                         |

|-------------------|---------------------------|--------------------------------------------------------------------------------------------|------------------|-----------------------------|----------------------------|------|------------------------------------------------------------|

| $V_{CC}$          | Supply Voltage            |                                                                                            | ●                | 0                           | 38                         |      | V                                                          |

| $V_{EE}$          | Supply Voltage            |                                                                                            | ●                | -16.5                       | 0                          |      | V                                                          |

| $V_{CC} - V_{EE}$ | Supply Voltage Difference |                                                                                            | ●                | 10                          | 38                         |      | V                                                          |

| $V_{DD}$          | Supply Voltage            |                                                                                            | ●                | 4.75                        | 5.00                       | 5.25 | V                                                          |

| $I_{VCC}$         | Supply Current            | 200ksps Sample Rate, 8 Channels Enabled<br>Acquisition Mode<br>Nap Mode<br>Power Down Mode | ●<br>●<br>●<br>● | 1.8<br>3.8<br>0.7<br>1      | 2.2<br>4.5<br>0.9<br>15    |      | $\text{mA}$<br>$\text{mA}$<br>$\text{mA}$<br>$\mu\text{A}$ |

| $I_{VEE}$         | Supply Current            | 200ksps Sample Rate, 8 Channels Enabled<br>Acquisition Mode<br>Nap Mode<br>Power Down Mode | ●<br>●<br>●<br>● | -2.8<br>-4.9<br>-1.1<br>-15 | -2.2<br>-4.0<br>-0.8<br>-1 |      | $\text{mA}$<br>$\text{mA}$<br>$\text{mA}$<br>$\mu\text{A}$ |

## CMOS I/O モード

|           |                |                                                                                                                                                                                                                              |                            |                                        |                                          |  |                                                                                            |

|-----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------|------------------------------------------|--|--------------------------------------------------------------------------------------------|

| $0V_{DD}$ | Supply Voltage |                                                                                                                                                                                                                              | ●                          | 1.71                                   | 5.25                                     |  | V                                                                                          |

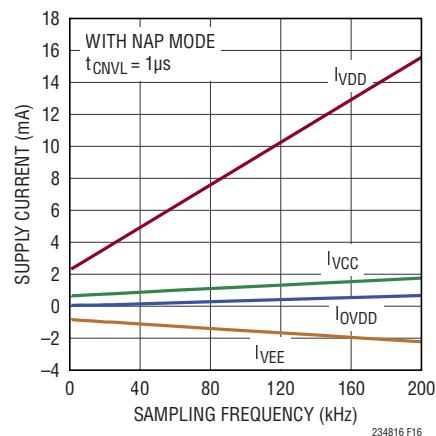

| $I_{VDD}$ | Supply Current | 200ksps Sample Rate, 8 Channels Enabled<br>200ksps Sample Rate, 8 Channels Enabled, $V_{REFBUF} = 5\text{V}$ (Note 15)<br>Acquisition Mode<br>Nap Mode<br>Power Down Mode (C-Grade and I-Grade)<br>Power Down Mode (H-Grade) | ●<br>●<br>●<br>●<br>●<br>● | 15.2<br>13.4<br>1.6<br>1.4<br>65<br>65 | 17.5<br>15.4<br>2.1<br>1.9<br>175<br>450 |  | $\text{mA}$<br>$\text{mA}$<br>$\text{mA}$<br>$\text{mA}$<br>$\mu\text{A}$<br>$\mu\text{A}$ |

## 電源要件

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 9)

| 記号         | パラメータ             | 条件                                                              | 最小値                   | 標準値                              | 最大値                            | 単位            |

|------------|-------------------|-----------------------------------------------------------------|-----------------------|----------------------------------|--------------------------------|---------------|

| $I_{OVDD}$ | Supply Current    | 200ksps Sample Rate, 8 Channels Enabled ( $C_L = 25\text{pF}$ ) | ●<br>●<br>●           | 1.6<br>1<br>1                    | 2.6<br>20<br>20                | $\mu\text{A}$ |

|            |                   | Acquisition or Nap Mode                                         |                       |                                  |                                |               |

|            |                   | Power Down Mode                                                 |                       |                                  |                                |               |

| $P_D$      | Power Dissipation | 200ksps Sample Rate, 8 Channels Enabled                         | ●<br>●<br>●<br>●<br>● | 140<br>125<br>30<br>0.36<br>0.36 | 169<br>152<br>40<br>1.4<br>2.8 | $\text{mW}$   |

|            |                   | Acquisition Mode                                                |                       |                                  |                                |               |

|            |                   | Nap Mode                                                        |                       |                                  |                                |               |

|            |                   | Power Down Mode (C-Grade and I-Grade)                           |                       |                                  |                                |               |

|            |                   | Power Down Mode (H-Grade)                                       |                       |                                  |                                |               |

## LVDS I/O モード

| 記号         | パラメータ             | 条件                                                                          | 最小値                   | 標準値                                 | 最大値                                | 単位            |

|------------|-------------------|-----------------------------------------------------------------------------|-----------------------|-------------------------------------|------------------------------------|---------------|

| $I_{OVDD}$ | Supply Voltage    | 200ksps Sample Rate, 8 Channels Enabled                                     | ●<br>●<br>●<br>●<br>● | 2.375<br>17.7<br>16.1<br>3.2<br>3.0 | 5.25<br>20.4<br>18.5<br>3.8<br>3.7 | $\text{V}$    |

|            |                   | 200ksps Sample Rate, 8 Channels Enabled, $V_{REFBUF} = 5\text{V}$ (Note 15) |                       |                                     |                                    |               |

|            |                   | Acquisition Mode                                                            |                       |                                     |                                    |               |

|            |                   | Nap Mode                                                                    |                       |                                     |                                    |               |

|            |                   | Power Down Mode (C-Grade and I-Grade)                                       |                       |                                     |                                    |               |

| $I_{OVDD}$ | Supply Current    | 200ksps Sample Rate, 8 Channels Enabled ( $R_L = 100\Omega$ )               | ●<br>●<br>●           | 7<br>7<br>1                         | 8.5<br>8.0<br>20                   | $\mu\text{A}$ |

|            |                   | Acquisition or Nap Mode ( $R_L = 100\Omega$ )                               |                       |                                     |                                    |               |

|            |                   | Power Down Mode                                                             |                       |                                     |                                    |               |

| $P_D$      | Power Dissipation | 200ksps Sample Rate, 8 Channels Enabled                                     | ●<br>●<br>●<br>●<br>● | 166<br>151<br>55<br>0.36<br>0.36    | 199<br>180<br>69<br>1.4<br>2.8     | $\text{mW}$   |

|            |                   | Acquisition Mode                                                            |                       |                                     |                                    |               |

|            |                   | Nap Mode                                                                    |                       |                                     |                                    |               |

|            |                   | Power Down Mode (C-Grade and I-Grade)                                       |                       |                                     |                                    |               |

|            |                   | Power Down Mode (H-Grade)                                                   |                       |                                     |                                    |               |

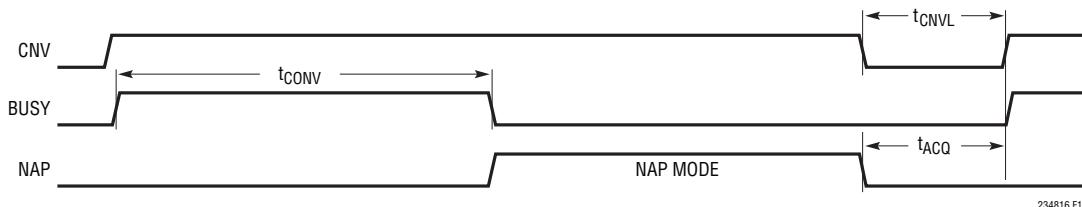

## A/Dコンバータのタイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 9)

| 記号         | パラメータ                                                                | 条件                                              | 最小値                                  | 標準値                                                          | 最大値   | 単位            |

|------------|----------------------------------------------------------------------|-------------------------------------------------|--------------------------------------|--------------------------------------------------------------|-------|---------------|

| $f_{SMPL}$ | Maximum Sampling Frequency                                           | 8 Channels Enabled                              | ●<br>●<br>●<br>●<br>●<br>●<br>●<br>● | 200<br>225<br>266<br>300<br>375<br>450<br>625<br>1000        |       | $\text{kspS}$ |

|            |                                                                      | 7 Channels Enabled                              |                                      |                                                              |       |               |

|            |                                                                      | 6 Channels Enabled                              |                                      |                                                              |       |               |

|            |                                                                      | 5 Channels Enabled                              |                                      |                                                              |       |               |

|            |                                                                      | 4 Channels Enabled                              |                                      |                                                              |       |               |

|            |                                                                      | 3 Channels Enabled                              |                                      |                                                              |       |               |

|            |                                                                      | 2 Channels Enabled                              |                                      |                                                              |       |               |

|            |                                                                      | 1 Channel Enabled                               |                                      |                                                              |       |               |

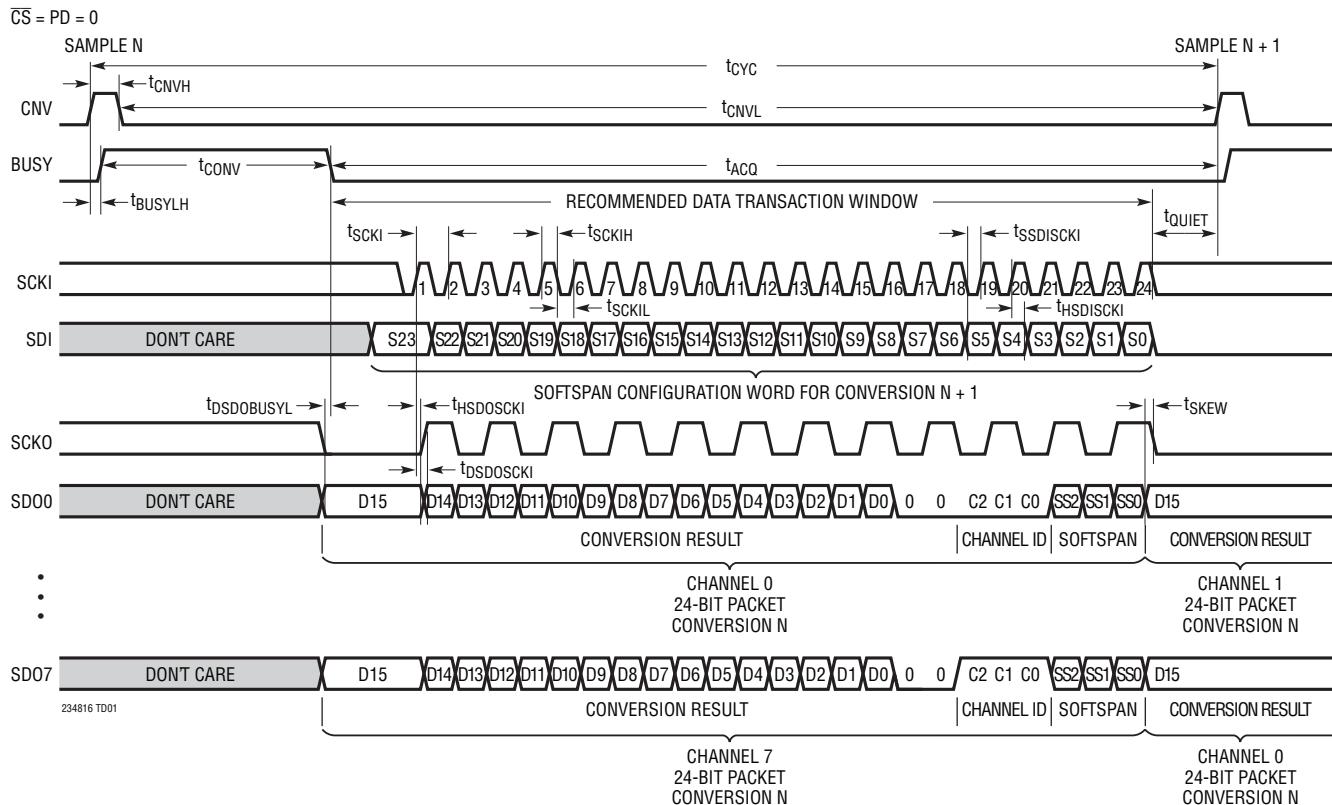

| $t_{CYC}$  | Time Between Conversions                                             | 8 Channels Enabled, $f_{SMPL} = 200\text{kspS}$ | ●<br>●<br>●<br>●<br>●<br>●<br>●<br>● | 5000<br>4444<br>3750<br>3333<br>2666<br>2222<br>1600<br>1000 |       | $\text{ns}$   |

|            |                                                                      | 7 Channels Enabled, $f_{SMPL} = 225\text{kspS}$ |                                      |                                                              |       |               |

|            |                                                                      | 6 Channels Enabled, $f_{SMPL} = 266\text{kspS}$ |                                      |                                                              |       |               |

|            |                                                                      | 5 Channels Enabled, $f_{SMPL} = 300\text{kspS}$ |                                      |                                                              |       |               |

|            |                                                                      | 4 Channels Enabled, $f_{SMPL} = 375\text{kspS}$ |                                      |                                                              |       |               |

|            |                                                                      | 3 Channels Enabled, $f_{SMPL} = 450\text{kspS}$ |                                      |                                                              |       |               |

|            |                                                                      | 2 Channels Enabled, $f_{SMPL} = 625\text{kspS}$ |                                      |                                                              |       |               |

|            |                                                                      | 1 Channel Enabled, $f_{SMPL} = 1000\text{kspS}$ |                                      |                                                              |       |               |

| $t_{CONV}$ | Conversion Time                                                      | N Channels Enabled, $1 \leq N \leq 8$           | ●                                    | 450•N                                                        | 500•N | 550•N         |

| $t_{ACQ}$  | Acquisition Time<br>( $t_{ACQ} = t_{CYC} - t_{CONV} - t_{BUSY LH}$ ) | 8 Channels Enabled, $f_{SMPL} = 200\text{kspS}$ | ●<br>●<br>●<br>●<br>●<br>●<br>●<br>● | 570<br>564<br>420<br>553<br>436<br>542<br>470<br>420         |       | $\text{ns}$   |

|            |                                                                      | 7 Channels Enabled, $f_{SMPL} = 225\text{kspS}$ |                                      |                                                              |       |               |

|            |                                                                      | 6 Channels Enabled, $f_{SMPL} = 266\text{kspS}$ |                                      |                                                              |       |               |

|            |                                                                      | 5 Channels Enabled, $f_{SMPL} = 300\text{kspS}$ |                                      |                                                              |       |               |

|            |                                                                      | 4 Channels Enabled, $f_{SMPL} = 375\text{kspS}$ |                                      |                                                              |       |               |

|            |                                                                      | 3 Channels Enabled, $f_{SMPL} = 450\text{kspS}$ |                                      |                                                              |       |               |

|            |                                                                      | 2 Channels Enabled, $f_{SMPL} = 625\text{kspS}$ |                                      |                                                              |       |               |

|            |                                                                      | 1 Channel Enabled, $f_{SMPL} = 1000\text{kspS}$ |                                      |                                                              |       |               |

234816fa

**A/Dコンバータのタイミング特性**

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 9)

| 記号           | パラメータ                                      | 条件                                                          | 最小値 | 標準値 | 最大値 | 単位 |

|--------------|--------------------------------------------|-------------------------------------------------------------|-----|-----|-----|----|

| $t_{CNVH}$   | CNV High Time                              |                                                             | ●   | 40  |     | ns |

| $t_{CNVL}$   | CNV Low Time                               |                                                             | ●   | 420 |     | ns |

| $t_{BUSYLH}$ | CNV $\uparrow$ to BUSY Delay               | $C_L = 25\text{pF}$                                         | ●   |     | 30  | ns |

| $t_{QUIET}$  | Digital I/O Quiet Time from CNV $\uparrow$ |                                                             | ●   | 20  |     | ns |

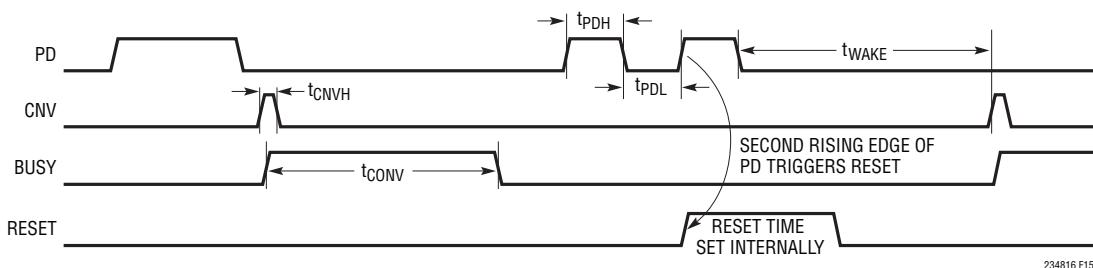

| $t_{PDH}$    | PD High Time                               |                                                             | ●   | 40  |     | ns |

| $t_{PDL}$    | PD Low Time                                |                                                             | ●   | 40  |     | ns |

| $t_{WAKE}$   | REFBUF Wake-Up Time                        | $C_{REFBUF} = 47\mu\text{F}$ , $C_{REFIN} = 0.1\mu\text{F}$ |     |     | 200 | ms |

**CMOS I/O モード**

|                 |                                              |                               |   |        |     |    |

|-----------------|----------------------------------------------|-------------------------------|---|--------|-----|----|

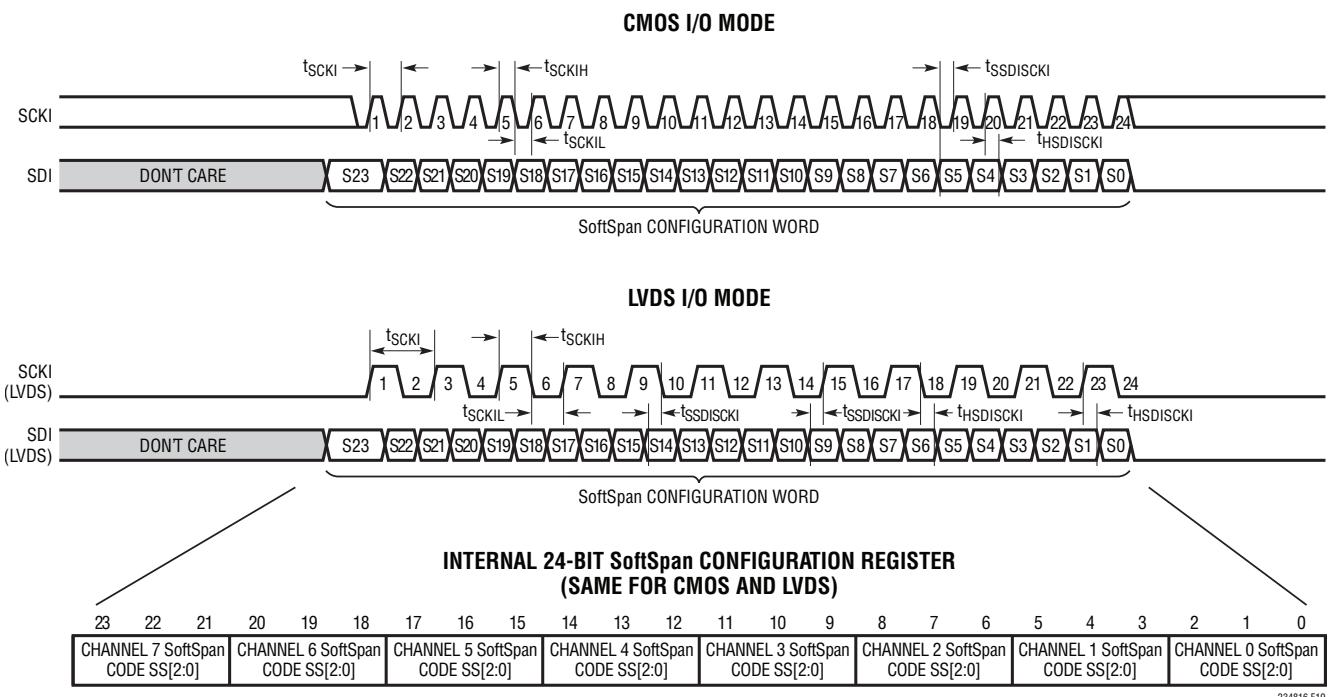

| $t_{SCKI}$      | SCKI Period                                  | (Notes 17, 18)                | ● | 10     |     | ns |

| $t_{SCKIH}$     | SCKI High Time                               |                               | ● | 4      |     | ns |

| $t_{SCKIL}$     | SCKI Low Time                                |                               | ● | 4      |     | ns |

| $t_{SSDISCKI}$  | SDI Setup Time from SCKI $\uparrow$          | (Note 17)                     | ● | 2      |     | ns |

| $t_{HSDISCKI}$  | SDI Hold Time from SCKI $\uparrow$           | (Note 17)                     | ● | 1      |     | ns |

| $t_{DSDOSCKI}$  | SDO Data Valid Delay from SCKI $\uparrow$    | $C_L = 25\text{pF}$ (Note 17) | ● |        | 7.5 | ns |

| $t_{HS DOSCKI}$ | SDO Remains Valid Delay from SCKI $\uparrow$ | $C_L = 25\text{pF}$ (Note 17) | ● | 1.5    |     | ns |

| $t_{SKEW}$      | SDO to SCKO Skew                             | (Note 17)                     | ● | -1 0 1 |     | ns |

| $t_{DSDOBUSYL}$ | SDO Data Valid Delay from BUSY $\downarrow$  | $C_L = 25\text{pF}$ (Note 17) | ● | 0      |     | ns |

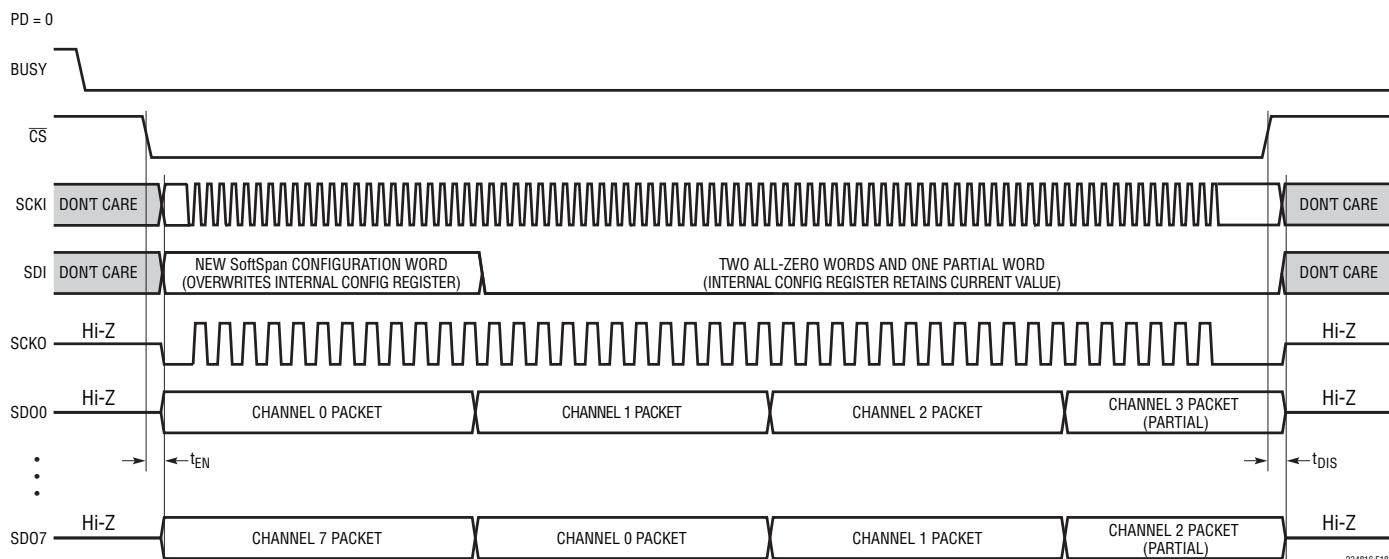

| $t_{EN}$        | Bus Enable Time After CS $\downarrow$        | (Note 17)                     | ● |        | 15  | ns |

| $t_{DIS}$       | Bus Relinquish Time After CS $\uparrow$      | (Note 17)                     | ● |        | 15  | ns |

**LVDS I/O モード**

|                 |                                             |                |   |            |    |    |

|-----------------|---------------------------------------------|----------------|---|------------|----|----|

| $t_{SCKI}$      | SCKI Period                                 | (Note 19)      | ● | 4          |    | ns |

| $t_{SCKIH}$     | SCKI High Time                              | (Note 19)      | ● | 1.5        |    | ns |

| $t_{SCKIL}$     | SCKI Low Time                               | (Note 19)      | ● | 1.5        |    | ns |

| $t_{SSDISCKI}$  | SDI Setup Time from SCKI                    | (Notes 11, 19) | ● | 1.2        |    | ns |

| $t_{HSDISCKI}$  | SDI Hold Time from SCKI                     | (Notes 11, 19) | ● | -0.2       |    | ns |

| $t_{DSDOSCKI}$  | SDO Data Valid Delay from SCKI              | (Notes 11, 19) | ● |            | 6  | ns |

| $t_{HS DOSCKI}$ | SDO Remains Valid Delay from SCKI           | (Notes 11, 19) | ● | 1          |    | ns |

| $t_{SKEW}$      | SDO to SCKO Skew                            | (Note 11)      | ● | -0.4 0 0.4 |    | ns |

| $t_{DSDOBUSYL}$ | SDO Data Valid Delay from BUSY $\downarrow$ | (Note 11)      | ● | 0          |    | ns |

| $t_{EN}$        | Bus Enable Time After CS $\downarrow$       |                | ● |            | 50 | ns |

| $t_{DIS}$       | Bus Relinquish Time After CS $\uparrow$     |                | ● |            | 15 | ns |

## A/Dコンバータのタイミング特性

**Note 1:**「絶対最大定格」のセクションに記載された値を超えるストレスはデバイスに回復不可能な損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与えるおそれがある。

**Note 2:**全ての電圧値はグラウンドを基準にしている。

**Note 3:**  $V_{DDLBY}$  は内蔵電圧レギュレーターの出力であり、「ピン機能」の項に示すようにこのピンをGNDにバイパスする場合は必ず  $2.2\mu F$  のセラミック・コンデンサに接続すること。いかなる外部回路にも、このピンを接続しないでください。

**Note 4:**これらのピンの電圧を  $V_{EE}$  より低くすると、 $V_{CC}$  より高くなると、その電圧は内部のダイオードによってクランプされる。この製品は、電圧が  $V_{EE}$  より低くなるか、 $V_{CC}$  より高くなってしまっても、ラッピングアップを生じることなく最大 100mAまでの入力電流に対応できる。

**Note 5:**これらのピンの電圧をグラウンドより低くすると、 $V_{DD}$  ピンまたは  $0V_{DD}$  ピンの電圧より高くなると、内部のダイオードによってクランプされる。この製品は、これらのピンの電圧がグラウンドより低くなるか、 $V_{DD}$  ピンまたは  $0V_{DD}$  ピンの電圧より高くなつた場合でも、ラッピングアップを生じることなく最大 100mAまでの入力電流に対応できる。

**Note 6:** 注記がない限り、 $-16.5V \leq V_{EE} \leq 0V$ 、 $0V \leq V_{CC} \leq 38V$ 、 $10V \leq (V_{CC} - V_{EE}) \leq 38V$ 、 $V_{DD} = 5V$ 。

**Note 7:** 推奨動作条件。

**Note 8:** いずれかのチャネルでこれらの限界値を超えた場合は、他のチャネルの変換結果が信頼できなくなる可能性があります。デバイスの信頼性に関わるピンの電圧限界値については、絶対最大定格の項を参照。

**Note 9:** 注記がない限り、 $V_{CC} = 15V$ 、 $V_{EE} = -15V$ 、 $V_{DD} = 5V$ 、 $0V_{DD} = 2.5V$ 、 $f_{SAMPL} = 200ksps$ 、内部リファレンスとバッファ、双極性 SoftSpan レンジ内の真の双極性入力信号駆動、単極性 SoftSpan レンジ内の単極性入力信号駆動。

**Note 10:** 積分非直線性は、実際の伝達曲線の端点を通る直線からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

**Note 11:** 設計によって保証されているが、テストされない。

**Note 12:** 双極性 SoftSpan レンジ 7、6、3、2 の場合の双極性ゼロスケール誤差は、出力コードが 0000 0000 0000 0000 と 1111 1111 1111 1111 の間を往復しているときに、-0.5LSB から測定されたオフセット電圧である。これらの SoftSpan レンジの場合のフルスケール誤差は、最初と最後のコード遷移の理想値からのワーストケースの偏差であり、オフセット誤差の影響を含む。単極性 SoftSpan レンジ 5、4、1 の場合のゼロスケール誤差は、出力コードが 0000 0000 0000 0000 と 0000 0000 0000 0001 の間を往復しているときに、0.5LSB から測定されたオフセット電圧である。これらの SoftSpan レンジの場合のフルスケール誤差は、最後のコード遷移の理値からのワーストケースの偏差であり、オフセット誤差の影響を含む。

**Note 13:** dB 単位で示す全ての仕様値は、対応する SoftSpan 入力レンジのクロストークを除去した分のフルスケール値である。クロストークを含む値は、クロストーク含有信号振幅という。

**Note 14:** 温度係数は出力電圧の最大変化を規定温度範囲で割って計算される。

**Note 15:**  $I_{REFBUF}$  をオーバードライブする場合は、 $REFIN = 0V$  に設定して内部リファレンス・バッファをディスエーブルしなければならない。

**Note 16:**  $I_{REFBUF}$  は、サンプル・レートとアクティブなチャネルの数に比例して変化する。

**Note 17:** パラメータは  $0V_{DD} = 1.71V$ 、 $0V_{DD} = 2.5V$ 、および  $0V_{DD} = 5.25V$  でテストされ、保証されている。

**Note 18:**  $t_{SCKI}$  の周期が最小 10ns であるため、立ち上がりで捕捉する場合は最大 100MHz のシフト・クロック周波数が可能である。

**Note 19:** LVDS 差動入力ペアの場合、 $V_{COM} = 1.2V$ 、 $V_{ID} = 350mV$ 。

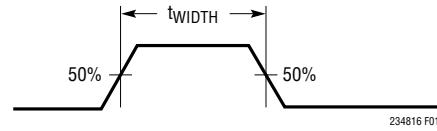

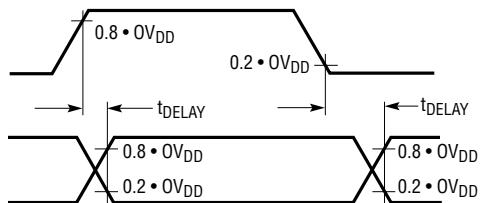

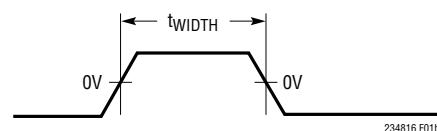

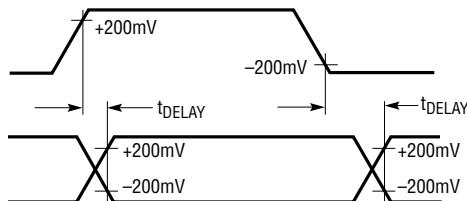

CMOS のタイミング特性

LVDS のタイミング特性(差動)

図1. タイミング仕様の電圧レベル

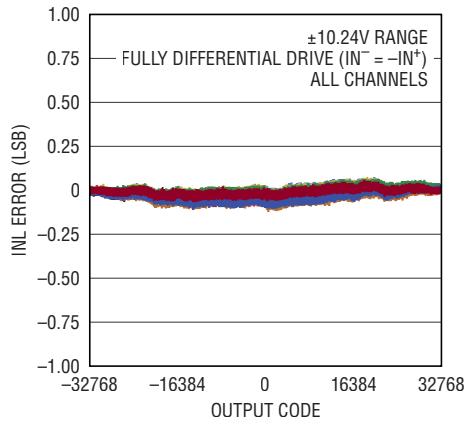

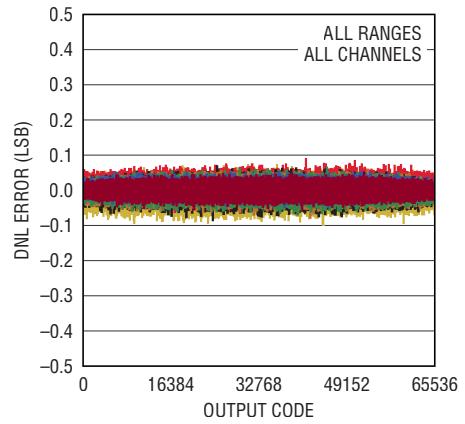

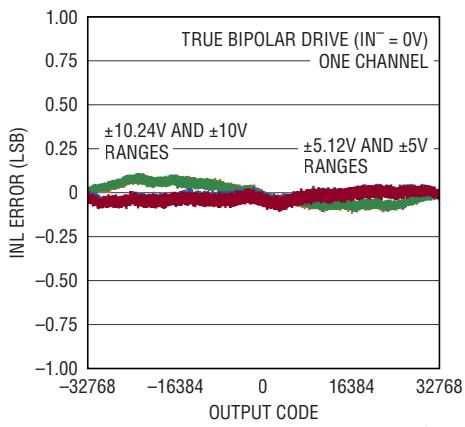

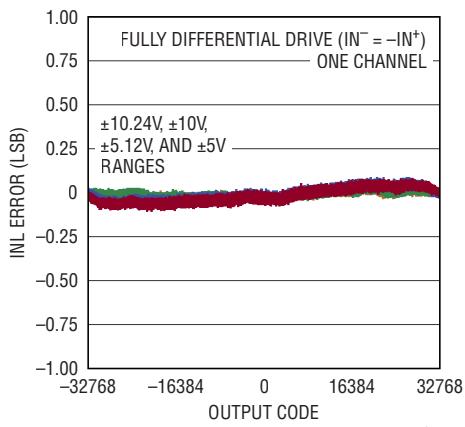

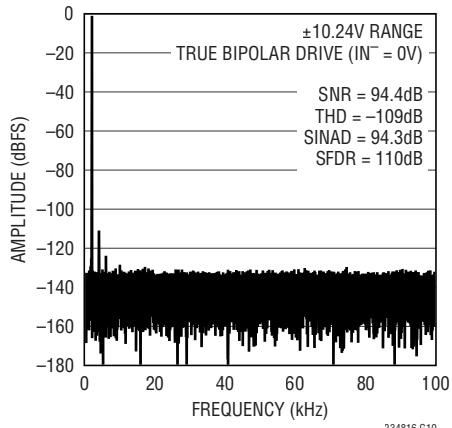

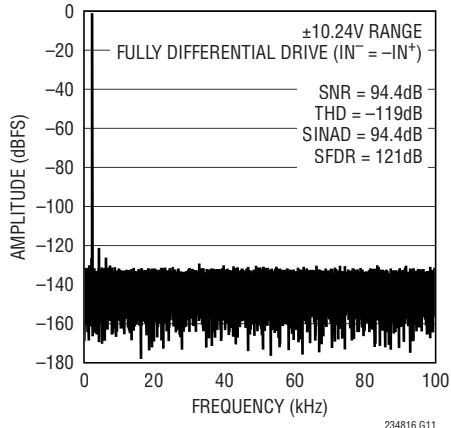

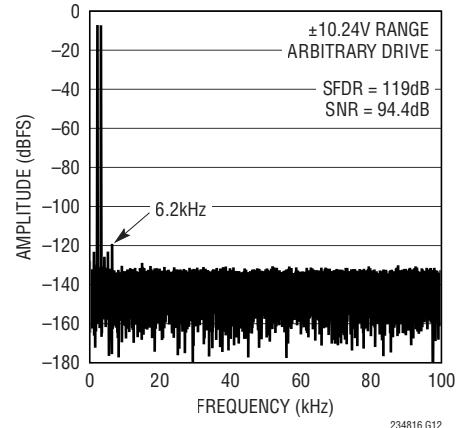

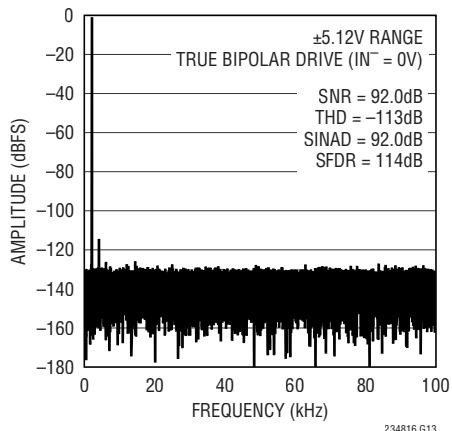

**標準的性能特性**

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{CC} = +15\text{V}$ 、 $V_{EE} = -15\text{V}$ 、 $V_{DD} = 5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、内部リファレンスとバッファ ( $V_{REFBUF} = 4.096\text{V}$ )、 $f_{SMPL} = 200\text{kspS}$ 。

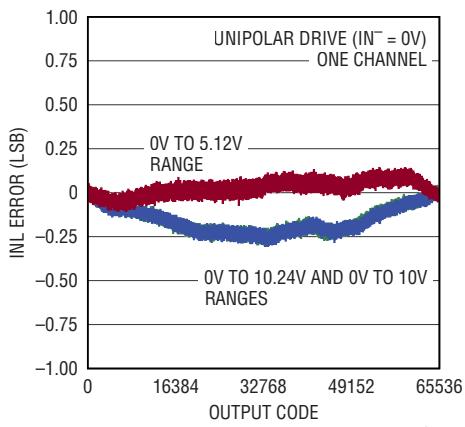

**積分非直線性と

出力コードとチャネル**

**積分非直線性と

出力コードとチャネル**

**差動非直線性と

出力コードとチャネル**

**積分非直線性と

出力コードとレンジ**

**積分非直線性と

出力コードとレンジ**

**積分非直線性と

出力コードとレンジ**

**積分非直線性と出力コード**

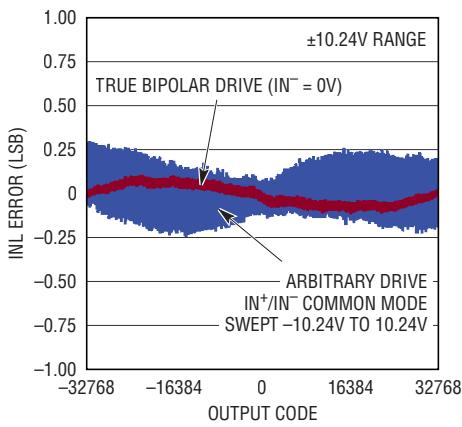

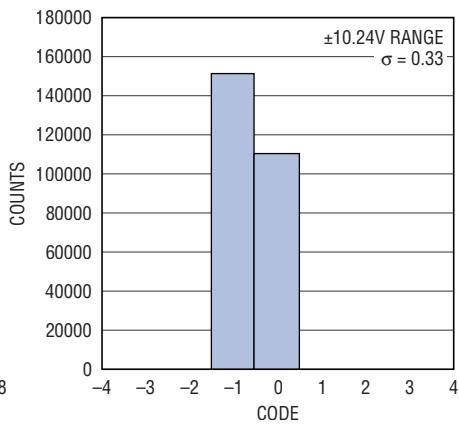

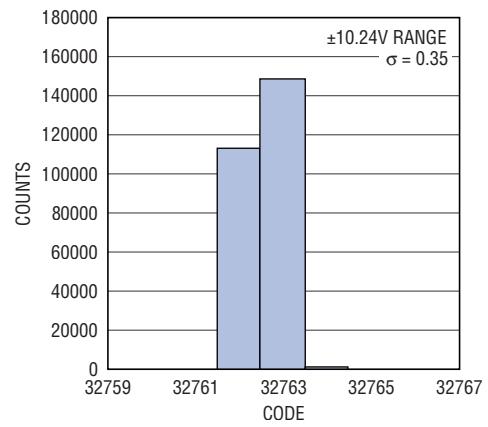

**DCヒストグラム(ゼロスケール)**

**DCヒストグラム

(フルスケール付近)**

234816fa

# LTC2348-16

## 標準的性能特性

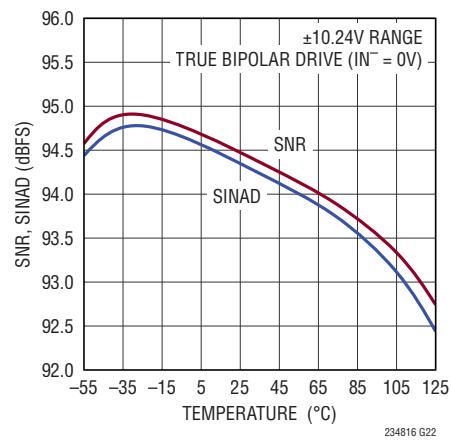

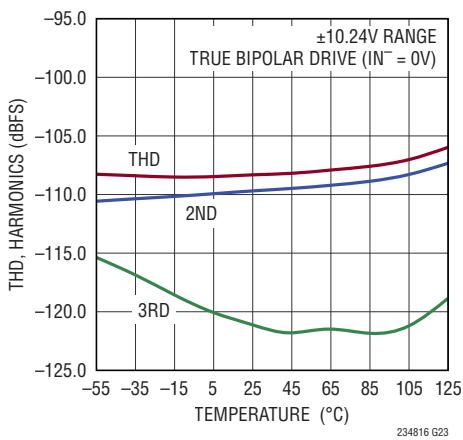

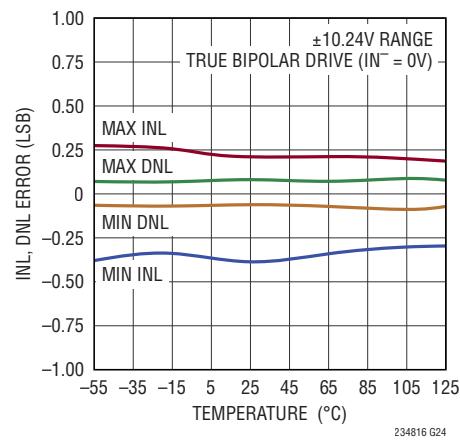

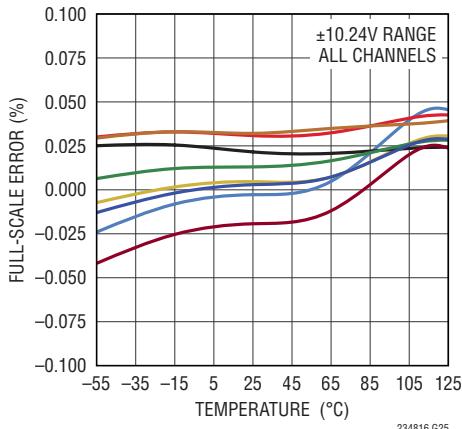

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{CC} = +15\text{V}$ 、 $V_{EE} = -15\text{V}$ 、 $V_{DD} = 5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、内部リファレンスとバッファ ( $V_{REFBUF} = 4.096\text{V}$ )、 $f_{SMPL} = 200\text{kspS}$ 。

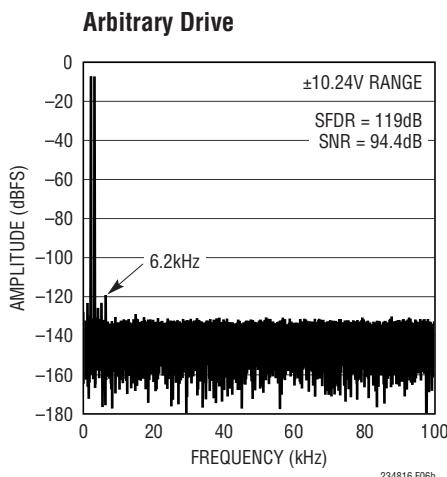

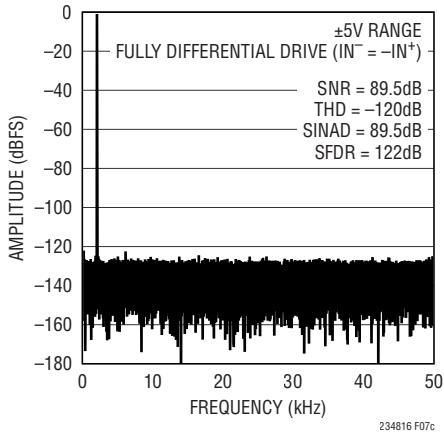

32kポイントのFFT、

$f_{SMPL} = 200\text{kHz}$ ,  $f_{IN} = 2\text{kHz}$

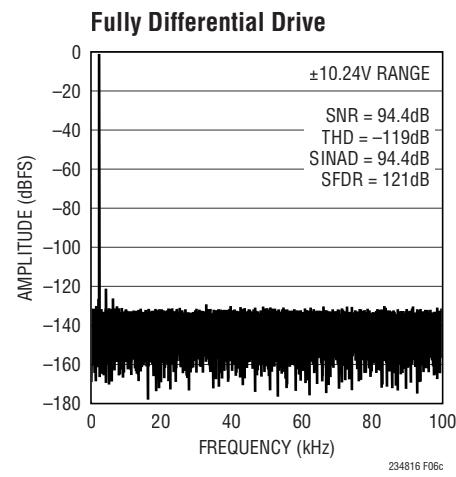

32kポイントのFFT、

$f_{SMPL} = 200\text{kHz}$ ,  $f_{IN} = 2\text{kHz}$

32kポイントの任意ソートーンFFT

$f_{SMPL} = 200\text{kHz}$ ,  $IN^+ = -7\text{dBFS}$  2kHz

正弦波,  $IN^- = -7\text{dBFS}$  3.1kHz 正弦波

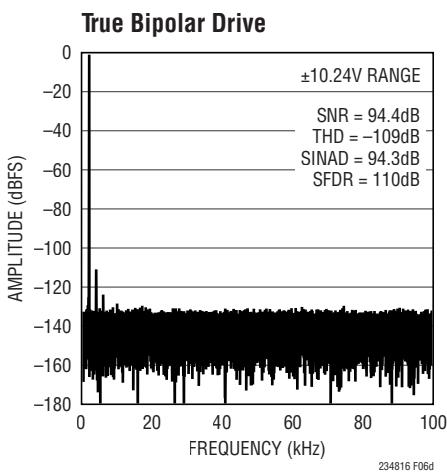

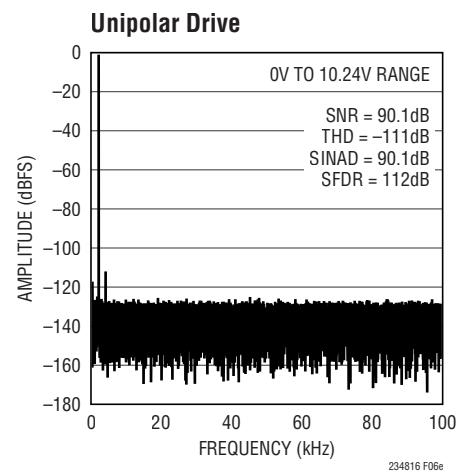

32kポイントのFFT  $f_{SMPL} = 200\text{kHz}$ 、

$f_{IN} = 2\text{kHz}$

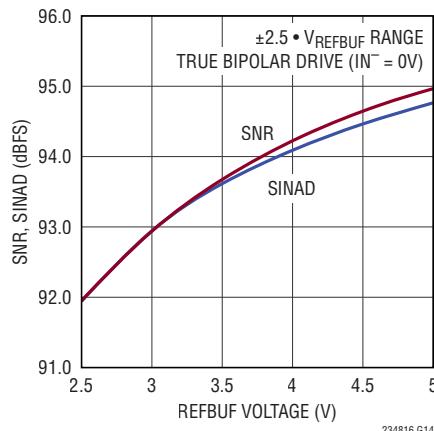

SNR および SINAD と  $V_{REFBUF}$ 、

$f_{IN} = 2\text{kHz}$

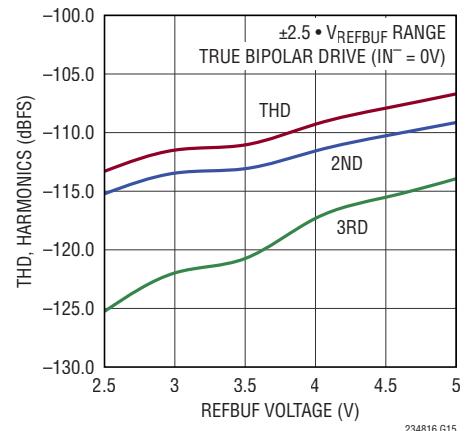

THD および高調波と  $V_{REFBUF}$ 、

$f_{IN} = 2\text{kHz}$

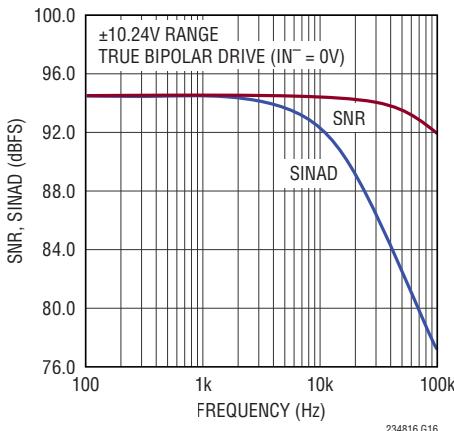

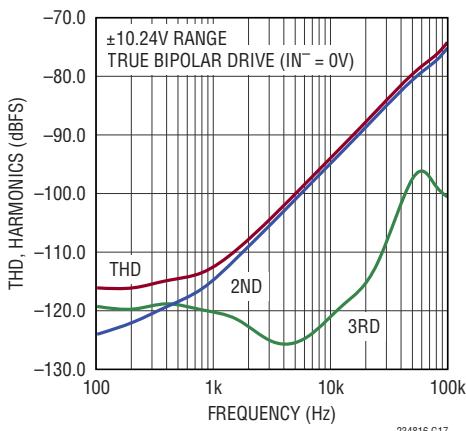

SNR および SINAD と入力周波数

THD および高調波と入力周波数

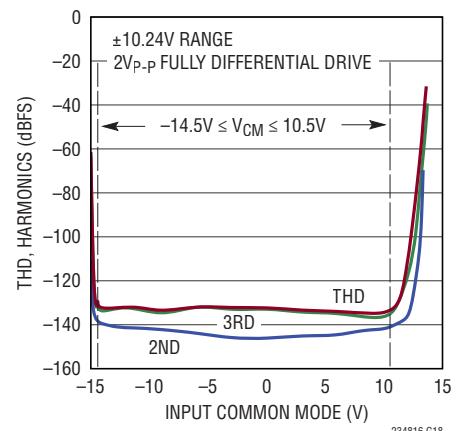

THD および高調波と入力同相電圧、

$f_{IN} = 2\text{kHz}$

234816fa

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{CC} = +15\text{V}$ 、 $V_{EE} = -15\text{V}$ 、 $V_{DD} = 5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、内部リファレンスとバッファ ( $V_{REFBUF} = 4.096\text{V}$ )、 $f_{SMPL} = 200\text{kspS}$ 。

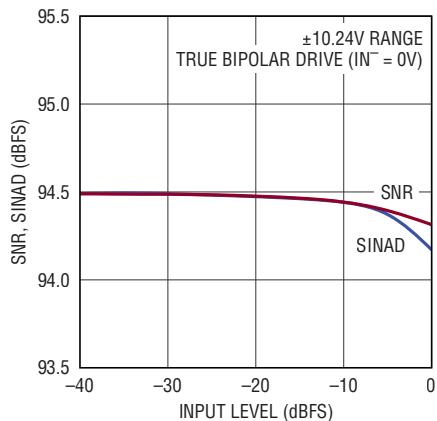

SNR および SINAD と入力レベル、

$f_{IN} = 2\text{kHz}$

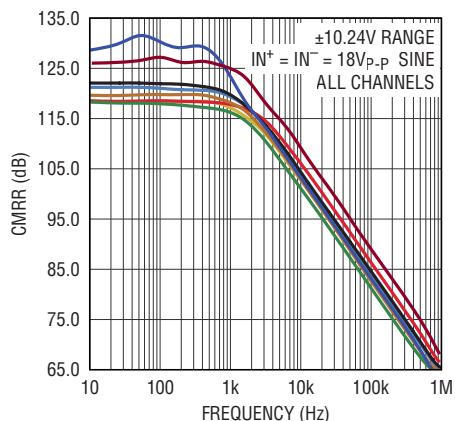

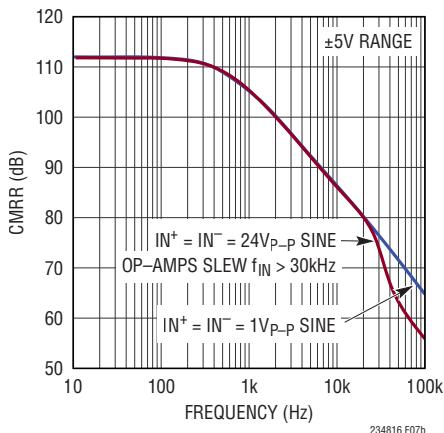

CMRR と入力周波数および

チャネル

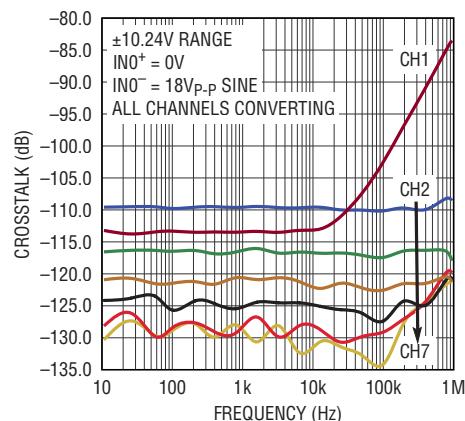

クロストークと入力周波数

およびチャネル

SNR および SINAD と温度、

$f_{IN} = 2\text{kHz}$

THD および高調波と温度、

$f_{IN} = 2\text{kHz}$

INL、DNL と温度

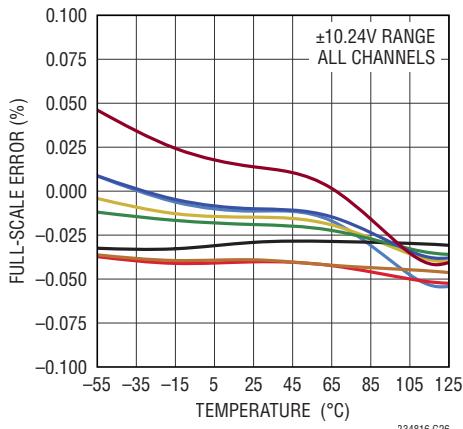

正のフルスケール誤差と

温度およびチャネル

負のフルスケール誤差と

温度およびチャネル

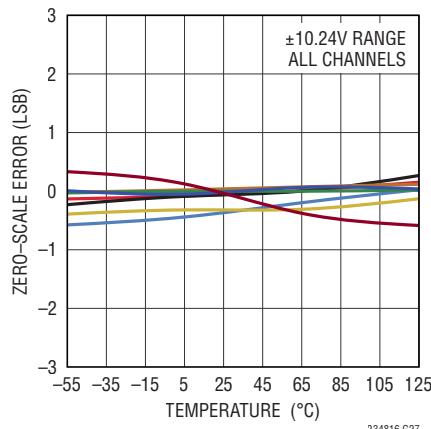

ゼロスケール誤差と

温度およびチャネル

**標準的性能特性** 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{CC} = +15\text{V}$ 、 $V_{EE} = -15\text{V}$ 、 $V_{DD} = 5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、内部リファレンスとバッファ ( $V_{REFBUF} = 4.096\text{V}$ )、 $f_{SMPL} = 200\text{kspS}$ 。

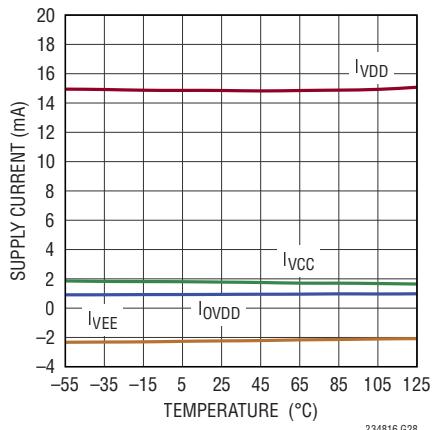

電源電流と温度

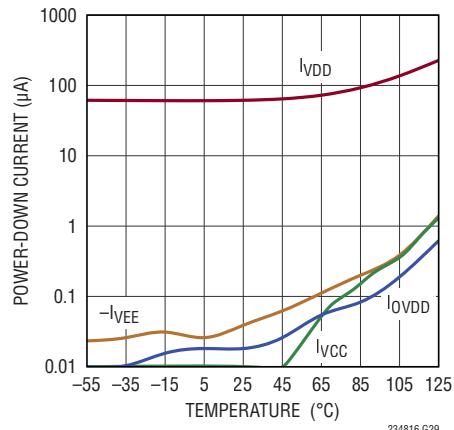

パワーダウン時電流と温度

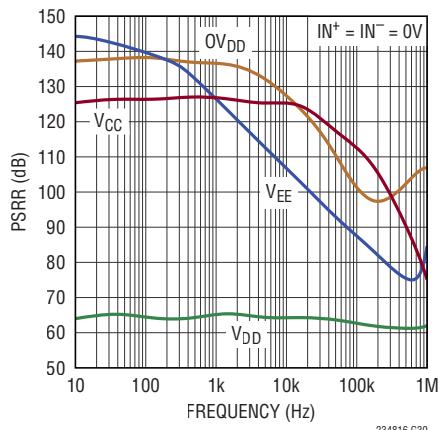

PSRRと周波数

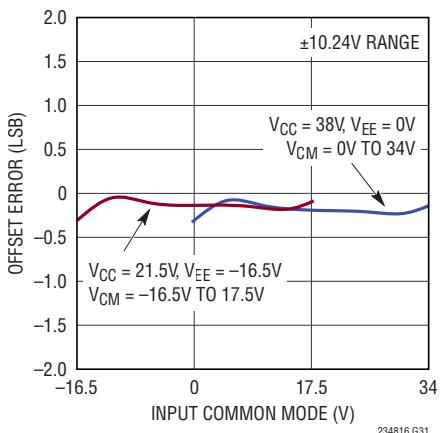

オフセット誤差と入力同相電圧

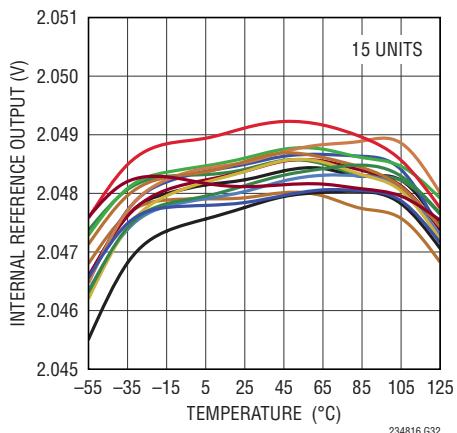

内部リファレンス出力と温度

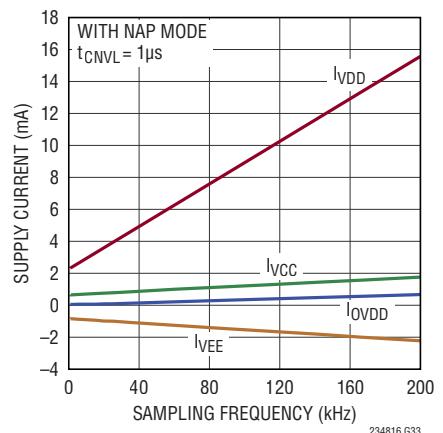

電源電流とサンプリング・レート

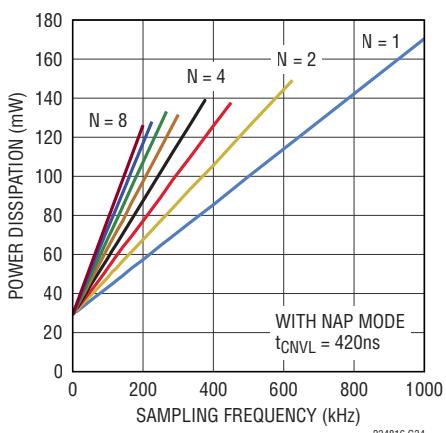

電力損失とサンプリング・レートおよびイネーブルされているチャネル数N

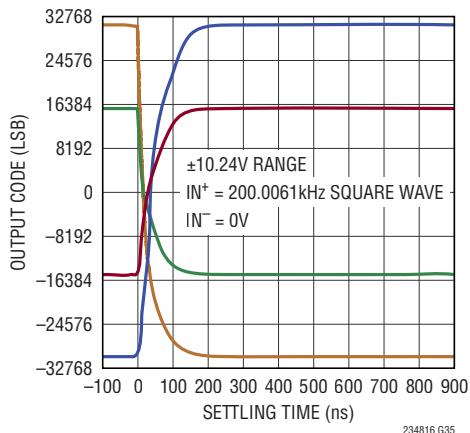

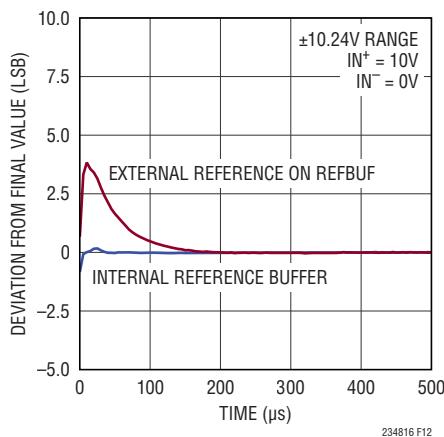

ステップ応答

(大信号セトリング時間)

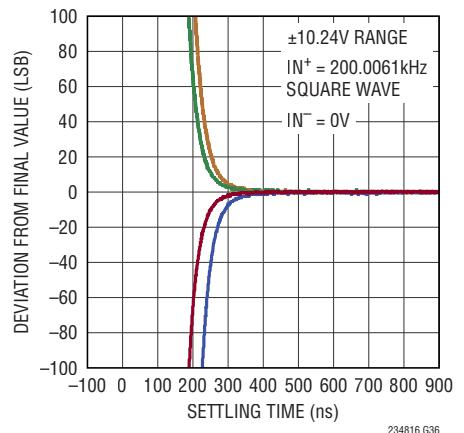

ステップ応答

(ファイン・セトリング時間)

## ピン機能

### 全てのデジタルI/Oモードで同じピン

**IN0<sup>+</sup>～IN7<sup>+</sup>、IN0<sup>-</sup>～IN7<sup>-</sup>(ピン1、2、3、4、5、6、7、8、9、10、11、12、13、14、47、48)**: 正と負のアナログ入力、チャネル0～7。コンバータは全てのチャネルの( $V_{IN+} - V_{IN-}$ )を同時にサンプリングし、デジタル化します。これらの入力は、入力同相電圧範囲が広く( $V_{EE} \leq V_{CM} \leq V_{CC} - 4V$ )、同相信号除去比が高いため、さまざまな信号の範囲に対応できます。フルスケール入力範囲は、チャネルのSoftSpan設定により決まります。

**GND(ピン15、18、20、30、41、44、46)**: グランド・ピン。全てのGNDピンを、切れ目のないグランド・プレーンに接続してください。

**V<sub>CC</sub>(ピン16)**: 正の高電圧電源。V<sub>CC</sub>の範囲は、GNDに対して0V～38V、V<sub>EE</sub>に対して10V～38Vです。V<sub>CC</sub>は、0.1μFのセラミック・コンデンサを使用してピンの近くでGNDにバイパスします。V<sub>CC</sub>をGNDに短絡させるアプリケーションの場合は、このコンデンサを省略できます。

**V<sub>EE</sub>(ピン17、45)**: 負の高電圧電源。V<sub>EE</sub>の範囲は、GNDに対して0V～−16.5V、V<sub>CC</sub>に対して−10V～−38Vです。ピン17と45を接続し、0.1μFのセラミック・コンデンサを使用して、V<sub>EE</sub>系統をピン17に近い位置でGNDにバイパスします。V<sub>EE</sub>をGNDに短絡せるアプリケーションの場合は、このコンデンサを省略できます。

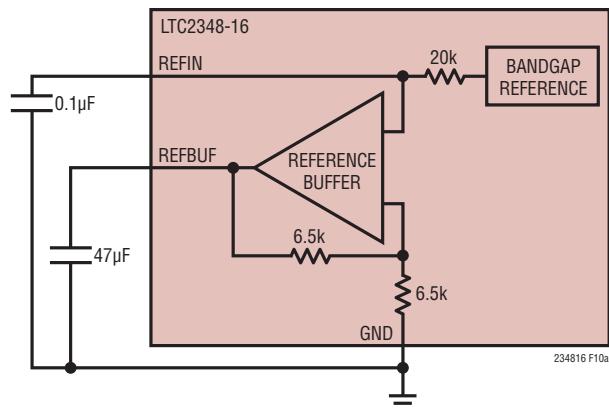

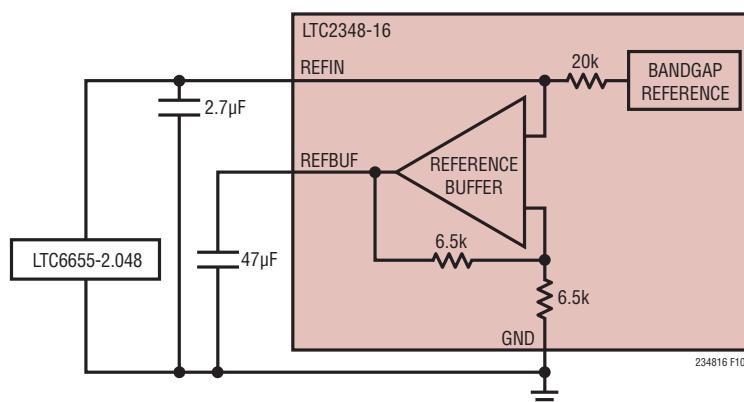

**REFIN(ピン19)**: バンドギャップ・リファレンス出力/リファレンス・バッファ入力。内蔵のバンドギャップ・リファレンスはこのピンに公称2.048Vを出力します。内部リファレンス・バッファは、V<sub>REFIN</sub>をコンバータのマスター・リファレンス電圧V<sub>REFBUF</sub> = 2 • V<sub>REFIN</sub>まで増幅してREFBUFピンに出力します。内部リファレンスを使用する場合は、バンドギャップ出力ノイズを除去するため、0.1μFのセラミック・コンデンサを使用してREFINをピンの近くでGND(ピン20)にバイパスします。さらに高い精度が必要な場合は、外部リファレンスによって1.25V～2.2Vの範囲でREFINをオーバードライブします。

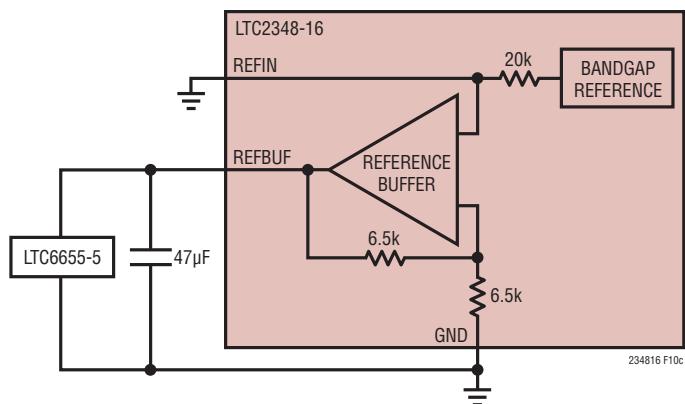

**REFBUF(ピン21)**: 内部リファレンス・バッファの出力。内部リファレンス・バッファは、V<sub>REFIN</sub>を増幅してコンバータのマスター・リファレンス電圧V<sub>REFBUF</sub> = 2 • V<sub>REFIN</sub>をこのピンに出力します。内部バンドギャップ・リファレンスを使用する場合、このピンの公称電圧は4.096Vです。REFBUFは、47μFのセラミック・コンデンサを使用してピンの近くでGND(ピン20)にバ

イパスします。内部リファレンス・バッファをディスエーブルするには、REFINのバッファ入力をグランド接続します。バッファをディスエーブルする場合は、外部リファレンス電圧を使用して2.5V～5Vの範囲でREFBUFをオーバードライブします。内部リファレンス・バッファを使用する場合は、REFBUFに接続される全ての外部回路の負荷を10μA未満に制限してください。外部回路へのV<sub>REFBUF</sub>は、高入力インピーダンス・アンプを使用してバッファすることを推奨します。

**PD(ピン22)**: パワーダウン入力。このピンが“H”になるとLTC2348-16はパワーダウンされ、その後の変換要求は無視されます。変換中にこの状態になった場合は、変換が完了した時点でデバイスがパワーダウン・モードになります。変換が行われていない間にこのピンを2回“H”にすると、パワーオン・リセット時と同様な内部グローバル・リセットが開始されます。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**LVDS/CMOS(ピン23)**: I/Oモードの選択。LVDS I/Oモードを選択する場合はこのピンをOV<sub>DD</sub>に接続し、CMOS I/Oモードを選択する場合はこのピンを接地します。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**CNV(ピン24)**: 変換開始入力。このピンの立ち上がりエッジで、内部のサンプル・アンド・ホールド回路がホールド・モードになり、新たに変換が開始されます。CNVはCSでゲート制御されていないため、シリアルI/Oバスの状態に関係なく変換を開始できます。

**BUSY(ピン38)**: ビジー出力。BUSY信号は、現在変換処理中であることを示します。このピンは各変換の開始時に“L”から“H”に遷移し、変換が完了するまで“H”的まとなります。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**V<sub>DDLYBYP</sub>(ピン40)**: 2.5Vの内部レギュレータのバイパス・ピン。このピンの電圧は、内部レギュレータを介してV<sub>DD</sub>から生成されます。このピンは、2.2μFのセラミック・コンデンサを使用してピンの近くでGNDにバイパスする必要があります。いかなる外部回路にも、このピンを接続しないでください。

**V<sub>DD</sub>(ピン42、43)**: 5V電源。V<sub>DD</sub>の範囲は4.75V～5.25Vです。ピン42と43を接続し、共有の0.1μFのセラミック・コンデンサを使用して、V<sub>DD</sub>系統をピンに近い位置でGNDにバイパスします。

## ピン機能

### CMOS I/Oモード

**SD00～SD07(ピン25、26、27、28、33、34、35、および36)：**CMOSシリアル・データ出力、チャネル0～7。SCKIの各立ち上がりエッジで、最新の変換結果とチャネル構成情報がSDOピンに出力されます。出力データの形式については、「デジタル・インターフェース」の項を参照してください。使用しないSDO出力ピンには何も接続しないでください。ロジック・レベルはOV<sub>DD</sub>によって決ります。

**SCKI(ピン29)：**CMOSシリアル・クロック入力。SCKIは、シリアルI/Oクロックで駆動してください。SCKIの立ち上がりエッジでSDIのシリアル・データがラッチされ、シリアル・データがSDO0～SDO7に出力されます。標準的なSPIバス動作の場合は、SCKIの立ち上がりエッジでレシーバの出力データを捕捉してください。SCKIは、“H”でも“L”でもアイドリング状態にできます。ロジック・レベルはOV<sub>DD</sub>によって決ります。

**OV<sub>DD</sub>(ピン31)：**I/Oインターフェースの電源。CMOS I/Oモード時、OV<sub>DD</sub>の範囲は1.71V～5.25Vです。OV<sub>DD</sub>は、0.1μFのセラミック・コンデンサを使用してピンの近くでGND(ピン30)にバイパスします。

**SCK0(ピン32)：**CMOSシリアル・クロック出力。SCKIの立ち上がりエッジは、SDO0～SDO7のシリアル出力データ・ストリームにスキー・マッチングされるSCK0の遷移をトリガします。その結果、SCK0の周波数はSCKの1/2になります。SCK0の立ち上がりエッジと立ち下がりエッジを使用すると、レシーバ(FPGA)のSDOデータを2倍のデータ・レート(DDR)で捕捉できます。標準的なSPIバス動作の場合は、SCK0は使用せず、未接続のままにしておいてください。SCK0は、BUSYの立ち下がりエッジで強制的に“L”になります。ロジック・レベルはOV<sub>DD</sub>によって決ります。

**SDI(ピン37)：**CMOSシリアル・データ入力。このピンは、SCKIの立ち上がりエッジでラッチされた、必要に応じた24ビットのSoftSpan設定ワード(表1aを参照)で駆動してください。全てのチャネルをSoftSpan 7のみで動作するように設定する場合は、SDIをOV<sub>DD</sub>に接続します。ロジック・レベルはOV<sub>DD</sub>によって決ります。

**CS(ピン39)：**チップ・セレクト入力。シリアル・データI/OバスはCSピンが“L”になるとイネーブルされ、CSピンが“H”になるとディスエーブルされます。CSは、外部シフト・クロックSCKIをゲート制御することもできます。ロジック・レベルはOV<sub>DD</sub>によって決ります。

### LVDS I/Oモード

**SD00、SD07、SDI(ピン25、36、37)：**CMOSシリアル・データの入出力。LVDS I/Oモード時、これらのピンは高インピーダンスになります。

**SDI<sup>+</sup>、SDI<sup>-</sup>(ピン26、27)：**LVDSの正負のシリアル・データ入力。SDI<sup>+/SDI<sup>-</sup>は、SCKI<sup>+/SCKI<sup>-</sup>の立ち上がりエッジと立ち下がりエッジの両方でラッチされた、必要に応じた24ビットのSoftSpan設定ワード(表1aを参照)で差動駆動してください。SDI<sup>+/SDI<sup>-</sup>入力のペアは、CSが“L”的ときは100Ωの差動抵抗で内部的に終端されます。</sup></sup></sup>

**SCKI<sup>+</sup>、SCKI<sup>-</sup>(ピン28、29)：**LVDSの正負のシリアル・クロック入力。SCKI<sup>+/SCKI<sup>-</sup>は、シリアルI/Oクロックで差動駆動してください。SCKI<sup>+/SCKI<sup>-</sup>の立ち上がりエッジと立ち下がりエッジでSDI<sup>+/SDI<sup>-</sup>のシリアル・データがラッチされ、シリアル・データがSDO<sup>+/SDO<sup>-</sup>に出力されます。CSの遷移時などには、SCKI<sup>+/SCKI<sup>-</sup>を“L”でアイドリング状態に保持してください。SCKI<sup>+/SCKI<sup>-</sup>入力のペアは、CS = 0のときは100Ωの差動抵抗で内部的に終端されます。</sup></sup></sup></sup></sup></sup>

**OV<sub>DD</sub>(ピン31)：**I/Oインターフェースの電源。LVDS I/Oモード時、OV<sub>DD</sub>の範囲は2.375V～5.25Vです。OV<sub>DD</sub>は、0.1μFのセラミック・コンデンサを使用してピンの近くでGND(ピン30)にバイパスします。

**SCK0<sup>+</sup>、SCK0<sup>-</sup>(ピン32、33)：**LVDSの正負のシリアル・クロック出力。SCK0<sup>+/SCK0<sup>-</sup>は、SCKI<sup>+/SCKI<sup>-</sup>に入力されSDO<sup>+/SDO<sup>-</sup>のシリアル・データ・ストリームとスキー・マッチングされたシリアルI/Oクロックを出力します。SCK0<sup>+/SCK0<sup>-</sup>の立ち上がりエッジと立ち下がりエッジを使用すると、レシーバ(FPGA)のSDO<sup>+/SDO<sup>-</sup>データを捕捉できます。SCK0<sup>+/SCK0<sup>-</sup>出力のペアは、レシーバ(FPGA)で100Ωの抵抗を使用して差動で終端する必要があります。</sup></sup></sup></sup></sup></sup>

**SDO<sup>+</sup>、SDO<sup>-</sup>(ピン34、35)：**LVDSの正負のシリアル・データ出力。SCKI<sup>+/SCKI<sup>-</sup>の立ち上がりエッジと立ち下がりエッジの両方で、最新の変換結果とチャネル構成情報がSDO<sup>+/SDO<sup>-</sup>に出力されます。動作はチャネル0から実行されます。SDO<sup>+/SDO<sup>-</sup>出力のペアは、レシーバ(FPGA)で100Ωの抵抗を使用して差動で終端する必要があります。</sup></sup></sup>

**CS(ピン39)：**チップ・セレクト入力。シリアル・データI/OバスはCSピンが“L”になるとイネーブルされ、CSピンが“H”になるとディスエーブルされ高インピーダンスになります。CSは、外部シフト・クロックSCKI<sup>+/SCKI<sup>-</sup>をゲート制御することもできます。CSが“H”的ときは、SCKI<sup>+/SCKI<sup>-</sup>とSDI<sup>+/SDI<sup>-</sup>の入力ペアの内部100Ω差動終端抵抗がディスエーブルされます。ロジック・レベルはOV<sub>DD</sub>によって決ります。</sup></sup></sup>

## 設定値一覧表

表1a. SoftSpan 設定値一覧表。この表と表1bを使用して、必要なアナログ入力レンジに応じて、各チャネルに使用する個々のSoftSpanのバイナリ・コードSS[2:0]を選択してください。複数のSoftSpanコードを組み合わせて24ビットのSoftSpan設定ワードS[23:0]を作成します。図19のように、シリアル・インターフェースを使用してLTC2348-16にSoftSpan設定ワードを書き込みます。

| バイナリ SoftSpan コード<br>SS[2:0] | アナログ入力電圧レンジ                        | フルスケール電圧範囲                   | 変換結果のバイナリ形式      |

|------------------------------|------------------------------------|------------------------------|------------------|

| 111                          | $\pm 2.5 \cdot V_{REFBUF}$         | $5 \cdot V_{REFBUF}$         | Two's Complement |

| 110                          | $\pm 2.5 \cdot V_{REFBUF}/1.024$   | $5 \cdot V_{REFBUF}/1.024$   | Two's Complement |

| 101                          | 0V to $2.5 \cdot V_{REFBUF}$       | $2.5 \cdot V_{REFBUF}$       | Straight Binary  |

| 100                          | 0V to $2.5 \cdot V_{REFBUF}/1.024$ | $2.5 \cdot V_{REFBUF}/1.024$ | Straight Binary  |

| 011                          | $\pm 1.25 \cdot V_{REFBUF}$        | $2.5 \cdot V_{REFBUF}$       | Two's Complement |

| 010                          | $\pm 1.25 \cdot V_{REFBUF}/1.024$  | $2.5 \cdot V_{REFBUF}/1.024$ | Two's Complement |

| 001                          | 0V to $1.25 \cdot V_{REFBUF}$      | $1.25 \cdot V_{REFBUF}$      | Straight Binary  |

| 000                          | Channel Disabled                   | Channel Disabled             | All Zeros        |

表1b. リファレンス設定値一覧表。LTC2348-16では、リファレンスを以下の3種類のいずれかに設定できます。アナログ入力範囲のスケールとコンバータのマスター・リファレンス電圧、 $V_{REFBUF}$

| リファレンス設定値                                    | $V_{REFIN}$          | $V_{REFBUF}$ | バイナリ SoftSpan コード<br>SS[2:0] | アナログ入力電圧レンジ   |

|----------------------------------------------|----------------------|--------------|------------------------------|---------------|

| 内部リファレンスと内部バッファ                              | 2.048V               | 4.096V       | 111                          | $\pm 10.24V$  |

|                                              |                      |              | 110                          | $\pm 10V$     |

|                                              |                      |              | 101                          | 0V to 10.24V  |

|                                              |                      |              | 100                          | 0V to 10V     |

|                                              |                      |              | 011                          | $\pm 5.12V$   |

|                                              |                      |              | 010                          | $\pm 5V$      |

|                                              |                      |              | 001                          | 0V to 5.12V   |

| 外部リファレンスと内部バッファ<br>(REFINピンを外部で<br>オーバードライブ) | 1.25V<br>(Min Value) | 2.5V         | 111                          | $\pm 6.25V$   |

|                                              |                      |              | 110                          | $\pm 6.104V$  |

|                                              |                      |              | 101                          | 0V to 6.25V   |

|                                              |                      |              | 100                          | 0V to 6.104V  |

|                                              |                      |              | 011                          | $\pm 3.125V$  |

|                                              |                      |              | 010                          | $\pm 3.052V$  |

|                                              |                      |              | 001                          | 0V to 3.125V  |

|                                              |                      |              | 111                          | $\pm 11V$     |

|                                              | 2.2V<br>(Max Value)  | 4.4V         | 110                          | $\pm 10.742V$ |

|                                              |                      |              | 101                          | 0V to 11V     |

|                                              |                      |              | 100                          | 0V to 10.742V |

|                                              |                      |              | 011                          | $\pm 5.5V$    |

|                                              |                      |              | 010                          | $\pm 5.371V$  |

|                                              |                      |              | 001                          | 0V to 5.5V    |

# LTC2348-16

## 設定値一覧表

表1b リファレンス設定値一覧表(続き)。LTC2348-16では、リファレンスを以下の3種類のいずれかに設定できます。

アナログ入力範囲のスケールとコンバータのマスタ・リファレンス電圧、 $V_{REFBUF}$

| リファレンス設定値                                                    | $V_{REFIN}$ | $V_{REFBUF}$        | バイナリ SoftSpan コード<br>SS[2:0] | アナログ入力電圧レンジ   |

|--------------------------------------------------------------|-------------|---------------------|------------------------------|---------------|

| 外部リファレンス、バッファなし<br>(REFBUFピンを外部で<br>オーバードライブ、<br>REFINピンを接地) | 0V          | 2.5V<br>(Min Value) | 111                          | $\pm 6.25V$   |

|                                                              |             |                     | 110                          | $\pm 6.104V$  |

|                                                              |             |                     | 101                          | 0V to 6.25V   |

|                                                              |             |                     | 100                          | 0V to 6.104V  |

|                                                              |             |                     | 011                          | $\pm 3.125V$  |

|                                                              |             |                     | 010                          | $\pm 3.052V$  |

|                                                              |             |                     | 001                          | 0V to 3.125V  |

|                                                              | 0V          | 5V<br>(Max Value)   | 111                          | $\pm 12.5V$   |

|                                                              |             |                     | 110                          | $\pm 12.207V$ |

|                                                              |             |                     | 101                          | 0V to 12.5V   |

|                                                              |             |                     | 100                          | 0V to 12.207V |

|                                                              |             |                     | 011                          | $\pm 6.25V$   |

|                                                              |             |                     | 010                          | $\pm 6.104V$  |

|                                                              |             |                     | 001                          | 0V to 6.25V   |

234816fa

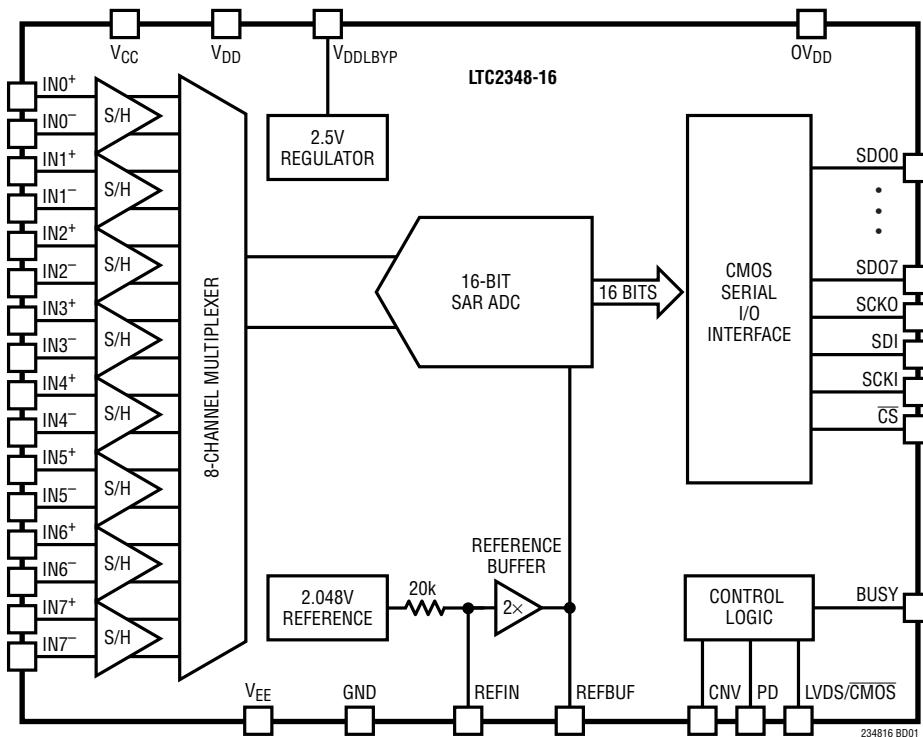

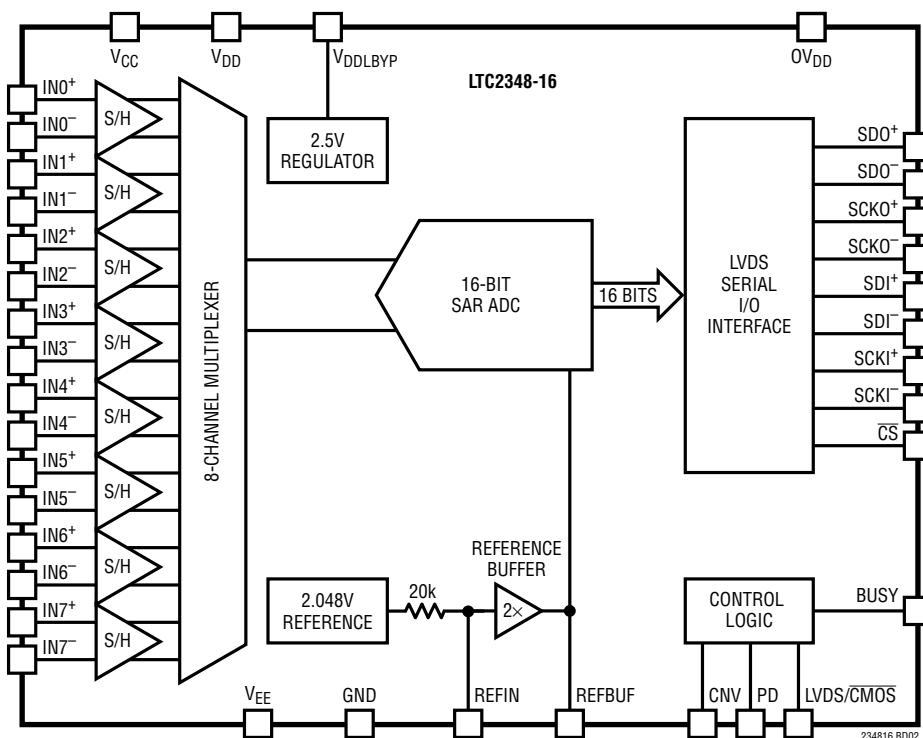

## 機能ブロック図

CMOS I/O モード

LVDS I/O モード

234816fa

# LTC2348-16

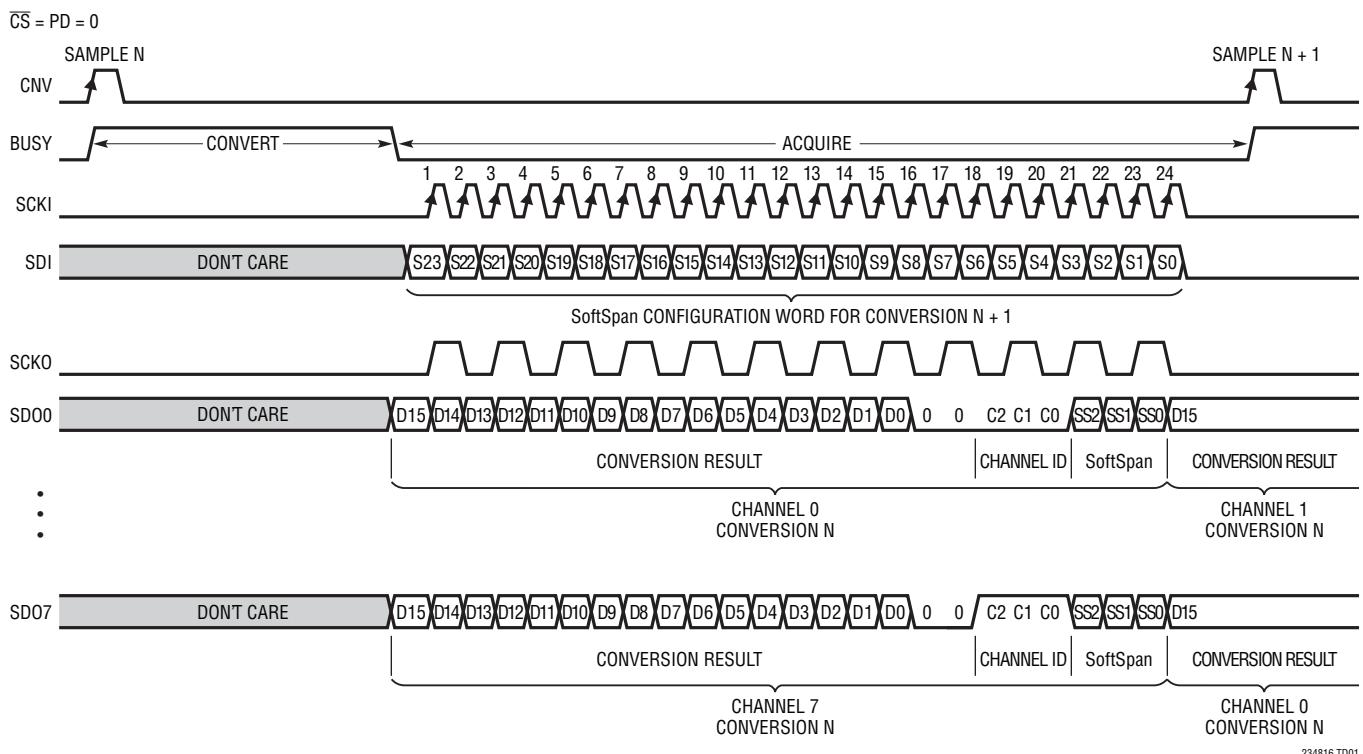

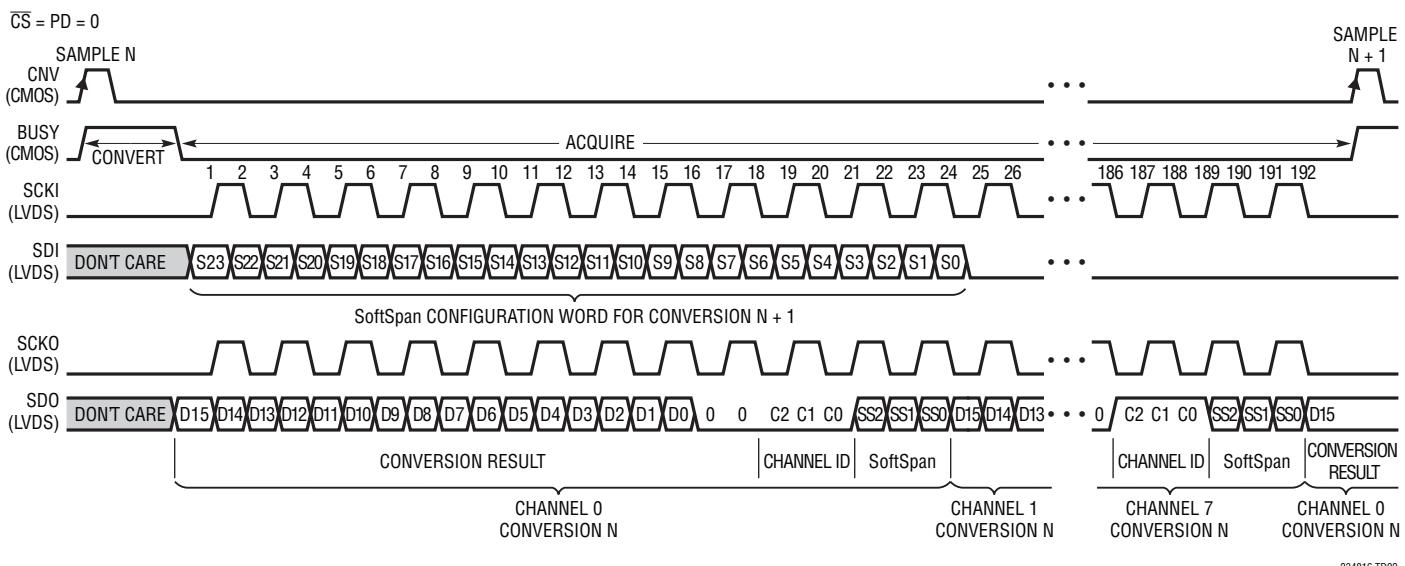

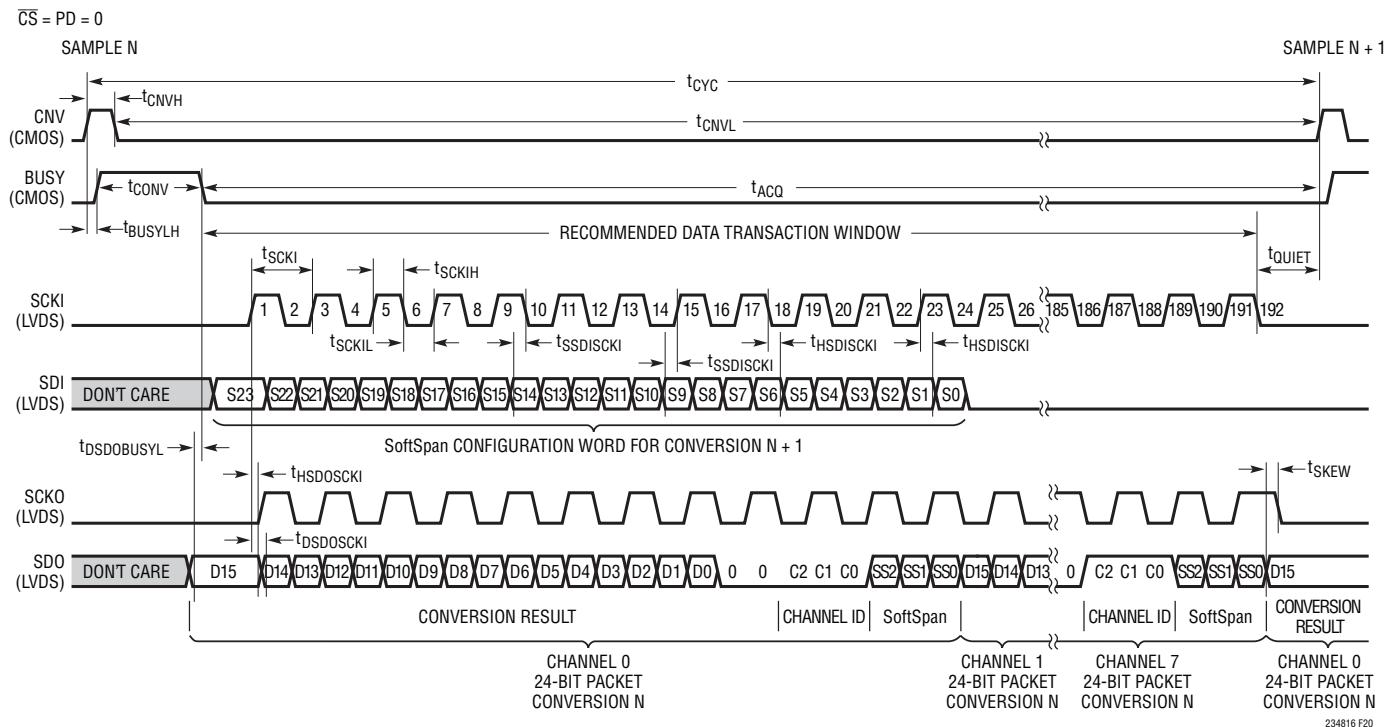

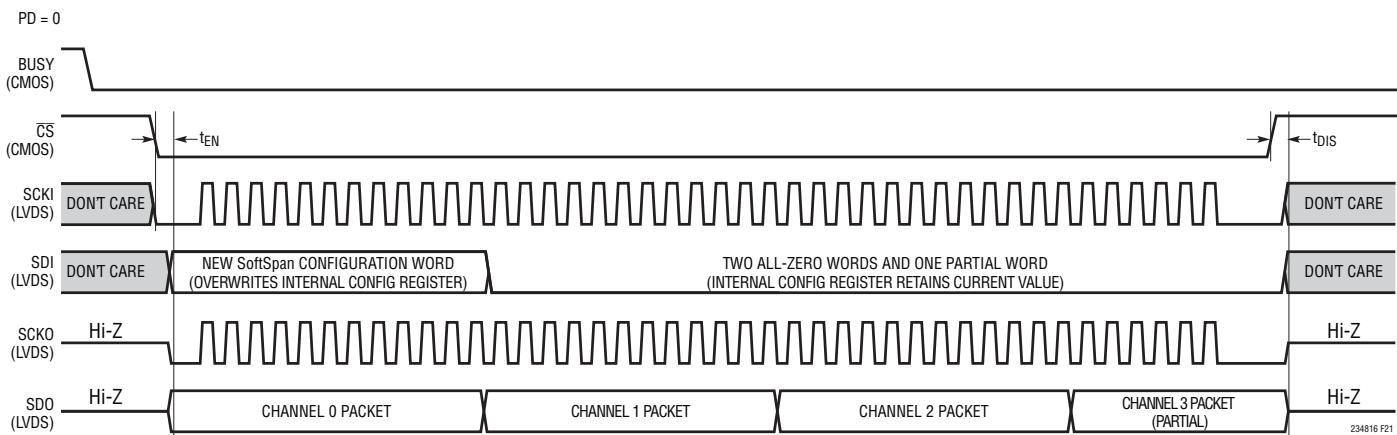

## タイミング図

### CMOS I/O モード

### LVDS I/O モード

234816fa

## アプリケーション情報

### 概要

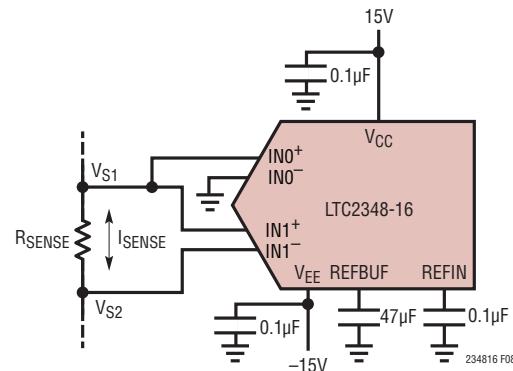

LTC2348-16は、差動入力で入力同相電圧範囲の広い、16ビット、低ノイズ、8チャネル、同時サンプリング逐次比較レジスタ(SAR) A/Dコンバータです。このA/Dコンバータは、5Vの低電圧から公称±15Vの高電圧まで柔軟に対応して動作できます。低ドリフトの内蔵リファレンスとバッファ(V<sub>REFBUF</sub> = 公称4.096V)を使用できる、このSoftSpan A/Dコンバータの各チャネルは、変換ごとに、±10.24V、0V ~ 10.24V、±5.12V、または0V ~ 5.12Vの信号を入力できるよう、個別に設定できます。外部12.5Vリファレンスを使用すると、入力信号範囲を最大±5Vまで拡大できます。また、チャネルを個別にディスエーブルして他のチャネルのスループットを上げることもできます。

LTC2348-16のアナログ入力は入力同相電圧範囲が広くCMRRが大きい(標準で118dB、V<sub>IN+</sub> = V<sub>IN-</sub> = 18VP-P 200Hz正弦波)ため、さまざまな信号をA/Dコンバータで直接デジタル化でき、信号チェーンの設計を簡素化できます。絶対同相入力電圧の範囲は、高電圧電源の選択により決まり、グランドを中心に非対称にバイアスでき、正または負の電源をグランドに直接接続することもできます。このような入力信号の柔軟性と±1LSBのINL、欠落コードのない16ビットの分解能、94.4dBのSNRを有するLTC2348-16は、広いダイナミック・レンジが要求されるさまざまな高電圧用途に最適です。

LTC2348-16には、ピンで選択可能なSPI CMOS(1.8V ~ 5V)とLVDSのシリアル・インターフェースが用意されており、旧型のマイクロコントローラとも最新のFPGAとも同等に通信できます。CMOSモード時はアプリケーションが使用するシリアル出力データ・レーン数を1~8個の間で調整できるため、バス幅とデータ・スループットを最適化できます。通常、LTC2348-16で、各チャネルのスループットが200kspsの条件で8つのアナログ入力チャネルを同時に変換するときの消費電力は、140mWです。オプションのナップ・モードとパワーダウン・モードを使用すると、非動作時の消費電力をさらに低減できます。

### コンバータの動作

LTC2348-16は2つの段階で動作します。収集段階では、各チャネルのサンプル・アンド・ホールド(S/H)回路のサンプル・コンデンサが対応するアナログ入力ピンに接続され、差動アナログ入力電圧(V<sub>IN+</sub> - V<sub>IN-</sub>)に追従します。CNVピンの立ち上がりエッジで、全てのチャネルのサンプル・アンド・ホールド回路がトラック・モードからホールド・モードになり、全てのチャネルの入力信号を同時にサンプリングして変換を開始します。変換段階では、同時に1つずつ、各チャネルのサンプリング・コンデンサが16ビットの電荷再分配型コンデンサD/Aコンバータ(CDAC)に接続されます。CDACは逐次比較アルゴリズムにより逐次制御され、差動コンパレータを使用して、サンプリングされた入力電圧を、チャネルのSoftSpanフルスケール範囲のバイナリ加重した分数(例: V<sub>FSR</sub>/2, V<sub>FSR</sub>/4 … V<sub>FSR</sub>/65536)と、効率的に比較します。この処理の終了時、CDACの出力はチャネルのサンプリングされたアナログ入力を近似する値になります。こうして全てのチャネルが変換されると、A/Dコンバータの制御ロジックが各チャネルから16ビットのデジタル出力コードを準備して、シリアル転送に備えます。

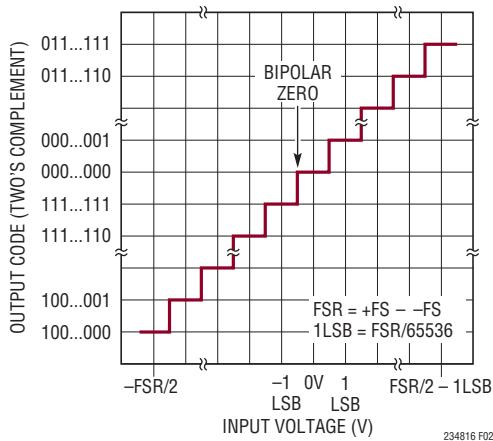

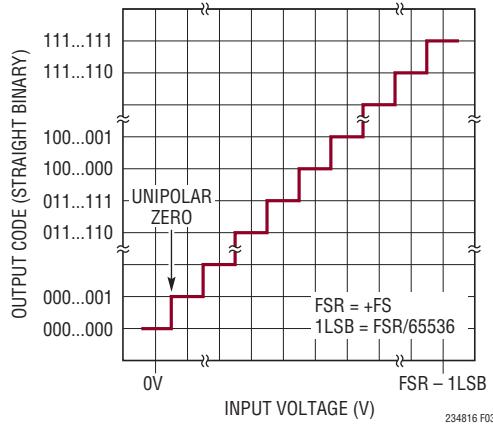

### 伝達関数

LTC2348-16は、各チャネルのフルスケールの電圧範囲を2<sup>16</sup>レベルにデジタル化します。表1a、1bのように、A/Dコンバータのマスター・リファレンス電圧V<sub>REFBUF</sub>とチャネルのSoftSpan設定により、入力電圧レンジ、フルスケール範囲、 LSBのサイズ、変換結果のバイナリ形式が決まります。たとえば、内部リファレンスとバッファ(V<sub>REFBUF</sub> = 公称値4.096V)を使用し、SoftSpan 7でチャネルが±10.24Vの双極性アナログ入力電圧レンジに対応するように設定する場合は、フルスケール範囲20.48V、LSB 312.5μVになります。その他のSoftSpan設定とリファレンス電圧を使用して、より広範囲の双極性、単極性の入力を変換することもできます。変換結果は、いずれの双極性SoftSpanレンジでも2の補数のバイナリ形式で出力され、いずれの単極性SoftSpanレンジでもストレート・バイナリ形式で出力されます。理想的な2の補数の伝達関数を図2に、理想的なストレート・バイナリの伝達関数を図3に示します。

# LTC2348-16

## アプリケーション情報

図2. LTC2348-16の2の補数の伝達関数

図3. LTC2348-16のストレート・バイナリ伝達関数

## アナログ入力

LTC2348-16の各チャネルは、A/Dコンバータの同相信号除去比(CMRR)が高いいため両入力ピンに共通な不要な信号を抑制して、広い同相入力電圧範囲にわたってアナログ入力ピン間の電圧差( $V_{IN+} - V_{IN-}$ )を同時にサンプリングできます。同相入力電圧範囲が広くCMRRが高いため、各ピンの電圧が( $V_{CC} - 4V$ )～ $V_{EE}$ の範囲内に保たれた場合は、アナログ入力 $IN^+$ / $IN^-$ が相互に自由な関係で振れることができます。このユニークな特長を備えたLTC2348-16は、疑似差動の単極性信号、疑似差動の真の双極性信号、完全差動信号などの従来型のアナログ入力信号を含むさまざまな信号の範囲に対応でき、信号チェーンの設計を簡素化できます。

高圧電源で動作範囲が広いため、入力同相電圧の柔軟性が高くなります。電圧差の限界値( $10V \leq V_{CC} - V_{EE} \leq 38V$ )の条件が守られている限り、 $V_{CC}$ と $V_{EE}$ をそれぞれの許容動作範囲内の任意の値に個別にバイアスでき、いずれかの電源を直接グランドに接続することもできます。LTC2348-16は、同相入力電圧範囲がこのような特長を備えているため、個々のアプリケーションの条件に合わせて対応できます。

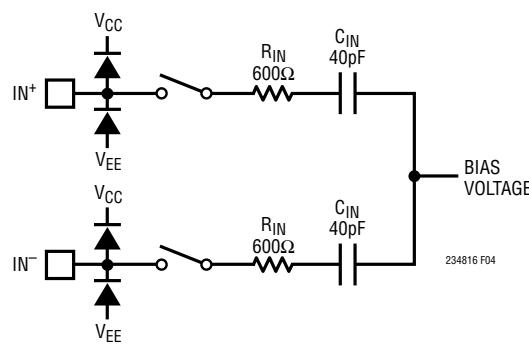

全てのSoftSpanレンジで、各チャネルのアナログ入力を、図4に示す等価回路によりモデル化できます。収集動作開始時、40pFのサンプリング・コンデンサ( $C_{IN}$ )は、それぞれのオン抵抗が約 $600\Omega$ ( $R_{IN}$ )のサンプリング・スイッチを介してアナログ入力ピン $IN^+$ / $IN^-$ に接続されます。収集開始時の両方のサンプリング・コンデンサの初期電圧は、前回の変換からサンプリングされた同相電圧( $V_{IN+} + V_{IN-}$ )/2とほぼ同じ値になります。 $IN^+$ と $IN^-$ に接続される外部回路は、収集動作周期の間にサンプリング・コンデンサが初期電圧から新たな入力ピン電圧になるときに、ソースまたはシンクとして、 $R_{IN}$ に電流を流す必要があります。変換時や、ナップ・モード時、パワーダウン・モード時にアナログ入力に流れるのはわずかな漏れ電流だけです。入力のダイオードはESD保護機能を果たします。

図4. 差動アナログ入力の等価回路

(図は1つのチャネルを示す)

## アプリケーション情報

### 両極性 SoftSpan 入力電圧レンジ

チャネルをSoftSpanレンジ7、6、3、または2に設定した場合、表1aのように、LTC2348-16は、それぞれ  $\pm 2.5 \cdot V_{REFBUF}$ 、 $\pm 2.5 \cdot V_{REFBUF}/1.024$ 、 $\pm 1.25 \cdot V_{REFBUF}$ 、または  $\pm 1.25 \cdot V_{REFBUF}/1.024$ の双極性レンジ上で差動アナログ入力電圧( $V_{IN+} - V_{IN-}$ )をデジタル化します。これらのSoftSpanレンジは、 $IN^+$ と $IN^-$ が相互に上下に振れるような入力信号をデジタル化する場合に役立ちます。典型的な例としては、同相電圧( $V_{IN+} + V_{IN-}$ )/2を中心にして相互の位相差が180度の状態で $IN^+$ と $IN^-$ が駆動される場合や、 $IN^-$ で駆動されて基準となるグランド・レベルの上下に振れる疑似差動の真の双極性の入力信号の場合などがあります。選択されているSoftSpanレンジに関わらず、 $IN^+/IN^-$ アナログ入力の同相入力電圧範囲が広くCMRRが高いため、各ピンの電圧が( $V_{CC} - 4V$ )と $V_{EE}$ の範囲内に保たれた場合は、これらのアナログ入力が相互に自由な関係で振れることができます。全ての双極性SoftSpanレンジで出力データは2の補数形式です。

### 単極性 SoftSpan 入力電圧レンジ

チャネルをSoftSpanレンジ5、4、または1に設定した場合、表1aのように、LTC2348-16は、それぞれ  $0V \sim 2.5 \cdot V_{REFBUF}$ 、 $0V \sim 2.5 \cdot V_{REFBUF}/1.024$ 、または  $0V \sim 1.25 \cdot V_{REFBUF}$ の単極性レンジ上で差動アナログ入力電圧( $V_{IN+} - V_{IN-}$ )をデジタル化します。これらのSoftSpanレンジは、 $IN^+$ が $IN^-$ より大きい値に保たれるような入力信号をデジタル化する場合に役立ちます。典型的な例としては、 $IN^+$ が $IN^-$ で駆動されて基準となるグランド・レベルより大きい範囲で振れるような疑似差動単極性入力信号の場合などがあります。選択されているSoftSpanレンジに関わらず、 $IN^+/IN^-$ アナログ入力の同相入力電圧範囲が広くCMRRが高いため、各ピンの電圧が( $V_{CC} - 4V$ )～ $V_{EE}$ の範囲内に保たれた場合は、これらのアナログ入力が相互に自由な関係で振れることができます。全ての単極性SoftSpanレンジで出力データはストレート・バイナリ形式です。

### 入力駆動回路

収集周期の間に、収集開始時の各チャネルのサンプリング・コンデンサの初期電圧が新たな入力ピン電圧に遷移して収束する必要があります。 $IN^+$ と $IN^-$ に接続される外部回路は、このセトリング動作時に、ソースまたはシンクとして、 $R_{IN}$ に電流を流す必要があります。LTC2348-16のサンプリング回路網のRC時定数が24nsであるため、フルスケール・ステップへの16ビットのセトリング時間は、約  $11 \cdot (R_{IN} \cdot C_{IN}) = 264\text{ns}$ になります。アナログ入力ピンに接続されている外部回路自身のインピーダンスとセトリング時間のため、全体のセトリングに要する時間は長くなります。低インピーダンスの信号源は、利得誤差なくLTC2348-16の入力を直接駆動できますが、高インピーダンスの信号源は、収集時に十分にセトリングを行えA/Dコンバータの直線性と歪み性能を最適化できるよう、バッファが必要があります。DC入力信号の場合でも、サンプリング・コンデンサの電圧が、収集開始時のアナログ入力ピンの電圧とは異なるため、セトリング時間に配慮することは重要です。

ほとんどの用途では、バッファ・アンプを使用してLTC2348-16のアナログ入力を駆動する必要があります。バッファ・アンプは出力インピーダンスが低いため、収集段階でアナログ信号の高速セトリングが可能です。また、バッファ・アンプは、収集開始時に信号源とアナログ入力での電荷の流れを切り離します。

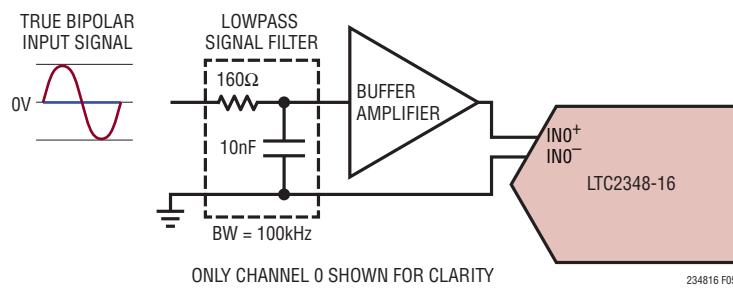

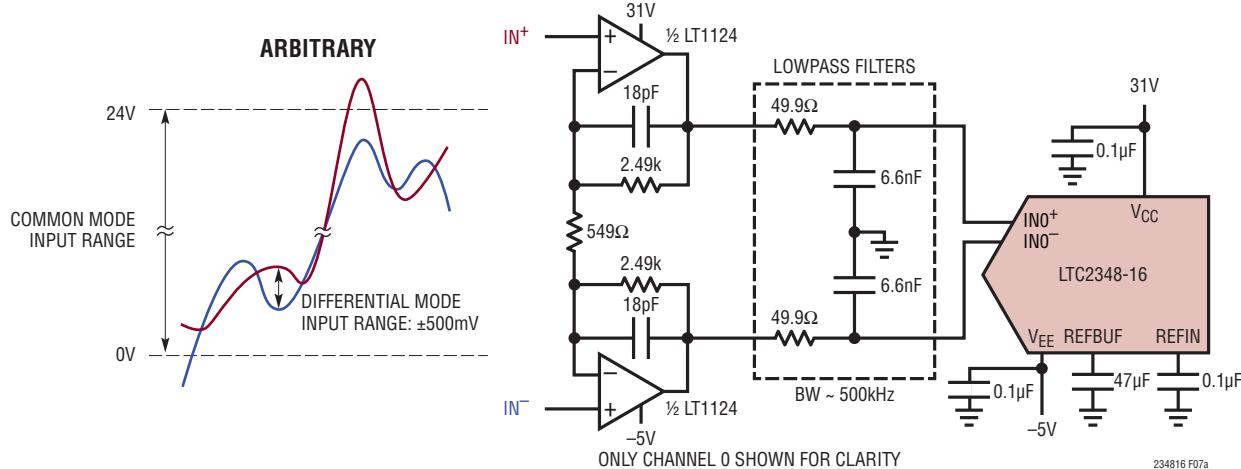

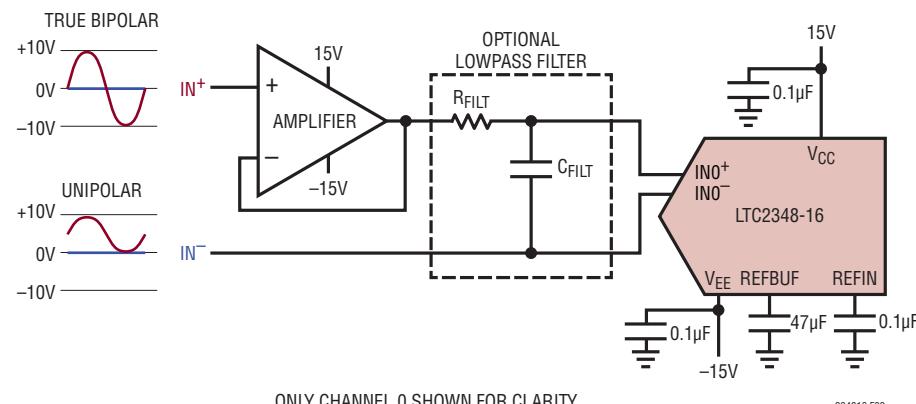

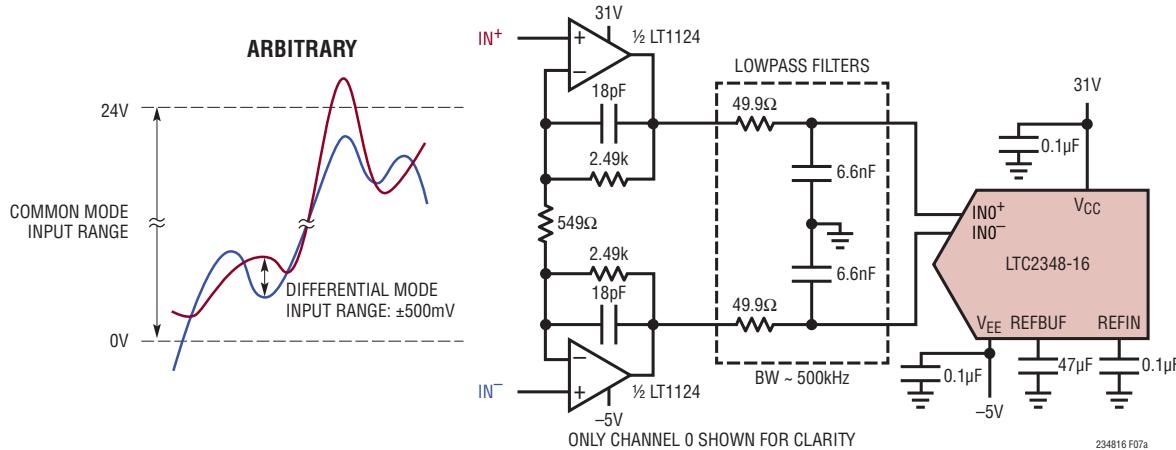

### 入力のフィルタリング

入力のバッファ・アンプやその他のサポート回路のノイズと歪みは、A/Dコンバータのノイズと歪みに上乗せされるため、これらを考慮する必要があります。ノイズの多い入力信号は、ノイズを最小限に抑えるため、バッファ・アンプの前で帯域幅の小さいフィルタによりフィルタ処理する必要があります。多くのアプリケーションでは、図5に示す簡単な1ポールのRCローパス・フィルタで十分です。

バッファの出力部では、オン抵抗( $R_{IN}$ )600Ωのサンプリング・スイッチと40pFサンプリング・コンデンサ( $C_{IN}$ )で形成されたローパスRCフィルタ回路網が、各チャネルの入力帯域幅を7MHzに制限します。この帯域幅は十分高速であり、収集時に十分な遷移収束時間を確保できるだけでなくドライバの広帯域ノイズをフィルタ処理できます。この帯域幅でのSNRの

## アプリケーション情報

図5. 入力フィルタリング機能を有する真の双極性信号チェーン

低下を最小限に抑えられるよう、ノイズ密度の小さいバッファ・アンプを選択する必要があります。フィルタ回路網をバッファアの出力とA/Dコンバータの入力の間に追加して、バッファに対するノイズの影響を最小限に抑えると同時に、A/Dコンバータの収集時のトランジエント電圧によるバッファへの妨害電圧を減らすことができます。多くのアプリケーションでは、簡単な1ポールのローパスRCフィルタで十分です。ただし、セトリングが不十分だとINLとTHDの性能が制限されることがあるため、A/Dコンバータの収集時間( $t_{ACQ}$ )内にアナログ入力を16ビット分解能まで完全にセトリングさせることができるように、このフィルタのRC時定数を十分に小さくすることが重要です。また、サンプリング周波数( $f_{SMPL}$ )とイネーブルされているチャネルの数によって最短収集時間が異なることに注意してください。

RCフィルタのコンデンサと抵抗は歪みを大きくする可能性があるので、これらの部品は高品質のものを使用します。NPO/COGタイプやシルバーマイカ・タイプの誘電体のコンデンサは優れた直線性を示します。表面実装型カーボン抵抗は、半田付け工程で生じる損傷および自己発熱により歪みが生じることがあります。表面実装型金属皮膜抵抗は、この2つの問題に対してはるかに耐性があります。

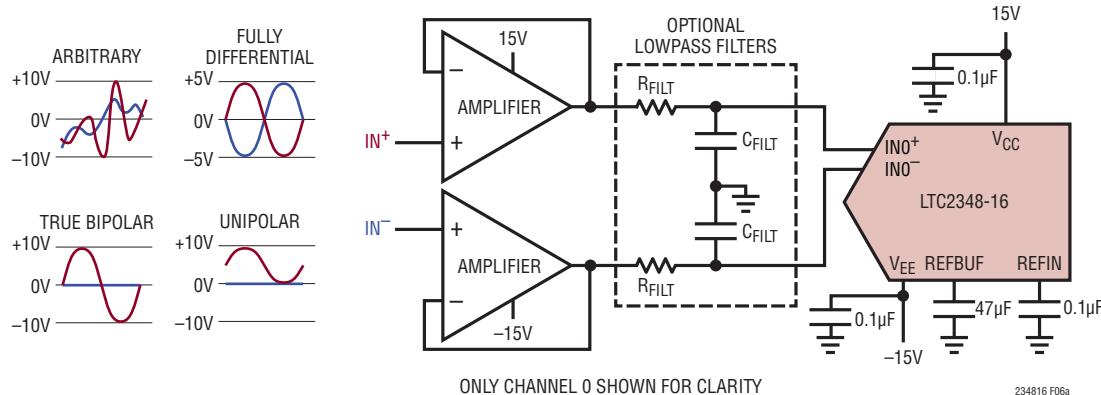

### 任意の入力信号と完全差動アナログ入力信号のバッファリング

LTC2348-16は同相入力電圧範囲が広くCMRRが高いため、各ピンの電圧が $(V_{CC} - 4V) \sim V_{EE}$ の範囲内に保たれた場合は、各チャネルのIN<sup>+</sup>、IN<sup>-</sup>ピンが相互に自由な関係で振れることができます。このユニークな特長を備えたLTC2348-16は、さまざまな信号の範囲に対応でき、信号チェーンの設計を簡素化できます。多くのアプリケーションでは、チャネルのIN<sup>+</sup>、IN<sup>-</sup>ピンを直接既存の信号チェーン回路に接続しても、A/Dコンバータの収集時間( $t_{ACQ}$ )内にチャネルのサンプリング回路網が16ビット分解能のレベルまで収束できません。このような場合は、図6aのように、信号源とA/Dコンバータ入力ピンの間に2つの単位利得バッファを挿入することを推奨します。この回路での使用を推奨するいくつかのアンプとローパス・フィルタの組み合わせを、表2に示します。LT1469は、高速セトリング特性、優れた直線性、低オフセットを兼ね備えた上に、 $5nV/\sqrt{Hz}$ の入力換算ノイズ密度を実現しており、図6b～6eのFFTのグラフで示すように、A/Dコンバータのデータシートに示すSNRとTHDの規格値を全て満たすことができます。SNRやTHDの性能が多少低くても良いようなアプリケーションの場合は、より消費電力の少ないLT1355でLTC2348-16

表2. 図6aおよび9に示すバッファ回路に推奨するアンプとフィルタの組み合わせ。

図6aの回路を使用し $\pm 10.24V$ の範囲で測定したAC性能

| アンプ      | R <sub>FILT</sub><br>(Ω) | C <sub>FILT</sub><br>(pF) | 入力信号の駆動            | SNR<br>(dB) | THD<br>(dB) | SINAD<br>(dB) | SFDR<br>(dB) |

|----------|--------------------------|---------------------------|--------------------|-------------|-------------|---------------|--------------|

| ½ LT1469 | 49.9                     | 1000                      | FULLY DIFFERENTIAL | 94.4        | -119        | 94.4          | 121          |

| ½ LT1355 | 100                      | 270                       | FULLY DIFFERENTIAL | 94.3        | -119        | 94.3          | 120          |

| ½ LT1469 | 49.9                     | 1000                      | TRUE BIPOLAR       | 94.4        | -109        | 94.3          | 110          |