## 特長

- 4チャネル同時サンプリングADC

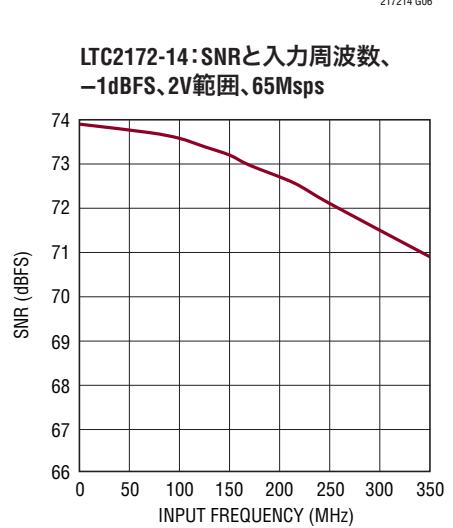

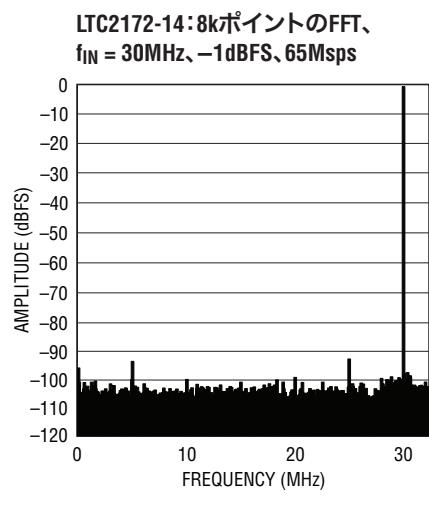

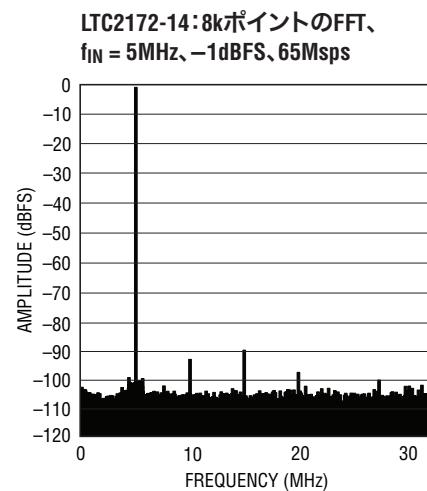

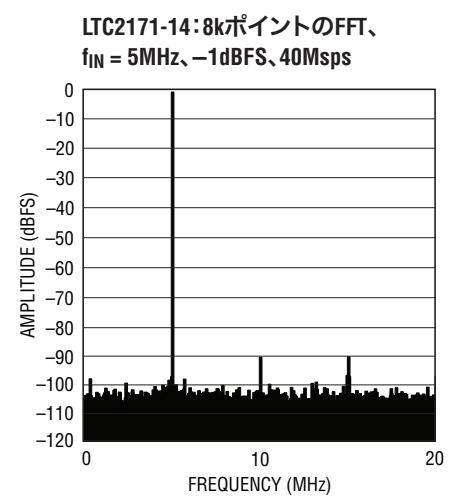

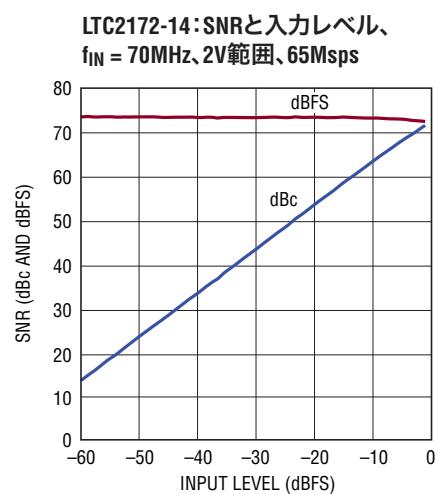

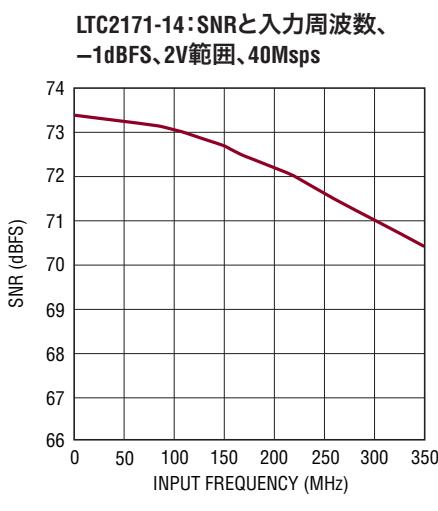

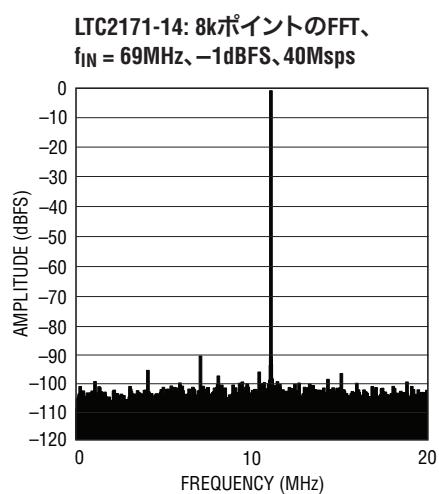

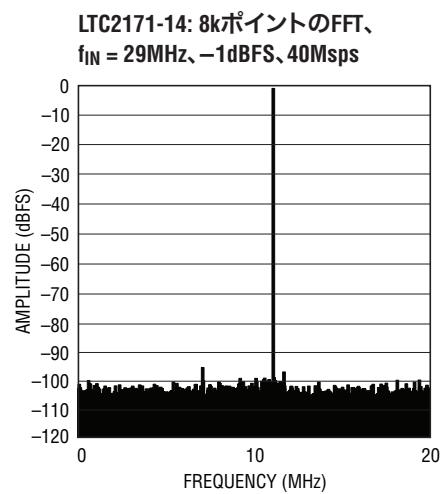

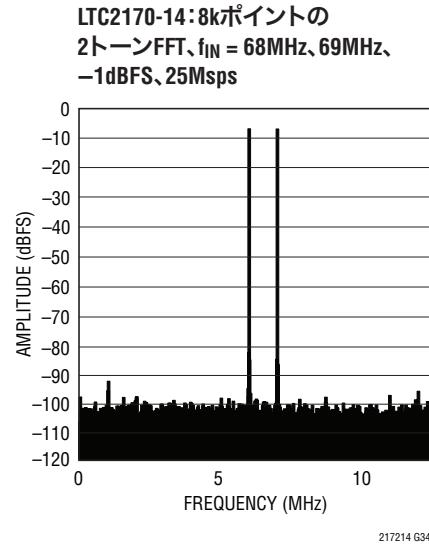

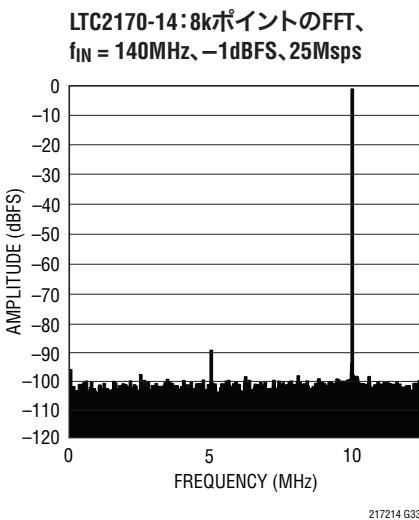

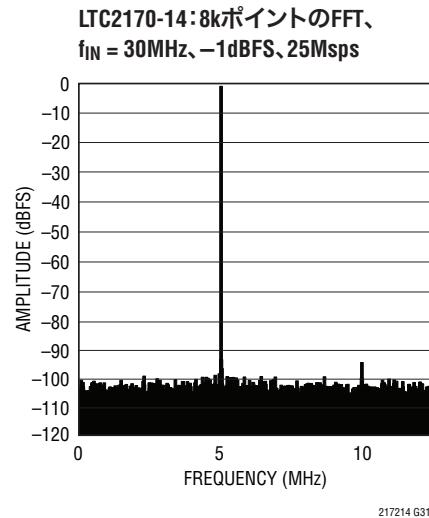

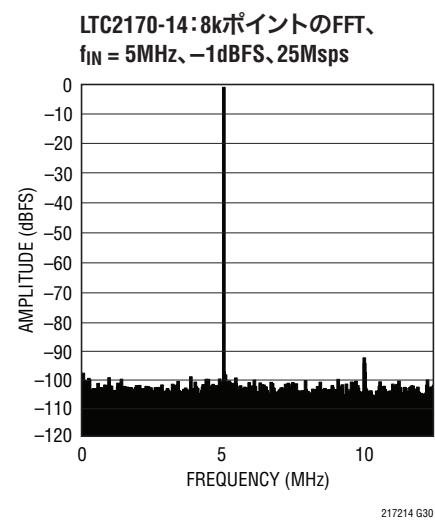

- SNR:73.7dB

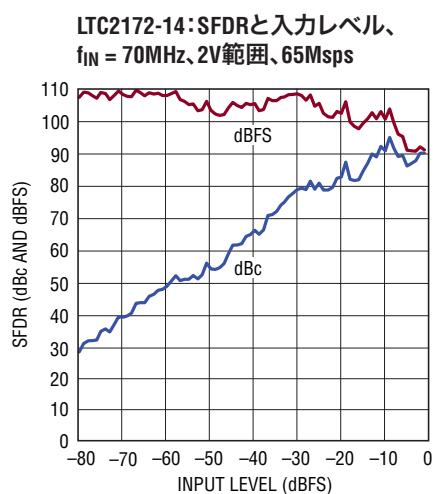

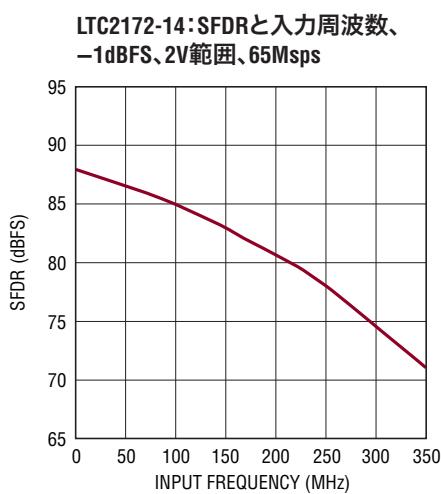

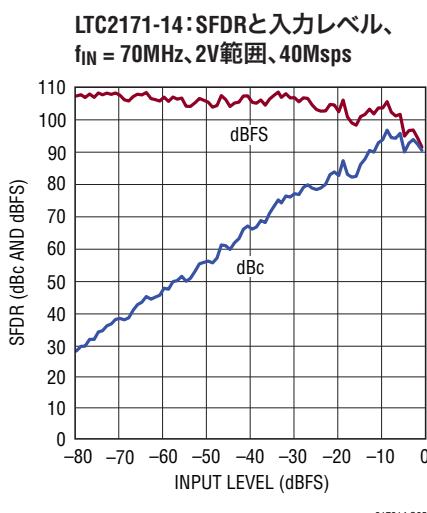

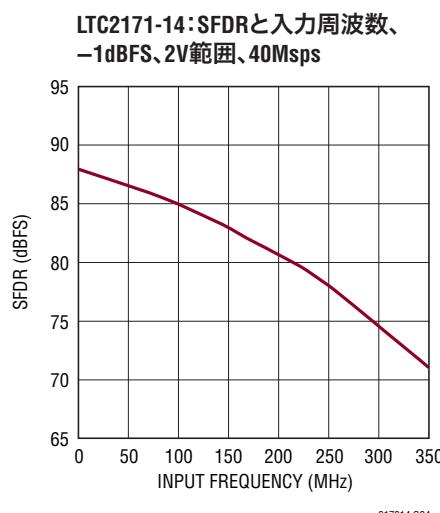

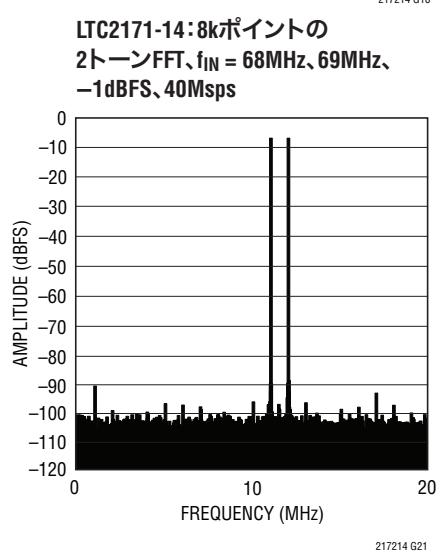

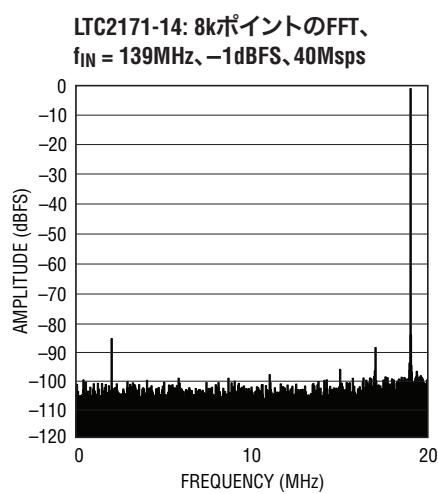

- SFDR:90dB

- 低消費電力:311mW/202mW/162mW(合計)、78mW/51mW/41mW(チャネル当たり)

- 単一1.8V電源

- シリアルLVDS出力:チャネル当たり1ビットまたは2ビット

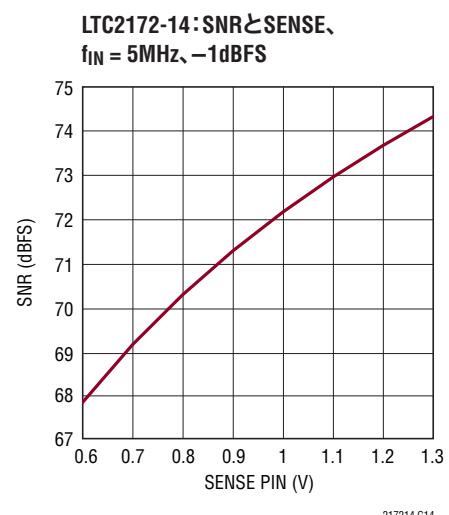

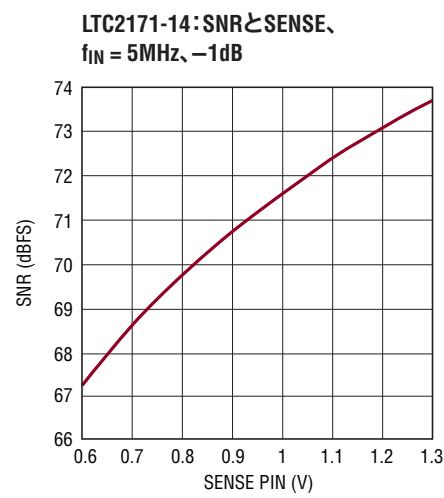

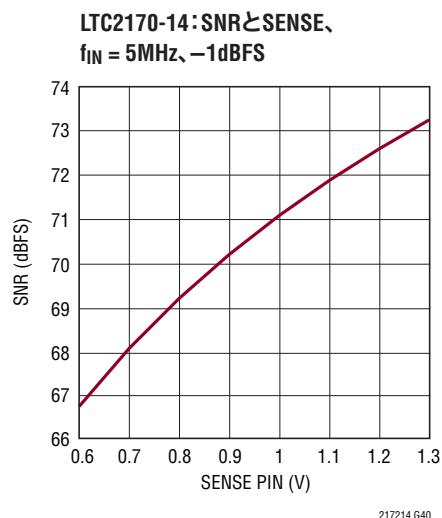

- 選択可能な入力範囲:1V<sub>P-P</sub>~2V<sub>P-P</sub>

- 800MHzのフルパワー帯域幅サンプル/ホールド

- シャットダウン・モードとナップ・モード

- 設定用のシリアルSPIポート

- ピン互換の14ビットおよび12ビット・バージョン

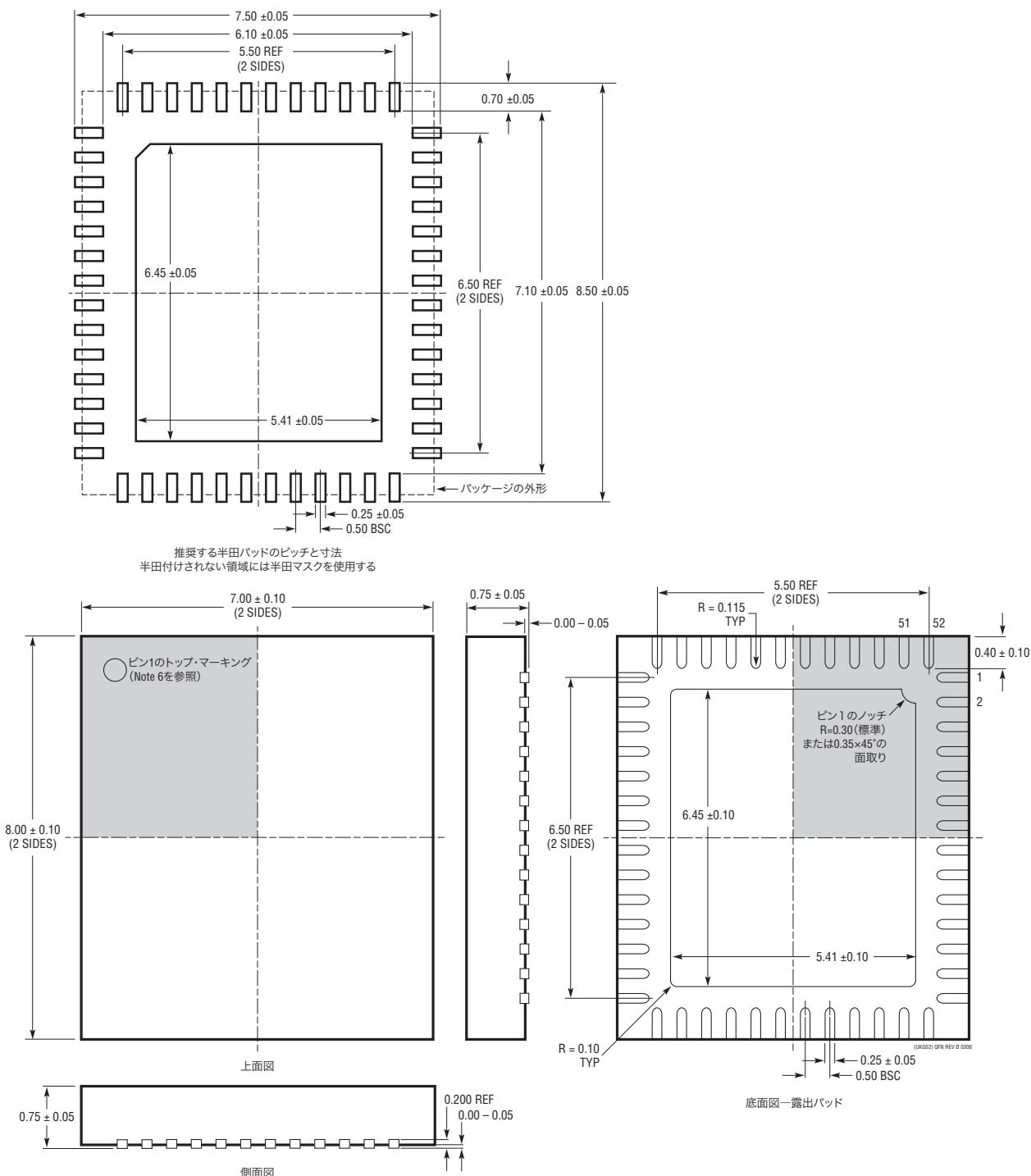

- 52ピン(7mm×8mm)QFNパッケージ

## アプリケーション

- 通信

- セルラー基地局

- ソフトウェア無線

- 携帯型医療用画像処理

- マルチチャネル・データ収集

- 非破壊試験

LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

## 概要

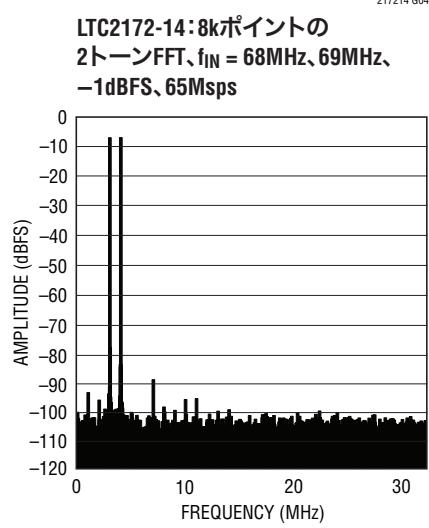

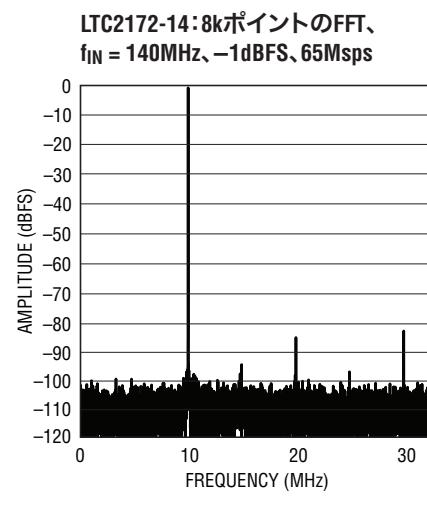

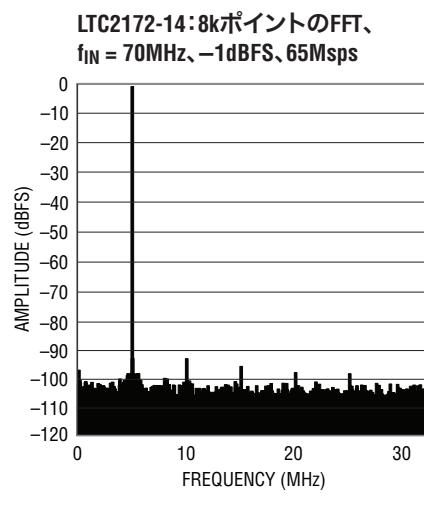

LTC<sup>®</sup>2172-14/LTC2171-14/LTC2170-14は、広いダイナミック・レンジの高周波信号をデジタル化する4チャネル同時サンプリング14ビットA/Dコンバータです。SNRが73.7dB、SFDRが90dBという優れたAC特性を備えているため、要求の厳しい通信アプリケーションに最適です。ジッタがわずか0.15psRMSなので、優れたノイズ性能を維持しながらIF周波数をアンダーサンプリングできます。

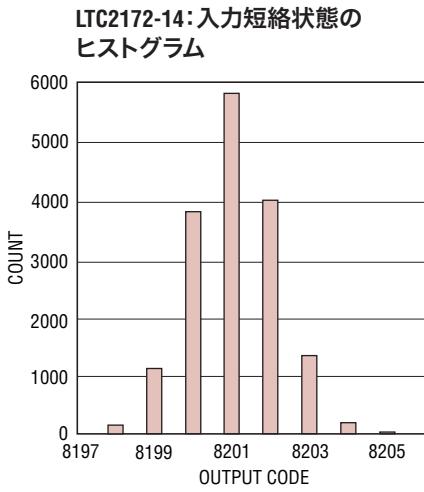

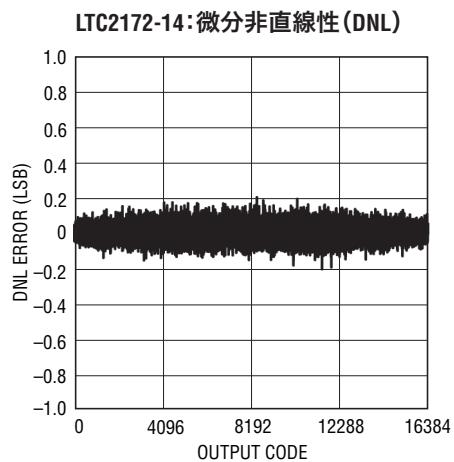

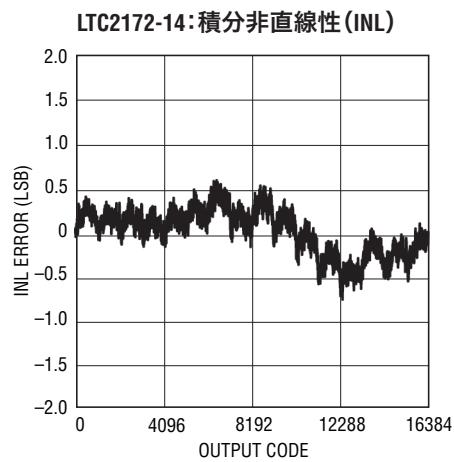

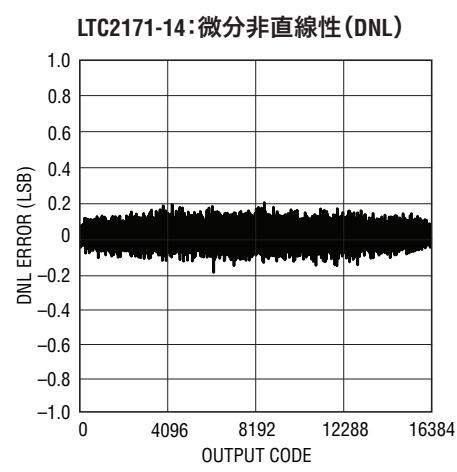

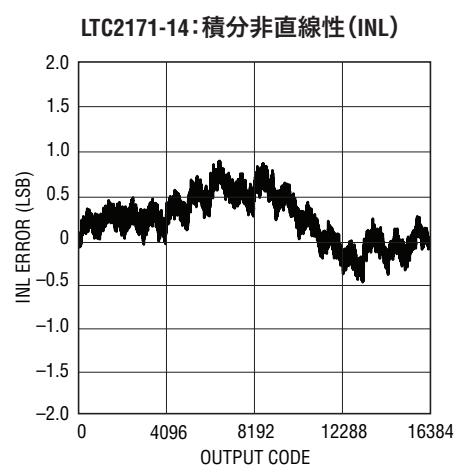

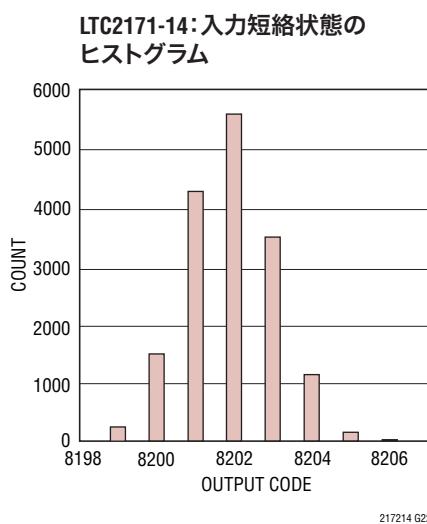

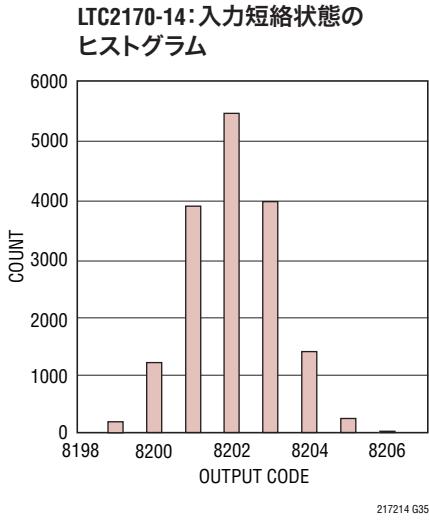

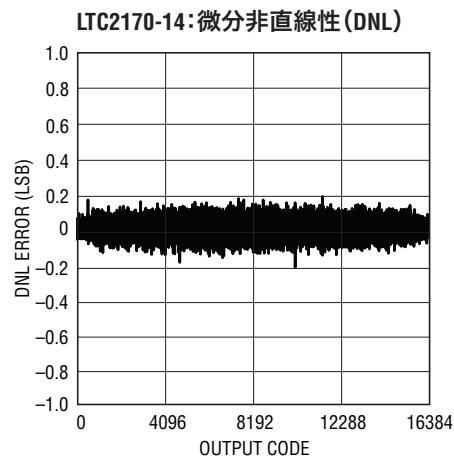

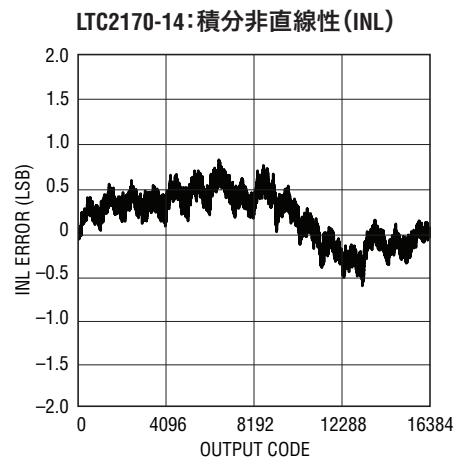

DC仕様では、±1 LSB(標準)のINLと±0.3 LSB(標準)のDNL、全温度範囲でミッシング・コードがないことが規定されています。遷移ノイズは1.2LSBRMSと低く抑えられています。

デジタル出力はシリアルLVDSなので、データ・ライン数を最小限に抑えることができます。各チャネルは一度に2ビット(2レーン・モード)または一度に1ビット(1レーン・モード)を出力します。LVDSドライバはオプションの内部終端を備え、出力レベルを調整できるので、クリーンなシグナルインテグリティを確保します。

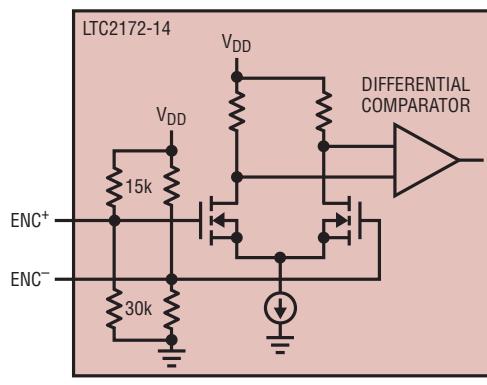

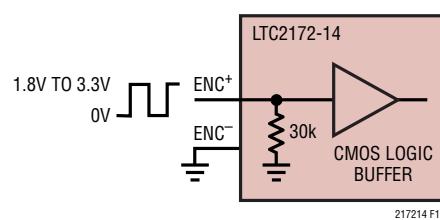

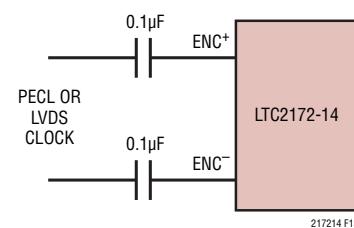

ENC<sup>+</sup>およびENC<sup>-</sup>入力は、正弦波、PECL、LVDS、TTLまたはCMOSの入力信号を使って差動またはシングルエンドでドライブ可能です。また、内蔵のクロック・デューティ・サイクル・スタビライザにより、広範なクロック・デューティ・サイクルにおいてフルスピードで高性能を達成できます。

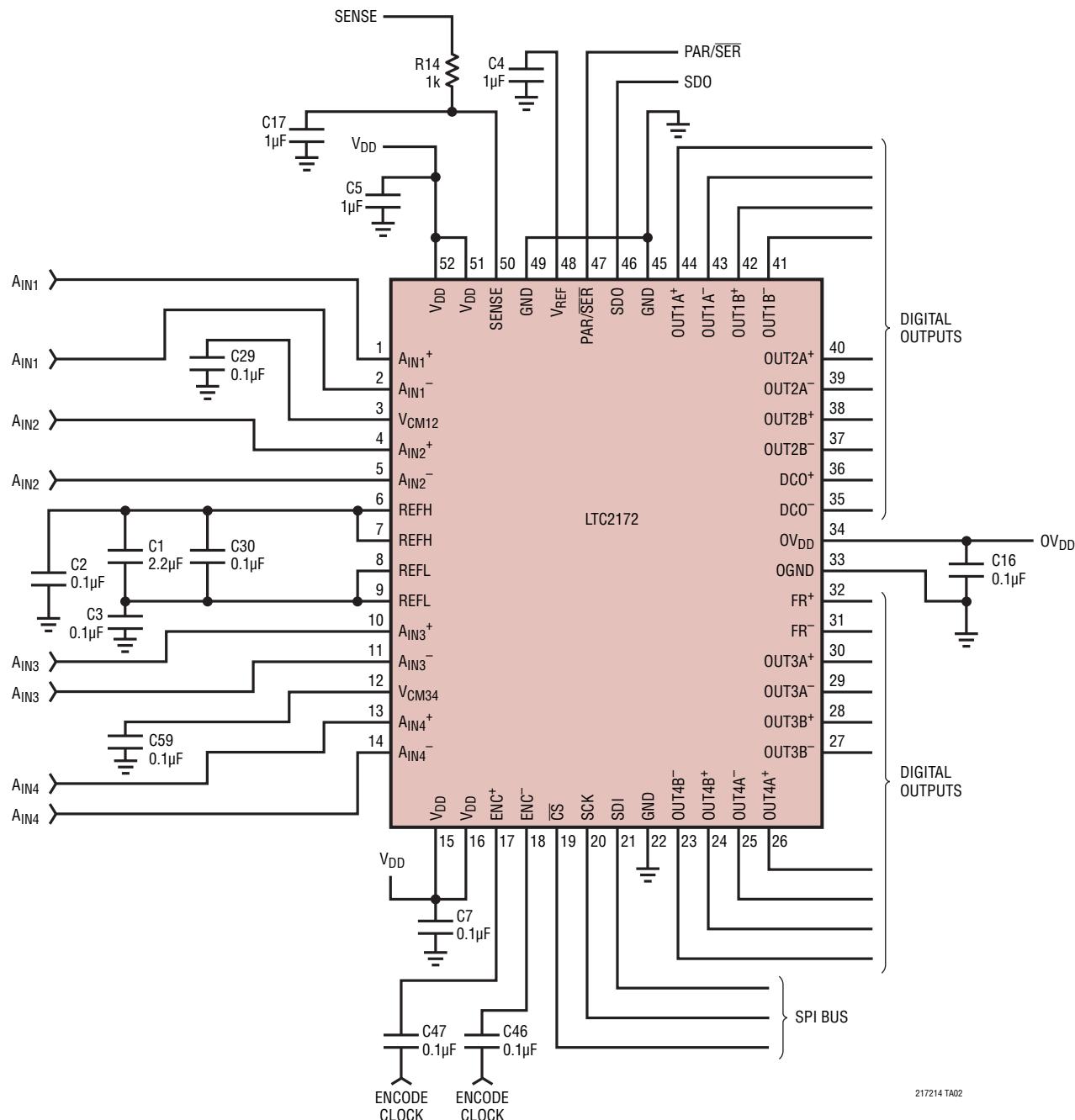

## 標準的応用例

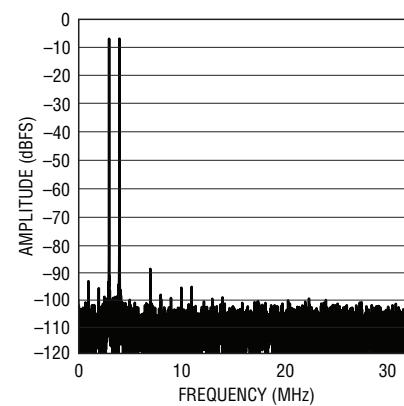

**LTC2172-14、65Msps、

2トーンFFT、f<sub>IN</sub> = 70MHzおよび75MHz**

# LTC2172-14/ LTC2171-14/LTC2170-14

## 絶対最大定格

(Note 1,2)

### 電源電圧

$V_{DD}$ 、 $0V_{DD}$  .....  $-0.3V \sim 2V$

アナログ入力電圧 ( $A_{IN}^+$ 、 $A_{IN}^-$ 、

$PAR/SER$ 、 $SENSE$ ) (Note 3) .....  $-0.3V \sim (V_{DD} + 0.2V)$

デジタル入力電圧 ( $ENC^+$ 、 $ENC^-$ 、 $\bar{CS}$ 、

$SDI$ 、 $SCK$ ) (Note 4) .....  $-0.3V \sim 3.9V$

$SDO$  (Note 4) .....  $-0.3V \sim 3.9V$

デジタル出力電圧 .....  $-0.3V \sim (0V_{DD} + 0.3V)$

### 動作温度範囲:

LTC2172C、LTC2171C、LTC2170C .....  $0^\circ C \sim 70^\circ C$

LTC2172I、LTC2171I、LTC2170I .....  $-40^\circ C \sim 85^\circ C$

保存温度範囲 .....  $-65^\circ C \sim 150^\circ C$

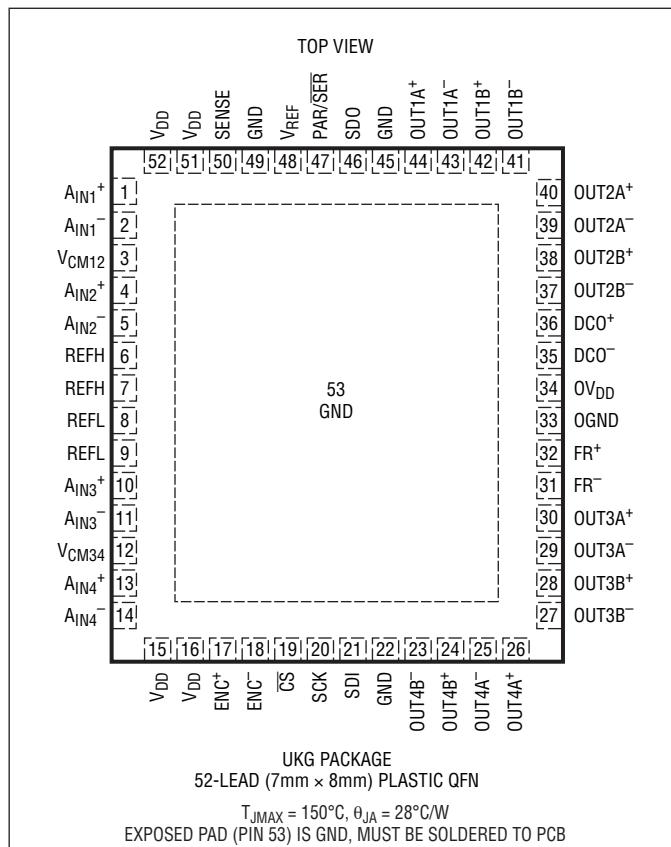

## ピン配置

## 発注情報

| 鉛フリー仕様             | テープアンドリール            | 製品マーキング*      | パッケージ                           | 温度範囲                          |

|--------------------|----------------------|---------------|---------------------------------|-------------------------------|

| LTC2172CUKG-14#PBF | LTC2172CUKG-14#TRPBF | LTC2172UKG-14 | 52-Lead (7mm x 8mm) Plastic QFN | $0^\circ C$ to $70^\circ C$   |

| LTC2172IUKG-14#PBF | LTC2172IUKG-14#TRPBF | LTC2172UKG-14 | 52-Lead (7mm x 8mm) Plastic QFN | $-40^\circ C$ to $85^\circ C$ |

| LTC2171CUKG-14#PBF | LTC2171CUKG-14#TRPBF | LTC2171UKG-14 | 52-Lead (7mm x 8mm) Plastic QFN | $0^\circ C$ to $70^\circ C$   |

| LTC2171IUKG-14#PBF | LTC2171IUKG-14#TRPBF | LTC2171UKG-14 | 52-Lead (7mm x 8mm) Plastic QFN | $-40^\circ C$ to $85^\circ C$ |

| LTC2170CUKG-14#PBF | LTC2170CUKG-14#TRPBF | LTC2170UKG-14 | 52-Lead (7mm x 8mm) Plastic QFN | $0^\circ C$ to $70^\circ C$   |

| LTC2170IUKG-14#PBF | LTC2170IUKG-14#TRPBF | LTC2170UKG-14 | 52-Lead (7mm x 8mm) Plastic QFN | $-40^\circ C$ to $85^\circ C$ |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## コンバータの特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$ での値。(Note 5)

| PARAMETER                     | CONDITIONS                         | LTC2172-14 |       |           | LTC2171-14 |       |           | LTC2170-14 |           |           | UNITS                        |     |

|-------------------------------|------------------------------------|------------|-------|-----------|------------|-------|-----------|------------|-----------|-----------|------------------------------|-----|

|                               |                                    | MIN        | TYP   | MAX       | MIN        | TYP   | MAX       | MIN        | TYP       | MAX       |                              |     |

| Resolution (No Missing Codes) |                                    | ●          | 14    |           |            | 14    |           | 14         |           |           | Bits                         |     |

| Integral Linearity Error      | Differential Analog Input (Note 6) | ●          | -3.25 | $\pm 1$   | 3.25       | -2.75 | $\pm 1$   | 2.75       | -2.75     | $\pm 1$   | 2.75                         | LSB |

| Differential Linearity Error  | Differential Analog Input          | ●          | -0.8  | $\pm 0.3$ | 0.8        | -0.8  | $\pm 0.3$ | 0.8        | -0.8      | $\pm 0.3$ | 0.8                          | LSB |

| Offset Error                  | (Note 7)                           | ●          | -12   | $\pm 3$   | 12         | -12   | $\pm 3$   | 12         | -12       | $\pm 3$   | 12                           | mV  |

| Gain Error                    | Internal Reference                 |            |       | -1        |            |       | -1        |            | -1        |           | %FS                          |     |

|                               | External Reference                 | ●          | -2.5  | -1        | 0.5        | -2.5  | -1        | 0.5        | -2.5      | -1        | 0.5                          | %FS |

| Offset Drift                  |                                    |            |       | $\pm 20$  |            |       | $\pm 20$  |            | $\pm 20$  |           | $\mu\text{V}/^\circ\text{C}$ |     |

| Full-Scale Drift              | Internal Reference                 |            |       | $\pm 35$  |            |       | $\pm 35$  |            | $\pm 35$  |           | $\text{ppm}/^\circ\text{C}$  |     |

|                               | External Reference                 |            |       | $\pm 25$  |            |       | $\pm 25$  |            | $\pm 25$  |           | $\text{ppm}/^\circ\text{C}$  |     |

| Gain Matching                 | External Reference                 |            |       | $\pm 0.2$ |            |       | $\pm 0.2$ |            | $\pm 0.2$ |           | %FS                          |     |

| Offset Matching               |                                    |            |       | $\pm 3$   |            |       | $\pm 3$   |            | $\pm 3$   |           | mV                           |     |

| Transition Noise              | External Reference                 |            |       | 1.2       |            |       | 1.2       |            | 1.2       |           | LSB <sub>RMS</sub>           |     |

## アナログ入力

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$ での値。(Note 5)

| SYMBOL       | PARAMETER                                            | CONDITIONS                                            | MIN | TYP                     | MAX      | UNITS                   |

|--------------|------------------------------------------------------|-------------------------------------------------------|-----|-------------------------|----------|-------------------------|

| $V_{IN}$     | Analog Input Range ( $A_{IN}^+ - A_{IN}^-$ )         | $1.7\text{V} < V_{DD} < 1.9\text{V}$                  | ●   | 1 to 2                  |          | $V_{P-P}$               |

| $V_{IN(CM)}$ | Analog Input Common Mode ( $A_{IN}^+ + A_{IN}^-$ )/2 | Differential Analog Input (Note 8)                    | ●   | $V_{CM} - 100\text{mV}$ | $V_{CM}$ | $V_{CM} + 100\text{mV}$ |

| $V_{SENSE}$  | External Voltage Reference Applied to SENSE          | External Reference Mode                               | ●   | 0.625                   | 1.250    | 1.300                   |

| $I_{IN(CM)}$ | Analog Input Common Mode Current                     | Per Pin, 65Msps<br>Per Pin, 40Msps<br>Per Pin, 25Msps |     | 81<br>50<br>31          |          | $\mu\text{A}$           |

| $I_{IN1}$    | Analog Input Leakage Current (No Encode)             | $0 < A_{IN}^+, A_{IN}^- < V_{DD}$                     | ●   | -1                      | 1        | $\mu\text{A}$           |

| $I_{IN2}$    | PAR/SER Input Leakage Current                        | $0 < \text{PAR/SER} < V_{DD}$                         | ●   | -3                      | 3        | $\mu\text{A}$           |

| $I_{IN3}$    | SENSE Input Leakage Current                          | $0.625 < \text{SENSE} < 1.3\text{V}$                  | ●   | -6                      | 6        | $\mu\text{A}$           |

| $t_{AP}$     | Sample-and-Hold Acquisition Delay Time               |                                                       |     | 0                       |          | ns                      |

| $t_{JITTER}$ | Sample-and-Hold Acquisition Delay Jitter             |                                                       |     |                         | 0.15     | $\text{ps}_{RMS}$       |

| CMRR         | Analog Input Common Mode Rejection Ratio             |                                                       |     | 80                      |          | dB                      |

| BW-3B        | Full-Power Bandwidth                                 | Figure 6 Test Circuit                                 |     | 800                     |          | MHz                     |

# LTC2172-14/ LTC2171-14/LTC2170-14

## ダイナミック精度

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $A_{IN} = -1\text{dBFS}$  (Note 5)

| SYMBOL  | PARAMETER                                             | CONDITIONS            | LTC2172-14 |      |      | LTC2171-14 |      |      | LTC2170-14 |     |     | UNITS |

|---------|-------------------------------------------------------|-----------------------|------------|------|------|------------|------|------|------------|-----|-----|-------|

|         |                                                       |                       | MIN        | TYP  | MAX  | MIN        | TYP  | MAX  | MIN        | TYP | MAX |       |

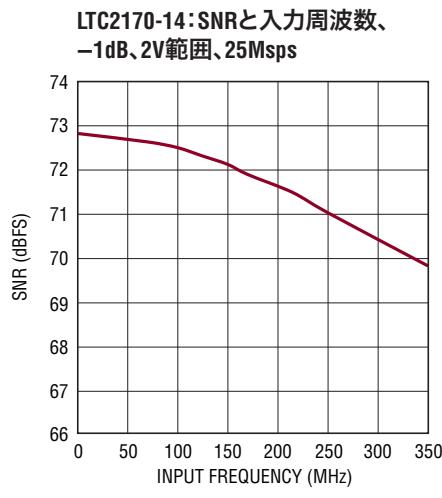

| SNR     | Signal-to-Noise Ratio                                 | 5MHz Input            | ●          | 73.7 |      | 73.5       |      | 72.9 |            |     |     | dBFS  |

|         |                                                       | 30MHz Input           |            | 72.0 | 73.7 | 71.7       | 73.4 | 71.1 | 72.9       |     |     | dBFS  |

|         |                                                       | 70MHz Input           |            | 73.5 |      | 73.4       |      | 72.8 |            |     |     | dBFS  |

|         |                                                       | 140MHz Input          |            | 73   |      | 72.8       |      | 72.3 |            |     |     | dBFS  |

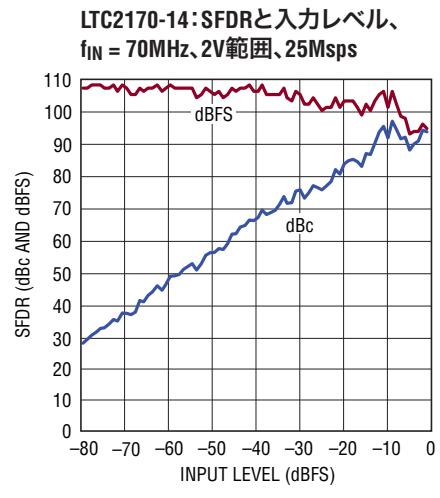

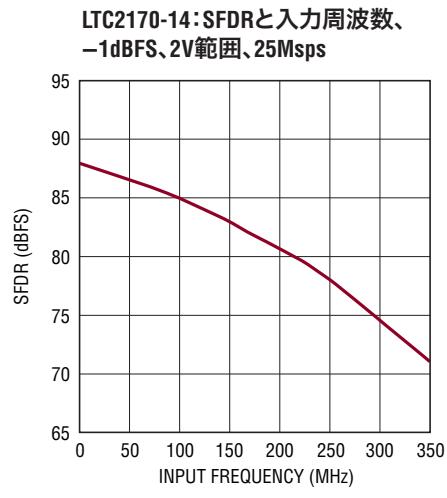

| SFDR    | Spurious Free Dynamic Range<br>2nd or 3rd Harmonic    | 5MHz Input            | ●          | 90   |      | 90         |      | 90   |            |     |     | dBFS  |

|         |                                                       | 30MHz Input           |            | 77   | 90   | 80         | 90   | 80   | 90         |     |     | dBFS  |

|         |                                                       | 70MHz Input           |            | 89   |      | 89         |      | 89   |            |     |     | dBFS  |

|         |                                                       | 140MHz Input          |            | 84   |      | 84         |      | 84   |            |     |     | dBFS  |

|         | Spurious Free Dynamic Range<br>4th Harmonic or Higher | 5MHz Input            | ●          | 90   |      | 90         |      | 90   |            |     |     | dBFS  |

|         |                                                       | 30MHz Input           |            | 85   | 90   | 85         | 90   | 85   | 90         |     |     | dBFS  |

|         |                                                       | 70MHz Input           |            | 90   |      | 90         |      | 90   |            |     |     | dBFS  |

|         |                                                       | 140MHz Input          |            | 90   |      | 90         |      | 90   |            |     |     | dBFS  |

| S/(N+D) | Signal-to-Noise Plus<br>Distortion Ratio              | 5MHz Input            | ●          | 73.6 |      | 73.3       |      | 72.8 |            |     |     | dBFS  |

|         |                                                       | 30MHz Input           |            | 71.2 | 73.5 | 71.3       | 73.2 | 70.8 | 72.7       |     |     | dBFS  |

|         |                                                       | 70MHz Input           |            | 73.2 |      | 73.1       |      | 72.5 |            |     |     | dBFS  |

|         |                                                       | 140MHz Input          |            | 72.5 |      | 72.3       |      | 71.9 |            |     |     | dBFS  |

|         | Crosstalk, Near Channel                               | 10MHz Input (Note 12) |            |      | -90  |            | -90  |      | -90        |     |     | dBc   |

|         | Crosstalk, Far Channel                                | 10MHz Input (Note 12) |            |      | -105 |            | -105 |      | -105       |     |     | dBc   |

## 内部リファレンスの特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $A_{IN} = -1\text{dBFS}$  (Note 5)

| PARAMETER                          | CONDITIONS                               | MIN                              | TYP                | MAX                              | UNITS  |

|------------------------------------|------------------------------------------|----------------------------------|--------------------|----------------------------------|--------|

| $V_{CM}$ Output Voltage            | $I_{OUT} = 0$                            | $0.5 \cdot V_{DD} - 25\text{mV}$ | $0.5 \cdot V_{DD}$ | $0.5 \cdot V_{DD} + 25\text{mV}$ | V      |

| $V_{CM}$ Output Temperature Drift  |                                          |                                  | $\pm 25$           |                                  | ppm/°C |

| $V_{CM}$ Output Resistance         | $-600\mu\text{A} < I_{OUT} < 1\text{mA}$ |                                  | 4                  |                                  | Ω      |

| $V_{REF}$ Output Voltage           | $I_{OUT} = 0$                            | 1.225                            | 1.250              | 1.275                            | V      |

| $V_{REF}$ Output Temperature Drift |                                          |                                  | $\pm 25$           |                                  | ppm/°C |

| $V_{REF}$ Output Resistance        | $-400\mu\text{A} < I_{OUT} < 1\text{mA}$ |                                  | 7                  |                                  | Ω      |

| $V_{REF}$ Line Regulation          | $1.7\text{V} < V_{DD} < 1.9\text{V}$     |                                  | 0.6                |                                  | mV/V   |

## デジタル入力とデジタル出力

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 5)

| SYMBOL                                                                             | PARAMETER                          | CONDITIONS                                                                | MIN    | TYP            | MAX            | UNITS    |

|------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------|--------|----------------|----------------|----------|

| <b>エンコード入力(ENC<sup>+</sup>、ENC<sup>-</sup>)</b>                                    |                                    |                                                                           |        |                |                |          |

| <b>差動エンコード・モード(ENC<sup>-</sup>はGNDに接続されていない)</b>                                   |                                    |                                                                           |        |                |                |          |

| $V_{ID}$                                                                           | Differential Input Voltage         | (Note 8)                                                                  | ●      | 0.2            |                | V        |

| $V_{ICM}$                                                                          | Common Mode Input Voltage          | Internally Set<br>Externally Set (Note 8)                                 | ●      | 1.2            | 1.6            | V        |

| $V_{IN}$                                                                           | Input Voltage Range                | ENC <sup>+</sup> , ENC <sup>-</sup> to GND                                | ●      | 0.2            | 3.6            | V        |

| $R_{IN}$                                                                           | Input Resistance                   | (See Figure 10)                                                           |        | 10             |                | kΩ       |

| $C_{IN}$                                                                           | Input Capacitance                  |                                                                           |        | 3.5            |                | pF       |

| <b>シングルエンド・エンコード・モード(ENC<sup>-</sup>はGNDに接続されている)</b>                              |                                    |                                                                           |        |                |                |          |

| $V_{IH}$                                                                           | High Level Input Voltage           | $V_{DD} = 1.8\text{V}$                                                    | ●      | 1.2            |                | V        |

| $V_{IL}$                                                                           | Low Level Input Voltage            | $V_{DD} = 1.8\text{V}$                                                    | ●      |                | 0.6            | V        |

| $V_{IN}$                                                                           | Input Voltage Range                | ENC <sup>+</sup> to GND                                                   | ●      | 0              | 3.6            | V        |

| $R_{IN}$                                                                           | Input Resistance                   | (See Figure 11)                                                           |        | 30             |                | kΩ       |

| $C_{IN}$                                                                           | Input Capacitance                  |                                                                           |        | 3.5            |                | pF       |

| <b>デジタル入力(CS、SDI、SCK:シリアル・プログラミング・モードまたはパラレル・プログラミング・モード。SD0:パラレル・プログラミング・モード)</b> |                                    |                                                                           |        |                |                |          |

| $V_{IH}$                                                                           | High Level Input Voltage           | $V_{DD} = 1.8\text{V}$                                                    | ●      | 1.3            |                | V        |

| $V_{IL}$                                                                           | Low Level Input Voltage            | $V_{DD} = 1.8\text{V}$                                                    | ●      |                | 0.6            | V        |

| $I_{IN}$                                                                           | Input Current                      | $V_{IN} = 0\text{V}$ to $3.6\text{V}$                                     | ●      | -10            | 10             | μA       |

| $C_{IN}$                                                                           | Input Capacitance                  |                                                                           |        | 3              |                | pF       |

| <b>SD0出力(シリアル・プログラミング・モード。オープン・ドレイン出力。SD0を使用する場合、2kのプルアップ抵抗が必要)</b>                |                                    |                                                                           |        |                |                |          |

| $R_{OL}$                                                                           | Logic Low Output Resistance to GND | $V_{DD} = 1.8\text{V}$ , SD0 = 0V                                         |        |                | 200            | Ω        |

| $I_{OH}$                                                                           | Logic High Output Leakage Current  | SD0 = 0V to $3.6\text{V}$                                                 | ●      | -10            | 10             | μA       |

| $C_{OUT}$                                                                          | Output Capacitance                 |                                                                           |        | 3              |                | pF       |

| <b>デジタル・データ出力</b>                                                                  |                                    |                                                                           |        |                |                |          |

| $V_{OD}$                                                                           | Differential Output Voltage        | 100Ω Differential Load, 3.5mA Mode<br>100Ω Differential Load, 1.75mA Mode | ●<br>● | 247<br>125     | 350<br>175     | mV<br>mV |

| $V_{OS}$                                                                           | Common Mode Output Voltage         | 100Ω Differential Load, 3.5mA Mode<br>100Ω Differential Load, 1.75mA Mode | ●<br>● | 1.125<br>1.125 | 1.250<br>1.250 | V<br>V   |

| $R_{TERM}$                                                                         | On-Chip Termination Resistance     | Termination Enabled, $0V_{DD} = 1.8\text{V}$                              |        |                | 100            | Ω        |

# LTC2172-14/ LTC2171-14/LTC2170-14

## 電源要件

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 9)

| SYMBOL        | PARAMETER                                                                            | CONDITIONS               | LTC2172-14 |     |     | LTC2171-14 |     |     | LTC2170-14 |     |     | UNITS |    |

|---------------|--------------------------------------------------------------------------------------|--------------------------|------------|-----|-----|------------|-----|-----|------------|-----|-----|-------|----|

|               |                                                                                      |                          | MIN        | TYP | MAX | MIN        | TYP | MAX | MIN        | TYP | MAX |       |    |

| $V_{DD}$      | Analog Supply Voltage                                                                | (Note 10)                | ●          | 1.7 | 1.8 | 1.9        | 1.7 | 1.8 | 1.9        | 1.7 | 1.8 | 1.9   | V  |

| $OV_{DD}$     | Output Supply Voltage                                                                | (Note 10)                | ●          | 1.7 | 1.8 | 1.9        | 1.7 | 1.8 | 1.9        | 1.7 | 1.8 | 1.9   | V  |

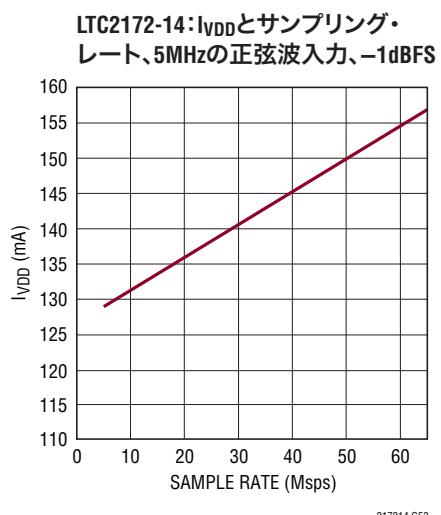

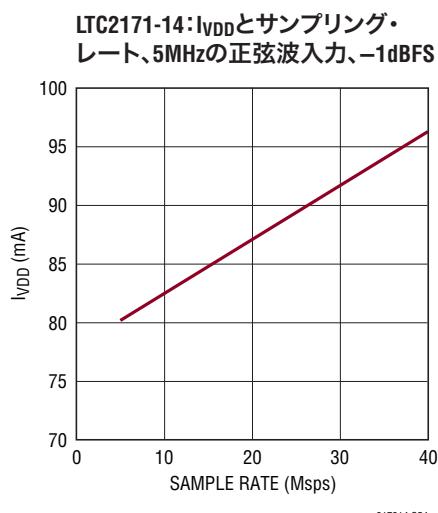

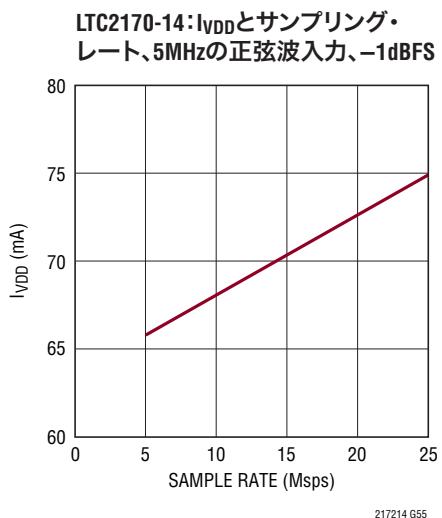

| $I_{VDD}$     | Analog Supply Current                                                                | Sine Wave Input          | ●          |     | 157 | 181        |     | 96  | 112        |     | 75  | 85    | mA |

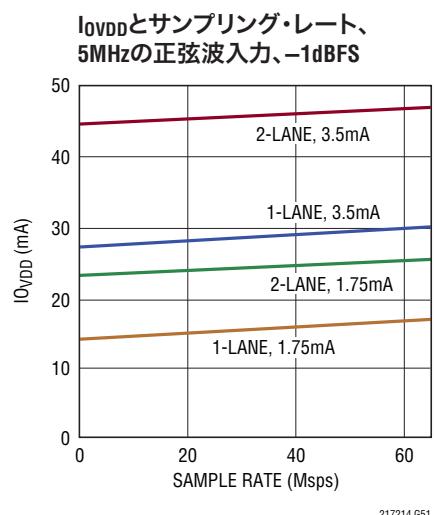

| $I_{OVDD}$    | Digital Supply Current                                                               | 1-Lane Mode, 1.75mA Mode |            |     | 16  |            |     | 16  |            |     | 15  |       | mA |

|               |                                                                                      | 1-Lane Mode, 3.5mA Mode  |            |     | 30  |            |     | 29  |            |     | 28  |       | mA |

|               |                                                                                      | 2-Lane Mode, 1.75mA Mode | ●          |     | 25  | 29         |     | 24  | 27         |     | 24  | 27    | mA |

|               |                                                                                      | 2-Lane Mode, 3.5mA Mode  | ●          |     | 47  | 52         |     | 46  | 51         |     | 45  | 50    | mA |

| $P_{DISS}$    | Power Dissipation                                                                    | 1-Lane Mode, 1.75mA Mode |            |     | 311 |            |     | 202 |            |     | 162 |       | mW |

|               |                                                                                      | 1-Lane Mode, 3.5mA Mode  |            |     | 337 |            |     | 225 |            |     | 185 |       | mW |

|               |                                                                                      | 2-Lane Mode, 1.75mA Mode | ●          |     | 328 | 378        |     | 216 | 250        |     | 178 | 202   | mW |

|               |                                                                                      | 2-Lane Mode, 3.5mA Mode  | ●          |     | 367 | 419        |     | 256 | 293        |     | 216 | 243   | mW |

| $P_{SLEEP}$   | Sleep Mode Power                                                                     |                          |            |     | 1   |            |     | 1   |            |     | 1   |       | mW |

| $P_{NAP}$     | Nap Mode Power                                                                       |                          |            |     | 75  |            |     | 75  |            |     | 75  |       | mW |

| $P_{DIFFCLK}$ | Power Increase with Differential Encode Mode Enabled<br>(No Increase for Sleep Mode) |                          |            |     | 20  |            |     | 20  |            |     | 20  |       | mW |

## タイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 5)

| SYMBOL     | PARAMETER                                 | CONDITIONS                | LTC2172-14 |     |      | LTC2171-14 |       |      | LTC2170-14 |     |     | UNITS |    |

|------------|-------------------------------------------|---------------------------|------------|-----|------|------------|-------|------|------------|-----|-----|-------|----|

|            |                                           |                           | MIN        | TYP | MAX  | MIN        | TYP   | MAX  | MIN        | TYP | MAX |       |    |

| $f_S$      | Sampling Frequency                        | (Notes 10, 11)            | ●          | 5   | 65   | 5          |       | 40   | 5          | 25  |     | MHz   |    |

| $t_{ENCL}$ | ENC Low Time (Note 8)                     | Duty Cycle Stabilizer Off | ●          | 7.3 | 7.69 | 100        | 11.88 | 12.5 | 100        | 19  | 20  | 100   | ns |

|            |                                           | Duty Cycle Stabilizer On  | ●          | 2   | 7.69 | 100        | 2     | 12.5 | 100        | 2   | 20  | 100   | ns |

| $t_{ENCH}$ | ENC High Time (Note 8)                    | Duty Cycle Stabilizer Off | ●          | 7.3 | 7.69 | 100        | 11.88 | 12.5 | 100        | 19  | 20  | 100   | ns |

|            |                                           | Duty Cycle Stabilizer On  | ●          | 2   | 7.69 | 100        | 2     | 12.5 | 100        | 2   | 20  | 100   | ns |

| $t_{AP}$   | Sample-and-Hold<br>Acquisition Delay Time |                           |            |     | 0    |            |       | 0    |            |     | 0   |       | ns |

## タイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 5)

| SYMBOL                                                                                          | PARAMETER                     | CONDITIONS                                                                                                                                                                                      |        | MIN                      | TYP                                                                                                                     | MAX                      | UNITS    |

|-------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------|----------|

| <b>デジタル・データ出力(<math>R_{TERM} = 100\Omega</math>差動、各出力でGNDに<math>C_L = 2\text{pF}</math>を接続)</b> |                               |                                                                                                                                                                                                 |        |                          |                                                                                                                         |                          |          |

| $t_{SER}$                                                                                       | Serial Data Bit Period        | 2-Lanes, 16-Bit Serialization<br>2-Lanes, 14-Bit Serialization<br>2-Lanes, 12-Bit Serialization<br>1-Lane, 16-Bit Serialization<br>1-Lane, 14-Bit Serialization<br>1-Lane, 12-Bit Serialization |        |                          | 1 / (8 • $f_S$ )<br>1 / (7 • $f_S$ )<br>1 / (6 • $f_S$ )<br>1 / (16 • $f_S$ )<br>1 / (14 • $f_S$ )<br>1 / (12 • $f_S$ ) |                          | s        |

| $t_{FRAME}$                                                                                     | FR to DCO Delay               | (Note 8)                                                                                                                                                                                        | ●      | $0.35 \cdot t_{SER}$     | $0.5 \cdot t_{SER}$                                                                                                     | $0.65 \cdot t_{SER}$     | s        |

| $t_{DATA}$                                                                                      | DATA to DCO Delay             | (Note 8)                                                                                                                                                                                        | ●      | $0.35 \cdot t_{SER}$     | $0.5 \cdot t_{SER}$                                                                                                     | $0.65 \cdot t_{SER}$     | s        |

| $t_{PD}$                                                                                        | Propagation Delay             | (Note 8)                                                                                                                                                                                        | ●      | $0.7n + 2 \cdot t_{SER}$ | $1.1n + 2 \cdot t_{SER}$                                                                                                | $1.5n + 2 \cdot t_{SER}$ | s        |

| $t_R$                                                                                           | Output Rise Time              | Data, DCO, FR, 20% to 80%                                                                                                                                                                       |        |                          | 0.17                                                                                                                    |                          | ns       |

| $t_F$                                                                                           | Output Fall Time              | Data, DCO, FR, 20% to 80%                                                                                                                                                                       |        |                          | 0.17                                                                                                                    |                          | ns       |

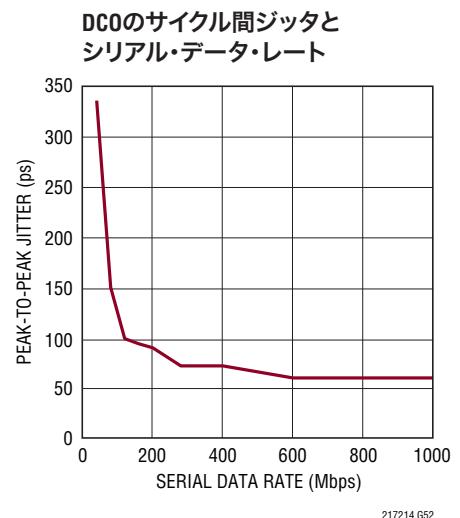

|                                                                                                 | DCO Cycle-to-Cycle Jitter     | $t_{SER} = 1\text{ns}$                                                                                                                                                                          |        |                          | 60                                                                                                                      |                          | pS-P-P   |

|                                                                                                 | Pipeline Latency              |                                                                                                                                                                                                 |        |                          | 6                                                                                                                       |                          | Cycles   |

| <b>SPIポートのタイミング (Note 8)</b>                                                                    |                               |                                                                                                                                                                                                 |        |                          |                                                                                                                         |                          |          |

| $t_{SCK}$                                                                                       | SCK Period                    | Write Mode<br>Readback Mode, $C_{SDO} = 20\text{pF}$ , $R_{PULLUP} = 2\text{k}\Omega$                                                                                                           | ●<br>● | 40<br>250                |                                                                                                                         |                          | ns<br>ns |

| $t_S$                                                                                           | $\bar{CS}$ to SCK Set-Up Time |                                                                                                                                                                                                 | ●      | 5                        |                                                                                                                         |                          | ns       |

| $t_H$                                                                                           | SCK to $\bar{CS}$ Set-Up Time |                                                                                                                                                                                                 | ●      | 5                        |                                                                                                                         |                          | ns       |

| $t_{DS}$                                                                                        | SDI Set-Up Time               |                                                                                                                                                                                                 | ●      | 5                        |                                                                                                                         |                          | ns       |

| $t_{DH}$                                                                                        | SDI Hold Time                 |                                                                                                                                                                                                 | ●      | 5                        |                                                                                                                         |                          | ns       |

| $t_{DO}$                                                                                        | SCK Falling to SDO Valid      | Readback Mode<br>$C_{SDO} = 20\text{pF}$ , $R_{PULLUP} = 2\text{k}\Omega$                                                                                                                       | ●      |                          |                                                                                                                         | 125                      | ns       |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**すべての電圧値は(注記がない限り) GNDとOGNDを短絡した状態のGNDを基準にしている。

**Note 3:**これらのピンの電圧をGNDより低くするとか $V_{DD}$ より高くすると、内部のダイオードによってクランプされる。この製品はGNDより低い、または $V_{DD}$ より高い電圧で、ラッチアップを起こさずに100mA以上の入力電流を処理することができる。

**Note 4:**これらのピンの電圧をGNDより低くすると、内部のダイオードによってクランプされる。これらのピンの電圧を $V_{DD}$ より高くすると、内部のダイオードによってクランプされない。この製品はGNDよりも低い電圧で、ラッチアップを起こさずに100mA以上の入力電流を処理することができる。

**Note 5:**注記がない限り、 $V_{DD} = 0V$ ,  $V_{DD} = 1.8V$ ,  $f_{SAMPLE} = 65\text{MHz}$  (LTC2172),  $40\text{MHz}$  (LTC2171),  $25\text{MHz}$  (LTC2170), 2レーン出力モード、差動 $ENC^+ / ENC^- = 2V_{P-P}$ の正弦波、入力範囲 = 差動ドライブで $2V_{P-P}$ 。消費電流および電力損失の規格値はデバイス全体の合計値であり、1チャネルあたりの値ではない。

**Note 6:**積分非直線性は伝達曲線に最も適合する直線からのコードの偏差として定義される。偏差は量子化幅の中心から測定する。

**Note 7:**オフセット誤差は、2の補数出力モードで出力コードを00 0000 0000 0000と11 1111 1111 1111の間でふらつかせるとき、-0.5 LSBから測定したオフセット電圧である。

**Note 8:**設計によって保証されており、テストされない。

**Note 9:**注記がない限り、 $V_{DD} = 0V$ ,  $V_{DD} = 1.8V$ ,  $f_{SAMPLE} = 65\text{MHz}$  (LTC2172),  $40\text{MHz}$  (LTC2171),  $25\text{MHz}$  (LTC2170), 2レーン出力モード、 $ENC^+ = \text{シングルエンドの} 1.8\text{V方形波}$ ,  $ENC^- = 0V$ , 入力範囲 = 差動ドライブで $2V_{P-P}$ 。消費電流および電力損失の規格値はデバイス全体の合計値であり、1チャネルあたりの値ではない。

**Note 10:**推奨動作条件。

**Note 11:**最大サンプリング周波数はデバイスの速度グレードによって異なり、どのシリアル化モードが使用されているかによっても異なる。最大シリアル・データ・レートは1000Mbpsなので、 $t_{SER}$ は1ns以上でなければならない。

**Note 12:**Near-channel crosstalkとは、Ch.1-Ch.2間およびCh.3-Ch.4間のクロストークのことを指す。Far-channel crosstalkとは、Ch.1-Ch.3間、Ch.1-Ch.4間、Ch.2-Ch.3間およびCh.2-Ch.4間のクロストークのことを指す。

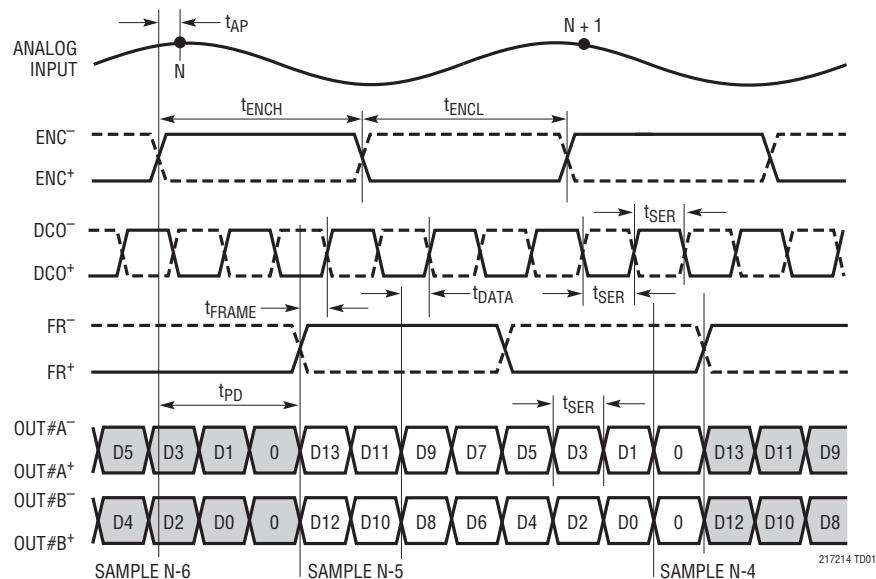

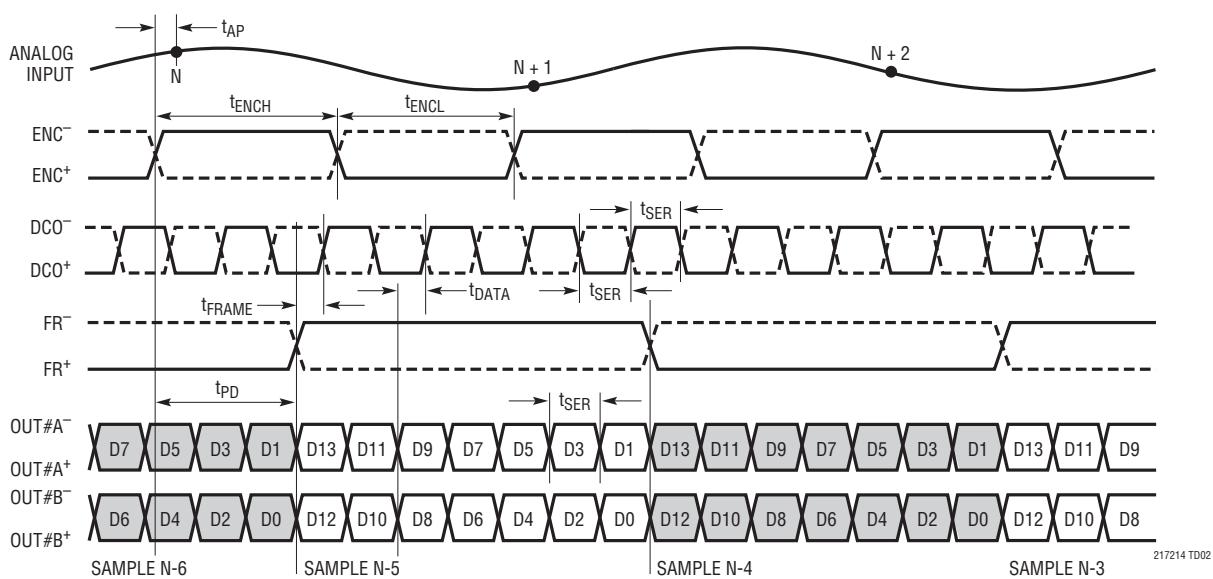

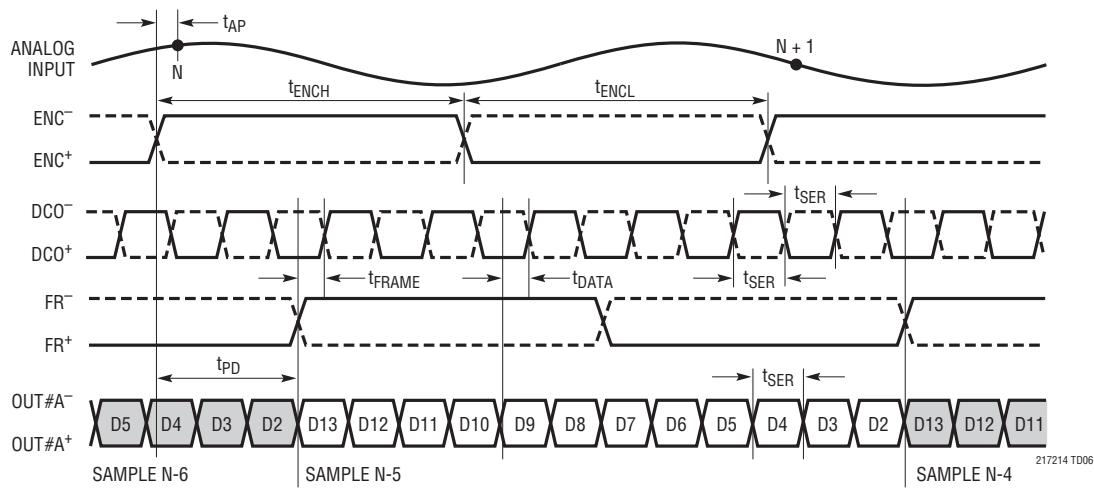

タイミング図

2レーン出力モード、16ビット・シリアル化\*

\*「デジタル出力」のセクションを参照

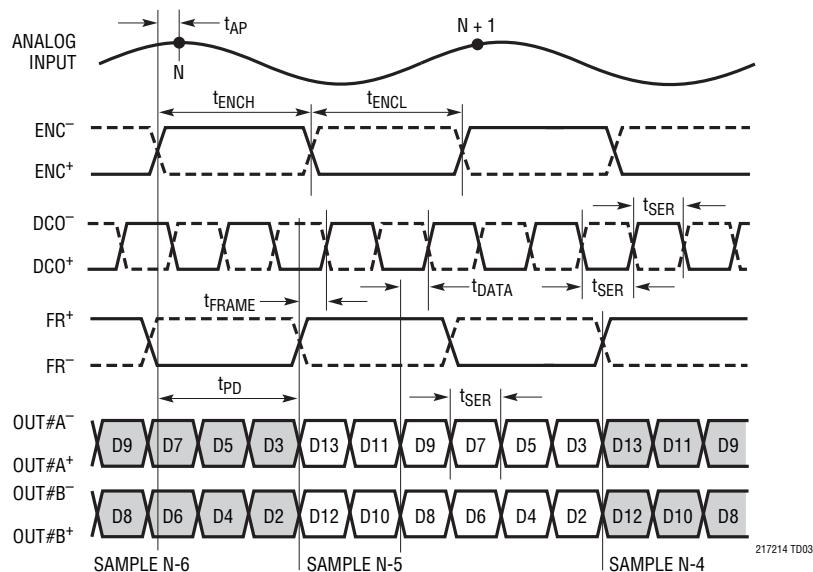

2レーン出力モード、14ビット・シリアル化

このモードではFR+/FR-の周期がENC+/ENC-の周期の2倍であることに注意

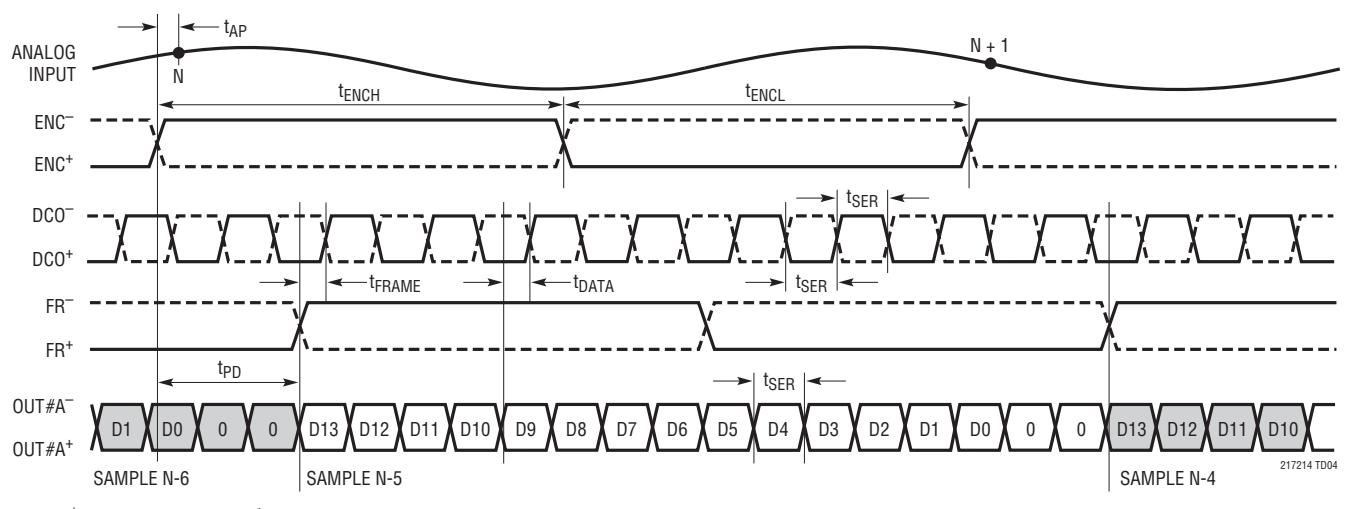

## タイミング図

2レーン出力モード、12ビット・シリアル化

1レーン出力モード、16ビット・シリアル化

# LTC2172-14/ LTC2171-14/LTC2170-14

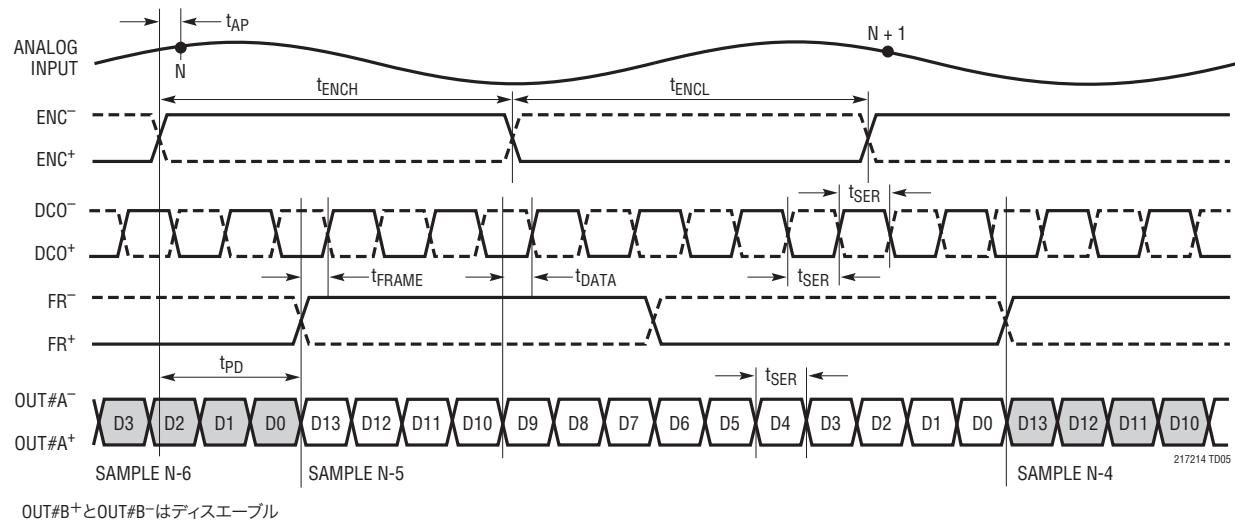

## タイミング図

1レーン出力モード、14ビット・シリアル化

OUT#B<sup>+</sup>とOUT#B<sup>-</sup>はディスエーブル

1レーン出力モード、12ビット・シリアル化

OUT#B<sup>+</sup>とOUT#B<sup>-</sup>はディスエーブル

21721014fb

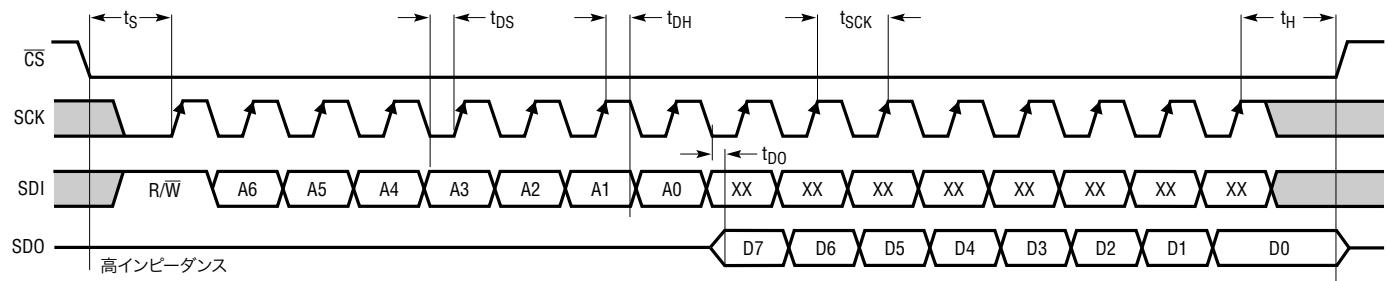

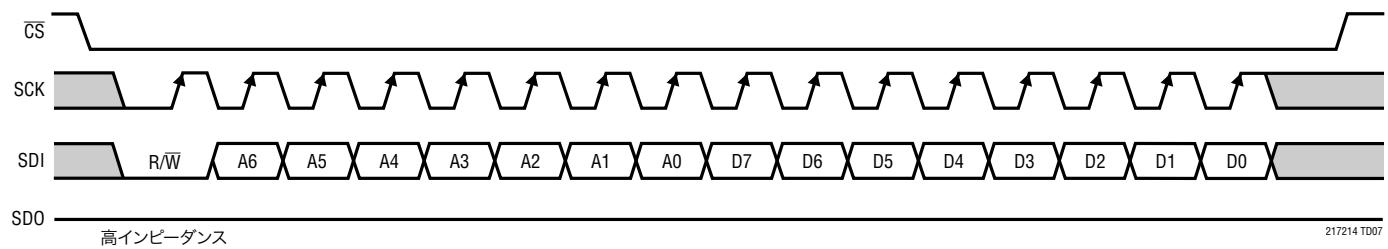

## タイミング図

SPIポートのタイミング(読み出しモード)

SPIポートのタイミング(書き込みモード)

217214 TD07

# LTC2172-14/ LTC2171-14/LTC2170-14

## 標準的性能特性

## 標準的性能特性

# LTC2172-14/ LTC2171-14/LTC2170-14

## 標準的性能特性

## 標準的性能特性

# LTC2172-14/ LTC2171-14/LTC2170-14

## 標準的性能特性

## ピン機能

**A<sub>IN1</sub><sup>+</sup>(ピン1)**: チャネル1の正の差動アナログ入力。

**A<sub>IN1</sub><sup>-</sup>(ピン2)**: チャネル1の負の差動アナログ入力。

**V<sub>CM12</sub>(ピン3)**: 公称V<sub>DD</sub>/2に等しい同相バイアス出力。V<sub>CM</sub>は、チャネル1とチャネル2のアナログ入力の同相レベルをバイアスするのに使用します。0.1μFのセラミック・コンデンサを使用してグランドにバイパスします。

**A<sub>IN2</sub><sup>+</sup>(ピン4)**: チャネル2の正の差動アナログ入力。

**A<sub>IN2</sub><sup>-</sup>(ピン5)**: チャネル2の負の差動アナログ入力。

**REFH(ピン6、7)**: ADCの“H”リファレンス。2.2μFのセラミック・コンデンサを使用してピン8とピン9にバイパスし、0.1μFのセラミック・コンデンサを使用してグランドにバイパスします。

**REFL(ピン8、9)**: ADCの“L”リファレンス。2.2μFのセラミック・コンデンサを使用してピン6とピン7にバイパスし、0.1μFのセラミック・コンデンサを使用してグランドにバイパスします。

**A<sub>IN3</sub><sup>+</sup>(ピン10)**: チャネル3の正の差動アナログ入力。

**A<sub>IN3</sub><sup>-</sup>(ピン11)**: チャネル3の負の差動アナログ入力。

**V<sub>CM34</sub>(ピン12)**: 公称V<sub>DD</sub>/2に等しい同相バイアス出力。V<sub>CM</sub>は、チャネル3とチャネル4のアナログ入力の同相レベルをバイアスするのに使用します。0.1μFのセラミック・コンデンサを使用してグランドにバイパスします。

**A<sub>IN4</sub><sup>+</sup>(ピン13)**: チャネル4の正の差動アナログ入力。

**A<sub>IN4</sub><sup>-</sup>(ピン14)**: チャネル4の負の差動アナログ入力。

**V<sub>DD</sub>(ピン15、16、51、52)**: 1.8Vのアナログ電源。0.1μFのセラミック・コンデンサを使用してグランドにバイパスします。隣接するピンはバイパス・コンデンサを共有することができます。

**ENC<sup>+</sup>(ピン17)**: エンコード入力。立ち上がりエッジで変換が開始されます。

**ENC<sup>-</sup>(ピン18)**: エンコード相補入力。立ち下がりエッジで変換が開始されます。

**CS(ピン19)**: シリアル・プログラミング・モード(PAR/SER = 0V)では、CSはシリアル・インターフェースのチップ・セレクト入力です。CSが“L”的とき、SCKがイネーブルされ、SDIのデータをモード制御レジスタにシフトします。パラレル・プログラミング・モード(PAR/SER = V<sub>DD</sub>)では、CSによって2レーンまたは1レーンの出力モードが選択されます。CSは1.8V～3.3Vのロジックでドライブできます。

**SCK(ピン20)**: シリアル・プログラミング・モード(PAR/SER = 0V)では、SCKはシリアル・インターフェースのクロック入力です。パラレル・プログラミング・モード(PAR/SER = V<sub>DD</sub>)では、SCKによって3.5mAまたは1.75mAのLVDS出力電流が選択されます。SCKは1.8V～3.3Vのロジックでドライブできます。

**SDI(ピン21)**: シリアル・プログラミング・モード(PAR/SER = 0V)では、SDIはシリアル・インターフェースのデータ入力です。SDIのデータはSCKの立ち上がりエッジでモード制御レジスタにクロックインされます。パラレル・プログラミング・モード(PAR/SER = V<sub>DD</sub>)では、SDIを使用してデバイスをパワーダウンさせることができます。SDIは1.8V～3.3Vのロジックでドライブできます。

**GND(ピン22、45、49、露出パッド・ピン53)**: ADCの電源グランド。露出パッドはPCBグランドに半田付けする必要があります。

**0GND(ピン33)**: 出力ドライバのグランド。非常に低いインダクタンスのパスによってグランド・プレーンに短絡する必要があります。ピンの近くに複数のビアを使用します。

**0V<sub>DD</sub>(ピン34)**: 出力ドライバの電源。0.1μFのセラミック・コンデンサを使用してグランドにバイパスします。

**SDO(ピン46)**: シリアル・プログラミング・モード(PAR/SER = 0V)では、SDOはオプションのシリアル・インターフェースのデータ出力です。SDOのデータは、モード制御レジスタから読み出してSCKの立ち下がりエッジでラッチすることができます。SDOはオープン・ドレインのNチャネルMOSFET出力で、1.8V～3.3V～2kのプルアップ抵抗を外付けする必要があります。モード制御レジスタから読み出す必要がない場合には、プルアップ抵抗は不要でSDOを未接続の状態にしておくことができます。パラレル・プログラミング・モード(PAR/SER = V<sub>DD</sub>)では、SDOはデジタル出力の100Ωの内部終端抵抗をイネーブルする入力です。SDOを入力として使用する場合には、1kの直列抵抗を介して1.8V～3.3Vのロジックでドライブすることができます。

## ピン機能

**PAR/SER(ピン47)** : プログラミング・モード選択ピン。シリアル・プログラミング・モードをイネーブルするにはグランドに接続します。 $\overline{CS}$ 、SCK、SDI、SDOは、A/Dの動作モードを制御するシリアル・インターフェースになります。パラレル・プログラミング・モードをイネーブルするにはV<sub>DD</sub>に接続します。この場合、 $\overline{CS}$ 、SCK、SDI、SDOは、A/Dの(種類が限定された)動作モードを制御するパラレル・ロジック入力になります。PAR/SERはグランドまたはデバイスのV<sub>DD</sub>に直接接続し、ロジック信号ではドライブしません。

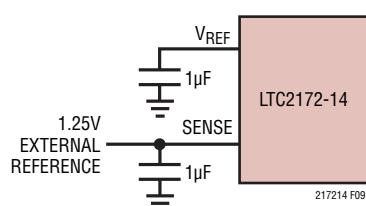

**V<sub>REF</sub>(ピン48)** : リファレンス電圧出力。1μFのセラミック・コンデンサを使用してグランドにバイパスします。公称1.25Vです。

**SENSE(ピン50)** : リファレンス・プログラミング・ピン。SENSEをV<sub>DD</sub>に接続すると、内部リファレンスと±1Vの入力範囲が選択されます。SENSEをグランドに接続すると、内部リファレンスと±0.5Vの入力範囲が選択されます。SENSEに0.625V～1.3Vの外部リファレンスを印加すると、±0.8 • V<sub>SENSE</sub>の入力範囲が選択されます。

### LVDS出力

以下に示すピンは差動LVDS出力です。出力電流レベルはプログラム可能です。各LVDS出力ペアのピンの間にはオプションの100Ωの内部終端抵抗が備わっています。

**OUT4B<sup>-</sup>/OUT4B<sup>+</sup>、OUT4A<sup>-</sup>/OUT4A<sup>+</sup>(ピン23/24、ピン25/26)** : チャネル4のシリアル・データ出力。1レーンの出力モードでは、OUT4A<sup>-</sup>/OUT4A<sup>+</sup>のみを使用します。

**OUT3B<sup>-</sup>/OUT3B<sup>+</sup>、OUT3A<sup>-</sup>/OUT3A<sup>+</sup>(ピン27/28、ピン29/30)** : チャネル3のシリアル・データ出力。1レーンの出力モードでは、OUT3A<sup>-</sup>/OUT3A<sup>+</sup>のみを使用します。

**FR<sup>-</sup>/FR<sup>+</sup>(ピン31/32)** : フレーム開始出力。

**DCO<sup>-</sup>/DCO<sup>+</sup>(ピン35/36)** : データ・クロック出力。

**OUT2B<sup>-</sup>/OUT2B<sup>+</sup>、OUT2A<sup>-</sup>/OUT2A<sup>+</sup>(ピン37/38、ピン39/40)** : チャネル2のシリアル・データ出力。1レーンの出力モードでは、OUT2A<sup>-</sup>/OUT2A<sup>+</sup>のみを使用します。

**OUT1B<sup>-</sup>/OUT1B<sup>+</sup>、OUT1A<sup>-</sup>/OUT1A<sup>+</sup>(ピン41/42、ピン43/44)** : チャネル1のシリアル・データ出力。1レーンの出力モードでは、OUT1A<sup>-</sup>/OUT1A<sup>+</sup>のみを使用します。

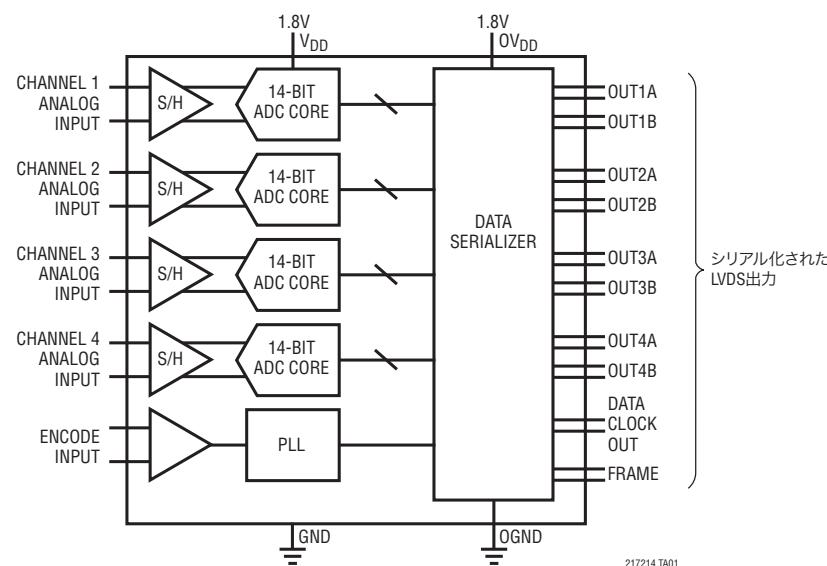

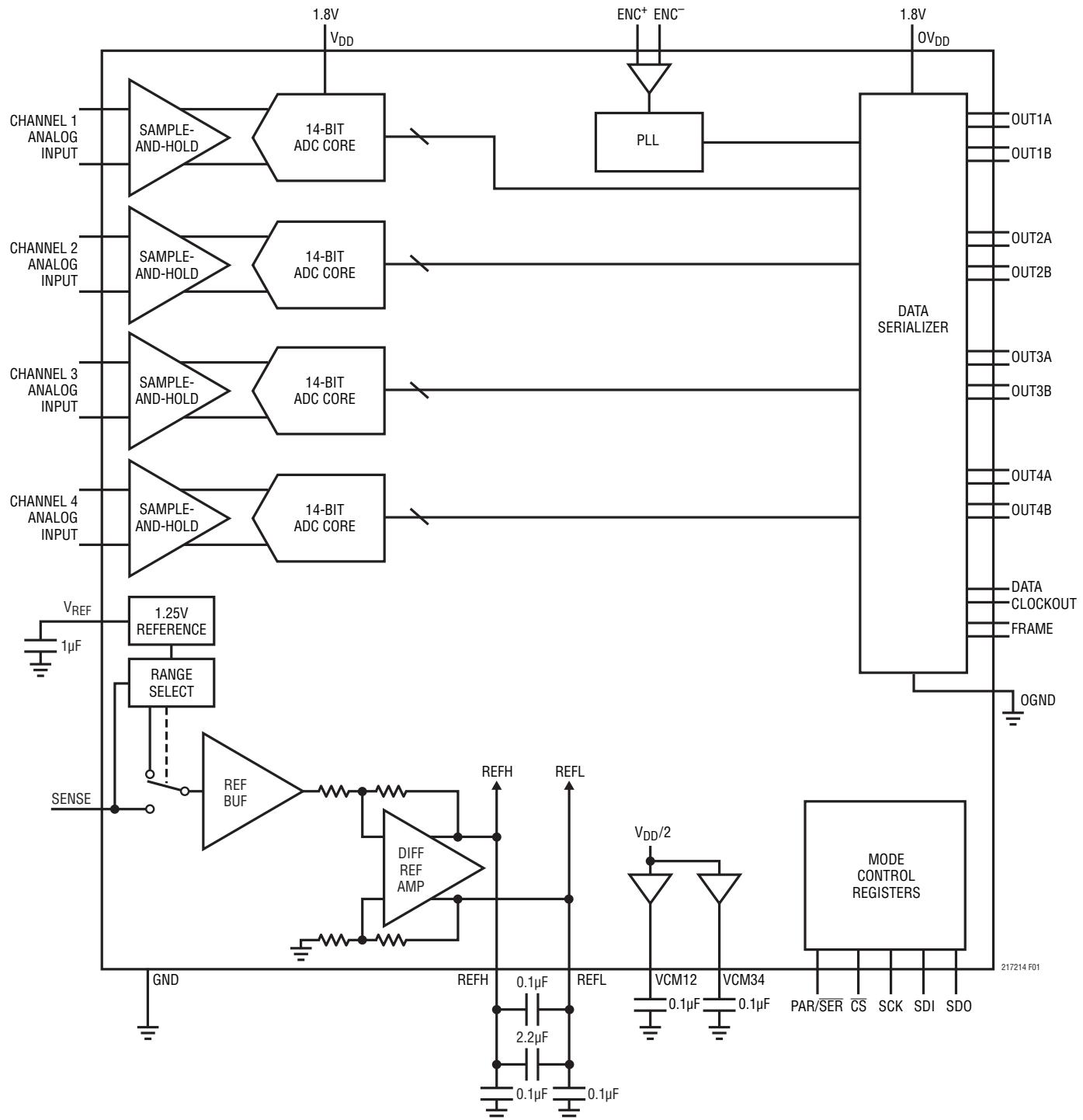

機能ブロック図

図1. 機能ブロック図

## アプリケーション情報

### コンバータの動作

LTC2172-14/LTC2171-14/LTC2170-14は、1.8V単一電源で動作する低消費電力、4チャネル、14ビット、65Msps/40Msps/25Msps A/Dコンバータです。アナログ入力は差動でドライブします。エンコード入力は最適なジッタ性能を得るために差動で、または消費電力を下げるためにシングルエンドでドライブすることができます。デジタル出力は、データ・ラインの数を最小限に抑えるためにシリアルLVDSを採用しています。各チャネルは一度に2ビット(2レーン・モード)または一度に1ビット(1レーン・モード)を出力します。シリアルSPIポートを介してモード制御レジスタをプログラムすることにより、多くの追加機能を選択することができます。

### アナログ入力

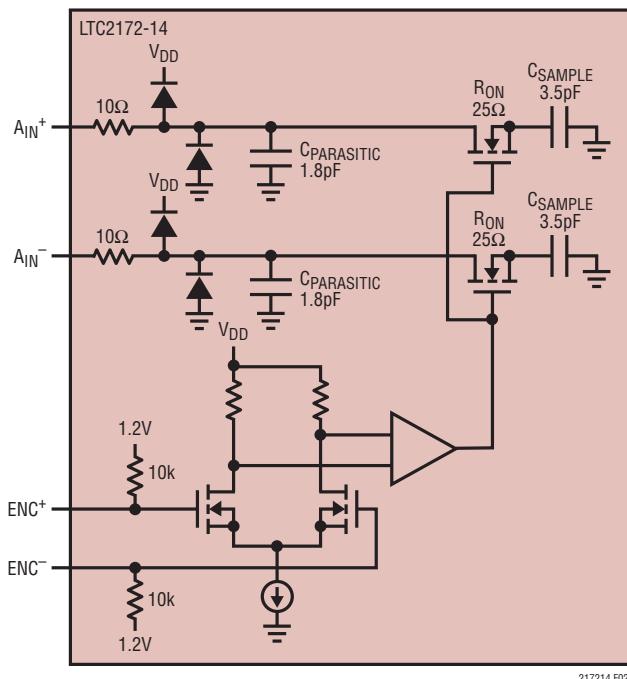

アナログ入力は差動CMOSサンプル・ホールド回路です(図2)。入力は、 $V_{CM12}$ 出力ピンまたは $V_{CM34}$ 出力ピンによって設定される同相電圧(公称 $V_{DD}/2$ )を中心にして差動でドライ

図2. 等価入力回路

4つのアナログ・チャネルの1つだけが示されている

ブする必要があります。2Vの入力範囲の場合、入力を $V_{CM}-0.5V$ から $V_{CM}+0.5V$ まで振幅させます。入力間には $180^{\circ}$ の位相差が必要です。

4つのチャネルは共有のエンコード回路(図2)によって同時にサンプリングされます。

### 入力ドライブ回路

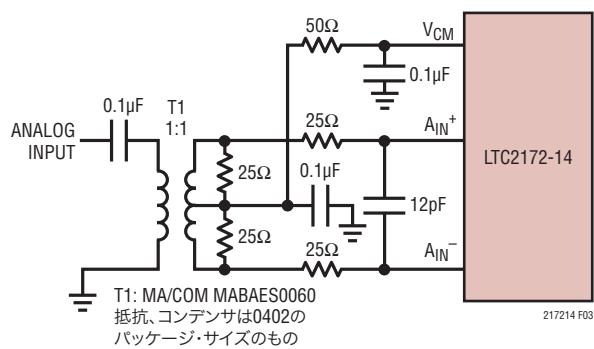

### 入力フィルタ

可能であれば、アナログ入力の間近にRCローパス・フィルタを置きます。このローパス・フィルタはドライブ回路をA/Dのサンプル・ホールドのスイッチング回路から絶縁し、ドライブ回路からの広帯域ノイズを制限します。入力RCフィルタの一例を図3に示します。RC部品の値はアプリケーションの入力周波数に基づいて選択します。

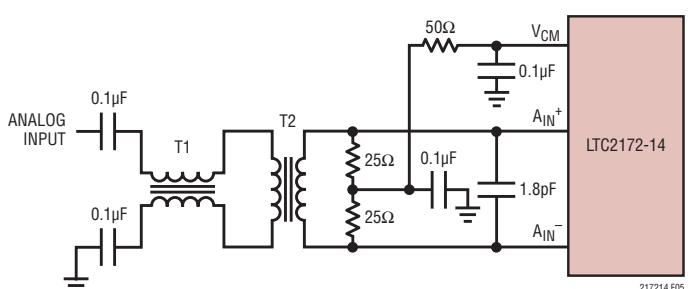

図3. トランスを使用したアナログ入力回路

5MHz～70MHzの入力周波数に対して推奨

## アプリケーション情報

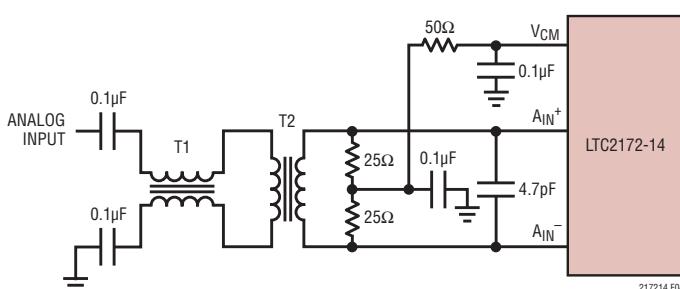

### トランス結合回路

2次側にセンタータップを備えたRFトランスによってドライブされるアナログ入力を図3に示します。センタータップはV<sub>CM</sub>でDCバイアスされており、A/Dの入力を最適DCレベルに設定します。高い入力周波数では、伝送ラインのバラン・トランス(図4～図6)のバランスが良くなるので、A/Dの歪みが小さくなります。

T1: MA/COM MABA-007159-000000

T2: MA/COM MABAES0060

抵抗、コンデンサは0402のパッケージ・サイズのもの

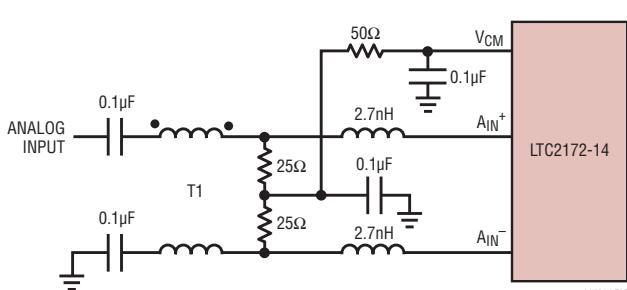

図4. 70MHz～170MHzの入力周波数用の

推奨フロントエンド回路

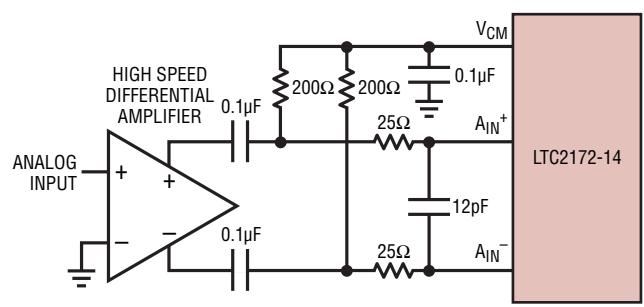

### アンプ回路

高速差動アンプによってドライブされるアナログ入力を図7に示します。アンプの出力はA/DにAC結合されているので、アンプの出力の同相電圧を最適に設定して歪みを最小限に抑えることができます。

非常に高い周波数では多くの場合、RF利得ブロックの方が差動アンプより歪みが小さくなります。利得ブロックがシングルエンドの場合には、A/Dをドライブする前にトランス回路(図4～図6)で信号を差動に変換します。

T1: MA/COM MABA-007159-000000

T2: COILCRAFT WBC1-1LB

抵抗、コンデンサは0402のパッケージ・サイズのもの

図5. 170MHz～300MHzの入力周波数用の

推奨フロントエンド回路

T1: MA/COM ETC1-1-13

抵抗、コンデンサは0402の

パッケージ・サイズのもの

図6. 300MHzを超える入力周波数用の

推奨フロントエンド回路

図7. 高速差動アンプを使用した

フロントエンド回路

# LTC2172-14/ LTC2171-14/LTC2170-14

## アプリケーション情報

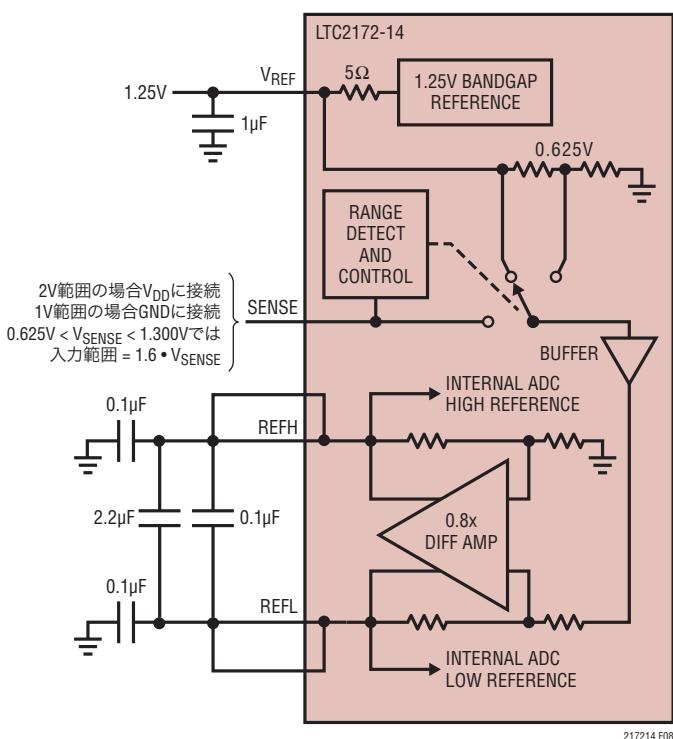

### リファレンス

LTC2172-14/LTC2171-14/LTC2170-14は1.25V電圧リファレンスを内蔵しています。内部リファレンスを使用する2Vの入力範囲の場合、SENSEをV<sub>DD</sub>に接続します。内部リファレンスを使用する1Vの入力範囲の場合、SENSEをグランドに接続します。外部リファレンスを使用する2Vの入力範囲の場合、1.25Vのリファレンス電圧をSENSEに印加します(図9)。

0.625V～1.30Vの電圧をSENSEに印加することによって入力範囲を調整することができます。入力範囲は $1.6 \cdot V_{SENSE}$ になります。

リファレンスは4つのADCチャネルの全てによって共有されているので、各チャネルの入力範囲を個別に調整することはできません。

V<sub>REF</sub>、REFH、REFLの各ピンは図8に示すようにバイパスします。REFHとREFLの間の0.1μFコンデンサは(回路基板の裏側ではなく)できるだけピンに近づけます。

図8. リファレンス回路

### エンコード入力

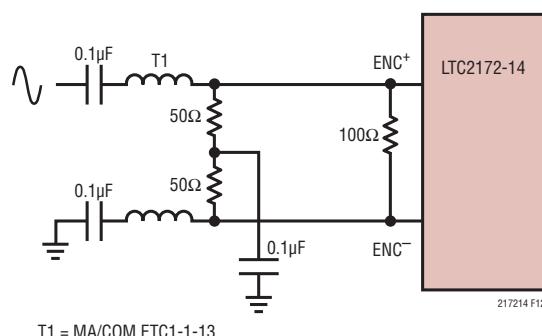

エンコード入力の信号品質はA/Dのノイズ性能に強く影響します。エンコード入力はアナログ信号として扱います。回路基板上でデジタル・トレースの隣に配線しないでください。エンコード入力には2つの動作モードがあります。差動エンコード・モード(図10)とシングルエンド・エンコード・モード(図11)です。

図9. 1.25Vの外部リファレンスを使用

図10. 差動エンコード・モードの等価エンコード入力回路

図11. シングルエンド・エンコード・モードの等価エンコード入力回路

## アプリケーション情報

正弦波、PECLまたはLVDSのエンコード入力には、差動エンコード・モードを推奨します(図12および図13)。エンコード入力は内部で10kの等価抵抗を介して1.2Vにバイアスされています。エンコード入力はVDDより高くすることができ(最大3.6V)、同相範囲は1.1V~1.6Vです。差動エンコード・モードでは、ENC<sup>+</sup>はグランドより200mV以上高く保って、シングルエンド・エンコード・モードを誤ってトリガしないようにします。良好なジッタ性能を得るため、ENC<sup>+</sup>の立ち上がり時間と立ち下がり時間を高速にします。

シングルエンド・エンコード・モードはCMOSエンコード入力で使用します。このモードを選択するには、ENC<sup>-</sup>をグランドに接続し、ENC<sup>+</sup>を方形波のエンコード入力でドライブします。ENC<sup>+</sup>はVDDより高くすることができるので(最大3.6V)、1.8V~3.3VのCMOSロジック・レベルを使用することができます。ENC<sup>+</sup>のスレッショルドは0.9Vです。良好なジッタ性能を得るため、ENC<sup>+</sup>の立ち上がり時間と立ち下がり時間を高速にします。

### クロックPLLとデューティ・サイクル・スタビライザ

エンコード・クロックは内部フェーズロック・ループ(PLL)によって乗算され、シリアル・デジタル出力データを生成します。エンコード信号の周波数が変化するか、またはオフした後、PLLが入力クロックにロックするのに25μsを要します。

クロック・デューティ・サイクル・スタビライザ回路により、印加されるエンコード信号のデューティ・サイクルは30%~70%の範囲の変動が許容されます。シリアル・プログラミング・モード

では、デューティ・サイクル・スタビライザをディスエーブルすることができますが、推奨しません。パラレル・プログラミング・モードでは、デューティ・サイクル・スタビライザは常にイネーブルされています。

### デジタル出力

LTC2172-14/LTC2171-14/LTC2170-14のデジタル出力はシリアル化されたLVDS信号です。各チャネルは一度に2ビット(2レーン・モード)または一度に1ビット(1レーン・モード)を出力します。データは16、14、または12ビットにシリアル化できます(詳細については「タイミング図」を参照)。12ビットにシリアル化する場合、2つの LSB は使用できないことに注意してください。このモードは、これらのデバイスの12ビット・バージョンと互換性をもたせるために用意されています。

出力データは、データ・クロック出力(DCO)の立ち上がりエッジと立ち下がりエッジでラッチされます。データ・フレーム出力(FR)を使用し、新たな変換のデータが出力され始める時点を決定することができます。2レーンの14ビット・シリアル化モードでは、FR出力の周波数は1/2になります。

データ出力の最大シリアル・データ・レートは1Gbpsなので、ADCの最大サンプリング・レートはADCの速度グレードだけでなく、シリアル化モードによっても異なります(表1を参照)。全てのシリアル化モードの最小サンプリング・レートは5Mspsです。

図12. 正弦波のエンコード・ドライブ

図13. PECLまたはLVDSのエンコード・ドライブ

## アプリケーション情報

表1. 全てのシリアル化モードの最大サンプリング周波数。これらの制限値はLTC2172-14のものであることに注意。遅い速度グレードのサンプリング周波数は、40MHz (LTC2171-14)または25MHz (LTC2170-14)を超えることはできない。

| シリアル化モード | 最大サンプリング周波数、 $f_s$ (MHz) | DCO周波数 | FR周波数           | シリアル・データ・レート    |

|----------|--------------------------|--------|-----------------|-----------------|

| 2-Lane   | 16-Bit Serialization     | 65     | $4 \cdot f_s$   | $f_s$           |

| 2-Lane   | 14-Bit Serialization     | 65     | $3.5 \cdot f_s$ | $0.5 \cdot f_s$ |

| 2-Lane   | 12-Bit Serialization     | 65     | $3 \cdot f_s$   | $f_s$           |

| 1-Lane   | 16-Bit Serialization     | 62.5   | $8 \cdot f_s$   | $f_s$           |

| 1-Lane   | 14-Bit Serialization     | 65     | $7 \cdot f_s$   | $f_s$           |

| 1-Lane   | 12-Bit Serialization     | 65     | $6 \cdot f_s$   | $f_s$           |

デフォルトでは、出力は出力電流が3.5mA、出力同相電圧が1.25Vの標準LVDSレベルです。各LVDS出力ペアには100Ωの差動終端抵抗を外付けする必要があります。終端抵抗はLVDSレシーバにできるだけ近づけて配置します。

出力はOV<sub>DD</sub>とOGND(それぞれ、A/Dのコア電源とグランドから絶縁されている)から電力供給されます。

### プログラム可能なLVDS出力電流

デフォルトの出力ドライバ電流は3.5mAです。シリアル・プログラミング・モードでは、この電流は制御レジスタA2によって調整することができます。使用可能な電流レベルは、1.75mA、2.1mA、2.5mA、3mA、3.5mA、4mAおよび4.5mAです。パラレル・プログラミング・モードでは、SCKピンは3.5mAまたは1.75mAのいずれかを選択できます。

### オプションのLVDSドライバの内部終端

ほとんどの場合、100Ωの外付け終端抵抗を使用するだけでLVDSの優れた信号品質が得られます。さらに、モード制御レジスタA2をシリアル・モードでプログラムすることにより、オプションの100Ωの内部終端抵抗をイネーブルすることができます。内部終端には、レシーバ側の不完全な終端によって生じる反射を吸収する効果があります。内部終端がイネーブルされると、出力ドライバ電流が2倍になって同じ出力電圧振幅を維持します。パラレル・プログラミング・モードでは、SDOピンによって内部終端がイネーブルされます。内部終端は、1.75mA、2.1mAまたは2.5mAのLVDS出力電流モードのときのみ使用します。

### データ・フォーマット

アナログ入力電圧とデジタル・データ出力ビット間の相関を表2に示します。デフォルトでは、出力のデータ・フォーマットはオフセット・バイナリです。モード制御レジスタA1をシリアル・モードでプログラムすることにより、2の補数のフォーマットを選択することができます。

表2. 出力コードと入力電圧

| $A_{IN}^+ - A_{IN}^-$<br>(2V範囲) | D13~D0<br>(オフセット・バイナリ) | D13~D0<br>(2の補数)  |

|---------------------------------|------------------------|-------------------|

| >1.000000V                      | 11 1111 1111 1111      | 01 1111 1111 1111 |

| +0.999878V                      | 11 1111 1111 1111      | 01 1111 1111 1111 |

| +0.999756V                      | 11 1111 1111 1110      | 01 1111 1111 1110 |

| +0.000122V                      | 10 0000 0000 0001      | 00 0000 0000 0001 |

| +0.000000V                      | 10 0000 0000 0000      | 00 0000 0000 0000 |

| -0.000122V                      | 01 1111 1111 1111      | 11 1111 1111 1111 |

| -0.000244V                      | 01 1111 1111 1110      | 11 1111 1111 1110 |

| -0.999878V                      | 00 0000 0000 0001      | 10 0000 0000 0001 |

| -1.000000V                      | 00 0000 0000 0000      | 10 0000 0000 0000 |

| ≤-1.000000V                     | 00 0000 0000 0000      | 10 0000 0000 0000 |

### デジタル出力ランダマイザ

A/Dのデジタル出力からの干渉を避けられない場合があります。デジタル信号による干渉は、容量性や誘導性の結合またはグランド・プレーンを介した結合から生じる可能性があります。結合係数が小さくても、ADCの出力スペクトルに不要なトーンを生じることができます。デジタル出力をデバイスから送出する前にランダム化することにより、これらの不要なトーンをランダム化し、不要なトーンの振幅を減少させることができます。

デジタル出力は、 LSBと他のすべてのデータ出力ビットの間で排他的論理とロジック演算を行うことによってランダム化されます。デコードするには、逆の演算を行います。つまりLSBと

## アプリケーション情報

他のすべてのビットの間で排他的論理和演算を行います。FR出力とDCO出力は影響を受けません。出力ランダマイザは、モード制御レジスタA1をシリアル・モードでプログラムすることによってイネーブルされます。

### デジタル出力のテストパターン

A/Dへのデジタル・インターフェースのインサーキット・テストを可能にするため、全てのチャネルのA/Dのデータ出力(D13~D0)を既知の値に強制するテスト・モードがあります。モード制御レジスタA3およびA4をシリアル・モードでプログラムすることにより、デジタル出力のテストパターンがイネーブルされます。テストパターンがイネーブルされると、他の全てのフォーマット・モード(2の補数およびランダマイザ)をオーバーライドします。

### 出力ディスエーブル

モード制御レジスタA2をシリアル・モードでプログラムすることにより、デジタル出力をディスエーブルすることができます。節電またはインサーキット・テストのイネーブルのため、DCOやFRを含む全てのデジタル出力の電流ドライブがディスエーブルされます。ディスエーブルされると、同相の各出力ペアが高インピーダンスになりますが、差動インピーダンスは低く保つことができます。

### スリープ・モードとナップ・モード

節電のため、A/Dをスリープ・モードまたはナップ・モードにすることができます。スリープ・モードでは、デバイス全体がパワーダウンし、1mWの消費電力になります。スリープ・モードは、モード制御レジスタA1(シリアル・プログラミング・モード)、またはSDI(パラレル・プログラミング・モード)によってイネーブルされます。スリープ・モードから回復するのに要する時間は、V<sub>REF</sub>、REFHおよびREFLのバイパス・コンデンサの容量によって決まります。図8の推奨値の場合、A/Dは2ms後に安定します。

ナップ・モードでは、どのA/Dチャネルの組み合わせもパワーダウンでき、内部リファレンス回路とPLLはアクティブなままで、スリープ・モードよりも速く回復することができます。ナップ・モードからの回復には少なくとも100クロック・サイクルを必要とします。非常に精確なDCセトリングが必要なアプリケーションの場合、50 $\mu$ sを追加することにより、A/Dがナップ・モードから移行するときの消費電流の変化によって生じるわずかな温度変化に対して内蔵リファレンスがセトリングできるようにします。ナップ・モードは、シリアル・プログラミング・モードのモード制御レジスタA1によってイネーブルされます。

### デバイスのプログラミング・モード

LTC2172-14/LTC2171-14/LTC2170-14の動作モードはパラレル・インターフェースまたはシンプルなシリアル・インターフェースのどちらでもプログラム可能です。シリアル・インターフェースの方が柔軟性に優れ、使用可能な全てのモードをプログラムすることができます。パラレル・インターフェースはそれに比べて限定されており、プログラムできるのはよく使用されるモードのいくつかだけです。

### パラレル・プログラミング・モード

パラレル・プログラミング・モードを使用するには、PAR/SERをV<sub>DD</sub>に接続します。CS、SCK、SDI、SDOの各ピンはバイナリ・ロジック入力で、特定の動作モードを設定します。これらのピンはV<sub>DD</sub>またはグランドに接続するか、あるいは1.8V、2.5Vまたは3.3VのCMOSロジックでドライブすることができます。SDOを入力として使用する場合には、1kの直列抵抗を介してドライブします。CS、SCK、SDIおよびSDOによって設定されるモードを表3に示します。

表3. パラレル・プログラミング・モードの制御ビット(PAR/SER = V<sub>DD</sub>)

| ピン  | 説明                                                                       |

|-----|--------------------------------------------------------------------------|

| CS  | 2レーン/1レーン選択ビット<br>0 = 2レーン、16ビット・シリアル化出力モード<br>1 = 1レーン、14ビット・シリアル化出力モード |

| SCK | LVDS電流選択ビット<br>0 = 3.5mA LVDS電流モード<br>1 = 1.75mA LVDS電流モード               |

| SDI | パワーダウン制御ビット<br>0 = 通常動作<br>1 = スリープ・モード                                  |

| SDO | 100 $\Omega$ の内部終端選択ビット<br>0 = 内部終端をディスエーブル<br>1 = 内部終端をイネーブル            |

### シリアル・プログラミング・モード

シリアル・プログラミング・モードを使用するには、PAR/SERをグランドに接続します。CS、SCK、SDI、SDOの各ピンは、A/Dのモード制御レジスタをプログラムするシリアル・インターフェースになります。データは16ビットのシリアル・ワードでレジスタに書き込まれます。レジスタの内容を検証するため、データをレジスタから読み出すこともできます。

シリアル・データ転送はCSが“L”になると開始されます。SDIピンのデータはSCKの最初の16個の立ち上がりエッジでラッチされます。最初の16個の後のSCKの立ち上がりエッジはどれも無視されます。データ転送はCSが再度“H”になると終了します。

## アプリケーション情報

16ビットの入力ワードの最初のビットはR/Wビットです。次の7ビットはレジスタのアドレス(A6:A0)です。最後の8ビットはレジスタのデータ(D7:D0)です。

R/Wビットが“L”的場合、シリアル・データ(D7:D0)が、アドレス・ビット(A6:A0)によって設定されるレジスタに書き込まれます。R/Wビットが“H”的場合、アドレス・ビット(A6:A0)によって設定されるレジスタ内のデータがSDOピンで読み出されます(「タイミング図」を参照)。読み出しコマンドの間レジスタは更新されず、SDIのデータは無視されます。

SDOピンはオープン・ドレイン出力で、200Ωのインピーダンスでグランドにプルダウンします。SDOを介してレジスタのデータを読み出す場合、2kのプルアップ抵抗を外付けする必要がある

ります。シリアル・データが書き込み専用で読み出しの必要がない場合は、SDOをフロートさせておくことができるので、プルアップ抵抗は必要ありません。モード制御レジスタのマップを表4に示します。

### ソフトウェアによるリセット

シリアル・プログラミングを使用する場合には、電源がオンして安定した後できるだけ早くモード制御レジスタをプログラムします。最初のシリアル・コマンドは、全てのレジスタのデータ・ビットをロジック0にリセットするソフトウェア・リセットでなければなりません。ソフトウェア・リセットを実行するには、リセット・レジスタのビットD7にロジック1を書き込みます。リセットSPI書き込みコマンドが完了した後、ビットD7は再度自動的にゼロに設定されます。

表4. シリアル・プログラミング・モードのレジスタ・マップ(PAR/SER = GND)

#### レジスタA0:リセット・レジスタ(アドレス00h)

| D7   | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|----|----|----|----|----|----|----|

| リセット | X  | X  | X  | X  | X  | X  | X  |

ビット7      **リセット**      ソフトウェア・リセット・ビット

0 = 不使用

1 = ソフトウェアによるリセット。全てのモード制御レジスタが00hにリセットされる。ADCは一時的にスリープ・モードになる。このビットはSPI書き込みコマンドの終了時に、再度、自動的にゼロに設定される。リセット・レジスタは書き込み専用。

ビット6~0      使用されない、ドントケア・ビット。

#### レジスタA1:パワーダウン・レジスタ(アドレス01h)

| D7     | D6   | D5       | D4    | D3    | D2    | D1    | D0    |

|--------|------|----------|-------|-------|-------|-------|-------|

| DCSOFF | RAND | TWOSCOMP | SLEEP | NAP_4 | NAP_3 | NAP_2 | NAP_1 |

ビット7      **DCSOFF**      クロック・デューティ・サイクル・スタビライザ・ビット

0 = クロック・デューティ・サイクル・スタビライザをオン

1 = クロック・デューティ・サイクル・スタビライザをオフ。これは推奨されない。

ビット6      **RAND**      データ出力ランダマイザ・モード制御ビット

0 = データ出力ランダマイザ・モードをオフ

1 = データ出力ランダマイザ・モードをオン

ビット5      **TWOSCOMP**      2の補数モード制御ビット

0 = オフセット・バイナリのデータ・フォーマット

1 = 2の補数のデータ・フォーマット

ビット4~0      **SLEEP:NAP\_4:NAP\_1**      スリープ/ナップ・モード制御ビット

00000 = 通常動作

0XX1 = チャネル1がナップ・モード

0X1X = チャネル2がナップ・モード

0X1XX = チャネル3がナップ・モード

01XXX = チャネル4がナップ・モード

1XXXX = スリープ・モード。全てのチャネルがディスエーブル

注記:ナップ・モードではチャネルのどの組み合わせも設定可能。

## アプリケーション情報

### レジスタA2:出力モード・レジスタ(アドレス02h)

| D7     | D6                                                                                                                                                                                                                                                 | D5     | D4     | D3     | D2       | D1       | D0       |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|----------|----------|----------|

| ILVDS2 | ILVDS1                                                                                                                                                                                                                                             | ILVDS0 | TERMON | OUTOFF | OUTMODE2 | OUTMODE1 | OUTMODE0 |

| ビット7~5 | <b>ILVDS2:ILVDS0</b> LVDS出力電流ビット<br>000 = 3.5mAのLVDS出力ドライバ電流<br>001 = 4.0mAのLVDS出力ドライバ電流<br>010 = 4.5mAのLVDS出力ドライバ電流<br>011 = 不使用<br>100 = 3.0mAのLVDS出力ドライバ電流<br>101 = 2.5mAのLVDS出力ドライバ電流<br>110 = 2.1mAのLVDS出力ドライバ電流<br>111 = 1.75mAのLVDS出力ドライバ電流 |        |        |        |          |          |          |

| ビット4   | <b>TERMON</b> LVDS内部終端ビット<br>0 = 内部終端をオフ<br>1 = 内部終端をオン。LVDS出力ドライバ電流はILVDS2:ILVDS0で設定された電流の2倍になる。内部終端は、1.75mA、2.1mAまたは2.5mAのLVDS出力電流モードのときのみ使用する。                                                                                                  |        |        |        |          |          |          |

| ビット3   | <b>OUTOFF</b> 出力ディスエーブル・ビット<br>0 = デジタル出力をイネーブル<br>1 = デジタル出力をディスエーブル                                                                                                                                                                              |        |        |        |          |          |          |

| ビット2~0 | <b>OUTMODE2:OUTMODE0</b> デジタル出力モード制御ビット<br>000 = 2レーン、16ビットのシリアル化<br>001 = 2レーン、14ビットのシリアル化<br>010 = 2レーン、12ビットのシリアル化<br>011 = 不使用<br>100 = 不使用<br>101 = 1レーン、14ビットのシリアル化<br>110 = 1レーン、12ビットのシリアル化<br>111 = 1レーン、16ビットのシリアル化                      |        |        |        |          |          |          |

### レジスタA3:テストパターンMSBレジスタ(アドレス03h)

| D7      | D6                                                                                            | D5   | D4   | D3   | D2   | D1  | D0  |

|---------|-----------------------------------------------------------------------------------------------|------|------|------|------|-----|-----|

| OUTTEST | X                                                                                             | TP13 | TP12 | TP11 | TP10 | TP9 | TP8 |

| ビット7    | <b>OUTTEST</b> デジタル出力のテストパターン制御ビット<br>0 = デジタル出力のテストパターンをオフ<br>1 = デジタル出力のテストパターンをオン          |      |      |      |      |     |     |

| ビット6    | 使用されない、ドントケア・ビット。                                                                             |      |      |      |      |     |     |

| ビット5~0  | <b>TP13:TP8</b> テストパターン・データ・ビット(MSB)<br>TP13:TP8により、データ・ビット13(MSB)のテストパターンがデータ・ビット8を介して設定される。 |      |      |      |      |     |     |

### レジスタA4: テストパターンLSBレジスタ(アドレス04h)

| D7     | D6                                                                                         | D5  | D4  | D3  | D2  | D1  | D0  |

|--------|--------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|

| TP7    | TP6                                                                                        | TP5 | TP4 | TP3 | TP2 | TP1 | TP0 |

| ビット7~0 | <b>TP7:TP0</b> テストパターン・データ・ビット(LSB)<br>TP7:TP0により、データ・ビット7のテストパターンがデータ・ビット0(LSB)を介して設定される。 |     |     |     |     |     |     |

## アプリケーション情報

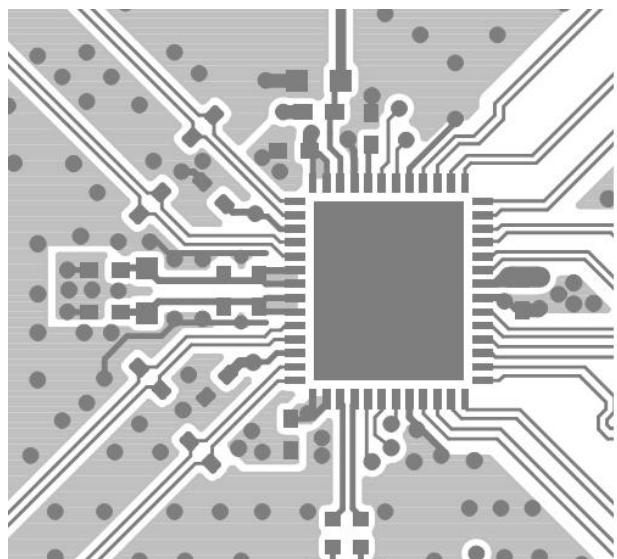

### 接地とバイパス

LTC2172-14/LTC2171-14/LTC2170-14には、切れ目のないクリーンなグランド・プレーンを備えたプリント基板が必要です。ADCの下の最初の層に内部グランド・プレーンを備えた多層基板を推奨します。プリント回路基板のレイアウトでは、デジタル信号ラインとアナログ信号ラインをできるだけ分離します。特に、アナログ信号トラックの横やADCの下にデジタル・トラックを通さないように注意する必要があります。

$V_{DD}$ 、 $OV_{DD}$ 、 $V_{CM}$ 、 $V_{REF}$ 、 $REFH$ 、 $REFL$ の各ピンには、高品質のセラミック・バイパス・コンデンサを使用します。バイパス・コンデンサは、できるだけピンの近くに配置する必要があります。特に重要なのは、 $REFH$ と $REFL$ の間の $0.1\mu F$ のコンデンサです。このコンデンサは回路基板のA/Dと同じ側に、できるだけデバイスに近づけて(1.5mm以内)配置してください。サイズが0402のセラミック・コンデンサを推奨します。 $REFH$ と $REFL$

の間の大きな $2.2\mu F$ のコンデンサはこれよりいくらか離れてもかまいません。ピンとバイパス・コンデンサを接続するトレースは短くし、できるだけ幅を広くする必要があります。

アナログ入力、エンコード信号、およびデジタル出力は互いに隣接しないように配線します。これらの信号を互いに絶縁するためのバリヤとして、グランド領域とグランド・ビアを使用します。

### 熱伝導

LTC2172-14/LTC2171-14/LTC2170-14が発生する熱の大部分はダイから底面の露出パッドとパッケージの端子を通ってプリント回路基板に伝わります。優れた電気的特性と熱特性を得るためにには、露出パッドをPC基板の大きな接地されたパッドに半田付けする必要があります。このパッドは複数のビアで内部グランド・プレーンに接続します。

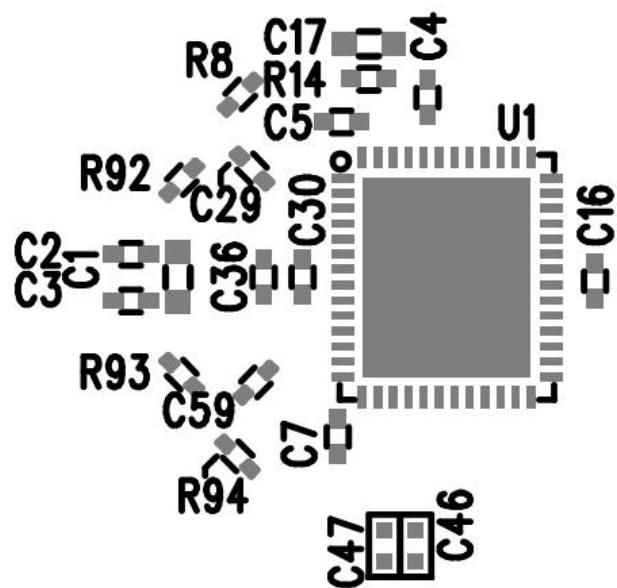

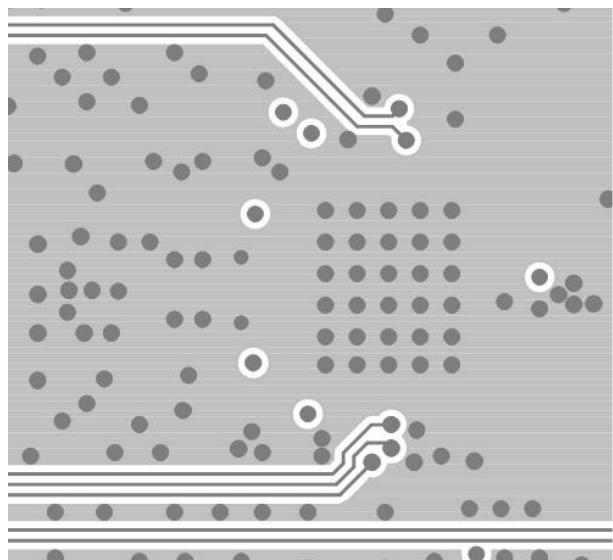

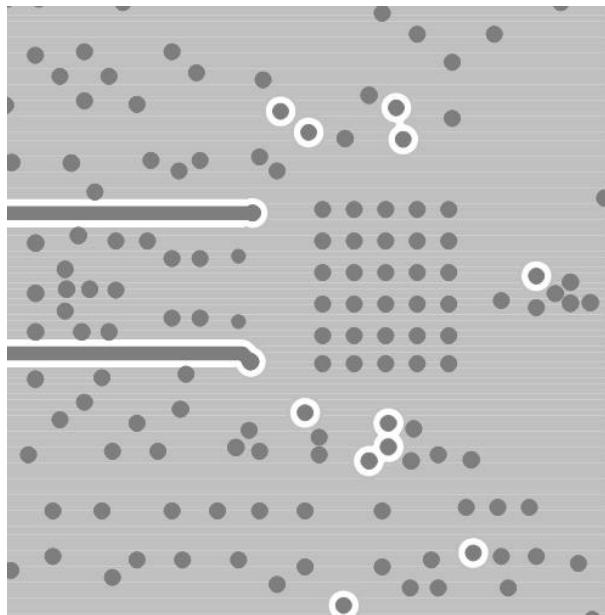

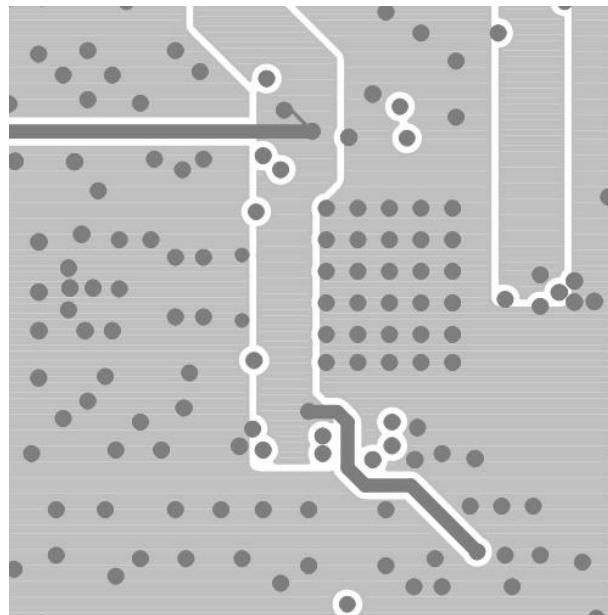

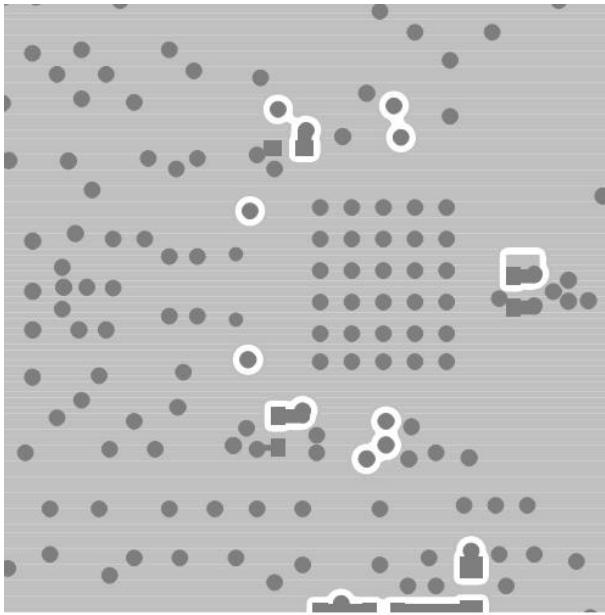

標準的応用例

シルクスクリーンの上面

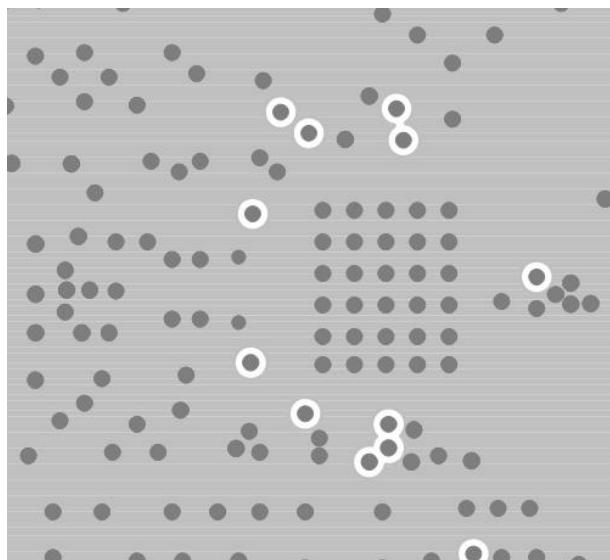

上面

内部第2層GND

内部第3層

標準的応用例

内部第4層

内部第5層電源

底面

シリクスクリーンの底面

C8

C9

C15

標準的応用例

LTC2172の回路図

パッケージ

UKGパッケージ

52ピン・プラスチックQFN(7mm×8mm)

(Reference LTC DWG # 05-08-1729 Rev Ø)

改訂履歴 (Rev Aよりスタート)

| Rev | 日付    | 概要                                                                                                                                     | ページ番号         |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------|---------------|

| A   | 03/10 | 「タイミング特性」のセクションのLTC2171-14のSampling FrequencyのMax値を45MHzから40MHzに変更<br>「アプリケーション情報」の「接地とバイパス」と「熱伝導」セクションに全製品名追加<br>「関連製品」セクションの説明と注釈の改訂 | 6<br>28<br>34 |

| B   | 07/11 | 「ピン機能」セクションの41~44ピンの名称を訂正(和文版では全バージョンで修正済み)<br>「アプリケーション情報」セクションの「ソフトウェアによるリセット」の段落と表4を改訂                                              | 18<br>26      |

# LTC2172-14/ LTC2171-14/LTC2170-14

## 関連製品

| 製品番号                                 | 説明                                                 | 注釈                                                                                        |

|--------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------|

| <b>ADC</b>                           |                                                    |                                                                                           |

| LTC2170-12/LTC2171-12/<br>LTC2172-12 | 12ビット、25Msps/40Msps/65Msps<br>1.8VクワッドADC、超低消費電力   | 160mW/198mW/306mW、SNR:71dB、SFDR:90dB、シリアルLVDS出力、<br>7mm×8mm QFN-52パッケージ                   |

| LTC2173-12/LTC2174-12/<br>LTC2175-12 | 12ビット、80Msps/105Msps/125Msps<br>1.8VクワッドADC、超低消費電力 | 369mW/439mW/545mW、SNR:70.6dB、SFDR:88dB、シリアルLVDS出力、<br>7mm×8mm QFN-52パッケージ                 |

| LTC2256-14/LTC2257-14/<br>LTC2258-14 | 14ビット、25Msps/40Msps/65Msps<br>1.8V ADC、超低消費電力      | 35mW/49mW/81mW、SNR:74dB、SFDR:88dB、DDR LVDS、<br>DDR CMOSまたはCMOS出力、6mm×6mm QFN-40パッケージ      |

| LTC2259-14/LTC2260-14/<br>LTC2261-14 | 14ビット、80Msps/105Msps/125Msps<br>1.8V ADC、超低消費電力    | 89mW/106mW/127mW、SNR:73.4dB、SFDR:85dB、DDR LVDS、<br>DDR CMOSまたはCMOS出力、6mm×6mm QFN-40パッケージ  |

| LTC2262-14                           | 14ビット、150Msps 1.8V ADC、<br>超低消費電力                  | 149mW、SNR:72.8dB、SFDR:88dB、DDR LVDS、<br>DDR CMOSまたはCMOS出力、6mm×6mm QFN-40パッケージ             |

| LTC2263-14/LTC2264-14/<br>LTC2265-14 | 14ビット、25Msps/40Msps/65Msps<br>1.8VデュアルADC、超低消費電力   | 94mW/113mW/171mW、SNR:73.7dB、SFDR:90dB、シリアルLVDS出力、<br>6mm×6mm QFN-40パッケージ                  |

| LTC2263-12/LTC2264-12/<br>LTC2265-12 | 12ビット、25Msps/40Msps/65Msps<br>1.8VデュアルADC、超低消費電力   | 94mW/112mW/167mW、SNR:71dB、SFDR:90dB、シリアルLVDS出力、<br>6mm×6mm QFN-40パッケージ                    |

| LTC2266-14/LTC2267-14/<br>LTC2268-14 | 14ビット80Msps/105Msps/125Msps<br>1.8VデュアルADC、超低消費電力  | 203mW/243mW/299mW、SNR:73.1dB、SFDR:88dB、シリアルLVDS出力、<br>6mm×6mm QFN-40パッケージ                 |

| LTC2266-12/LTC2267-12/<br>LTC2268-12 | 12ビット80Msps/105Msps/125Msps<br>1.8VデュアルADC、超低消費電力  | 200mW/238mW/292mW、SNR:70.6dB、SFDR:88dB、シリアルLVDS出力、<br>6mm×6mm QFN-40パッケージ                 |

| <b>RFミキサ/復調器</b>                     |                                                    |                                                                                           |

| LTC5517                              | 40MHz～900MHz<br>ダイレクトコンバージョン直交復調器                  | 高いIIP3:800MHzで21dBm、LO直交ジェネレータ内蔵                                                          |

| LTC5527                              | 400MHz～3.7GHz高直線性<br>ダウンコンバーティング・ミキサ               | IIP3:900MHzで24.5dBm、1900MHzで23.5dBm、NF = 12.5dB、<br>50ΩシングルエンドのRFポートとLOポート、5V電源           |

| LTC5557                              | 400MHz～3.8GHz高直線性<br>ダウンコンバーティング・ミキサ               | IIP3:1950MHzで24.7dBm、2.6GHzで23.7dBm、NF = 13.2dB、<br>3.3V電源動作、トランス内蔵                       |

| LTC5575                              | 800MHz～2.7GHz<br>ダイレクトコンバージョン直交復調器                 | 高いIIP3:900MHzで28dBm、LO直交ジェネレータ内蔵、<br>RFとLOの入力にトランス内蔵                                      |

| <b>アンプ、フィルタ</b>                      |                                                    |                                                                                           |

| LTC6412                              | 800MHz、31dBレンジ、<br>アナログ制御VGA                       | 連続調整可能な利得制御、240MHzでのOIP3:35dBm、<br>ノイズフィギュア:10dB、4mm×4mm QFN-24パッケージ                      |

| LTC6420-20                           | 300MHzのIF周波数向けデュアル<br>低ノイズ、低歪み、差動ADCドライバ           | 10V/Vの固定利得、総入力換算ノイズ:2.2nV/√Hz、消費電流:1アンプ当たり<br>80mA、100MHzでのOIP3:46dBm、3mm×4mm QFN-20パッケージ |

| LTC6421-20                           | 140MHzの1F周波数向けデュアル<br>低ノイズ、低歪み、差動ADCドライバ           | 10V/Vの固定利得、総入力換算ノイズ:2.2nV/√Hz、消費電流:1アンプ当たり<br>40mA、100MHzでのOIP3:42dBm、3mm×4mm QFN-20パッケージ |

| LTC6605-7/ LTC6605-10/<br>LTC6605-14 | 整合されたデュアル7MHz/10MHz/14MHz<br>フィルタおよびADCドライバ        | 差動ドライバ付きの整合されたデュアル2次ローパス・フィルタ、<br>利得をピンで設定可能、6mm×3mm DFN-22パッケージ                          |

| <b>シグナルチェーン・レシーバ</b>                 |                                                    |                                                                                           |

| LTM9002                              | 14ビット、デュアルチャネルIF/<br>ベースバンド・レシーバ・サブシステム            | 高速ADC、パッシブ・フィルタ、固定利得差動アンプを内蔵                                                              |

21721014fb