## 特長

- 高効率で低ノイズのトポロジー

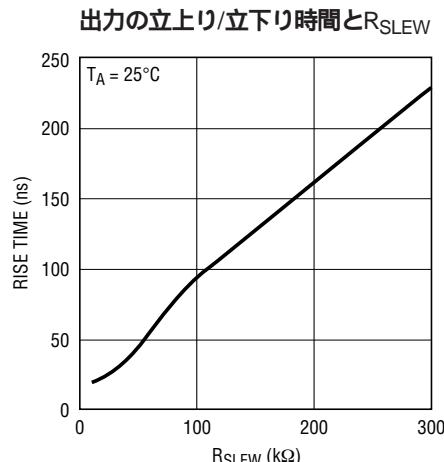

- 調整可能な出力スルーレートによるEMIの低減

- 双方向電流制御用全波ブリッジ・コントローラ

- 調整可能なパルス毎の双方向TEC電流制限

- サーミスタの開放/短絡の表示

- TEC電圧クランプ

- TEC電流、電圧、加熱/冷却状態出力

- 低電流シャットダウン: $I_Q = 10\mu A$

- 調節/同期可能な発振器周波数によるフィルタ部品のサイズとシステム・ノイズの低減

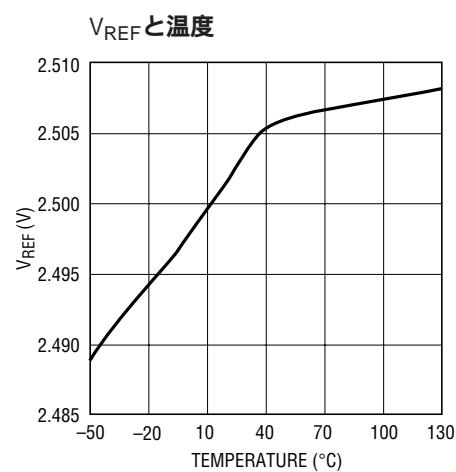

- 2.5Vリファレンス電圧出力

## アプリケーション

- レーザー・ベースの光ファイバ・リンク

- 医療機器

- CPU温度レギュレータ

、LTC、LTはリニアテクノロジー社の登録商標です。

## 概要

LTC®1923は、片方向または双方向ドライブ回路を必要とする熱電冷却器(TEC)または加熱器のアプリケーション用に設計されたPWMコントローラです。LTC1923には、全波ブリッジをドライブするために必要なすべての制御回路と2組のコンプリメンタリ出力ドライバが内蔵されており、TECに双方向電流を効率的に流します。数個の外付け部品を追加するだけで、レーザー・ダイオード・システムの温度を安定化する高精度な温度制御ループを簡単に構成できます。LTC1923を使用することにより、0.1°の標準的な温度設定点精度が達成できます。さらに、計装アンプを前段に追加すると、設定点の安定度を0.01°に近づけることができます。

LTC1923は、加熱と冷却に対して別個に調整可能なパルス毎の電流制限、起動制御用の電流ソフトスタート、システム・ノイズを低減する出力スルーレート制御、差動電流検出と電圧アンプ、さらにレーザーを保護し、冗長システムをモニタする補助回路のホストを備えています。LTC1923は28ピン細型SSOPパッケージで供給されます。

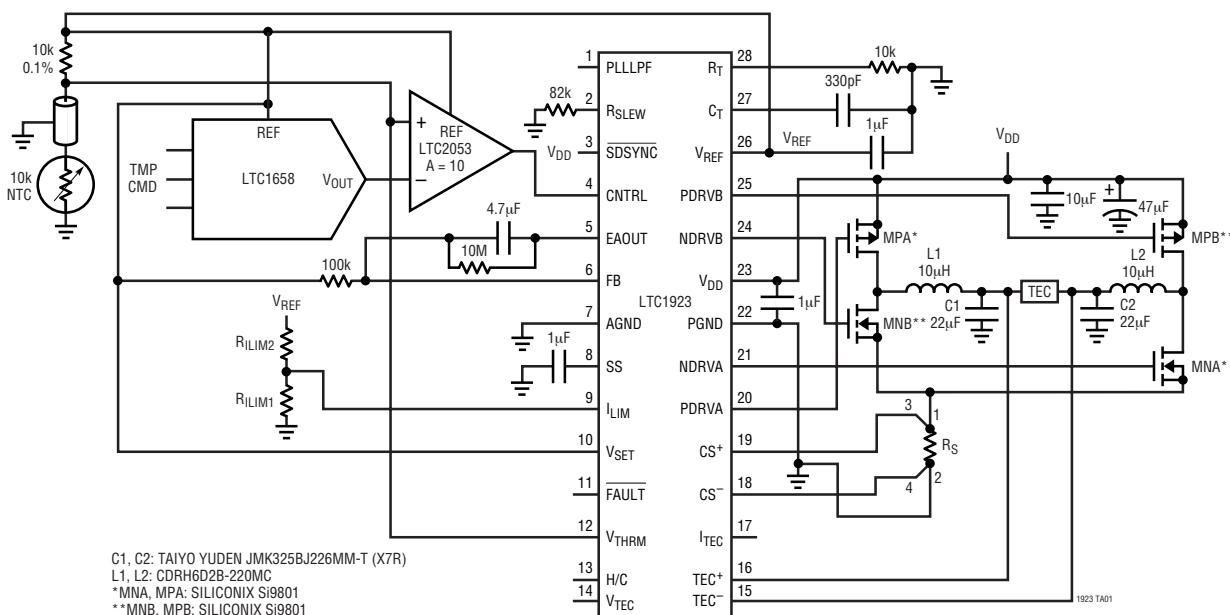

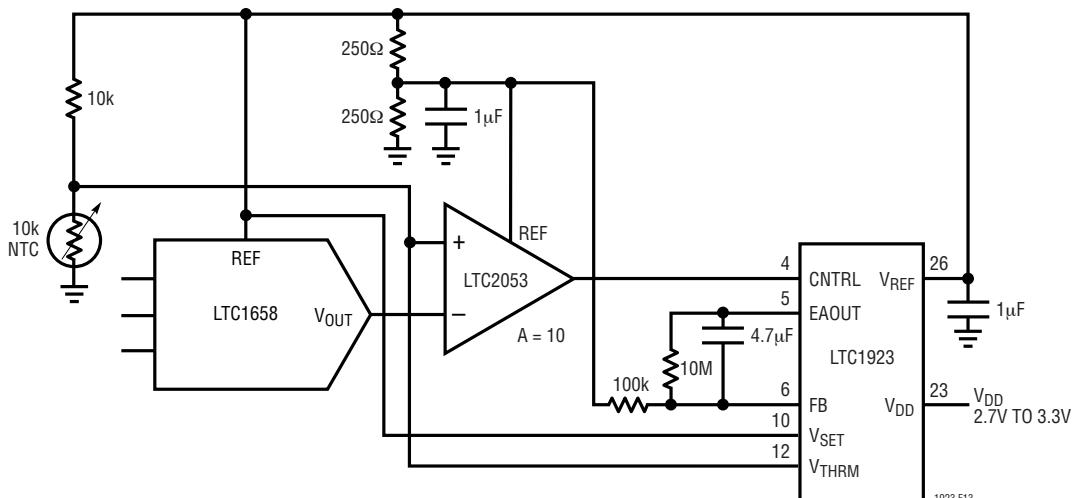

## 標準的応用例

0.01°に近づく設定点安定性を達成するレーザー温度制御ループ

## 絶対最大定格

(Note 1)

|                                |             |

|--------------------------------|-------------|

| $V_{DD} \sim GND$              | - 0.3V ~ 6V |

| $R_{SLEW}$                     | - 0.3V ~ 6V |

| $FB, CNTRL, V_{THRM}, I_{LIM}$ | - 0.3V ~ 6V |

| $CS^+, CS^-, TEC^+, TEC^-$     | - 0.3V ~ 6V |

| $FAULT, H/C$                   | - 0.3V ~ 6V |

| 動作温度範囲 (Note 2)                | - 40 ~ 85   |

| 保存温度範囲                         | - 65 ~ 125  |

| リード温度 (半田付け、10秒)               | 300         |

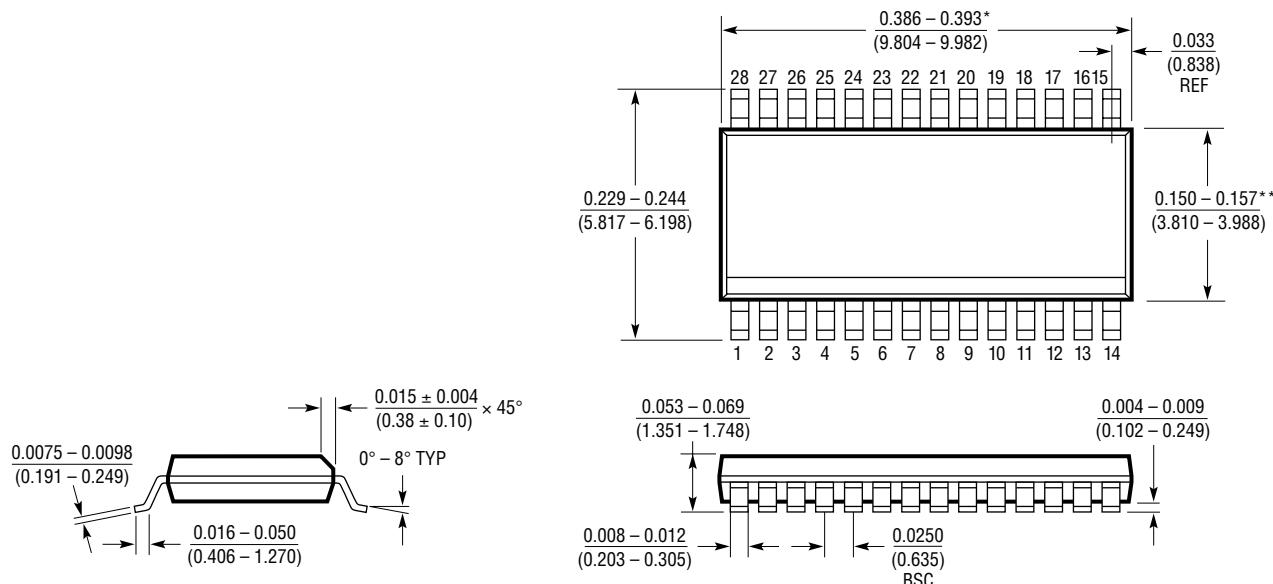

## パッケージ/発注情報

| TOP VIEW |  | ORDER PART NUMBER |

|----------|--|-------------------|

|          |  | LTC1923EGN        |

GN PACKAGE

28-LEAD PLASTIC SSOP

$T_{JMAX} = 125^\circ\text{C}$ ,  $\theta_{JA} = 120^\circ\text{C/W}$

より広い動作温度範囲で規定されるデバイスについては、弊社へお問い合わせください。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

注記がない限り、 $V_{DD} = 5\text{V}$ 、 $R_{SLEW} = V_{DD}$ 、 $SDSYNC = V_{DD}$ 、 $R_T = 10\text{k}\Omega$ 、 $C_T = 330\text{pF}$ 。

| SYMBOL              | PARAMETER                | CONDITIONS                            | MIN | TYP | MAX | UNITS         |   |

|---------------------|--------------------------|---------------------------------------|-----|-----|-----|---------------|---|

| <b>Input Supply</b> |                          |                                       |     |     |     |               |   |

| UVLO                | Undervoltage Lockout     | Low to High Threshold                 | ●   | 2.6 | 2.7 | V             |   |

| UVHYST              | Hysteresis               | High to Low                           | ●   | 50  | 130 | mV            |   |

| $I_{DD}$            | Operating Supply Current | No Output Load, Outputs Not Switching |     | 2   | 4   | mA            |   |

| $I_{DDSHDN}$        | Shutdown $I_{DD}$        | $SDSYNC = 0\text{V}$                  |     | 10  | 25  | $\mu\text{A}$ |   |

| SHDNTH              | Shutdown Threshold       | Measured at PDRV A, PDRV B            |     | 0.3 | 0.8 | 1.4           | V |

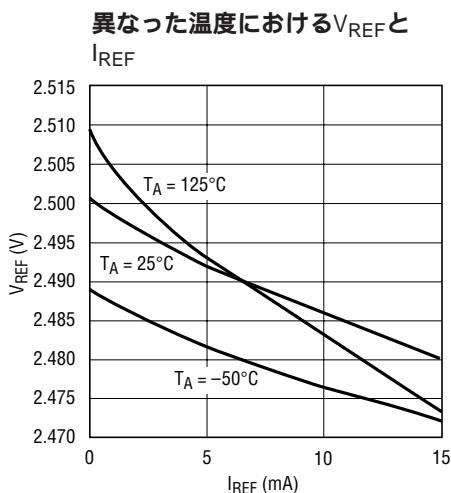

### Reference

|              |                          |                                              |   |       |      |       |    |

|--------------|--------------------------|----------------------------------------------|---|-------|------|-------|----|

| $V_{REF}$    | Reference Output Voltage | No Load                                      | ● | 2.462 | 2.5  | 2.538 | V  |

|              |                          |                                              |   | 2.450 |      | 2.550 | V  |

| $V_{REFGD}$  | $V_{REF}$ Good Threshold | $V_{REF}$ Rising Threshold                   | ● | 2.25  | 2.45 |       | V  |

| LDREG        | Load Regulation          | $ I_{LOAD}  = -1\text{mA}$ to $-10\text{mA}$ |   | 10    | 25   |       | mV |

| LINEREG      | Line Regulation          | $V_{DD} = 2.7\text{V}$ to $5.5\text{V}$      |   | 5     | 20   |       | mV |

| $V_{REFISC}$ | Short-Circuit Current    | $V_{REF} = 0\text{V}$                        |   | 10    | 20   |       | mA |

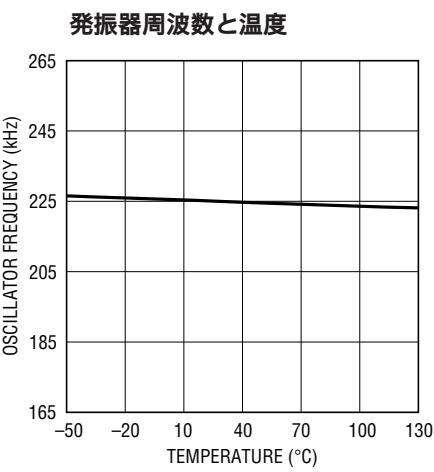

### Oscillator and Phase-Locked Loop

|            |                              |                                                 |   |     |      |     |               |

|------------|------------------------------|-------------------------------------------------|---|-----|------|-----|---------------|

| $f_{OSCI}$ | Initial Oscillator Frequency | $R_T = 10\text{k}\Omega$ , $C_T = 330\text{pF}$ |   | 190 | 225  | 260 | kHz           |

| $f_{osc}$  | Frequency Variation          | $V_{DD} = 2.7\text{V}$ to $5\text{V}$           | ● | 165 | 225  | 270 | kHz           |

| OSCPK      | $C_T$ Ramp Peak              |                                                 |   | 1.4 | 1.5  | 1.6 | V             |

| OSCVLY     | $C_T$ Ramp Valley            |                                                 |   | 0.4 | 0.5  | 0.6 | V             |

| $C_{TICH}$ | $C_T$ Charge Current         | $C_T = 0.3\text{V}$ , $R_T = 10\text{k}\Omega$  |   |     | -150 |     | $\mu\text{A}$ |

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

注記がない限り、 $V_{DD} = 5\text{V}$ 、 $R_{SLEW} = V_{DD}$ 、 $SDSYNC = V_{DD}$ 、 $R_T = 10\text{k}\Omega$ 、 $C_T = 330\text{pF}$ 。

| SYMBOL      | PARAMETER                                            | CONDITIONS                                     | MIN            | TYP            | MAX  | UNITS         |

|-------------|------------------------------------------------------|------------------------------------------------|----------------|----------------|------|---------------|

| $C_{TIDIS}$ | $C_T$ Discharge Current                              | $C_T = 1.8\text{V}$ , $R_T = 10\text{k}\Omega$ |                | 150            |      | $\mu\text{A}$ |

| PLLGAIN     | Gain from PLLPF to $R_T$                             |                                                | -1.1           | -0.9           | -0.7 | V/V           |

| $I_{PLLPF}$ | Phase Detector Output Current<br>Sinking<br>Sourcing | $f_{SYNC} < f_{OSC}$<br>$f_{SYNC} > f_{OSC}$   |                | 12             | -12  | $\mu\text{A}$ |

| MSTTH       | Master Threshold On PLLPF Pin                        | Measured at $SDSYNC$ Pin                       | $V_{DD} - 0.7$ | $V_{DD} - 0.4$ |      | V             |

| SDDLY       | Shutdown Delay to Output                             |                                                | 20             | 45             |      | $\mu\text{s}$ |

### Error Amplifier

|              |                                  |                                                                  |  |      |                |     |

|--------------|----------------------------------|------------------------------------------------------------------|--|------|----------------|-----|

| $V_{OS}$     | Input Offset Voltage             | $EAOUT = 1\text{V}$ , $V_{CM} = 2.5\text{V}$                     |  | -18  | 18             | mV  |

| AOL          | Open-Loop Gain                   | $EAOUT = 0.45\text{V}$ to $1.55\text{V}$ , $CNTRL = 2.5\text{V}$ |  | 80   |                | dB  |

| $V_{CM}$     | Common Mode Input Range          | $EAOUT = 1\text{V}$                                              |  | 0.2  | $V_{DD} + 0.2$ | V   |

| $I_{IB}$     | FB and CNTRL Input Bias Currents | $FB = CNTRL = 1.25$                                              |  | -100 | 100            | nA  |

| $V_{OH}$     | Output High                      | $I_{LOAD} = -100\mu\text{A}$                                     |  | 1.65 |                | V   |

| $V_{OL}$     | Output Low                       | $I_{LOAD} = 100\mu\text{A}$                                      |  | 0.3  | 0.45           | V   |

| $I_{SOURCE}$ | Sourcing Current                 | $EAOUT = 1\text{V}$ , $FB = 1\text{V}$ , $CNTRL = 2\text{V}$     |  | -1.5 | -0.5           | mA  |

| $I_{SINK}$   | Sinking Current                  | $EAOUT = 1\text{V}$ , $FB = 1\text{V}$ , $CNTRL = 0\text{V}$     |  | 1    | 2              | mA  |

| GBW          | Gain-Bandwidth Product           | $f = 100\text{kHz}$ (Note 3)                                     |  |      | 2              | MHz |

### Current Sense Amplifier

|              |                                    |                                                       |   |                |                |      |               |

|--------------|------------------------------------|-------------------------------------------------------|---|----------------|----------------|------|---------------|

| ACS          | Amplifier Gain                     |                                                       |   | 10             |                | V/V  |               |

| CSOFF        | Amplifier Offset                   |                                                       |   | -15            | -2             | 10   | mV            |

| $I_{TECH}$   | Output High Voltage                | $I_{LOAD} = -50\mu\text{A}$                           |   | $V_{DD} - 0.2$ | $V_{DD} - 0.1$ |      | V             |

| $I_{TECL}$   | Output Low Voltage                 | $I_{LOAD} = 50\mu\text{A}$                            |   | 0.1            | 0.2            |      | V             |

| f3dB         | -3dB Frequency                     | (Note 3)                                              |   | 500            |                |      | kHz           |

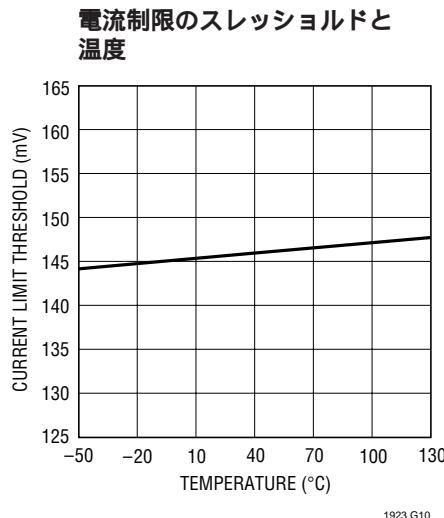

| $I_{LIMTH}$  | Current Limit Threshold            | Measured at $CS^+$ , $CS^-$                           | ● | 125            | 145            | 165  | mV            |

| $I_{LIMDLY}$ | Current Limit Delay to Output      |                                                       |   | 300            | 450            |      | ns            |

| $SSI_{CHG}$  | Soft-Start Charge Current          | $SS = 0.75\text{V}$                                   |   | -2.5           | -1.5           | -0.5 | $\mu\text{A}$ |

| $SSI_{LIM}$  | Soft-Start Current Limit Threshold | $SS = 0.5\text{V}$ , Measured at $CS^+$ , $CS^-$      |   | 50             | 70             | 90   | mV            |

| $I_{LIM}$    | $I_{LIM}$ Current Limit Threshold  | $I_{LIM} = 0.5\text{V}$ , Measured at $CS^+$ , $CS^-$ |   | 50             | 70             | 90   | mV            |

### TEC Voltage Amplifier

|            |                       |                                                |  |      |     |      |     |

|------------|-----------------------|------------------------------------------------|--|------|-----|------|-----|

| ATEC       | Amplifier Gain        |                                                |  | 0.98 | 1   | 1.02 | V/V |

| TECOFF     | Amplifier Offset      | Measured at $V_{TEC}$ , $V_{CM} = 2.5\text{V}$ |  |      | -7  |      | mV  |

| TECCMR     | Common Mode Rejection | $0.1\text{V} < V_{CM} < 4.9\text{V}$           |  |      | 60  |      | dB  |

| $V_{TECH}$ | Output High Voltage   | $I_{LOAD} = -50\mu\text{A}$                    |  | 4.7  | 4.9 |      | V   |

| $V_{TECL}$ | Output Low Voltage    | $I_{LOAD} = 50\mu\text{A}$                     |  | 0.1  | 0.3 |      | V   |

| f3dB       | -3dB Frequency        | (Note 3)                                       |  |      | 1   |      | MHz |

### Output Drivers

|             |                     |                                                          |  |   |     |     |    |

|-------------|---------------------|----------------------------------------------------------|--|---|-----|-----|----|

| OUTH        | Output High Voltage | $I_{OUT} = -100\text{mA}$                                |  | 4 | 4.5 |     | V  |

| OUTL        | Output Low Voltage  | $I_{OUT} = 100\text{mA}$                                 |  |   | 0.7 | 1.2 | V  |

| $t_{RISE}$  | Output Rise Time    | $C_{LOAD} = 1\text{nF}$                                  |  |   | 20  |     | ns |

| $t_{FALL}$  | Output Fall Time    | $C_{LOAD} = 1\text{nF}$                                  |  |   | 20  |     | ns |

| $t_{rSLEW}$ | Output Rise Time    | $C_{LOAD} = 1\text{nF}$ , $R_{SLEW} = 10\text{k}\Omega$  |  |   | 20  |     | ns |

| $t_{fSLEW}$ | Output Fall Time    | $C_{LOAD} = 1\text{nF}$ , $R_{SLEW} = 10\text{k}\Omega$  |  |   | 20  |     | ns |

| $t_{rSLEW}$ | Output Rise Time    | $C_{LOAD} = 1\text{nF}$ , $R_{SLEW} = 100\text{k}\Omega$ |  |   | 90  |     | ns |

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

注記がない限り、 $V_{DD} = 5\text{V}$ 、 $R_{SLEW} = V_{DD}$ 、 $\overline{\text{SDSYNC}} = 5\text{V}$ 、 $R_T = 10\text{k}\Omega$ 、 $C_T = 330\text{pF}$ 。

| SYMBOL     | PARAMETER                    | CONDITIONS                                               | MIN | TYP  | MAX | UNITS |

|------------|------------------------------|----------------------------------------------------------|-----|------|-----|-------|

| $t_{SLEW}$ | Output Slew Fall Time        | $C_{LOAD} = 1\text{nF}$ , $R_{SLEW} = 100\text{k}\Omega$ |     | 90   |     | ns    |

| SLEWVT     | $R_{SLEW}$ Disable Threshold |                                                          |     | 2.75 |     | V     |

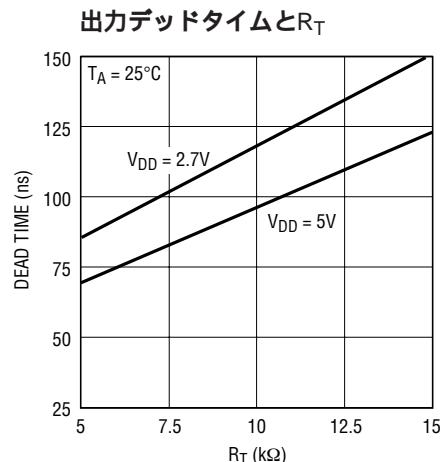

| DLY        | Output Dead Time             | $R_T = 10\text{k}\Omega$                                 |     | 90   |     | ns    |

### Fault

|        |                              |                                                            |  |       |     |    |

|--------|------------------------------|------------------------------------------------------------|--|-------|-----|----|

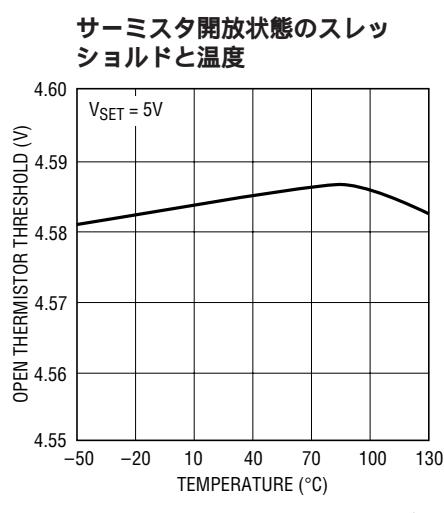

| OPENTH | Open Thermistor Threshold    | $V_{SET} = 5\text{V}$ , Measured with Respect to $V_{SET}$ |  | -350  |     | mV |

| SHRTTH | Shorted Thermistor Threshold | $V_{SET} = 5\text{V}$ , Measured with Respect to GND       |  | 0.975 |     | V  |

| FLTV   | Fault Output Low Voltage     | 1mA Into $\overline{\text{FAULT}}$ , During Fault          |  | 150   | 300 | mV |

### Direction Comparator

|      |                        |                                                                                          |  |     |     |    |

|------|------------------------|------------------------------------------------------------------------------------------|--|-----|-----|----|

| DIRH | Low-to-High Threshold  | $TEC^- = 2.5\text{V}$ , Measured with Respect to $TEC^-$<br>Sensed When H/C Toggles Low  |  | 50  |     | mV |

| DIRL | High-to-Low Threshold  | $TEC^- = 2.5\text{V}$ , Measured with Respect to $TEC^-$<br>Sensed When H/C Toggles High |  | -50 |     | mV |

| HCV  | H/C Output Low Voltage | 1mA Into Pin, $TEC^+ = 2.7\text{V}$ , $TEC^- = 2.5\text{V}$                              |  | 150 | 300 | mV |

Note 1:絶対最大定格はそれを超えるとデバイスの寿命に影響を及ぼす値。

Note 2:LTC1923Eは、0 ~ 70 °C の温度範囲で仕様に適合することが保証されている。-40 ~ 85 °C の動作温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。

Note 3:設計によって保証されているが、製造時にはテストされない。

## 標準的性能特性

## 標準的性能特性

## 標準的性能特性

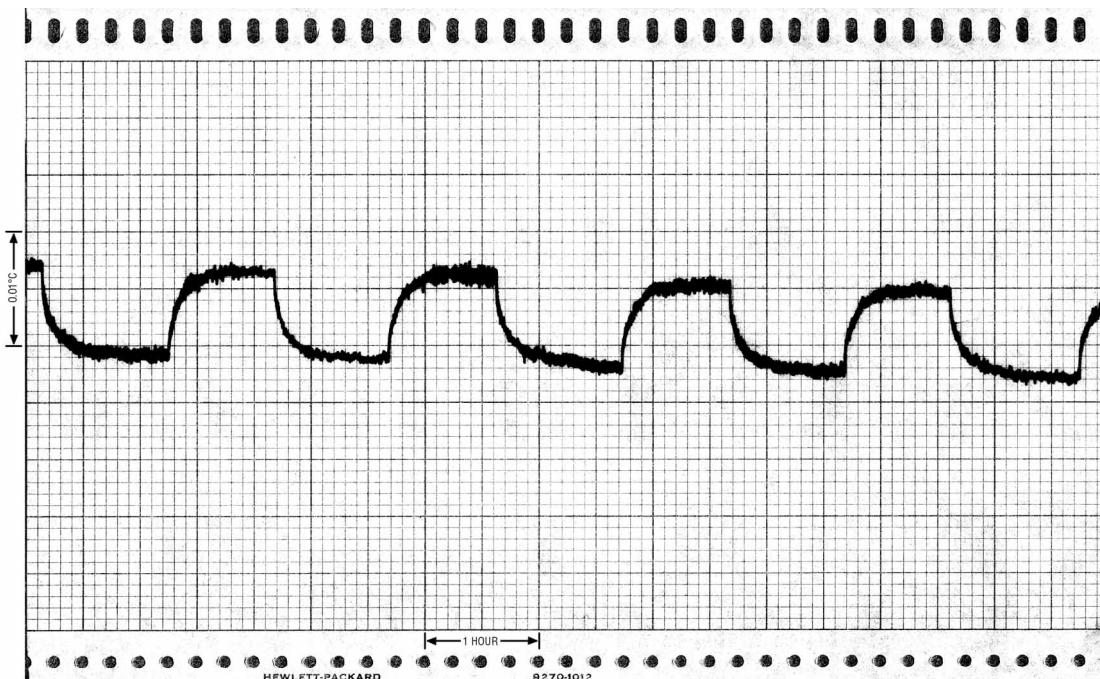

1時間ごとに周囲温度を20度超えるステップの生じる環境で測定した長期冷却モード安定性。その結果、データは0.008 のピーク・ツー・ピークの変化を示し、2500の熱利得を示している。プロット区間ににおけるベースラインの0.0025 の傾きは周囲温度の変化からきている。

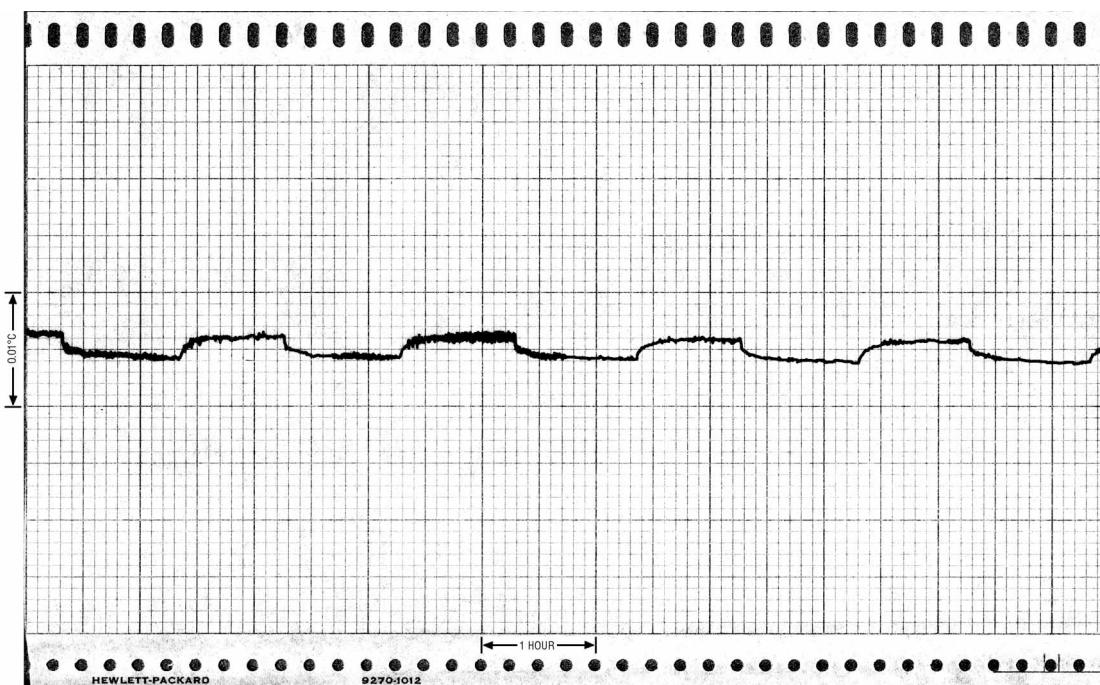

加熱モードであること以外は、上と同一のテスト条件。TECの高い加熱モード効率により、熱利得が高くなる。ピーク・ツー・ピークの変化は0.002 で、安定性が4倍改善された。かろうじて検出できるベースラインの傾きも、上と比べて同様に4倍の改善を示している。

## ピン機能

**PLLLPF (ピン1) :** このピンは、デバイスの同期時にフェーズロック・ループのローバス・フィルタとして機能します。このピンの平均電圧は、発振器の充電電流と放電電流の両方に等しく反映され、それによって動作周波数が変化します。このピンの電圧を $V_{DD} - 0.4V$ より高くすると、デバイスは同期マスタに指定されます。これによって、同じ基板上の複数のデバイスを同一周波数で動作させることができます。各 $C_T$ 充電サイクル時にSDSYNCピンを“L”に引き下げて同期します。

**R<sub>SLEW</sub> (ピン2) :** このピンとAGND間に抵抗を接続して、出力ドライバ・ピンの電圧スルーレートを設定します。最小抵抗値は10kで、最大値は300kです。このピンを $V_{DD}$ に接続するとスルーレートの制限を無効にすることができます、出力が最大速度で遷移します。

**SDSYNC (ピン3) :** このピンを使って、ICを無効にしたり、内部発振器の同期をとったり、あるいは他のデバイスの同期をとるマスタにすることができます。このピンをグランドに接続すると、全内部回路を無効にし、NDRVVAとNDRVVBを“L”にし、PDRVVAとPDRVVBを $V_{DD}$ にします。EAOUTは“L”になります。FAULTも“L”になり、故障状態を示します。このピンは、シャットダウン回路をトリガすることなしに、20μsまで“L”に引き下げておくことができます。デバイスは外部クロックのスレーブにもなれるし、マスタとしても使えます(詳細については、「アプリケーション情報」を参照)。

**CNTRL (ピン4) :** 誤差アンプの非反転入力。

**EAOUT (ピン5) :** 誤差アンプの出力。ループ補償ネットワークは、このピンとFB間に接続します。このピンの電圧はPWMコンパレータへの入力で、デューティ・サイクルを0%~100%のどこかに設定して温度検出素子の温度を制御します。

**FB (ピン6) :** 誤差アンプの反転入力。この入力は、補償帰還ネットワークを介してEAOUTに接続します。

**AGND (ピン7) :** 信号グランド。すべての電圧はAGNDを基準にして測定されます。低ESRコンデンサを使って、 $V_{DD}$ と $V_{REF}$ をこのピンの近くのグランド・プレーンにバイパスします。

**SS (ピン8) :** このピンからグランドにコンデンサを追加して、TEC電流をソフトスタートすることができます。このコンデンサは1.5μAの電流源から充電されます。このピンは電流制限コンパレータの反転入力の1つに接続されているので、TEC電流はゼロから直線的に増加することができます。このピンの電圧が1.5Vより高くないと、サーミスタの開放/短絡ウィンドウ・コンパレータは故障信号を出せません。

**I<sub>LIM</sub> (ピン9) :**  $V_{REF}$ からこのピンに接続した電圧分割器により、TECの電流制限スレッショルドが設定されます。このピンの電圧を1Vより高く設定すると、 $I_{LIM} = 150mV/R_S$ となり、内部電流制限コンパレータのレベルとなります。このピンの電圧を1Vより低く設定すると、コンパレータがトリップする電流制限値は次のようになります。

$$I_{LIM} = [0.15 \cdot R_{ILIM1} \cdot V_{REF}] / [(R_{ILIM1} + R_{ILIM2}) \cdot R_S]$$

**V<sub>SET</sub> (ピン10) :** これは、温度検出素子の分割器ネットワーク(プリッジ)の設定点リファレンスの入力です。このピンはサーミスタ分割器ネットワークのバイアス源に接続する必要があります。

**FAULT (ピン11) :**  $V_{THRM}$ の電圧が指定されたウィンドウを外れた状態、デバイスのシャットダウン、低電圧ロックアウト(UVLO) またはリファレンス不良が発生すると、“L”に下がってそれらの発生を知らせるオープン・ドレイン出力。 $V_{THRM}$ の電圧が指定されたウィンドウから外れると、サーミスタのインピーダンスが許容範囲から外れていることを意味します。この信号を使って、マイクロコントローラによるシステムのシャットダウンまたはプリッジへの電源接続の遮断のためのフラグを出すことができます。この信号を使った冗長保護については、「アプリケーション情報」を参照してください。

**V<sub>THRM</sub> (ピン12) :** サーミスタ両端の電圧。このピンの電圧が( $V_{SET} - 350mV$ )~(0.2· $V_{SET}$ )の範囲から外れると、FAULTピンが“L”になり(ラッチされて) サーミスタの温度が許容範囲の外に出てしまったことを知らせます。

**H/C (ピン13) :** このオープン・ドレイン出力はTEC電流の方向を知らせます。TEC<sup>+</sup>がTEC<sup>-</sup>より大きいと(これは通常システムの冷却に対応します)、この出力は“L”になります。反対の場合、このピンは“H”になります。

## ピン機能

$V_{TEC}$  (ピン14) : TECの両端の電圧の大きさに等しい、差動TEC電圧アンプの出力。

$TEC^-$  (ピン15) : 差動TEC電圧アンプの反転入力。このアンプの利得は1に固定されており、その出力はAGNDを基準にしたTEC両端の電圧です。この入力は $TEC^+$ とともに、TECがレーザーの加熱と冷却のどちらを行っているかをH/Cピンによって表します。

$TEC^+$  (ピン16) : 差動TEC電圧アンプの非反転入力。

$I_{TEC}$  (ピン17) : 差動電流検出アンプの出力。このピンの電圧は約 $10 \cdot I_{TEC} \cdot R_S$ です。ここで、 $I_{TEC}$ は熱電冷却器の電流で、 $R_S$ はこの電流の検出に使われる検出抵抗です。この電圧は電流の大きさだけを表し、電流の方向に関する情報は与えません。このピンの電圧が、SSの電圧の1.5倍、 $I_{LIM}$ の電圧の1.5倍、または1.5Vの中の一番低い値を超すと、電流制限が機能します。この状態になると、(現在導通している)出力対は即座にターンオフします。 $C_T$ ピンが次の対応するピークまたは谷に達すると、電流制限は解除されます(「電流制限」の項を参照)。

$CS^-$  (ピン18) : 差動電流検出アンプの反転入力。

$CS^+$  (ピン19) : 差動電流検出アンプの非反転入力。このアンプの利得は10に固定されています。

PDRVVA、PDRVVB (ピン20、25) : これらのプッシュ-パル出力は、全波ブリッジ構成の相対する上側PMOSスイッチをドライブするように配置されています。

NDRVVA、NDRVVB (ピン21、24) : これらのプッシュ-パル出力は、全波ブリッジ構成の相対する下側スイッチをドライブするように配置されています。

PGND (ピン22) : これはICの高電流グランドです。外部の電流検出抵抗は、このポイントを基準にします。

$V_{DD}$  (ピン23) : ICの正電源レール。10μFよりも大きな低ESL、低ESRのセラミック・コンデンサを使って、このピンをPGNDとAGNDにバイパスします。 $V_{DD}$ のターンオン電圧レベルは2.6Vで、130mVのヒステリシスがあります。

$V_{REF}$  (ピン26) : これはリファレンスの出力です。このピンは、1μFのセラミック・コンデンサを使ってGNDへバイパスします。このリファレンスは最小10mAの電流を供給することができ、内部で短絡電流制限されています。

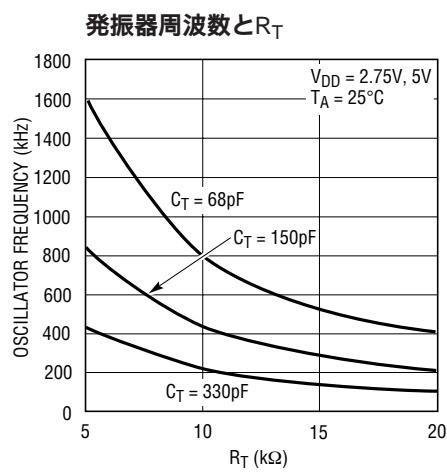

$C_T$  (ピン27) : 発振器の周波数設定には、この三角波発振器タイミング・コンデンサのピンが $R_T$ とともに使われます。周波数の計算式は次のとおりです。

$$f_{OSC} = \frac{0.75}{R_T \cdot C_T} \text{ Hz}$$

$R_T$  (ピン28) :  $R_T$ とAGND間の1個の抵抗により、三角波発振器の充電電流と放電電流が設定されます。このピンにより、一方の出力対のターンオフから他方の出力対のターンオンまでのデッドタイムも設定され、双方の出力が同時に導通することを防ぎます。このピンの電圧は0.5Vに安定化されています。最高の性能を実現するには、 $R_T$ ピンから供給される電流を最大150μAに制限します。10kの $R_T$ を選択することを推奨します。これを使うとデッドタイムは90nsになります。

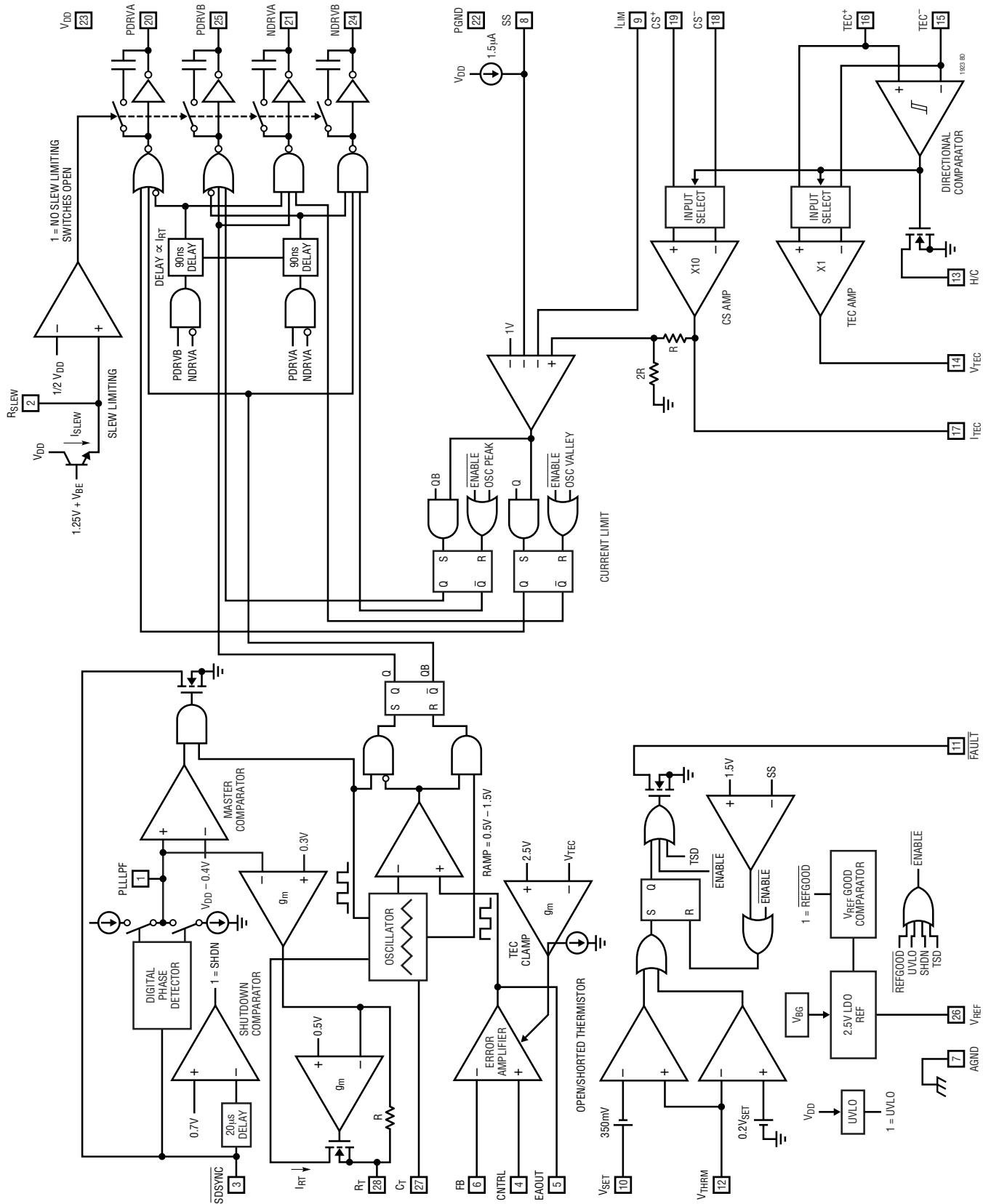

## 機能図

## 動作

### メイン制御ループ

LTC1923は固定周波数の電圧モード・アーキテクチャを使って温度を制御します。(Hブリッジとも呼ばれる)全波ブリッジに構成された2対のNチャネル/Pチャネル外部MOSFETの相対デューティ・サイクルは、システムの温度を制御するために調節されます。全波ブリッジ・アーキテクチャは、熱電冷却器(TEC)または他の加熱素子を通じて双方向電流が流れることを助けます。電流の流れる方向により、システムが加熱されるか、それとも冷却されるかが決まります。通常、サーミスタ、プラチナRTD、または他の適切な素子を使って、システムの温度を検知します。制御ループは、この検出素子とTECの周りで閉じられます。

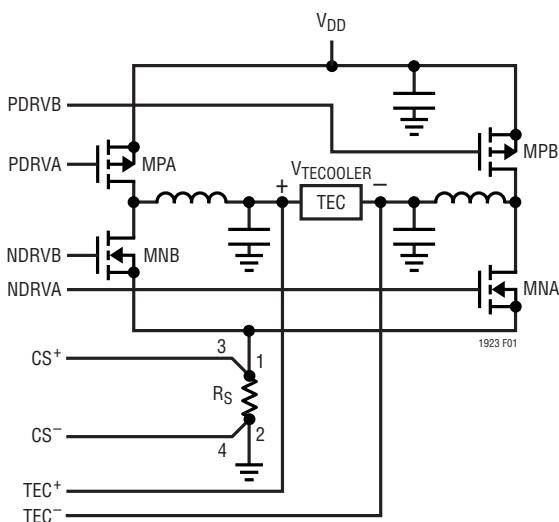

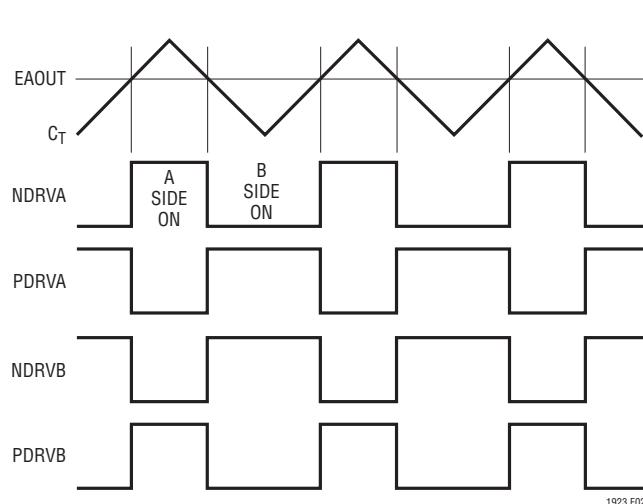

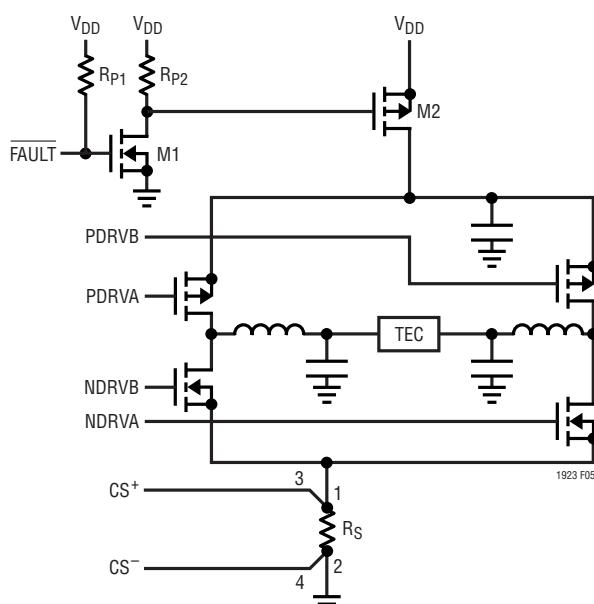

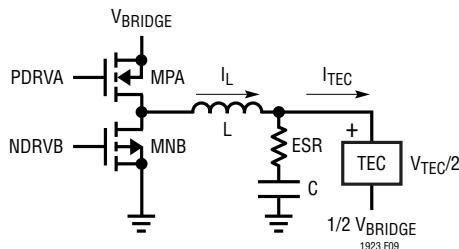

$C_T$ の三角波に関連して、誤差アンプの出力電圧(EAOUT)が、TECが加熱するか、それとも冷却するかを制御します。外部全波ブリッジの回路図を図1に示します。ブリッジの“A”側は、左上のPMOS(MPA)と右下NMOS(MNA)で構成されます。これらのデバイスのゲートはそれぞれ、LTC1923のPDRVVA出力とNDRVVA出力に接続されています。ブリッジの“B”側は、PMOS(MPB)とNMOS(MNB)で構成されます。これらのMOSFETのゲートは、LTC1923のPDRVVB出力とNDRVVB出力によって制御されます。

ブリッジの“A”側は、図2に示されているように、誤差アンプの出力が $C_T$ ピンの電圧より小さいときターンオ

図1. 全波ブリッジの回路図

ンします(NDRVVAが“H”で、PDRVVAが“L”)。この状態では、各出力ドライバの状態は次のとおりです。PDRVVAは“L”、NDRVVAは“H”、PDRVVBは“H”、およびNDRVVBは“L”。EAOUTの電圧が $C_T$ ピンの電圧よりも大きいと、ブリッジの“B”側がターンオンします。TEC両端の平均電圧 $V_{TECOOLER}$ はおよそ次のとおりです。

$$V_{TECOOLER} = V_{TEC^+} - V_{TEC^-} = V_{DD} \cdot (D_A - D_B)$$

ここで、

$$V_{DD} = \text{全波ブリッジ電源電圧}$$

$$V_{TECOOLER} = V_{TEC^+} - V_{TEC^-}$$

$D_A$  = ブリッジの“A”側のデューティ・サイクル、つまり“A”側がオンしている時間を発振器の周期で割ったもの

$D_B$  = ブリッジの“B”側のデューティ・サイクル

デューティ・サイクルの項( $D_A$ と $D_B$ )の関係は次式で表されます。

$$D_A = 1 - D_B$$

定常状態では、 $V_{TECOOLER}$ の極性は、システムが加熱中か、それとも冷却中かを示します。通常、電流が冷却器のTEC<sup>+</sup>側に流れ込む時にシステムは冷却され、電流がこの端子から流れ出る時に加熱されます。NOTE : TECのTEC<sup>+</sup>側と、LTC1923のTEC<sup>+</sup>入力は相互に接続しますが、両者を混同しないでください。

図2. 誤差アンプの出力、 $C_T$ 、ならびに出力ドライバの波形

## 動作

### 保護機能

多くの保護機能がLTC1923に組み込まれており、TECへの過剰なストレスの印加やシステムの熱暴走を防ぎます。これらの機能には、パルス毎の電流制限、TEC電圧のクランプおよびサーミスタの開放/短絡検出が含まれます。

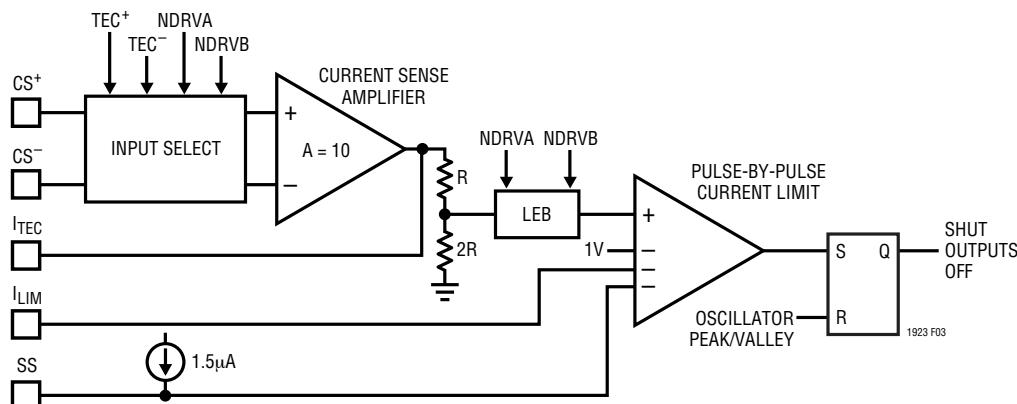

### 電流制限

MNAとMNBのNMOSの共通ソース接続とグランド間に検出抵抗 $R_S$ を接続することにより、全波ブリッジのピーク電流をスイッチング・サイクル毎に制限することができます。図1に示されているように、CS<sup>+</sup>とCS<sup>-</sup>を接続します。電流制限は、固定利得10の差動アンプ、減衰器(抵抗分割器)および電流制限コンパレータで構成されています。回路の詳細を図3に示します。差動アンプの出力 $I_{TEC}$ が与えられているので、ユーザーはブリッジを流れる瞬時電流をモニタすることができます。平均電流が望ましい場合は、外部RCフィルタを使って $I_{TEC}$ 出力をフィルタすることができます。約50nsの先頭エッジ・プランギング機能も内蔵されており、電流検出回路の誤起動を防ぎます。これにより、CS入力ピンのフィルタリング条件が緩和されます。

スイッチング・サイクルの間、 $I_{TEC}$ の電圧が次の3条件のうちの最低値を超すと電流が制限されます。1) SSピンの電圧の1.5倍、2)  $I_{LIM}$ ピンの電圧の1.5倍、または3) 1.5V。電流制限条件が検出されると、4個の外部すべてFETが即座にシャットオフします。これらのデバイスは、電流制限条件が生じたときと同じ状態(充電または放電のどちらか)に $C_T$ が達した後に初めて、再度ターン

オンします。たとえば、 $C_T$ の充電中に電流制限が生じた場合、この充電時間の残りと $C_T$ の全放電時間にわたって出力はオフにされ、 $C_T$ が最低電圧に達して充電を再開した時に初めて、再度有効になります。 $C_T$ の放電中に電流制限が生じた場合、類似の順序で事象が発生します。

SSピンからグランドにコンデンサを接続して、全波ブリッジ電流をソフトスタートする(徐々に増加させる)ことができます。1.5μAの電流がチップから供給され、このコンデンサを充電します。これにより、起動時の突入電流を制限し、TECに供給する電流をゼロから直線的に増加させることができます。

LTC1923には電流制限調節用の専用ピン( $I_{LIM}$ )が備わっています。 $I_{LIM}$ に加わる電圧が1Vより大きい場合、既定の電流制限値 $I_{LIMIT}$ は次のようにになります。

$$I_{LIMIT} = 150\text{mV}/R_S$$

ここで、 $R_S$  = 電流検出抵抗です。

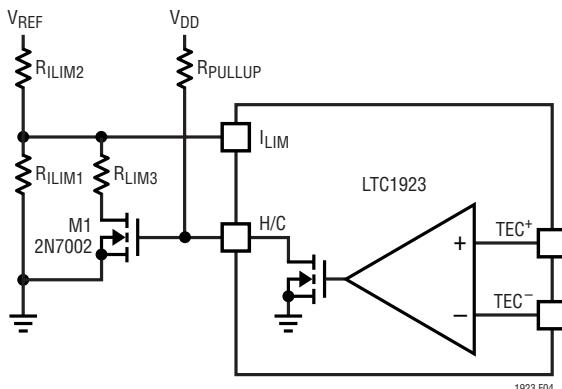

$I_{LIM}$ ピンを利用すると、電流制限スレッショルドの設定と調節が簡単に行えます(電流制限スレッショルドは $R_S$ を変えても調節できます)。もっと重要なことは、トランジスタ1個の追加により、加熱と冷却の電流制限を個別に設定できることです。3個の抵抗と外部NMOS(M1)を使ってこれを実現する方法を図4に示します。多くのアプリケーションでは、高い冷却能力が望まれます。TEC<sup>+</sup>がTEC<sup>-</sup>より大きいとき、H/C出力が“L”になり、システムが冷却中であることを表します(ほとんどのレーザーではこれが普通です)。

図3. 電流検出回路

# LTC1923

## 動作

図4 . 別個に設定された加熱/冷却電流制限

トランジスタM1はオフしており、電流制限スレッショルドは次式で与えられます。

$$I_{LIMIT} = \frac{0.15 \cdot R_{ILIM1} \cdot V_{REF}}{(R_{ILIM1} + R_{ILIM2}) \cdot R_S}$$

TEC<sup>-</sup>がTEC<sup>+</sup>よりも大きいとき、オープン・ドレイン出力H/CはR<sub>PULLUP</sub>を通して“H”に引き上げられ、M1はターンオンします。

電流制限値は次式で与えられ、加熱時の電流制限スレッショルドは減少します。

$$I_{LIMIT} = \frac{0.15 \cdot (R_{ILIM1} \| R_{ILIM3}) \cdot V_{REF}}{(R_{ILIM2} + R_{ILIM1} \| R_{ILIM3}) \cdot R_S}$$

冷却時の制限よりも加熱時の電流制限を大きくする必要があれば、反転回路を追加することができます。

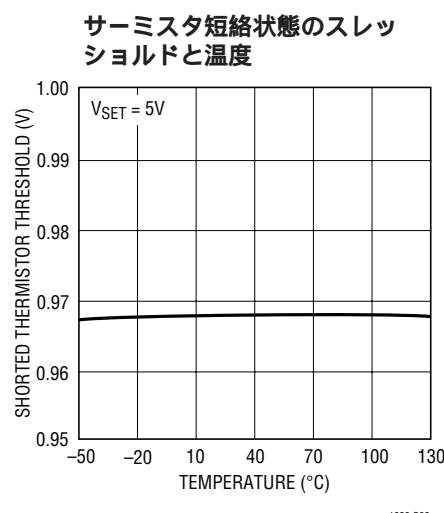

### サーミスタの開放/短絡の検出

システムが温度を制御するには、温度検出素子( NTC サーミスタ、プラチナRTD、その他のコンポーネント )を正しく接続する必要があります。検出素子の接続が正しくないと、システムは温度を制御できず、熱暴走を起こす可能性があります。

TECは本来の性質上、そこを流れる電流に応じて、デバイスの両側で温度差を生じます。発生可能な温度差には上限があり、それはTECの寸法やヒートシンクの方法など、いくつかの物理パラメータに依存します。TEC自体

が電力を消費して温度差を生じさせ、熱を発生しますが、この熱も除去する必要があります。TEC内の電力消費が一定のレベルに達すると、両側とも過熱し始めます。これは、TECが自己発熱を外部に放出できないためで、熱暴走を引き起こす可能性があります。デバイスが熱暴走を起こすと、TECやおそらく温度制御の対象となっているコンポーネントが損傷を受けます。

LTC1923には専用のコンパレータが2個用意されており、サーミスタの電圧を直接モニタします。この電圧が有効なウィンドウから外れると、ラッチが掛かり、FAULTピンが“L”になります。出力ドライバはシャットオフせず、また制御回路もディスエーブルされず、デバイスは温度を制御しようとし続けます。FAULT信号を使って適当な回路をディスエーブルするのはユーザ次第です。これを行うには2つの方法があります。1つの方法は、FAULT信号をシステムのマイクロプロセッサに送り、SDSYNCピンを使ってシステムをシャットダウンさせることです。システム保護の別の方法を図5に示します。2個のプルアップ抵抗( RP1とRP2 )とともに、外部NMOS M1とPMOS M2が追加されています。M1とRP2はFAULT信号を反転し、M2はブリッジに直列に接続されたスイッチとして機能します。

図5 . 冗長故障保護回路

## 動作

フォールト状態ではないとき、M1のゲートは $V_{DD}$ に引き上げられており、M2のゲートを“L”に引き下げるのと、プリッジは前に説明したとおり動作します。不具合が生じてFAULTが“L”になると、M1はシャットオフし、M2のゲートは“H”に引き上げられてM2をシャットオフします。このため、電源パスは開放され、TECには電流が供給されません。M2の $R_{DS(ON)}$ は低くなければなりません（M2による電力損失を抑えるため、 $R_s$ の値以下）。 $R_{P1}$ と $R_{P2}$ にはおよそ100kのものを選択することができます。

下側のコンパレータのスレッショルド・レベルは $V_{SET}$ の20%で、上側のコンパレータのスレッショルド・レベルは $V_{SET}$ より350mV下です。ここで、 $V_{SET}$ は $V_{SET}$ ピンに印加された電圧です。 $V_{SET}$ は通常、サーミスタ分割器のバイアス源に接続されるので、どんな変動も追尾します。

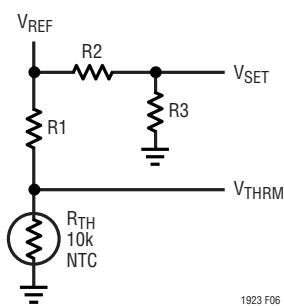

$V_{SET}$ ピンは入力インピーダンスが高いので、分割された電圧をこのピンに供給してサーミスタの許容インピーダンス範囲を修正することができます。これを図6に示します。 $V_{SET}$ ピンに印加する電圧は最低2V必要です。サーミスタのインピーダンスの低い方のスレッショルドは次のようにになります。

$$R_{TH(LOWER)} = \frac{0.2 \cdot R_1 \cdot R_3}{R_2 + 0.8 \cdot R_3}$$

インピーダンスの高い方のスレッショルドは次のようになります。

$$R_{TH(UPPER)} = \frac{R_1(R_3 - \alpha(R_2 + R_3))}{R_2 + \alpha(R_2 + R_3)}$$

ここで、 $\alpha = 0.35/V_{SET}$ 。

$R_1$ を変えると、サーミスタの有効インピーダンス範囲も変わります。

図6. サーミスタの許容範囲の変更

例： $V_{REF} = V_{SET} = 2.5V$

$R_1=10k$ 、 $R_2 = 0$  、  $R_3 = \text{開放}$

$R_{TH}=\text{温度係数が}25\text{ で} -4.4\%/\text{ の} 10k \text{ NTC サーミスタ}.$

フォールトを生じる前のサーミスタの許容インピーダンス範囲は $2.5k \sim 61k$  です。これは約 $-10 \sim 60$  の有効温度範囲に対応します。

デバイスが起動時にFAULT状態にならないように、FAULTはソフトスタートが完了するまではラッチされません。これはSSの電圧が1.5Vに達することに相当します。1μFのソフトスタート・コンデンサの場合、この遅延は約1秒です。これにより、すべての電源( $V_{DD}$ 、設定点リファレンス、および $V_{REF}$ )がそれぞれの最終値に安定するのに十分な時間が与えられます。

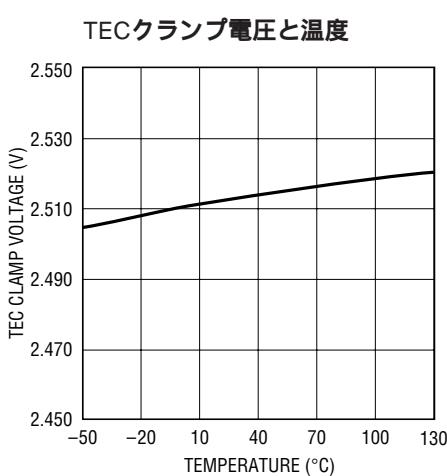

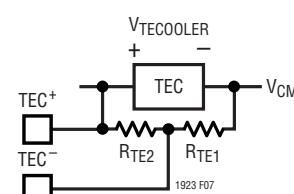

## TEC電圧クランプ

クランプ回路が内蔵されていて、TECを過電圧状態から保護します。TEC両端の電圧差が2.5Vを超えると、PWMコンパレータの入力のところの誤差アンプの出力電圧が制限されます。これにより、出力ドライバのデューティ・サイクルが、つまりTEC両端の電圧がクランプされます。図7に示すようにTECと並列に抵抗分割器を置き、 $TEC^+$ と $TEC^-$ に適切に接続することにより、クランプが生じる電圧を増加させることができます。分割器により、クランプが起動するTEC両端の電圧 $V_{TECOOLER}$ は次の値に増加します。

$$V_{TECOOLER} = \frac{\left(1 + \frac{R_{TE1}}{R_{TE2}} + \frac{R_{TE1}}{100k}\right) \cdot 2.5 - V_{CM} \left(\frac{R_{TE1}}{200k}\right)}{1 + \frac{R_{TE1}}{200k}}$$

固定抵抗値を含む項は、差動アンプの入力インピーダンスによって導入される負荷誤差です。 $R_{TE1}$ と $R_{TE2}$ の追加により、アンプの完全な差動特性が変わるために、同相モード電圧誤差も導入されます。

図7. 電圧クランプ・スレッショルドの増加

## 動作

これらの誤差を抑えるため、 $R_{TE1}$ と $R_{TE2}$ には10k以下のものを選択します。上式は次のようになります。

$$V_{TECOOLER} \approx \left(1 + \frac{R_{TE1}}{R_{TE2}}\right) 2.5$$

クランプ電圧を上げる完全差動方式については、「高電圧アプリケーション」の項で説明します。

これは、同様に加熱と冷却の方向を示すスレッショルドも同じ係数で変え、次の値までスレッショルドを増加させます( $R_{TE1}$ と $R_{TE2}$ は10k以下であると仮定しています)。

$$DIRH = 50mV \left(1 + \frac{R_{TE1}}{R_{TE2}}\right)$$

$$DIRL = -50mV \left(1 + \frac{R_{TE1}}{R_{TE2}}\right)$$

VTECピンの出力電圧 $V_{VTEC}$ は同じ比率で減少します。

$$V_{VTEC} = \frac{V_{TECOOLER}}{1 + \frac{R_{TE1}}{R_{TE2}}}$$

### 発振器周波数

発振器により、スイッチング周波数とすべての高調波の基本位置が決定されます。スイッチング周波数は、与えられたインダクタ・リップル電流に対して選択する必要のあるインダクタのサイズにも影響します(フィルタのインダクタとコンデンサの両方の関数であるTECのリップル電流とは対照的です)。スイッチング周波数が高いと、与えられたリップル電流に対して小さな値のインダクタが使えます。発振器は三角波を出力するように設計されています。コンデンサ $C_T$ の充放電には、外部抵抗 $R_T$ で定まる電流が使われます。充電速度と放電速度は同じです。発振周波数を安定させるには、高品質の部品(5%より優れた多層NPOまたはX7Rのセラミック・コンデンサ)の選択が重要です。

発振周波数は次式で定まります。

$$f_{OSC(kHz)} = 750 \cdot 10^6 / [R_T(k\Omega) \cdot C_T(pF)]$$

LTC1923は1MHzまでの周波数で動作可能です。選択された $R_T$ の値は、全波ブリッジの一方がターンオフして

から他方がターンオンするまでの遅延時間にも影響します。この時間は「ブレイク・ビフォア・メイク」時間としても知られています。標準的な10kでは90nsの「ブレイク・ビフォア・メイク」時間となります。もっと高い周波数のアプリケーションでは、この遅延時間を短くするために、 $R_T$ の値を小さくする必要があるかもしれません。スルーレートが大きく制限されているか、外部ゲート・ドライバ・チップが使われているアプリケーションでは、デッドタイムを増加するために大きな値の $R_T$ が必要なことがあります。「ブレイク・ビフォア・メイク」時間は次式で概算することができます。

$$t_{DELAY} = R_T (k\Omega) \cdot 5.75 \cdot 10^{-9} + 35ns$$

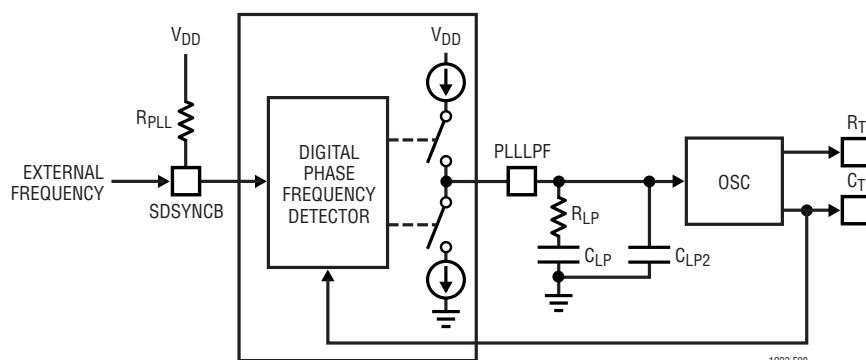

### フェーズロック・ループ

LTC1923には、フェーズロック・ループを構成する電圧制御発振器(VCO)と位相検出器が内蔵されています。このため、SDSYNCピンを使ってマスタへスレーブさせることにより、この発振器を別の発振器に同期させることができます。PLLIPFピンを $V_{DD}$ へ引き上げることにより、このデバイスをマスタとして指定することができます。こうすると、デバイスは設定された発振周波数でSDSYNCピンをトグルします。次に、この信号を使って、他の発振器の同期をとることができます。

別の発振器にスレーブする場合、周波数は目標の周波数より20%~30%低く設定します。周波数のロック範囲は約±50%です。

位相検出器はエッジ検出のデジタル・タイプで、外部発振器と内部発振器の位相のずれはゼロ度となります。この検出器はVCOの中心周波数の高調波に近い入力周波数にはロックしません。VCOのホールドイン範囲はキャプチャ範囲に等しく $dfH = dfC = \pm 0.5f_0$ となります。

位相検出器の出力は、PLLIPFピンに接続された外部フィルタ・ネットワークを充放電するコンプリメンタリ電流ソースの対です。簡略ブロック図を図8に示します。

外部周波数( $f_{PLLIN}$ )が発振器周波数より大きいと、電流はPLLIPFピンから連続的にソースされます。外部周波数が発振器周波数より小さいと、電流はPLLIPFピンにシンクされます。

## アプリケーション情報

ループ・フィルタの部品 $R_{LP}$ 、 $C_{LP}$ および $C_{LP2}$ により、位相検出器からの電流パルスが平滑化され、安定した入力がVCOへ与えられます。これらの部品により、ループがロックする速度も決定されます。ほとんどの場合、ループを安定させるのに、 $C_{LP}$ を省き、 $R_{LP}$ を1kに設定し、 $C_{LP2}$ を $0.01\mu F \sim 0.1\mu F$ の範囲で選択することができます。不要のスイッチング・ノイズがPLLの性能を損なわないように、フィルタ部品の低電位側がAGNDに接続されていることを確認してください。

前に述べたように、1つのLTC1923をマスタとして、他のLTC1923または同期をとる必要のある他のデバイスの

同期をとることができます。これを実現するには、発振器周波数の項で与えられた式を使って $R_T$ と $C_T$ の値を決め、マスタに必要な自走発振器周波数を求めます。図8に示すように、マスタのPLLLPFピンを抵抗 $R_{PLL}$ を介して $V_{DD}$ に接続します。 $R_{PLL}$ は通常、10kに設定することができますが、(250kHzを超す)高い周波数の動作が必要な場合、もっと小さくする必要があるかもしれません。スレーブの自走周波数は、これより20%~30%低く設定します。マスタのSDSYNCピンはその自走周波数(約50%のデューティ・サイクル)でスイッチングし、これを使って他のデバイスの同期をとることができます。

図8. フェーズロック・ループのブロック図

## アプリケーション情報

サーミスタは制御回路から分離されていることがあります。比較的高い入力インピーダンスをもっているので、ノイズを拾いやすくなります。信号線を(同軸ケーブルで)シールドして、この信号にノイズがのらないように最大の注意を払う必要があります。サーミスタとLTC2053の入力の間にローパス・フィルタを追加することができますが、ここは信号経路なので、どれだけ追加できるかには限度があります。

### インダクタのリップル電流

ブリッジを流れる電流は2つの成分に分けられます。TECを流れるDC電流と、コントローラのスイッチ・モードの性質から生じるインダクタのリップル電流です。TEC電流はそれ自身リップル成分をもっていますが、適切なフィルタリングにより、このリップルをイン

ダクタのリップル電流に比べて小さく抑えるので、TEC電流は一定であるという仮定は有効です(「TECのリップル電流」の項を参照)。定常状態のブリッジの簡略化した回路半分を図9に示します。インダクタ(L)を流れる電流 $I_L$ はリップル電流( $I_1$ )と静的TEC電流( $I_{TEC}$ )からなります。リップル電流の大きさ( $I_1$ )は次式を使って計算できます。

$$\Delta I_1 = (V_{BRIDGE}^2 - V_{TEC}^2) / (4 \cdot f_{OSC} \cdot L \cdot V_{BRIDGE})$$

ここで、

$V_{BRIDGE}$ は全波ブリッジ電源電圧(通常は $V_{DD}$ )

$f_{OSC}$ は発振器周波数

$L$ はフィルタのインダクタの値

$V_{TEC}$ はTEC両端のDC電圧降下

## アプリケーション情報

図9. 全波ブリッジの回路半分

ピーク・インダクタ電流は  $I_{TECA} + I_1/2$  に等しく、電流制限コンパレータをトリップする電流レベルです。  $I_{TECA}$  に比べてリップル電流の成分を小さく抑えると、電流制限のトリップ・レベルはTECを流れる電流に等しくなります。

例 :  $V_{BRIDGE} = 5V$ 、  $R_{TEC} = 2.5$  、  $V_{TEC} = 2.5V$ 、  $I_{TECA} = 1A$ ,  $L = 22\mu H$ 、  $f_{OSC} = 250kHz$ 。

上式を使うと、ピーク・ツー・ピーク・リップル電流は以下の値になります。

$$\Delta I_1 = 170mA$$

したがって、1AのDC TEC電流を得るには、ピーク・インダクタ電流は1.085Aとなります。

## TECのリップル電流

TECはすべて、その両端に生じさせることができる最大温度差( 主にTECの物理特性に基づいた )基本的限界があります。この最大温度差を発生させる能力は、デバイスを流れるリップル電流の( DC成分に対比した )大きさによって影響を受けます。TECのリップル電流によるこの性能低下の程度は次式によって概算できます。

$$dT/dT_{MAX} = 1/(1 + N^2)$$

ここで、

$dT$  は調節された達成可能な温度差

$dT_{MAX}$  は厳密にDC電流がTECに供給されたときの最大可能温度差で、通常製造元によって仕様が定められています。

$N$  は、DC電流に対するTECのリップル電流の比

TECの製造元は通常、 $N$ が10%を超えないように指定しています。

このアプリケーションでは、ブリッジの電源電圧、発振器周波数、および外部フィルタ部品により、TECを流れるリップル電流の大きさが決まります。値の大きなフィルタ部品を使うとTECを流れるリップル電流を小さくできますが、代償としてボード面積が増加します。フィルタ・コンデンサのESRは、インダクタのリップル電流とともに、TEC両端のピーク・ツー・ピーク電圧リップルを決め、したがって( TECは抵抗性として現れるので )リップル電流も決めます。

TECを流れるリップル電流  $I_{TEC(RIPPLE)}$  はおよそ次式に等しくなります。

$$I_{TEC(RIPPLE)} \approx \frac{V_{BRIDGE}^2 - V_{TEC}^2}{16 \cdot f_{OSC}^2 \cdot L \cdot C \cdot R_{TEC} \cdot V_{BRIDGE}} + \frac{(V_{BRIDGE}^2 - V_{TEC}^2) \cdot ESR}{2 \cdot f_{OSC} \cdot L \cdot V_{BRIDGE} \cdot R_{TEC}}$$

ここで、

$f_{OSC}$  = 発振器周波数

$L$  = フィルタのインダクタの値

$C$  = フィルタのコンデンサの値

$R_{TEC}$  = TECの抵抗値

$V_{TEC}$  = TEC両端のDC電圧降下

$ESR$  = フィルタのコンデンサの等価直列抵抗

$V_{BRIDGE}$  = 通常は  $V_{DD}$  に等しい全波ブリッジ電源電圧

上式はTECのリップル電流に2つの成分があることを示しています。第1項はフィルタのコンデンサの充電による電圧増加です。第2項はフィルタのコンデンサのESRによるもので、通常支配的要因となります。したがって、選択したコンデンサのESRは低くなければなりません。このコンデンサには、マルチレベル・セラミック、電解OS-CON、その他の適当なコンデンサを使うことができます。両方の項とも動作周波数に反比例するので、発振器周波数の増加によってもTECのリップル電流を小さくできます。

例 :  $V_{BRIDGE} = 5V$ 、  $R_{TEC} = 2.5$  、  $V_{TEC} = 2.5V$ 、  $L = 22\mu H$ 、  $C = 22\mu F$ 、  $f_{OSC} = 250kHz$ 、  $ESR = 100m\Omega$  。

$$I_{TEC(RIPPLE)} = 3.1mA + 13.6mA = 16.7mA$$

## アプリケーション情報

この例では、TECを流れるDC電流は1Aで、リップル電流は約1.7%に相当します( このため、 $I_{TEC}$ をDCとして近似できます)。

帰還ループを閉じる

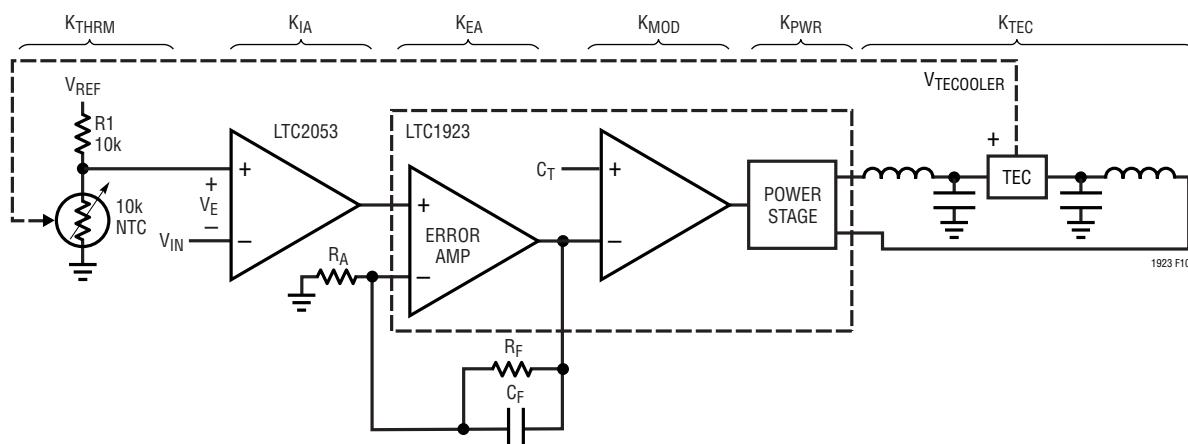

TECおよびサーミスタ(または他の温度検出素子)の周囲で帰還ループを閉じることには、熱システムの極の位置を認識し、制御ループの安定化するために電気的な極(および零点)を配置することが含まれます。システムの温度の厳密な制御には高いDCループ利得が理想的です。残念ながら、必要なループ利得が高ければ高いほど、システムの安定化に必要な補償値も大きくなります。熱システムに関連した時定数は本質的に大きいので(秒のオーダー)部品の値が過度に大きくなる可能性があります。したがって、必要な温度精度を保つのに必要なループ利得を計算してから、いくらかゆとりをもたせて、これをシステムの目標DCループ利得にする必要があります。システムのブロック図を図10に示します。利得ブロックは次のとおりです。

$K_{IA}$  = 計装アンプの利得 (V/V)

$K_{EA}$  = 誤差アンプの利得 (V/V)

$K_{MOD}$  = 変調器の利得 (d/V)

$K_{PWB}$  = 電力段の利得 (V/d)

$K_{TEC} = TEC$ の利得(%)

$K_{TURM}$  = サーミスターの利得 (V/V)

$K_{IA}$ と $K_{EA}$ は計装アンプとLTC1923の誤差アンプに関連した電気的利得です。スイッチング・レギュレータはサンプリング・システムで、電圧をデューティ・サイクル( $d$ )に変換します。このため、 $K_{MOD}$ と $K_{PWR}$ の利得項はデューティ・サイクルと電圧の関数として現されます。TECは電圧を温度変化に変換し、サーミスタのインピーダンス(したがって、その両端の電圧)は温度とともに変化します。

ループの利得は次式で表すことができます。

$$T \text{ (loop gain)} = K_{IA} \cdot K_{EA} \cdot K_{MOD} \cdot K_{PWB} \cdot K_{TEC} \cdot K_{THRM}$$

システムの有限の利得によって生じる誤差 $V_E$ は次式で表すことができます。

$$V_E = V_{IN} / (1 + T)$$

この電圧誤差は温度の設定点誤差に再度変換されます。

例：

$$R_{THRM} = 10k$$

25 で4.4% のNTC

$$R_1 = 10k$$

$$V_{REF} = 2.5V$$

T = 25

温度設定点が25 のこのサーミスタの場合、温度による

サーミスタ電圧の変化は  $-25\text{mV}/^\circ\text{C}$  で与えられます。

0.01 の温度精度を保つには、誤差信号  $V_E$  は  $250\mu\text{V}$  とな

ります。

図10. ループの簡略ブロック図

## アプリケーション情報

最小ループ利得は上式を使って計算することができます。

$$V_E = V_{IN}/(1 + T)$$

25 の設定点温度の場合、 $V_{REF} = 2.5V$ に対して  $V_{IN} = 1.25V$ にする必要があります。必要なループ利得は 5000、つまり 74dB です。

ループ利得を調節する2つの要素( $K_{IA}$ と $K_{EA}$ )があります。他の要素は固定されており、TECとサーミスタの特性( $K_{TEC}$ と $K_{THRM}$ の場合)、 $V_{SET}$ と $R1$ ( $K_{THRM}$ の場合)および $V_{DD}$ ( $K_{MOD}$ と $K_{PWR}$ の場合)に依存します。変調器利得と電力段利得の積は次式で与えられます。

$$K_{MOD} \cdot K_{PWR} = 2 \cdot V_{DD}/V_{CT} = 2 \cdot V_{DD}$$

ここで、 $V_{CT} = 1V$ の固定振幅をもった $C_T$ 電圧。

TECの利得は選択したTECに依存し、デバイス両端の電圧と発生した温度差の関係に相当します。この利得項は、動作温度およびTECが加熱中か冷却中にしたがって変化します。TECは本質的に、冷却時よりも過熱時の方が効率が高くなります(したがって、利得が大きくなります)。最悪時の利得は、与えられた温度変化を強制するのに必要な最大TEC電圧をTECの仕様で参照して概算することができます。

$$K_{TEC} = dT/V_{TEC(MAX)}$$

サーミスタの利得は温度の設定点の近くで直線化します。

例：

$$\text{設定点 } T = 25$$

$$V_{DD} = 5V$$

$$R_{THRM} = 10k \text{ NTC (25 度 } 4.4\%/\text{ )}$$

$$R1 = 10k$$

$$V_{REF} = 2.5V$$

$$dT/V_{TEC(MAX)} = 45 / 1.5V = 30 / V$$

25 周辺の直線化したサーミスタ利得は  $-25mV/V$  です。上で計算した5000の最小ループ利得の場合、計装アンプと誤差アンプの合計利得は次式で計算することができます。

$$K_{IA} \cdot K_{EA} = T/(K_{MOD} \cdot K_{PWR} \cdot K_{TEC} \cdot K_{THRM})$$

$$K_{IA} \cdot K_{EA} = 5000/(10 \cdot 30 \cdot 0.025) = 667$$

十分なマージンをとって、1000の結合利得を選択することができます。計装アンプの利得は通常10に設定します。こうするとどんな誤差も利得係数だけ減衰するからです。したがって、誤差アンプの利得は、図10に示されている利得設定抵抗( $R_F$ と $R_A$ )によって、残りの分に制限されるでしょう。

$$R_F/R_A = K_{EA} - 1$$

TEC/サーミスタのシステムには複数の極が関連するため、補償が難しくなります。この問題を悪くしているのは同じシステムの熱時定数の偏差が大きいことであり、精密な補償方法を確実に実現することを困難にしています。最も確かな(つまり、最も発振しにくい)方法は、支配的な極がシステムの熱時定数( )の十分下(何秒から何分のオーダー)にくるようにすることです。この時定数により、次式にしたがってコンデンサの値が決まります。

$$C_F = \tau/R_F$$

ループ補償の詳細については、「アプリケーションノート89」を参照してください。セラミック・コンデンサはシステムにノイズをもちこむおそれのある圧電効果を示すので、積分コンデンサや信号経路のどこかに使用することはお勧めしません。このデータシートの表紙に示してある部品の値は出発点として使えますが、応答を最適化するには、いくらか調整が必要かもしれません。

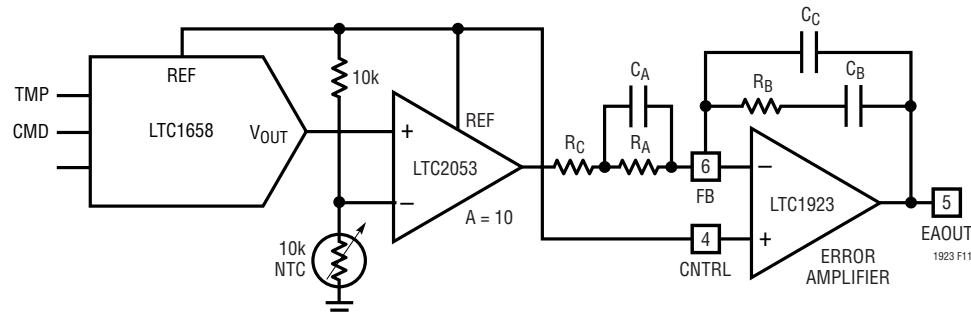

支配的な極の補償には限界があります。それは、広範なレーザー・モジュールのタイプに対して優れたループ応答を実現しますが、温度のステップ変化に対する最速の過渡応答は実現しません。最速の過渡応答が不可欠な場合、図11に示されている複雑な補償方法が必要になるかもしれません。この方法では、帰還ループにゼロを追加して、過渡応答を加速します。まず、LTC1923の誤差アンプがここでは反転構成で動作するので、LTC2053の入力が入れ替わっていることに注意してください。コンデンサ $C_A$ はリード項を与えるのに必要です。抵抗 $R_C$ を使って、容量性負荷に対するバッファをLTC2053に与え、誤差アンプの高周波利得を制限しています。

システムの熱的な極の位置は分らないので、質的補償方法を採用する必要があります。

## アプリケーション情報

図11. 過渡応答を改善する別の補償方法

これには、温度の小信号ステップ変化に対してTECが(本質的に高い利得により)加熱しているときの過渡応答の観察と、補償部品の変更による応答の改善が必要です。妥当な出発点として、このデータシートの表紙から得られる応答に似た応答の得られる部品を選択します。したがって、 $R_A$ 、 $R_B$ および $C_B$ には、それぞれ1M $\Omega$ 、1M $\Omega$ 、および0.47 $\mu$ Fを選びます。 $R_C$ は $R_A$ の1/100のものを選ぶか、およそ10kにします。コンデンサ $C_A$ を導入する前に、ループが安定していることを確認します。 $C_A$ を追加するとループの位相がいくらか上がります(実際、熱システムに付随する極の1つを相殺します)。ほぼ $C_B$ と等しい $C_A$ から始めて、システムの応答に対するその影響を記録します。 $C_B$ を減らしてセトリング時間を改善することを目標に、過渡応答が改善したかどうか観察して値を調節します。システムの熱的な極は「同一」の(つまり、同じ製造元の同じモデルの)レーザー・モジュール相互でも偏差がありうるので、熱に関連したこれらの項に偏差があったとしても、選択した値が必要な応答を実現するように注意する必要があります。ブランドが異なると熱的な項は大きく異なることがあるので、補償は各レーザー・モジュールごとに個別に調節する必要があります。 $C_C$ は高周波利得をロールオフして、出力のノイズを抑えます。これは通常、 $C_B$ の約1/25です。 $C_A$ 、 $C_B$ 、および $C_C$ は薄膜コンデンサにします。

### 温度の安定性

温度の精度と安定性を区別することが重要です。各レーザーの出力はある温度で最大になるので、温度の設定点は通常、このピークに達するまで上げていきます。その後は、温度の安定性だけが必要です。温度の安定性に影響を与える支配的パラメータは、サーミスタ、サーミスター・バイアス抵抗、および前段の電気回路のすべてのオ

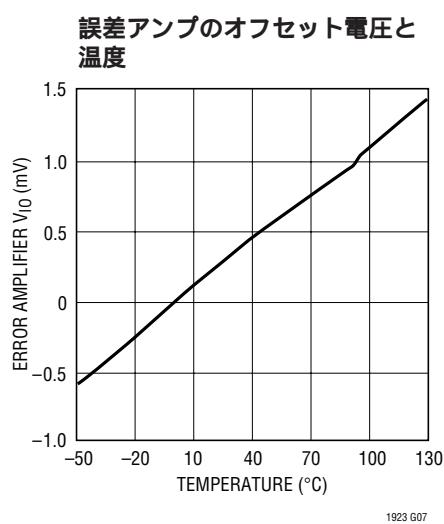

フェセット・ドリフトです。ループ利得が十分だと、下りのどんな偏差も温度安定性に大きく影響することはありません。レーザー・モジュール内の動作条件が比較的穏やかだと、サーミスターの長期安定性を促進します。サーミスターのバイアスには、温度係数の小さな高品質の抵抗を選択します。10kの抵抗の温度係数が100ppm/°Cの場合、必要な25°Cのレーザー設定点に対し、0°C ~ 70°Cの周囲温度範囲では0.18°Cの設定点温度差に相当します。システムの温度安定性の要求によっては、これは大きな値です。したがって、温度係数がもっと小さな抵抗が必要かもしれません。LTC2053の最大オフセット・ドリフトは50nV/°Cで、これは0°C ~ 70°Cの周囲温度で0.001以下への変化に相当します。

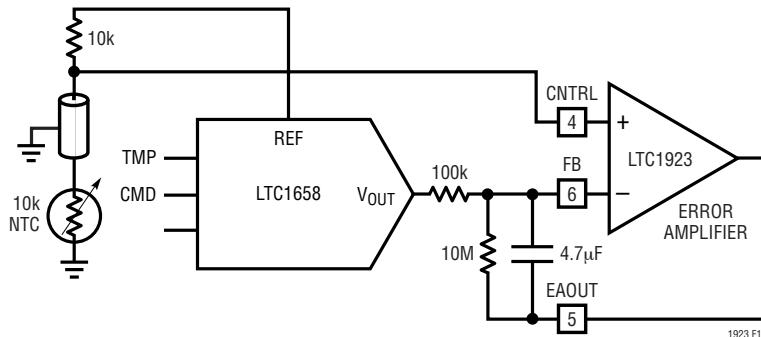

LTC1923の誤差アンプのオフセット・ドリフトをLTC2053の利得で割ったものも、温度安定性に影響を与えます。LTC1923のオフセット・ドリフト(特性曲線を参照)は、0°C ~ 70°Cの周囲温度範囲で通常1mVです。LTC2053の利得だけ減衰させると、これは0.004°Cの温度設定点の変動に相当します。これらのオフセットはどちらも大きな経時ドリフトは示しません。システムの設定点温度の安定性の要求によっては、LTC2053計装アンプは必要ないかもしれません。LTC2053を省いた簡略回路を図12に示します。

### ノイズとスルーレートの制御

スイッチング・レギュレータの不利な点の1つは、スイッチングにより、広帯域の高調波エネルギーが発生することです。高周波成分により、関連回路に問題が生じることがあります。

## アプリケーション情報

図12 . LTC2053計装アンプの前段を省いた簡略温度制御ループ

この問題を解決するため、LTC1923には $R_{SLEW}$ と呼ばれるピンがあり、出力のドライブ波形のスルーレートを制御します。遷移時間を遅くすると、エネルギーを長い時間にわたって分散して、高調波成分を減らします。遷移時間の延長により、効率がいくらか(およそ2%から3%)失われますが、入力電源に反射される高周波ノイズが大きく改善されます。

スルーレートの制御は $R_{SLEW}$ からAGNDに抵抗を接続して行います。スルーレートの制御が不要なら、 $R_{SLEW}$ ピンを $V_{DD}$ に接続して、出力ドライバが最高速で遷移できるようにします。抵抗値は10k(最高速遷移)と300k(最低速遷移)のあいだに設定します。これにより、スルーレートの範囲は約10:1となり、ノイズ性能を最適化します。スルーレート制御を行う場合、特に低速の遷移速度では、「ブレイク・ビフォア・メイク」時間を大きくする必要があるかもしれません。 $R_T$ の値を大きくして(同じ周波数動作を維持するため $C_T$ を小さくすることができます)調節をおこない、ブリッジのMOSFETのドライブが重ならないようにします。

### パワーMOSFET の選択

LTC1923と組み合わせて使う4個の外部MOSFETを選択する必要があります。ブリッジ下側の1対のNチャネルMOSFETとブリッジ上側の対角線上にある1対のPチャネルMOSFETです。MOSFETは $R_{DS(ON)}$ 、ゲート電荷、および $V_{DS}$ と $V_{GS}$ の最大定格によって選択します。5Vと12Vのブリッジ・アプリケーションには、20Vの最大 $V_{DS}$ 定格で十分ですが、「高電圧アプリケーション」の項で述べられているように、12Vの最大 $V_{GS}$ 定格では不十分で、もっと高電圧用のMOSFETを選択する必要があります。

$R_{DS(ON)}$ とゲート電荷のあいだにはトレードオフがあります。 $R_{DS(ON)}$ は導通損失( $I_{TEC}^2 \cdot R_{DS(ON)}$ )に影響を与え、ゲート電荷はスイッチング損失に対して支配的な影響を与えます。 $R_{DS(ON)}$ の大きなMOSFETは通常、ゲート容量が小さいので、同じ $BV_{DSS}$ に対して小さなゲート充電電流しか必要としません。1AのTECアプリケーションの場合、Si9801DYまたはSi9928DYのコンプリメンタリNチャネル/PチャネルMOSFETを使うと、スイッチング損失と導通損失のあいだの適切な妥協点が得られます。これ以上のTEC電流レベルでは、高電流での高効率を維持するため、選択されたMOSFETの $R_{DS(ON)}$ は小さくなればなりません。

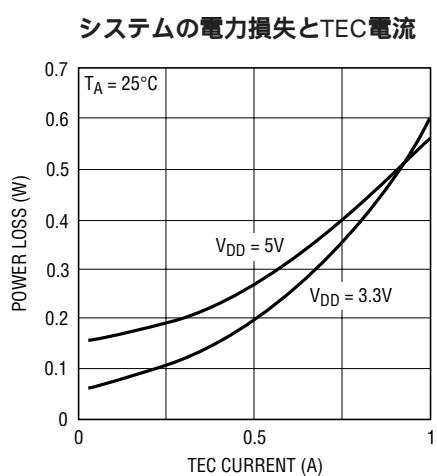

### 効率の検討

負荷電流には無関係に出力電圧が固定されている標準的電圧レギュレータとは異なり、このレギュレータの出力電圧は負荷電流とともに変化します。これは、TECが抵抗性をもつように見え、TECを流れる電流が電圧を定めるためです。レギュレータの出力電力は次のように定義されます。

$$P_{OUT} = I_{TEC}^2 \cdot R_{TEC}$$

スイッチング・レギュレータの効率は、出力電力 ÷ 入力電力 × 100%で表されます。個々の損失を解析して、効率を制限する要素が何であり、またどの要素が変化すれば最も効率が改善されるかを判断できる場合がよくあります。効率は次式で表すことができます。

$$\text{Efficiency} = 100\% - (L_1 + L_2 + L_3 + \dots)$$

ここで、 $L_1$ 、 $L_2$ などは入力電力に対するパーセンテージで表される個々の損失です。

## アプリケーション情報

このアプリケーションの場合、また効率が懸念されるのは、一般に出力電力が大きいときです。大きな電力損失はシステムの温度上昇が大きいことを意味し、ヒートシンクが必要となり、システムのサイズとコストの両方が増加します。

データシートの表紙に示されているアプリケーションの損失の大部分を生じさせる3つの主要な要素があります。入力電源電流、MOSFETのスイッチング損失および $I^2R$ 損失です。

1)入力電源電流は、LTC1658、LTC2053、LTC1923およびすべての追加回路に流れる消費電流からなります。これらのデバイスの最大電源電流の合計はおよそ5mAなので、全電力消費は25mWになります。この電力損失はTECの電流とは無関係です。

2)MOSFETドライバ電流は、パワーMOSFETのゲート容量のスイッチングによって生じます。ゲートが“L”から“H”、そして再び“L”に切り替わるたびに、 $V_{DD}$ からグランドに微小電荷 $dQ$ が移動します。ゲート充電電流は $I_{GATECHG} = 2 \cdot f \cdot (Q_P + Q_N)$ です。ここで、 $Q_P$ と $Q_N$ はブリッジの片側のNMOSとPMOSの総ゲート電荷で、 $f$ は発振器周波数です。ブリッジ全体は2組のMOSFETで構成されているので、係数2が必要になります。スイッチング周波数を上げると動的電流が増加するので、同じ割合で電力消費が増加します。この電力損失はTECの電流とは無関係です。

例： $Q_N = \text{最大 } 10\text{nC}$ 、 $Q_P = \text{最大 } 15\text{nC}$ 、 $f = 225\text{kHz}$ 、 $V_{DD} = 5\text{V}$

$$\text{Power loss} = 2 \cdot f \cdot (Q_P + Q_N) \cdot V_{DD} = 56\text{mW}$$

3)外部ブリッジのMOSFET、フィルタのインダクタ、および検出抵抗のDC抵抗は、一般にTEC電流が大きいときには損失の支配的要因です。電流の導通経路には1個のNMOS、1個のPMOS、2個のインダクタ、およびセンス抵抗が含まれるので、これらの部品に関連したDC抵抗が電力を消費します。

例：

$$5\text{Vでの } R_{DS(ON)NMOS} = \text{最大 } 0.055$$

$$5\text{Vでの } R_{DS(ON)PMOS} = \text{最大 } 0.08$$

$$R_S = 0.1$$

$$R_L = 0.1$$

$$I_{TEC} = 1\text{A}$$

$$R_{TEC} = 2.5$$

$$\begin{aligned}\text{総直列抵抗} &= 0.055 + 0.08 + 2 \cdot 0.1 + 0.1 \\ &= 0.435\end{aligned}$$

$$\text{電力損失} = (1\text{A})^2 \cdot 0.435 = 0.435\text{W}$$

$$\text{出力電力} = (1\text{A})^2 \cdot 2.5 = 2.5\text{W}$$

これは導通損失による17%の効率損失を表しています。他の2つの電力損失の要因は、この出力電力レベルで3%をわずかに超える効率損失になります。これは、電気的効率が主要な関心事である場合は問題となりますが、低 $R_{DS(ON)}$ のMOSFET、低直列抵抗のインダクタ、および値の小さなセンス抵抗を選択すれば容易に改善することができます。温度上昇が主要な関心事である場合は、この電力消費は許容できるでしょう。高い電流レベルでは、この例が示すように、抵抗値の小さな部品を選択します。

### 低電圧要求

このデータシートの表紙に示されているすべての部品は2.7Vの入力電源で動作します。正しい動作を保証するにはわずかな修正が必要です。LTC2053のREF入力の電圧は $V_{DD}$ より少なくとも1V低くする必要があります。その実現方法を図13に示します。2.5Vリファレンスを500のインピーダンスで分割し、これをLTC2053のREF入力とLTC1923の誤差アンプの積分抵抗に与えることにより、同相モードの問題はすべて回避されます。

## アプリケーション情報

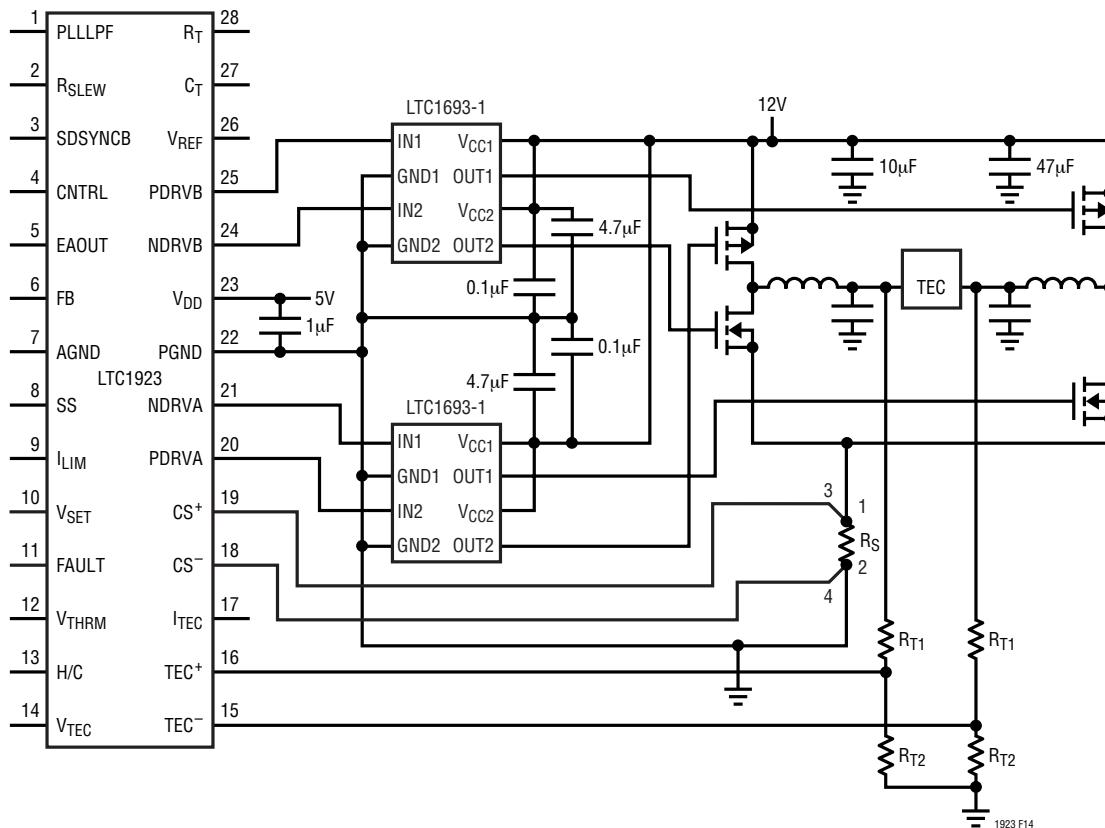

### 高電圧アプリケーション

アプリケーションで使用する基板面積を小さく抑えるために、複数のTECを直列に配線することができます。直列接続されたTECの個数と、それらの最大電圧降下の大きさに依存して、高い電圧電源が必要になります。他のアプリケーションでは、高電流の電源が1個だけ利用可能で、この電源の出力電圧はLTC1923の絶対最大電圧定格を超えているかもしれません。LTC1923の絶対最大入力電圧は6Vです。LTC1923を流れる電流は小さいので、低電流5V(またはそれ以下の)電源が使えます。全波ブリッジを駆動する12Vアプリケーションを図14に示します。2個のLTC1693-1高速デュアルMOSFETドライバが使われており、LTC1923ドライバが発生した低電圧を、全波ブリッジの駆動に必要な高電圧レベルに昇圧しています。LTC1693は、スイッチングが高速でAC電流が大きいので、適切なバイパスと接地が必要です。低ESRのバイパス・コンデンサをできるだけピンに近づけて実装し、リードができるだけ短くしてインダクタンスを減らします。詳細については、LTC1693のデータシートを参照してください。LTC1693-1の“L”から“H”と“H”から“L”的伝播遅延はほとんど等しいので(標準35ns)、これらのドライバの追加によるスキューはほとんどありません。LTC1923によって設定される、ブリッジの一方のシャットオフから他方のターンオンまでの十分なデッドタイム(標準50ns)が維持されます。このデッドタイムが不十分な場合、R<sub>T</sub>ピンに接続する抵抗の値を大きくしてこの時間を長くすることができます。最大ドレイ

ン・ソース電圧V<sub>DS</sub>、ゲート・ソース電圧V<sub>GS</sub>、およびR<sub>DS(ON)</sub>に基づいて、適切な外部MOSFETが選択されているか注意を払って確認します。絶対最大V<sub>DS</sub>が20VのMOSFETの多くは最大V<sub>GS</sub>がわずか12Vであり、12Vのアプリケーションには不十分です。最大V<sub>GS</sub>定格が14VのSi9801DYでさえ、12Vのブリッジ電源電圧に対して、マージンが適切ではないかもしれません。R<sub>DS(ON)</sub>に関するMOSFETの選択の詳細については、「効率の検討」を参照してください。

2対の抵抗R<sub>T1</sub>とR<sub>T2</sub>を追加して、TEC<sup>+</sup>入力とTEC<sup>-</sup>入力で絶対最大入力電圧を超ないようにします。TEC<sup>+</sup>とTEC<sup>-</sup>の最大電圧は、LTC1923のV<sub>DD</sub>入力電源(この例では5V)より小さくなければなりません。次式により、これが保証されます：

$$(1 + R_{T1}/R_{T2} + R_{T1}/100k) \cdot V_{BRIDGE} < V_{DD}$$

ここで、V<sub>BRIDGE</sub>は外部ブリッジ回路の電源電圧で、V<sub>DD</sub>はLTC1923の入力電源です。

これらの追加のレベルシフト用抵抗は、データシートのいくつかのパラメータに影響を与えます。方向コンパレータのスレッショルドは次の値に増加します。

$$(1 + R_{T1}/R_{T2} + R_{T1}/100k) \cdot 50mV \text{ および }$$

$$(1 + R_{T1}/R_{T2} + R_{T1}/100k) \cdot -50mV$$

図13. 低入力電源電圧回路

## アプリケーション情報

図14 . LTC1923を使った高電圧アプリケーション

V<sub>TEC</sub>ピンの出力電圧は、TEC (V<sub>TECOOLER</sub>)両端の電圧を  $1/(1+R_{T1}/R_{T2}+R_{T1}/100k)$  に減少させた値を表します。つまり、

$$V_{VTEC} = V_{TECOOLER} / (1 + R_{T1} / R_{T2} + R_{T1} / 100k)$$

100kを含む項は、差動アンプの入力インピーダンスによって生じる負荷誤差です。一般にこの値は100kとなります。通常のプロセスのバラツキと温度により(最大±30%)変化する可能性があります。この変動に対応するため、負荷効果を最小に抑えて、TECクランプ電圧の許容差を厳しく保ちます。これは、R<sub>T1</sub>の値をできるだ

け小さくすることによって達成できます。ただし、消費電流は増加します。

このレベルシフトの結果、クランプを起動するのに必要なTEC電圧は上昇します。クランプが起動するTEC両端の電圧は次のようにになります。

$$V_{TECOOLER} = (1 + R_{T1} / R_{T2} + R_{T1} / 100k) \cdot 2.5V$$

LTC1693 MOSFETドライバを使うと不利な点の1つは、出力ドライバのスルーレートを調節してシステムのノイズを減らすことができないことです。

## パッケージ寸法

**GNパッケージ**

**28ピン・プラスチックSSOP(細型0.150インチ)**

(Reference LTC DWG # 05-08-1641)

\*寸法にはモールドのバリを含まない。モールドのバリは各サイドで0.006"(0.152mm)を超えないこと

\*\*寸法にはリード間のバリを含まない。リード間のバリは各サイドで0.010"(0.254mm)を超えないこと

GN28 (SSOP) 1098

## 関連製品

| 製品番号      | 説明                          | 注釈                                               |

|-----------|-----------------------------|--------------------------------------------------|

| LTC1658   | 14ビット・レール・ツー・レール・マイクロパワーDAC | 3Vまたは5Vの単電源動作、 $I_{CC} = 270\mu A$ 、8ピンMSOPパッケージ |

| LTC1693-1 | 高速デュアルNチャネルMOSFETドライバ       | 1.5Aピーク出力電流、1G 電気的絶縁、SO-8パッケージ                   |

| LTC2053   | ゼロ・ドリフト計装アンプ                | 最大利得誤差:0.01%、入力オフセット・ドリフト: 50nV/、入力オフセット電圧:10μV  |