## 特長

- 広い電源電圧範囲 :  $2.7V \leq V_{CC} \leq 5.5V$

- 広いリファレンス電圧範囲 :  $0V \sim 5.5V$

- 2つのインターフェース・モード :

- パルス・モード(インクリメント専用)

- プッシュボタン・モード(インクリメント/デクリメント)

- 低消費電流 :  $50\mu A$

- シャットダウン時の消費電流 :  $0.2\mu A$

- 8ピンMSOPおよびSOパッケージで供給

- シャットダウン時にもDAC設定を保持

- 立上り時にDAC出力は中間レンジに設定

- 低出力インピーダンス :  $<100$

- 出力周波数 : 5kHz標準

## アプリケーション

- LCDコントラストおよびバックライト輝度制御

- 電源電圧の調整

- バッテリ・チャージャ電圧および電流調整

- GaAs FETバイアス調整

- トリマ・ポットの代替え

## 概要

LTC<sup>®</sup>1426はデュアル・マイクロパワー6ビットPWM DACで、多様なPWM出力や柔軟性の高いプッシュボタン対応デジタル・インターフェースを備えています。DAC出力は0Vから $V_{REF}$ に振幅するPWM信号を供給し、 $V_{REF}$ の電圧を調整することによってフルスケール出力を変化させることができます。PWM出力周波数は標準5kHzで、出力フィルタリング条件が単純になります。 $V_{CC}$ 電源電流は標準 $50\mu A$ で、シャットダウン時には $0.2\mu A$ に低下します。

LTC1426はプッシュボタンとパルスの2つのインターフェース・モードの1つを使用して制御できます。LTC1426はCLKピンの状態をモニタして、始動時に自身を自動的に適切なモードに構成します。プッシュボタン・モードでは、CLKピンを外部プッシュボタンに直接接続して、DAC出力を制御することができます。パルス・モードでは、CLKピンをCMOSコンパチブル・ロジックに接続できます。DAC出力は最初は1/2スケールで立ち上がり、シャットダウン時には内部DACレジスタの内容が保持されます。

LTC1426は8ピンMSOPおよびSOパッケージで供給されます。

**L**、**LTC**、**LT**はリニアテクノロジー社の登録商標です。

## 標準的応用例

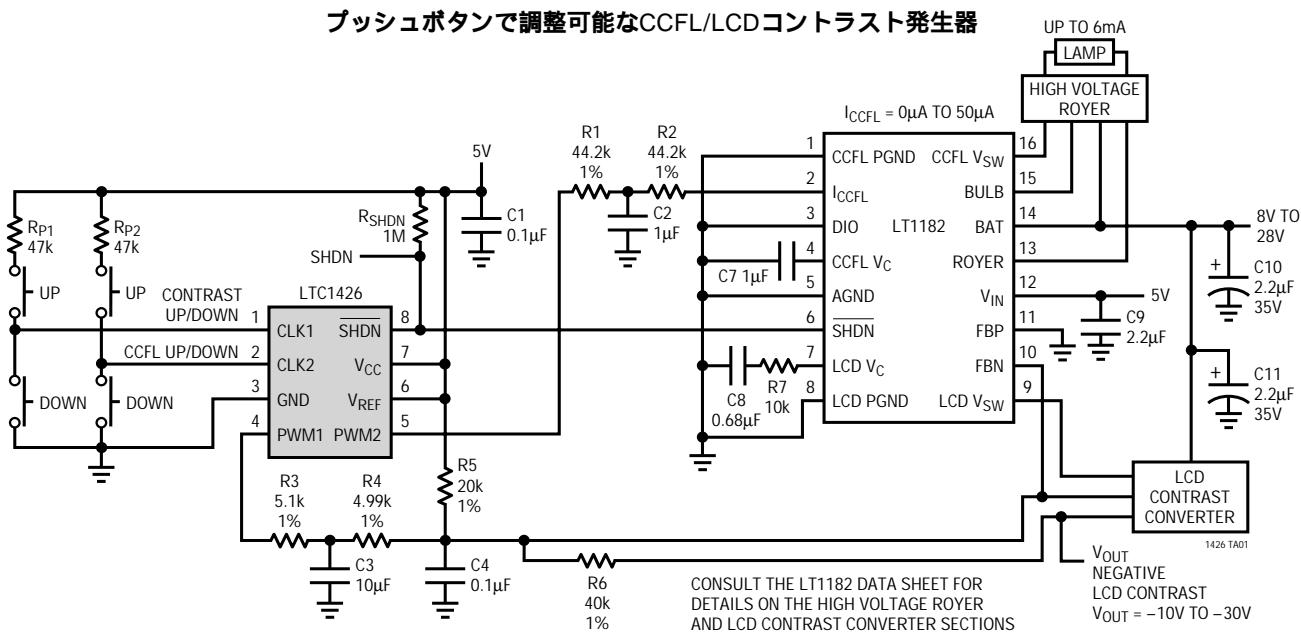

### プッシュボタンで調整可能なCCFL/LCDコントラスト発生器

## 絶対最大定格

(Note 1)

|                       |                            |

|-----------------------|----------------------------|

| 全電源電圧( $V_{CC}$ )     | 7V                         |

| リファレンス電圧( $V_{REF}$ ) | - 0.3 ~ 7V                 |

| 入力電圧(全入力)             | - 0.3 ~ ( $V_{CC}$ + 0.3V) |

| DAC出力短絡時間             | 無限                         |

| $I_{PWM\ MAX}$        | 100mA                      |

## 動作温度範囲

|                 |            |

|-----------------|------------|

| LTC1426C        | 0 ~ 70     |

| LTC1426I        | - 40 ~ 85  |

| 保存温度範囲          | - 65 ~ 150 |

| リード温度(半田付け、10秒) | 300        |

## パッケージ/発注情報

| ORDER PART NUMBER |

|-------------------|

| LTC1426CMS8       |

| LTC1426CS8        |

| LTC1426IS8        |

| MS8 PART MARKING  |

| LTBQ              |

| S8 PART MARKING   |

| 1426              |

| 1426I             |

TOP VIEW

MS8 PACKAGE 8-LEAD PLASTIC MSOP

S8 PACKAGE 8-LEAD PLASTIC SO

$T_{JMAX} = 100^{\circ}\text{C}$ ,  $\theta_{JA} = 200^{\circ}\text{C}/\text{W}$  (MS8)

$T_{JMAX} = 100^{\circ}\text{C}$ ,  $\theta_{JA} = 130^{\circ}\text{C}/\text{W}$  (S8)

ミリタリ・グレードに関してはお問い合わせください。

電気的特性 注記がない限り、 $T_A = 25$  (Note 2)

| SYMBOL    | PARAMETER                             | CONDITIONS                                                                                                                                                                                  | MIN                | TYP             | MAX                    | UNITS                                           |

|-----------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|------------------------|-------------------------------------------------|

| $V_{CC}$  | Supply Voltage                        |                                                                                                                                                                                             | ●                  | 2.7             | 5.5                    | V                                               |

| $V_{REF}$ | Reference Voltage                     |                                                                                                                                                                                             | ●                  | 0               | 5.5                    | V                                               |

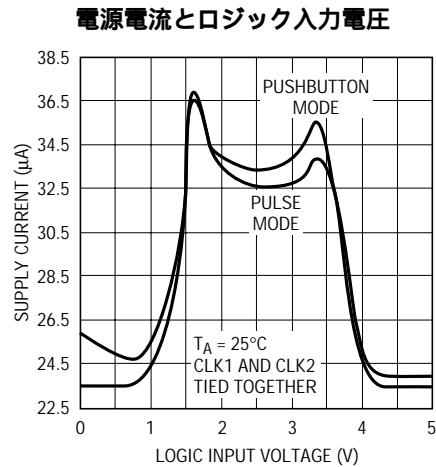

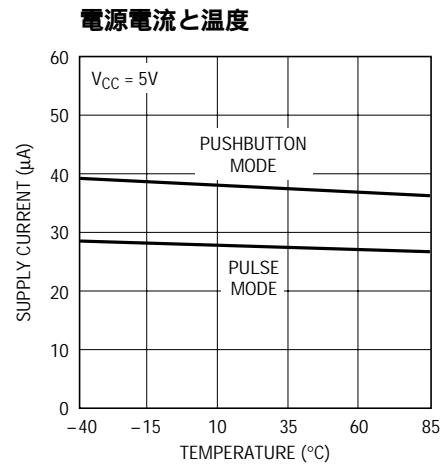

| $I_{CC}$  | Supply Current                        | Pulse Mode: $V_{SHDN} = V_{CC}$ , $V_{CLK1} = V_{CLK2} = 0V$ , $PWM1 = PWM2 = NC$<br>Pushbutton Mode: $V_{SHDN} = V_{CC}$ , $V_{CLK1} = V_{CLK2} = PWM1 = PWM2 = NC$<br>$SHDN = 0$ (Note 3) | ●<br>●<br>●        | 40<br>50<br>0.2 | 100<br>100<br>$\pm 10$ | $\mu\text{A}$<br>$\mu\text{A}$<br>$\mu\text{A}$ |

| $I_{REF}$ | Reference Current                     | Pulse Mode: $V_{SHDN} = V_{CC}$ , $V_{CLK1} = V_{CLK2} = 0V$ , $PWM1 = PWM2 = NC$<br>Pushbutton Mode: $V_{SHDN} = V_{CC}$ , $V_{CLK1} = V_{CLK2} = PWM1 = PWM2 = NC$<br>$SHDN = 0$ (Note 3) | ●<br>●<br>●        | 75<br>75<br>0.2 | 150<br>150<br>$\pm 10$ | $\mu\text{A}$<br>$\mu\text{A}$<br>$\mu\text{A}$ |

|           | DAC Resolution                        |                                                                                                                                                                                             |                    | 6               |                        | bits                                            |

|           | DAC Frequency                         | $0^{\circ}\text{C} \leq T_A \leq 70^{\circ}\text{C}$<br>$-40^{\circ}\text{C} \leq T_A \leq 85^{\circ}\text{C}$                                                                              | ●<br>●             | 3<br>2          | 5<br>5                 | kHz                                             |

|           | DAC Output Impedance                  | $V_{CC} = 2.7\text{V}$ , $V_{REF} = 0.5\text{V}$                                                                                                                                            | ●                  | 20              | 100                    | $\Omega$                                        |

|           | DAC Full-Scale Duty Cycle             |                                                                                                                                                                                             |                    | 98.44           |                        | %                                               |

|           | DAC Zero-Scale Duty Cycle             |                                                                                                                                                                                             |                    | 0               |                        | %                                               |

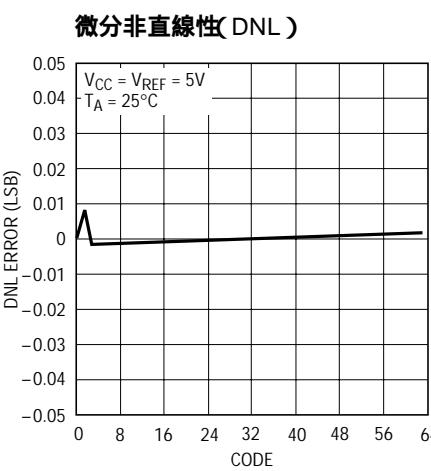

| DNL       | DAC Differential Nonlinearity         | Monotonicity Guaranteed (Note 4)                                                                                                                                                            | ●                  |                 | $\pm 0.05$             | LSB                                             |

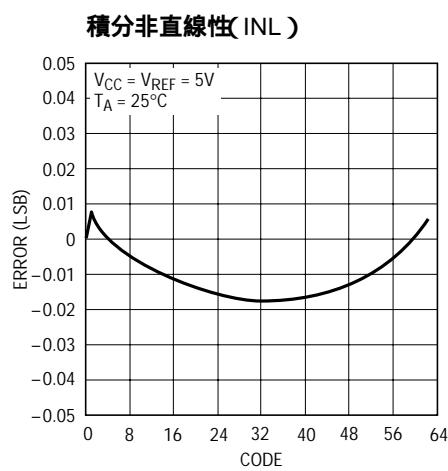

| INL       | DAC Integral Nonlinearity             | (Note 4)                                                                                                                                                                                    | ●                  |                 | $\pm 0.05$             | LSB                                             |

| FS Error  | DAC Full-Scale Error                  |                                                                                                                                                                                             | ●                  |                 | $\pm 0.50$             | LSB                                             |

| $I_{IN}$  | Logic Input Current                   | Pulse Mode: $0V \leq V_{IN} \leq V_{CC}$                                                                                                                                                    | SHDN<br>CLK1, CLK2 | ●<br>●          | $\pm 5$<br>$\pm 5$     | $\mu\text{A}$<br>$\mu\text{A}$                  |

|           |                                       | Pushbutton Mode: $0V \leq V_{IN} \leq V_{CC}$                                                                                                                                               | SHDN<br>CLK1, CLK2 | ●<br>●          | $\pm 5$<br>$\pm 10$    | $\mu\text{A}$<br>$\mu\text{A}$                  |

| $V_{IH}$  | CLK High Level Input Voltage (Note 5) | $V_{CC} = 5.5\text{V}$                                                                                                                                                                      | SHDN<br>CLK1, CLK2 | ●<br>●          | 2.0<br>4.4             | V<br>V                                          |

|           |                                       | $V_{CC} = 3.6\text{V}$                                                                                                                                                                      | SHDN<br>CLK1, CLK2 | ●<br>●          | 1.9<br>2.9             | V<br>V                                          |

電気的特性 注記がない限り、 $T_A = 25$  (Note 2)

| SYMBOL       | PARAMETER                            | CONDITIONS                                                 | MIN    | TYP        | MAX      | UNITS          |    |

|--------------|--------------------------------------|------------------------------------------------------------|--------|------------|----------|----------------|----|

| $V_{IL}$     | CLK Low Level Input Voltage (Note 5) | $V_{CC} = 4.5V$ SHDN<br>CLK1, CLK2                         | ●      |            | 0.8      | V              |    |

|              |                                      | $V_{CC} = 2.7V$ SHDN<br>CLK1, CLK2                         | ●      |            | 0.45     | V              |    |

| $I_{OZ}$     | Three-State Output Leakage           | SHDN = 0                                                   | ●      |            | $\pm 5$  | $\mu A$        |    |

| $Z_{IN}$     | CLK Input Resistance                 | Pushbutton Mode, CLK1/CLK2                                 |        |            | 2.5      | $M\Omega$      |    |

| $f_{CLK}$    | Clock Frequency                      | Pulse Mode, $V_{CC} = 3.3V$<br>Pulse Mode, $V_{CC} = 2.7V$ | ●<br>● |            | 1<br>750 | $MHz$<br>$kHz$ |    |

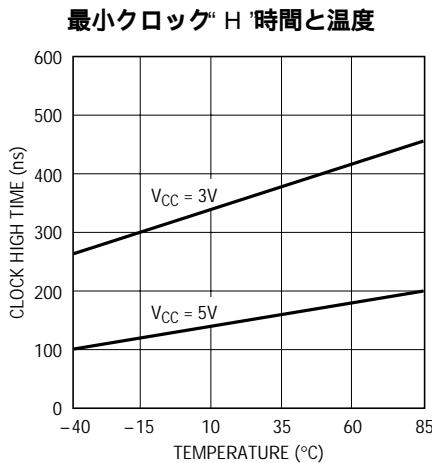

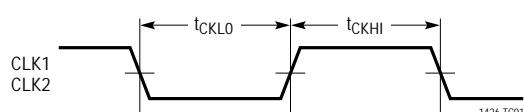

| $t_{CKHI}$   | Clock High Time                      | Pulse Mode, $V_{CC} = 3.3V$<br>Pulse Mode, $V_{CC} = 2.7V$ | ●<br>● | 450<br>600 |          | ns<br>ns       |    |

| $t_{CKLO}$   | Clock Low Time                       | Pulse Mode, $V_{CC} = 3.3V$<br>Pulse Mode, $V_{CC} = 2.7V$ | ●<br>● | 450<br>600 |          | ns<br>ns       |    |

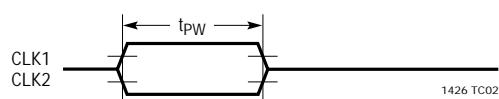

| $t_{PW}$     | Pulse Width                          | Pushbutton Mode                                            | ●      | 670        |          | $\mu s$        |    |

| $t_{DEB}$    | Debounce Time                        | Pushbutton Mode                                            | ●      | 10.7       | 12.8     | 21.3           | ms |

| $t_{DELAY}$  | Repeat Rate Delay                    | Pushbutton Mode                                            | ●      | 340        | 410      | 680            | ms |

| $f_{REPEAT}$ | Repeat Frequency                     | Pushbutton Mode                                            | ●      | 11.7       | 19.5     | 23.4           | Hz |

は全動作温度範囲の規格値を意味する。

Note 1 : 絶対最大定格はそれを超えるとデバイスの寿命に影響を及ぼす値。

Note 2 : デバイスのピンに流入する電流はすべて正。デバイスのピンから流出する電流はすべて負。注記がない限り、電圧はすべてグランドを基準とする。すべての標準値は  $V_{CC} = V_{REF} = 5V$ 、 $T_A = 25^\circ C$ 、および PWM1/PWM2出力は GND、 $C_{PWM} = 10pF$  で得られる。

Note 3 :  $V_{CC} > V_{REF}$  または  $V_{REF} > V_{CC}$  の場合、リーコンデンサのためシャットダウン電流は負の可能性がある。

Note 4 : 設計で保証されている。 $V_{CC}$  ピンおよび  $V_{REF}$  ピンは高品質、低ESR、低ESLの0.1 $\mu F$ コンデンサを使用してGNDにデカップルし、PWMスイッチング・ノイズを除去すること。そうしないとCLK1/CLK2のハイ・インピーダンス入力パッファに結合されるおそれがある。デカップリング・コンデンサをこれらのピンの近くに配置して、グランド・ラインが最大の効果を発揮するようにする。

Note 5 : 入力スレッショルドはプッシュボタンとパルス・モードの両方に適用される。

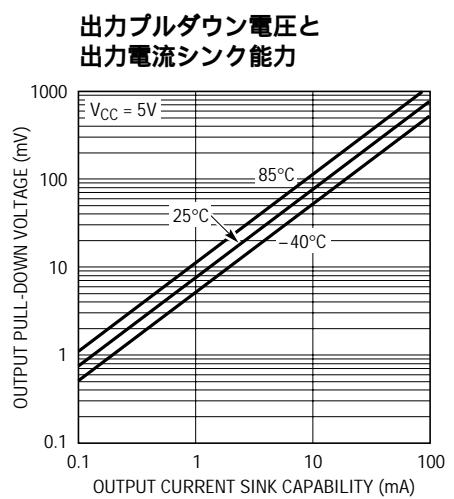

## 標準的性能特性

## 標準的性能特性

1426 G04

1426 F05

1426 G06

## ピン機能

CLK1(ピン1): チャネル1クロック/プッシュボタン入力

CLK2(ピン2): チャネル2クロック/プッシュボタン入力

GND(ピン3): グランド。GNDはグランド・プレーンに接続してください。

PWM1(ピン4): チャネル1 PWM出力

PWM2(ピン5): チャネル2 PWM出力

$V_{REF}$ (ピン6): 電圧リファレンス入力。 $V_{REF}$ はDAC出力バッファに電力を供給し、出力幅を制御するのに使用できます。

外付けコンデンサで $V_{REF}$ をGNDにバイパスして、出力誤差を最小限に抑えます。必要に応じて $V_{REF}$ を $V_{CC}$ に接続できます。

6

$V_{CC}$ (ピン7): 電圧電源。この電源は直接グランド・プレーンにバイパスして、ノイズやリップルが乗らないようにしなければなりません。

$SHDN$ (ピン8): シャットダウン。このピンに“L”を印加すると、チップはシャットダウン・モードになります。PWM出力がハイ・インピーダンス状態になります。シャットダウン中もDACのデジタル設定値が保持されます。

## タイミング図

### パルス・モード・タイミング

### プッシュボタン・モード・タイミング

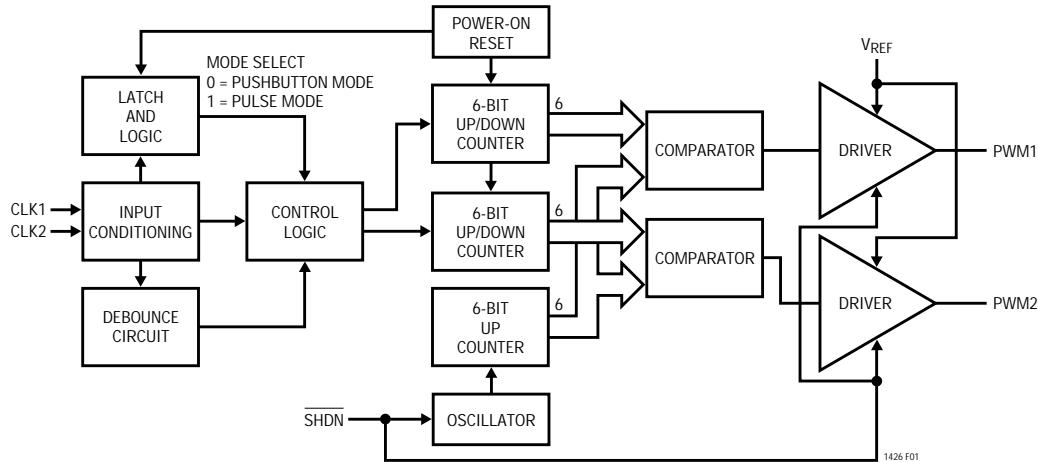

## プロック図

図1. LTC1426のプロック図

## 定義

LSB : 最下位ビット、つまり2つの連続したコードの理想的なデューティ・サイクルの差です。

$$LSB = DC_{MAX} / 64$$

$$DC_{MAX} = DAC\text{出力の最大デューティ・サイクル}$$

分解能 : 分解能はフルスケール出力デューティ・サイクル・レンジを分割するDAC出力状態の数( 64 )です。分解能は必ずしも直線性を意味しません。

INL : エンドポイント積分非直線性は、DAC伝達曲線の両端を通る直線からの最大偏差です。与えられたコードでのINL誤差は、次のとおり計算されます :

$$INL = ( DC_{OUT} - DC_{IDEAL} ) / LSB$$

$$DC_{IDEAL} = ( \text{Code} ) / LSB$$

$DC_{OUT}$  = 与えられたクロック・パルス数で測定されるDAC出力のデューティ・サイクル

DNL : 微分直線性誤差は、任意の2つの隣接するコード間で測定した変化と理想的な1LSBデューティ・サイクル変化の差です。2つのコード間のDNL誤差は次式で計算されます。

$$DNL = ( DC_{OUT} - LSB ) / LSB$$

$DC_{OUT}$  = 2つの隣接するコード間で測定したデューティ・サイクルの差。

フルスケール誤差 : フルスケール誤差はすべてのビットを1にセットしたときの( コード = 63 )、DAC出力のデューティ・サイクルの理想値と測定値の差です。フルスケール誤差は次式で計算されます。

$$FSE = ( DC_{OUT} - DC_{IDEAL} ) / LSB$$

$$DC_{IDEAL} = DC_{MAX}$$

## アプリケーション情報

## デュアル6ビットPWM DAC

図1にLTC1426のプロック図を示します。各6ビットPWM DACは単調性が保証されており、64の等ステップでデジタル的に調整が可能です。これは0%から98.5%デューティ・サイクル( フルスケール )に対応します。カウンタは電源立ち上げ時に100000Bにリセットされ、2つのDACは中点デューティ・サイクルに設定されます。PWM出力の出力インピーダンスは100 Ω以下です。DAC出力は0Vからリファレンス電

圧 $V_{REF}$ まで振幅します。 $V_{REF}$ は0Vから5.5Vまでバイアス可能です。DAC出力の周波数は3kHzを超え、出力のフィルタリングが容易です。

純粋な抵抗負荷の場合、負荷 $R_L$ で測定した電圧は次式で与えられます。

$$V = ( V_{PWM} \cdot R_L ) / ( R_L + R_{OUT} )$$

## アプリケーション情報

ただし、 $V_{\text{PWM}}$ は無負荷時のDAC出力電圧、 $R_L$ は抵抗負荷、 $R_{\text{OUT}}$ はDAC出力インピーダンスです。したがって、抵抗負荷  $R_L$ は負荷電圧に対する出力インピーダンスの影響を無視できるよう十分大きくなければなりません。

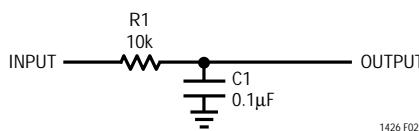

図2にPWM出力のフィルタリングに推奨される標準ローパス・フィルタを示します。フィルタを使用しない場合、フィルタなしの出力から得られた結果は、電圧計で測定した場合に誤差が増加する可能性があります。フィルタの時定数tとPWM周波数の比で、システムに供給される出力リップル周波数の量が決まります。さらに、出力の負荷によってR1両端の追加誤差電圧も決まります。

図2. PWM平均化用ローパス・フィルタ

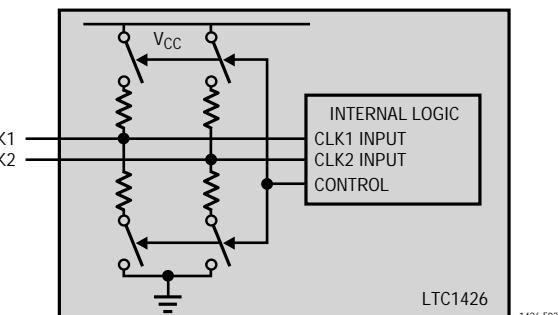

### デジタル・インターフェース

LTC1426はパルス・モードとプッシュボタン・モードの2つのインターフェース・モードの1つを使用して制御できます。動作インターフェース・モードは電源立ち上げ時に決定されます。CLK1およびCLK2の両入力が電源立ち上げ時にフロートしている場合、インターフェース・モード検出回路は次に $V_{\text{CC}}$ がリセットされるまでチップをプッシュボタン・モードに構成します(図3)。しかし、CLK1またはCLK2のいずれかが電源立ち上げ時にロジック0または1の場合、チップは次に $V_{\text{CC}}$ がリセットされるまで、パルス・モードに構成されます。

### 標準的応用例

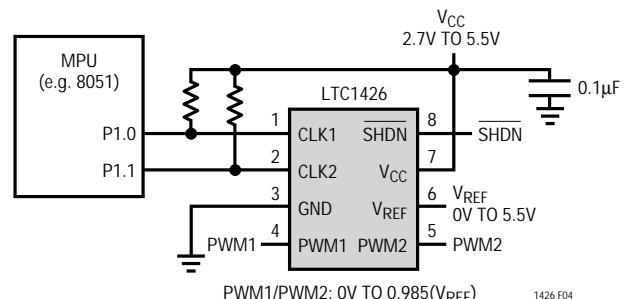

このICの標準アプリケーションには、デジタル較正、産業プロセス制御、自動テスト装置、セルラー電話、ポータブル・バッテリ電源アプリケーションなどがあります。図4および5にこのICがいかに使いやすいかを示します。どのアプリケーションでも、PWMフルスケール出力電圧は $V_{\text{REF}}$ によって設定されます。したがって、多様なリファレンス・スパンが必要なときに、インターフェースが便利になります。

#### パルス・モード

図4にパルス・モード、独立型アプリケーションのLTC1426を示します。LTC1426は最小限の外付け部品で、ほとんどのポピュラーなマイクロプロセッサ(MPU)にインターフェース可能です。LTC1426との直接インターフェースを例示するた

めにインテル8051を選択しました。これは、このマイクロプロセッサが擬似双方向ポートを備えており、 $V_{\text{CC}}$ への追加プルアップ抵抗が不要であるという理由からです。しかし、図3に電源立ち上げ時のインターフェース・モードを決定するための簡略化したロジックを示します。LTC1426は1組のプルアップ/プルダウン抵抗によって、電源立ち上げ時のCLKピンの状態を検知することができます。CLK1ピンとCLK2ピンの両方が電源立ち上げ時にフロートしている場合、LTC1426からの制御信号によって、これらの抵抗が切り離されるため、LTC1426は各CLKピンの動作状態、つまり“H”、“L”、および“中間(フローティング)”を検出することができます。CLKピンが電源立ち上げ時にロジック0または1のいずれかに接続された場合、制御信号はこれらの抵抗を切り離してCLK1とCLK2をCMOSコンパチブル入力ピンにします。

2つのCLKピンが常に同じモードなることに注意してください。電源立ち上げ時に1つのピンがフロートしており、もう1つのピンがロジック“H”“L”的場合、LTC1426はパルス・モードになります。

図3. インタフェース・モード検出回路

めにインテル8051を選択しました。これは、このマイクロプロセッサが擬似双方向ポートを備えており、 $V_{\text{CC}}$ への追加プルアップ抵抗が不要であるという理由からです。しかし、

図4. 独立型パルス・モード・インターフェース

## アプリケーション情報

マイクロプロセッサがリセット中にポート・ピンを“H”にプルアップしない場合は、外部プルアップ抵抗を使用しなければなりません。

パルス・モードでは、CLK1またはCLK2入力に印加される各クロック・パルスが、それぞれのカウンタを1カウントずつインクリメントします。カウンタがフルスケール(111111B)を超えて増えると、カウンタはロールオーバして、ゼロ・スケール(000000B)になります。このように、CLK1またはCLK2入力に1個のパルスを印加すると対応するカウンタが1カウントだけインクリメントされ、63個のパルスでカウンタが1カウントだけデクリメントされます。

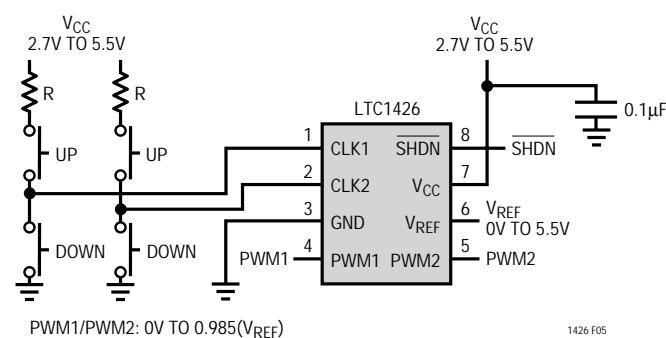

### プッシュボタン・モード

図5に、標準的なプッシュボタン・アプリケーションでLTC1426を使用する方法を示します。プッシュボタン・モードでは、ロジック1がCLK1またはCLK2入力に印加されると、それぞれのカウンタが1カウントだけインクリメントされ、カウンタがフルスケール(111111B)に達するとインクリメントが停止されます。CLK1またはCLK2入力にロジック0パルスが印加されると、対応するカウンタが1カウントだけデクリメントされ、カウンタがゼロ・スケール(000000B)に達するとデクリメントを停止します。オンチップ・デバウンス回路は、バウンシング・プッシュボタンによる不測のカウントを防止するために、12.8msのデバウンス時間が設定されています。プッシュボタンを押したままの場合、カウンタは410msの遅延後に19.5Hzの繰返し速度でインクリメント/デクリメントを開始します。

CLKおよびPWMトレースが互いに接近しないように注意してください。プッシュボタン・モードではCLKピンはハイ・インピーダンス入力ノードになるため、適切に配線していない場合は、PWM出力による電流スパイクがPWMラインとCLKライン間の寄生容量を介して貫通します。最適な性能を達成するには、適切な接地手法を使用し、これらのラインを正しく配置しなければなりません。

PWM1/PWM2: 0V TO 0.985(V<sub>REF</sub>)

LIMITING RESISTOR R PREVENTS SHORTING OF V<sub>CC</sub> AND GND WHEN BOTH BUTTONS ARE SIMULTANEOUSLY PUSHED. THIS RESISTOR CAN BE PLACED EITHER IN THE V<sub>CC</sub> OR GND LEG AND THIS DETERMINES THE FUNCTION WHEN BOTH BUTTONS ARE PUSHED. VALUE OF R < 50k

図5. プッシュボタン・モード・インターフェース

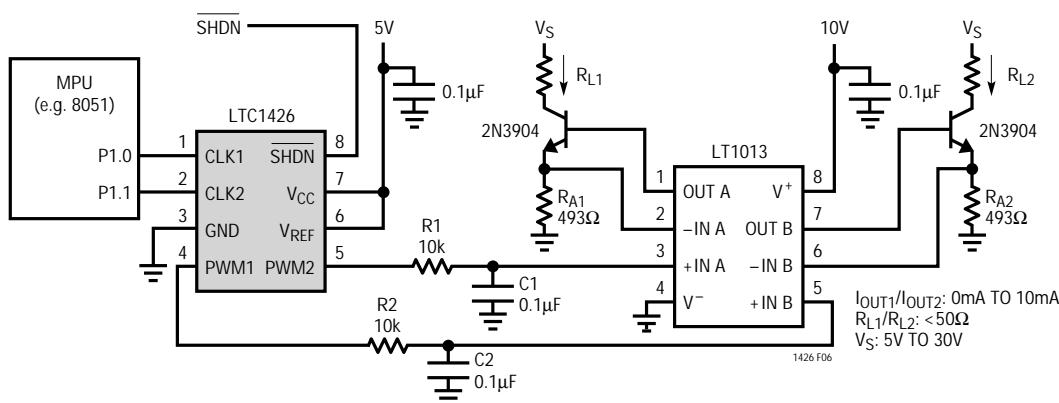

図6にLT<sup>®</sup>1013デュアル高精度オペアンプと2個のNPNトランジスタ(2N3904)を使用した、デュアルのデジタル・プログラマブル電流源を示します。R1とC1( R2、C2 )を組み合わせてローパス・フィルタを構成すれば、出力は0V ~ 4.93Vまで振幅します。図に示す構成ではこの電圧は抵抗R<sub>A1</sub>( R<sub>A2</sub> )に印加されます。R<sub>A1</sub>( R<sub>A2</sub> )に493Ωを選択すれば、出力電流はゼロ・スケールの0mAからフルスケールの10mAまで変化します。V<sub>S</sub>の最小電圧は、負荷抵抗R<sub>L1</sub>( R<sub>L2</sub> )とQ1( Q2 )のV<sub>CESAT</sub>電圧によって決まります。50Ωの負荷抵抗では、電圧源は最低5Vにすることができます。

図6にLT<sup>®</sup>1013デュアル高精度オペアンプと2個のNPNトランジスタ(2N3904)を使用した、デュアルのデジタル・プログラマブル電流源を示します。R1とC1( R2、C2 )を組み合わせてローパス・フィルタを構成すれば、出力は0V ~ 4.93Vまで振幅します。図に示す構成ではこの電圧は抵抗R<sub>A1</sub>( R<sub>A2</sub> )に印加されます。R<sub>A1</sub>( R<sub>A2</sub> )に493Ωを選択すれば、出力電流はゼロ・スケールの0mAからフルスケールの10mAまで変化します。V<sub>S</sub>の最小電圧は、負荷抵抗R<sub>L1</sub>( R<sub>L2</sub> )とQ1( Q2 )のV<sub>CESAT</sub>電圧によって決まります。50Ωの負荷抵抗では、電圧源は最低5Vにすることができます。

図6. デュアルのデジタル的にプログラム可能な電流源

## 標準的応用例

### シャットダウン・モード

“L”のシャットダウン信号を印加すると、IC全体がマイクロパワー・シャットダウン・モードになり、 $V_{CC}$ 電源電流が標準0.3 $\mu$ A以下に低減されます。シャットダウン機

能の特徴として、現在のPWM1およびPWM2コードのデータ保持があり、シャットダウン状態からリリースされるとこれらの状態は元に戻ります。これはPWM1出力とPWM2出力に中点がプリセットされる電源立上り時と比較した場合の機能的な違いです。

## 関連製品

| PART NUMBER                              | DESCRIPTION                                                                                              | COMMENTS                                                |

|------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| LT1182/LT1183                            | CCFL/LCD Contrast Switching Regulators                                                                   | 3V to 30V Single Supply in 16-Pin SO                    |

| LTC1257<br>Up to 12V, i.e., FS Max = 12V | Single 12-Bit $V_{OUT}$ DAC, Full Scale: 2.048V, $V_{CC}$ : 4.75V to 15.75V. Reference Can Be Overdriven | 5V to 15V Single Supply, Complete $V_{OUT}$ DAC in SO-8 |

| LTC1329/LTC1329-10/LTC1329-50            | Micropower $I_{OUT}$ 8-Bit Current DAC                                                                   | 2.7V to 6.5V Single Supply in SO-8                      |

| LTC1446/LTC1446L                         | Dual, Serial I/O $V_{OUT}$ 12-Bit DAC in SO-8                                                            | Rail-to-Rail $V_{OUT}$ , 5V/3V Single Supply            |

| LTC1451/LTC1452/LTC1453                  | Complete Serial I/O $V_{OUT}$ 12-Bit DACs                                                                | Rail-to-Rail $V_{OUT}$ , 3V/5V Single Supply in SO-8    |

| LTC1590                                  | Dual, Serial I/O Multiplying $I_{OUT}$ 12-Bit DAC                                                        | 5V Single Supply in 16-pin SO Package                   |

| LTC8043                                  | Serial I/O Multiplying $I_{OUT}$ 12-Bit DAC                                                              | 5V Single Supply in SO-8                                |