## 特長

■ ソフトウェア選択可能なケーブル終端：

RS232(V.28)

RS423(V.10)

RS422(V.11)

RS485

RS449

EIA530

EIA530-A

V.35

V.36

X.21

■ 電源オフ時に出力はラインの負荷にならない

## 概要

LTC<sup>®</sup>1344は6個のソフトウェア選択可能なマルチプロトコル・ケーブル・ターミネータを備えています。各ターミネータは、RS422(V.10)100 最小差動負荷、V.35 Tネットワーク負荷、あるいは自身が終端をもつRS232(V.28)またはRS423(V.10)トランシーバで使用するためのオープン回路として構成することができます。LTC1343と組み合わせると、LTC1344は完全なソフトウェア選択可能なマルチプロトコル・シリアル・ポートを構成します。データ・バス・ラッチ機能によって、複数のインターフェース・ポート間でセレクト・ラインを共用できます。

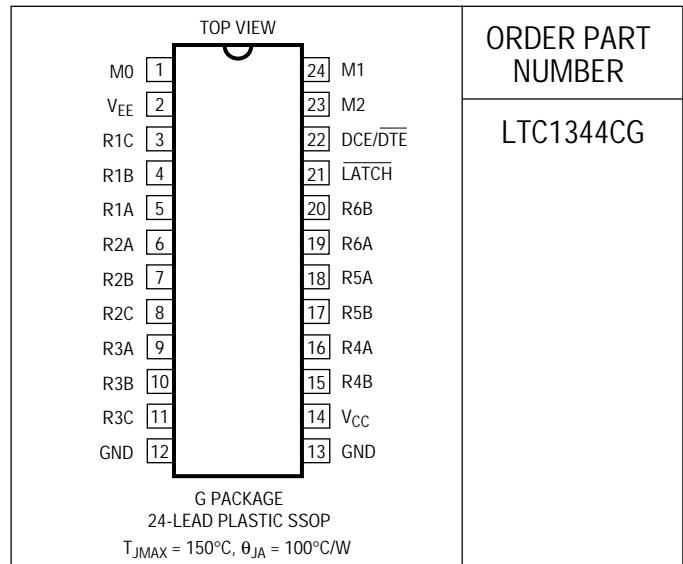

LTC1344は24ピンSSOPで供給されます。

## アプリケーション

- データ・ネットワーク

- CSUおよびDSU

- データ・ルータ

LT、LTC、LTはリニアテクノロジー社の登録商標です。

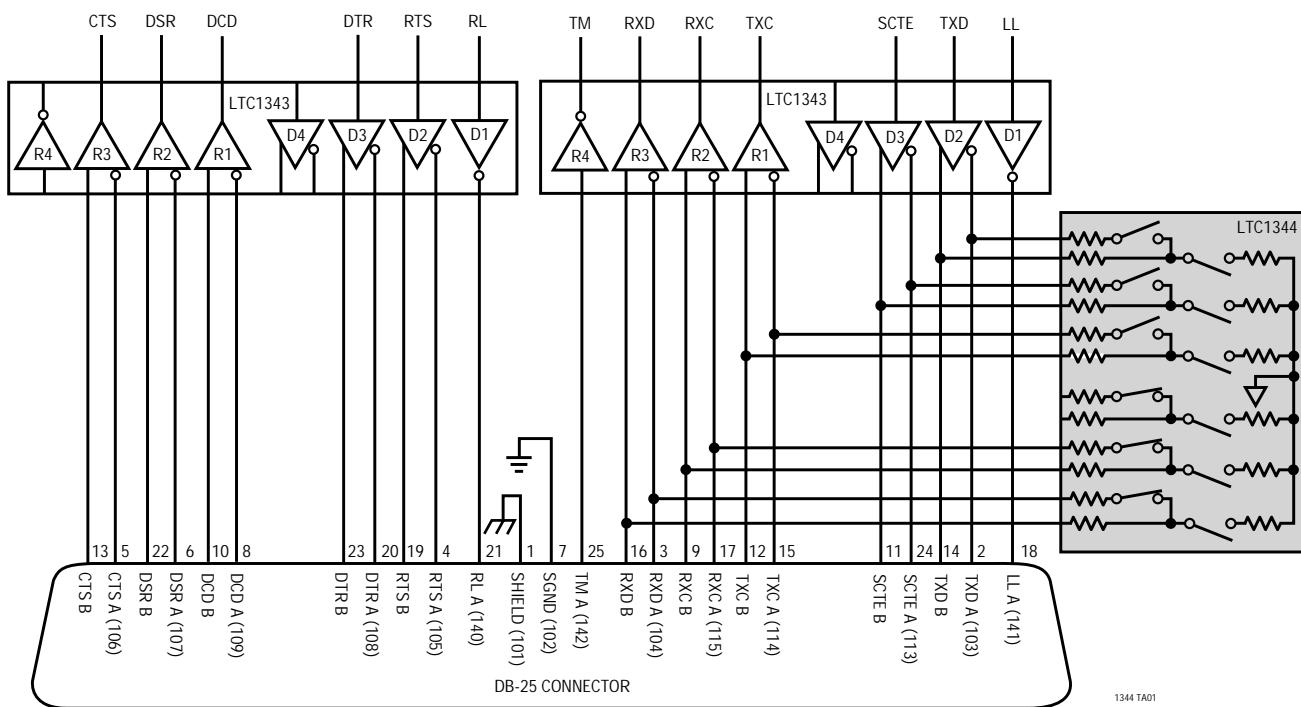

## 標準的応用例

**絶対最大定格**

(Note 1)

|                     |                                    |

|---------------------|------------------------------------|

| 正電源電圧( $V_{CC}$ )   | 7V                                 |

| 負電源電圧( $V_{EE}$ )   | - 13.2V                            |

| 入力電圧( ロジック入力 )      | $V_{EE} - 0.3V \sim V_{CC} + 0.3V$ |

| 入力電圧( 負荷入力 )        | $\pm 18V$                          |

| 動作温度範囲              | 0 ~ 70                             |

| 保存温度範囲              | - 65 ~ 150                         |

| リード温度( 半田付け、10sec ) | 300                                |

**パッケージ/発注情報**

インダストリアルおよびミリタリ・グレードに関してはお問い合わせください。

**電気的特性**

5

注記がない限り、 $V_{CC} = 5V \pm 5\%$ 、 $V_{EE} = - 5V \pm 5\%$ 、 $T_A = 0 \sim 70$  (Notes 2, 3)

| SYMBOL                 | PARAMETER                                            | CONDITIONS                                                                                         |        | MIN       | TYP        | MAX        | UNITS    |

|------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------|-----------|------------|------------|----------|

| <b>Supplies</b>        |                                                      |                                                                                                    |        |           |            |            |          |

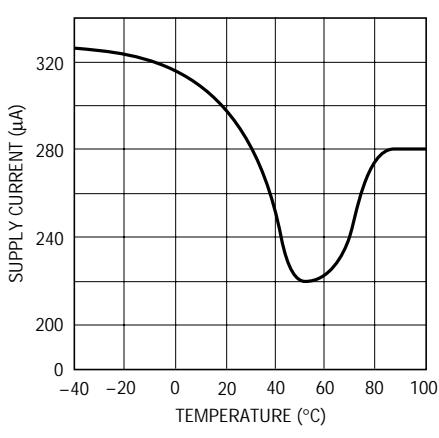

| $I_{CC}$               | Supply Current                                       | All Digital Pins = GND or $V_{CC}$                                                                 | ●      | 200       | 500        |            | $\mu A$  |

| <b>Terminator Pins</b> |                                                      |                                                                                                    |        |           |            |            |          |

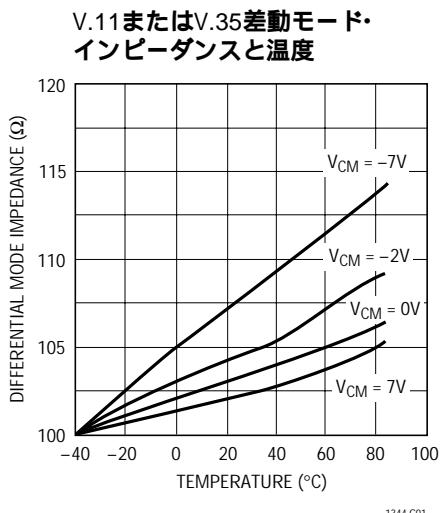

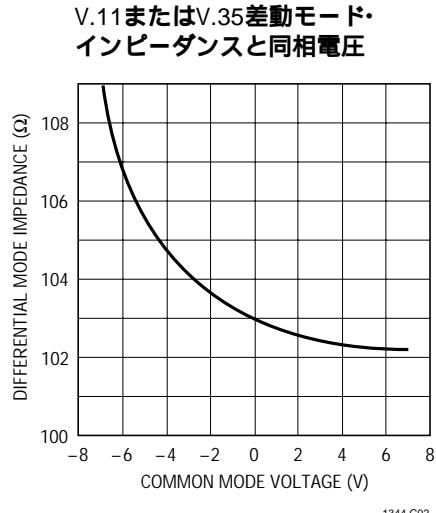

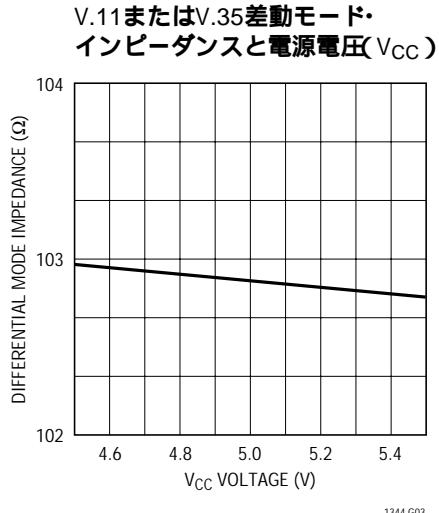

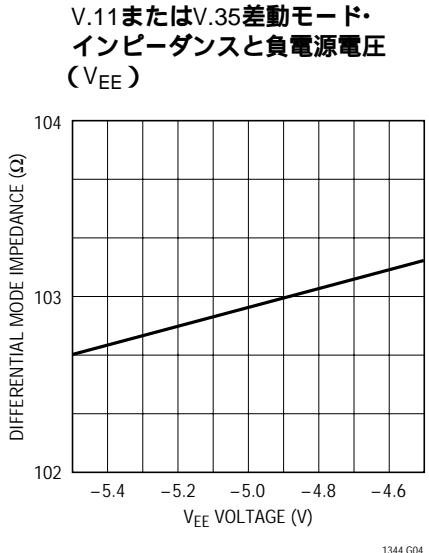

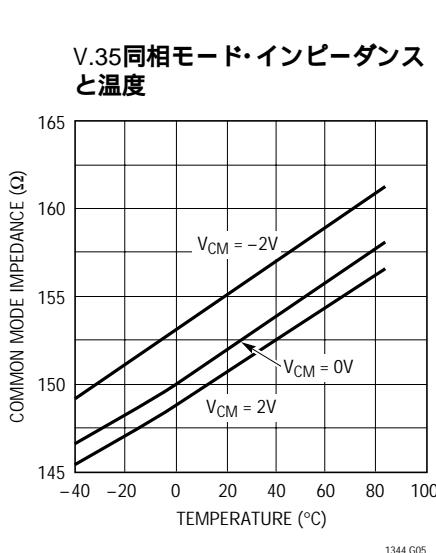

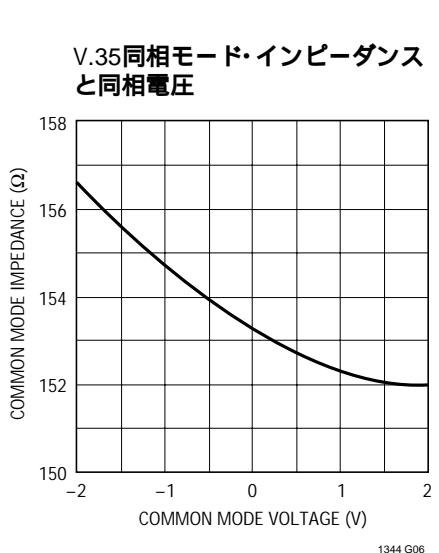

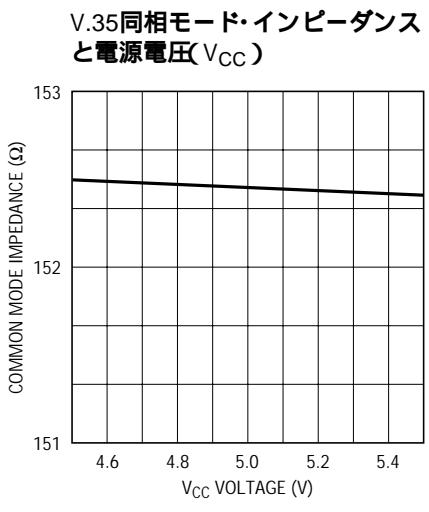

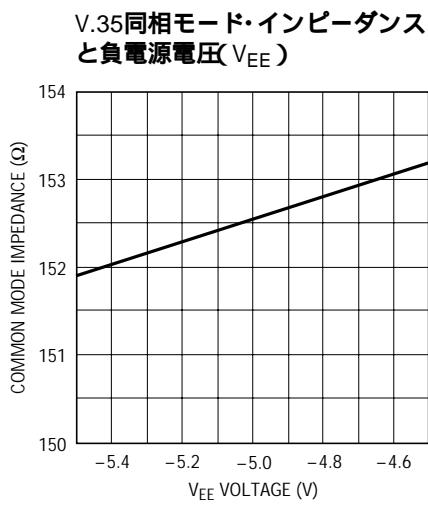

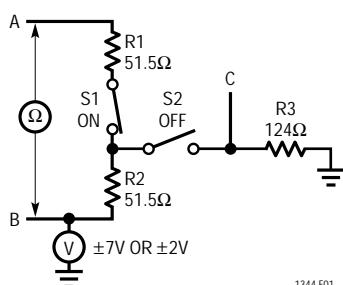

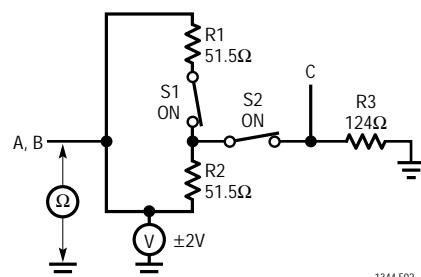

| $R_{V.35}$             | Differential Mode Impedance<br>Common Mode Impedance | All Loads (Figure 1), $-2V \leq V_{CM} \leq 2V$<br>All Loads (Figure 2), $-2V \leq V_{CM} \leq 2V$ | ●<br>● | 90<br>135 | 103<br>153 | 110<br>165 | $\Omega$ |

| $R_{V.11}$             | Differential Mode Impedance                          | All Loads (Figure 1), $-7V \leq V_{CM} \leq 7V$                                                    | ●      | 100       | 103        |            | $\Omega$ |

| $I_{LEAK}$             | High Impedance Leakage Current                       | All Loads, $-7V \leq V_{CM} \leq 7V$                                                               | ●      |           | $\pm 1$    | $\pm 50$   | $\mu A$  |

| <b>Logic Inputs</b>    |                                                      |                                                                                                    |        |           |            |            |          |

| $V_{IH}$               | Input High Voltage                                   | All Logic Input Pins                                                                               | ●      | 2         |            |            | V        |

| $V_{IL}$               | Input Low Voltage                                    | All Logic Input Pins                                                                               | ●      |           | 0.8        |            | V        |

| $I_{IN}$               | Input Current                                        | All Logic Input Pins                                                                               | ●      |           |            | $\pm 10$   | $\mu A$  |

は全動作温度範囲の規格値を意味する。

Note 1 : 絶対最大定格はそれを超えるとデバイスの寿命に影響を及ぼす値。

Note 2 : デバイスのピンに流入する電流はすべて正、デバイスのピンから流出する電流はすべて負。注記がない限り、すべての電圧はグランドを基準にする。

Note 3 : すべての標準値は  $V_{CC} = 5V$ 、 $V_{EE} = - 5V$ 、 $T_A = 25$  で得られる。

## 標準的性能特性

1344 G01

1344 G02

1344 G03

1344 G04

1344 G05

1344 G06

1344 G07

1344 G08

1344 G09

## ピン機能

M0( ピン1 ): TTLレベル・モード・セレクト入力。M0のデータはLATCHが“H”的ときにラッチされます。

V<sub>EE</sub>( ピン2 ): 負電源電圧入力。LTC1343 V<sub>EE</sub>ピンに直接接続できます。

R1Q( ピン3 ): ロード1センタタップ

R1B( ピン4 ): ロード1ノードB

R1A( ピン5 ): ロード1ノードA

R2A( ピン6 ): ロード2ノードA

R2B( ピン7 ): ロード2ノードB

R2Q( ピン8 ): ロード2センタタップ

R3A( ピン9 ): ロード3ノードA

R2B( ピン10 ): ロード2ノードB

R3Q( ピン11 ): ロード3センタタップ

GND( ピン12 ): ロード1からロード3に対するグランド接続

GND( ピン13 ): ロード4からロード6に対するグランド接続

V<sub>CC</sub>( ピン14 ): 正電源入力。4.75V ≤ V<sub>CC</sub> ≤ 5.25V。

R4B( ピン15 ): ロード4ノードB

R4A( ピン16 ): ロード4ノードA

R5B( ピン17 ): ロード5ノードB

R5A( ピン18 ): ロード5ノードA

R6A( ピン19 ): ロード6ノードA

R6B( ピン20 ): ロード6ノードB

LATCH( ピン21 ): TTLレベル・ロジック信号ラッチ入力。“L”的ときに、M0、M1、M2、およびDCE/DTEの入力バッファは簡易制御されます。“H”的ときに、ロジック・ピンはそれぞれの入力バッファにラッチされます。データ・ラッチによって、複数のI/Oポート間でセレクト・ラインを共用することができます。

DCE/DTE( ピン22 ): TTLレベル・モード・セレクト入力。“H”的ときにDCEモード、“L”的ときにDTEモードが選択されます。DCE/DTEのデータはLATCHが“H”的ときにラッチされます。

M2( ピン23 ): TTLレベル・モード・セレクト入力1。M2のデータはLATCHが“H”的ときにラッチされます。

M1( ピン24 ): TTLレベル・モード・セレクト入力2。M1のデータはLATCHが“H”的ときにラッチされます。

## テスト回路

図1. 差動V.11またはV.35インピーダンスの測定

図2. V.35同相インピーダンスの測定

## モード選択

| LTC1344<br>MODE NAME | DCE/DTE | M2 | M1 | M0 | R1   | R2   | R3   | R4   | R5   | R6   |

|----------------------|---------|----|----|----|------|------|------|------|------|------|

| V.10/RS423           | X       | 0  | 0  | 0  | Z    | Z    | Z    | Z    | Z    | Z    |

| RS530A               | 0       | 0  | 0  | 1  | Z    | Z    | Z    | V.11 | V.11 | V.11 |

|                      | 1       | 0  | 0  | 1  | Z    | Z    | Z    | V.11 | V.11 | V.11 |

| Reserved             | 0       | 0  | 1  | 0  | Z    | Z    | Z    | V.11 | V.11 | V.11 |

|                      | 1       | 0  | 1  | 0  | V.11 | V.11 | V.11 | Z    | Z    | Z    |

| X.21                 | 0       | 0  | 1  | 1  | Z    | Z    | Z    | V.11 | V.11 | V.11 |

|                      | 1       | 0  | 1  | 1  | Z    | Z    | Z    | V.11 | V.11 | V.11 |

| V.35                 | 0       | 1  | 0  | 0  | V.35 | V.35 | Z    | V.35 | V.35 | V.35 |

|                      | 1       | 1  | 0  | 0  | V.35 | V.35 | V.35 | Z    | V.35 | V.35 |

| RS530/RS449/V.36     | 0       | 1  | 0  | 1  | Z    | Z    | Z    | V.11 | V.11 | V.11 |

|                      | 1       | 1  | 0  | 1  | Z    | Z    | Z    | Z    | V.11 | V.11 |

| V.28/RS232           | X       | 1  | 1  | 0  | Z    | Z    | Z    | Z    | Z    | Z    |

| No Cable             | X       | 1  | 1  | 1  | V.11 | V.11 | V.11 | V.11 | V.11 | V.11 |

X = don't care, 0 = logic low, 1 = logic high

図3. LTC1344モード

## アプリケーション情報

### マルチプロトコル・ケーブル終端

マルチプロトコル・シリアル・インターフェースの設計者が遭遇する最も困難な問題の1つは、コネクタ・ピンを共用しながらトランスマッタとレシーバをどのように異なる電気規格に対応させるかということです。各インターフェース規格に対応するトランスマッタとレシーバをまとめて接続して、適切な回路をイネーブルすることで対応できる場合もあります。しかし、最も大きな問題が残っています。つまり、異なる規格で要求される各種ケーブル終端をどのようにして切り替えるかということです。

従来の方法は、高価なリレー付きスイッチング抵抗を用いたり、インターフェース規格が変更されるたびにユーザに終端モジュールを変更させることなどでした。ケーブル・ヘッドに終端を備えたカスタム・ケーブルを使用するか、ボード上に別々の終端が実装され、カスタム・ケーブルが信号を適切な終端につなぎます。FETによる終端の切替えは困難です。信号電圧がFETドライバの電源電圧を超えるか、あるいは電源がオフになった場合でも、FETがオフ状態を保持しなければならないためです。

LTC1344はソフトウェア・コントロールによって、ケーブル終端の切替え問題を解決しています。LTC1344はV.10( RS423 )、V.11( RS422 )、V.28( RS232 )、およびV.35電気的プロトコルに対応する終端を提供します。

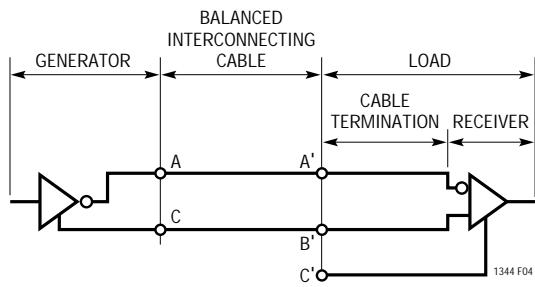

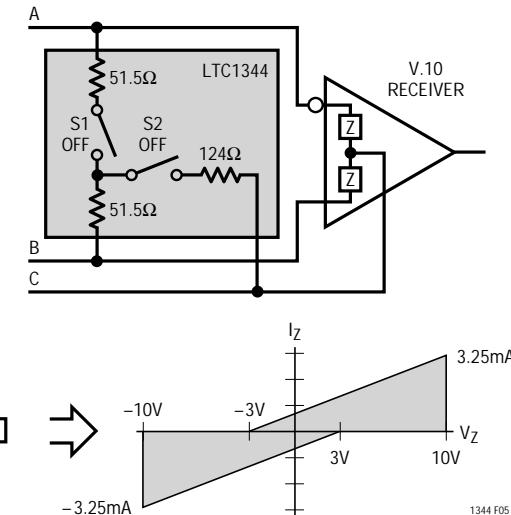

### V.10( RS423 )終端

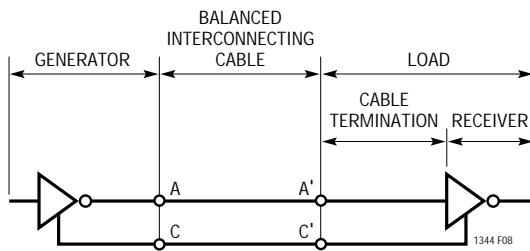

標準V.10不平衡型インターフェースを図4に示します。グランドCを備えたV.10シングル・エンド・ジェネレータ出力Aは差動レシーバに接続され、入力A'はAに、また入力B'は信号リターン・グランドCに接続されます。レシーバのグランドC'は信号リターンから分離しています。通常V.10インターフェースにはケーブル終端は必要ありませんが、レシーバ入力は図5のインピーダンス曲線に従わなければなりません。

V.10モードではスイッチS1とS2の両方がターンオフするため、ケーブル終端だけがV.10レシーバの入力インピーダンスになります。

図4. 標準V.10インターフェース

図5. LTC1344を使用したV.10インターフェース

5

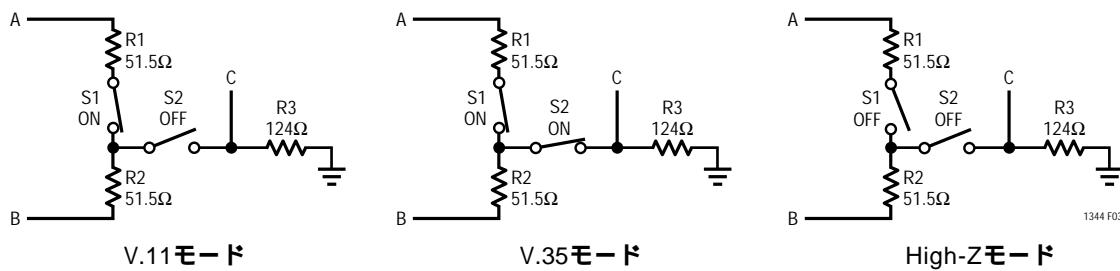

### V.11( RS422 )終端

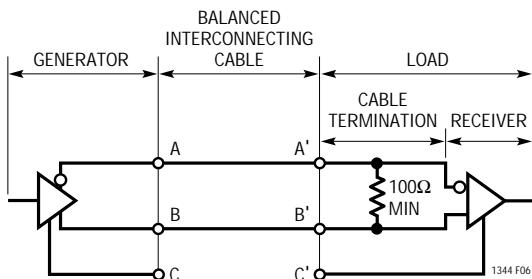

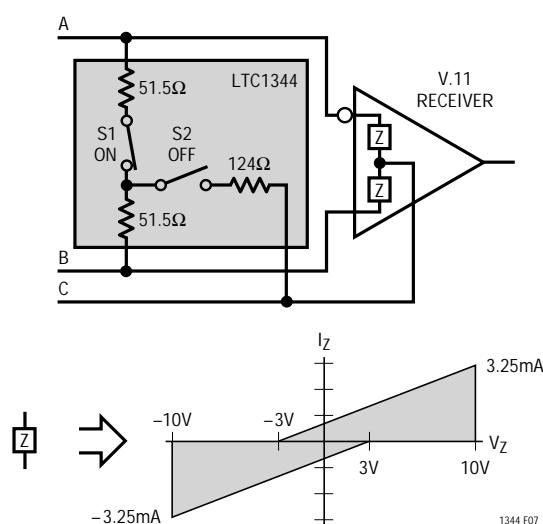

標準V.11平衡型インターフェースを図6に示します。出力AおよびBそしてグランドCを備えたV.11差動ジェネレータは、グランドC'を備えた差動レシーバに接続され、入力A'はAに、またB'はBに接続されます。V.11インターフェースは最小100  $\Omega$ を持つレシーバ・エンドに異なる終端が必要です。レシーバ入力も図7に示すインピーダンス曲線に従わなければなりません。

V.11モードではスイッチS1がターンオンし、S2がターンオフするため、ケーブルは103  $\Omega$  インピーダンスで終端されます。

## アプリケーション情報

図6. 標準V.11インターフェース

図8. 標準V.28インターフェース

図7. LTC1344を使用したV.11インターフェース

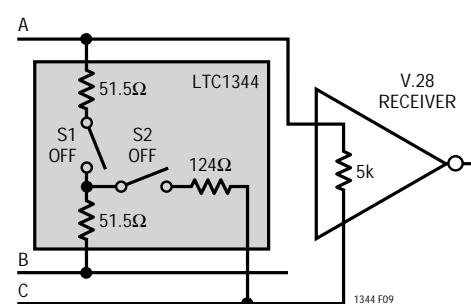

## V.28(RS232)終端

標準V.28不平衡型インターフェースを図8に示します。グランドCを備えたV.28シングル・エンデッド・ジェネレータ出力Aは、シングル・エンデッド・レシーバに接続され、入力A'はAに、またグランドC'は信号リターン・グランドを通してCに接続されます。V.28規格では接地した5k終端抵抗が必要であり、図9に示すとおり、ほとんど全部の適合レシーバに内蔵されています。終端がレシーバに内蔵されているため、LTC1344のスイッチS1とS2がターンオフします。

図9. LTC1344を使用したV.28インターフェース

## V.35終端

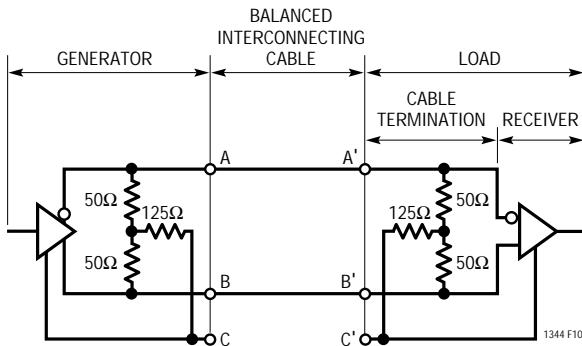

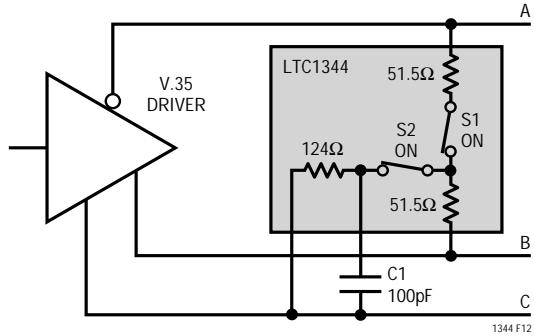

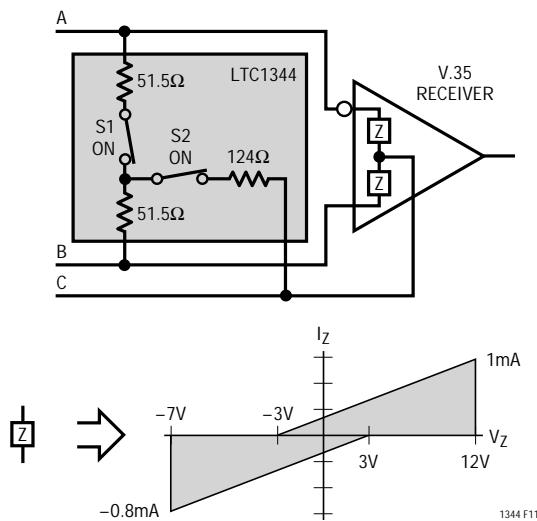

標準V.35平衡型インターフェースを図10に示します。出力AおよびB、そしてグランドCを備えたV.35差動ジェネレータが、グランドC'を備えた差動レシーバに接続され、入力A'はAに、また入力B'はBに接続されます。V.35インターフェースにはレシーバ・エンドとジェネレータ・エンドに、Tネットワーク終端が必要です。V.35モードでは、図11に示すように、LTC1344のスイッチS1とS2がターンオンします。

コネクタで測定される差動インピーダンスは、 $100 \pm 10$  Ωでなければならず、グランドC'に短絡した端子A'およびB'間のインピーダンスは $150 \pm 15$  Ωでなければなりません。V.35レシーバの入力インピーダンスは、LTC1344内のTネットワークと並列に接続され、合計インピーダンスが下限仕様を下回る可能性があります。しかし、リニアテクノロジーのすべてのV.35レシーバは、図11に示すとおり、RS485入力インピーダンス仕様に適合しており、LTC1344とともに使用する場合は、V.35仕様に適合することが保証されます。

## アプリケーション情報

図10. 標準V.35インターフェース

図12. LTC1344を使用したV.35 ドライバ

図11. LTC1344を使用したV.35 レシーバ

ジェネレータの差動インピーダンスは50 ~ 150 でなければならず、グランドCに短絡した端子AおよびB間のインピーダンスは $150 \pm 15$  でなければなりません。ジェネレータを終端するには、スイッチS1とS2を両方ともオンにし、センタ抵抗のトップサイドをピンに引き出します。これによって図12に示すとおり、外

付けコンデンサでバイパスして、同相ノイズを低減することができます。

ドライバの立上り時間と立下り時間の不整合、またはドライバ伝搬遅延のスキューリングによって、センタ終端抵抗からグランドに電流が流れ、AおよびB端子に高周波の同相スパイクが発生します。同相スパイクがEMI問題を引き起こすことがあります。多くの同相エネルギーをケーブルではなく、グランドに分流させるコンデンサC1によって軽減されます。

5

### LATCHピン

LATCHピン( 21 )によって、セレクト・ライン( M0、M1、M2、DCE/DTE )を、それぞれが専用のLATCH信号を持つ複数のLTC1344で共用することができます。LATCHピンが“ L ”に保持されると、セレクト・ライン入力バッファが簡易制御になります。LATCHピンが“ H ”にプルアップされると、セレクト・ライン入力バッファはセレクト・ピンの状態をラッチするため、セレクト・ラインの変化は、LATCHが再度“ L ”にプルダウンされるまで無視されます。ラッチ機能が使用されていない場合、LATCHピンはグランドに接続しなければなりません。

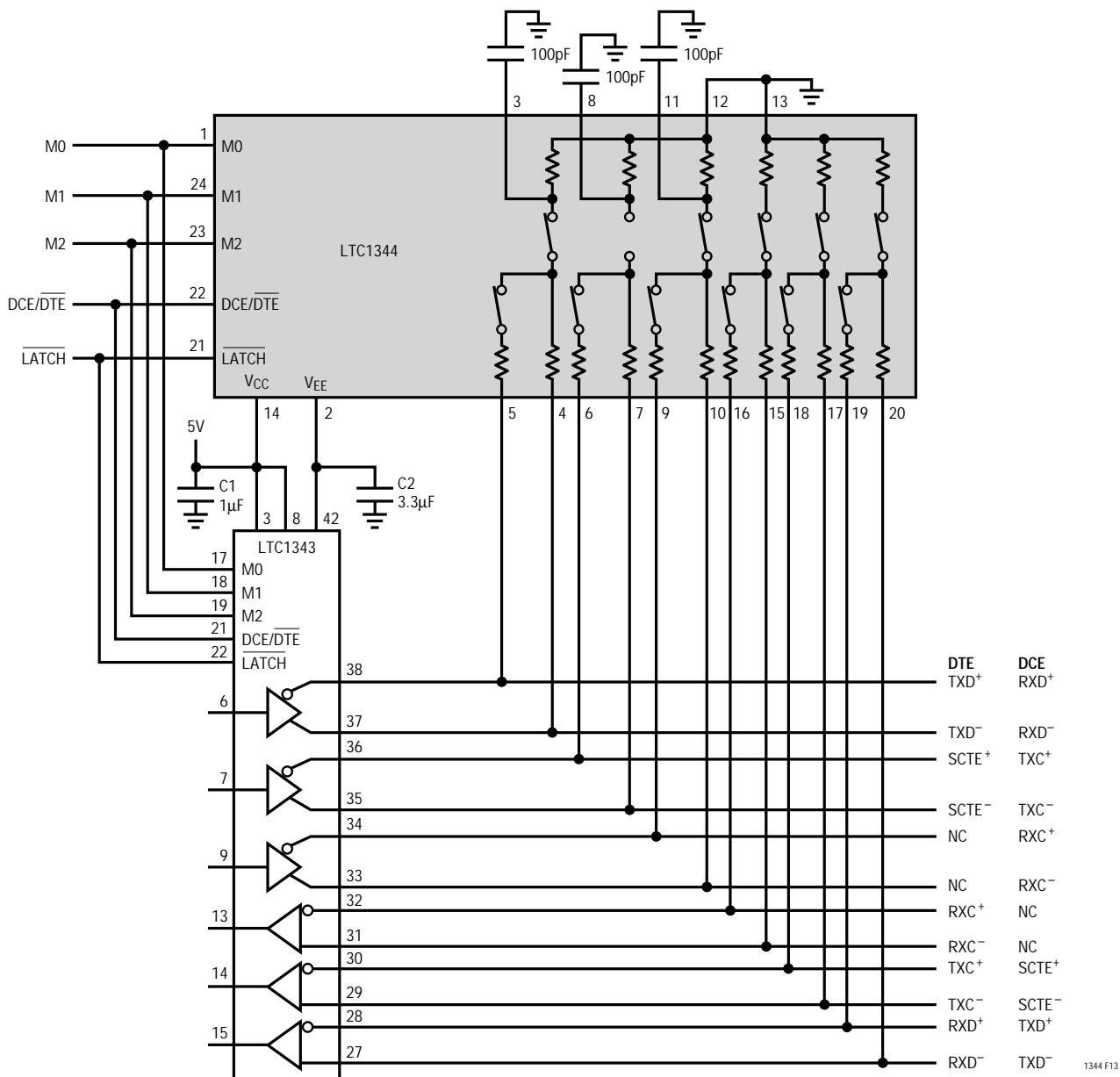

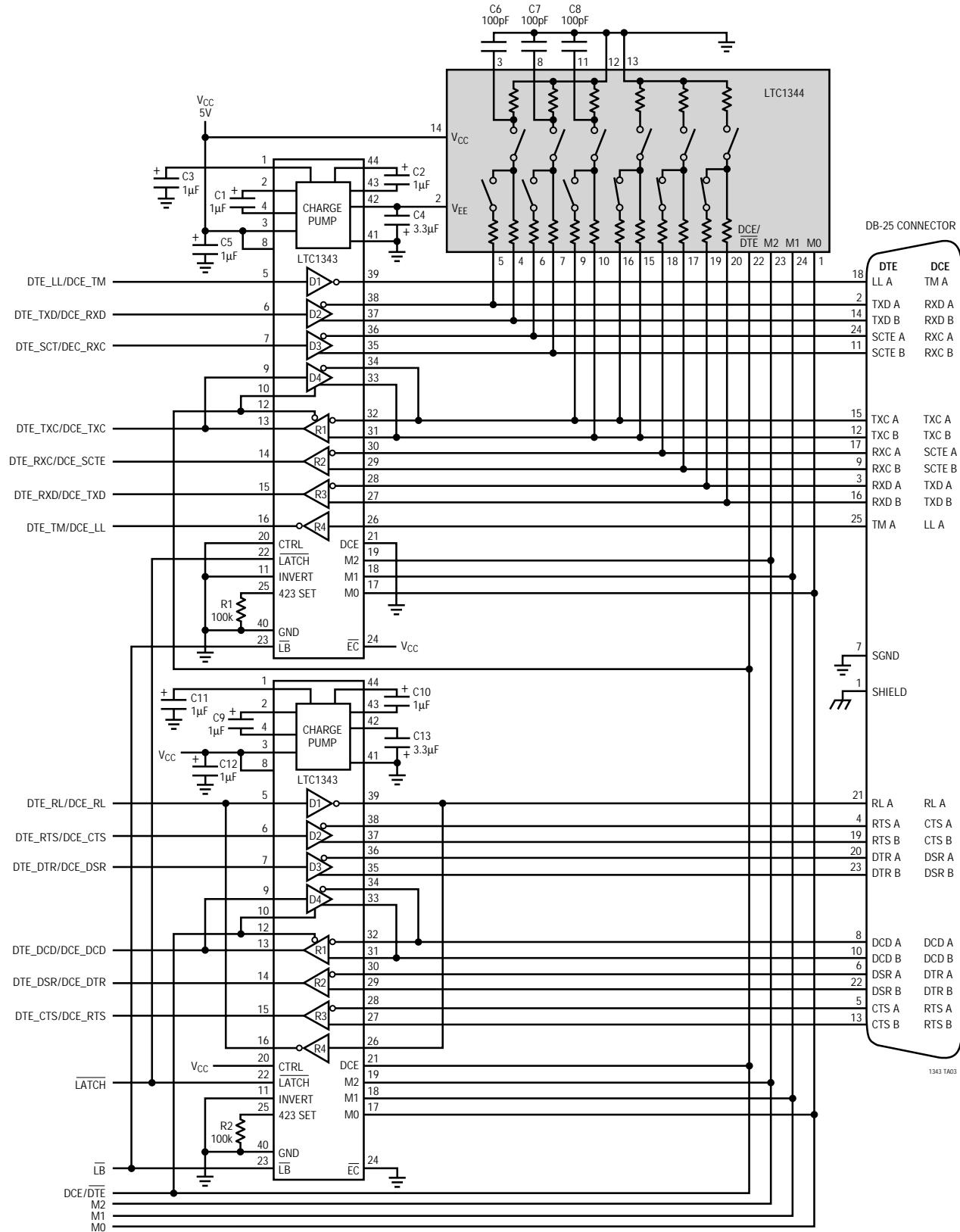

## 標準的応用例

図13にシリアル・インターフェース用のクロックおよびデータ信号を生成するLTC1343混合モード・トランシーバ・チップを使用したLTC1344の標準的応用例を示します。LTC1344のV<sub>EE</sub>電源はLTC1343のチャージポンプから生成され、セレクト・ラインM0、M1、M2、DCE、お

よりLATCHは両方のチップで共用されます。各ドライバ出力およびレシーバ入力は、LTC1344の終端ポートの1つに接続されます。したがって、各電気的プロトコルはデジタル・セレクト・ラインを使用して選択されます。

図13. LTC1344を使用した標準的応用例

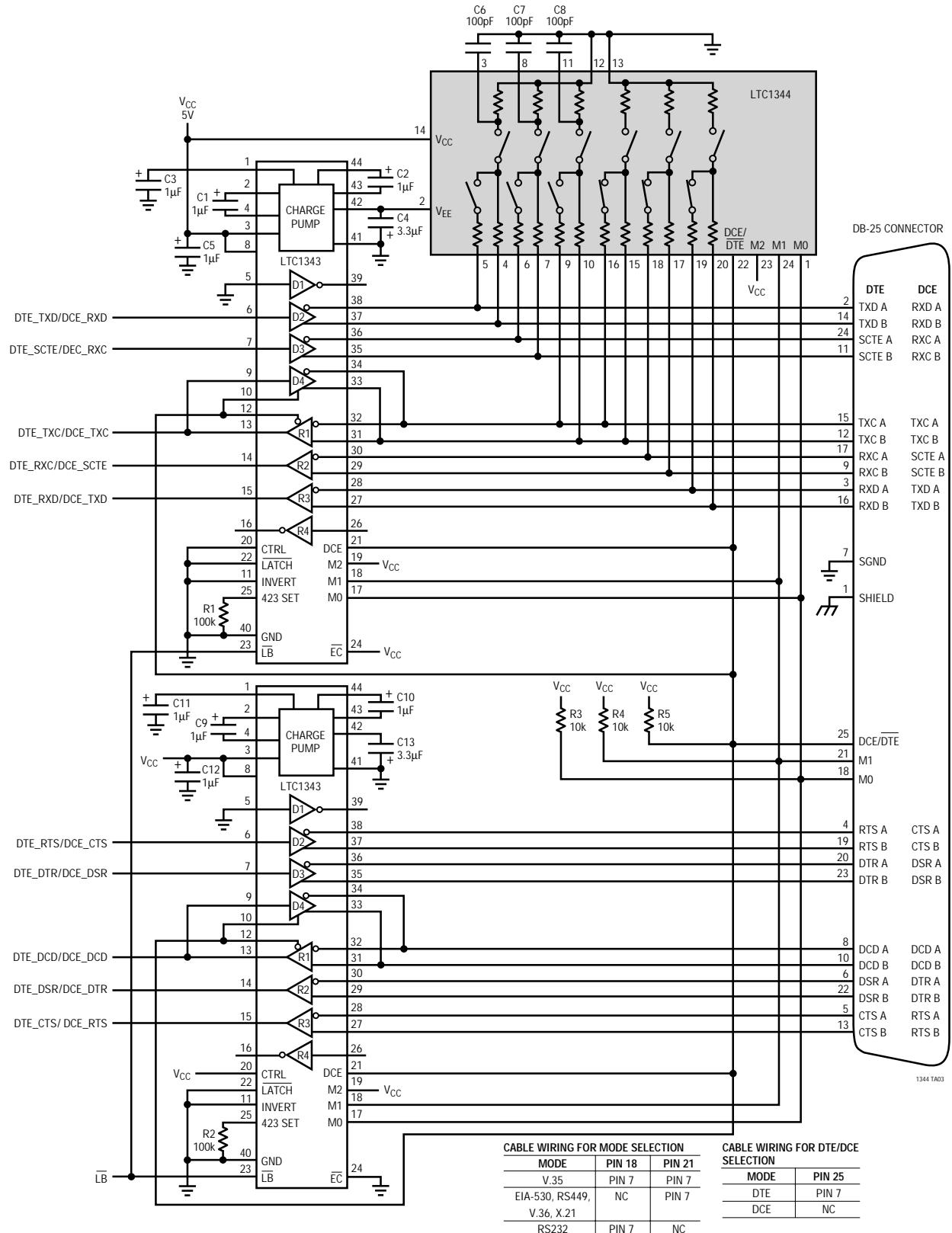

## 標準的応用例

## DB-25コネクタ付きコントローラで選択可能なマルチプロトコルDTEポート

## 標準的応用例

DB-25コネクタ付きケーブル選択可能なマルチプロトコルDTEポート

**関連製品**

| PART NUMBER | DESCRIPTION                           | COMMENTS                                    |

|-------------|---------------------------------------|---------------------------------------------|

| LTC1334     | Single Supply RS232/RS485 Transceiver | 2 RS485 Dr/Rx or 4 RS232 Dr/Rx Pairs        |

| LTC1343     | Multiprotocol Serial Transceiver      | Software Selectable Multiprotocol Interface |

| LTC1345     | Single Supply V.35 Transceiver        | 3 Dr/3 Rx for Data and CLK Signals          |

| LTC1346A    | Dual Supply V.35 Transceiver          | 3 Dr/3 Rx for Data and CLK Signals          |