## 特長

- 耐圧60Vのフローティング・トップ・ドライバ・スイッチ

- トップNチャンネルMOSFETのゲートを負荷高電圧源により高くドライブ可能

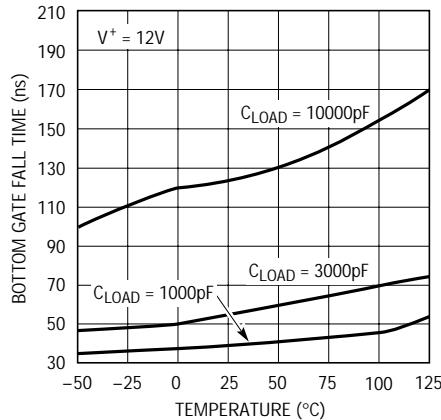

- 10,000pF ドライブ時の遷移時間 : 180ns

- シュートスルーを防止する適応型非オーバラップ・ゲート・ドライブ

- 高デューティ・サイクルでのトップ・ドライブ保護

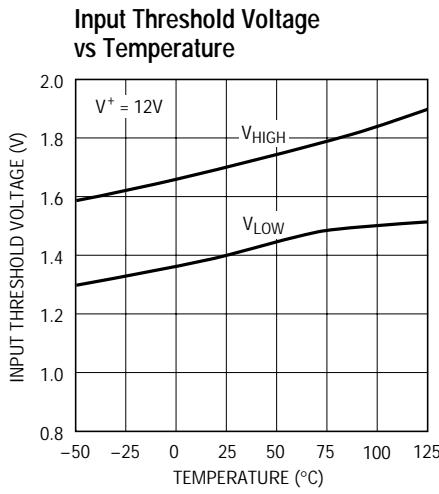

- TTL/CMOS入力レベル

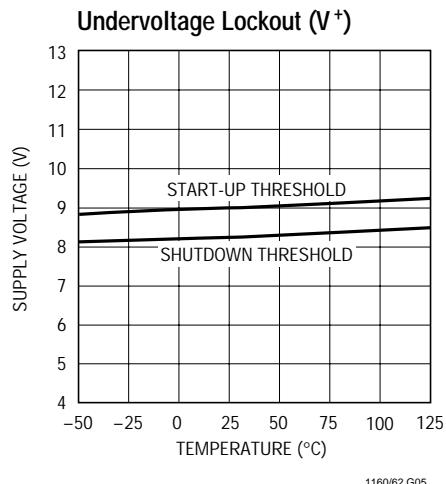

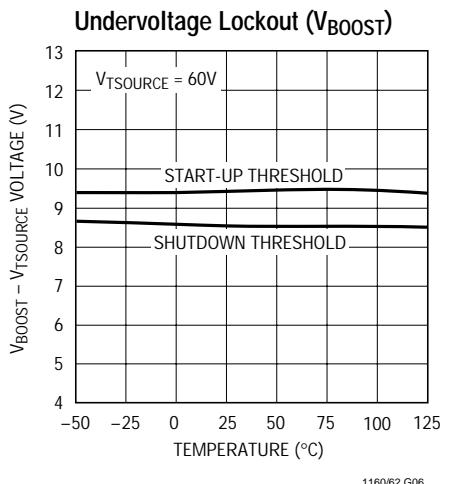

- ヒステリシスを備えた低電圧ロックアウト

- 10Vから15Vの電源電圧で動作

- 独立したトップおよびボトム・ドライブ・ピン

## アプリケーション

- 高電流誘導性負荷のPWM

- 半波ブリッジおよび全波ブリッジ・モータ制御

- 同期式ステップダウン・スイッチング・レギュレータ

- 3相ブラシレス・モータ駆動

- 高電流トランステューサ・ドライバ

- D級パワー・アンプ

## 概要

LT<sup>®</sup>1160/LT1162は経済的な半波/全波ブリッジNチャンネル・パワーMOSFETドライバです。フローティング・ドライバは、トップ・サイドNチャンネル・パワーMOSFETを、最大60V(絶対最大値)の高電圧(HV)レベルまでドライブすることができます。

内部ロジックは入力によって、半波ブリッジのパワーMOSFETが同時にターンオンするのを防止します。ユニークなシュートスルー電流に対する適応型保護機能によって、2つのMOSFETに対するすべての整合要求が不要になります。これによって高効率モータ制御およびスイッチング・レギュレータ・システムの設計が大幅に簡素化されます。

低電源電圧または低起動時電圧条件では、低電圧ロックアウトがドライバ出力をアクティブに“L”にプルダウンし、パワーMOSFETが不完全導通するのを防止します。0.5Vのヒステリシスをもたせてあるため、電源が緩やかに変化しても、高信頼性動作が可能です。

LT1162はLT1160のデュアル・バージョンであり、24ピンPDIPまたは24ピンSOワイド・パッケージで供給されます。

**LT**、LTC、LTはリニアテクノロジー社の登録商標です。

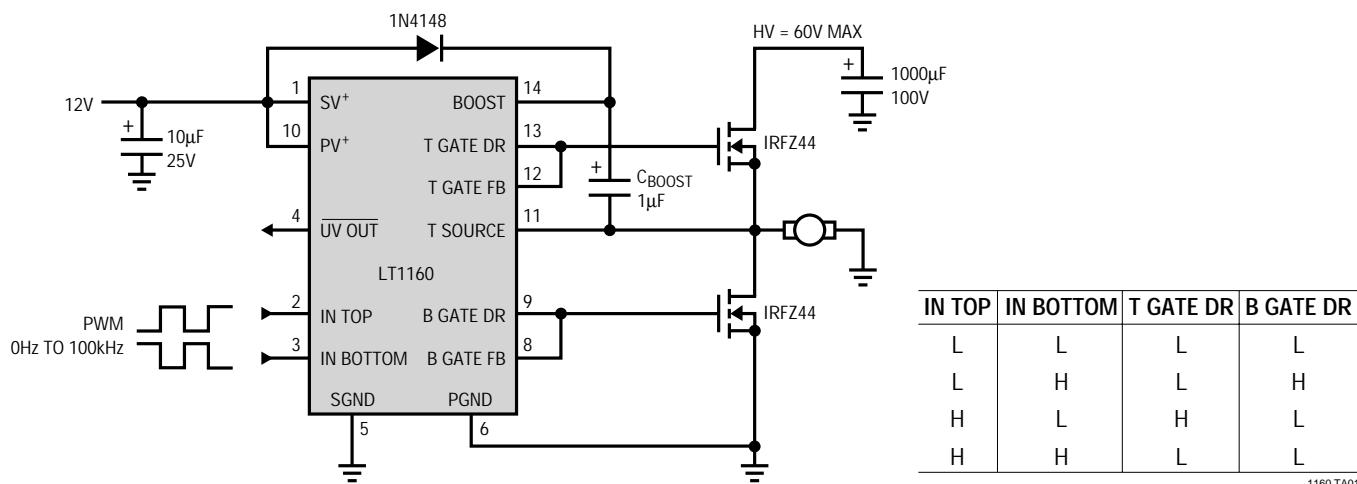

## TYPICAL APPLICATION

## ABSOLUTE MAXIMUM RATINGS

|                                     |                                |

|-------------------------------------|--------------------------------|

| Supply Voltage (Note 1) .....       | 20V                            |

| Boost Voltage .....                 | 75V                            |

| Peak Output Currents (< 10μs) ..... | 1.5A                           |

| Input Pin Voltages .....            | -0.3V to V <sup>+</sup> + 0.3V |

| Top Source Voltage .....            | -5V to 60V                     |

| Boost to Source Voltage .....       | -0.3V to 20V                   |

|                                            |                |

|--------------------------------------------|----------------|

| Operating Temperature Range                |                |

| Commercial .....                           | 0°C to 70°C    |

| Industrial .....                           | -40°C to 85°C  |

| Junction Temperature (Note 2) .....        | 125°C          |

| Storage Temperature Range .....            | -65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) ..... | 300°C          |

## PACKAGE/ORDER INFORMATION

| TOP VIEW  | ORDER PART NUMBER | TOP VIEW                                                 |   |       |                 |          |                                                          |                   |                         |             |             |    |             | ORDER PART NUMBER |

|-----------|-------------------|----------------------------------------------------------|---|-------|-----------------|----------|----------------------------------------------------------|-------------------|-------------------------|-------------|-------------|----|-------------|-------------------|

|           |                   | SV <sup>+</sup> A                                        | 1 | BOOST | 14              | IN TOP A | 2                                                        | 24                | BOOST A                 | LT1162CN    | IN BOTTOM A | 3  | 23          | T GATE DR A       |

| IN TOP    | LT1160CN          | IN TOP                                                   | 2 | 13    | T GATE DR       | 13       | 22                                                       | T GATE FB A       | LT1162CSW               | UV OUT A    | 4           | 21 | T SOURCE A  |                   |

| IN BOTTOM | LT1160CS          | UV OUT                                                   | 4 | 12    | T GATE FB       | 12       | 20                                                       | PV <sup>+</sup> A | LT1162IN                | GND A       | 5           | 19 | B GATE DR A |                   |

| UV OUT    | LT1160IN          | SGND                                                     | 5 | 11    | T SOURCE        | 11       | 18                                                       | BOOST B           | LT1162ISW               | B GATE FB A | 6           | 17 | T GATE DR B |                   |

| SGND      | LT1160IS          | P GND                                                    | 6 | 10    | PV <sup>+</sup> | 10       | 16                                                       | T GATE FB B       |                         | GND B       | 11          | 15 | T SOURCE B  |                   |

| NC        |                   | PGND                                                     | 6 | 9     | B GATE DR       | 9        | 14                                                       | PV <sup>+</sup> B |                         | B GATE FB B | 12          | 13 | B GATE DR B |                   |

|           |                   |                                                          | 7 | 8     | B GATE FB       | 8        |                                                          |                   |                         |             |             |    |             |                   |

|           |                   | N PACKAGE                                                |   |       |                 |          | N PACKAGE                                                |                   | SW PACKAGE              |             |             |    |             |                   |

|           |                   | 14-LEAD PDIP                                             |   |       |                 |          | 24-LEAD PDIP                                             |                   | 24-LEAD PLASTIC SO WIDE |             |             |    |             |                   |

|           |                   | S PACKAGE                                                |   |       |                 |          |                                                          |                   |                         |             |             |    |             |                   |

|           |                   | 14-LEAD PLASTIC SO                                       |   |       |                 |          |                                                          |                   |                         |             |             |    |             |                   |

|           |                   | T <sub>JMAX</sub> = 125°C, θ <sub>JA</sub> = 70°C/W (N)  |   |       |                 |          | T <sub>JMAX</sub> = 125°C, θ <sub>JA</sub> = 58°C/W (N)  |                   |                         |             |             |    |             |                   |

|           |                   | T <sub>JMAX</sub> = 125°C, θ <sub>JA</sub> = 110°C/W (S) |   |       |                 |          | T <sub>JMAX</sub> = 125°C, θ <sub>JA</sub> = 80°C/W (SW) |                   |                         |             |             |    |             |                   |

Consult factory for Military grade parts.

## ELECTRICAL CHARACTERISTICS

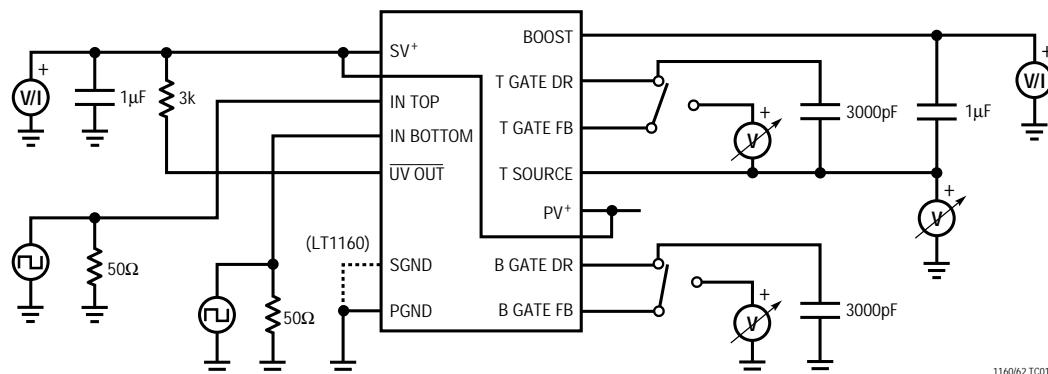

Test Circuit, T<sub>A</sub> = 25°C, V<sup>+</sup> = V<sub>BOOST</sub> = 12V, V<sub>TSOURCE</sub> = 0V, C<sub>GATE</sub> = 3000pF.

Gate Feedback pins connected to Gate Drive pins, unless otherwise specified.

| SYMBOL                        | PARAMETER                                          | CONDITIONS                                                                                                                    | MIN | TYP | MAX | UNITS |

|-------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| I <sub>S</sub>                | DC Supply Current (Note 3)                         | V <sup>+</sup> = 15V, V <sub>INTOP</sub> = 0.8V, V <sub>INBOTTOM</sub> = 2V                                                   | 7   | 11  | 15  | mA    |

|                               |                                                    | V <sup>+</sup> = 15V, V <sub>INTOP</sub> = 2V, V <sub>INBOTTOM</sub> = 0.8V                                                   | 7   | 10  | 15  | mA    |

|                               |                                                    | V <sup>+</sup> = 15V, V <sub>INTOP</sub> = 0.8V, V <sub>INBOTTOM</sub> = 0.8V                                                 | 7   | 11  | 15  | mA    |

| I <sub>BOOST</sub>            | Boost Current (Note 3)                             | V <sup>+</sup> = 15V, V <sub>TSOURCE</sub> = 60V, V <sub>BOOST</sub> = 75V, V <sub>INTOP</sub> = V <sub>INBOTTOM</sub> = 0.8V | 3   | 4.5 | 6   | mA    |

| V <sub>IL</sub>               | Input Logic Low                                    |                                                                                                                               | ●   | 1.4 | 0.8 | V     |

| V <sub>IH</sub>               | Input Logic High                                   |                                                                                                                               | ●   | 2   | 1.7 | V     |

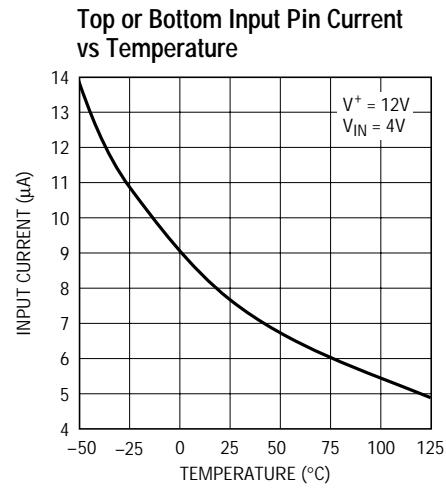

| I <sub>IN</sub>               | Input Current                                      | V <sub>INTOP</sub> = V <sub>INBOTTOM</sub> = 4V                                                                               | ●   | 7   | 25  | μA    |

| V <sup>+</sup> <sub>UVH</sub> | V <sup>+</sup> Undervoltage Start-Up Threshold     |                                                                                                                               |     | 8.4 | 8.9 | 9.4   |

| V <sup>+</sup> <sub>UVL</sub> | V <sup>+</sup> Undervoltage Shutdown Threshold     |                                                                                                                               |     | 7.8 | 8.3 | 8.8   |

| V <sub>BUVH</sub>             | V <sub>BOOST</sub> Undervoltage Start-Up Threshold | V <sub>TSOURCE</sub> = 60V (V <sub>BOOST</sub> - V <sub>TSOURCE</sub> )                                                       |     | 8.8 | 9.3 | 9.8   |

| V <sub>BULV</sub>             | V <sub>BOOST</sub> Undervoltage Shutdown Threshold | V <sub>TSOURCE</sub> = 60V (V <sub>BOOST</sub> - V <sub>TSOURCE</sub> )                                                       |     | 8.2 | 8.7 | 9.2   |

## ELECTRICAL CHARACTERISTICS

Test Circuit,  $T_A = 25^\circ\text{C}$ ,  $V^+ = V_{\text{BOOST}} = 12\text{V}$ ,  $V_{\text{TSOURCE}} = 0\text{V}$ ,  $C_{\text{GATE}} = 3000\text{pF}$ .

Gate Feedback pins connected to Gate Drive pins, unless otherwise specified.

| SYMBOL      | PARAMETER                      | CONDITIONS                                                                                        | MIN | TYP | MAX  | UNITS         |

|-------------|--------------------------------|---------------------------------------------------------------------------------------------------|-----|-----|------|---------------|

| $I_{UVOUT}$ | Undervoltage Output Leakage    | $V^+ = 15\text{V}$                                                                                | ●   | 0.1 | 5    | $\mu\text{A}$ |

| $V_{UVOUT}$ | Undervoltage Output Saturation | $V^+ = 7.5\text{V}$ , $I_{UVOUT} = 2.5\text{mA}$                                                  | ●   | 0.2 | 0.4  | V             |

| $V_{OH}$    | Top Gate ON Voltage            | $V_{INTOP} = 2\text{V}$ , $V_{INBOTTOM} = 0.8\text{V}$                                            | ●   | 11  | 11.3 | 12            |

|             | Bottom Gate ON Voltage         | $V_{INTOP} = 0.8\text{V}$ , $V_{INBOTTOM} = 2\text{V}$                                            | ●   | 11  | 11.3 | 12            |

| $V_{OL}$    | Top Gate OFF Voltage           | $V_{INTOP} = 0.8\text{V}$ , $V_{INBOTTOM} = 2\text{V}$                                            | ●   | 0.4 | 0.7  | V             |

|             | Bottom Gate OFF Voltage        | $V_{INTOP} = 2\text{V}$ , $V_{INBOTTOM} = 0.8\text{V}$                                            | ●   | 0.4 | 0.7  | V             |

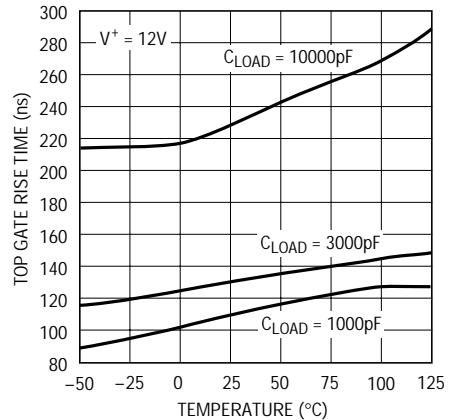

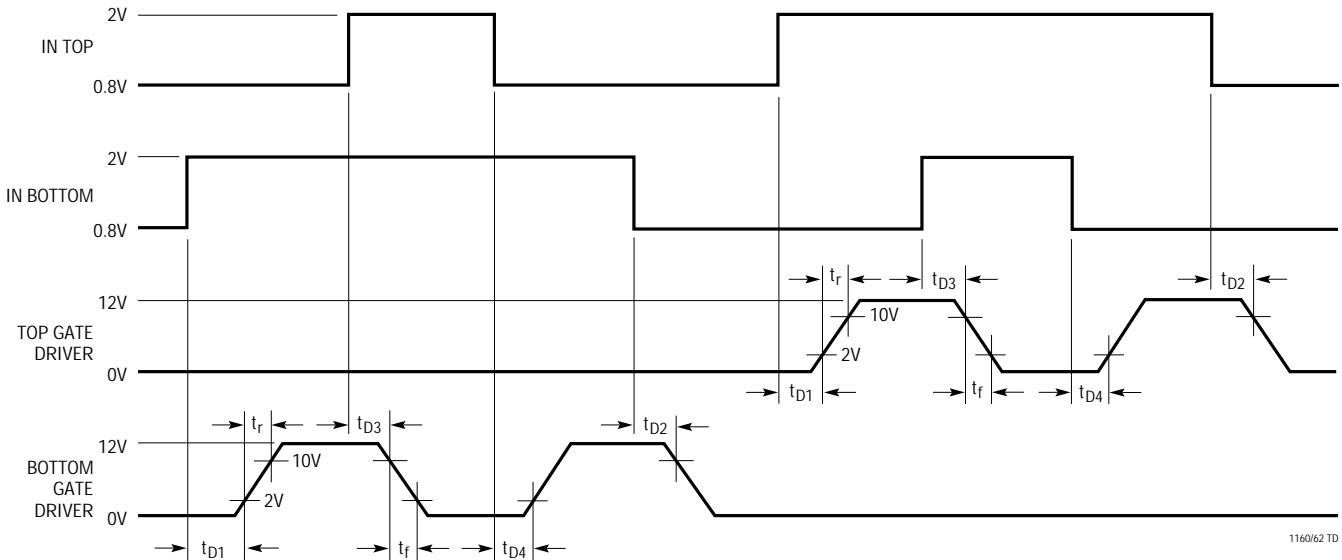

| $t_r$       | Top Gate Rise Time             | $V_{INTOP}$ (+) Transition, $V_{INBOTTOM} = 0.8\text{V}$ ,<br>Measured at $V_{TGATE}$ DR (Note 4) | ●   | 130 | 200  | ns            |

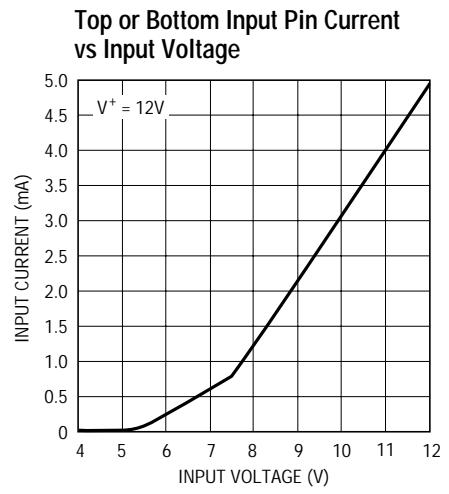

|             | Bottom Gate Rise Time          | $V_{INBOTTOM}$ (+) Transition, $V_{INTOP} = 0.8\text{V}$ ,<br>Measured at $V_{BGATE}$ DR (Note 4) | ●   | 90  | 200  | ns            |

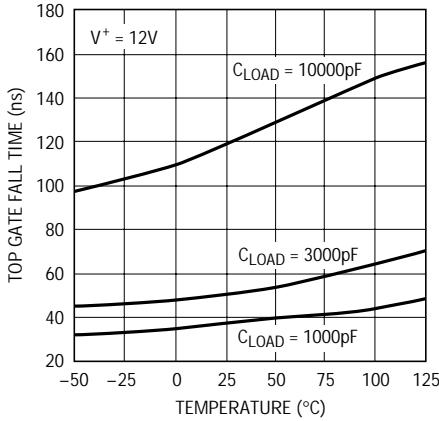

| $t_f$       | Top Gate Fall Time             | $V_{INTOP}$ (-) Transition, $V_{INBOTTOM} = 0.8\text{V}$ ,<br>Measured at $V_{TGATE}$ DR (Note 4) | ●   | 60  | 140  | ns            |

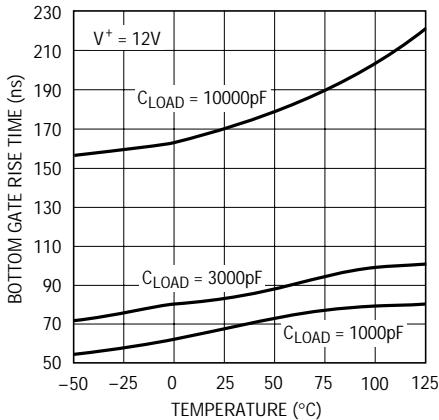

|             | Bottom Gate Fall Time          | $V_{INBOTTOM}$ (-) Transition, $V_{INTOP} = 0.8\text{V}$ ,<br>Measured at $V_{BGATE}$ DR (Note 4) | ●   | 60  | 140  | ns            |

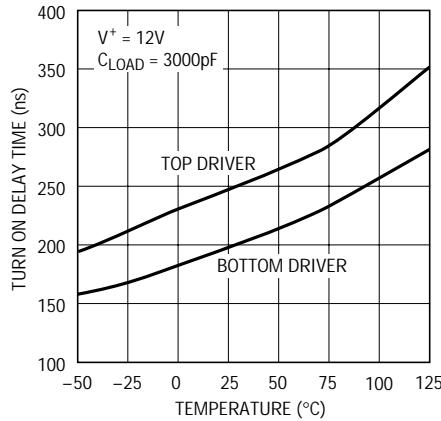

| $t_{D1}$    | Top Gate Turn-On Delay         | $V_{INTOP}$ (+) Transition, $V_{INBOTTOM} = 0.8\text{V}$ ,<br>Measured at $V_{TGATE}$ DR (Note 4) | ●   | 250 | 500  | ns            |

|             | Bottom Gate Turn-On Delay      | $V_{INBOTTOM}$ (+) Transition, $V_{INTOP} = 0.8\text{V}$ ,<br>Measured at $V_{BGATE}$ DR (Note 4) | ●   | 200 | 400  | ns            |

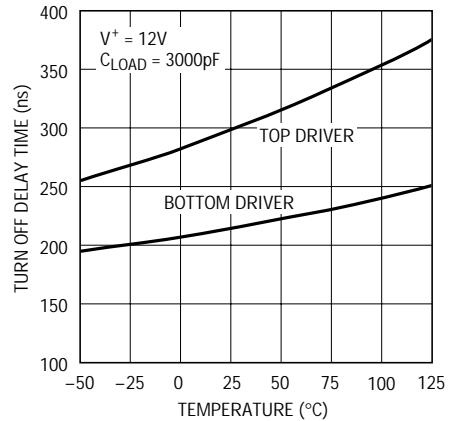

| $t_{D2}$    | Top Gate Turn-Off Delay        | $V_{INTOP}$ (-) Transition, $V_{INBOTTOM} = 0.8\text{V}$ ,<br>Measured at $V_{TGATE}$ DR (Note 4) | ●   | 300 | 600  | ns            |

|             | Bottom Gate Turn-Off Delay     | $V_{INBOTTOM}$ (-) Transition, $V_{INTOP} = 0.8\text{V}$ ,<br>Measured at $V_{BGATE}$ DR (Note 4) | ●   | 200 | 400  | ns            |

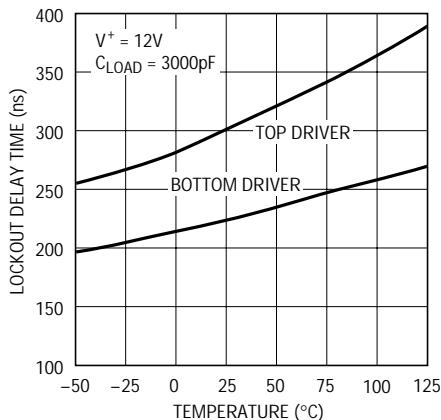

| $t_{D3}$    | Top Gate Lockout Delay         | $V_{INBOTTOM}$ (+) Transition, $V_{INTOP} = 2\text{V}$ ,<br>Measured at $V_{TGATE}$ DR (Note 4)   | ●   | 300 | 600  | ns            |

|             | Bottom Gate Lockout Delay      | $V_{INTOP}$ (+) Transition, $V_{INBOTTOM} = 2\text{V}$ ,<br>Measured at $V_{BGATE}$ DR (Note 4)   | ●   | 250 | 500  | ns            |

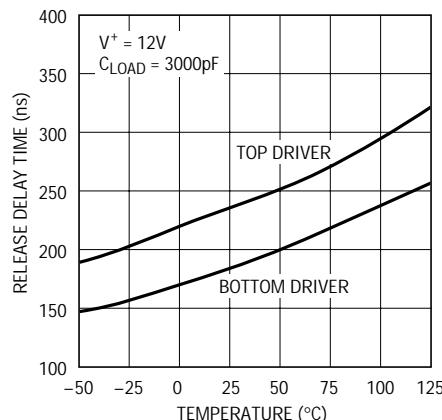

| $t_{D4}$    | Top Gate Release Delay         | $V_{INBOTTOM}$ (-) Transition, $V_{INTOP} = 2\text{V}$ ,<br>Measured at $V_{TGATE}$ DR (Note 4)   | ●   | 250 | 500  | ns            |

|             | Bottom Gate Release Delay      | $V_{INTOP}$ (-) Transition, $V_{INBOTTOM} = 2\text{V}$ ,<br>Measured at $V_{BGATE}$ DR (Note 4)   | ●   | 200 | 400  | ns            |

The ● denotes specifications which apply over the full operating temperature range.

**Note 1:** For the LT1160, Pins 1, 10 should be connected together. For the LT1162, Pins 1, 7, 14, 20 should be connected together.

**Note 2:**  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formulas:

$$\text{LT1160CN/LT1160IN: } T_J = T_A + (P_D)(70^\circ\text{C}/\text{W})$$

$$\text{LT1160CS/LT1160IS: } T_J = T_A + (P_D)(110^\circ\text{C}/\text{W})$$

$$\text{LT1162CN/LT1162IN: } T_J = T_A + (P_D)(58^\circ\text{C}/\text{W})$$

$$\text{LT1162CS/LT1162IS: } T_J = T_A + (P_D)(80^\circ\text{C}/\text{W})$$

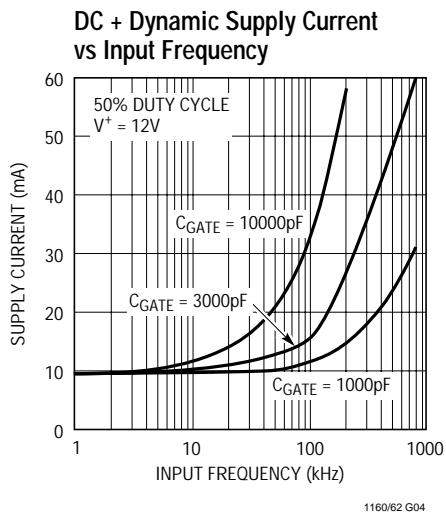

**Note 3:**  $I_S$  is the sum of currents through  $SV^+$ ,  $PV^+$  and Boost pins.  $I_{\text{BOOST}}$  is the current through the Boost pin. Dynamic supply current is higher due to the gate charge being delivered at the switching frequency. See Typical Performance Characteristics and Applications Information sections. The LT1160 = 1/2 LT1162.

**Note 4:** See Timing Diagram. Gate rise times are measured from 2V to 10V and fall times are measured from 10V to 2V. Delay times are measured from the input transition to when the gate voltage has risen to 2V or decreased to 10V.

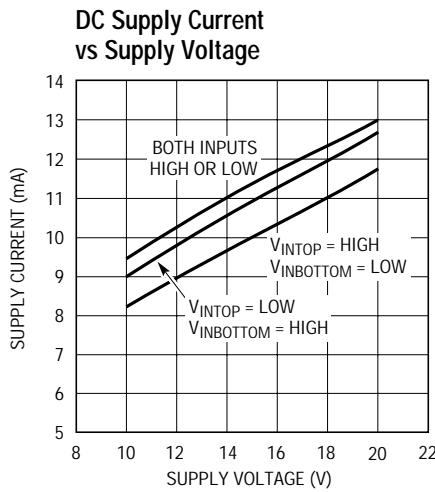

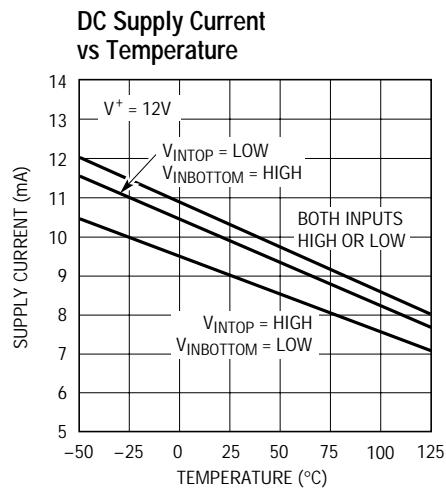

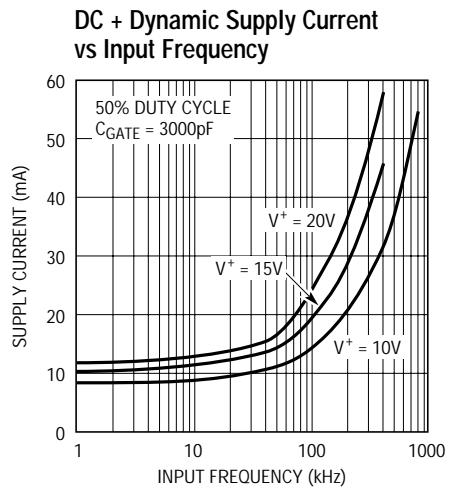

## TYPICAL PERFORMANCE CHARACTERISTICS (LT1160 or 1/2 LT1162)

1160/62 G01

1160/62 G02

1160/62 G03

1160/62 G04

1160/62 G05

1160/62 G06

1160/62 G07

1160/62 G08

1160/62 G09

## TYPICAL PERFORMANCE CHARACTERISTICS (LT1160 or 1/2 LT1162)

**Bottom Gate Rise Time vs Temperature**

1160/62 G10

**Bottom Gate Fall Time vs Temperature**

1160/62 G11

**Top Gate Rise Time vs Temperature**

1160/62 G12

**Top Gate Fall Time vs Temperature**

1160/62 G13

**Turn-On Delay Time vs Temperature**

1160/62 G14

**Turn-Off Delay Time vs Temperature**

1160/62 G15

**Lockout Delay Time vs Temperature**

1160/62 G16

**Release Delay Time vs Temperature**

1160/62 G17

## ピン機能

### LT1160

SV<sup>+</sup>( ピン1 ): メイン信号電源。信号グランド・ピン5に近づけてデカップリングしなければなりません。

IN TOP( ピン2 ): トップ・ドライバ入力。ピン2はピン3が“H”のときにディスエーブルされます。5V内部クランプの前段に3k の入力抵抗を接続すると、入力トランジスタの飽和が防止されます。

IN BOTTOM( ピン3 ): ボトム・ドライバ入力。ピン3はピン2が“H”的ときにディスエーブルされます。5V内部クランプの前段に3k の入力抵抗を接続すると、入力トランジスタの飽和が防止されます。

UV OUT( ピン4 ): 低電圧出力。V<sup>+</sup>が低電圧スレッショルドより低下するとターンオンするオープン・コレクタNPNです。

SGND( ピン5 ): 小信号グランド。別のグランドやシステム・グランドから独立していかなければなりません。

PGND( ピン6 ): ボトムドライバのパワーグランド。ボトムNチャンネルMOSFETのソースと接続します。

B GATE FB( ピン8 ): ボトムゲート帰還。ボトムパワーMOSFETゲートに直接接続しなければなりません。トップMOSFETは、ピン8が放電し2.5Vより低くなるまでターンオンしません。

B GATE DR( ピン9 ): ボトムゲート・ドライブ。ボトムMOSFETに対する高電流ドライブ点です。ゲート抵抗を使用する場合、それをピン9およびMOSFETゲート間に挿入します。

PV<sup>+</sup>( ピン10 ): ボトムドライバ電源。ピン1と同じ電源に接続しなければなりません。

T SOURCE( ピン11 ): トップ・ドライバのリターン。トップMOSFETのソースおよびブートストラップ・コンデンサの下側に接続します。

T GATE FB( ピン12 ): トップ・ゲート帰還。トップ・パワーMOSFETゲートに直接接続しなければなりません。ボトムMOSFETは、V<sub>12</sub> - V<sub>11</sub>が放電し2.9Vより低くなるまでターンオンしません。

T GATE DR( ピン13 ): トップ・ゲート・ドライブ。トップMOSFETに対する高電流ドライブ点です。ゲート抵抗を使用する場合、それをピン13およびMOSFETのゲート間に挿入します。

BOOST( ピン14 ): トップ・ドライバ電源。ブートストラップ・コンデンサの上側に接続します。

### LT1162

SV<sup>+</sup>( ピン1,7 ): 主信号電源。グランド・ピン5および11に近づけてデカップリングしなければなりません。

IN TOP( ピン2,8 ): トップ・ドライバ入力。入力トップは、入力ボトムが“H”的ときにディスエーブルされます。5V内部クランプの前段に3k の入力抵抗を使用すると、入力トランジスタの飽和が防止されます。

IN BOTTOM( ピン3,9 ): ボトム・ドライバ入力。入力ボトムは、入力トップが“H”的ときにディスエーブルされます。5V内部クランプの前段に3k の入力抵抗を使用すると、入力トランジスタの飽和が防止されます。

UV OUT( ピン4,10 ): 低電圧出力。V<sup>+</sup>が低電圧スレッショルドより低下すると、ターンオンするオープン・コレクタNPN出力です。

GND( ターンオン5,11 ): グランド接続。

B GATE FB( ピン6,12 ): ボトムゲート帰還。ボトムパワーMOSFETゲートに直接接続しなければなりません。トップMOSFETは、ボトムゲート帰還ピンが放電し2.5Vより低くなるまでターンオンしません。

B GATE DR( ピン13,19 ): ボトムゲート・ドライブ。ボトムMOSFETに対する高電流ドライブ点です。ゲート抵抗を使用する場合、それをボトムゲート・ドライブ・ピンおよびMOSFETのゲート間に挿入します。

PV<sup>+</sup>( ピン14,20 ): ボトムドライバ電源。ピン1および7と同じ電源に接続しなければなりません。

T SOURCE( ピン15,21 ): トップ・ドライバ・リターン。トップMOSFETソースおよびブートストラップ・コンデンサの上側に接続します。

T GATE FB( ピン16,22 ): トップ・ゲート帰還。トップ・パワーMOSFETゲートに直接接続しなければなりません。ボトムMOSFETは、V<sub>TGF</sub> - V<sub>TSOURCE</sub>が放電し2.9Vより低くなるまでターンオンしません。

T GATE DR( ピン17,23 ): トップ・ゲート・ドライブ。トップMOSFETに対する高電流ドライブ点です。ゲート抵抗を使用する場合、それをトップ・ドライブ・ピンおよびMOSFETのゲート間に挿入します。

BOOST( ピン18,24 ): トップ・ドライバ電源。ブートストラップ・コンデンサの上側に接続します。

動作( 機能図を参照 )

# LT1160/LT1162

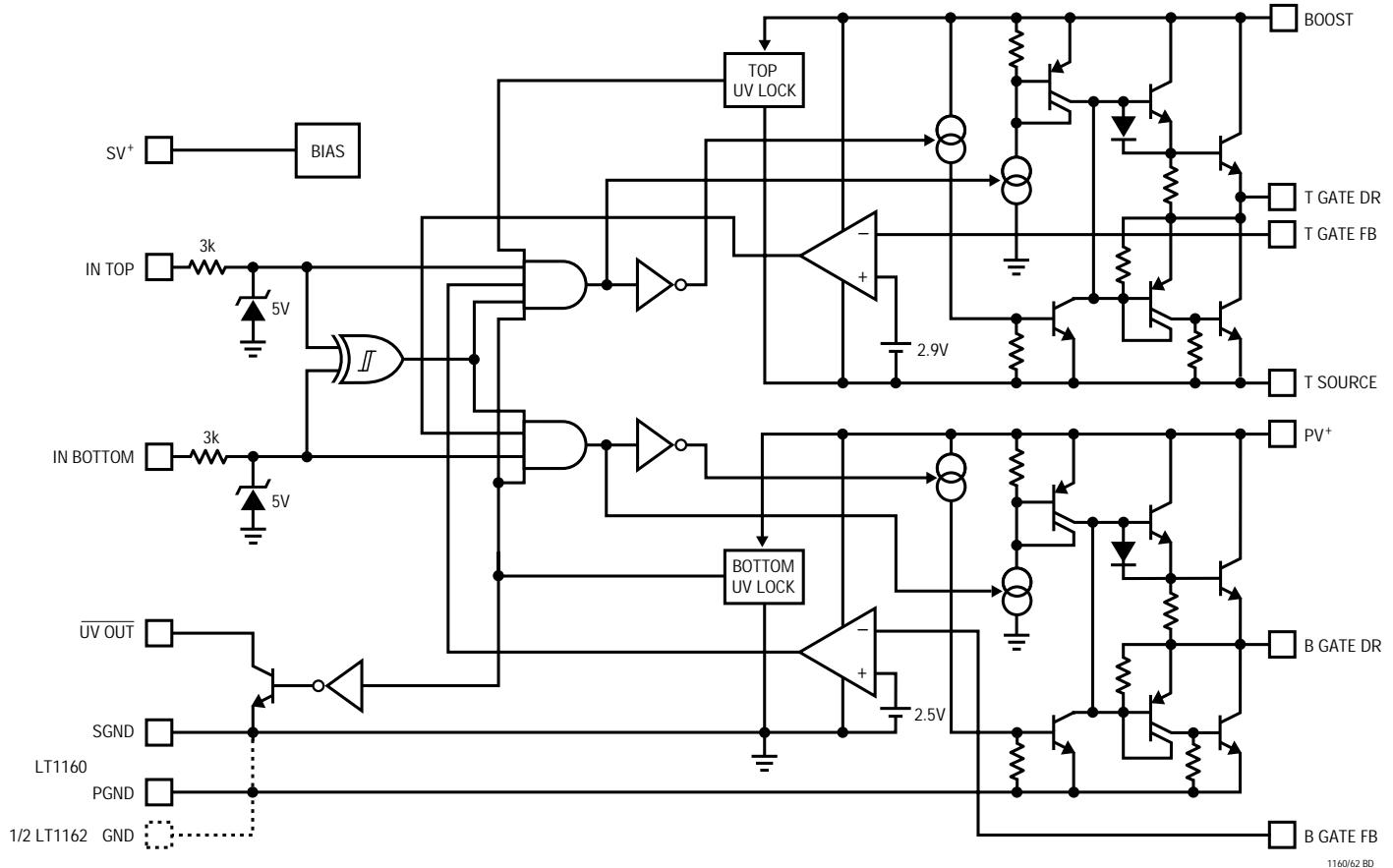

## FUNCTIONAL DIAGRAM (LT1160 or 1/2 LT1162)

## TEST CIRCUIT (LT1160 or 1/2 LT1162)

## TIMING DIAGRAM

## 動作(機能図を参照)

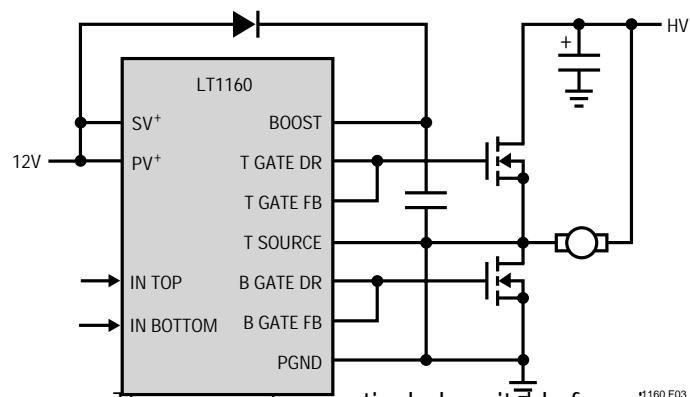

LT1160( または1/2LT1162 )は、入力と出力が分離した2本の独立したドライバ・チャンネルを内蔵しています。入力はTTL/CMOSコンパチブルで、 $V^+$ の入力電圧に耐えることができます。1.4Vの入力スレッショルドは安定化され、300mVのヒステリシスが組み込まれています。両方のチャンネルとも非反転ドライバです。内部ロジックによって、いかなる入力条件でも、両方の出力が同時にターンオンしないようになっています。両方の入力が“H”的場合、どちらの出力もアクティブ“L”に保持されます。

トップ・ドライバ用のフローティング電源は、ブースト・ピンとトップ・ソース・ピンの間に接続されたブーストストラップ・コンデンサから供給されます。このコンデンサは負プレーンが、PWM動作で“L”になるたびに再充電されます。

$V^+$ が低電圧トリップ点より低い場合、低電圧検出回路が両方のチャンネルをディスエーブルします。

$V_{BOOST} - V_{TSOURCE}$ が低電圧トリップ点より低い場合は、独立したUV検出プロックがハイサイド・チャンネルをディスエーブルします。

LT1160のトップおよびボトム・ゲート・ドライバは、それぞれ次の2つのゲート接続を利用します。1)ゲート・ドライブ・ピン - オプションの直列ゲート抵抗を介して電流をターンオンおよびターンオフします。2)ゲート帰還ピン - ゲートに直接接続され、ゲート・ソース間電圧をモニタします。

出力に状態を変化するよう指示する入力遷移があると、LT1160は論理シーケンスに従って、1個のMOSFETをターンオフし、ついでもう1個のMOSFETをターンオンします。まず、ターンオフが開始し、次に $V_{GS}$ がターンオフ・スレッショルド以下に低下するまでモニタし、最後に一方のゲートがターンオンします。

## アプリケーション情報

### パワーMOSFETの選択

LT1160(または1/2 LT1162)は本質的に、トップおよびボトムMOSFETが同時に導通しないよう保護するため、サイズや整合に関する制約はまったくありません。したがって、動作電圧と $R_{DS(ON)}$ 条件に基づいてデバイスを選択することができます。MOSFETの $BV_{DSS}$ はHVより大きくし、故障が頻繁に起こるような苛酷な環境では、 $2 \times HV$ にまで高くなる必要があります。LT1160の60Vの最大動作HV電源に対しては、MOSFETの $BV_{DSS}$ は60Vから100Vでなければなりません。

MOSFETの $R_{DS(ON)}$ は $T_J=25^\circ C$ で規定されており、最大MOSFET接合部温度を超えない限り、通常は動作効率条件に基づいて選択します。各MOSFETがオンしているときの消費電力は次式で与えられます。

$$P = D(I_{DS})^2(1 + \theta)R_{DS(ON)}$$

ただし、Dはデューティ・サイクルであり、 $\theta$ は推定MOSFET接合部温度での $R_{DS(ON)}$ の増加量です。この式から次のとおり所要 $R_{DS(ON)}$ を導出することができます。

$$R_{DS(ON)} = \frac{P}{D(I_{DS})^2(1 + \theta)}$$

たとえば、MOSFETが5Aおよび90%のデューティ・サイクルで動作している場合に、MOSFETの損失を2Wに制限しなければならないときには、所要 $R_{DS(ON)}$ は0.089 /  $(1 + \theta)$ になります。 $(1 + \theta)$ は各MOSFETに対しては、正規化 $R_{DS(ON)}$ 対温度曲線の形式で与えられますが、 $\theta = 0.007 / T_A$ を低電圧MOSFETの近似値として使用できます。したがって、 $T_A = 85^\circ C$ で利用できるヒートシンクの熱抵抗が20  $^\circ C/W$ の場合、MOSFET接合部温度は125  $^\circ C$ 、 $\theta = 0.007(125 - 25) = 0.7$ となります。つまり、MOSFETの所要 $R_{DS(ON)}$ は $0.089 / 1.7 = 0.0523$ であり、これはInternational Rectifier社のIRFZ34で条件を満足することができます。

遷移損失はオフからオンへ、またはオンからオフへ変化する時間に、各MOSFETで消費される電力が原因で発生します。これらの損失は $f \times (HV)^2$ に比例し、数種の高電圧アプリケーションではわずかである場合もあれば、動作周波数を制限する要素になることもあります。

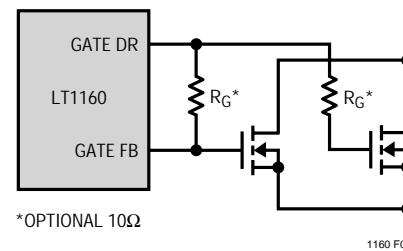

### MOSFETの並列接続

上記の計算で、 $R_{DS(ON)}$ が1つのMOSFETで経済的に実現可能な値より小さい場合は、2つ以上のMOSFETを並列に接続することができます。MOSFETは熱的に接続されている限り(たとえば、共通ヒートシンクにより)本質的に $R_{DS(ON)}$ 比に従って電流を分担します。LT1160のトップおよびボトム・ドライバは、スイッチング速度をわずかに低下させるだけで、それぞれ5つのパワーMOSFETを並列にドライブすることができます(代表的性能特性を参照)。各MOSFETを隣接するMOSFETと「デカップル」して高周波発振を防止するには、それぞれのMOSFETゲートと直列に低い値の抵抗(10 ~ 47  $\Omega$ )が必要になります(メーカーの推奨事項を参照)。ゲート・デカップリング抵抗を使用する場合、対応するゲート帰還ピンを図1に示すとおり、ゲートのいずれかに接続することができます。

複数のMOSFETを並列にドライブするときは、LT1160の消費電力が過剰になるのを防止するために、動作周波数が制限される場合があります(下記のゲート電荷とドライバの消費電力を参照)。

Figure 1. Paralleling MOSFETs

### ゲート電荷とドライバの消費電力

ドライバに課されるMOSFET負荷の有効な指標が全ゲート電荷 $Q_G$ で、これにはゲート・ドレイン間振幅に必要な余分な電荷が含まれています。 $Q_G$ は通常、 $V_{GS} = 10V$ および $V_{DS} = 0.8V_{DS(MAX)}$ に対して規定されています。スイッチング・アプリケーションで電源電流を測定する場合、MOSFETゲート電荷を供給するのに余分な電源電流が必要なため、次のとおり電源電流はDC電気特性で与えられる値より大きくなります。

$$I_{SUPPLY} = I_{DC} + \left( \frac{dQ_G}{dt} \right)_{TOP} + \left( \frac{dQ_G}{dt} \right)_{BOTTOM}$$

## アプリケーション情報

実際の電源電流の増加量はLT1160のスイッチング損失と、ゲートが10V以上に充電されるため、わずかに高くなります。電源電流対入力周波数を代表的性能特性に示します。

LT1160の接合部温度は、電気特性の注2に記載された式を使用して評価できます。たとえば、12V電源から電流を供給する場合、LT1160のISは31mA以下に制限されます。

$$\begin{aligned} T_J &= 85 + (31\text{mA} \times 12\text{V} \times 110 \text{ mW}) \\ &= 126 \quad (\text{絶対最大値を超える}) \end{aligned}$$

最大接合部温度を超えないようにするために、最大スイッチング周波数で選択したMOSFETタイプのコンプリメント全体をドライブしながら、LT1160の電源電流を確認しなければなりません。

### 厄介な過渡問題

PWMアプリケーションでは、トップMOSFETのドレン電流が入力周波数およびデューティ・サイクルで方形波になります。トップ・ドレンに大きな電圧過渡が発生しないようにするには、低ESRの電解コンデンサを使用し、パワー・グランドにリターンさせなければなりません。コンデンサは一般に25μFから5000μFまでのものを使用し、加熱や早期故障を回避するために、ドレンを流れるRMS電流に応じて物理的サイズを決定しなければなりません。さらに、LT1160ではピン1と5の間に別の10μFコンデンサを接続する必要があります(LT1162ではピン1と5、およびピン7と11の間に2個の10μFコンデンサを接続します)。

LT1160のトップ・ソースは内部でグランド以下および電源以上の過渡信号から保護されています。しかし、ゲート・ドライブ・ピンをグランド以下の電圧にすることはできません。ほとんどのアプリケーションでは、トップMOSFETのソースからゲートに結合される負の過渡信号によって問題が生じることはできません。

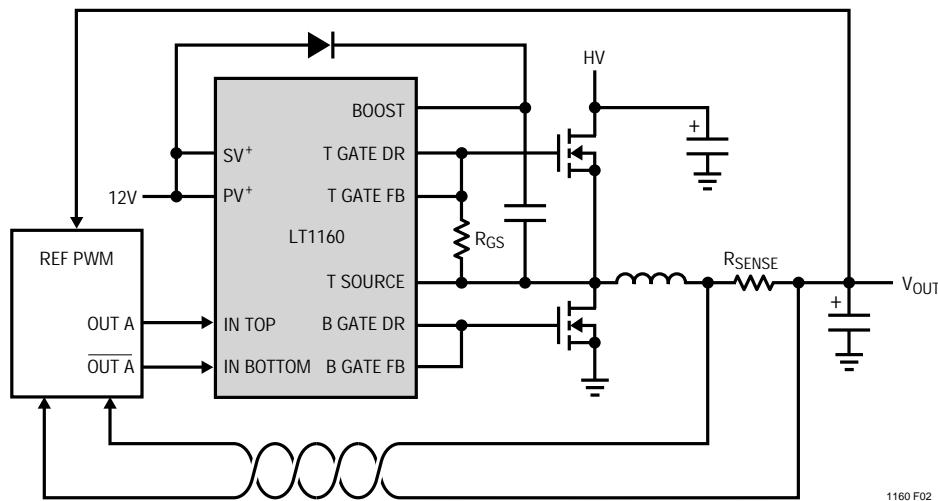

### スイッチング・レギュレータ・アプリケーション

LT1160(または1/2 LT1162)は同期式スイッチ・ドライバとして最適で、ステップダウン(バック)スイッチング・レギュレータの効率を改善します。ほとんどのステップダウン・レギュレータは高電流ショットキ・ダイオードを使用して、スイッチがオフのときにインダクタ電流を流しま

す。スイッチがオン(スイッチが導通)およびオフ(ダイオードが導通)の発振器周期は、以下の式で与えられます。

$$\text{スイッチ・オン} = \left( \frac{V_{\text{OUT}}}{HV} \right) \times \text{全周期}$$

$$\text{スイッチ・オフ} = \left( \frac{HV - V_{\text{OUT}}}{HV} \right) \times \text{全周期}$$

$HV > 2V_{\text{OUT}}$ の場合、スイッチはオフ時間より長くオフし、ダイオード損失がスイッチ損失より大幅に大きくなることに注意してください。ダイオードのワーストケースは短絡時で、 $V_{\text{OUT}}$ がゼロに近づき、ダイオードはほぼ連続して短絡電流を流します。

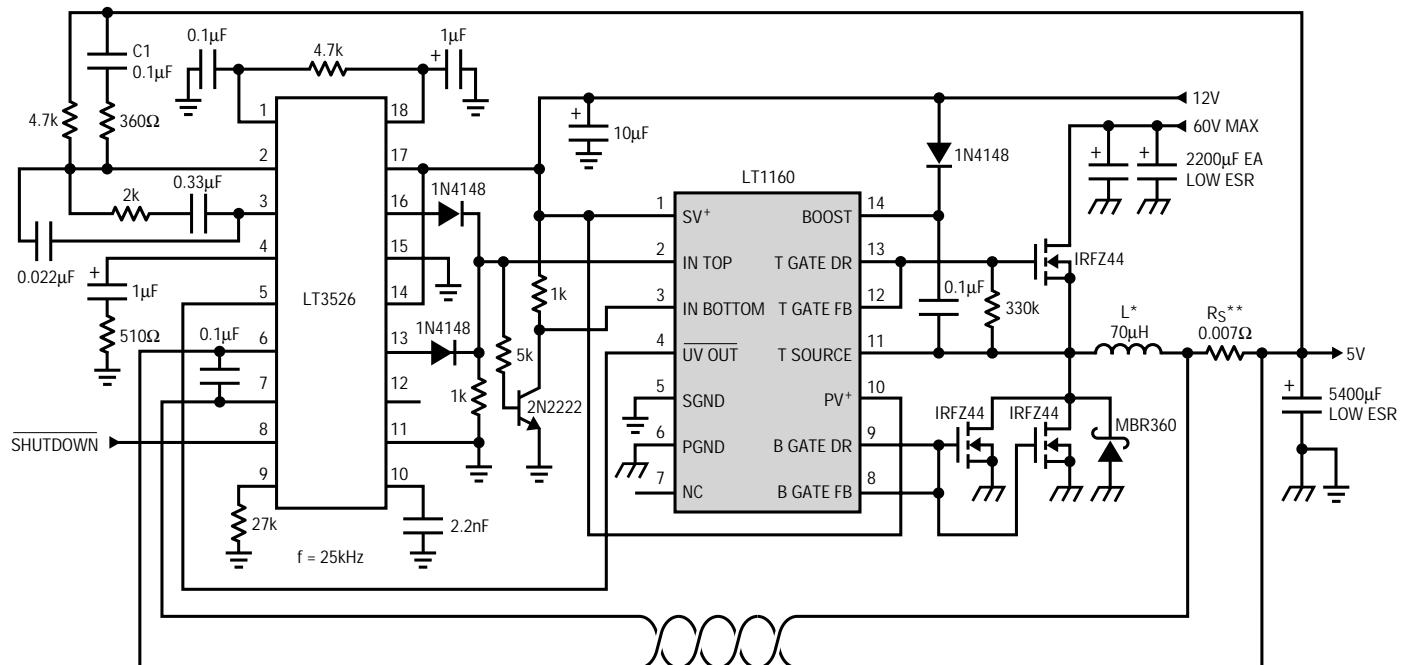

図2に、LT1160を使用し、ステップダウン・レギュレータ・アプリケーションで1組のパワーMOSFETを同期させてドライブする様子を示します。ここではトップMOSFETがスイッチで、ボトムMOSFETがショットキ・ダイオードを置き換えます。2つの導通パスの損失が低いため、ほとんどのアプリケーションでこの方式が非常に高い効率(90% ~ 95%)を実現します。10A以下のレギュレータでは、低 $R_{\text{DS(ON)}}$ NチャンネルMOSFETを使用すれば、ヒートシンクが不要になります。12V電源の前にHVが供給されるときには、 $R_{\text{GS}}$ がトップMOSFETをオフに保持します。

同期スイッチングを行うステップダウン・レギュレータ動作での1つの基本的な違いは、軽負荷時には不連続にならないということです。インダクタ電流がゼロに近づいてもランプダウンを停止しませんが、実際には極性を反転させるため、負荷に関係なくリップル電流が一定になります。スイッチがオンに復帰するときに、負のインダクタ電流がHVに戻るために、これによって効率が大幅に低下することはありません(予測したとおりです)しかし、これらの条件では、再循環電流によって $I^2R$ 損失が発生します。

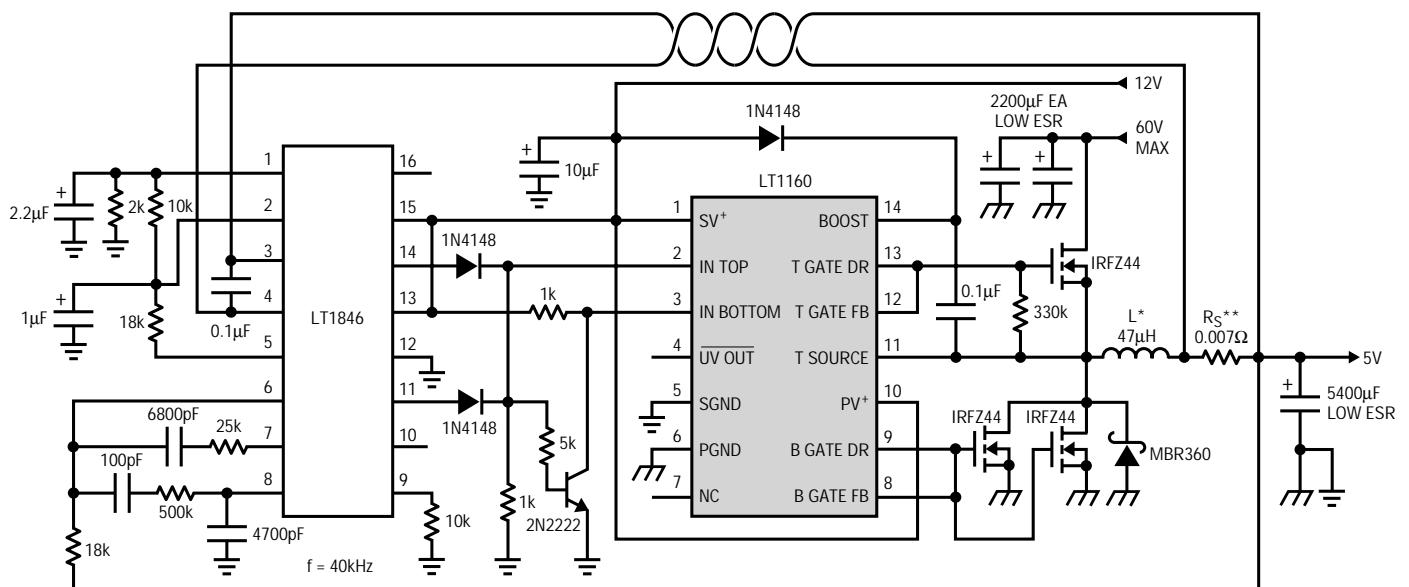

LT1160はステップダウン・スイッチング・レギュレータで、MOSFETを同期してドライブします。完全なレギュレータを構成するには、リファレンスとPWMが必要です。電圧モードまたは電流モードPWMコントローラが使用できますが、LT3526は図4に示す10A回路など、特に高電力、高効率のアプリケーションに適しています。高電流レギュレータでは、ボトムMOSFETの両端に1個の小型ショットキ・ダイオードを使用すれば、逆回復スイッチング損失を低減することができます。

### モータ駆動アプリケーション

## アプリケーション情報

Figure 2. Adding Synchronous Switching to a Step-Down Switching Regulator

回転方向が常に同じアプリケーションでは、半波ブリッジを制御する1個のLT1160を使用して、DCモータを駆動することができます。図3に示すように、モータの一端を電源またはグランドに接続することができます。この構成のモータは、運転、自走停止(惰行)、高速停止( MOSFETの1個でモータを短絡した「逆転防止」ブレーキ)の3種類の選択肢をもつ入力によって制御されます。

LT1162を使用してHブリッジ出力段をドライブすれば、DCモータを双方向に駆動できます。この構成では、モータは右回り運転、左回り運転、急速停止(「逆転防止」ブレーキ)、または自走(惰行)停止が可能です。モータを完全に停止させるには、より慎重に設計を行う必要がありますが、急速停止は電流を逆流させるだけで実現できます。実際には通常、タコメータ帰還を用いた閉ループ制御システムが必要です。

これらの例では、パルス幅変調された方形波によってド

ライバをスイッチングすればモータ速度を制御できます。この方法は特にマイクロコンピュータ/DSP制御ループに適しています。

waves. This approach is particularly suitable for micro-computers/DSP control loops.

Figure 3. Driving a Supply Referenced Motor

## TYPICAL APPLICATIONS

\* MAGNETICS CORE #55585-A2

30 TURNS 14GA MAGNET WIRE

\*\* DALE TYPE LVR-3

ULTRONIX RCS01

1160/62 F04

Figure 4. 90% Efficiency, 40V to 5V 10A Low Dropout Voltage Mode Switching Regulator

\* HURRICANE LAB

HL-KM147U

\*\* DALE TYPE LVR-3

ULTRONIX RCS01

1160/62 F05

Figure 5. 90% Efficiency, 40V to 5V 10A Low Dropout Current Mode Switching Regulator

## TYPICAL APPLICATIONS

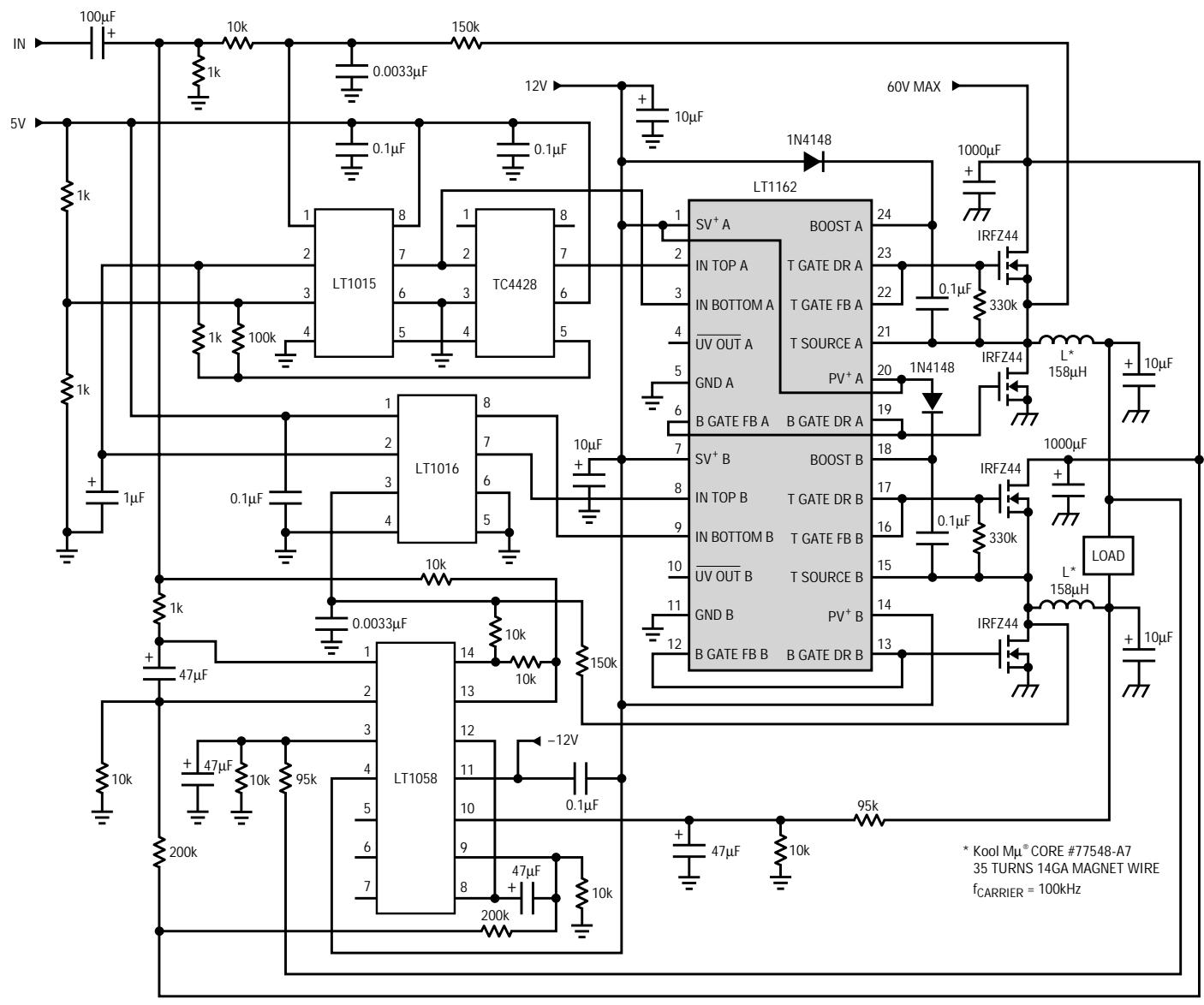

Figure 6. 200W Class D, 10Hz to 1kHz Amplifier

Kool Mu® is a registered trademark of Magnetics, Inc.

## RELATED PARTS

| PART NUMBER | DESCRIPTION                                                    | COMMENTS                                                                              |

|-------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------|

| LT1158      | Half-Bridge N-Channel Power MOSFET Driver                      | Single Input, Continuous Current Protection and Internal Charge Pump for DC Operation |

| LT1336      | Half-Bridge N-Channel Power MOSFET Driver with Boost Regulator | Onboard Boost Regulator to Supply the High Side Driver                                |