# 遅延クロック付 5kV、6 チャンネル デジタル・アイソレータ、SPI 用

## データシート

## ADuM4150

### 特長

遅延クロック・モードで最大 40 MHz の SPI クロック速度をサポート

4 線モードで最大 17 MHz の SPI クロック速度をサポート

4 チャンネルの高速・短伝搬遅延 SPI 信号アイソレーション・チャンネル

2 チャンネルの 250 kbps データ・チャンネル

遅延された補償クロック線

8.3 mm 沿面距離を備えた 20 ピン SOIC パッケージを採用

高温動作 : 125°C

高いコモンモード過渡電圧耐性 : 25 kV/μs 以上

安全性の認定および規制当局の認可

UL 認定 : UL1577

5000 V rms、1 分間の耐力を持つ SOIC ロング・パッケージ

CSA Component Acceptance Notice 5A に準拠

VDE 適合性認定 (申請中)

DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

$V_{IORM} = 846 \text{ Vpeak}$

### アプリケーション

工業用プログラマブル・ロジック・コントローラ (PLC)

センサーのアイソレーション

### 概要

ADuM4150<sup>1</sup> は、絶縁されたシリアル・ペリフェラル・インターフェース(SPI)用に最適化された 6 チャンネルのデジタル・アイソレータ(SPIisolator<sup>TM</sup>)です。アナログ・デバイセズ社のチップ・スケール・トランジス技術 iCoupler 技術をベースとし、CLK、MO/SI、MI/SO、及び SS SPI バスの短伝搬遅延により、最大 17 MHz までの SPI クロック速度をサポートします。これらのチャンネルは伝搬遅延 13ns 及びジッタ 1ns で動作し、SPI のタイミングを最適化します。

ADuM4150 アイソレータはまた、各方向 1 チャンネル、合計 2 チャンネルの独立した低速度のデータ・アイソレーション・チャンネルも追加提供します。低速チャンネルのデータは、サンプリングされ、2.5 μs のジッタを備えた速度 250 kbps の直列データに変換されます。

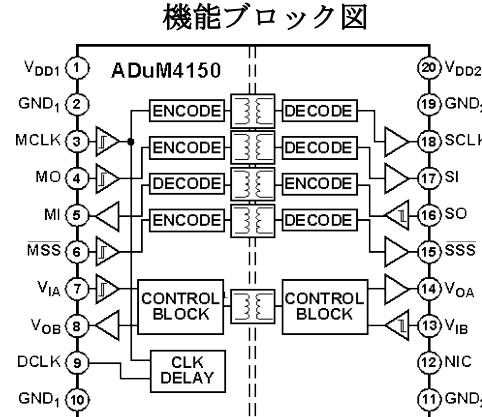

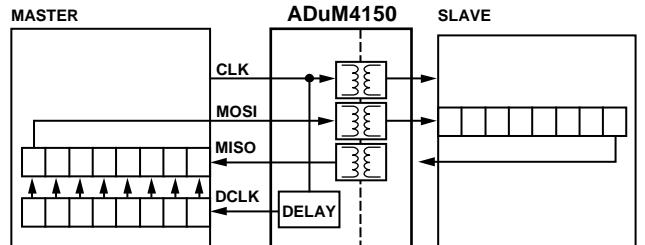

図 1.

ADuM4150 は、デバイスのマスター側で遅延クロック出力をサポートします。この出力は、40 MHz のクロック性能をサポートするためにマスター側にある追加のクロック・ポートと一緒に使用することができます。

表 1. 関連製品

| 製品                             | 説明                            |

|--------------------------------|-------------------------------|

| ADuM3150                       | 3.75 kV、高速、クロック遅延 SPIisolator |

| ADuM3151/ADuM3152/<br>ADuM3153 | 3.75 kV、マルチチャンネル SPIisolator  |

| ADuM3154                       | 3.75 kV、マルチ・スレーブ SPIisolator  |

<sup>1</sup>.米国特許 5,952,849; 6,873,065; 6,262,600; 7,075,329 により保護されています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2015 Analog Devices, Inc. All rights reserved.

## 目次

|                                             |                        |

|---------------------------------------------|------------------------|

| 特長.....                                     | エラー! ブックマークが定義されていません。 |

| アプリケーション.....                               | 1                      |

| 機能ブロック図.....                                | 1                      |

| 概要.....                                     | 1                      |

| 改訂履歴.....                                   | 2                      |

| 仕様.....                                     | 3                      |

| 電気的特性-5V 動作 .....                           | 3                      |

| 電気的特性-3.3V 動作 .....                         | 5                      |

| 電気的特性-5V/3.3V 混合動作.....                     | 7                      |

| 電気的特性-3.3V/5V 混合動作.....                     | 9                      |

| パッケージの特性.....                               | 11                     |

| 適用規格.....                                   | 11                     |

| 絶縁および安全性関連の仕様 .....                         |                        |

| DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 |                        |

| 絶縁特性.....                                   | 12                     |

| 推奨動作条件 .....                                | 12                     |

|                                 |    |

|---------------------------------|----|

| 絶対最大定格 .....                    | 13 |

| ESD に関する注意 .....                | 13 |

| ピン配置およびピン機能の説明 .....            | 14 |

| 代表的な性能特性 .....                  | 15 |

| アプリケーション情報 .....                | 16 |

| はじめに .....                      | 16 |

| プリント回路ボード(PCB)のレイアウト .....      | 17 |

| 伝搬遅延関連のパラメータ .....              | 18 |

| DC 精度と磁界耐性 .....                | 18 |

| 消費電力 ... エラー! ブックマークが定義されていません。 |    |

| 絶縁寿命 .....                      | 19 |

| 外形寸法 .....                      | 21 |

| オーダー・ガイド .....                  | 21 |

## 改訂履歴

10/14—Revision 0: Initial Version

## 仕様

## 電気的特性—5 V動作

すべての代表的仕様は、 $T_A = 25^\circ\text{C}$ 、 $V_{DD1} = V_{DD2} = 5\text{ V}$ で規定。最小及び最大仕様は次に示す推奨動作電圧範囲全体に適用されます：特に指定のない限り、 $4.5\text{ V} \leq V_{DD1} \leq 5.5\text{ V}$ 、 $4.5\text{ V} \leq V_{DD2} \leq 5.5\text{ V}$ 、 $-40^\circ\text{C} \leq T_A \leq +125^\circ\text{C}$ 。スイッチング特性は、特に指定のない限り、 $C_L = 15\text{ pF}$ 及びCMOS信号レベルを用いてテストされます。

表2 スイッチング仕様

| パラメータ                                              | 記号                                   | Aグレード |     |     | Bグレード |     |     | 単位   | テスト条件／コメント                                                    |

|----------------------------------------------------|--------------------------------------|-------|-----|-----|-------|-----|-----|------|---------------------------------------------------------------|

|                                                    |                                      | Min   | Typ | Max | Min   | Typ | Max |      |                                                               |

| MCLK, MO, SO                                       |                                      |       |     |     |       |     |     |      |                                                               |

| SPIクロック・レート                                        | SPI <sub>MCLK</sub>                  |       | 10  |     |       | 17  |     | MHz  |                                                               |

| 高速データ・レート(MO, SO)                                  | DR <sub>FAST</sub>                   |       | 40  |     |       | 40  |     | Mbps | PWD制限内                                                        |

| 伝播遅延                                               | t <sub>PHL</sub> , t <sub>PPLH</sub> |       | 24  |     | 12    | 13  |     | ns   | 50%入力から50%出力まで                                                |

| パルス幅                                               | PW                                   | 12.5  |     |     | 12.5  |     |     | ns   | PWD制限内                                                        |

| パルス幅歪み                                             | PWD                                  |       | 2   |     |       | 2   |     | ns   | t <sub>PPLH</sub> - t <sub>PHL</sub>                          |

| 同方向チャンネル間マッチング <sup>1</sup>                        | t <sub>PSKCD</sub>                   |       | 2   |     |       | 2   |     | ns   |                                                               |

| ジッタ、高速                                             | J <sub>HS</sub>                      | 1     |     |     | 1     |     |     | ns   |                                                               |

| MSS                                                |                                      |       |     |     |       |     |     |      |                                                               |

| 高速データ・レート                                          | DR <sub>FAST</sub>                   |       | 40  |     |       | 40  |     | Mbps | PWD制限内                                                        |

| 伝播遅延                                               | t <sub>PHL</sub> , t <sub>PPLH</sub> | 21    | 24  |     | 21    | 24  |     | ns   | 50%入力から50%出力まで                                                |

| パルス幅                                               | PW                                   | 12.5  |     |     | 12.5  |     |     | ns   | PWD制限内                                                        |

| パルス幅歪み                                             | PWD                                  |       | 2   |     |       | 2   |     | ns   | t <sub>PPLH</sub> - t <sub>PHL</sub>                          |

| セットアップ時間 <sup>2</sup>                              | MSS<br>SETUP                         | 1.5   |     |     | 10    |     |     | ns   |                                                               |

| ジッタ、高速                                             | J <sub>HS</sub>                      | 1     |     |     | 1     |     |     | ns   |                                                               |

| DCLK <sup>3</sup>                                  |                                      |       |     |     |       |     |     |      |                                                               |

| データ・レート                                            |                                      |       | 40  |     |       | 40  |     | MHz  |                                                               |

| 伝播遅延                                               | t <sub>PHL</sub> , t <sub>PPLH</sub> |       | 50  |     |       | 35  |     | ns   | t <sub>PMCLK</sub> + t <sub>PSO</sub> + 3 ns                  |

| パルス幅歪み                                             | PWD                                  |       | 3   |     |       | 3   |     | ns   | t <sub>PPLH</sub> - t <sub>PHL</sub>                          |

| パルス幅                                               | PW                                   | 12    |     |     | 12    |     |     | ns   | PWD制限内                                                        |

| クロック遅延エラー                                          | DCLK <sub>ERR</sub>                  | 0     | 4.5 | 12  | 1     | 5.5 | 12  | ns   | t <sub>PDCLK</sub> - (t <sub>PMCLK</sub> + t <sub>PSO</sub> ) |

| ジッタ                                                | J <sub>DCLK</sub>                    | 1     |     |     | 1     |     |     | ns   |                                                               |

| V <sub>IA</sub> , V <sub>IB</sub>                  |                                      |       |     |     |       |     |     |      |                                                               |

| 低速データ・レート                                          | DR <sub>SLOW</sub>                   |       | 250 |     |       | 250 |     | kbps | PWD制限内                                                        |

| 伝播遅延                                               | t <sub>PHL</sub> , t <sub>PPLH</sub> | 0.1   | 2.6 | 0.1 | 2.6   |     |     | μs   | 50%入力から50%出力まで                                                |

| パルス幅                                               | PW                                   | 4     |     | 4   |       |     |     | μs   | PWD制限内                                                        |

| ジッタ、低速                                             | J <sub>LS</sub>                      |       | 2.5 |     |       | 2.5 |     | μs   |                                                               |

| V <sub>lx</sub> <sup>4</sup> 最小入力スキュー <sup>5</sup> | t <sub>Vlx</sub> SKEW                | 10    |     |     | 10    |     |     | ns   |                                                               |

<sup>1</sup> 同方向チャンネル間マッチングは、アイソレーション障壁の同じ側に入力を持つ2つのチャンネル間の伝搬遅延の差の絶対値を表します。

<sup>2</sup> MSS信号は両方の速度グレードでグリッチ・フィルタがかけられます。他の高速信号はBグレードではグリッチ・フィルタがかけられません。MSS信号がもう1つの高速信号の前に到着するのを保証するためには、MSS信号を速度グレードによって異なる時間だけ競合する信号の前にセットアップしてください。

<sup>3</sup> t<sub>PMCLK</sub>は、サイド1からサイド2までのMCLK信号の伝播遅延時間です。t<sub>PSO</sub>はサイド2からサイド1までのSO信号の伝播遅延時間です。t<sub>PDCLK</sub>はDCLK信号と往復の伝播遅延時間の差です。

<sup>4</sup> V<sub>lx</sub> = V<sub>IA</sub> または V<sub>IB</sub>。

<sup>5</sup> ユーザーは使用できない内部非同期クロックが低速信号をサンプリングします。最終アプリケーションで同方向のチャンネルにおけるエッジ・シーケンスが重要な意味を持つ場合、出力での同時到着を保証するためには、先行パルスは少なくとも1t<sub>Vlx</sub> SKEW時間だけ後続パルスの前に存在しなければなりません。

表3 すべてのグレードに対して<sup>1, 2, 3</sup>

| パラメータ                                                 | 記号           | Min             | Typ             | Max | 単位      | テスト条件／コメント                                                                        |

|-------------------------------------------------------|--------------|-----------------|-----------------|-----|---------|-----------------------------------------------------------------------------------|

| 電源電流                                                  |              |                 |                 |     |         |                                                                                   |

| 1 MHz, A グレード及び B グレード                                | $I_{DD1}$    |                 | 5               | 6.5 | mA      | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 1 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$  |

|                                                       | $I_{DD2}$    |                 | 6.5             | 9.0 | mA      | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 1 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$  |

| 17 MHz, B グレード                                        | $I_{DD1}$    |                 | 15              | 18  | mA      | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 17 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$ |

|                                                       | $I_{DD2}$    |                 | 13.5            | 16  | mA      | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 17 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$ |

| DC 仕様                                                 |              |                 |                 |     |         |                                                                                   |

| MCLK, <u>MSS</u> , MO, SO, $V_{IA}$ , $V_{IB}$        |              |                 |                 |     |         |                                                                                   |

| 入力スレッショルド                                             |              |                 |                 |     |         |                                                                                   |

| ロジック・ハイ                                               | $V_{IH}$     | 0.7 × $V_{DDx}$ |                 |     | V       |                                                                                   |

| ロジック・ロー                                               | $V_{IL}$     |                 | 0.3 × $V_{DDx}$ |     | V       |                                                                                   |

| 入力ヒステリシス                                              | $V_{IHYST}$  |                 | 500             |     | mV      |                                                                                   |

| チャンネル当たり入力電流                                          | $I_I$        | -1              | +0.01           | +1  | μA      | $0 \text{ V} \leq V_{INPUT} \leq V_{DDx}$                                         |

| SCLK, <u>SSS</u> , MI, SI, $V_{OA}$ , $V_{OB}$ , DCLK |              |                 |                 |     |         |                                                                                   |

| 出力電圧                                                  |              |                 |                 |     |         |                                                                                   |

| ロジック・ハイ                                               | $V_{OH}$     | $V_{DDx} - 0.1$ | 5.0             |     | V       | $I_{OUTPUT} = -20 \mu\text{A}$ , $V_{INPUT} = V_{IH}$                             |

|                                                       |              | $V_{DDx} - 0.4$ | 4.8             |     | V       | $I_{OUTPUT} = -4 \text{ mA}$ , $V_{INPUT} = V_{IL}$                               |

| ロジック・ロー                                               | $V_{OL}$     |                 | 0.0             | 0.1 | V       | $I_{OUTPUT} = 20 \mu\text{A}$ , $V_{INPUT} = V_{IL}$                              |

|                                                       |              |                 | 0.2             | 0.4 | V       | $I_{OUTPUT} = 4 \text{ mA}$ , $V_{INPUT} = V_{IL}$                                |

| $V_{DD1}$ , $V_{DD2}$ 低電圧ロックアウト                       | UVLO         |                 | 2.6             |     | V       |                                                                                   |

| 高速チャンネル当たりの電源電流                                       |              |                 |                 |     |         |                                                                                   |

| ダイナミック入力                                              | $I_{DD1(D)}$ |                 | 0.080           |     | mA/Mbps |                                                                                   |

| ダイナミック出力                                              | $I_{DD2(D)}$ |                 | 0.046           |     | mA/Mbps |                                                                                   |

| 全低速チャンネルに対する電源電流                                      |              |                 |                 |     |         |                                                                                   |

| サイド1 静止電流                                             | $I_{DD1(Q)}$ |                 | 4.4             |     | mA      |                                                                                   |

| サイド2 静止電流                                             | $I_{DD2(Q)}$ |                 | 6.1             |     | mA      |                                                                                   |

| AC 仕様                                                 |              |                 |                 |     |         |                                                                                   |

| 出力立ち上がり／立下り時間                                         | $t_R/t_F$    |                 | 2.5             |     | ns      | 10%から 90%まで                                                                       |

| コモンモード過渡電圧耐性 <sup>4</sup>                             | $ CM $       | 25              | 35              |     | kV/μs   | $V_{INPUT} = V_{DDx}$ , $V_{CM} = 1000 \text{ V}$ ,<br>過渡電圧 = 800 V               |

<sup>1</sup>  $V_{DDx} = V_{DD1}$  または  $V_{DD2}$ .<sup>2</sup>  $V_{INPUT}$  は、MCLK, MSS, MO, SO,  $V_{IA}$ , または  $V_{IB}$  ピンのいずれかの入力電圧です。<sup>3</sup>  $I_{OUTPUT}$  は、SCLK, DCLK, SSS, MI, SI,  $V_{OA}$ , または  $V_{OB}$  ピンのいずれかの出力電流です。<sup>4</sup>  $|CM|$  は、出力電圧を  $V_{OH}$  と  $V_{OL}$  の制限以内に維持できるコモンモード電圧の最大スルーレートです。

## 電気的特性—3.3 V動作

すべての代表的仕様は、 $T_A = 25^\circ\text{C}$ 、 $V_{DD1} = V_{DD2} = 3.3\text{ V}$ で規定。最小及び最大仕様は次に示す推奨動作電圧範囲全体に適用されます：特に指定のない限り、 $3.0\text{ V} \leq V_{DD1} \leq 3.6\text{ V}$ 、 $3.0\text{ V} \leq V_{DD2} \leq 3.6\text{ V}$ 、 $-40^\circ\text{C} \leq T_A \leq +125^\circ\text{C}$ 。スイッチング特性は、特に指定のない限り、 $C_L = 15\text{ pF}$ 及びCMOS信号レベルを用いてテストされます。

表4 スイッチング仕様

| パラメータ                                                 | 記号                                     | Aグレード |      |     | Bグレード |      |      | 単位   | テスト条件／コメント                                               |

|-------------------------------------------------------|----------------------------------------|-------|------|-----|-------|------|------|------|----------------------------------------------------------|

|                                                       |                                        | Min   | Typ  | Max | Min   | Typ  | Max  |      |                                                          |

| MCLK, MO, SO                                          |                                        |       |      |     |       |      |      |      |                                                          |

| SPIクロック・レート                                           | $\text{SPI}_{\text{MCLK}}$             |       |      | 8.3 |       |      | 12.5 | MHz  |                                                          |

| 高速データ・レート(MO, SO)                                     | $\text{DR}_{\text{FAST}}$              |       |      | 40  |       |      | 40   | Mbps | PWD制限内                                                   |

| 伝播遅延                                                  | $t_{\text{PHL}}, t_{\text{PLH}}$       |       |      | 30  |       |      | 20   | ns   | 50%入力から50%出力まで                                           |

| パルス幅                                                  | PW                                     | 12.5  |      |     | 12.5  |      |      | ns   | PWD制限内                                                   |

| パルス幅歪み                                                | PWD                                    |       | 3    |     |       | 3    |      | ns   | $ t_{\text{PLH}} - t_{\text{PHL}} $                      |

| 同方向チャンネル間マッチング <sup>1</sup>                           | $t_{\text{PSKCD}}$                     |       | 3    |     |       | 3    |      | ns   |                                                          |

| ジッタ、高速                                                | J <sub>HS</sub>                        |       | 1    |     |       | 1    |      | ns   |                                                          |

| MSS                                                   |                                        |       |      |     |       |      |      |      |                                                          |

| 高速データ・レート                                             | $\text{DR}_{\text{FAST}}$              |       |      | 40  |       |      | 40   | Mbps | PWD制限内                                                   |

| 伝播遅延                                                  | $t_{\text{PHL}}, t_{\text{PLH}}$       |       |      | 30  |       |      | 30   | ns   | 50%入力から50%出力まで                                           |

| パルス幅                                                  | PW                                     | 12.5  |      |     | 12.5  |      |      | ns   | PWD制限内                                                   |

| パルス幅歪み                                                | PWD                                    |       | 3    |     |       | 3    |      | ns   | $ t_{\text{PLH}} - t_{\text{PHL}} $                      |

| セットアップ時間 <sup>2</sup>                                 | $\overline{\text{MSS}}_{\text{SETUP}}$ | 1.5   |      |     | 10    |      |      | ns   |                                                          |

| ジッタ、高速                                                | J <sub>HS</sub>                        |       | 1    |     |       | 1    |      | ns   |                                                          |

| DCLK <sup>3</sup>                                     |                                        |       |      |     |       |      |      |      |                                                          |

| データ・レート                                               |                                        |       |      | 40  |       |      | 40   | MHz  |                                                          |

| 伝播遅延                                                  | $t_{\text{PHL}}, t_{\text{PLH}}$       |       |      | 60  |       |      | 40   | ns   | $t_{\text{PMCLK}} + t_{\text{PSO}} + 3\text{ ns}$        |

| パルス幅歪み                                                | PWD                                    |       | 3    |     |       | 3    |      | ns   | $ t_{\text{PLH}} - t_{\text{PHL}} $                      |

| パルス幅                                                  | PW                                     | 12    |      |     | 12    |      |      | ns   | PWD制限内                                                   |

| クロック遅延エラー                                             | $\text{DCLK}_{\text{ERR}}$             | -4    | +2.4 | +9  | -3    | +2.5 | +8   | ns   | $t_{\text{PDCLK}} - (t_{\text{PMCLK}} + t_{\text{PSO}})$ |

| ジッタ                                                   | J <sub>DCLK</sub>                      |       | 1    |     |       | 1    |      | ns   |                                                          |

| $V_{\text{IA}}, V_{\text{IB}}$                        |                                        |       |      |     |       |      |      |      |                                                          |

| 低速データ・レート                                             | $\text{DR}_{\text{SLOW}}$              |       |      | 250 |       |      | 250  | kbps | PWD制限内                                                   |

| 伝播遅延                                                  | $t_{\text{PHL}}, t_{\text{PLH}}$       | 0.1   | 2.6  | 0.1 | 2.6   |      |      | μs   | 50%入力から50%出力まで                                           |

| パルス幅                                                  | PW                                     | 4     |      | 4   |       |      |      | μs   | PWD制限内                                                   |

| ジッタ、低速                                                | J <sub>LS</sub>                        |       | 2.5  |     |       | 2.5  |      | μs   |                                                          |

| $V_{\text{Ix}}^4 = V_{\text{IA}}$ または $V_{\text{IB}}$ | $t_{\text{Vlx}}_{\text{SKEW}}$         | 10    |      | 10  |       |      |      | ns   |                                                          |

<sup>1</sup> 同方向チャンネル間マッチングは、アイソレーション障壁の同じ側に入力を持つ2つのチャンネル間の伝播遅延の差の絶対値を表します。

<sup>2</sup> MSS信号は両方の速度グレードでグリッチ・フィルタがかけられますが、他の高速信号はBグレードではグリッチ・フィルタがかけられません。MSS信号がもう1つの高速信号の前に到着するのを保証するためには、MSS信号を速度グレードによって異なる時間だけ競合する信号の前にセットアップしてください。

<sup>3</sup>  $t_{\text{PMCLK}}$ は、サイド1からサイド2までのMCLK信号の伝播遅延時間です。 $t_{\text{PSO}}$ はサイド2からサイド1までのSO信号の伝播遅延時間です。 $t_{\text{PDCLK}}$ はDCLK信号と往復の伝播遅延時間の差です。

<sup>4</sup>  $V_{\text{Ix}} = V_{\text{IA}}$ または $V_{\text{IB}}$ 。

<sup>5</sup> ユーザーは使用できない内部非同期クロックが低速信号をサンプリングします。最終アプリケーションで同方向のチャンネルにおけるエッジ・シーケンスが重要な意味を持つ場合、出力での同時到着を保証するためには、先行パルスは少なくとも1  $t_{\text{Vlx}}_{\text{SKEW}}$ 時間だけ後続パルスの前に存在しなければなりません。

表5 すべてのグレードに対して<sup>1, 2, 3</sup>

| パラメータ                                                                                          | 記号                           | Min                    | Typ                    | Max | 単位    | テスト条件/コメント                                                                        |

|------------------------------------------------------------------------------------------------|------------------------------|------------------------|------------------------|-----|-------|-----------------------------------------------------------------------------------|

| 電源電流<br>1 MHz, A グレード及び B グレード                                                                 | I <sub>DD1</sub>             |                        | 3.5                    | 5.2 | mA    | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 1 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$  |

|                                                                                                | I <sub>DD2</sub>             |                        | 4.9                    | 6.3 | mA    | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 1 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$  |

| 17 MHz, B グレード                                                                                 | I <sub>DD1</sub>             |                        | 9.5                    | 15  | mA    | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 17 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$ |

|                                                                                                | I <sub>DD2</sub>             |                        | 8                      | 12  | mA    | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 17 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$ |

| DC 仕様<br>MCLK, <u>MSS</u> , MO, SO, V <sub>IA</sub> , V <sub>IB</sub><br>入力スレッショールド<br>ロジック・ハイ | V <sub>IH</sub>              | 0.7 × V <sub>DDx</sub> |                        |     | V     |                                                                                   |

| ロジック・ロー                                                                                        | V <sub>IL</sub>              |                        | 0.3 × V <sub>DDx</sub> |     | V     |                                                                                   |

| 入力ヒステリシス<br>チャンネル当たり入力電流                                                                       | V <sub>IHYST</sub>           | 500                    |                        |     | mV    |                                                                                   |

| SCLK, <u>SSS</u> , MI, SI, V <sub>OA</sub> , V <sub>OB</sub> , DCLK<br>出力電圧<br>ロジック・ハイ         | I <sub>I</sub>               | -1                     | +0.01                  | +1  | μA    | 0 V ≤ V <sub>INPUT</sub> ≤ V <sub>DDx</sub>                                       |

| ロジック・ロー                                                                                        | V <sub>OH</sub>              | V <sub>DDx</sub> - 0.1 | 5.0                    |     | V     | I <sub>OUTPUT</sub> = -20 μA, V <sub>INPUT</sub> = V <sub>IH</sub>                |

|                                                                                                | V <sub>OL</sub>              | V <sub>DDx</sub> - 0.4 | 4.8                    |     | V     | I <sub>OUTPUT</sub> = -4 mA, V <sub>INPUT</sub> = V <sub>IH</sub>                 |

| V <sub>DD1</sub> , V <sub>DD2</sub> 低電圧ロックアウト<br>高速チャンネル当たりの電源電流<br>ダイナミック入力<br>ダイナミック出力       | UVLO                         | 0.0                    | 0.1                    |     | V     | I <sub>OUTPUT</sub> = 20 μA, V <sub>INPUT</sub> = V <sub>IL</sub>                 |

| 全低速チャンネルに対する電源電流<br>サイド1 静止電流 t                                                                | I <sub>DD1(Q)</sub>          | 0.2                    | 0.4                    |     | V     | I <sub>OUTPUT</sub> = 4 mA, V <sub>INPUT</sub> = V <sub>IL</sub>                  |

| サイド2 静止電流                                                                                      | I <sub>DD2(Q)</sub>          | 2.6                    |                        |     | V     |                                                                                   |

| AC 仕様<br>出力立ち上がり／立下り時間<br>コモンモード過渡電圧耐性 <sup>4</sup>                                            | t <sub>R/t<sub>F</sub></sub> |                        | 2.5                    |     | ns    | 10%から 90%まで                                                                       |

|                                                                                                | CM                           | 25                     | 35                     |     | kV/μs | V <sub>INPUT</sub> = V <sub>DDx</sub> , V <sub>CM</sub> = 1000 V,<br>過渡電圧 = 800 V |

<sup>1</sup> V<sub>DDx</sub> = V<sub>DD1</sub> または V<sub>DD2</sub>.<sup>2</sup> V<sub>INPUT</sub> は、MCLK, MSS, MO, SO, V<sub>IA</sub>, または V<sub>IB</sub> ピンのいずれかの入力電圧です。<sup>3</sup> I<sub>OUTPUT</sub> は、SCLK, DCLK, SSS, MI, SI, V<sub>OA</sub>, または V<sub>OB</sub> ピンのいずれかの出力電流です。<sup>4</sup> |CM| は、出力電圧を V<sub>OH</sub> と V<sub>OL</sub> の制限以内に維持

## 電気的特性—5 V/3.3 V 混合動作

すべての代表的仕様は、 $T_A = 25^\circ\text{C}$ 、 $V_{DD1} = 5\text{ V}$ 、 $V_{DD2} = 3.3\text{ V}$ で規定。最小及び最大仕様は次に示す推奨動作電圧範囲全体に適用されます：特に指定のない限り、 $4.5\text{ V} \leq V_{DD1} \leq 5.5\text{ V}$ 、 $3.0\text{ V} \leq V_{DD2} \leq 3.6\text{ V}$ 、 $-40^\circ\text{C} \leq T_A \leq +125^\circ\text{C}$ 。スイッチング特性は、特に指定のない限り、 $CL = 15\text{ pF}$ 及びCMOS信号レベルを用いてテストされます。

表 6 スイッチング仕様

| パラメータ                                   | 記号                                     | A グレード |     |     | B グレード |      |      | 単位   | テスト条件／コメント                                               |

|-----------------------------------------|----------------------------------------|--------|-----|-----|--------|------|------|------|----------------------------------------------------------|

|                                         |                                        | Min    | Typ | Max | Min    | Typ  | Max  |      |                                                          |

| MCLK, MO, SO                            |                                        |        |     |     |        |      |      |      |                                                          |

| SPI クロック・レート                            | $\text{SPI}_{\text{MCLK}}$             |        |     | 9.2 |        |      | 15.6 | MHz  |                                                          |

| 高速データ・レート (MO, SO)                      | $\text{DR}_{\text{FAST}}$              |        |     | 40  |        |      | 40   | Mbps | PWD 制限内                                                  |

| 伝播遅延                                    | $t_{\text{PHL}}, t_{\text{PLH}}$       |        |     | 27  |        |      | 16   | ns   | 50%入力から 50%出力まで                                          |

| パルス幅                                    | PW                                     | 12.5   |     |     | 12.5   |      |      | ns   | PWD 制限内                                                  |

| パルス幅歪み                                  | PWD                                    |        | 3   |     |        | 2    |      | ns   | $ t_{\text{PLH}} - t_{\text{PHL}} $                      |

| 同方向チャンネル間マッチング <sup>1</sup>             | $t_{\text{PSKCD}}$                     |        | 2   |     |        | 2    |      | ns   |                                                          |

| ジッタ、高速                                  | $J_{\text{HS}}$                        |        | 1   |     |        | 1    |      | ns   |                                                          |

| MSS                                     |                                        |        |     |     |        |      |      |      |                                                          |

| 高速データ・レート                               | $\text{DR}_{\text{FAST}}$              |        |     | 40  |        |      | 40   | Mbps | PWD 制限内                                                  |

| 伝播遅延                                    | $t_{\text{PHL}}, t_{\text{PLH}}$       |        |     | 26  |        |      | 26   | ns   | 50%入力から 50%出力まで                                          |

| パルス幅                                    | PW                                     | 12.5   |     |     | 12.5   |      |      | ns   | PWD 制限内                                                  |

| パルス幅歪み                                  | PWD                                    |        | 2   |     |        | 2    |      | ns   | $ t_{\text{PLH}} - t_{\text{PHL}} $                      |

| セットアップ時間 <sup>2</sup>                   | $\overline{\text{MSS}}_{\text{SETUP}}$ | 1.5    |     |     | 10     |      |      | ns   |                                                          |

| ジッタ、高速                                  | $J_{\text{HS}}$                        |        | 1   |     |        | 1    |      | ns   |                                                          |

| DCLK <sup>3</sup>                       |                                        |        |     |     |        |      |      |      |                                                          |

| データ・レート                                 |                                        |        |     | 40  |        |      | 40   | MHz  |                                                          |

| 伝播遅延                                    | $t_{\text{PHL}}, t_{\text{PLH}}$       |        |     | 50  |        |      | 35   | ns   | $t_{\text{PMCLK}} + t_{\text{PSO}} + 3\text{ ns}$        |

| パルス幅歪み                                  | PWD                                    |        | 3   |     |        | 3    |      | ns   | $ t_{\text{PLH}} - t_{\text{PHL}} $                      |

| パルス幅                                    | PW                                     | 12     |     |     | 12     |      |      | ns   | PWD 制限内                                                  |

| クロック遅延エラー                               | $\text{DCLK}_{\text{ERR}}$             | -5     | 0   | +7  | -5     | +1.2 | +9   | ns   | $t_{\text{PDCLK}} - (t_{\text{PMCLK}} + t_{\text{PSO}})$ |

| ジッタ                                     | $J_{\text{DCLK}}$                      |        | 1   |     |        | 1    |      | ns   |                                                          |

| $V_{\text{IA}}, V_{\text{IB}}$          |                                        |        |     |     |        |      |      |      |                                                          |

| 低速データ・レート                               | $\text{DR}_{\text{SLOW}}$              |        |     | 250 |        |      | 250  | kbps | PWD 制限内                                                  |

| 伝播遅延                                    | $t_{\text{PHL}}, t_{\text{PLH}}$       | 0.1    | 2.6 | 0.1 | 2.6    |      |      | μs   | 50%入力から 50%出力まで                                          |

| パルス幅                                    | PW                                     | 4      |     | 4   |        |      |      | μs   | PWD 制限内                                                  |

| ジッタ、低速                                  | $J_{\text{LS}}$                        |        | 2.5 |     |        | 2.5  |      | μs   |                                                          |

| $V_{\text{Ix}}^4$ 最小入力スキュー <sup>5</sup> | $t_{\text{Vlx SKEW}}$                  | 10     |     | 10  |        |      |      | ns   |                                                          |

<sup>1</sup> 同方向チャンネル間マッチングは、アイソレーション障壁の同じ側に入力を持つ2つのチャンネル間の伝搬遅延の差の絶対値を表します。

<sup>2</sup> MSS 信号は両方の速度グレードでグリッチ・フィルタがかけられますが、他の高速信号は B グレードではグリッチ・フィルタがかけられません。MSS 信号がもう1つの高速信号の前に到着するのを保証するためには、MSS 信号を速度グレードによって異なる時間だけ競合する信号の前にセットアップしてください。

<sup>3</sup>  $t_{\text{PMCLK}}$  は、サイド 1 からサイド 2 までの MCLK 信号の伝播遅延時間です。 $t_{\text{PSO}}$  はサイド 2 からサイド 1 までの SO 信号の伝播遅延時間です。 $t_{\text{PDCLK}}$  は DCLK 信号と往復の伝播遅延時間の差です。

<sup>4</sup>  $V_{\text{Ix}} = V_{\text{IA}}$  または  $V_{\text{IB}}$ 。

<sup>5</sup> ユーザーは使用できない内部非同期クロックが低速信号をサンプリングします。最終アプリケーションで同方向のチャンネルにおけるエッジ・シーケンスが重要な意味を持つ場合、出力での同時到着を保証するためには、先行パルスは少なくとも 1  $t_{\text{Vlx SKEW}}$  時間だけ後続パルスの前に存在しなければなりません。

表 7 すべてのグレードに対して<sup>1, 2, 3</sup>

| パラメータ | 記号        | Min | Typ | Max | 単位 | テスト条件／コメント                                                                        |

|-------|-----------|-----|-----|-----|----|-----------------------------------------------------------------------------------|

| 電源電流  | $I_{DD1}$ |     | 5.3 | 6.5 | mA | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 1 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$  |

|       | $I_{DD2}$ |     | 4.9 | 6.3 | mA | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 1 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$  |

|       | $I_{DD1}$ |     | 16  | 18  | mA | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 17 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$ |

|       | $I_{DD2}$ |     | 10  | 12  | mA | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 17 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$ |

| DC 仕様 |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

| AC 仕様 |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

|       |           |     |     |     |    |                                                                                   |

<sup>1</sup>  $V_{DDx} = V_{DD1}$  または  $V_{DD2}$ .<sup>2</sup>  $V_{INPUT}$  は、MCLK, MSS, MO, SO,  $V_{IA}$ , または  $V_{IB}$  ピンのいずれかの入力電圧です。<sup>3</sup>  $I_{OUTPUT}$  は、SCLK, DCLK, SSS, MI, SI,  $V_{OA}$ , または  $V_{OB}$  ピンのいずれかの出力電流です。<sup>4</sup>  $|CM|$  は、出力電圧を  $V_{OH}$  と  $V_{OL}$  の制限以内に維持できるコモンモード電圧の最大スルーレートです。

## 電気的特性—3.3V/5V 混合動作

すべての代表的仕様は、 $T_A = 25^\circ\text{C}$ 、 $V_{DD1} = 3.3\text{ V}$ 、 $V_{DD2} = 5\text{ V}$  で規定。最小及び最大仕様は次に示す推奨動作電圧範囲全体に適用されます：特に指定のない限り、 $3.0\text{ V} \leq V_{DD1} \leq 3.6\text{ V}$ 、 $4.5\text{ V} \leq V_{DD2} \leq 5.5\text{ V}$ 、 $-40^\circ\text{C} \leq T_A \leq +125^\circ\text{C}$ 。スイッチング特性は、特に指定のない限り、 $CL = 15\text{ pF}$  及び CMOS 信号レベルを用いてテストされます。

表 8 スイッチング仕様

| パラメータ                             | 記号                                  | A グレード |      |     | B グレード |      |     | 単位   | テスト条件／コメント                                                    |

|-----------------------------------|-------------------------------------|--------|------|-----|--------|------|-----|------|---------------------------------------------------------------|

|                                   |                                     | Min    | Typ  | Max | Min    | Typ  | Max |      |                                                               |

| MCLK, MO, SO                      | SPI <sub>MCLK</sub>                 | 12.5   | 9.2  |     |        | 15.6 |     | MHz  |                                                               |

|                                   | DR <sub>FAST</sub>                  |        | 40   |     |        | 40   |     | Mbps | PWD 制限内                                                       |

|                                   | t <sub>PHL</sub> , t <sub>PLH</sub> |        | 27   |     |        | 16   |     | ns   | 50%入力から 50%出力まで                                               |

|                                   | PW                                  |        |      |     | 12.5   |      |     | ns   | PWD 制限内                                                       |

|                                   | PWD                                 |        | 2    |     |        | 2    |     | ns   | t <sub>PLH</sub> - t <sub>PHL</sub>                           |

|                                   | t <sub>PSKCD</sub>                  |        | 3    |     |        | 3    |     | ns   |                                                               |

|                                   | J <sub>HS</sub>                     |        | 1    |     |        | 1    |     | ns   |                                                               |

| MSS                               | DR <sub>FAST</sub>                  | 1.5    | 40   |     |        | 40   |     | Mbps | PWD 制限内                                                       |

|                                   | t <sub>PHL</sub> , t <sub>PLH</sub> |        | 26   |     |        | 26   |     | ns   | 50%入力から 50%出力まで                                               |

|                                   | PW                                  |        | 12.5 |     |        | 12.5 |     | ns   | PWD 制限内                                                       |

|                                   | PWD                                 |        | 3    |     |        | 3    |     | ns   | t <sub>PLH</sub> - t <sub>PHL</sub>                           |

|                                   | MSS                                 |        |      |     | 10     |      |     | ns   |                                                               |

|                                   | SETUP                               |        |      |     |        |      |     |      |                                                               |

|                                   | J <sub>HS</sub>                     |        | 1    |     |        | 1    |     | ns   |                                                               |

| DCLK <sup>3</sup>                 | Data Rate                           | 12     | 40   |     |        | 40   |     | MHz  |                                                               |

|                                   | 伝播遅延                                |        | 60   |     |        | 40   |     | ns   | t <sub>PMCLK</sub> + t <sub>PSO</sub> + 3 ns                  |

|                                   | パルス幅歪み                              |        | PWD  | 3   |        | 3    |     | ns   | t <sub>PLH</sub> - t <sub>PHL</sub>                           |

|                                   | パルス幅                                |        | PW   | 12  |        | 12   |     | ns   | PWD 制限内                                                       |

|                                   | DCLK <sub>ERR</sub>                 |        | 2    | 7   | 13     | 2    | 6.8 | 11   | ns                                                            |

|                                   | J <sub>DCLK</sub>                   |        | 1    |     |        | 1    |     | ns   | t <sub>PDCLK</sub> - (t <sub>PMCLK</sub> + t <sub>PSO</sub> ) |

|                                   |                                     |        |      |     |        |      |     |      |                                                               |

| V <sub>IA</sub> , V <sub>IB</sub> | DR <sub>SLOW</sub>                  | 4      | 250  |     |        | 250  |     | kbps | PWD 制限内                                                       |

|                                   | t <sub>PHL</sub> , t <sub>PLH</sub> |        | 0.1  | 2.6 |        | 0.1  | 2.6 | μs   | 50%入力から 50%出力まで                                               |

|                                   | PW                                  |        | 4    |     |        | 4    |     | μs   | PWD 制限内                                                       |

|                                   | J <sub>LS</sub>                     |        |      |     | 2.5    |      | 2.5 | μs   |                                                               |

|                                   | t <sub>Vlx</sub> SKEW               |        | 10   |     |        | 10   |     | ns   |                                                               |

<sup>1</sup> 同方向チャンネル間マッチングは、アイソレーション障壁の同じ側に入力を持つ 2 つのチャンネル間の伝搬遅延の差の絶対値を表します。

<sup>2</sup> MSS 信号は両方の速度グレードでグリッチ・フィルタがかけられますが、他の高速信号は B グレードではグリッチ・フィルタがかけられません。MSS 信号がもう 1 つの高速信号の前に到着するのを保証するためには、MSS 信号を速度グレードによって異なる時間だけ競合する信号の前にセットアップしてください。

<sup>3</sup> t<sub>PMCLK</sub> は、サイド 1 からサイド 2 までの MCLK 信号の伝播遅延時間です。t<sub>PSO</sub> はサイド 2 からサイド 1 までの SO 信号の伝播遅延時間です。t<sub>PDCLK</sub> は DCLK 信号と往復の伝播遅延時間の差です。

<sup>4</sup> V<sub>lx</sub> = V<sub>IA</sub> または V<sub>IB</sub>。

<sup>5</sup> ユーザーは使用できない内部非同期クロックが低速信号をサンプリングします。最終アプリケーションで同方向のチャンネルにおけるエッジ・シーケンスが重要な意味を持つ場合、出力での同時到着を保証するためには、先行パルスは少なくとも 1 t<sub>Vlx</sub> SKEW 時間だけ後続パルスの前に存在しなければなりません。

表9 すべてのグレードに対して<sup>1, 2, 3</sup>

| パラメータ                                                 | 記号           | Min             | Typ             | Max | 単位    | テスト条件／素子                                                                          |

|-------------------------------------------------------|--------------|-----------------|-----------------|-----|-------|-----------------------------------------------------------------------------------|

| 電源電流                                                  |              |                 |                 |     |       |                                                                                   |

| 1 MHz, A グレード及び B グレード                                | $I_{DD1}$    |                 | 3.5             | 5.2 | mA    | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 1 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$  |

|                                                       | $I_{DD2}$    |                 | 6.8             | 9   | mA    | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 1 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$  |

| 17 MHz, B グレード                                        | $I_{DD1}$    |                 | 12.5            | 15  | mA    | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 17 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$ |

|                                                       | $I_{DD2}$    |                 | 14              | 16  | mA    | $C_L = 0 \text{ pF}$ , $DR_{FAST} = 17 \text{ MHz}$ , $DR_{SLOW} = 0 \text{ MHz}$ |

| DC 仕様                                                 |              |                 |                 |     |       |                                                                                   |

| MCLK, <u>MSS</u> , MO, SO, $V_{IA}$ , $V_{IB}$        |              |                 |                 |     |       |                                                                                   |

| 入力スレッショルド                                             |              |                 |                 |     |       |                                                                                   |

| ロジック・ハイ                                               | $V_{IH}$     | 0.7 × $V_{DDx}$ |                 |     | V     |                                                                                   |

| ロジック・ロー                                               | $V_{IL}$     |                 | 0.3 × $V_{DDx}$ |     | V     |                                                                                   |

| 入力ヒステリシス                                              | $V_{IHYST}$  |                 | 500             |     | mV    |                                                                                   |

| チャンネル当たり入力電流                                          | $I_I$        | -1              | +0.01           | +1  | μA    | $0 \text{ V} \leq V_{INPUT} \leq V_{DDx}$                                         |

| SCLK, <u>SSS</u> , MI, SI, $V_{OA}$ , $V_{OB}$ , DCLK |              |                 |                 |     |       |                                                                                   |

| 出力電圧                                                  |              |                 |                 |     |       |                                                                                   |

| ロジック・ハイ                                               | $V_{OH}$     | $V_{DDx} - 0.1$ | 5.0             |     | V     | $I_{OUTPUT} = -20 \mu\text{A}$ , $V_{INPUT} = V_{IH}$                             |

|                                                       |              | $V_{DDx} - 0.4$ | 4.8             |     | V     | $I_{OUTPUT} = -4 \text{ mA}$ , $V_{INPUT} = V_{IH}$                               |

| ロジック・ロー                                               | $V_{OL}$     |                 | 0.0             | 0.1 | V     | $I_{OUTPUT} = 20 \mu\text{A}$ , $V_{INPUT} = V_{IL}$                              |

|                                                       |              |                 | 0.2             | 0.4 | V     | $I_{OUTPUT} = 4 \text{ mA}$ , $V_{INPUT} = V_{IL}$                                |

| $V_{DD1}$ , $V_{DD2}$ 低電圧ロックアウト                       | <u>UVLO</u>  |                 | 2.6             |     | V     |                                                                                   |

| 全低速チャンネルに対する電源電流                                      |              |                 |                 |     |       |                                                                                   |

| サイド1 静止電流 $t$                                         | $I_{DD1(Q)}$ |                 | 2.9             |     | mA    |                                                                                   |

| サイド2 静止電流                                             | $I_{DD2(Q)}$ |                 | 6.1             |     | mA    |                                                                                   |

| AC 仕様                                                 |              |                 |                 |     |       |                                                                                   |

| 出力立ち上がり／立下り時間                                         | $t_R/t_F$    |                 | 2.5             |     | ns    | 10%から 90%まで                                                                       |

| コモンモード過渡電圧耐性 <sup>4</sup>                             | $ CM $       | 25              | 35              |     | kV/μs | $V_{INPUT} = V_{DDx}$ , $V_{CM} = 1000 \text{ V}$ , 過渡電圧 = 800 V                  |

<sup>1</sup>  $V_{DDx} = V_{DD1}$  または  $V_{DD2}$ 。<sup>2</sup>  $V_{INPUT}$  は、MCLK, MSS, MO, SO,  $V_{IA}$ , または  $V_{IB}$  ピンのいずれかの入力電圧です。<sup>3</sup>  $I_{OUTPUT}$  は、SCLK, DCLK, SSS, MI, SI,  $V_{OA}$ , または  $V_{OB}$  ピンのいずれかの出力電流です。<sup>4</sup>  $|CM|$  は、出力電圧を  $V_{OH}$  と  $V_{OL}$  の制限以内に維持できるコモンモード電圧の最大スルーレートです。

## パッケージ特性

表 10

| パラメータ                    | 記号               | Min | Typ              | Max | 単位   | テスト条件／コメント       |

|--------------------------|------------------|-----|------------------|-----|------|------------------|

| 抵抗 (入力-出力間) <sup>1</sup> | R <sub>I-O</sub> |     | 10 <sup>12</sup> |     | Ω    |                  |

| 容量 (入力-出力間) <sup>1</sup> | C <sub>I-O</sub> |     | 1.0              |     | pF   | f = 1 MHz        |

| 入力容量 <sup>2</sup>        | C <sub>I</sub>   |     | 4.0              |     | pF   |                  |

| IC 接合-ケース間の熱抵抗           | θ <sub>JA</sub>  |     | 46               |     | °C/W | パッケージ中央真下に熱電対を装着 |

<sup>1</sup> デバイスは 2 ピンデバイスと見なします。すなわち、ピン 1～ピン 8 を相互に接続し、ピン 9～ピン 16 を相互に接続します。

<sup>2</sup> 入力容量は任意の入力データ・ピンとグラウンド間で測定。

## 適用規格

ADuM4150 は表 11 に示す機関から認定済み、または認定を申請中です。特定のクロスアイソレーション波形と絶縁レベルに対する推奨最大動作電圧については、表 16 及び絶縁寿命のセクションを参照してください。

表 11

| UL                                                                             | CSA                                                                                                                                                                                                                                                 | VDE (申請中)                                                                                                   |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| UL 1577 部品認定プログラムによる認定 <sup>1</sup><br>5000 V rms シングル・プロテクション<br>File E214100 | CSA 部品受入通知#5A、<br>CSA 60950-1-07+A1 および IEC 60950-1 による基本絶縁、800 V rms (1131 V peak) 最大動作電圧 <sup>3</sup><br>CSA 60950-1-07+A1 および IEC 60950-1, 400 V rms (565 V peak) 最大動作電圧<br>IEC 60601-1 による強化絶縁、<br>250 V rms (353 V peak)、最大動作電圧<br>File 205078 | DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 による認定 <sup>2</sup><br>強化絶縁、846 V peak<br>File 2471900-4880-0001 |

<sup>1</sup> UL 1577 に従い、各モデルは 6000 V rms の絶縁試験電圧を 1 秒間印加する耐圧試験が行われます (電流リーク検出限界 = 5 μ A)。

<sup>2</sup> DIN V VDE V 0884-10 に基づき、各モデルは 1590 V peak の絶縁試験電圧を 1 秒間印加する耐圧試験が行われます (部分放電の検出規定値=5 pC)。The asterisk 素子上のアスタリスク (\*) マークは、DIN V VDE V 0884-10 認定製品を表します。

<sup>3</sup> 400 VAC RMS を超える動作電圧の使用は、アイソレータの寿命を著しく短縮する可能性があります。AC 及び DC 条件の下での推奨最大動作電圧については、表 16 を参照してください。

## 絶縁および安全性関連の仕様

表 12

| パラメータ               | 記号     | 値     | 単位     | 条件                               |

|---------------------|--------|-------|--------|----------------------------------|

| 定格誘電体絶縁電圧           |        | 5000  | V rms  | 1 分間                             |

| 最小外部空間距離 (クリアランス)   | L(I01) | 8.3   | mm min | 入力ピンから出力ピンまでの空間最短距離を測定           |

| 最小外部沿面間距離 (クリページ)   | L(I02) | 8.3   | mm min | 入力ピンから出力ピンまでのボディ表面に沿う最短パスを測定     |

| 最小内部空間距離 (内部クリアランス) | CTI    | 0.017 | mm min | 絶縁体を通過する絶縁距離                     |

| 耐トラッキング性 (トラッキング指数) |        | >400  | V      | DIN IEC 112/VDE 0303 Part 1      |

| 絶縁グループ              |        | II    |        | 絶縁グループ (DIN VDE 0110, 1/89, 表 1) |

## DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 絶縁特性

このアイソレータは、安全性制限値データ以内でのみ強化された電気的絶縁に対して有効です。安全性データの維持は、保護回路によって確実にされます。パッケージ上のアスタリスク (\*) マークは、DIN V VDE V 0884-10 認定製品を表します。

表 13

| 項目                                   | テスト条件/コメント                                                                                                                      | 記号          | 特性      | 単位     |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------|---------|--------|

| DIN VDE 0110 による絶縁分類                 |                                                                                                                                 |             |         |        |

| 定格メイン電圧 $\leq 150 \text{ V rms}$ の場合 |                                                                                                                                 | I-IV        |         |        |

| 定格メイン電圧 $\leq 300 \text{ V rms}$ の場合 |                                                                                                                                 | I-III       |         |        |

| 定格メイン電圧 $\leq 400 \text{ V rms}$ の場合 |                                                                                                                                 | I-II        |         |        |

| 環境による分類                              |                                                                                                                                 | 40/105/21   |         |        |

| 汚染度(DIN VDE 0110, Table 1)           |                                                                                                                                 | 2           |         |        |

| 最大動作絶縁電圧                             |                                                                                                                                 | $V_{IORM}$  | 846     | V peak |

| 入力-出力間テスト電圧、メソッド b1                  | $V_{IORM} \times 1.875 = V_{pd(m)}$ , 100% 出荷テスト、<br>$t_{ini} = t_m = 1 \text{ sec}$ 、部分放電 $< 5 \text{ pC}$                     | $V_{pd(m)}$ | 1590    | V peak |

| 入力-出力間テスト電圧、メソッド a                   | $V_{IORM} \times 1.5 = V_{pd(m)}$ , $t_{ini} = 60 \text{ sec}$ , $t_m = 10 \text{ sec}$ ,<br>partial discharge $< 5 \text{ pC}$ | $V_{pd(m)}$ | 1375    | V peak |

| 環境テスト・サブグループ 1 の後                    | $V_{IORM} \times 1.2 = V_{pd(m)}$ , $t_{ini} = 60 \text{ sec}$ , $t_m = 10 \text{ sec}$ ,<br>部分放電 $< 5 \text{ pC}$              | $V_{pd(m)}$ | 1018    | V peak |

| 入力および/または安全性テスト・サブグループ 2,3 の後        |                                                                                                                                 | $V_{IOTM}$  | 7000    | V peak |

| 最大許容過電圧                              |                                                                                                                                 | $V_{IOSM}$  | 6000    | V peak |

| サージ絶縁電圧                              | $V_{IOSM(TEST)} = 10 \text{ kV}$ 、 $1.2 \mu\text{s}$ 立ち上がり時間、 $50 \mu\text{s}$ , 50% 立下り時間                                      |             |         |        |

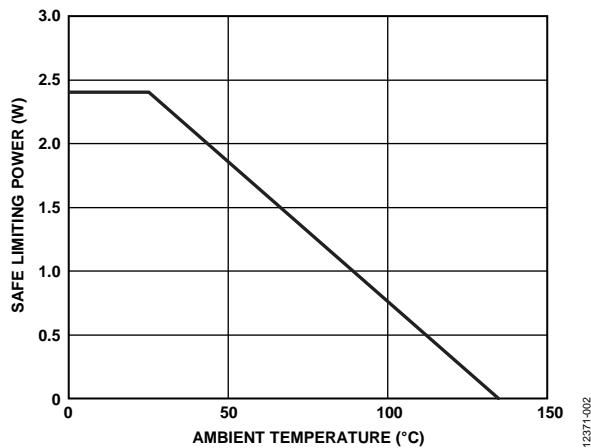

| 安全性制限値                               | 故障時に許容できる最大値 (図 2 参照)                                                                                                           | $T_s$       | 135     | °C     |

| ケース温度                                |                                                                                                                                 | $P_s$       | 2.4     | W      |

| 安全な全消費電力                             |                                                                                                                                 | $R_s$       | $>10^9$ | Ω      |

| $T_s$ での絶縁抵抗                         | $V_{IO} = 500 \text{ V}$                                                                                                        |             |         |        |

図 2 温度ディレーティング・カーブ、DIN V VDE V 0884-10 による

安全な規定値のケース温度に対する依存性。

## 推奨動作条件

表 14

| パラメータ                             | 記号                       | 値               |

|-----------------------------------|--------------------------|-----------------|

| Operating Temperature Range       | $T_A$                    | -40°C to +125°C |

| Supply Voltage Range <sup>1</sup> | $V_{DD1}$ ,<br>$V_{DD2}$ | 3.0 V to 5.5 V  |

| Input Signal Rise/Fall Times      |                          | 1.0 ms          |

<sup>1</sup> 外部磁界耐性については、DC 精度と磁界耐性のセクションを参照してください。

## 絶対最大定格

特に指定のない限り、 $T_A = 25^\circ\text{C}$

表 15

| パラメータ                                                         | 定格 <sup>1</sup>            |

|---------------------------------------------------------------|----------------------------|

| 保存温度 ( $T_{ST}$ ) 範囲                                          | -65°C ~ +150°C             |

| 動作時周囲温度 ( $T_A$ ) 範囲                                          | -40°C ~ +125°C             |

| 電源電圧 ( $V_{DD1}, V_{DD2}$ )                                   | -0.5 V ~ +7.0 V            |

| 入力電圧 ( $V_{IA}, V_{IB}, MCLK, MO, SO, \overline{MSS}$ )       | -0.5V ~ $V_{DDx} + 0.5$ V  |

| 出力電圧 ( $SCLK, DCLK, \overline{SSS}, MI, SI, V_{OA}, V_{OB}$ ) | -0.5 V ~ $V_{DDx} + 0.5$ V |

| ピン当たりの平均出力電流 <sup>2</sup>                                     | -10 mA ~ +10 mA            |

| コモンモード過渡電圧 <sup>3</sup>                                       | -100 kV/μs ~ +100 kV/μs    |

<sup>1</sup>  $V_{DDx} = V_{DD1}$  または  $V_{DD2}$ 。

<sup>2</sup> 温度に対する最大安全定格電流値については図 2 を参照してください。

<sup>3</sup> 絶縁障壁にまたがるコモンモード過渡電圧を表します。絶対最大定格を超えるコモン・モード・トランジエントは、ラッチアップまたは永久故障の原因になります。

上記の絶対最大定格またはそれ以上のストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上のデバイスの動作を定めたものではありません。デバ

イスを長時間最大動作条件以上で動作させるとデバイスの信頼性に影響を与えます。

表 16 最大連続動作電圧<sup>1</sup>

| パラメータ       | 値           | 制約                                              |

|-------------|-------------|-------------------------------------------------|

| 60 Hz AC 電圧 | 400 V rms   | 故障率 0.1%、平均電圧ゼロでの寿命 20 年                        |

| DC 電圧       | 1173 V peak | パッケージの沿面距離、汚染度 2、絶縁グループ II による制限 <sup>2,3</sup> |

<sup>1</sup> 詳細については、絶縁寿命のセクションを参照してください。

<sup>2</sup> 他の汚染度及び絶縁グループの要求条件では制限値が異なります。

<sup>3</sup> システム・レベルの標準によっては、印刷配線基板 (PWB) の沿面距離の使用を認める場合もあります。そのような標準の場合は、サポートされる DC 電圧はより高くなることがあります。

## ESD に関する注意

ESD(静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

## ピン配置および機能説明

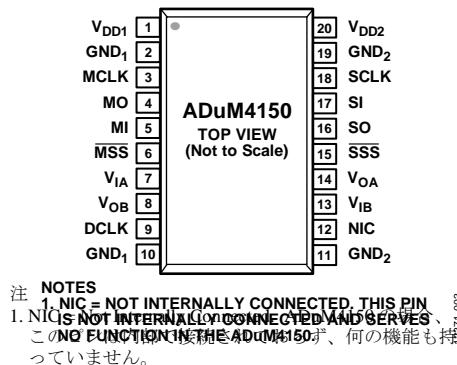

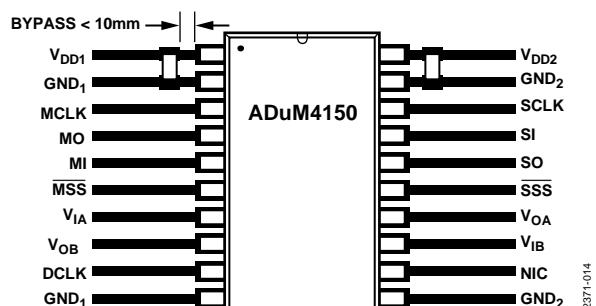

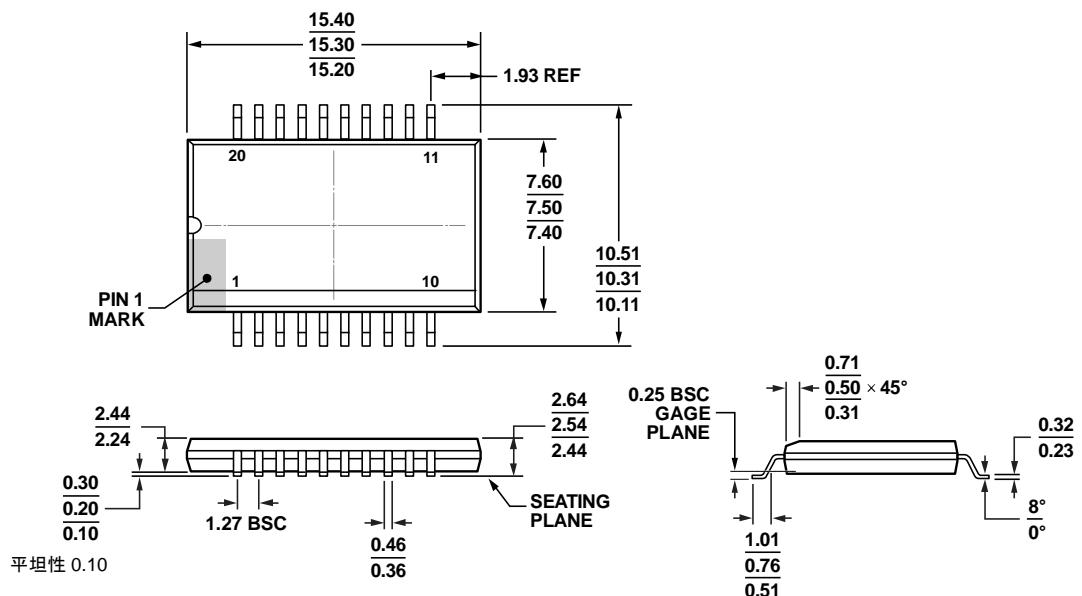

図 3. ピン配置

表 17. ピン機能の説明

| ピン番号  | 記号               | 方向     | 説明                                                                                                           |

|-------|------------------|--------|--------------------------------------------------------------------------------------------------------------|

| 1     | V <sub>DD1</sub> | Power  | アイソレータ、サイド 1 の電源入力ピン。V <sub>DD1</sub> と GND <sub>1</sub> およびローカル・グラウンドの間にバイパス・コンデンサを接続する必要があります。             |

| 2,10  | GND <sub>1</sub> | Return | グラウンド 1。アイソレータ、サイド 1 の基準グラウンド。                                                                               |

| 3     | MCLK             | Clock  | マスター・コントローラからの SPI クロック。                                                                                     |

| 4     | MO               | Input  | マスターからスレーブ MO/SI ラインへの SPI データ。                                                                              |

| 5     | MI               | Output | スレーブからマスター MI/SO ラインへの SPI データ。                                                                              |

| 6     | MSS              | Input  | マスターからのスレーブ選択。この信号はアクティブ・ロー論理を使用しています。スレーブ選択ピンは、速度グレードによっては次のクロックまたはデータのエッジから最大 10ns のセットアップ時間が必要となる場合があります。 |

| 7     | V <sub>IA</sub>  | Input  | 低速データ入力 A。                                                                                                   |

| 8     | V <sub>OB</sub>  | Output | 低速データ出力 B。                                                                                                   |

| 9     | DCLK             | Output | 遅延クロック出力。このピンは MCLK の遅延されたコピーを出力します。                                                                         |

| 11,19 | GND <sub>2</sub> | Return | グラウンド 2。アイソレータ、サイド 2 の基準グラウンド。                                                                               |

| 12    | NIC              | None   | 内部接続なし。このピンは内部で接続されておらず、ADuM4150 では何の機能も持っていない。                                                              |

| 13    | V <sub>IB</sub>  | Input  | 低速データ入力 B。                                                                                                   |

| 14    | V <sub>OA</sub>  | Output | 低速データ出力 A。                                                                                                   |

| 15    | SSS              | Output | スレーブへのスレーブ選択。この信号はアクティブ・ロー論理を使用しています。                                                                        |

| 16    | SO               | Input  | スレーブからマスター MI/SO ラインへの SPI データ。                                                                              |

| 17    | SI               | Output | マスターからスレーブ MO/SI ラインへの SPI データ。                                                                              |

| 18    | SCLK             | Output | マスター・コントローラからの SPI クロック。                                                                                     |

| 20    | V <sub>DD2</sub> | Power  | アイソレータ、サイド 2 の電源入力ピン。V <sub>DD2</sub> と GND <sub>2</sub> およびローカル・グラウンドの間にバイパス・コンデンサを接続する必要があります。             |

表 18 電源オフ時のデフォルト状態の真理値表（正論理）<sup>1</sup>

| V <sub>DD1</sub> の状態 | V <sub>DD2</sub> の状態 | サイド 1 出力 | サイド 2 出力 | SSS | コメント                                                |

|----------------------|----------------------|----------|----------|-----|-----------------------------------------------------|

| 電源オフ                 | 電源オン                 | Z        | Z        | Z   | 電源オフ側の出力は、グラウンドから 1 ダイオード電圧降下以内の電位で高インピーダンス状態になります。 |

| 電源オン                 | 電源オフ                 | Z        | Z        | Z   | 電源オフ側の出力は、グラウンドから 1 ダイオード電圧降下以内の電位で高インピーダンス状態になります。 |

<sup>1</sup> Z は高インピーダンス

## 代表的な性能特性

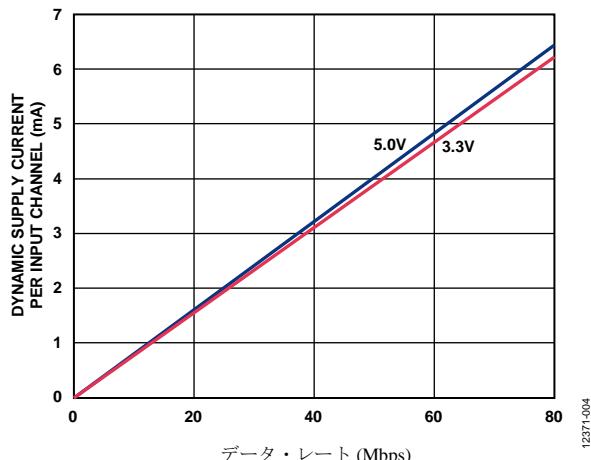

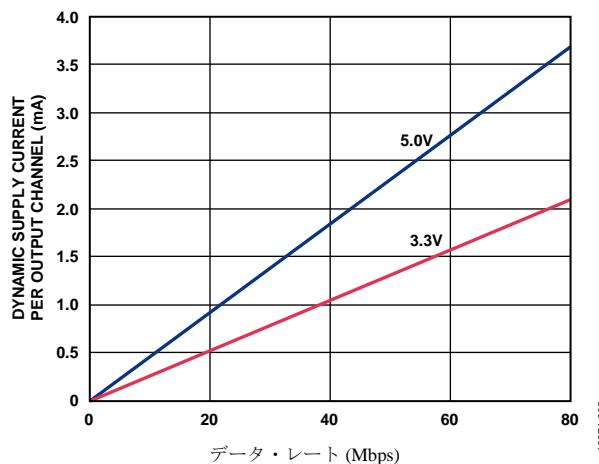

図 4 入力チャンネルあたりの代表的ダイナミック電源電流 対データ・レート、5.0V 及び 3.3V 動作

図 5 出力チャンネルあたりの代表的ダイナミック電源電流対データ・レート、5.0V および 3.3V 動作

出力チャンネルあたりの

ダイナミック電源電流 (mA)

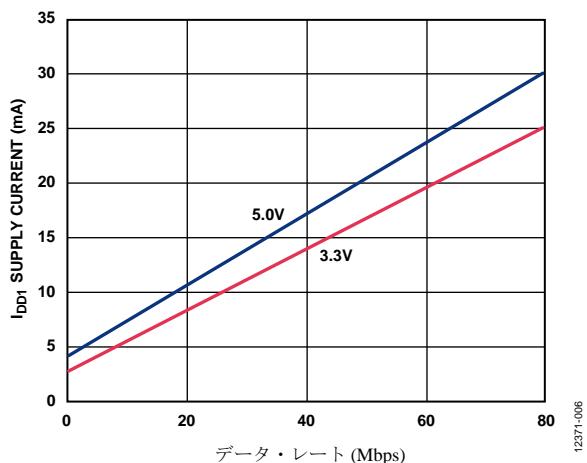

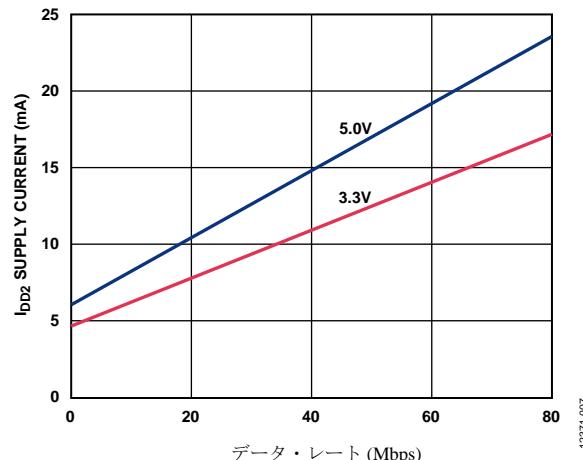

図 7 電源電流  $I_{DD2}$  (Typ) 対 5.0V および 3.3V 動作でのデータ・レート

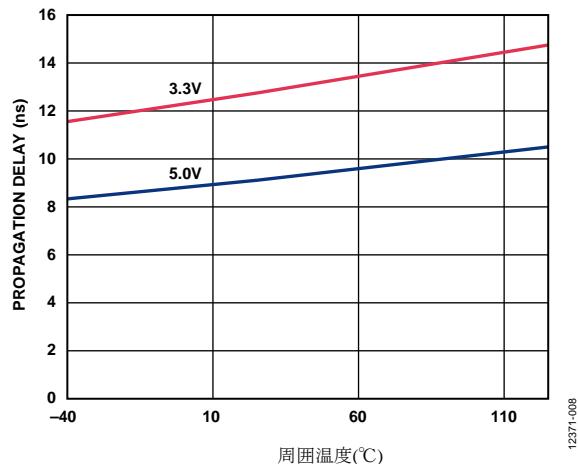

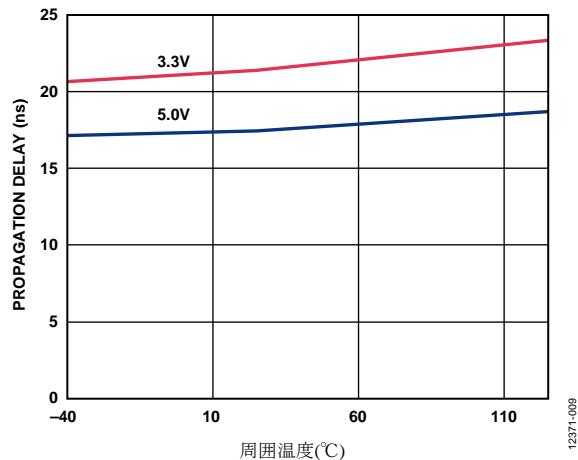

図 8 グリッチ・フィルタがない高速チャンネルでの代表的な伝播遅延時間の温度特性（詳細については高速チャンネルのセクションを参照してください）

図 9. グリッチ・フィルタがある高速チャンネルでの代表的な伝播遅延時間の温度特性（詳細については高速チャンネルのセクションを参照してください）

## アプリケーション情報

### はじめに

ADuM4150 は、高速 SPI の絶縁を最適化し、制御及び状態監視機能のために低速チャンネルも提供するように設計されたデバイス・ファミリの 1 つです。このアイソレータは、高速化及び雑音耐性の向上に向けた差動信号 iCoupler 技術をベースとしています。

### 高速チャンネル

ADuM4150 は 4 つの高速チャンネルを持っています。最初の 3 つのチャンネル、すなわち CLK、MI/SO、及び MO/SI (スラッシュは、SPI バス信号に対応してアイソレータを横切るデータ・パスを形成する特殊な入力及び出力の接続を表します。) は、B グレードでの低伝播遅延または A グレードでの高雑音耐性のいずれかのために最適化されています。A グレードと B グレードの違いは、A グレードにおいてはこれら 3 つのチャンネルにグリッチ・フィルタが追加されていることがあります。B グレード・バージョンは、最大伝播遅延時間が 13ns であり、標準の 4 線 SPI で最大クロック速度 17 MHz をサポートします。しかし、B グレード・バージョンにはグリッチ・フィルタがないため、使用時には 10ns 以下のスプリアス・グリッチが存在しないことを確認してください。

B グレード・デバイスで 10ns 以下のグリッチがあると、グリッチの第二エッジの見逃しを生ずる可能性があります。このパルス条件は、リフレッシュまたは次の有効データ・エッジによって是正される出力上のスプリアス・データ遷移として観測されます。雑音が多い環境の場合は、A グレード・デバイスの使用が推奨されます。

SPI 信号経路と ADuM4150 のピン記号及びデータの方向の関係を表 19 に示します。

表 19 ピン記号と SPI 信号バス名の対応

| SPI 信号経路 | マスター・サイド 1 | データの方向 | スレーブ・サイド 2 |

|----------|------------|--------|------------|

| CLK      | MCLK       | →      | SCLK       |

| MO/SI    | MO         | →      | SI         |

| MI/SO    | MI         | ←      | SO         |

| SS       | MSS        | →      | SSS        |

データ・バスは SPI モードには依存しません。CLK と MO/SI SPI データ経路は伝播遅延及びチャンネル間マッチングに対して最適化されています。MI/SO SPI データ経路は伝播遅延に対して最適化されています。デバイスはクロック・チャンネルに同期しないため、クロックの極性やデータ線に対するタイミングには制約がありません。

SS (スレーブ選択バー) は通常アクティブ・ローの信号です。スレーブ選択バーは、SPI 及び SPI 類似のバスに多くの異なる機能を持つことができます。これらの機能の多くはエッジ・トリガーであり、そのために SS パスには A グレードと B グレードの両方にグリッチ・フィルタが含まれています。グリッチ・フィルタは短いパルスが出力に

伝播したり、動作中に他のエラーを引き起こしたりするのを防ぎます。MSS 信号には、最初のアクティブ・クロック・エッジの前にグリッチ・フィルタに伝播遅延の追加を可能にするために B グレードで 10ns のセットアップ時間が要求されます。

### 低速データ・チャンネル

低速データ・チャンネルは、タイミングがあまり重要でない場合に経済的な絶縁データ毛色として使用することができます。デバイスの与えられた側でのすべての高速及び低速入力の DC 値は同時にサンプリングされ、絶縁コイルを横切ってシフトされます。高速チャンネルは DC 精度が比較され、低速データは適切な低速出力に転送されます。次にデバイスの反対側の入力を読み込み、それらをパケット化し、類似の処理のために送り返すことによってプロセスが逆転されます。高速チャンネルに対する DC の精度のデータは内部で処理され、低速データは同時に出力にクロックされます。

この双方向性データの往復動作は、フリー・ランニングの内部クロックによって制約されます。データはクロックに基づく離散時間でサンプリングされるため、低速チャンネルに対する伝播遅延は 0.1  $\mu$ s から 2.6  $\mu$ s までの間であり、内部サンプリング・クロックに対する入力データ・エッジの変化に依存して変わります。

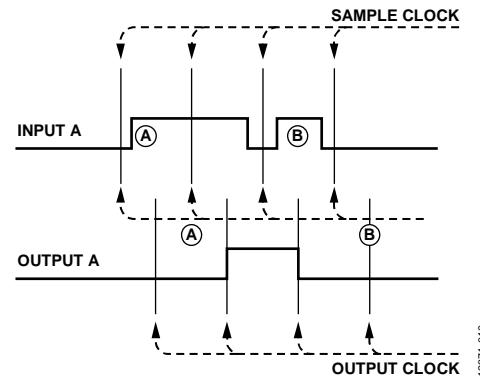

図 10 に、低速チャンネルの動作を示します。

- ポイント A: データはサンプリングされる前に最大 2.6  $\mu$ s 変動し、その後出力まで伝播するのに約 0.1  $\mu$ s かかります。この違いは、伝播遅延時間の 2.5  $\mu$ s の不確定性として現れます。

- ポイント B: 最小低速パルス幅より狭いデータ・パルスはサンプリングされないため、伝播されることはありません。

図 10. 低速チャンネルのタイミング

## 遅延クロック

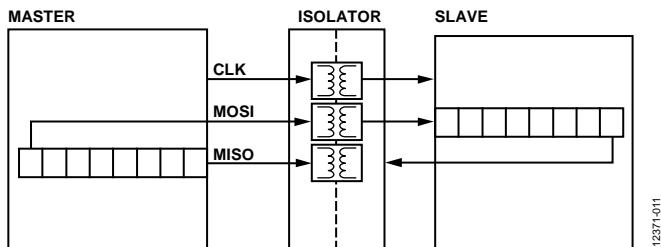

遅延クロック (DCLK)機能により、SPI データを通常伝播遅延によって決められている制限を越えた速度で転送することができます。4 線 SPI アプリケーションでのクロックの最大速度は、データが 1 つのクロック・エッジでシフトアウトし、戻りデータは相補クロック・エッジでシフトアウトするという要求条件によって設定されます。絶縁されたシステムでは、アイソレータでの遅延は重要な意味を持ちます。スレーブにデータを提示するように伝える第一のクロック・エッジはアイソレータを通って伝播する必要があります。スレーブはクロック・エッジに反応し、データはアイソレータ経由で伝播してマスターに戻ります。データがマスターに正しくシフト入力されるためには、データに対する相補クロック・エッジが来る前にマスターに到着していなければなりません。

図 11 に示される例では、アイソレータが 50ns の伝播遅延を持つ場合、応答がスレーブからマスターに到達するためには 100ns 以上の応答時間が必要です。このことは、SPI バスの最速クロック周期は 200ns (5 MHz) であり、簡単に言えば理想的な条件は配線パターンの伝播遅延やスレーブでの遅延がないことを意味しています。

図 11. 標準的な SPI の構成

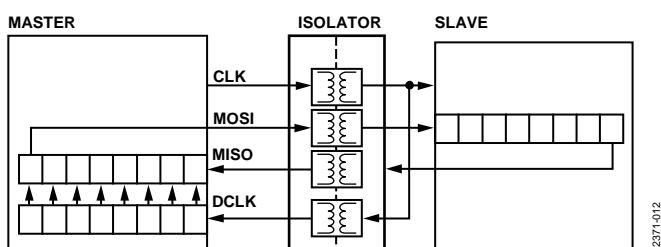

SPI クロックのこの制限は、図 12 に示すように、スレーブから戻ってくるデータに合うように遅延されるクロック信号と一緒に第二の受信バッファを使用することによって回避することができます。クロックの適切な遅延は、マッチング・アイソレータ・チャンネルを通してクロックのコピーを送り返し、スレーブ・データを第二のバッファにシフト入力するために遅延クロックを使用することによって過去に達成されています。追加チャンネルの使用は、高速アイソレータ・チャンネルの使用を伴うためコスト高になります。

図 12. アイソレーション・チャンネルの遅延を用いた高速 SPI の構成

ADuM4150 では、図 13 に示すようにマスター側に遅延回路を搭載することによって別途高速チャンネルを追加する必要性を省いています。DCLK は、出荷試験の際に各アイ

ソレータの往復伝播遅延に合致するように調整されます。この DCLK 信号は、あたかもクロック信号が以前に説明した回路内でスレーブからのデータと並行して伝播したかのように使用することができます。

図 13. 精密なクロック遅延を用いた高速 SPI の構成

この回路構成は、最大 40 MHz 迄のクロックで動作することができます。MI/SO データは DCLK によって第二の受信バッファにシフト入力された後、マスターによって最終目的地まで内部で転送されます。ADuM4150 では、高速なデータ転送速度を得るために別途高価なアイソレータ・チャンネルを追加する必要はありません。図 13 には、簡単化のために SS チャンネルは示されていません。

## プリント回路ボード(PCB)のレイアウト

ADuM4150 デジタル・アイソレータには、ロジック・インターフェース用の外付けインターフェース回路は不要です。V<sub>DD1</sub> ピンと V<sub>DD2</sub> ピンの両方とも、電源バイパス・コンデンサを接続することが推奨されます(図 14 参照)。コンデンサの値は、0.01  $\mu$  F から 0.1  $\mu$  F の間でなければなりません。コンデンサの両端と入力電源ピンとの間のパターン長は 20 mm 以下にする必要があります。

図 14. 推奨 PCB レイアウト

高いコモンモード過渡電圧が発生するアプリケーションでは、アイソレーション障壁を通過するボード結合を最小化することが重要です。さらに、如何なる結合もデバイス側のすべてのピンで等しく発生するように PCB レイアウトをデザインしてください。この注意を怠ると、ピン間で発生する電位差がデバイスの絶対最大定格を超えてしまい、ラッチアップまたは恒久的な損傷が発生することがあります。

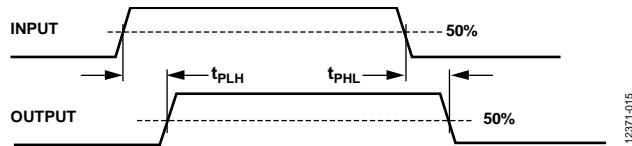

### 伝搬遅延関連のパラメータ

伝搬遅延時間は、ロジック信号がデバイスを通過するのに要する時間を表すパラメータです。高レベルから低レベルへの遷移における入力から出力までの伝搬遅延は、低レベルから高レベルへの遷移における伝搬遅延と異なることがあります。

図 15 伝搬遅延パラメータ

パルス幅歪みとはこれら 2 値の間の最大の差を意味し、入力信号のタイミングが output 信号で再現される精度を表します。

チャンネル間マッチングとは、1 つの ADuM4150 デバイス内にある複数のチャンネル間の伝搬遅延差の最大値を意味します。

### DC 精度と磁界耐性

アイソレータ入力での正および負のロジック変化により、狭いパルス(～1 ns)がトランジスを経由してデコーダに送られます。デコーダは双安定であるため、パルスによるセットまたはリセットにより入力ロジックの変化が表されます。1.2  $\mu$ s 以上入力にロジック変化がない場合、該当する入力状態を表す周期的な更新パルスのセットが出力の DC 精度を確保するために低速チャンネルを経由して送出されます。

低速デコーダが約 5  $\mu$ s 以上この更新パルスを受信しないと、入力側が電源オフであるか非動作状態にあると見なされ、ウォッチドッグ・タイマー回路によりアイソレータ出力が強制的に高インピーダンス(high-Z)状態にされます。

デバイスの磁界耐性の限界は、トランジスの受信側コイルに発生する誘導電圧が十分大きくなり、デコーダをセットまたはリセットさせる誤動作が発生することで決まります。そのような条件は以下の解析で決定されます。ADuM4150 は、この製品が最も誘導電圧の影響を受けやすい 3 V 動作の条件でテストされます。

トランジス出力でのパルスは、1.5 V 以上の振幅になります。デコーダは約 1.0 V の検出スレッショールドを持ったため、誘導電圧に対しては 0.5 V の余裕を持っています。受信側コイルへの誘導電圧は次式で与えられます。

$$V = (-d\beta/dt) \sum \pi r_n^2; n = 1, 2, \dots, N$$

ここで、

$\beta$  は磁束密度(Gauss)、

$r_n$  は受信側コイル巻き数  $n$  回目の半径、

$N$  は受信側コイルの巻き数です。

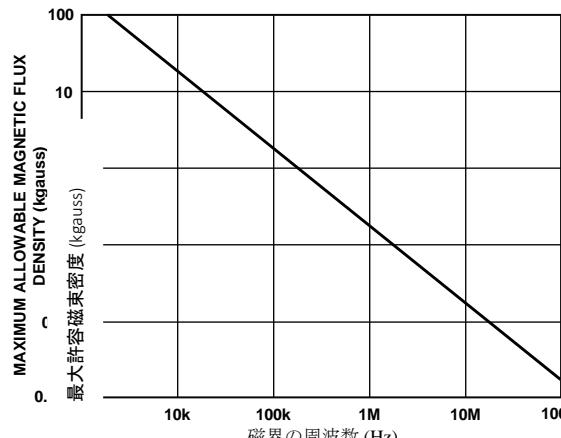

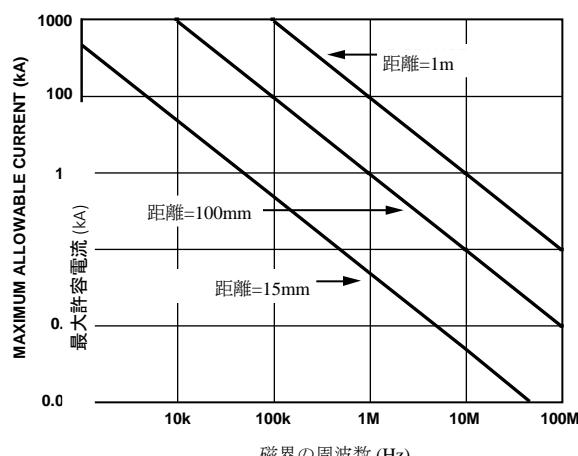

ADuM4150 の受信側コイルの形状が与えられ、かつ誘導電圧がデコーダにおける 0.5 V 余裕の最大 50% であるという条件が与えられると、最大許容磁界は図 16 のように計算されます。

図 16 最大許容外部磁束密度

たとえば、磁界周波数 = 1 MHz で、最大許容磁界 = 0.5 kGauss の場合、受信コイルでの誘導電圧は 0.25 V になります。この電圧は検出スレッショールドの約 50% であるため、出力変化の誤動作はありません。そのようなイベントが発生した場合、最悪ケースの極性でパルス送信中に、干渉によって受信パルスの振幅が 1.0 V 以上から 0.75 V に減少させられます。この電圧はまだデコーダの検出閾値 0.5 V より十分大きいままです。

前述の磁束密度値は、ADuM4150 トランジスからある与えられた距離だけ離れた特定の電流値に対応します。図 17 は、周波数の関数としての許容電流値を、与えられた距離に対して示しています。ADuM4150 は外部電磁界に非常に鈍感です。ADuM4150 が影響される可能性があるのは、素子に非常に近い場所を流れる極めて大きな高周波電流のみです。前述の 1 MHz の例では、0.5 kA の電流を ADuM4150 から 5mm の距離まで近づけると部品動作に影響が生じます。

図 17 ADuM4150 までの距離、及び周波数に対する最大許容電流

強い磁界と高周波が組合わざると、PCB のパターンで形成されるループに十分大きな誤差電圧が誘導されて、後段回路のスレッショールドがトリガーされてしまうことに注意が必要です。ループを形成するような PCB 構造を避けるように注意する必要があります。

## 消費電力

ADuM4150 アイソレータのあるチャンネルの供給電流は、電源電圧、チャンネルのデータ速度、チャンネルの出力負荷、及びそれが高速チャンネルであるか低速チャンネルであるかによって決まります。

低速チャンネルは、内部のピンポン・データ・バスによって生成される一定の静止電流を引き込みます。動作周波数は十分低いため、推奨される容量性負荷が発生する容量性損失は静止電流による損失に比べて無視できます。データ速度の詳細な計算は単純化のために省略されており、低速チャンネルに起因するアイソレータの各側の静止電流は、特定の動作電圧に対してそれぞれ表3、表5、表7、及び表9で見ることができます。これらの静止電流は、アイソレータの各側での全電流に対して以下の式で示されるように高速電流に加算されます。ダイナミック電流は、それぞれの電圧に対して表3及び表5から与えられます。

サイド1では、電源電流は次式で与えられます。

$$\begin{aligned} I_{DD1} = & I_{DD1(D)} \times (f_{MCLK} + f_{MO} + f_{MSS}) + \\ & f_{MI} \times (I_{DDO(D)} + ((0.5 \times 10^{-3}) \times C_{L(MI)} \times V_{DD1})) + \\ & f_{MCLK} \times (I_{DDO(D)} + ((0.5 \times 10^{-3}) \times C_{L(DCLK)} \times V_{DD1})) \\ & + I_{DD1(Q)} \end{aligned}$$

サイド2では、電源電流は次式で与えられます。

$$\begin{aligned} I_{DD2} = & I_{DD2(D)} \times f_{SO} + \\ & f_{SCLK} \times (I_{DDO(D)} + ((0.5 \times 10^{-3}) \times C_{L(SCLK)} \times V_{DD2})) + \\ & f_{SI} \times (I_{DDO(D)} + ((0.5 \times 10^{-3}) \times C_{L(SI)} \times V_{DD2})) + \\ & f_{SSx} \times (I_{DDO(D)} + ((0.5 \times 10^{-3}) \times C_{L(SSx)} \times V_{DD2})) + I_{DD2(Q)} \end{aligned}$$

ここで、

$I_{DD1(D)}$  と  $I_{DDO(D)}$  は、それぞれチャンネル当たりの入力ダイナミック電源電流と出力ダイナミック電源電流です (mA/Mbps)。

$f_x$  は指定されたチャンネルに対する論理信号のデータ速度です (単位は Mbps)。

$C_{L(x)}$  は指定された出力の負荷容量(pF)です。

$V_{DDx}$  は、評価される側の電源電圧(V)です。

$I_{DD1(Q)}$ 、 $I_{DD2(Q)}$  は指定されたサイド1及びサイド2の静止電源電流 (mA)です。

図4と図5はそれぞれ、入力及び無負荷状態の出力に対するデータ・レートの関数としての、チャンネル当たりの代表的ダイナミック電源電流を示します。図6と図7はそれぞれ、同じ速度で動作する高速チャンネル及びアイドル状態の低速チャンネルを持つADuM4150チャンネル構成での、データ・レートの関数としての全  $I_{DD1}$  及び  $I_{DD2}$  電源電流を示します。

## 絶縁部の寿命

すべての絶縁構造は、十分長い時間電圧ストレスを受けるとブレークダウンします。絶縁性能の低下率は、絶縁に加

えられる電圧波形の特性、及び材料と材料インターフェースに依存します。

絶縁性能劣化の原因は、主として空気に曝される表面に沿ってのブレークダウンと絶縁耐力の損耗の2つに分けられます。表面ブレークダウンは、表面トラッキングの現象であり、システム・レベル標準における表面沿面距離要求条件の主要決定要因です。絶縁耐力の損耗は、絶縁材内部への電荷注入または変位電流によって絶縁性能が長期間にわたって次第に劣化して行く現象です。

## 表面トラッキング

表面トラッキングは、電気的安全標準において、動作電圧、環境条件、及び絶縁材の特性に基づいて最小沿面距離を設定することによって対処されます。安全規制当局は、表面絶縁耐力の評価試験を行って、素子を異なった絶縁グループに分類しています。絶縁グループの等級が低いほど表面トラッキングに対する耐性が大きくなり、より小さな沿面距離で適切な絶縁寿命が達成されます。各システム・レベル標準における与えられた動作電圧及び絶縁グループでの最小沿面距離は、絶縁部にかかる全 rms 電圧、汚染の程度、及び絶縁グループに基づいて決定されます。ADuM4150 アイソレータの絶縁グループ及び沿面距離を表12に示します。

## 絶縁耐力の損耗

材料の消耗に伴う絶縁寿命は、その厚さ、材料の特性、及び印加される電圧のストレスによって決定されます。製品の寿命がアプリケーションにおける動作電圧に対して適切であるかどうかを検証することが重要です。損耗に対してアイソレータが保証する動作電圧は、トラッキングに対して保証する動作電圧と同じとは限りません。ほとんどの標準で規定されている動作電圧は、トラッキングに対して適用される動作電圧です。

試験及びモデル解析の結果から、長期的な絶縁耐力低下の主な原因是、ポリイミド絶縁材に漸増的ダメージを生ずる変位電流であることが示されています。絶縁材へのストレスは大別して、変位電流がないため損耗はほとんど生じないDCストレス、及び時間的に変動して損耗を生ずるACストレスに分けられます。保証書に記載される定格は通常、ライン電圧からの絶縁性を反映するストレスである60 Hzの正弦波ストレスに基づいて決められています。

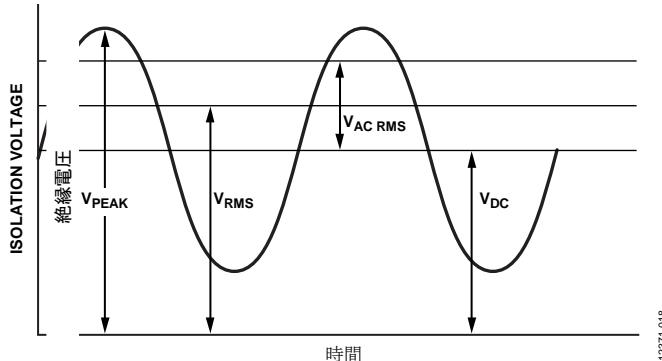

しかし、多くの実際的アプリケーションでは、式(1)に示されるように絶縁障壁にかかる 60 Hz AC と DC 電圧の組み合わせが使用されています。絶縁耐力の損耗を引き起こすのはストレスの交流成分のみであるため、この式は式(2)のように AC rms 電圧を計算するように変形されます。この製品で使用されているポリイミド材に関する絶縁耐力損耗の場合、AC rms 電圧が製品寿命を決定します。

$$V_{RMS} = \sqrt{V_{AC\ RMS}^2 + V_{DC}^2} \quad (1)$$

または

$$V_{AC\ RMS} = \sqrt{V_{RMS}^2 - V_{DC}^2} \quad (2)$$

ここで、

$V_{RMS}$  は合計 rms 動作電圧、

$V_{AC\ RMS}$  は動作電圧の時間変動成分、

$V_{DC}$  は動作電圧のオフセット成分です。

#### パラメータの計算及び使用例

電力変換アプリケーションで頻繁に発生する例を以下に示します。絶縁の片側でのライン電圧が 240V、絶縁の他の側での DC バス電圧が 400V であると仮定します。絶縁材はポリイミドです。沿面距離とデバイスの寿命を決定するための限界電圧を確定するためには、図 18 及び以下の式を参照してください。

12371-018

図 18. 限界電圧の例

絶縁障壁にかかる動作電圧は、式(1)から以下のように計算されます。

$$V_{RMS} = \sqrt{V_{AC\ RMS}^2 + V_{DC}^2}$$

$$V_{RMS} = \sqrt{240^2 + 400^2}$$

$$V_{RMS} = 466 \text{ V rms}$$

この動作電圧 466Vrms は、システム標準によって要求される沿面距離を参照する際に、絶縁グループと汚染の程度と一緒に使用されます。

寿命が適切であるかどうかを判断するためには、動作電圧の時間変動成分を求める必要があります。AC rms 電圧は、式(2)から以下のように計算されます。

$$V_{AC\ RMS} = \sqrt{V_{RMS}^2 - V_{DC}^2}$$

$$V_{AC\ RMS} = \sqrt{466^2 - 400^2}$$

$$V_{AC\ RMS} = 240 \text{ V rms}$$