# キーパッド・デコーダと I/O ポート・エクスパンダ

## データシート

## ADP5586

### 特長

- FIFO で 16 個のイベントを記録可能

- 設定可能な 10 本の I/O によって下記の機能を実現

- 最大 5x5 のマトリクスのキーパッド・デコーディングに対応

- キー・プレス/キー・リリース割込み

- GPIO 機能

- 割込みレベルを選択できる GPI

- 100kΩ または 300kΩ のプルアップ抵抗

- 300kΩ のプルダウン抵抗

- プッシュプルまたはオープン・ドレイン付き GPO

- プログラム可能なロジック・ブロック

- パルス・ジェネレータ

- 周期とオン時間

- 125 ms 単位で 30 分以上

- 1 ms 単位で最大 255 ms

- リセット・ジェネレータ

- 最大 1MHz の Fast-mode Plus (Fm+) に対応した I<sup>2</sup>C インターフェース

- オープン・ドレイン割込み出力

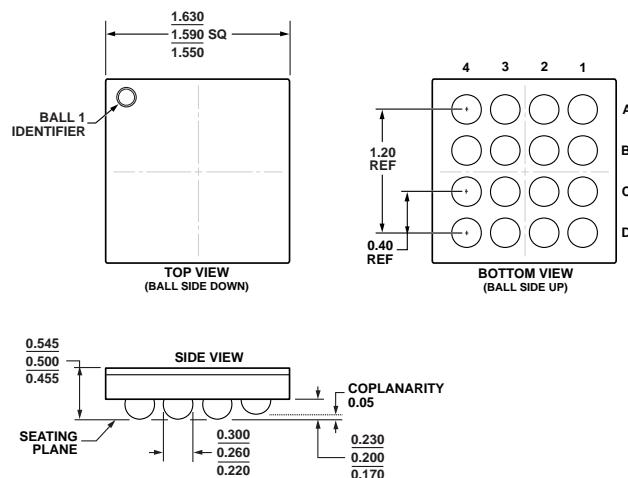

- 16 ポール WLCSP、1.59 mm × 1.59 mm

### アプリケーション

- キーパッド・エントリーと I/O 拡張機能を必要とする機器

- スマートフォン、リモート制御、カメラ

- 健康機器、工業用、計測器

### 概要

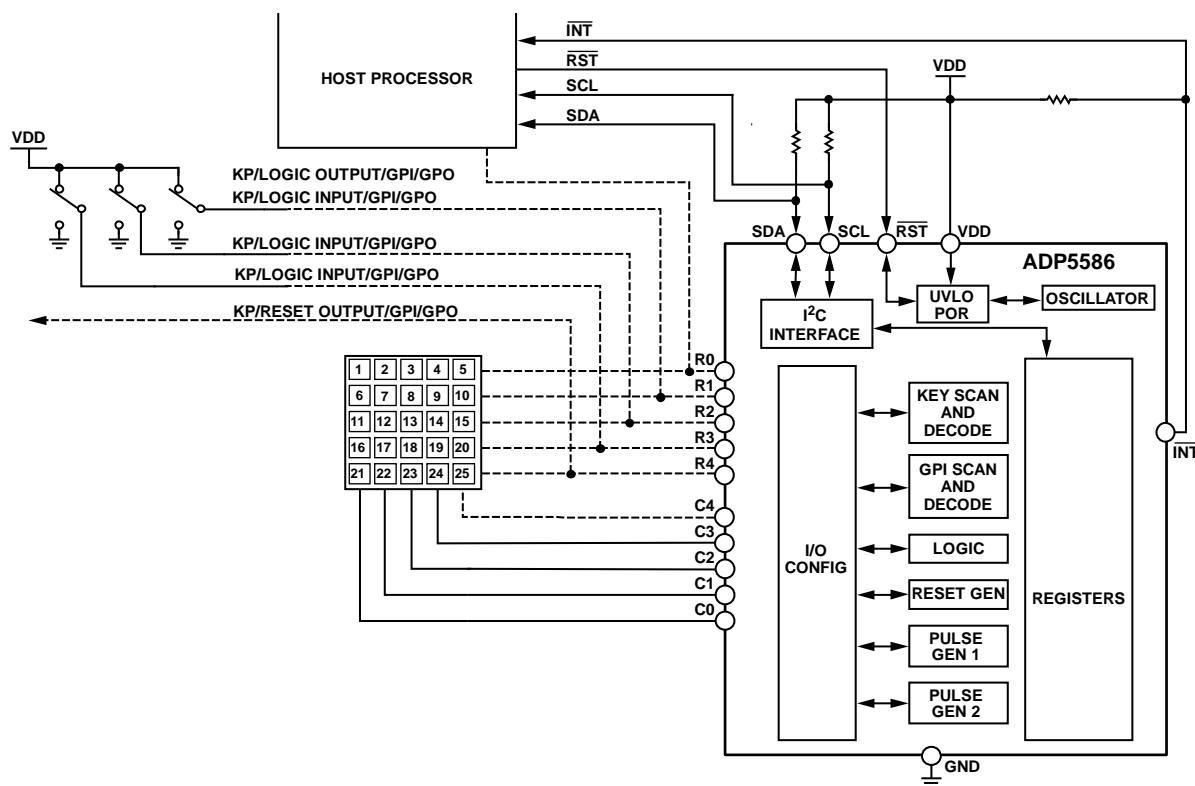

**ADP5586** は、キーパッド・マトリクス・デコーダ、プログラマブル・ロジック、リセット・ジェネレータ、およびパルス・ジェネレータを内蔵した、10 ポートの I/O エキスパンダです。I/O エキスパンダ IC は、携帯機器（電話機、リモコン、カメラなど）や携帯用ではないアプリケーション（健康機器、工業および計測分野など）に使用されます。I/O エキスパンダは、プロセッサで必要な入/出力の数を増やすために使用したり、あるいはフロントパネルの設計のためにインターフェース・コネクタを通して要求される I/O 数を削減するのに使用する事ができます。

**ADP5586** は、全てのキー・スキャニングとデコーディングを処理し、新規のキー・イベントの発生を割込み・ラインを介してメイン・プロセッサに知らせます。GPI の変化とロジックの変

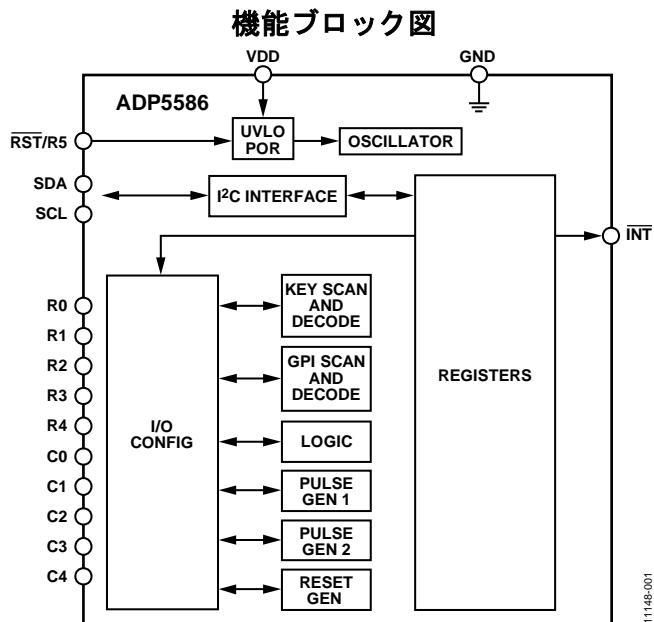

図 1.

11148-001

化は、FIFO を介してイベントとして追跡することも出来るので、イベント変化のたびに異なるレジスタをモニターする必要性がありません。**ADP5586** は、最大 16 イベントまで格納できる FIFO を備えています。プロセッサは、I<sup>2</sup>C 互換インターフェースを介してイベントを読み出す事ができます。

**ADP5586** によってメインのプロセッサはキーパッドを監視する必要がなくなるため、消費電力が低減し、そして/あるいはプロセッサの帯域幅が増大し、他の機能を実行できるようになります。

プログラム可能なロジック機能により、必要な共通ロジックを GPIO エキスパンダの一部として内蔵する事ができるので、ボード面積とコストを節約できます。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                          |   |               |    |

|--------------------------|---|---------------|----|

| 特長                       | 1 | イベント FIFO     | 9  |

| アプリケーション                 | 1 | キー・スキャン制御     | 10 |

| 機能ブロック図                  | 1 | GPI 入力        | 13 |

| 概要                       | 1 | GPO 出力        | 13 |

| 改訂履歴                     | 2 | ロジック・ロック      | 14 |

| 仕様                       | 3 | リセット・ロック      | 15 |

| I <sup>2</sup> C タイミング仕様 | 4 | 割込み           | 15 |

| 絶対最大定格                   | 5 | パルス・ジェネレータ    | 16 |

| 熱抵抗                      | 5 | レジスタ・インターフェース | 17 |

| ESD の注意                  | 5 | レジスタ・マップ      | 19 |

| ピン配置およびピン機能説明            | 6 | レジスタの詳細説明     | 21 |

| 動作原理                     | 7 | アプリケーション図     | 41 |

| デバイス・イネーブル。              | 8 | 外形寸法          | 42 |

| デバイスの概要                  | 8 | オーダー・ガイド      | 42 |

| 機能説明                     | 9 |               |    |

## 改訂履歴

3/13—Revision 0:初版

## 仕様

特に指定のない限り、VDD = 1.8 V～3.3 V、TA = TJ = -40°C～+85°C。<sup>1</sup>

表 1.

| Parameter                                                                                                                                                                   | Symbol               | Test Conditions/Comments                                                          | Min       | Typ       | Max       | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------|-----------|-----------|-----------|------|

| SUPPLY VOLTAGE<br>VDD Input Voltage Range<br>Undervoltage Lockout Threshold                                                                                                 | VDD                  | UVLO active, VDD falling<br>UVLO inactive, VDD rising                             | 1.65      |           | 3.6       | V    |

|                                                                                                                                                                             | UVLO <sub>VDD</sub>  |                                                                                   | 1.2       | 1.3       |           | V    |

|                                                                                                                                                                             |                      |                                                                                   |           | 1.4       | 1.6       | V    |

| SUPPLY CURRENT<br>Standby Current<br>Operating Current (One Key Press)                                                                                                      | I <sub>STNBY</sub>   | VDD = 1.65 V<br>VDD = 3.3 V                                                       |           | 1         | 4         | μA   |

|                                                                                                                                                                             | I <sub>SCAN1</sub>   | Scan = 10 ms, CORE_FREQ = 50 kHz,<br>scan active, 300 kΩ pull-up,<br>VDD = 1.65 V |           | 1         | 10        | μA   |

|                                                                                                                                                                             | I <sub>SCAN2</sub>   | Scan = 10 ms, CORE_FREQ = 50 kHz,<br>scan active, 300 kΩ pull-up,<br>VDD = 3.3 V  |           | 30        | 40        | μA   |

| PULL-UP, PULL-DOWN RESISTANCE<br>Pull-Up<br>Option 1<br>Option 2<br>Pull-Down                                                                                               |                      |                                                                                   | 75        | 85        |           | μA   |

|                                                                                                                                                                             |                      |                                                                                   | 50        | 100       | 150       | kΩ   |

|                                                                                                                                                                             |                      |                                                                                   | 150       | 300       | 450       | kΩ   |

| INPUT LOGIC LEVEL (RST, SCL, SDA, R0, R1,<br>R2, R3, R4, R5, C0, C1, C2, C3, C4)<br>Input Voltage<br>Logic Low<br>Logic High<br>Input Leakage Current (Per Pin)             | V <sub>IL</sub>      |                                                                                   |           | 0.7 × VDD | 0.3 × VDD | V    |

|                                                                                                                                                                             | V <sub>IH</sub>      |                                                                                   |           |           | 0.1       | V    |

|                                                                                                                                                                             | V <sub>I-LEAK</sub>  |                                                                                   |           |           | 1         | μA   |

| PUSH-PULL OUTPUT LOGIC LEVEL (R0, R1,<br>R2, R3, R4, R5, C0, C1, C2, C3, C4)<br>Output Voltage<br>Logic Low<br>Logic High<br>Logic High Output Leakage Current<br>(Per Pin) | V <sub>OL1</sub>     | Sink current = 10 mA, maximum of<br>five GPIOs active simultaneously              |           |           | 0.4       | V    |

|                                                                                                                                                                             | V <sub>OL2</sub>     | Sink current = 10 mA, all GPIOs active<br>simultaneously                          |           |           | 0.5       | V    |

|                                                                                                                                                                             | V <sub>OH</sub>      | Source current = 5 mA                                                             | 0.7 × VDD | 0.1       | 1         | V    |

| OPEN-DRAIN OUTPUT LOGIC LEVEL<br>(INT, SDA)<br>Output Voltage<br>Logic Low<br>INT<br>SDA<br>Logic High Output Leakage Current (Per Pin)                                     | V <sub>OL3</sub>     | I <sub>SINK</sub> = 10 mA                                                         |           |           | 0.4       | V    |

|                                                                                                                                                                             | V <sub>OL4</sub>     | I <sub>SINK</sub> = 20 mA                                                         |           |           | 0.4       | V    |

|                                                                                                                                                                             | V <sub>OH-LEAK</sub> |                                                                                   |           | 0.1       | 1         | μA   |

| Logic Propagation Delay<br>Flip-Flop (FF) Hold Time <sup>2</sup><br>FF Setup Time <sup>2</sup><br>GPIO Debounce <sup>2</sup><br>Internal Oscillator Frequency <sup>3</sup>  |                      |                                                                                   |           | 125       | 300       | ns   |

|                                                                                                                                                                             |                      |                                                                                   |           | 0         |           | ns   |

|                                                                                                                                                                             |                      |                                                                                   |           | 175       |           | ns   |

|                                                                                                                                                                             |                      |                                                                                   |           |           | 70        | μs   |

|                                                                                                                                                                             |                      |                                                                                   | 720       | 800       | 880       | kHz  |

|                                                                                                                                                                             | OSC <sub>FREQ</sub>  |                                                                                   |           |           |           |      |

<sup>1</sup> 限界温度におけるすべての限界値は、標準の統計的品質管理(SQC)を使用した相関によって保証されています。Typ 値は TA = 25°C、VDD = 1.8 V での値です。

<sup>2</sup> 設計上で保証します。

<sup>3</sup> すべてのタイマーはベース発振器を基準とし、同じ±10%の精度を持ちます。

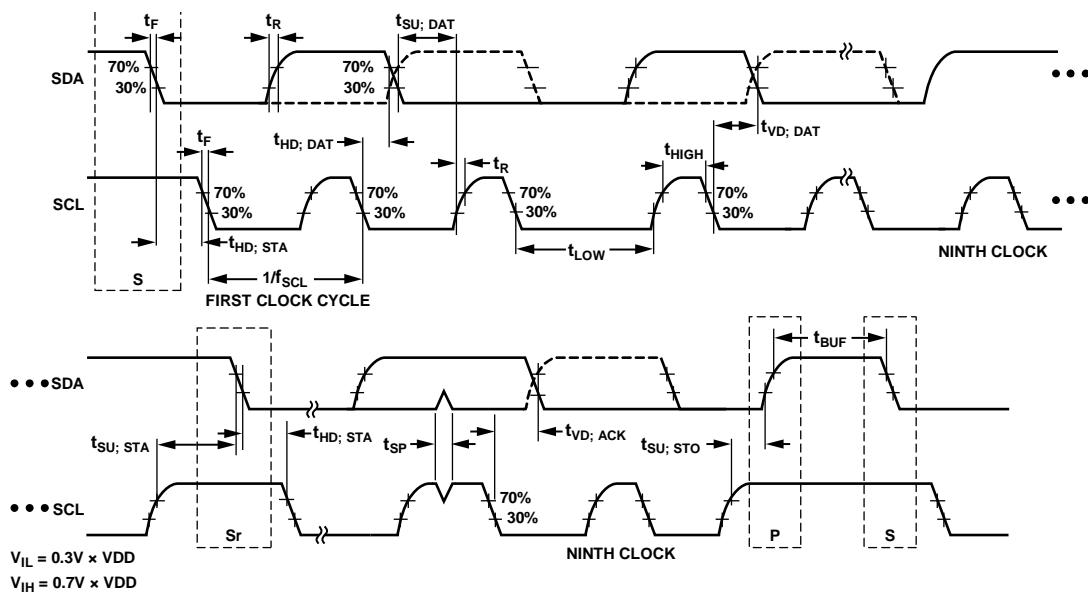

**I<sup>2</sup>C タイミング仕様**

表 2.

| Parameter                                               | Description                                 | Min  | Max  | Unit |

|---------------------------------------------------------|---------------------------------------------|------|------|------|

| I <sup>2</sup> C TIMING SPECIFICATIONS                  |                                             |      |      |      |

| Delay from UVLO/RST Inactive to I <sup>2</sup> C Access |                                             |      | 60   | μs   |

| f <sub>SCL</sub>                                        | SCL clock frequency                         | 0    | 1000 | kHz  |

| t <sub>HIGH</sub>                                       | SCL high time                               | 0.26 |      | μs   |

| t <sub>LOW</sub>                                        | SCL low time                                | 0.5  |      | μs   |

| t <sub>SU; DAT</sub>                                    | Data setup time                             | 50   |      | ns   |

| t <sub>HD; DAT</sub>                                    | Data hold time                              | 0    |      | μs   |

| t <sub>SU; STA</sub>                                    | Setup time for repeated start               | 0.26 |      | μs   |

| t <sub>HD; STA</sub>                                    | Hold time for start/repeated start          | 0.26 |      | μs   |

| t <sub>BUF</sub>                                        | Bus free time for stop and start conditions | 0.5  |      | μs   |

| t <sub>SU; STO</sub>                                    | Setup time for stop condition               | 0.26 |      | μs   |

| t <sub>VD; DAT</sub>                                    | Data valid time                             |      | 0.45 | μs   |

| t <sub>VD; ACK</sub>                                    | Data valid acknowledge                      |      | 0.45 | μs   |

| t <sub>R</sub>                                          | Rise time for SCL and SDA                   |      | 120  | ns   |

| t <sub>F</sub>                                          | Fall time for SCL and SDA                   |      | 120  | ns   |

| t <sub>SP</sub>                                         | Pulse width of suppressed spike             | 0    | 50   | ns   |

| C <sub>B</sub> <sup>1</sup>                             | Capacitive load for each bus line           |      | 550  | pF   |

<sup>1</sup> C<sub>B</sub>は、1本のバス・ラインの合計容量(pF)です。

**タイミング図**

11148-002

図 2. I<sup>2</sup>C インターフェースのタイミング図

## 絶対最大定格

表 3.

| Parameter                                                                  | Rating                      |

|----------------------------------------------------------------------------|-----------------------------|

| VDD to GND                                                                 | -0.3 V to +4 V              |

| SCL, SDA, <u>RST</u> , <u>INT</u> , R0, R1, R2, R3, R4, C0, C1, C2, C3, C4 | -0.3 V to (VDD + 0.3 V)     |

| Temperature Range                                                          |                             |

| Operating (Ambient)                                                        | -40°C to +85°C <sup>1</sup> |

| Operating (Junction)                                                       | -40°C to +125°C             |

| Storage                                                                    | -65°C to +150°C             |

消費電力が大きくかつ熱抵抗が大きなアプリケーションでは、最大周囲温度を下げる必要があります。最大周囲温度( $T_A(MAX)$ )は最大動作ジャンクション温度( $T_J(MAXOP) = 125^\circ\text{C}$ )、デバイスの最大消費電力( $P_D(MAX)$ )、アプリケーション上のデバイス/パッケージのジャンクション-周囲間熱抵抗( $\theta_{JA}$ )に依存し、次の式が成立します。 $T_A(MAX) = T_J(MAXOP) - (\theta_{JA} \times P_D(MAX))$ 。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作の節に記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に晒すとデバイスの信頼性に影響を与える可能性があります。

絶対最大定格は、組み合わせではなく個別に適用されます。特に注記がない限り、すべての電圧は GND を基準にします。

## 熱抵抗

$\theta_{JA}$  はワーストケース条件、つまり表面実装型パッケージの場合、デバイスを回路基板(PCB)にハンダ付けした状態で規定されます。

表 4.

| Thermal Resistance        | $\theta_{JA}$ | Unit |

|---------------------------|---------------|------|

| 16-Ball WLCSP             | 62            | °C/W |

| Maximum Power Dissipation | 70            | mW   |

## ESD の注意

ESD (静電放電) の影響を受けやすいデバイスです。充電したデバイスや回路基板が検知されないまま放電する事があります。本製品は当社独自の ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

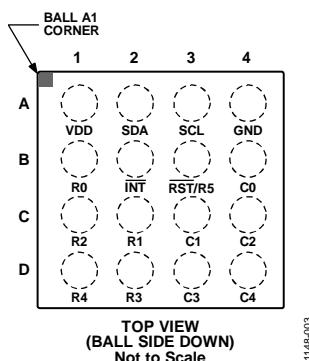

## ピン配置およびピン機能説明

図 3. ピン配置

表 5 ピン機能の説明

| ピン番号 | 記号            | 説明                                                                                                                 |

|------|---------------|--------------------------------------------------------------------------------------------------------------------|

| A1   | VDD           | 電源入力。                                                                                                              |

| A2   | SDA           | I <sup>2</sup> C データ入力/出力。                                                                                         |

| A3   | SCL           | I <sup>2</sup> C のクロック入力。                                                                                          |

| A4   | GND           | グラウンド。                                                                                                             |

| B1   | R0            | GPIO 1 (GPIO の代替機能 : ロジック・ブロック出力 LY)。キーパッド・モードに設定した時、このピンは行 0 として機能します。                                            |

| B2   | <u>INT</u>    | オープン・ドレイン割込み出力。                                                                                                    |

| B3   | <u>RST/R5</u> | 入力リセット信号(RST)。リセット信号機能は ADP5586ACBZ-01-R7 を除くすべてのモデルに適用されます。<br>GPIO 6/Row 5 (R5)。この機能は ADP5586ACBZ-01-R7 モデルにのみ適用 |

| B4   | C0            | GPIO 7 (GPIO の代替機能 : PULSE_GEN_1)。キーパッド・モードに設定した時、このピンは列 0 として機能します。                                               |

| C1   | R2            | GPIO 3 (GPIO の代替機能 : ロジック・ブロック入力 LB)。キーパッド・モードに設定した時、このピンは行 2 として機能します。                                            |

| C2   | R1            | GPIO 2 (GPIO の代替機能 : ロジック・ブロック入力 LA)。キーパッド・モードに設定した時、このピンは行 1 として機能します。                                            |

| C3   | C1            | GPIO 8 (GPIO の代替機能 : PULSE_GEN_2)。キーパッド・モードに設定した時、このピンは列 1 として機能します。                                               |

| C4   | C2            | GPIO 9。キーパッド・モードに設定した時、このピンは列 2 として機能します。                                                                          |

| D1   | R4            | GPIO 5 (GPIO の代替機能 : RESET_OUT)。キーパッド・モードに設定した時、このピンは行 4 として機能します。                                                 |

| D2   | R3            | GPIO 4 (GPIO の代替機能 : ロジック・ブロック入力 LC)。キーパッド・モードに設定した時、このピンは行 3 として機能します。                                            |

| D3   | C3            | GPIO 10。キーパッド・モードに設定した時、このピンは列 3 として機能します。                                                                         |

| D4   | C4            | GPIO 11。キーパッド・モードに設定した時、このピンは列 4 として機能します。                                                                         |

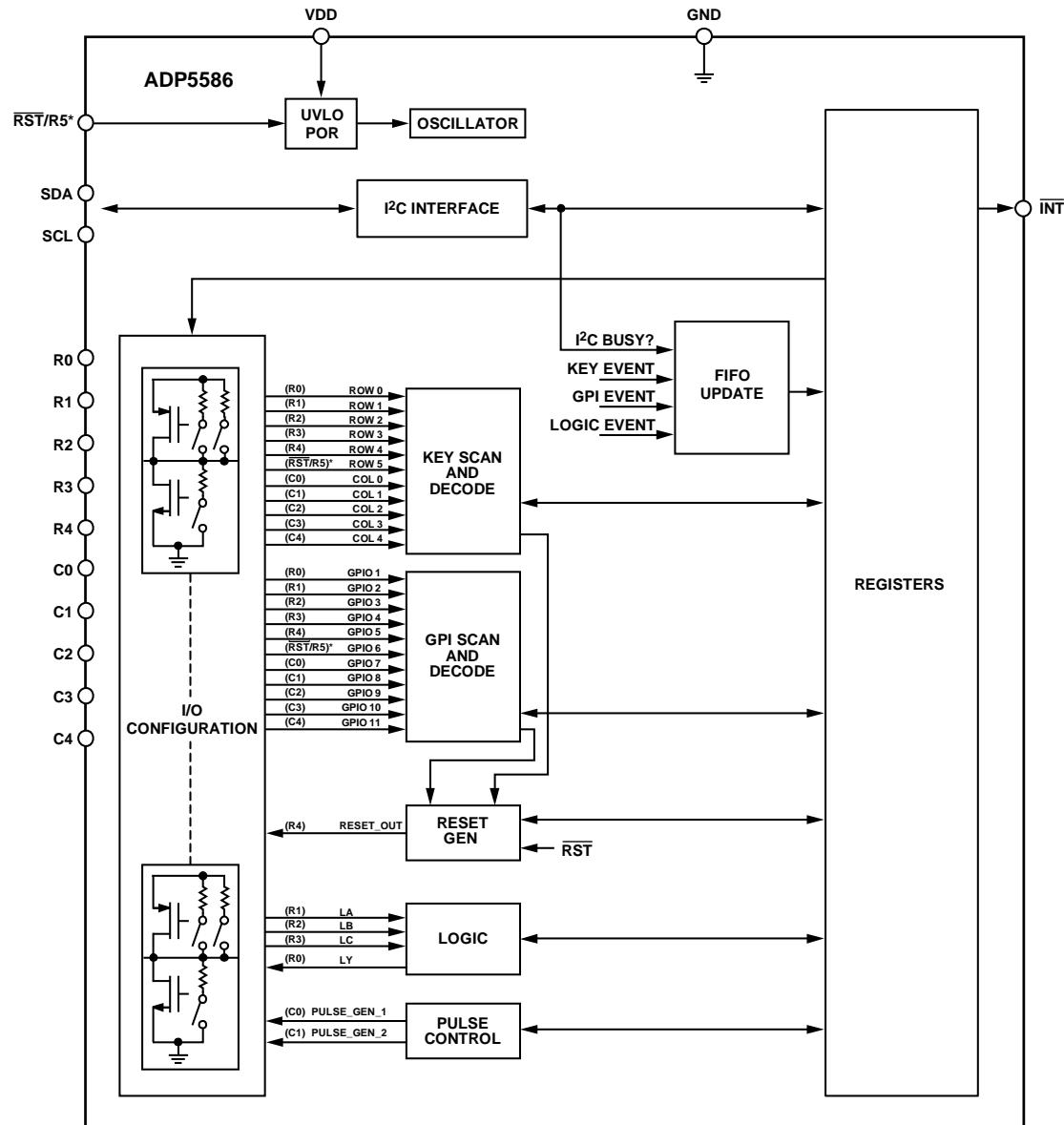

## 動作原理

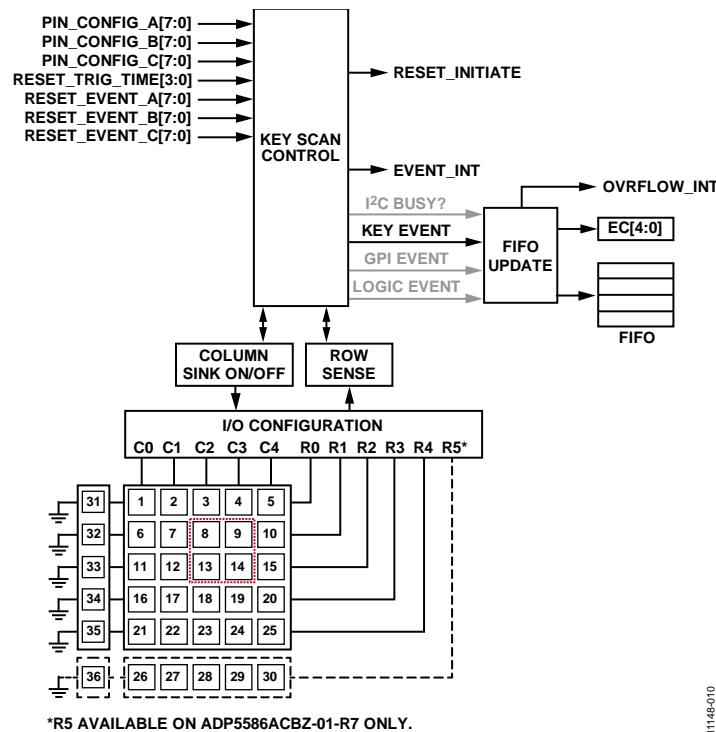

\*R5 AVAILABLE ON ADP5586ACBZ-01-R7 ONLY.

11148-004

図4. 内部ブロック図

## デバイス・イネーブル

十分な電圧を VDD に印加し RST ピンをロジック・ハイレベルで駆動した時、ADP5586 はスタンバイ・モードで起動し、すべての設定がデフォルト状態になります。ユーザは I<sup>2</sup>C インターフェースを介してデバイスを設定できます。RST ピンをローにすると、ADP5586 はリセット状態に入りすべての設定がデフォルトに状態に戻ります。RST ピンはデバウンス・フィルタを備えています。

ADP5586ACBZ-01-R7 のデバイス・モデルを使用する場合、RST ピンは追加の列ピン(R5)として動作します。リセット・ピン無しのデバイスをリセットためには、VDD を UVLO スレッショルド以下に下げるか、あるいは SW\_RESET ビットを 1 (レジスタ 0x3D、ビット 2)に設定します。

## デバイスの概要

ADP5586 には複数の設定が可能な 10 本の入力/出力ピンがあります。これらのピンをプログラムしてデバイスをイネーブルにする事によって、下記の様々な機能を実行できます。

- キーパッド・マトリクスのデコーディング (最大 5 列 X 5 行のマトリックス)

- 汎用 I/O の拡張機能 (最大 10 本の入力/出力)

- リセット・ジェネレータ

- ロジック機能ビルディング・ブロック (最大 3 入力/1 出力)

- 2 個のパルス・ジェネレータ

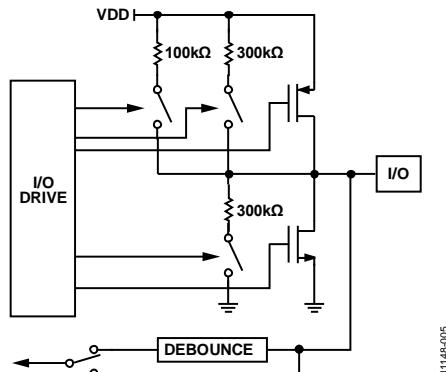

10 本の入力/出力ピンはすべて図 5 に示すような I/O 構造になっています。

図 5. I/O の構造

各 I/O は抵抗 100 kΩ 又は 300 kΩ でプルアップ、あるいは抵抗 300 kΩ でプルダウンが可能です。ロジック出力駆動のために、各 I/O にはプッシュプル・タイプ出力用の 5 mA の PMOS ソースと 10 mA の NMOS シンクが内蔵されています。オープン・ドレイン出力の場合、5 mA の PMOS ソースはイネーブルしません。ロジック入力のアプリケーションでは、各 I/O を直接、あるいはデバウンス・フィルタを通してサンプリングすることができます。

図 5 に示す I/O 構造によってすべての GPI と GPO 機能が可能になります。PWM やクロック周波数機能も実現できます。キー・マトリックスのスキャンとデコードの場合、スキャニング回路は抵抗 100 kΩ 又は 300 kΩ を使用してキーパッドの行ピンをプルアップし、10 mA の NMOS シンクを使用してキーパッドの列ピンを接地します (キー・コーディングについての詳細についてはキー・スキャン制御セクションを参照)。

デバイスの設定は I<sup>2</sup>C インターフェースを介して一連の内部抵抗をプログラムする事によって実行されます。デバイス状態のフィードバックや保留中の割込みは INT ピンを使用する事により外部プロセッサに伝える事ができます。

ADP5586 には 3 種類の機能セットがあります。表 6 は ADP5586 の各モデルで可能な機能の一覧です。供給状況そして/あるいはその他構成については最寄の ADI 代理店の担当者にご相談ください。

表 6. デバイス・モデルによるマトリックス・オプション<sup>1</sup>

| Model             | Description                                                          |

|-------------------|----------------------------------------------------------------------|

| ADP5586ACBZ-00-R7 | GPIO pull-down on startup<br>5-row × 5-column matrix                 |

| ADP5586ACBZ-01-R7 | Row 5 added to GPIOs<br>6-row × 5-column matrix                      |

| ADP5586ACBZ-03-R7 | Alternate I <sup>2</sup> C address (0x30)<br>5-row × 5-column matrix |

<sup>1</sup> ここに示されていない構成の供給状態についてはアナログ・デバイセズにご相談ください。

## 機能説明

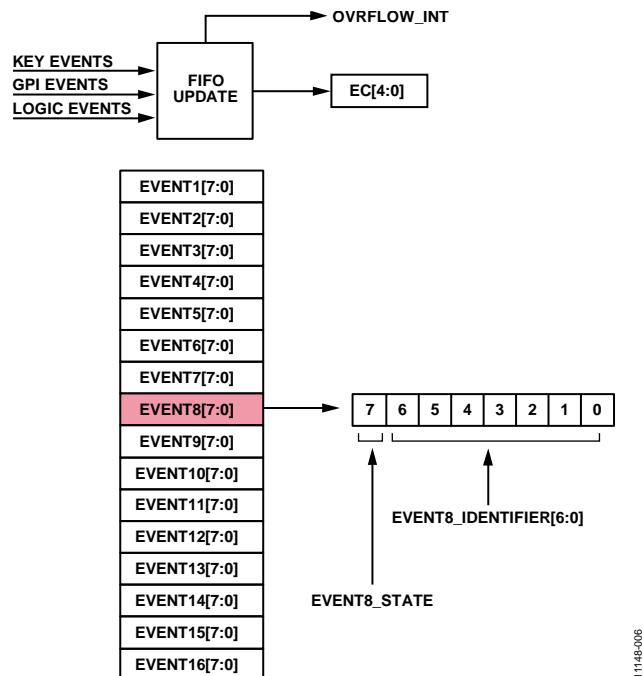

### イベント FIFO

ADP5586 の各種ブロックの詳細に入る前に、ADP5586 に用いられているイベント FIFO の機能を理解する事が重要です。イベント FIFO (レジスタ 0x03～レジスタ 0x12) は最大 16 イベントの記録ができます。デフォルトでは、FIFO は主にキー・プレスやキー・リリースのようなキー・イベントを記録します。しかし、汎用入力(GPI)とロジック動作を設定して FIFO に関するイベント情報を生成する事もできます。イベント・カウント EC[4:0] (レジスタ 0x02、ビット [4:0]) は 5 ビットで構成され、FIFO と連係して動作するのでユーザは FIFO に保存されているイベント数がわかります。

FIFO は 16 個の 8 ビットレジスタで構成されています。各レジスタのビット[6:0]はイベント識別子を保持し、ビット 7 はイベント状態を保持します。ユーザは FIFO\_1～FIFO\_16 のレジスタの中から FIFO の一番上のレジスタを読出す事ができます。ADP5586 には複数コピーの FIFO レジスタがあるので、1 回の I<sup>2</sup>C バースト読み出しで完全な FIFO を読出す事ができます。

図 6. Eventx[7:0] ビットの内容

図 7. FIFO 動作

FIFO レジスタは常に、FIFO の上端（すなわち、EVENT1[7:0]の位置）を指示します。ユーザが FIFO のどの位置から読出そうとしても、データは常にその FIFO の一番上から取られます。これによって、イベントを発生の順番通りに読出す事ができるので、FIFO システムの整合性を保つことができます。

前述のように、ADP5586 に搭載されているいくつかの機能を設定して、FIFO に関するイベントを生成することができます。FIFO への更新は、FIFO 更新制御ブロックが管理します。I<sup>2</sup>C トランザクションがいずれかの FIFO アドレス位置にアクセスしている場合は、I<sup>2</sup>C トランザクションが完了するまで更新が一時停止します。

外部プロセッサが FIFO を読み出してクリアしないうちに 16 を超えるイベントが生成されると、FIFO のオーバーフローが発生します。

オーバーフロー状態が生ずると、オーバーフロー割込み状態ビット(OVRFLW\_INT、レジスタ 0x01、ビット 2)が設定されます。オーバーフロー割込みがイネーブルになると、割込みが生成され、16 を超えるイベントが発生したことをプロセッサに通知します。

11148-006

## キー・スキャン制御

### 一般事項

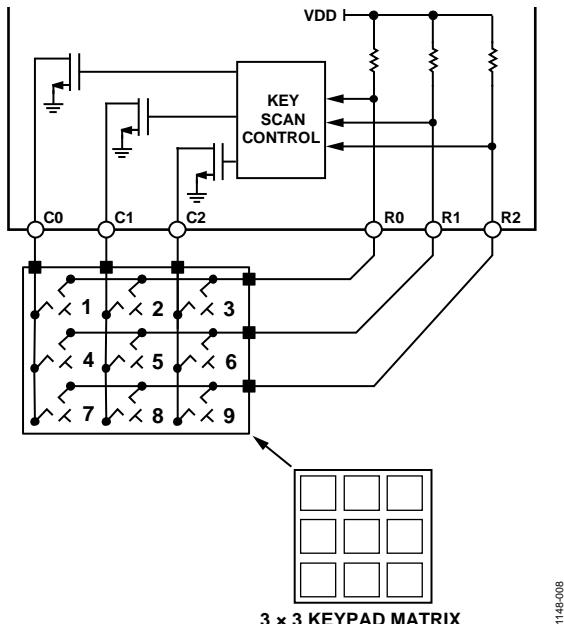

10本の入力/出力ピンを設定する事により、PIN\_CONFIG\_A、PIN\_CONFIG\_B、PIN\_CONFIG\_Cの各レジスタ（レジスタ0x3A～0x3C）を使って最大25個のスイッチ（5×5マトリクス）までのキーパッド・マトリクスをデコードすることができます。マトリクスをこれより小さく設定することも可能で、その場合は未使用の行／列ピンをほかのI/O機能に使用することができます。

R0～R4のI/Oピンは、キーパッド・マトリクスの行を構成します。C0～C4のI/Oピンは、キーパッド・マトリクスの列を構成します。行に使用するピンは、内部の300 kΩ（または100 kΩ）抵抗を介してプルアップされます。列に使用するピンは、内部のNMOS電流シンクによってローレベルに駆動されます。

図8. キー・スキャン・ブロックの簡略図

1114B-008

図8は、3×3の小さい9スイッチ・キーパッド・マトリクスに接続した3つの行ピンと3つの列ピンを使用するキー・スキャ

ン・ブロックの簡略図です。キー・スキャナがアイドル状態の時、行ピンはハイレベルになり、列ピンはローレベルに駆動されます。キー・スキャナは、行ピンがローレベルであるかどうかを確認する事によって動作します。

マトリクスのスイッチ6が押されると、R1はC2に接続します。キー・スキャン回路は、1本の行ピンがローレベルになったことを感知し、キー・スキャン・サイクルを開始します。キー・スキャニングでは、すべての列ピンをハイレベルに駆動してから、各列ピンを1つずつローレベルに駆動し、行ピンがローレベルになっているか感知します。すべての行／列ペアがスキャンされます；したがって、もし複数のキーがプレスされたら、それらは検出されます。

グリッヂあるいは有効なキー・プレスとして登録するには時間が短すぎるプレスを避けるために、キー・スキャナは、キーが2スキャン・サイクルの間プレスされる事を要求します。キー・スキャナには各スキャン・サイクルの間に待ち時間があります。したがって、キーがプレスされたとして登録するには、少なくともこの待ち時間の間キーがプレスされたままになっている必要があります。キーが連続的にプレスされたままになっている場合、キーがプレスされている限りキー・スキャナはスキャンと待機を繰り返します。

スイッチ6がリリースされると、R1とC2の間の接続が切れ、R1はハイレベルにプルアップされます。キーのリリースは必ずしもキー・スキャナと同期しないので、キー・スキャナは、2スキャン・サイクルの間キーがリリースされていることを要求します。キーのリリースが登録されるには、最大で2回の待機／スキャンのサイクルが必要になります。キーのリリースが登録され、他のキーもプレスされていないと、キー・スキャナはアイドル・モードに戻ります。

キーのプレス/リリースの状態を簡単なロジック信号で図示します。ロジック・ハイはキーがプレスされている状態を示し、ロジック・ローはキーがリリースされている状態を示します。このように考えればキー・イベントについて説明する際、個々の行/列の信号を描く必要がなくなります。

図9. ロジック・ロー：キー・リリース；

ロジック・ハイ：キー・プレス

1114B-009

\*R5 AVAILABLE ON ADP5586ACBZ-01-R7 ONLY.

11148-010

図 10.キー・スキャン・ブロックの詳細図

図 10 は、キー・スキャン・ブロックとそれに関連するすべての制御信号とステータス信号の詳細です。全部の行ピンと列ピンを使えば、25 個の固有のキーのマトリクスをスキャンすることができます。

PIN\_CONFIG\_A[5:0]、PIN\_CONFIG\_B[4:0] の各レジスタ(それぞれレジスタ 0x3A と レジスタ 0x3B)は、I/O をキーパッド・デコーディング用に設定する時に使用します。各キー・スイッチ上の番号ラベルは、そのスイッチがプレスされた場合に記録されるイベント識別子を示します。すべての行／列ピンを設定すると、FIFO で 25 個のキー識別子のすべてを確認することができます。

しかし、たとえば C2、C3 の列ピンと R1、R2 の行ピンを使用して、 $2 \times 2$  の小さいマトリクスを設定した場合は、図 10 に示すように FIFO で確認できるのは 4 つのイベント識別子 (8、9、13、14) のみになります。

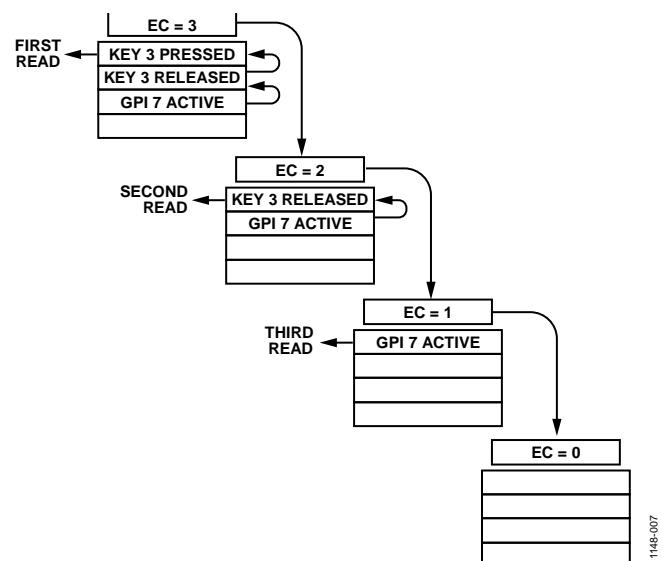

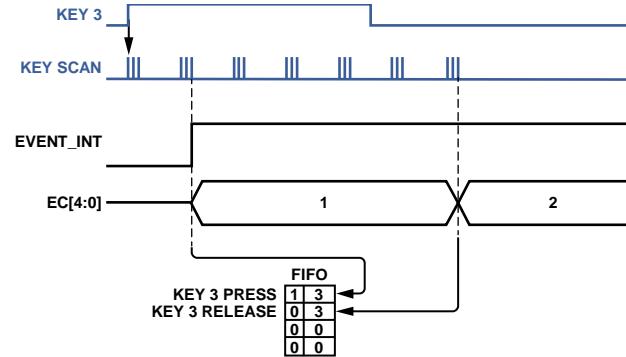

ADP5586 は、デフォルトでキーのプレスとリリースを FIFO に記録します。図 11 に、1 つのキーがプレスされたり、リリースされた時に何が起こるかを示します。最初は、キー・スキャナはアイドル状態です。キー 3 がプレスされると、スキャナは、設定されたすべての行／列ペアのスキャンを開始します。スキャン待ち時間の後、スキャナは、設定されたすべての行／列ペアを再びスキャンし、キー 3 がプレスされたままであることを検出し、EVENT\_INT 割込みビット (レジスタ 0x01、ビット 0) を設定します。次にイベント・カウンタ EC[4:0](レジスタ 0x02、ビット [4:0])は 1 にインクリメントします； FIFO の EVENT1\_IDENTIFIER[6:0]は 3 に設定されたイベント識別子によって更新されます；そして EVENT1\_STATE ビットは 1 に設定され、キー・プレスを示します。

図 11.プレスとリリースのイベント

キーがプレスされた状態の間、キー・スキャナはスキャン／待機のサイクルを続行します。2つの連続したスキャン・サイクルの間、キーがリリースされていることをスキャナが検出すると、イベント・カウンタ EC[4:0]が 2 にインクリメントされ、FIFO の EVENT2\_IDENTIFIER[6:0]が 3 に設定されたイベント識別子によって更新されます。EVENT2\_STATE ビットは 0 に設定され、リリースを示します。他のキーがプレスされていないので、キー・スキャナはアイドル・モードに戻ります。

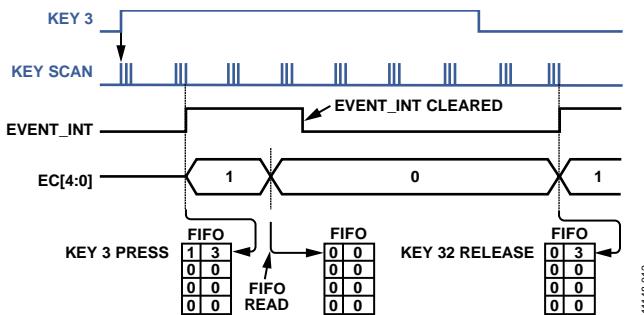

EVENT\_INT 割込み（レジスタ 0x01、ビット 0）は、プレスとリリースの両方のキー・イベントによってトリガーすることができます。図 12 に示すように、キー 3 がプレスされた場合、EVENT\_INT がアサートされ、EC[4:0] が更新され、そして FIFO が更新されます。キーがまだプレスされている間は、FIFO を読み出す事ができ、これによって、イベント・カウンタが 0 にデクリメントし、EVENT\_INT がクリアされます。キーが最終的にリリースされた時、EVENT\_INT がアサートされ、イベント・カウンタがインクリメントされ、FIFO はリリース・イベント情報によって更新されます。

図 12. EVENT\_INT 割込みのアサート

## キーパッドの拡張

図 10 に示すように、キーパッドは各行をスイッチで直接グラウンドに接続すれば拡張できます。R0 とグラウンドの間に位置しているスイッチをプレスすれば、全部の行が接地します。キー・スキャナはスキャニングを完了すると、通常キー 1～キー 5 がプレスされたとして検出します；しかし、この特殊な状態は ADP5586 によってデコードされ、これに対し Key Event 31 が割り当てられます。さらにあと 5 個までキー・イベントの割り当てが可能で、キーパッド・サイズを最大 30 まで拡張できます。しかし、もし拡張したキーの 1 つがプレスされたら、その行のキーはどれも検出できません。グラウンド・キーの起動はその行を共用している他のすべてのキーを検出不能にします。

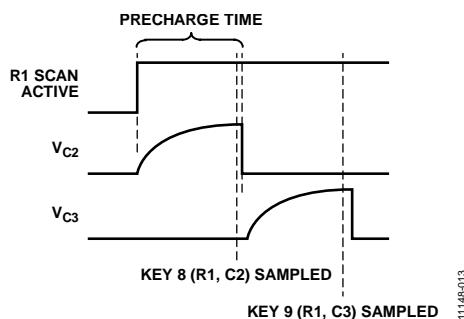

## プリチャージ時間

スキャン・シーケンスの間、行は列の端から端まで順にスキャンします。各行/列の組み合わせは KEY\_POLL\_TIME ビット（レジスタ 0x39、ビット [1:0]）で指定されたレートでテストされます。これらの各スキャン時間の中で、各列は

PRECHARGE\_TIME ビット（レジスタ 0x39、ビット 3）で指定された時間の間スキャンされます。図 13 に示すように、（たとえばプルアップ/プルダウン抵抗などの）直列抵抗と個々の列で観測される並列容量によって決まる抵抗コンデンサ（RC）時定数はキー・プレス・イベントのサンプリングに影響を及ぼします。

図 13. プリチャージ時間

ADP5586 はプリチャージ時間の終わり近くで行/列ペアの状態をサンプリングします。このプリチャージ時間を延長する事により、RC 時定数が高い場合にも対応できます。物理的なボタンを使うアプリケーションでは、通常 RC 時定数の問題はありませんが、外部リレー・スイッチあるいは複数の外付け MUX を列に接続した場合、RC 時定数が増大する可能性があります。行のプルアップ抵抗（レジスタ 0x3C、ビット 7）で小さい方を使用すれば、RC 時定数を低減します。

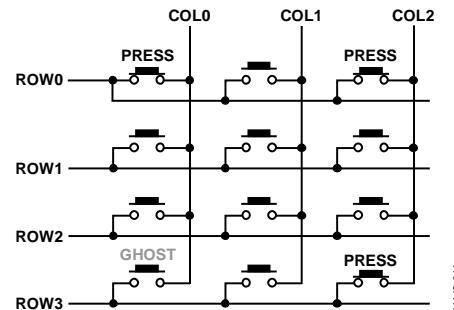

## ゴースト

ゴーストはキーパッド・マトリクス上のあるキー・プレスの組み合わせによっては、誤って他のキーの読出しを検出してしまう現象です。ゴーストが発生するのは、複数の行または列で 3 つ以上のキーが同時にプレスされた時です（図 14 を参照）。キーパッド・マトリクス上で直角になるキーの組み合わせによってゴーストが生じる傾向があります。

図 14. ゴーストの例：キー・プレス中に行 0、列 0、列 2、行 3 の間で短絡すると列 0/行 3 はゴースト・キーになります。

ゴーストの解決方法は、一緒にプレスされる可能性が最も高い 3 つのキーの組み合わせを考慮してキーパッド・マトリクスのレイアウトを選択することです。1 つの行または 1 つの列にわたって複数のキーがプレスされても、ゴーストが発生することはありません。キーをずらして同じ列にならないようにすることによって、ゴーストを回避することもできます。よく行われている方法は、同時にプレスされる可能性のあるキーと同じ行あるいは同じ列に置くことです。同時にプレスされる可能性のあるキーのいくつかの例を下記に示します。

- セレクト・キーとナビゲーション・キーの組み合わせ

- スペース・バーとナビゲーション・キーの組み合わせ

- CTRL + ALT + DEL のようなリセット組み合わせキー

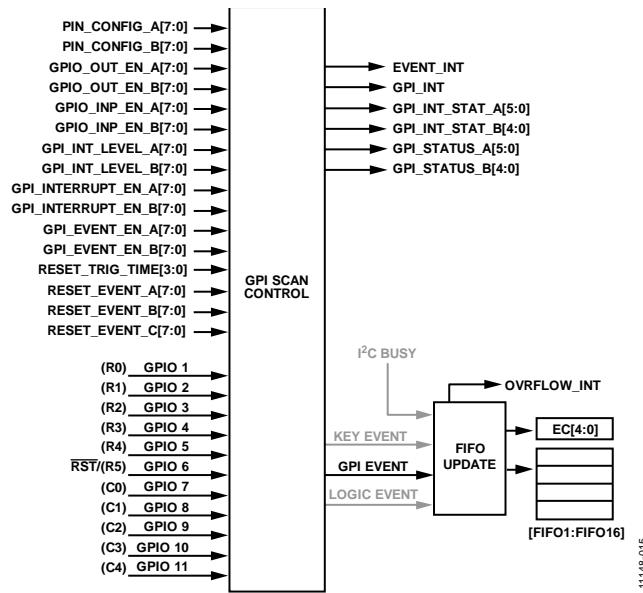

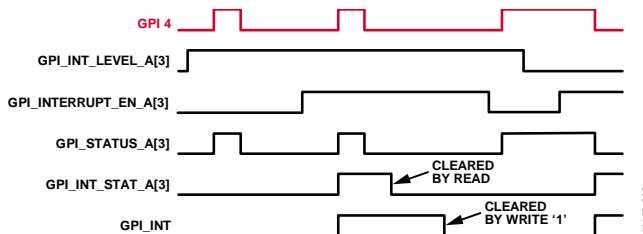

## GPI 入力

10本のI/O線は、それぞれGPIO\_INP\_EN\_AとGPIO\_INP\_EN\_Bレジスタ（レジスタ0x29とレジスタ0x2A）を使って汎用ロジック入力線として設定できます。GPIO線は入力と出力の両方とも同時に設定できます。図15は、GPIスキャン、検索ブロックとその関連する制御信号とステータス信号の詳細を示します。

図15. GPIスキャン&検出ブロック

各GPIの電流入力状態は、GPI\_STATUS\_xレジスタ（レジスタ0x15とレジスタ0x16）を使用して読み出すことができます。各GPIは、GPI\_INTERRUPT\_EN\_xレジスタ（レジスタ0x1Fとレジスタ0x20）によって割込みを生成するように設定できます。割込みステータスは、GPI\_INT\_STAT\_xレジスタ（レジスタ0x13とレジスタ0x14）に格納されます。GPI割込みは、GPI\_INT\_LEVEL\_xレジスタ（レジスタ0x1Bとレジスタ0x1C）を設定する事により、立上がりエッジまたは立下りエッジでトリガーされるように設定できます。いずれかのGPI割込みがトリガーされると、マスクGPI\_INT割込みビット（レジスタ0x01、ビット1）もトリガーされます。図16に、単一GPIと、その対応するステータス・ビットおよび割込みステータス・ビットへの影響を示します。

図16. 単一 GPI の例

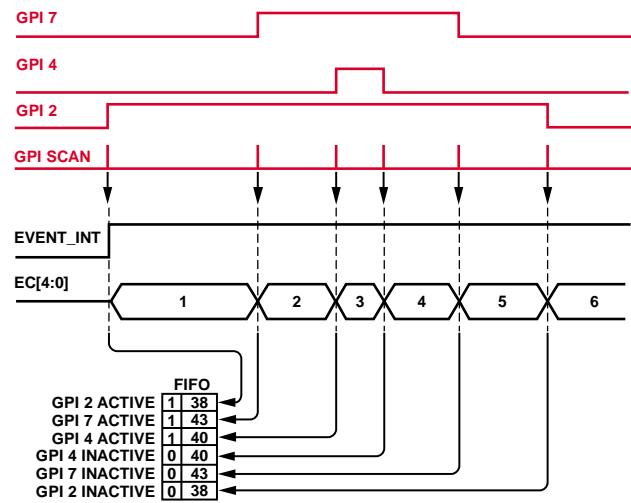

GPIは、GPI\_EVENT\_EN\_xレジスタ（レジスタ0x1Dとレジスタ0x1E）によってFIFOイベントを生成するように設定できます。このモードのGPIは、GPI\_INT割込みを生成しません。代わりに、それらはEVENT\_INT割込み（レジスタ0x01、ビット0）を生成します。図17は、いくつかのGPI線と、FIFOおよびイベント・カウント、EC[4:0]に対するその影響を示します。

図17. 複数 GPI の例

GPIスキャナは、レベル変化を検出するまでアイドル状態です。次にGPIスキャナは、GPI入力をスキャンし、それに応じて更新を行います。更新後、GPIスキャナは直ちにアイドル状態に戻ります；キー・スキャナのようにスキャン/待機を行いません。このため、GPIスキャナは、70μs (typ) の入力デバウンス・フィルタを通過後、狭いパルスの両エッジを検出できます。

## GPO 出力

10本のI/O線は、それぞれGPIO\_OUT\_EN\_AとGPIO\_OUT\_EN\_Bレジスタ（レジスタ0x27とレジスタ0x28）を使用して汎用出力（GPO）線として設定できます。GPIO線を入力と出力の両方を行えるように設定できます（I/O構造の詳細図については図5を参照）。GPOの設定と使い方を、GPO\_DATA\_OUT\_xとGPO\_OUT\_MODE\_xレジスタ（レジスタ0x23～レジスタ0x26）にプログラミます。詳細については、レジスタの詳細説明セクションを参照してください。

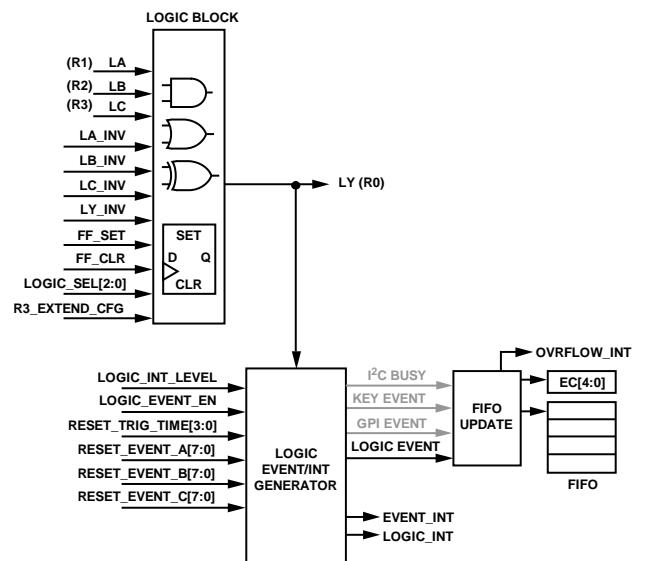

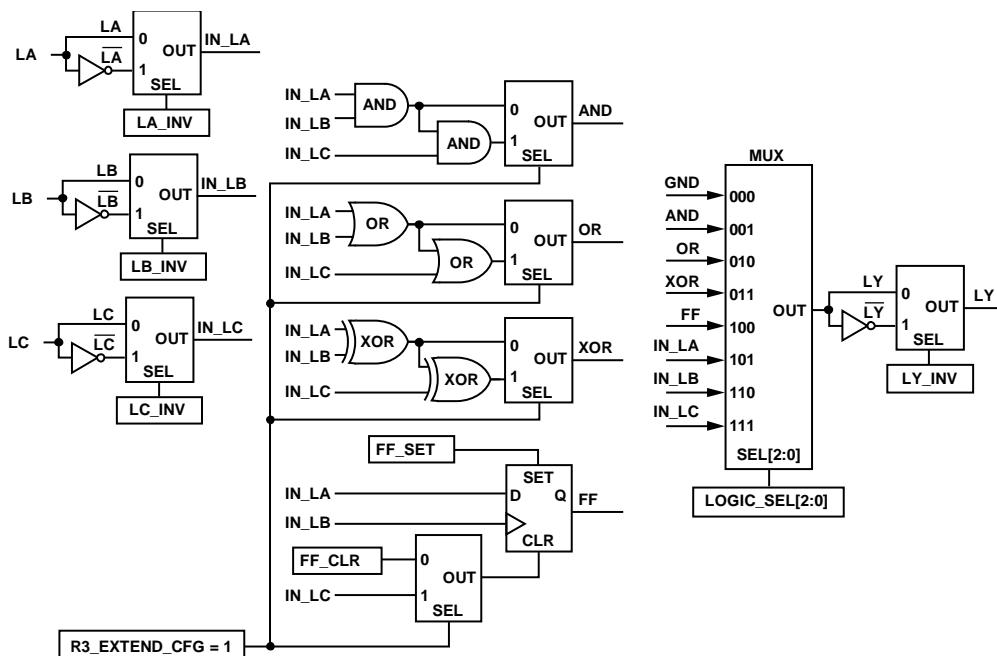

## ロジック・ブロック

ADP5586 の入/出力線の一部は、共通ロジック機能を実行するための入出力として使用することができます。

入出力ピン R1、R2、R3 はロジック・ブロックの入力として使用でき、入出力ピン R0 は出力として使用できます。入力線 R1、R2、R3 を使用する時は、入力を許可するために

GPIO\_4\_INP\_EN ビット、GPIO\_3\_INP\_EN ビット、

GPIO\_2\_INP\_EN ビット（レジスタ 0x29、ビット[3:1]）をイネ

ーブルにする必要があります。R0 ピンをロジック・ブロックの出力として使用する時は、GPIO\_1\_OUT\_EN ビット（レジスタ 0x27、ビット 0）をイネーブルする必要があります。

ロジック・ブロックからの出力は割込みを生成するために設定できます。又、それらは FIFO に関するイベントを生成するために設定する事もできます。

図 19 はロジック・ブロックの内部構造の詳細回路ですが、実行する事ができる可能なロジック機能を示しています。

図 18. ロジック・ブロックの概要

11148-019

図 19. ロジック・ブロックの内部構造

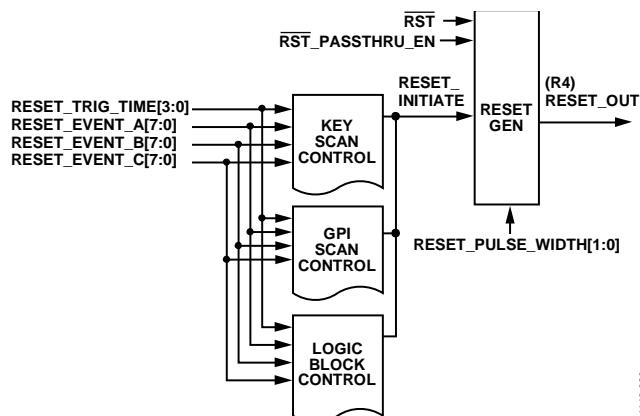

## リセット・ブロック

ADP5586 は、特定のイベントが同時に検出された場合にリセット条件を生成できるリセット・ブロックを備えています。RESET\_OUT には、最大3つのリセット・トリガー・イベントを設定できます。イベント・スキヤン制御ブロックは RESET\_TRIG\_TIME[3:0] (レジスタ 0xE、ビット [5:2]) の期間中にこれらのイベントが存在するかどうかを監視します。もしイベントが存在した場合は、リセット開始信号がリセット・ジェネレータ・ブロックへ送信されます。生成されるリセット信号のパルス幅はプログラマブルです。

図 20. リセット・ブロック

RESET\_OUT 信号は、その出力として I/O ピン R4 を使用しますが、出力機能を有効にするためには GPIO\_5\_OUT\_EN ビット (レジスタ 0x27、ビット 4) を介して設定する必要があります。パス・スルー・モードを使用すれば、RST ピンを R4 ピンに出力することもできます。

リセット生成信号は、システム・プロセッサが動かなくなり、システムが入力イベントに応答しない時に役に立ちます。ユーザーは、リセット・イベントの組み合わせの1つをプレスして、システム全体のリセットを開始できます。これによって、システムからバッテリを取り除いてハード・リセットを実行しなければならない必要性が減ります。

直接のトリガータイム設定 (表 55 を参照) は非常に少ないノイズ条件でのみ使用する事をお勧めします；さもないと誤ったトリガーが起こる可能性があります。

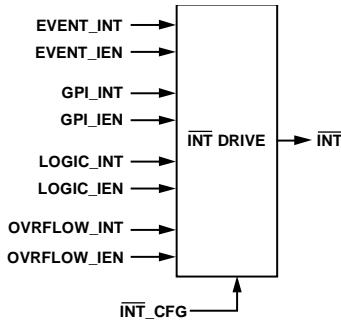

## 割込み

いざれかの内部割込みソースがアクティブである場合、INT ピンをローレベルにアサートすることができます。ユーザーは外部割込みピンと交信する内部割込みをレジスタ 0x3E (表 71 を参照) の中で選べます。ユーザーはレジスタ 0x3D を使って外部割込みピンをアサートされた状態のまますか、(複数の内部割込みがアサートされ、1つの内部割込みがクリアされた場合のように) 50 µs の間アサートを解除した後再びアサートするかを選択できます。 (表 70 を参照)

図 21. INT をローレベルにアサート

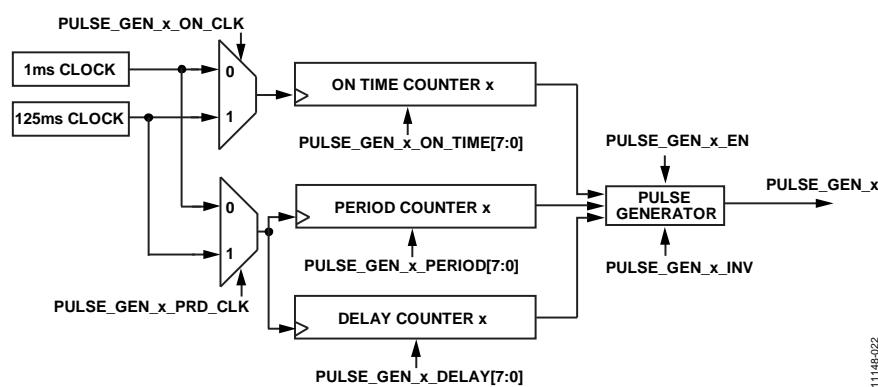

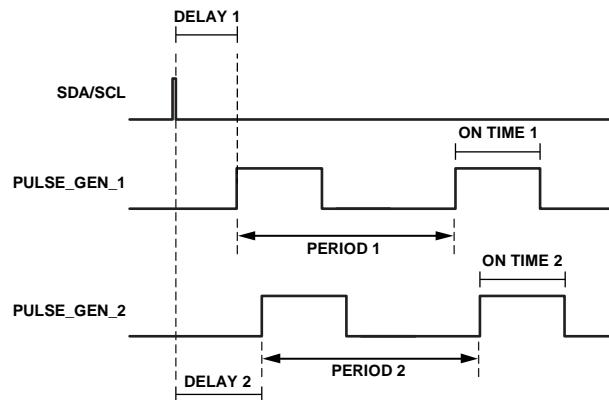

## パルス・ジェネレータ

ADP5586にはインジケータのLED駆動信号、ウォッチドッグ・タイマー、その他長時間パルス駆動のアプリケーションに利用できる2個のパルス・ジェネレータが含まれています。ADP5586はオン時間と発生パルスの周期を8ビットで定義ができます。長い時間のタイミングを可能にするために、ユーザは1msクロックと125msクロックのどちらかを選び、これらのタイマーをインクリメントさせる事ができます。2個のパルス・ジェネレータの周期はPULSE\_GEN\_1\_PERIODとPULSE\_GEN\_2\_PERIODレジスタ(それぞれレジスタ0x30とレジスタ0x33)を使って指定します。PULSE\_GEN\_CONFIGレジスタ(レジスタ0x35、ビット1とビット5)でクロック周期125msを選択するとパルス・ジェネレータの周期を31.875秒まで設定が可能になります。PULSE\_GEN\_x\_ON\_CLKビットをステップサイズ125msに設定して、PULSE\_GEN\_x\_PRD\_CLKビットをステップサイズ1msに設定する事はできません。

アクティブ・ローのアプリケーションに対応するために、PULSE\_GEN\_CONFIGレジスタの中のビット7とビット3(PULSE\_GEN\_x\_INV)を使い信号反転を設定する事ができます。チャンネル間で同期するオフセットを作成するために遅延を導入する事ができます。もし両方のチャンネルが同時にイネーブル(すなわち、同じI<sup>2</sup>Cの書き込みからイネーブルされる)になる場合、遅延の差はチャンネル間のオフセットになります。もし1チャンネルがアクティブの状態で遅延を同期させる場合、ユーザは同じI<sup>2</sup>C書き込み命令で両方のパルス・ジェネレータをディスエーブルにする前にまず両方のパルス・ジェネレータをディスエーブルにする必要があります。遅延カウンタは周期カウンタと同じクロック選択を使います。詳細については、表56～表61を参照してください。C1そしてあるいはC0のパルス・ジェネレータ出力をイネーブルにするにはGPIO\_8\_OUT\_ENビットそしてあるいはGPIO\_7\_OUT\_ENビット(レジスタ0x28、ビット[1:0])をイネーブルにする必要があります。

図22. パルス・ジェネレータ・ブロック図

11148-022

図23. パルス・ジェネレータのタイミング例

11148-023

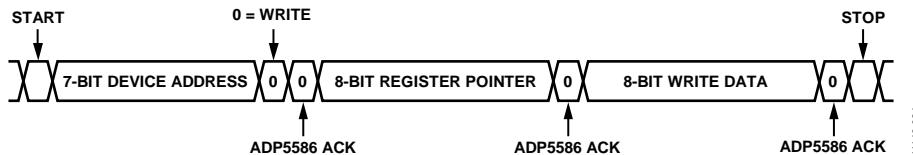

## レジスタ・インターフェース

ADP5586 のレジスタは、I<sup>2</sup>C 互換シリアル・インターフェース経由でアクセスします。このインターフェースは、最大 1 MHz のクロック周波数まで対応できます。ユーザが FIFO またはキー・イベント・カウンタ (KEC) にアクセスしている時は、FIFO/KEC の更新が一時停止します。クロック周波数がかなり低いと、イベントをタイムリーに記録できないことがあります。I<sup>2</sup>C の読み書きには I<sup>2</sup>C の数サイクルが必要であるため、FIFO または KEC の更新は割込みがアサートされてから最大 23 μs 後に行なうことができます。この遅延がユーザに問題にならないようにしてください。

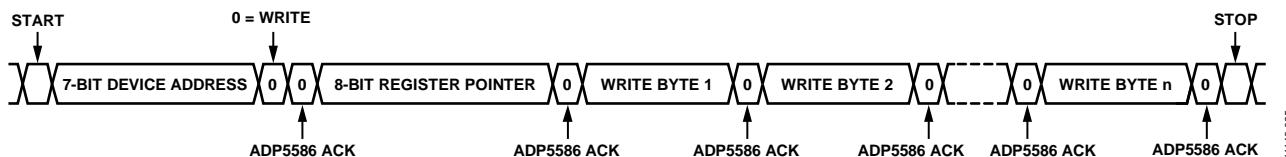

図 24 に、内部レジスタを設定する代表的な書き込みシーケンスを示します。このサイクルはスタート条件で開始し、その後 7 ビットのデバイス・アドレス (ADP5586 は 0x34) が続き、さらに (書き込みサイクルのために 0 に設定された) R/W ビットが続けます。ADP5586 は、データ線をローレベルにして、アドレス・バイトをアクノリッジします。データを書込むレジスタのアドレスが次に送信されます。ADP5586 は、データ線をローレベルにして、レジスタのポインタ・バイトをアクノリッジします。次に書込むデータバイトが送信されます。ADP5586 は、データ線をローレベルにして、データバイトをアクノリッジします。このシーケンスは、ストップ条件で完了します。

図 25 は、内部レジスタを設定するための代表的な複数バイト書き込みシーケンスです。このサイクルはスタート条件で開始し、その後 7 ビットのデバイス・アドレス (0x34) が続き、

さらに (書き込みサイクルのために 0 に設定された) R/W ビットが続けます。ADP5586 は、データ線をローレベルにして、アドレス・バイトをアクノリッジします。データを書込むレジスタのアドレスが次に送信されます。ADP5586 は、データ線をローレベルにして、レジスタのポインタ・バイトをアクノリッジします。書き込むデータバイトが次に送信されます。ADP5586 は、データ線をローレベルにして、データバイトをアクノリッジします。その後次のデータバイトを書込むためにポインタ・アドレスがインクリメントし、N データバイトまで書き込みます。ADP5586 は、各バイト後にデータ線をローレベルにし、ストップ条件でこのシーケンスが完了します。

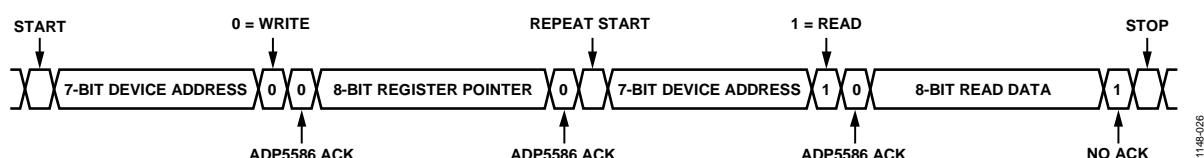

図 26 は、内部レジスタを読出すための代表的なバイト読出しシーケンスです。

このサイクルはスタート条件で開始し、その後 7 ビットのデバイス・アドレスが続き、さらに (書き込みサイクルのために 0 に設定された) R/W ビットが続けます。ADP5586 は、データ線をローレベルにして、アドレス・バイトをアクノリッジします。データを読出すレジスタのアドレスが次に送信されます。ADP5586 は、データ線をローレベルにして、レジスタのポインタ・バイトをアクノリッジします。スタート条件が繰り返され、その後 7 ビットのデバイス・アドレス (0x34) が続き、さらに (読出しサイクルのために 1 に設定された) R/W ビットが続けます。ADP5586 は、データ線をローレベルにして、アドレス・バイトをアクノリッジします。次に、8 ビット・データが読出されます。ホストはデータ線をハイレベルにし (ノー・アクノリッジ)、ストップ条件でこのシーケンスが完了します。

図 24. I<sup>2</sup>C 単一バイト書き込みシーケンス

図 25. I<sup>2</sup>C 複数バイト書き込みシーケンス

図 26. I<sup>2</sup>C 単一バイト読出しシーケンス

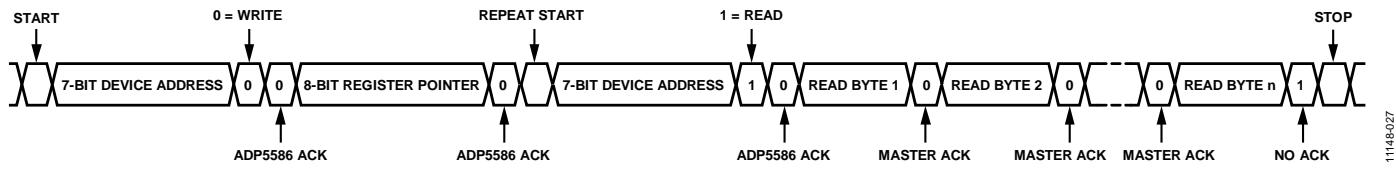

図27は、内部レジスタを読出すための代表的な複数バイト読出しシーケンスです。このサイクルはスタート条件で開始し、その後7ビットのデバイス・アドレス(0x34)が続き、さらに（書き込みサイクルのために0に設定された）R/Wビットが続きます。ADP5586は、データ線をローレベルにして、アドレス・バイトをアクノリッジします。データを読出すレジスタのアドレスが次に送信されます。ADP5586は、データ線をローレベルにして、レジスタのポインタ・バイトをアクノリッジします。スタート条件が繰り返され、その後7ビットのデバイス・アドレス（0x34）が続き、さ

らに（読み出しサイクルのために1に設定された）R/Wビットが続きます。ADP5586は、データ線をローレベルにして、アドレス・バイトをアクノリッジします。次に、8ビット・データが読出されます。その後次のデータバイトを読出すためにポインタ・アドレスがインクリメントし、ホストは各バイトでNデータバイトが読出されるまでデータ線をロー・レベル（マスター・アクノレッジ）にし続けます。最後のバイトが読出された後、ホストはデータ線をハイレベルにし（ノー・アクノレッジ）、ストップ条件でこのシーケンスが完了します。

図27. I<sup>2</sup>C複数バイト読出しシーケンス

11148-027

## レジスタ・マップ

表 7.

| Reg Addr | Register Name       | R/W <sup>1</sup> | Bit 7         | Bit 6                   | Bit 5             | Bit 4             | Bit 3            | Bit 2            | Bit 1            | Bit 0     |

|----------|---------------------|------------------|---------------|-------------------------|-------------------|-------------------|------------------|------------------|------------------|-----------|

| 0x00     | ID                  | R                | MAN_ID        |                         |                   |                   |                  | REV_ID           |                  |           |

| 0x01     | INT_STATUS          | R/W              | Reserved      |                         |                   | LOGIC_INT         | Reserved         | OVRFLOW_INT      | GPIO_INT         | EVENT_INT |

| 0x02     | Status              | R                | Reserved      | LOGIC_STAT              | Reserved          | EC[4:0]           |                  |                  |                  |           |

| 0x03     | FIFO_1              | R                | EVENT1_STATE  | EVENT1_IDENTIFIER[6:0]  |                   |                   |                  |                  |                  |           |

| 0x04     | FIFO_2              | R                | EVENT2_STATE  | EVENT2_IDENTIFIER[6:0]  |                   |                   |                  |                  |                  |           |

| 0x05     | FIFO_3              | R                | EVENT3_STATE  | EVENT3_IDENTIFIER[6:0]  |                   |                   |                  |                  |                  |           |

| 0x06     | FIFO_4              | R                | EVENT4_STATE  | EVENT4_IDENTIFIER[6:0]  |                   |                   |                  |                  |                  |           |

| 0x07     | FIFO_5              | R                | EVENT5_STATE  | EVENT5_IDENTIFIER[6:0]  |                   |                   |                  |                  |                  |           |

| 0x08     | FIFO_6              | R                | EVENT6_STATE  | EVENT6_IDENTIFIER[6:0]  |                   |                   |                  |                  |                  |           |

| 0x09     | FIFO_7              | R                | EVENT7_STATE  | EVENT7_IDENTIFIER[6:0]  |                   |                   |                  |                  |                  |           |

| 0x0A     | FIFO_8              | R                | EVENT8_STATE  | EVENT8_IDENTIFIER[6:0]  |                   |                   |                  |                  |                  |           |

| 0x0B     | FIFO_9              | R                | EVENT9_STATE  | EVENT9_IDENTIFIER[6:0]  |                   |                   |                  |                  |                  |           |

| 0x0C     | FIFO_10             | R                | EVENT10_STATE | EVENT10_IDENTIFIER[6:0] |                   |                   |                  |                  |                  |           |

| 0x0D     | FIFO_11             | R                | EVENT11_STATE | EVENT11_IDENTIFIER[6:0] |                   |                   |                  |                  |                  |           |

| 0x0E     | FIFO_12             | R                | EVENT12_STATE | EVENT12_IDENTIFIER[6:0] |                   |                   |                  |                  |                  |           |

| 0x0F     | FIFO_13             | R                | EVENT13_STATE | EVENT13_IDENTIFIER[6:0] |                   |                   |                  |                  |                  |           |

| 0x10     | FIFO_14             | R                | EVENT14_STATE | EVENT14_IDENTIFIER[6:0] |                   |                   |                  |                  |                  |           |

| 0x11     | FIFO_15             | R                | EVENT15_STATE | EVENT15_IDENTIFIER[6:0] |                   |                   |                  |                  |                  |           |

| 0x12     | FIFO_16             | R                | EVENT16_STATE | EVENT16_IDENTIFIER[6:0] |                   |                   |                  |                  |                  |           |

| 0x13     | GPIO_INT_STAT_A     | R                | Reserved      | GPIO_6_INT              | GPIO_5_INT        | GPIO_4_INT        | GPIO_3_INT       | GPIO_2_INT       | GPIO_1_INT       |           |

| 0x14     | GPIO_INT_STAT_B     | R                | Reserved      |                         | GPIO_11_INT       | GPIO_10_INT       | GPIO_9_INT       | GPIO_8_INT       | GPIO_7_INT       |           |

| 0x15     | GPIO_STATUS_A       | R                | Reserved      | GPIO_6_STAT             | GPIO_5_STAT       | GPIO_4_STAT       | GPIO_3_STAT      | GPIO_2_STAT      | GPIO_1_STAT      |           |

| 0x16     | GPIO_STATUS_B       | R                | Reserved      |                         | GPIO_11_STA       | GPIO_10_STA       | GPIO_9_STAT      | GPIO_8_STAT      | GPIO_7_STAT      |           |

| 0x17     | R_PULL_CONFIG_A     | R/W              | R3_PULL_CFG   |                         | R2_PULL_CFG       |                   | R1_PULL_CFG      |                  | R0_PULL_CFG      |           |

| 0x18     | R_PULL_CONFIG_B     | R/W              | Reserved      |                         |                   |                   | R5_PULL_CFG      |                  | R4_PULL_CFG      |           |

| 0x19     | R_PULL_CONFIG_C     | R/W              | C3_PULL_CFG   |                         | C2_PULL_CFG       |                   | C1_PULL_CFG      |                  | C0_PULL_CFG      |           |

| 0x1A     | R_PULL_CONFIG_D     | R/W              | Reserved      |                         |                   |                   |                  |                  | C4_PULL_CFG      |           |

| 0x1B     | GPIO_INT_LEVEL_A    | R/W              | Reserved      | GPIO_6_INT_LEVEL        | GPIO_5_INT_LEVEL  | GPIO_4_INT_LEVEL  | GPIO_3_INT_LEVEL | GPIO_2_INT_LEVEL | GPIO_1_INT_LEVEL |           |

| 0x1C     | GPIO_INT_LEVEL_B    | R/W              | Reserved      |                         | GPIO_11_INT_LEVEL | GPIO_10_INT_LEVEL | GPIO_9_INT_LEVEL | GPIO_8_INT_LEVEL | GPIO_7_INT_LEVEL |           |

| 0x1D     | GPIO_EVENT_EN_A     | R/W              | Reserved      | GPIO_6_EVENT_EN         | GPIO_5_EVENT_EN   | GPIO_4_EVENT_EN   | GPIO_3_EVENT_EN  | GPIO_2_EVENT_EN  | GPIO_1_EVENT_EN  |           |

| 0x1E     | GPIO_EVENT_EN_B     | R/W              | Reserved      |                         | GPIO_11_EVENT_EN  | GPIO_10_EVENT_EN  | GPIO_9_EVENT_EN  | GPIO_8_EVENT_EN  | GPIO_7_EVENT_EN  |           |

| 0x1F     | GPIO_INTERRUPT_EN_A | R/W              | Reserved      | GPIO_6_INT_EN           | GPIO_5_INT_EN     | GPIO_4_INT_EN     | GPIO_3_INT_EN    | GPIO_2_INT_EN    | GPIO_1_INT_EN    |           |

| 0x20     | GPIO_INTERRUPT_EN_B | R/W              | Reserved      |                         | GPIO_11_INT_EN    | GPIO_10_INT_EN    | GPIO_9_INT_EN    | GPIO_8_INT_EN    | GPIO_7_INT_EN    |           |

| 0x21     | DEBOUNCE_DIS_A      | R/W              | Reserved      | GPIO_6_DEB_DIS          | GPIO_5_DEB_DIS    | GPIO_4_DEB_DIS    | GPIO_3_DEB_DIS   | GPIO_2_DEB_DIS   | GPIO_1_DEB_DIS   |           |

| 0x22     | DEBOUNCE_DIS_B      | R/W              | Reserved      |                         | GPIO_11_DEB_DIS   | GPIO_10_DEB_DIS   | GPIO_9_DEB_DIS   | GPIO_8_DEB_DIS   | GPIO_7_DEB_DIS   |           |

| 0x23     | GPO_DATA_OUT_A      | R/W              | Reserved      | GPO_6_DATA              | GPO_5_DATA        | GPO_4_DATA        | GPO_3_DATA       | GPO_2_DATA       | GPO_1_DATA       |           |

| 0x24     | GPO_DATA_OUT_B      | R/W              | Reserved      |                         | GPO_11_DATA       | GPO_10_DATA       | GPO_9_DATA       | GPO_8_DATA       | GPO_7_DATA       |           |

| 0x25     | GPO_OUT_MODE_A      | R/W              | Reserved      | GPO_6_OUT_MODE          | GPO_5_OUT_MODE    | GPO_4_OUT_MODE    | GPO_3_OUT_MODE   | GPO_2_OUT_MODE   | GPO_1_OUT_MODE   |           |

| 0x26     | GPO_OUT_MODE_B      | R/W              | Reserved      |                         | GPO_11_OUT_MODE   | GPO_10_OUT_MODE   | GPO_9_OUT_MODE   | GPO_8_OUT_MODE   | GPO_7_OUT_MODE   |           |

| Reg Addr | Register Name       | R/W <sup>1</sup> | Bit 7               | Bit 6               | Bit 5               | Bit 4          | Bit 3           | Bit 2              | Bit 1               | Bit 0                          |

|----------|---------------------|------------------|---------------------|---------------------|---------------------|----------------|-----------------|--------------------|---------------------|--------------------------------|

| 0x27     | GPIO_OUT_EN_A       | R/W              | Reserved            |                     | GPIO_6_OUT_EN       | GPIO_5_OUT_EN  | GPIO_4_OUT_EN   | GPIO_3_OUT_EN      | GPIO_2_OUT_EN       | GPIO_1_OUT_EN                  |

| 0x28     | GPIO_OUT_EN_B       | R/W              |                     | Reserved            |                     | GPIO_11_OUT_EN | GPIO_10_OUT_EN  | GPIO_9_OUT_EN      | GPIO_8_OUT_EN       | GPIO_7_OUT_EN                  |

| 0x29     | GPIO_INP_EN_A       | R/W              |                     | Reserved            | GPIO_6_INP_EN       | GPIO_5_INP_EN  | GPIO_4_INP_EN   | GPIO_3_INP_EN      | GPIO_2_INP_EN       | GPIO_1_INP_EN                  |

| 0x2A     | GPIO_INP_EN_B       | R/W              |                     | Reserved            |                     | GPIO_11_INP_EN | GPIO_10_INP_EN  | GPIO_9_INP_EN      | GPIO_8_INP_EN       | GPIO_7_INP_EN                  |

| 0x2B     | RESET_EVENT_A       | R/W              | RESET_EVENT_A_LEVEL |                     |                     |                |                 |                    |                     | RESET_EVENT_A, Bits[6:0]       |

| 0x2C     | RESET_EVENT_B       | R/W              | RESET_EVENT_B_LEVEL |                     |                     |                |                 |                    |                     | RESET_EVENT_B, Bits[6:0]       |

| 0x2D     | RESET_EVENT_C       | R/W              | RESET_EVENT_C_LEVEL |                     |                     |                |                 |                    |                     | RESET_EVENT_C, Bits[6:0]       |

| 0x2E     | RESET_CFG           | R/W              | RESET_POL           | RST_PASSTHRU_EN     |                     |                |                 |                    |                     | RESET_PULSE_WIDTH, Bits[1:0]   |

| 0x2F     | PULSE_GEN_1_DELAY   | R/W              |                     |                     |                     |                |                 |                    |                     | PULSE_GEN_1_DELAY, Bits[7:0]   |

| 0x30     | PULSE_GEN_1_PERIOD  | R/W              |                     |                     |                     |                |                 |                    |                     | PULSE_GEN_1_PERIOD, Bits[7:0]  |

| 0x31     | PULSE_GEN_1_ON_TIME | R/W              |                     |                     |                     |                |                 |                    |                     | PULSE_GEN_1_ON_TIME, Bits[7:0] |

| 0x32     | PULSE_GEN_2_DELAY   | R/W              |                     |                     |                     |                |                 |                    |                     | PULSE_GEN_2_DELAY, Bits[7:0]   |

| 0x33     | PULSE_GEN_2_PERIOD  | R/W              |                     |                     |                     |                |                 |                    |                     | PULSE_GEN_2_PERIOD, Bits[7:0]  |

| 0x34     | PULSE_GEN_2_ON_TIME | R/W              |                     |                     |                     |                |                 |                    |                     | PULSE_GEN_2_ON_TIME, Bits[7:0] |

| 0x35     | PULSE_GEN_CONFIG    | R/W              | PULSE_GEN_1_INV     | PULSE_GEN_1_ON_CLK  | PULSE_GEN_1_PRD_CLK | PULSE_GEN_1_EN | PULSE_GEN_2_INV | PULSE_GEN_2_ON_CLK | PULSE_GEN_2_PRD_CLK | PULSE_GEN_2_EN                 |

| 0x36     | LOGIC_CFG           | R/W              | Reserved            | LY_INV              | LC_INV              | LB_INV         | LA_INV          |                    |                     | LOGIC_SEL, Bits[2:0]           |

| 0x37     | LOGIC_FF_CFG        | R/W              |                     |                     |                     |                |                 |                    | FF_SET              | FF_CLR                         |

| 0x38     | LOGIC_INT_EVENT_EN  | R/W              |                     |                     |                     |                |                 | LY_DBNC_DIS        | LOGIC_EVENT_EN      | LOGIC_INT_LEVEL                |

| 0x39     | POLL_TIMECFG        | R/W              |                     |                     |                     |                | PRECHARGE_TIME  | Reserved           |                     | KEY_POLL_TIME, Bits[1:0]       |

| 0x3A     | PIN_CONFIG_A        | R/W              | Reserved            |                     | R5_CONFIG           | R4_CONFIG      | R3_CONFIG       | R2_CONFIG          | R1_CONFIG           | R0_CONFIG                      |

| 0x3B     | PIN_CONFIG_B        | R/W              |                     | Reserved            |                     | C4_CONFIG      | C3_CONFIG       | C2_CONFIG          | C1_CONFIG           | C0_CONFIG                      |

| 0x3C     | PIN_CONFIG_C        | R/W              | PULL_SELECT         | C0_EXTE_ND_CFG      | R4_EXTEND_CFG       | C1_EXTEND      | R3_EXTEND_CFG   |                    |                     | R0_EXTEND_CFG                  |

| 0x3D     | GENERAL_CFG         | R/W              | OSC_EN              | OSC_FREQ, Bits[1:0] |                     |                | Reserved        | SW_RESET           | INT_CFG             | RST_CFG                        |

| 0x3E     | INT_EN              | R/W              |                     | Reserved            |                     | LOGIC_IEN      | Reserved        | OVRFLOW_IEN        | GPL_IEN             | EVENT_IEN                      |

<sup>1</sup> R は読み出しを意味し、W は書き込みを意味し、R/W は読み出し/書き込みを意味します。

## レジスタの詳細説明

特に指定がない限り、すべてのレジスタはデフィルト値の 0000 0000 に設定されます。

### ID、レジスタ 0x00

デフォルト:0011 XXXX (ここで X = don't care)

表 8. ID ビットの説明

| Bits  | Bit Name | Access    | Description        |

|-------|----------|-----------|--------------------|

| [7:4] | MAN_ID   | Read only | メーカーID、デフォルト=0011。 |

| [3:0] | REV_ID   | Read only | リビジョン ID。          |

### INT\_STATUS、レジスタ 0x01

表 9. INT\_STATUS ビットの説明

| Bits  | Bit Name     | Access     | Description <sup>1</sup>                                                                                                                   |

|-------|--------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5] | Reserved     | Reserved   | 予約済み。                                                                                                                                      |

| 4     | LOGIC_INT    | Read/write | 0 = 割込みなし。<br>1 = 一般的なロジック条件による割込み。                                                                                                        |

| 3     | Reserved     | Reserved   | 予約済み。                                                                                                                                      |

| 2     | OVERFLOW_INT | Read/write | 0 = 割込みなし。<br>1 = オーバーフロー条件による割込み。                                                                                                         |

| 1     | GPI_INT      | Read/write | このビットは、FIFO とイベント・カウントの更新に設定された GPI では設定されません。<br>このビットは、すべての GPI_x_INT ビットがクリアされるまでクリアすることはできません。<br>0 = 割込みなし。<br>1 = 一般的な GPI 条件による割込み。 |

| 0     | EVENT_INT    | Read/write | 0 = 割込みなし。<br>1 = キー・イベント (プレス/リリース)、GPI イベント (GPI は FIFO 更新に設定)、またはロジック・イベント (FIFO 更新に設定) による割込み。                                         |

<sup>1</sup> 割込みビットはフラッグに 1 を書込む事によりクリアされます；0 の書き込みあるいはフラッグの読み出しは影響しません。

### ステータス、レジスタ 0x02

表 10. ステータス ビットの説明

| Bits  | Bit Name   | Access    | Description                                                            |

|-------|------------|-----------|------------------------------------------------------------------------|

| 7     | Reserved   | Reserved  | 予約済み。                                                                  |

| 6     | LOGIC_STAT | Read only | 0 = ロジック・ブロックからの出力 (LY) はローレベルです。<br>1 = ロジック・ブロックからの出力 (LY) はハイレベルです。 |

| 5     | Reserved   | Reserved  | 予約済み                                                                   |

| [4:0] | EC[4:0]    | Read only | イベント・カウント値。FIFO に現在格納されているイベント数を表示します。                                 |

### FIFO\_1、レジスタ 0x03

表 11. FIFO\_1 ビットの説明

| Bits  | Bit Name          | Access    | Description                                                                                                                                                                                                                                                                                     |

|-------|-------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | EVENT1_STATE      | Read only | このビットは EVENT1_IDENTIFIER[6:0] ビットに記録されたイベントの状態を示します。<br>イベント 1 ~ イベント 36 のキー・イベント場合、次の設定を使います：<br>1 = キーがプレスされている。<br>0 = キーがリリースされている。<br>GPI およびイベント 37 ~ イベント 48 のロジック・イベントの場合、次の設定を使います：<br>1 = GPI/ロジックはアクティブです。<br>0 = GPI/ロジックは非アクティブです。<br>イベント 37 ~ イベント 48 のアクティブ/非アクティブ状態はプログラマブルです。 |

| [6:0] | EVENT1_IDENTIFIER | Read only | ピンのイベント識別子を含みます。イベント・デコーディング情報については表 12 を参照してください。                                                                                                                                                                                                                                              |

表 12. イベント・デコーディング

| Event No. | Meaning         | Event No. | Meaning          |

|-----------|-----------------|-----------|------------------|

| 0         | No event        | 25        | Key 25 (R4, C4)  |

| 1         | Key 1 (R0, C0)  | 26        | Key 26 (R5, C0)  |

| 2         | Key 2 (R0, C1)  | 27        | Key 27 (R5, C1)  |

| 3         | Key 3 (R0, C2)  | 28        | Key 28 (R5, C2)  |

| 4         | Key 4 (R0, C3)  | 29        | Key 29 (R5, C3)  |

| 5         | Key 5 (R0, C4)  | 30        | Key 30 (R5, C4)  |

| 6         | Key 6 (R1, C0)  | 31        | Key 31 (R0, GND) |

| 7         | Key 7 (R1, C1)  | 32        | Key 32 (R1, GND) |

| 8         | Key 8 (R1, C2)  | 33        | Key 33 (R2, GND) |

| 9         | Key 9 (R1, C3)  | 34        | Key 34 (R3, GND) |

| 10        | Key 10 (R1, C4) | 35        | Key 35 (R4, GND) |

| 11        | Key 11 (R2, C0) | 36        | Key 36 (R5, GND) |

| 12        | Key 12 (R2, C1) | 37        | GPI 1 (R0)       |

| 13        | Key 13 (R2, C2) | 38        | GPI 2 (R1)       |

| 14        | Key 14 (R2, C3) | 39        | GPI 3 (R2)       |

| 15        | Key 15 (R2, C4) | 40        | GPI 4 (R3)       |

| 16        | Key 16 (R3, C0) | 41        | GPI 5 (R4)       |

| 17        | Key 17 (R3, C1) | 42        | GPI 6 (R5)       |

| 18        | Key 18 (R3, C2) | 43        | GPI 7 (C0)       |

| 19        | Key 19 (R3, C3) | 44        | GPI 8 (C1)       |

| 20        | Key 20 (R3, C4) | 45        | GPI 9 (C2)       |

| 21        | Key 21 (R4, C0) | 46        | GPI 10 (C3)      |

| 22        | Key 22 (R4, C1) | 47        | GPI 11 (C4)      |

| 23        | Key 23 (R4, C2) | 48        | Logic            |

| 24        | Key 24 (R4, C3) | 49 ~ 127  | 未使用              |

**FIFO\_2、レジスタ 0x04**

表 13. FIFO\_2 ビットの説明

| Bits  | Bit Name               | Access    | Description            |

|-------|------------------------|-----------|------------------------|

| 7     | EVENT2_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT2_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**FIFO\_3、レジスタ 0x05**

表 14. FIFO\_3 ビットの説明

| Bits  | Bit Name               | Access    | Description            |

|-------|------------------------|-----------|------------------------|

| 7     | EVENT3_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT3_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**FIFO\_4、レジスタ 0x06**

表 15. FIFO\_4 ビットの説明

| Bits  | Bit Name               | Access    | Description            |

|-------|------------------------|-----------|------------------------|

| 7     | EVENT4_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT4_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**FIFO\_5、レジスタ 0x07**

表 16. FIFO\_5 ビットの説明

| Bits  | Bit Name               | Access    | Description            |

|-------|------------------------|-----------|------------------------|

| 7     | EVENT5_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT5_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**FIFO\_6、レジスタ 0x08**

表 17. FIFO\_6 ビットの説明

| Bits  | Bit Name               | Access    | Description            |

|-------|------------------------|-----------|------------------------|

| 7     | EVENT6_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT6_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**FIFO\_7、レジスタ 0x09**

表 18. FIFO\_7 ビットの説明

| Bits  | Bit Name               | Access    | Description            |

|-------|------------------------|-----------|------------------------|

| 7     | EVENT7_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT7_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**FIFO\_8、レジスタ 0x0A**

表 19. FIFO\_8 ビットの説明

| Bits  | Bit Name               | Access    | Description            |

|-------|------------------------|-----------|------------------------|

| 7     | EVENT8_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT8_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**FIFO\_9、レジスタ 0x0B**

表 20. FIFO\_9 ビットの説明

| Bits  | Bit Name               | Access    | Description            |

|-------|------------------------|-----------|------------------------|

| 7     | EVENT9_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT9_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**FIFO\_10、レジスタ 0x0C**

表 21. FIFO\_10 ビットの説明

| Bits  | Bit Name                | Access    | Description            |

|-------|-------------------------|-----------|------------------------|

| 7     | EVENT10_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT10_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**FIFO\_11、レジスタ 0x0D**

表 22.FIFO\_11 ビットの説明

| Bits  | Bit Name                | Access    | Description            |

|-------|-------------------------|-----------|------------------------|

| 7     | EVENT11_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT11_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**FIFO\_12、レジスタ 0x0E**

表 23.FIFO\_12 ビットの説明

| Bits  | Bit Name                | Access    | Description            |

|-------|-------------------------|-----------|------------------------|

| 7     | EVENT12_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT12_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**FIFO\_13、レジスタ 0x0F**

表 24.FIFO\_13 ビットの説明

| Bits  | Bit Name                | Access    | Description            |

|-------|-------------------------|-----------|------------------------|

| 7     | EVENT13_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT13_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**FIFO\_14、レジスタ 0x10**

表 25. FIFO\_14 ビットの説明

| Bits  | Bit Name                | Access    | Description            |

|-------|-------------------------|-----------|------------------------|

| 7     | EVENT14_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT14_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**FIFO\_15、レジスタ 0x11**

表 26. FIFO\_15 ビットの説明

| Bits  | Bit Name                | Access    | Description            |

|-------|-------------------------|-----------|------------------------|

| 7     | EVENT15_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT15_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**FIFO\_16、レジスタ 0x12**

表 27. FIFO\_16 ビットの説明

| Bits  | Bit Name                | Access    | Description            |

|-------|-------------------------|-----------|------------------------|

| 7     | EVENT16_STATE           | Read only | ビットの説明は表 11 を参照してください。 |

| [6:0] | EVENT16_IDENTIFIER[6:0] | Read only | ビットの説明は表 11 を参照してください。 |

**GPI\_INT\_STAT\_A、レジスタ 0x13**

表 28. GPI\_INT\_STAT\_A ビットの説明

| Bits  | Bit Name  | Access    | Description                                       |

|-------|-----------|-----------|---------------------------------------------------|

| [7:6] | Reserved  | Reserved  | 予約済み。                                             |

| 5     | GPI_6_INT | Read only | 0 = 割込みなし。<br>1 = GPI 6 (R5 ピン) による割込み。読み出し時にクリア。 |

| 4     | GPI_5_INT | Read only | 0 = 割込みなし。<br>1 = GPI 5 (R4 ピン) による割込み。読み出し時にクリア。 |

| 3     | GPI_4_INT | Read only | 0 = 割込みなし。<br>1 = GPI 4 (R3 ピン) による割込み。読み出し時にクリア。 |

| 2     | GPI_3_INT | Read only | 0 = 割込みなし。<br>1 = GPI 3 (R2 ピン) による割込み。読み出し時にクリア。 |

| 1     | GPI_2_INT | Read only | 0 = 割込みなし。<br>1 = GPI 2 (R1 ピン) による割込み。読み出し時にクリア。 |

| 0     | GPI_1_INT | Read only | 0 = 割込みなし。<br>1 = GPI 1 (R0 ピン) による割込み。読み出し時にクリア。 |

**GPI\_INT\_STAT\_B、レジスタ 0x14**

表 29. GPI\_INT\_STAT\_B ビットの説明

| Bits  | Bit Name   | Access    | Description                                        |

|-------|------------|-----------|----------------------------------------------------|

| [7:5] | Reserved   | Reserved  | 予約済み。                                              |

| 4     | GPI_11_INT | Read only | 0 = 割込みなし。<br>1 = GPI 11 (C4 ピン) による割込み。読み出し時にクリア。 |

| 3     | GPI_10_INT | Read only | 0 = 割込みなし。<br>1 = GPI 10 (C3 ピン) による割込み。読み出し時にクリア。 |

| 2     | GPI_9_INT  | Read only | 0 = 割込みなし。<br>1 = GPI 9 (C2 ピン) による割込み。読み出し時にクリア。  |

| 1     | GPI_8_INT  | Read only | 0 = 割込みなし。<br>1 = GPI 8 (C1 ピン) による割込み。読み出し時にクリア。  |

| 0     | GPI_7_INT  | Read only | 0 = 割込みなし。<br>1 = GPI 7 (C0 ピン) による割込み。読み出し時にクリア。  |

**GPI\_STATUS\_A、レジスタ 0x15**

表 30. GPI\_STATUS\_A ビットの説明

| Bits  | Bit Name   | Access    | Description                                                |

|-------|------------|-----------|------------------------------------------------------------|

| [7:6] | Reserved   | Reserved  | 予約済み。                                                      |

| 5     | GPI_6_STAT | Read only | 0 = GPI 6 (R5 ピン) はローレベルです。<br>1 = GPI 6 (R5 ピン) はハイレベルです。 |

| 4     | GPI_5_STAT | Read only | 0 = GPI 5 (R4 ピン) はローレベルです。<br>1 = GPI 5 (R4 ピン) はハイレベルです。 |

| 3     | GPI_4_STAT | Read only | 0 = GPI 4 (R5 ピン) はローレベルです。<br>1 = GPI 4 (R5 ピン) はハイレベルです。 |

| 2     | GPI_3_STAT | Read only | 0 = GPI 3 (R2 ピン) はローレベルです。<br>1 = GPI 3 (R2 ピン) はハイレベルです。 |

| 1     | GPI_2_STAT | Read only | 0 = GPI 2 (R1 ピン) はローレベルです。<br>1 = GPI 2 (R1 ピン) はハイレベルです。 |

| 0     | GPI_1_STAT | Read only | 0 = GPI 1 (R0 ピン) はローレベルです。<br>1 = GPI 1 (R0 ピン) はハイレベルです。 |

**GPI\_STATUS\_B、レジスタ 0x16**

表 31. GPI\_STATUS\_B ビットの説明

| Bits  | Bit Name    | Access    | Description                                                  |

|-------|-------------|-----------|--------------------------------------------------------------|

| [7:5] | Reserved    | Reserved  | 予約済み。                                                        |

| 4     | GPI_11_STAT | Read only | 0 = GPI 11 (C4 ピン) はローレベルです。<br>1 = GPI 11 (C4 ピン) はハイレベルです。 |

| 3     | GPI_10_STAT | Read only | 0 = GPI 10 (C3 ピン) はローレベルです。<br>1 = GPI 10 (C3 ピン) はハイレベルです。 |

| 2     | GPI_9_STAT  | Read only | 0 = GPI 9 (C2 ピン) はローレベルです。<br>1 = GPI 9 (C2 ピン) はハイレベルです。   |

| 1     | GPI_8_STAT  | Read only | 0 = GPI 8 (C1 ピン) はローレベルです。<br>1 = GPI 8 (C1 ピン) はハイレベルです。   |

| 0     | GPI_7_STAT  | Read only | 0 = GPI 7 (C0 ピン) はローレベルです。<br>1 = GPI 7 (C0 ピン) はハイレベルです。   |

**R\_PULL\_CONFIG\_A、レジスタ 0x17**

デフォルト=0101 0101

**表 32. R\_PULL\_CONFIG\_A ビットの説明**

| Bits  | Bit Name    | Access     | Description                                                                                                               |

|-------|-------------|------------|---------------------------------------------------------------------------------------------------------------------------|

| [7:6] | R3_PULL_CFG | Read/write | 00 = 300 kΩ プルアップ抵抗をイネーブル。<br>01 = 300 kΩ プルダウン抵抗をイネーブル。<br>10 = 100 kΩ プルアップ抵抗をイネーブル。<br>11 = すべてのプルアップ/プルダウン抵抗をディスエーブル。 |

| [5:4] | R2_PULL_CFG | Read/write | 00 = 300 kΩ プルアップ抵抗をイネーブル。<br>01 = 300 kΩ プルダウン抵抗をイネーブル。<br>10 = 100 kΩ プルアップ抵抗をイネーブル。<br>11 = すべてのプルアップ/プルダウン抵抗をディスエーブル。 |

| [3:2] | R1_PULL_CFG | Read/write | 00 = 300 kΩ プルアップ抵抗をイネーブル。<br>01 = 300 kΩ プルダウン抵抗をイネーブル。<br>10 = 100 kΩ プルアップ抵抗をイネーブル。<br>11 = すべてのプルアップ/プルダウン抵抗をディスエーブル。 |

| [1:0] | R0_PULL_CFG | Read/write | 00 = 300 kΩ プルアップ抵抗をイネーブル。<br>01 = 300 kΩ プルダウン抵抗をイネーブル。<br>10 = 100 kΩ プルアップ抵抗をイネーブル。<br>11 = すべてのプルアップ/プルダウン抵抗をディスエーブル。 |

**R\_PULL\_CONFIG\_B、レジスタ 0x18**

デフォルト=0000 0101

**表 33. R\_PULL\_CONFIG\_B ビットの説明**

| Bits  | Bit Name    | Access     | Description                                                                                                                                                 |

|-------|-------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:4] | Reserved    | Reserved   | 予約済み。                                                                                                                                                       |

| [3:2] | R5_PULL_CFG | Read/write | ADP5586ACBZ-01-R7 オプションを除き予約済み<br>00 = 300 kΩ プルアップ抵抗をイネーブル。<br>01 = 300 kΩ プルダウン抵抗をイネーブル。<br>10 = 100 kΩ プルアップ抵抗をイネーブル。<br>11 = すべてのプルアップ/プルダウン抵抗をディスエーブル。 |

| [1:0] | R4_PULL_CFG | Read/write | 00 = 300 kΩ プルアップ抵抗をイネーブル。<br>01 = 300 kΩ プルダウン抵抗をイネーブル。<br>10 = 100 kΩ プルアップ抵抗をイネーブル。<br>11 = すべてのプルアップ/プルダウン抵抗をディスエーブル。                                   |

**R\_PULL\_CONFIG\_C、レジスタ 0x19**

デフォルト=0101 0001

**表 34. R\_PULL\_CONFIG\_C ビットの説明**

| Bits  | Bit Name    | Access     | Description                                                                                                               |

|-------|-------------|------------|---------------------------------------------------------------------------------------------------------------------------|

| [7:6] | C3_PULL_CFG | Read/write | 00 = 300 kΩ プルアップ抵抗をイネーブル。<br>01 = 300 kΩ プルダウン抵抗をイネーブル。<br>10 = 100 kΩ プルアップ抵抗をイネーブル。<br>11 = すべてのプルアップ/プルダウン抵抗をディスエーブル。 |

| [5:4] | C2_PULL_CFG | Read/write | 00 = 300 kΩ プルアップ抵抗をイネーブル。<br>01 = 300 kΩ プルダウン抵抗をイネーブル。<br>10 = 100 kΩ プルアップ抵抗をイネーブル。<br>11 = すべてのプルアップ/プルダウン抵抗をディスエーブル。 |

| [3:2] | C1_PULL_CFG | Read/write | 00 = 300 kΩ プルアップ抵抗をイネーブル。<br>01 = 300 kΩ プルダウン抵抗をイネーブル。<br>10 = 100 kΩ プルアップ抵抗をイネーブル。<br>11 = すべてのプルアップ/プルダウン抵抗をディスエーブル。 |

| [1:0] | C0_PULL_CFG | Read/write | 00 = 300 kΩ プルアップ抵抗をイネーブル。<br>01 = 300 kΩ プルダウン抵抗をイネーブル。<br>10 = 100 kΩ プルアップ抵抗をイネーブル。<br>11 = すべてのプルアップ/プルダウン抵抗をディスエーブル。 |

**R\_PULL\_CONFIG\_D、レジスタ 0x1A**

デフォルト=0000 0001

**表 35. R\_PULL\_CONFIG\_D ピットの説明**

| Bits  | Bit Name    | Access     | Description                                                                                                               |

|-------|-------------|------------|---------------------------------------------------------------------------------------------------------------------------|

| [7:2] | Reserved    | Reserved   | 予約済み。                                                                                                                     |

| [1:0] | C4_PULL_CFG | Read/write | 00 = 300 kΩ プルアップ抵抗をイネーブル。<br>01 = 300 kΩ プルダウン抵抗をイネーブル。<br>10 = 100 kΩ プルアップ抵抗をイネーブル。<br>11 = すべてのプルアップ/プルダウン抵抗をディスエーブル。 |

**GPI\_INT\_LEVEL\_A、レジスタ 0x1B****表 36. GPI\_INT\_LEVEL\_A ピットの説明**

| Bits  | Bit Name        | Access     | Description                                                                                                              |

|-------|-----------------|------------|--------------------------------------------------------------------------------------------------------------------------|

| [7:6] | Reserved        | Reserved   | 予約済み。                                                                                                                    |

| 5     | GPI_6_INT_LEVEL | Read/write | 0 = GPI 6 割込みはアクティブ・ローです (GPI_6_INT は R5 がローになるたびに設定されます)。<br>1 = GPI 6 割込みはアクティブ・ハイです (GPI_6_INT は R5 がハイになるたびに設定されます)。 |

| 4     | GPI_5_INT_LEVEL | Read/write | 0 = GPI 5 割込みはアクティブ・ローです (GPI_5_INT は R4 がローになるたびに設定されます)。<br>1 = GPI 5 割込みはアクティブ・ハイです (GPI_5_INT は R4 がハイになるたびに設定されます)。 |

| 3     | GPI_4_INT_LEVEL | Read/write | 0 = GPI 4 割込みはアクティブ・ローです (GPI_4_INT は R3 がローになるたびに設定されます)。<br>1 = GPI 4 割込みはアクティブ・ハイです (GPI_4_INT は R3 がハイになるたびに設定されます)。 |

| 2     | GPI_3_INT_LEVEL | Read/write | 0 = GPI 3 割込みはアクティブ・ローです (GPI_3_INT は R2 がローになるたびに設定されます)。<br>1 = GPI 3 割込みはアクティブ・ハイです (GPI_3_INT は R2 がハイになるたびに設定されます)。 |

| 1     | GPI_2_INT_LEVEL | Read/write | 0 = GPI 2 割込みはアクティブ・ローです (GPI_2_INT は R1 がローになるたびに設定されます)。<br>1 = GPI 2 割込みはアクティブ・ハイです (GPI_2_INT は R1 がハイになるたびに設定されます)。 |

| 0     | GPI_1_INT_LEVEL | Read/write | 0 = GPI 1 割込みはアクティブ・ローです (GPI_1_INT は R0 がローになるたびに設定されます)。<br>1 = GPI 1 割込みはアクティブ・ハイです (GPI_1_INT は R0 がハイになるたびに設定されます)。 |

**GPI\_INT\_LEVEL\_B、レジスタ 0x1C****表 37. GPI\_INT\_LEVEL\_B ピットの説明**

| Bits  | Bit Name         | Access     | Description                                                                                                                    |

|-------|------------------|------------|--------------------------------------------------------------------------------------------------------------------------------|

| [7:5] | Reserved         | Reserved   | 予約済み。                                                                                                                          |

| 4     | GPI_11_INT_LEVEL | Read/write | 0 = GPI 11 割込みはアクティブ・ローです (GPI_11_INT は R10 がローになるたびに設定されます)。<br>1 = GPI 11 割込みはアクティブ・ハイです (GPI_11_INT は R10 がハイになるたびに設定されます)。 |

| 3     | GPI_10_INT_LEVEL | Read/write | 0 = GPI 10 割込みはアクティブ・ローです (GPI_10_INT は R9 がローになるたびに設定されます)。<br>1 = GPI 10 割込みはアクティブ・ハイです (GPI_10_INT は R9 がハイになるたびに設定されます)。   |

| 2     | GPI_9_INT_LEVEL  | Read/write | 0 = GPI 9 割込みはアクティブ・ローです (GPI_9_INT は R8 がローになるたびに設定されます)。<br>1 = GPI 9 割込みはアクティブ・ハイです (GPI_9_INT は R8 がハイになるたびに設定されます)。       |

| 1     | GPI_8_INT_LEVEL  | Read/write | 0 = GPI 8 割込みはアクティブ・ローです (GPI_8_INT は R7 がローになるたびに設定されます)。<br>1 = GPI 8 割込みはアクティブ・ハイです (GPI_8_INT は R7 がハイになるたびに設定されます)。       |

| 0     | GPI_7_INT_LEVEL  | Read/write | 0 = GPI 7 割込みはアクティブ・ローです (GPI_7_INT は R6 がローになるたびに設定されます)。<br>1 = GPI 7 割込みはアクティブ・ハイです (GPI_7_INT は R6 がハイになるたびに設定されます)。       |

**GPI\_EVENT\_EN\_A、レジスタ 0x1D**

表 38. GPI\_EVENT\_EN\_A ビットの説明

| Bits  | Bit Name       | Access     | Description                                                                              |

|-------|----------------|------------|------------------------------------------------------------------------------------------|

| [7:6] | Reserved       | Reserved   | 予約済み。                                                                                    |

| 5     | GPI_6_EVENT_EN | Read/write | 0 = GPI 6からの GPI イベントをディスエーブルします。<br>1 = GPI 6 アクティビティは FIFO のイベントを生成できます <sup>1</sup> 。 |

| 4     | GPI_5_EVENT_EN | Read/write | 0 = GPI 5からの GPI イベントをディスエーブルします。<br>1 = GPI 5 アクティビティは FIFO のイベントを生成できます <sup>1</sup> 。 |

| 3     | GPI_4_EVENT_EN | Read/write | 0 = GPI 4からの GPI イベントをディスエーブルします。<br>1 = GPI 4 アクティビティは FIFO のイベントを生成できます <sup>1</sup> 。 |

| 2     | GPI_3_EVENT_EN | Read/write | 0 = GPI 3からの GPI イベントをディスエーブルします。<br>1 = GPI 3 アクティビティは FIFO のイベントを生成できます <sup>1</sup> 。 |

| 1     | GPI_2_EVENT_EN | Read/write | 0 = GPI 2からの GPI イベントをディスエーブルします。<br>1 = GPI 2 アクティビティは FIFO のイベントを生成できます <sup>1</sup> 。 |

| 0     | GPI_1_EVENT_EN | Read/write | 0 = GPI 1からの GPI イベントをディスエーブルします。<br>1 = GPI 1 アクティビティは FIFO のイベントを生成できます <sup>1</sup> 。 |

<sup>1</sup> このモードの GPI は FIFO イベントとみなされ、アンロックに使用できます。このモードの GPI アクティビティは EVENT\_INT 割込みを生じます。このモードの GPI は、GPI\_INT 割込みを生成しません。

**GPI\_EVENT\_EN\_B、レジスタ 0x1E**

表 39. GPI\_EVENT\_EN\_B ビットの説明

| Bits  | Bit Name        | Access     | Description                                                                  |

|-------|-----------------|------------|------------------------------------------------------------------------------|

| [7:5] | Reserved        | Reserved   | 予約済み。                                                                        |

| 4     | GPI_11_EVENT_EN | Read/write | 0 = GPI 11からの GPI イベントをディスエーブルします。<br>1 = GPI 11 アクティビティは FIFO のイベントを生成できます。 |

| 3     | GPI_10_EVENT_EN | Read/write | 0 = GPI 10からの GPI イベントをディスエーブルします。<br>1 = GPI 10 アクティビティは FIFO のイベントを生成できます。 |

| 2     | GPI_9_EVENT_EN  | Read/write | 0 = GPI 9からの GPI イベントをディスエーブルします。<br>1 = GPI 9 アクティビティは FIFO のイベントを生成できます。   |

| 1     | GPI_8_EVENT_EN  | Read/write | 0 = GPI 8からの GPI イベントをディスエーブルします。<br>1 = GPI 8 アクティビティは FIFO のイベントを生成できます。   |

| 0     | GPI_7_EVENT_EN  | Read/write | 0 = GPI 7からの GPI イベントをディスエーブルします。<br>1 = GPI 7 アクティビティは FIFO のイベントを生成できます。   |

<sup>1</sup> このモードの GPI は FIFO イベントとみなされ、アンロックに使用できます。このモードの GPI アクティビティは EVENT\_INT 割込みを生じます。このモードの GPI は、GPI\_INT 割込みを生成しません。

**GPI\_INTERRUPT\_EN\_A、レジスタ 0x1F**

表 40. GPI\_INTERRUPT\_EN\_A ビットの説明

| Bits  | Bit Name      | Access     | Description                                                                                                                       |

|-------|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | Reserved      | Reserved   | 予約済み。                                                                                                                             |

| 5     | GPIO_6_INT_EN | Read/write | 0 = GPIO_6_INT はディスエーブルです。<br>1 = GPIO_6_INT はイネーブルです。GPIO_6_INT が設定され、GPIO 6 割込み条件を満足する場合、GPIO_INT ビット（レジスタ 0x01、ビット 1）をアサートします。 |

| 4     | GPIO_5_INT_EN | Read/write | 0 = GPIO_5_INT はディスエーブルです。<br>1 = GPIO_5_INT はイネーブルです。GPIO_5_INT が設定され、GPIO 5 割込み条件を満足する場合、GPIO_INT ビット（レジスタ 0x01、ビット 1）をアサートします。 |

| 3     | GPIO_4_INT_EN | Read/write | 0 = GPIO_4_INT はディスエーブルです。<br>1 = GPIO_4_INT はイネーブルです。GPIO_4_INT が設定され、GPIO 4 割込み条件を満足する場合、GPIO_INT ビット（レジスタ 0x01、ビット 1）をアサートします。 |

| 2     | GPIO_3_INT_EN | Read/write | 0 = GPIO_3_INT はディスエーブルです。<br>1 = GPIO_3_INT はイネーブルです。GPIO_3_INT が設定され、GPIO 3 割込み条件を満足する場合、GPIO_INT ビット（レジスタ 0x01、ビット 1）をアサートします。 |

| 1     | GPIO_2_INT_EN | Read/write | 0 = GPIO_2_INT はディスエーブルです。<br>1 = GPIO_2_INT はイネーブルです。GPIO_2_INT が設定され、GPIO 2 割込み条件を満足する場合、GPIO_INT ビット（レジスタ 0x01、ビット 1）をアサートします。 |

| 0     | GPIO_1_INT_EN | Read/write | 0 = GPIO_1_INT はディスエーブルです。<br>1 = GPIO_1_INT はイネーブルです。GPIO_1_INT が設定され、GPIO 1 割込み条件を満足する場合、GPIO_INT ビット（レジスタ 0x01、ビット 1）をアサートします。 |

**GPI\_INTERRUPT\_EN\_B、レジスタ 0x20**

表 41. GPI\_INTERRUPT\_EN\_B ビットの説明

| Bits  | Bit Name       | Access     | Description                                                                                                                           |

|-------|----------------|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| [7:5] | Reserved       | Reserved   | 予約済み                                                                                                                                  |

| 4     | GPIO_11_INT_EN | Read/write | 0 = GPIO_11_INT はディスエーブルです。<br>1 = GPIO_11_INT はイネーブルです。GPIO_11_INT が設定され、GPIO 11 割込み条件を満足する場合、GPIO_INT ビット（レジスタ 0x01、ビット 1）をアサートします。 |

| 3     | GPIO_10_INT_EN | Read/write | 0 = GPIO_10_INT はディスエーブルです。<br>1 = GPIO_10_INT はイネーブルです。GPIO_10_INT が設定され、GPIO 10 割込み条件を満足する場合、GPIO_INT ビット（レジスタ 0x01、ビット 1）をアサートします。 |

| 2     | GPIO_9_INT_EN  | Read/write | 0 = GPIO_9_INT はディスエーブルです。<br>1 = GPIO_9_INT はイネーブルです。GPIO_9_INT が設定され、GPIO 9 割込み条件を満足する場合、GPIO_INT ビット（レジスタ 0x01、ビット 1）をアサートします。     |

| 1     | GPIO_8_INT_EN  | Read/write | 0 = GPIO_8_INT はディスエーブルです。<br>1 = GPIO_8_INT はイネーブルです。GPIO_8_INT が設定され、GPIO 8 割込み条件を満足する場合、GPIO_INT ビット（レジスタ 0x01、ビット 1）をアサートします。     |

| 0     | GPIO_7_INT_EN  | Read/write | 0 = GPIO_7_INT はディスエーブルです。<br>1 = GPIO_7_INT はイネーブルです。GPIO_7_INT が設定され、GPIO 7 割込み条件を満足する場合、GPIO_INT ビット（レジスタ 0x01、ビット 1）をアサートします。     |

**DEBOUNCE\_DIS\_A、レジスタ 0x21****表 42. DEBOUNCE\_DIS\_A ビットの説明**

| <b>Bits</b> | <b>Bit Name</b> | <b>Access</b> | <b>Description</b>                                   |

|-------------|-----------------|---------------|------------------------------------------------------|

| [7:6]       | Reserved        | Reserved      | 予約済み。                                                |

| 5           | GPI_6_DEB_DIS   | Read/write    | 0=GPI 6 でデバウンスはイネーブルです。<br>1=GP16 でバウンスはディスエーブルです。   |

| 4           | GPI_5_DEB_DIS   | Read/write    | 0=GPI 5 でデバウンスはイネーブルです。<br>1=GPI 5 でデバウンスはディスエーブルです。 |

| 3           | GPI_4_DEB_DIS   | Read/write    | 0=GPI 4 でデバウンスはイネーブルです。<br>1=GPI 4 でデバウンスはディスエーブルです。 |

| 2           | GPI_3_DEB_DIS   | Read/write    | 0=GPI 3 でデバウンスはイネーブルです。<br>1=GPI 3 でデバウンスはディスエーブルです。 |

| 1           | GPI_2_DEB_DIS   | Read/write    | 0=GPI 2 でデバウンスはイネーブルです。<br>1=GPI 2 でデバウンスはディスエーブルです。 |

| 0           | GPI_1_DEB_DIS   | Read/write    | 0=GPI 1 でデバウンスはイネーブルです。<br>1=GPI 1 でデバウンスはディスエーブルです。 |

**DEBOUNCE\_DIS\_B、レジスタ 0x22****表 43. DEBOUNCE\_DIS\_B ビットの説明**

| <b>Bits</b> | <b>Bit Name</b> | <b>Access</b> | <b>Description</b>                                     |

|-------------|-----------------|---------------|--------------------------------------------------------|

| [7:5]       | Reserved        | Reserved      | 予約済み。                                                  |

| 4           | GPI_11_DEB_DIS  | Read/write    | 0=GPI 11 でデバウンスはイネーブルです。<br>1=GPI 11 でデバウンスはディスエーブルです。 |

| 3           | GPI_10_DEB_DIS  | Read/write    | 0=GPI 10 でデバウンスはイネーブルです。<br>1=GPI 10 でデバウンスはディスエーブルです。 |

| 2           | GPI_9_DEB_DIS   | Read/write    | 0=GPI 9 でデバウンスはイネーブルです。<br>1=GPI 9 でデバウンスはディスエーブルです。   |

| 1           | GPI_8_DEB_DIS   | Read/write    | 0=GPI 8 でデバウンスはイネーブルです。<br>1=GPI 8 でデバウンスはディスエーブルです。   |

| 0           | GPI_7_DEB_DIS   | Read/write    | 0=GPI 7 でデバウンスはイネーブルです。<br>1=GPI 7 でデバウンスはディスエーブルです。   |

**GPO\_DATA\_OUT\_A、レジスタ 0x23****表 44. GPO\_DATA\_OUT\_A ビットの説明**

| <b>Bits</b> | <b>Bit Name</b> | <b>Access</b> | <b>Description</b>               |

|-------------|-----------------|---------------|----------------------------------|

| [7:6]       | Reserved        | Reserved      | 予約済み。                            |

| 5           | GPO_6_DATA      | Read/write    | 0=出力をローレベルに設定。<br>1=出力をハイレベルに設定。 |

| 4           | GPO_5_DATA      | Read/write    | 0=出力をローレベルに設定。<br>1=出力をハイレベルに設定。 |

| 3           | GPO_4_DATA      | Read/write    | 0=出力をローレベルに設定。<br>1=出力をハイレベルに設定。 |

| 2           | GPO_3_DATA      | Read/write    | 0=出力をローレベルに設定。<br>1=出力をハイレベルに設定。 |

| 1           | GPO_2_DATA      | Read/write    | 0=出力をローレベルに設定。<br>1=出力をハイレベルに設定。 |

| 0           | GPO_1_DATA      | Read/write    | 0=出力をローレベルに設定。<br>1=出力をハイレベルに設定。 |

**GPO\_DATA\_OUT\_B、レジスタ 0x24****表 45. GPO\_DATA\_OUT\_B ビットの説明**

| <b>Bits</b> | <b>Bit Name</b> | <b>Access</b> | <b>Description</b>                   |

|-------------|-----------------|---------------|--------------------------------------|

| [7:5]       | Reserved        | Reserved      | 予約済み。                                |

| 4           | GPO_11_DATA     | Read/write    | 0 = 出力をローレベルに設定。<br>1 = 出力をハイレベルに設定。 |