# 高精度イネーブルおよびパワーグッド出力付き 1800 mA トリプル降圧レギュレータ

## データシート

## ADP5135

### 特長

- 入力電圧範囲: 3.0 V~5.5 V

- 3 個の 1800 mA 降圧レギュレータを内蔵

- 4 mm × 4 mm の 24 ピン LFCSP パッケージを採用

- レギュレータ精度: ±1.8%

- VOUTx ピンを出荷時設定または外部調整可能

- 高精度なため電源シケンシングが容易

- 各レギュレータ・モニタ用のパワーグッド・ピン

- 強制 PWM モードおよび自動 PWM/PSM モードによる 3 MHz 降圧レギュレーション動作

- BUCK1/BUCK2/BUCK3 の出力電圧範囲: 0.8 V~3.8 V

### アプリケーション

- プロセッサ、ASIC、フィールド・プログラマブル・ゲート・アレイ (FPGA)、無線周波数 (RF) チップセット向けの電源

- 携帯型計装機器および医用機器

- 省スペース機器

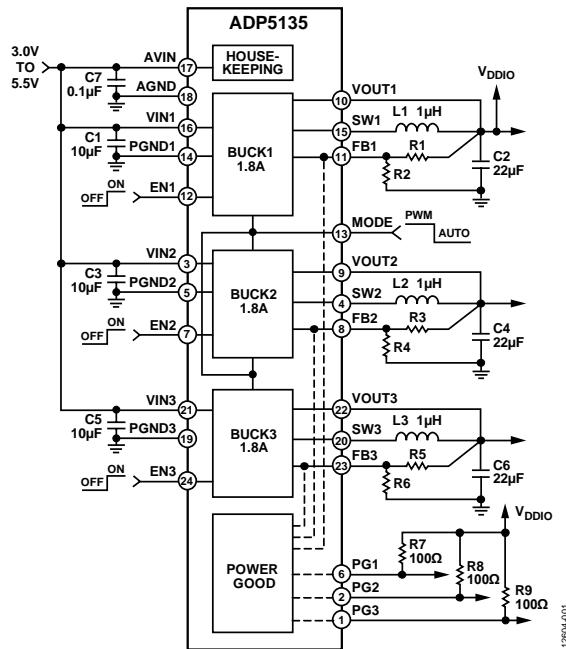

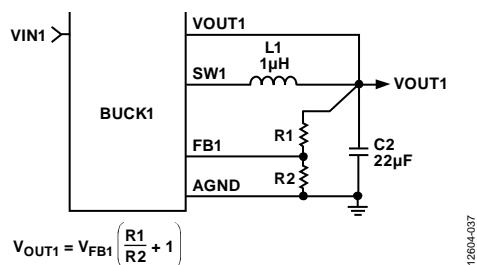

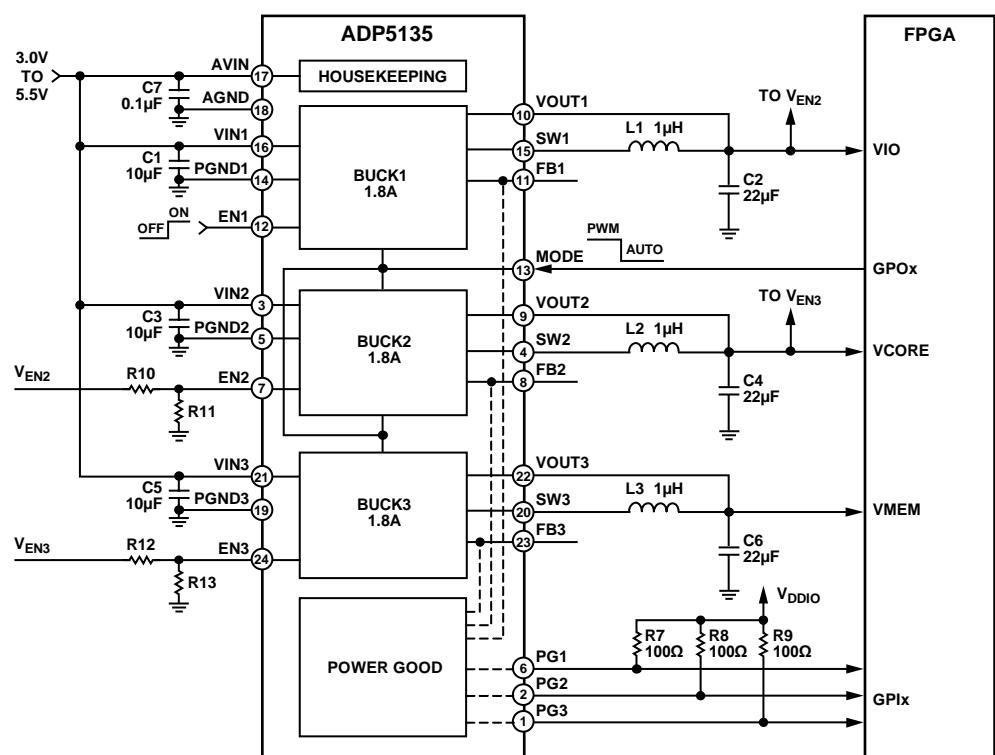

### 代表的なアプリケーション回路

図 1.

表 1. ファミリー・デバイス

| Device  | Channels                                                                               | Max Current       | Package                              |

|---------|----------------------------------------------------------------------------------------|-------------------|--------------------------------------|

| ADP5023 | 2 buck regulators, 1 LDO                                                               | 800 mA,<br>300 mA | LFCSP (CP-24-10)                     |

| ADP5024 | 2 buck regulators, 1 LDO                                                               | 1.2 A,<br>300 mA  | LFCSP (CP-24-10)                     |

| ADP5034 | 2 buck regulators, 2 LDOs                                                              | 1.2 A,<br>300 mA  | LFCSP (CP-24-10),<br>TSSOP (RE-28-1) |

| ADP5037 | 2 buck regulators, 2 LDOs                                                              | 800 mA,<br>300 mA | LFCSP (CP-24-10)                     |

| ADP5033 | 2 buck regulators, 2 LDOs with 2 ENx pins                                              | 800 mA,<br>300 mA | WLCSP (CB-16-8)                      |

| ADP5040 | 1 buck regulator, 2 LDOs                                                               | 1.2 A,<br>300 mA  | LFCSP (CP-20-10)                     |

| ADP5041 | 1 buck regulator, 2 LDOs with supervisory circuit, watchdog function, and manual reset | 1.2 A,<br>300 mA  | LFCSP (CP-20-10)                     |

| ADP5133 | 2 buck regulators with 2 ENx pins                                                      | 800 mA            | WLCSP (CB-16-8)                      |

| ADP5134 | 2 buck regulators, 2 LDOs with precision enable and power good                         | 1.2 A,<br>300 mA  | LFCSP (CP-24-7)                      |

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                   |   |                             |    |

|-------------------|---|-----------------------------|----|

| 特長                | 1 | 動作原理                        | 13 |

| アプリケーション          | 1 | パワーマネジメント・ユニット              | 13 |

| 代表的なアプリケーション回路    | 1 | 降圧レギュレータ: BUCK1、BUCK2、BUCK3 | 15 |

| 概要                | 1 | アプリケーション情報                  | 17 |

| 改訂履歴              | 2 | 降圧レギュレータ外付け部品の選択            | 17 |

| 仕様                | 3 | 代表的なアプリケーション回路図             | 19 |

| BUCK1、BUCK2、BUCK3 | 4 | 消費電力と熱についての考慮事項             | 21 |

| 推奨入力コンデンサと出力コンデンサ | 4 | 降圧レギュレータの消費電力               | 21 |

| 絶対最大定格            | 5 | ジャンクション温度                   | 22 |

| 熱抵抗               | 5 | PCB レイアウトのガイドライン            | 23 |

| ESD の注意           | 5 | 外形寸法                        | 24 |

| ピン配置およびピン機能説明     | 6 | オーダー・ガイド                    | 24 |

| 代表的な性能特性          | 7 |                             |    |

## 改訂履歴

11/14—Revision 0: Initial Version

## 仕様

特に指定がない限り、 $V_{AVIN} = V_{IN1} = V_{IN2} = V_{IN3} = 3.0\text{ V} \sim 5.5\text{ V}$ ; 最小／最大仕様では  $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、typ 仕様では  $T_A = 25^\circ\text{C}$ 。

表 2.

| Parameter                           | Symbol                                | Test Conditions/Comments                                        | Min  | Typ  | Max  | Unit             |

|-------------------------------------|---------------------------------------|-----------------------------------------------------------------|------|------|------|------------------|

| INPUT VOLTAGE RANGE                 | $V_{AVIN}, V_{IN1}, V_{IN2}, V_{IN3}$ |                                                                 | 3.0  | 5.5  |      | V                |

| THERMAL SHUTDOWN                    |                                       |                                                                 |      |      |      |                  |

| Threshold                           | $T_{SD}$                              | $T_J$ rising                                                    |      | 150  |      | $^\circ\text{C}$ |

| Hysteresis                          | $T_{SD\_HYS}$                         |                                                                 |      | 20   |      | $^\circ\text{C}$ |

| START-UP TIME <sup>1</sup>          |                                       |                                                                 |      |      |      |                  |

| BUCK1                               | $t_{START1}$                          |                                                                 |      | 450  |      | $\mu\text{s}$    |

| BUCK2                               | $t_{START2}$                          |                                                                 |      | 550  |      | $\mu\text{s}$    |

| BUCK3                               | $t_{START3}$                          |                                                                 |      | 550  |      | $\mu\text{s}$    |

| START-UP TIME, BUCK3 FIRST          |                                       |                                                                 |      |      |      |                  |

| BUCK3                               | $t_{START4}$                          |                                                                 |      | 550  |      | $\mu\text{s}$    |

| BUCK1                               | $t_{START5}$                          |                                                                 |      | 200  |      | $\mu\text{s}$    |

| BUCK2                               | $t_{START6}$                          |                                                                 |      | 300  |      | $\mu\text{s}$    |

| SHUTDOWN CONTROL                    |                                       | All ENx pins below $V_{IL\_EN}$ level to achieve $I_{SHUTDOWN}$ |      |      |      | V                |

| Level High                          | $V_{IH\_EN}$                          |                                                                 | 0.9  |      |      |                  |

| Level Low                           | $V_{IL\_EN}$                          |                                                                 |      | 0.35 |      | V                |

| PRECISION ENABLE PINS               |                                       | Regulator activation/deactivation thresholds                    |      |      |      | V                |

| Analog Activation Threshold         | $V_{ENR}$                             | Device out of shutdown ( $V_{ENx} > V_{IH\_EN}$ )               | 0.94 | 0.97 | 1    |                  |

| Hysteresis (Regulator Deactivation) | $V_{ENH}$                             |                                                                 |      | 80   |      | mV               |

| Input Leakage Current               | $V_{I\_LEAKAGE}$                      |                                                                 |      | 0.05 | 1    | $\mu\text{A}$    |

| POWER-GOOD PINS                     |                                       | Monitors $V_{OUT}$ falling out of regulation                    |      |      |      |                  |

| Falling Threshold                   | $V_{PGLOW}$                           |                                                                 |      | 85   |      | % $V_{OUT}$      |

| Rising Threshold                    | $V_{PGHYS}$                           |                                                                 | 91   | 94   | 97   | % $V_{OUT}$      |

| Delay                               | $t_{PGDLY}$                           |                                                                 |      | 20   |      | $\mu\text{s}$    |

| Leakage Current                     | $I_{PGIQ}$                            | $V_{PG} = V_{IN}$                                               |      |      | 1    | $\mu\text{A}$    |

| Output Voltage Low                  | $V_{PGOL}$                            | Load current = 1 mA                                             |      | 0.02 | 0.15 | V                |

| MODE PIN                            |                                       |                                                                 |      |      |      |                  |

| Level High                          | $V_{IH\_MOD}$                         |                                                                 | 1.1  |      |      | V                |

| Level Low                           | $V_{IL\_MOD}$                         |                                                                 |      | 0.4  |      | V                |

| INPUT CURRENT                       |                                       | No load, no buck switching                                      |      |      |      |                  |

| All Channels Enabled                | $I_{STBY\_NOSW}$                      |                                                                 |      | 85   | 110  | $\mu\text{A}$    |

| All Channels Disabled               | $I_{SHUTDOWN}$                        | $T_J = -40^\circ\text{C} \text{ to } +85^\circ\text{C}$         |      | 0.3  | 1.5  | $\mu\text{A}$    |

| AVIN UNDERVOLTAGE LOCKOUT           |                                       |                                                                 |      |      |      |                  |

| Mid UVLO Input Voltage Rising       | $UVLO_{AVINRISE}$                     |                                                                 |      |      | 2.95 | V                |

| Mid UVLO Input Voltage Falling      | $UVLO_{AVINFALL}$                     |                                                                 |      | 2.45 |      | V                |

<sup>1</sup> スタートアップ時間は、 $EN1 = EN2 = EN3$  が 0 V から  $V_{AVIN}$  に変化した時点から、 $V_{OUT1}$ 、 $V_{OUT2}$ 、 $V_{OUT3}$  が公称値の 90% に達する時点までの時間として定義されます。別のチャンネルが既にイネーブルされている場合、各チャンネルのスタートアップ時間は短くなります。詳細については、代表的な性能特性のセクションを参照してください。

**BUCK1、BUCK2、BUCK3**

特に指定がない限り、 $V_{AVIN} = V_{IN1} = V_{IN2} = V_{IN3} = 3.0\text{ V} \sim 5.5\text{ V}$ ; 最小／最大仕様では  $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、typ 仕様では  $T_A = 25^\circ\text{C}$ 。<sup>1</sup>

表 3.

| Parameter                   | Symbol                                                                                                                               | Test Conditions/Comments                                                                       | Min   | Typ   | Max   | Unit             |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------|-------|-------|------------------|

| OUTPUT CHARACTERISTICS      |                                                                                                                                      |                                                                                                |       |       |       |                  |

| Output Voltage Accuracy     | $\Delta V_{OUT1}/V_{OUT1}, \Delta V_{OUT2}/V_{OUT2}, \Delta V_{OUT3}/V_{OUT3}$                                                       | PWM mode; $I_{LOAD1} = I_{LOAD2} = I_{LOAD3} = 0\text{ mA}$                                    | -1.8  | +1.8  |       | %                |

| Line Regulation             | $(\Delta V_{OUT1}/V_{OUT1})/\Delta V_{IN1}, (\Delta V_{OUT2}/V_{OUT2})/\Delta V_{IN2}, (\Delta V_{OUT3}/V_{OUT3})/\Delta V_{IN3}$    | PWM mode                                                                                       |       | -0.05 |       | %/V              |

| Load Regulation             | $(\Delta V_{OUT1}/V_{OUT1})/\Delta I_{OUT1}, (\Delta V_{OUT2}/V_{OUT2})/\Delta I_{OUT2}, (\Delta V_{OUT3}/V_{OUT3})/\Delta I_{OUT3}$ | $I_{LOAD} = 0\text{ mA}$ to 1800 mA, PWM mode                                                  |       | -0.1  |       | %/A              |

| VOLTAGE FEEDBACK            | $V_{FB1}, V_{FB2}$                                                                                                                   | Models with adjustable outputs                                                                 | 0.491 | 0.5   | 0.509 | V                |

| OPERATING SUPPLY CURRENT    |                                                                                                                                      |                                                                                                |       |       |       |                  |

| BUCK1 Only                  | $I_{IN1}$                                                                                                                            | MODE = ground<br>$I_{LOAD1} = 0\text{ mA}$ , device not switching, all other channels disabled |       | 42    |       | $\mu\text{A}$    |

| BUCK2 Only                  | $I_{IN2}$                                                                                                                            | $I_{LOAD2} = 0\text{ mA}$ , device not switching, all other channels disabled                  |       | 52    |       | $\mu\text{A}$    |

| BUCK3 Only                  | $I_{IN3}$                                                                                                                            | $I_{LOAD3} = 0\text{ mA}$ , device not switching, all other channels disabled                  |       | 52    |       | $\mu\text{A}$    |

| BUCK1, BUCK2, and BUCK3     | $I_{IN}$                                                                                                                             | $I_{LOAD1} = I_{LOAD2} = I_{LOAD3} = 0\text{ mA}$ , device not switching                       |       | 85    |       | $\mu\text{A}$    |

| PSM CURRENT THRESHOLD       | $I_{PSM}$                                                                                                                            | PSM to PWM operation                                                                           | 100   |       |       | mA               |

| SWx CHARACTERISTICS         |                                                                                                                                      |                                                                                                |       |       |       |                  |

| SWx On Resistance           | $R_{NFET}$                                                                                                                           | $V_{IN1} = V_{IN2} = V_{IN3} = 3.6\text{ V}$                                                   | 140   | 225   |       | $\text{m}\Omega$ |

|                             | $R_{PFET}$                                                                                                                           | $V_{IN1} = V_{IN2} = V_{IN3} = 3.6\text{ V}$                                                   | 190   | 295   |       | $\text{m}\Omega$ |

|                             | $R_{NFET}$                                                                                                                           | $V_{IN1} = V_{IN2} = V_{IN3} = 5.5\text{ V}$                                                   | 122   | 189   |       | $\text{m}\Omega$ |

|                             | $R_{PFET}$                                                                                                                           | $V_{IN1} = V_{IN2} = V_{IN3} = 5.5\text{ V}$                                                   | 147   | 228   |       | $\text{m}\Omega$ |

| Current Limit               | $I_{LIMIT1}, I_{LIMIT2}, I_{LIMIT3}$                                                                                                 | Positive channel field effect transistor (PFET) switch peak current limit                      | 2250  | 2600  | 2950  | mA               |

| ACTIVE PULL-DOWN RESISTANCE | $R_{PWDN}$                                                                                                                           | $V_{IN1} = V_{IN2} = V_{IN3} = 3.6\text{ V}$ ; channel disabled                                | 75    |       |       | $\Omega$         |

| OSCILLATOR FREQUENCY        | $f_{SW}$                                                                                                                             |                                                                                                | 2.5   | 3.0   | 3.5   | MHz              |

<sup>1</sup> 温度限界におけるすべての規定値は、標準の統計的品質管理手法(SQC)を使う相関により保証。

**推奨入力コンデンサと出力コンデンサ**

特に指定のない限り、 $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 。

表 4.

| Parameter                                  | Symbol                         | Min   | Typ | Max | Unit          |

|--------------------------------------------|--------------------------------|-------|-----|-----|---------------|

| NOMINAL INPUT AND OUTPUT CAPACITOR RATINGS |                                |       |     |     |               |

| BUCK1, BUCK2, and BUCK3                    |                                |       |     |     |               |

| Input Capacitor Ratings                    | $C_{MIN1}, C_{MIN2}, C_{MIN3}$ | 4.7   | 40  |     | $\mu\text{F}$ |

| Output Capacitor Ratings                   | $C_{MIN4}, C_{MIN5}, C_{MIN6}$ | 10    | 40  |     | $\mu\text{F}$ |

| CAPACITOR ESR                              | $R_{ESR}$                      | 0.001 | 1   |     | $\Omega$      |

## 絶対最大定格

表 5.

| Parameter                                                                      | Rating                   |

|--------------------------------------------------------------------------------|--------------------------|

| AVIN to AGND                                                                   | -0.3 V to +6 V           |

| VIN1, VIN2, VIN3 to AVIN                                                       | -0.3 V to +0.3 V         |

| PGND1, PGND2, PGND3 to AGND                                                    | -0.3 V to +0.3 V         |

| VOUT1, VOUT2, VOUT3, FB1, FB2, FB3, EN1, EN2, EN3, MODE, PG1, PG2, PG3 to AGND | -0.3 V to (AVIN + 0.3 V) |

| SW1 to PGND1                                                                   | -0.3 V to (VIN1 + 0.3 V) |

| SW2 to PGND2                                                                   | -0.3 V to (VIN2 + 0.3 V) |

| SW3 to PGND3                                                                   | -0.3 V to (VIN3 + 0.3 V) |

| Storage Temperature Range                                                      | -65°C to +150°C          |

| Operating Junction Temperature Range                                           | -40°C to +125°C          |

| Soldering Conditions                                                           | JEDEC J-STD-020          |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上での製品動作を定めたものではありません。製品を長時間絶対最大定格状態に置くと製品の信頼性に影響を与えます。

消費電力の詳細については、消費電力と熱についての考慮事項のセクションを参照してください。

### 熱抵抗

$\theta_{JA}$  はワーストケース条件で規定。すなわち表面実装パッケージの場合、デバイスを回路ボードにハンダ付けした状態で規定。

表 6. 热抵抗

| Package Type  | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|---------------|---------------|---------------|------|

| 24-Lead LFCSP | 35            | 3             | °C/W |

### ESD の注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

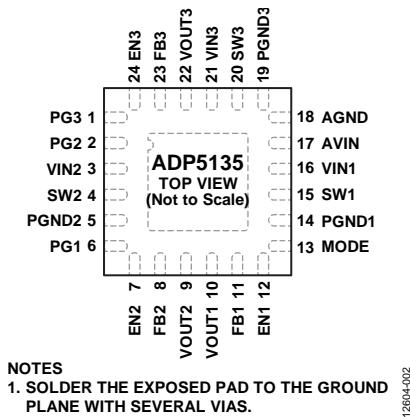

## ピン配置およびピン機能説明

図 2. ピン配置—チップ上面図

表 7. ピン機能の説明

| ピン番号 | 記号    | 説明                                                                                                      |

|------|-------|---------------------------------------------------------------------------------------------------------|

| 1    | PG3   | BUCK3 出力電圧をモニタするオープン・ドレインのパワーグッド出力。                                                                     |

| 2    | PG2   | BUCK2 出力電圧をモニタするオープン・ドレインのパワーグッド出力。                                                                     |

| 3    | VIN2  | BUCK2 入力電源 (3.0 V~5.5 V)。VIN2 を VIN1、VIN3、AVIN へ接続してください。                                               |

| 4    | SW2   | BUCK2 のスイッチング・ノード。                                                                                      |

| 5    | PGND2 | BUCK2 の専用電源グラウンド。                                                                                       |

| 6    | PG1   | BUCK1 出力電圧をモニタするオープン・ドレインのパワーグッド出力。                                                                     |

| 7    | EN2   | BUCK2 イネーブル。ハイ・レベルでこのレギュレータがオンになり、ロー・レベルでオフになります。                                                       |

| 8    | FB2   | BUCK2 帰還入力。調整可能な出力電圧を持つデバイス・モデルでは、このピンを BUCK2 抵抗分圧器の中点に接続してください。固定出力電圧を持つデバイス・モデルでは、このピンを未接続のままにしてください。 |

| 9    | VOUT2 | BUCK2 出力電圧検出入力。VOUT2 を VOUT2 のコンデンサの上側へ接続してください。                                                        |

| 10   | VOUT1 | BUCK1 出力電圧検出入力。VOUT1 を VOUT1 のコンデンサの上側へ接続してください。                                                        |

| 11   | FB1   | BUCK1 帰還入力。調整可能な出力電圧を持つデバイス・モデルでは、このピンを BUCK1 抵抗分圧器の中点に接続してください。固定出力電圧を持つデバイス・モデルでは、このピンを未接続のままにしてください。 |

| 12   | EN1   | BUCK1 イネーブル。ハイ・レベルでこのレギュレータがオンになり、ロー・レベルでオフになります。                                                       |

| 13   | MODE  | BUCK1/BUCK2 動作モード。MODE = ハイ・レベルになると強制 PWM 動作になります。MODE = ロー・レベルになると、自動 PWM/PSM 動作になります。                 |

| 14   | PGND1 | BUCK1 の専用電源グラウンド。                                                                                       |

| 15   | SW1   | BUCK1 のスイッチング・ノード。                                                                                      |

| 16   | VIN1  | BUCK1 入力電源 (3.0 V~5.5 V)。VIN1 を VIN2、VIN3、AVIN へ接続してください。                                               |

| 17   | AVIN  | アナログ入力電源 (3.0 V~5.5 V)。AVIN を VIN1、VIN2、VIN3 へ接続してください。                                                 |

| 18   | AGND  | アナログ・グラウンド。                                                                                             |

| 19   | PGND3 | BUCK3 の専用電源グラウンド。                                                                                       |

| 20   | SW3   | BUCK3 のスイッチング・ノード。                                                                                      |

| 21   | VIN3  | BUCK3 入力電源 (3.0 V~5.5 V)。VIN3 を VIN1、VIN2、AVIN へ接続してください。                                               |

| 22   | VOUT3 | BUCK3 出力電圧検出入力。VOUT3 を VOUT3 のコンデンサの上側へ接続してください。                                                        |

| 23   | FB3   | BUCK3 帰還入力。調整可能な出力電圧を持つデバイス・モデルでは、このピンを BUCK3 抵抗分圧器の中点に接続してください。固定出力電圧を持つデバイス・モデルでは、このピンを未接続のままにしてください。 |

| 24   | EN3   | BUCK3 イネーブル。ハイ・レベルでこのレギュレータがオンになり、ロー・レベルでオフになります。                                                       |

|      | EP    | エクスポートード・パッド。エクスポートード・パッドはグラウンド・プレーンにハンダ付けしてください。                                                       |

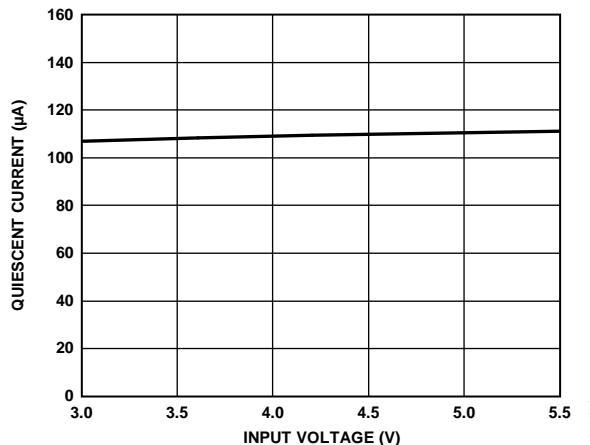

## 代表的な性能特性

特に指定がない限り、 $V_{IN1} = V_{IN2} = V_{IN3} = 3.6\text{ V}$ 、 $T_A = 25^\circ\text{C}$ 。

図 3. 入力電圧対システム静止電流、 $V_{OUT1} = 3.3\text{ V}$ 、 $V_{OUT2} = 1.8\text{ V}$ 、 $V_{OUT3} = 1.2\text{ V}$ 、全チャンネル無負荷

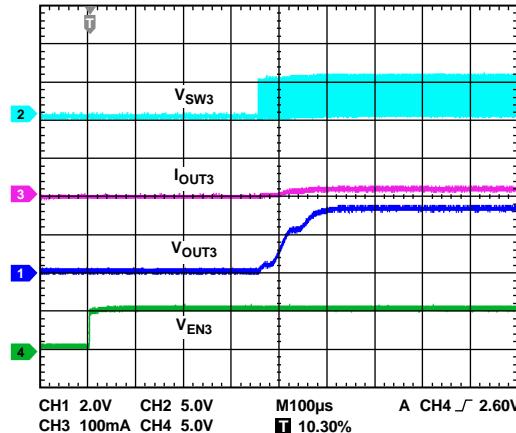

図 6.BUCK3 のスタートアップ、 $V_{OUT3} = 3.3\text{ V}$ 、 $I_{OUT3} = 20\text{ mA}$

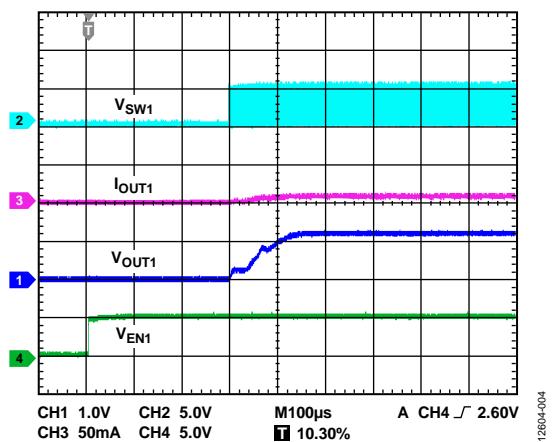

図 4.BUCK1 のスタートアップ、 $V_{OUT1} = 1.2\text{ V}$ 、 $I_{OUT1} = 10\text{ mA}$

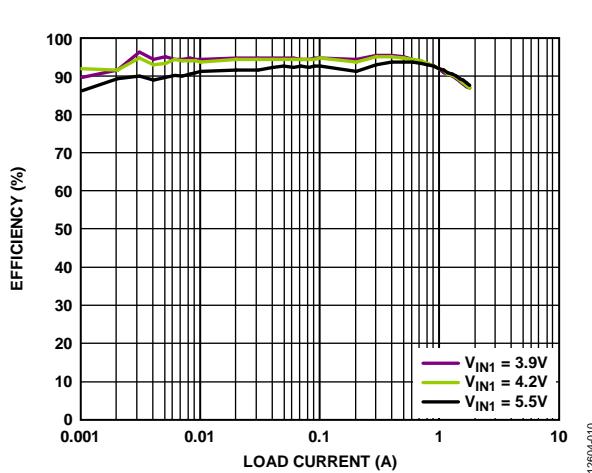

図 7. 様々な入力電圧での BUCK1 負荷レギュレーション

$V_{OUT1} = 3.3\text{ V}$ 、PWM モード

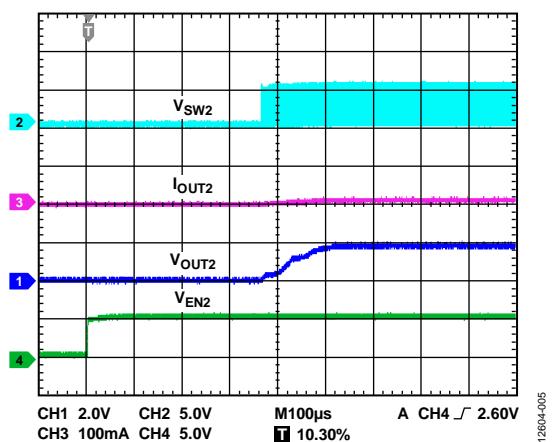

図 5.BUCK2 のスタートアップ、 $V_{OUT2} = 1.8\text{ V}$ 、 $I_{OUT2} = 10\text{ mA}$

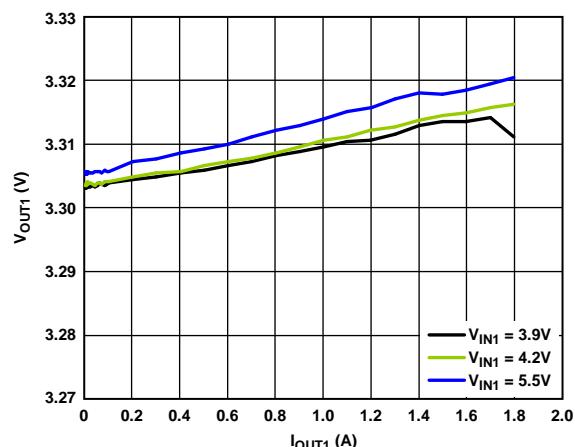

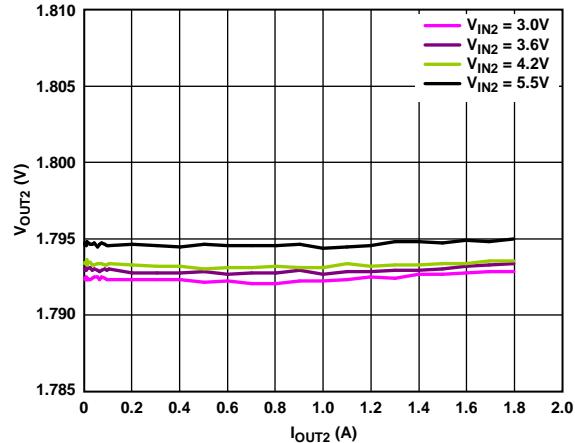

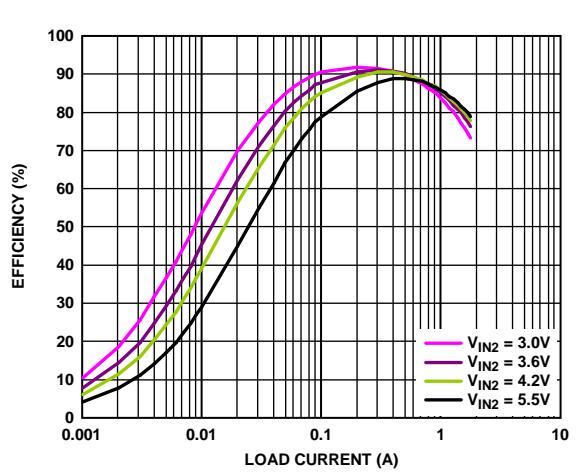

図 8. 様々な入力電圧での BUCK2 負荷レギュレーション

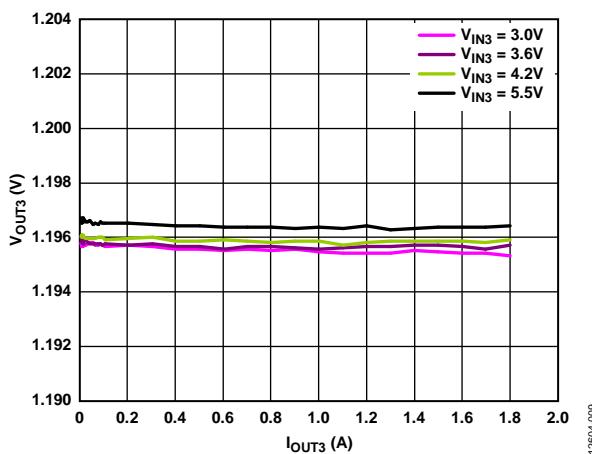

$V_{OUT2} = 1.8\text{ V}$ 、PWM モード

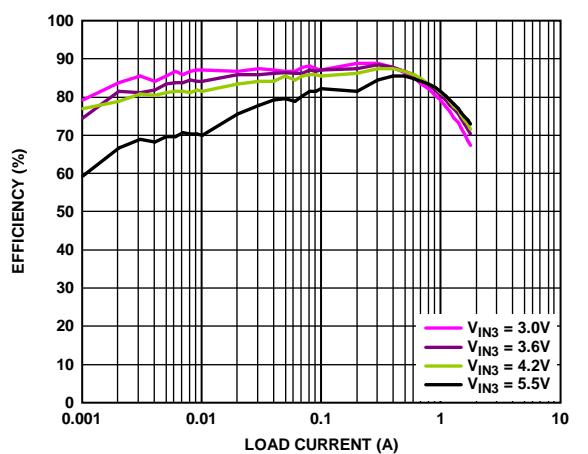

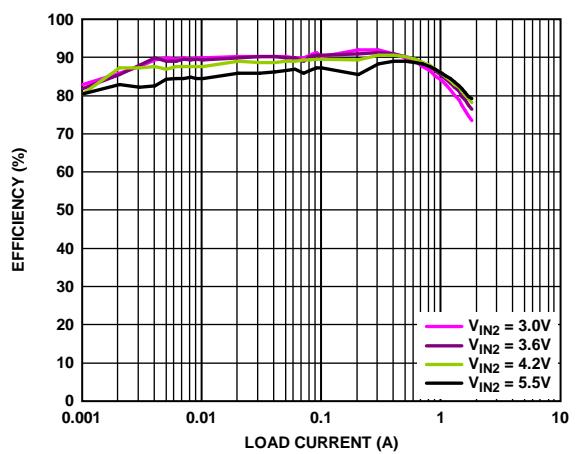

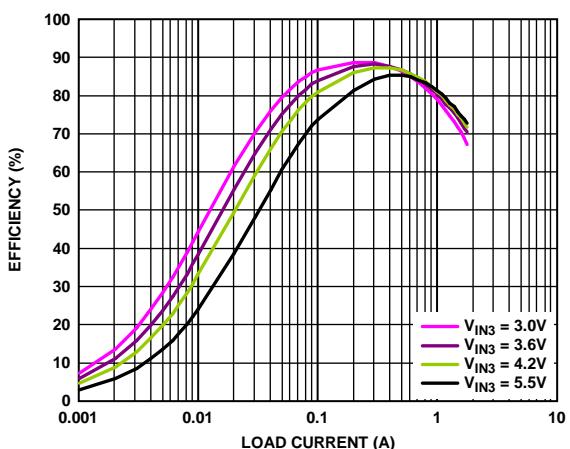

図 15. 様々な入力電圧での負荷電流対 BUCK3 効率、

$V_{OUT3} = 1.2$  V、PWM モード

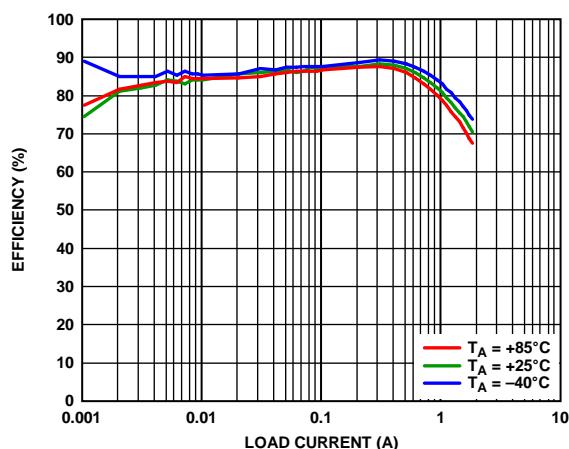

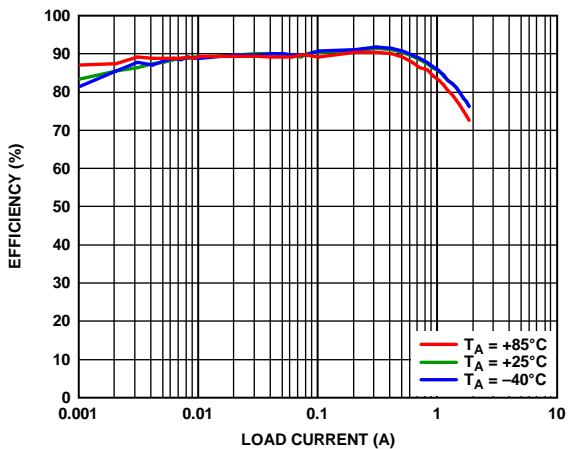

図 18. 様々な温度での負荷電流対 BUCK3 効率、

$V_{OUT3} = 1.2$  V、自動モード

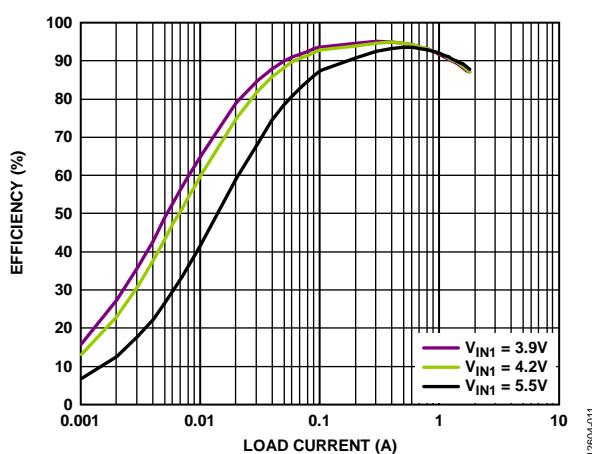

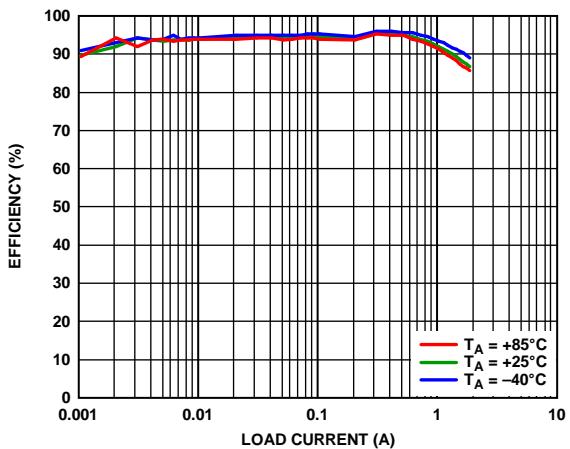

図 16. 様々な温度での負荷電流対 BUCK1 効率、

$V_{OUT1} = 3.3$  V、自動モード

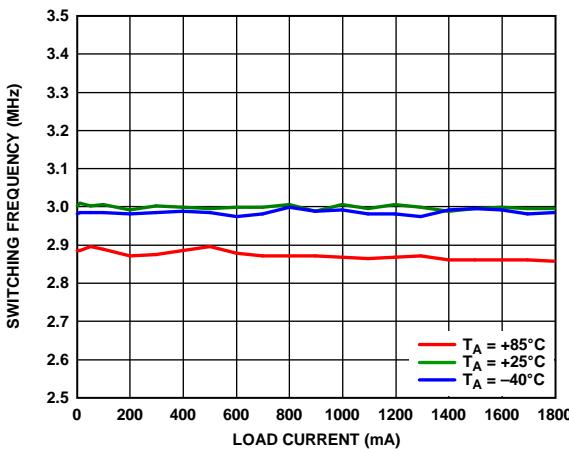

図 19. 様々な温度での負荷電流対 BUCK2 スイッチング周波数、

$V_{OUT2} = 1.8$  V、PWM モード

図 17. 様々な温度での負荷電流対 BUCK2 効率、

$V_{OUT2} = 1.8$  V、自動モード

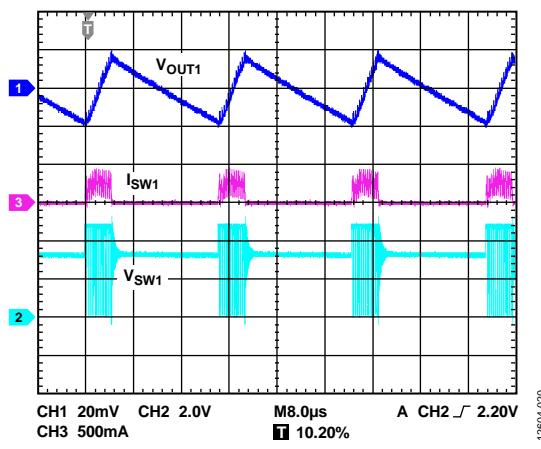

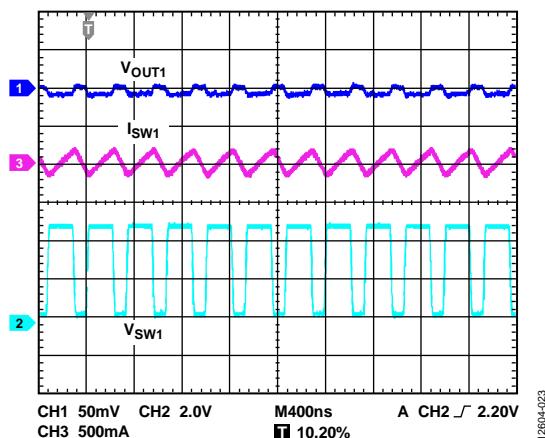

図 20. 代表的波形、 $V_{OUT1} = 3.3$  V

負荷電流 = 50 mA、自動モード

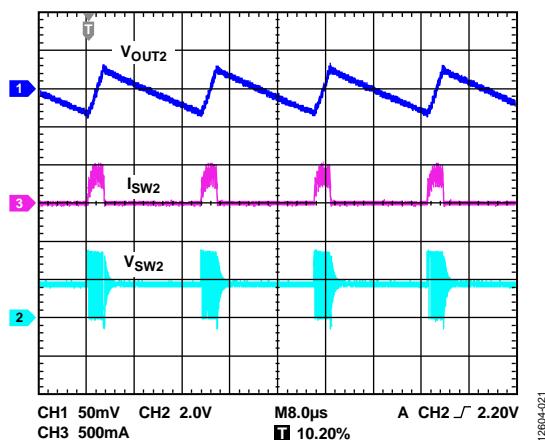

図 21.代表的波形、 $V_{OUT2} = 1.8\text{ V}$ 、負荷電流 = 50 mA

自動モード

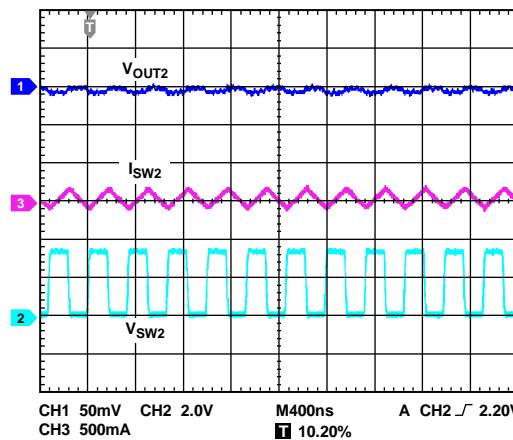

図 24.代表的波形、 $V_{OUT2} = 1.8\text{ V}$ 、負荷電流 = 50 mA

PWM モード

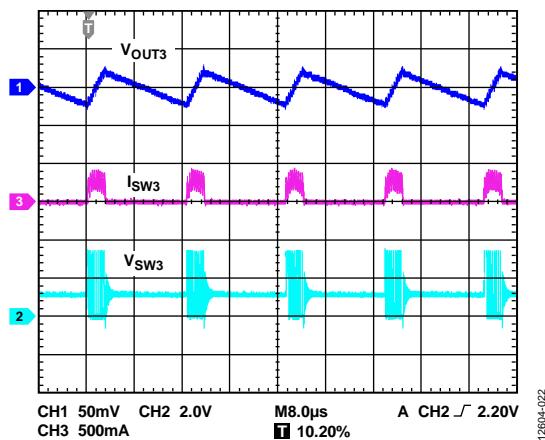

図 22.代表的波形、 $V_{OUT3} = 1.2\text{ V}$ 、負荷電流 = 50 mA

自動モード

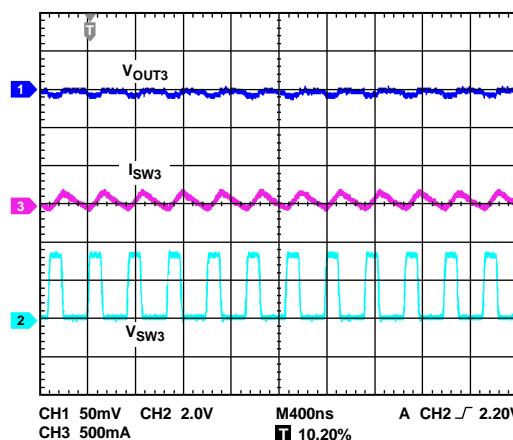

図 25.代表的波形、 $V_{OUT3} = 1.2\text{ V}$ 、負荷電流 = 50 mA

PWM モード

図 23.代表的波形、 $V_{OUT1} = 3.3\text{ V}$ 、負荷電流 = 50 mA

PWM モード

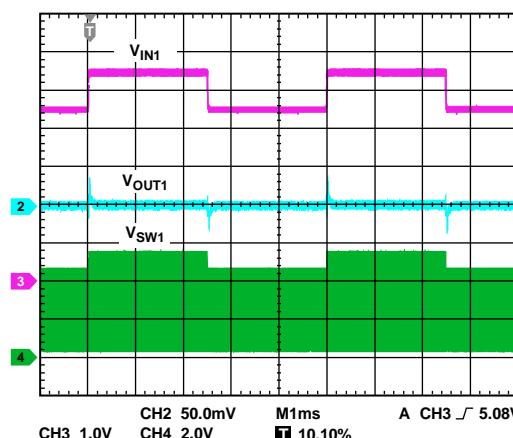

図 26.ライン過渡電圧に対する BUCK1 の応答

入力電圧 4.5 V~5.5 V、 $V_{OUT1} = 3.3\text{ V}$

負荷電流 = 50 mA、PWM モード

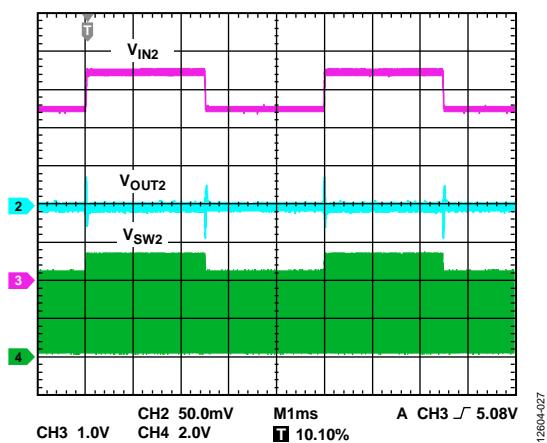

図 27. ライン過渡電圧に対する BUCK2 の応答、入力電圧 4.5 V ~5.5 V、 $V_{OUT2} = 1.8$  V、負荷電流 = 50 mA、PWM モード

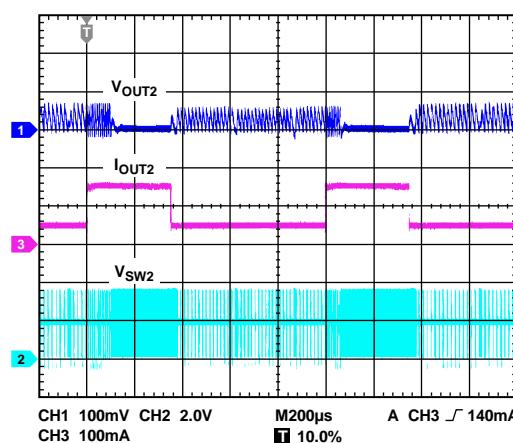

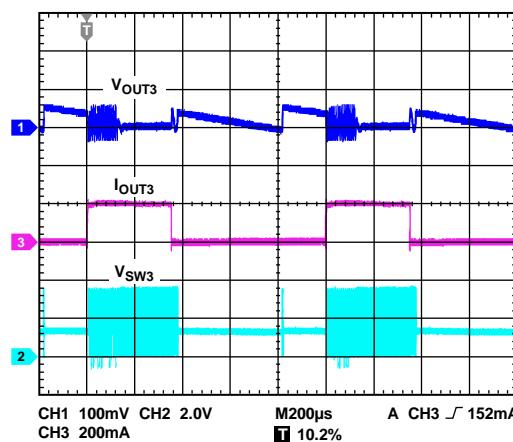

図 30. 負荷過渡電圧に対する BUCK2 の応答、負荷電流 = 50 mA~200 mA、 $V_{OUT2} = 1.8$  V、自動モード

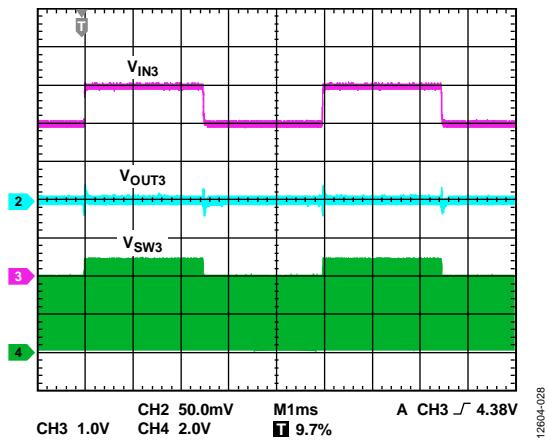

図 28. ライン過渡電圧に対する BUCK3 の応答、入力電圧 4.0 V ~5.0 V、 $V_{OUT3} = 1.2$  V、負荷電流 = 50 mA、PWM モード

図 31. 負荷過渡電圧に対する BUCK3 の応答、負荷電流 = 1 mA ~200 mA、 $V_{OUT3} = 1.2$  V、自動モード

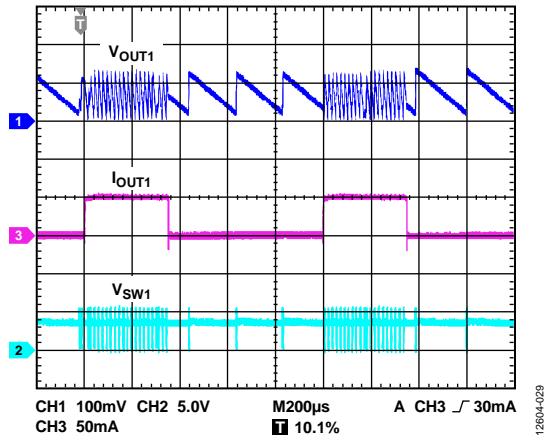

図 29. 負荷過渡電圧に対する BUCK1 の応答、負荷電流 = 1 mA ~50 mA、 $V_{OUT1} = 3.3$  V、自動モード

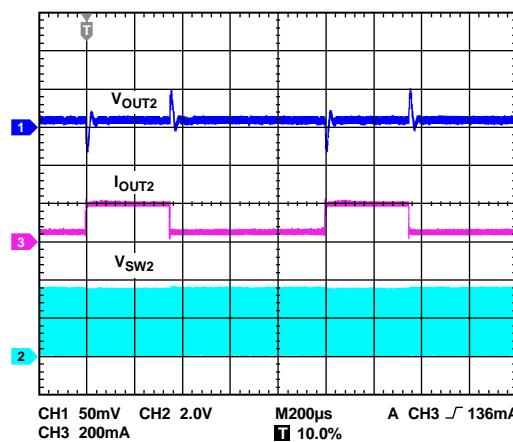

図 32. 負荷過渡電圧に対する BUCK2 の応答、負荷電流 = 1 mA ~200 mA、 $V_{OUT3} = 1.2$  V、PWM モード

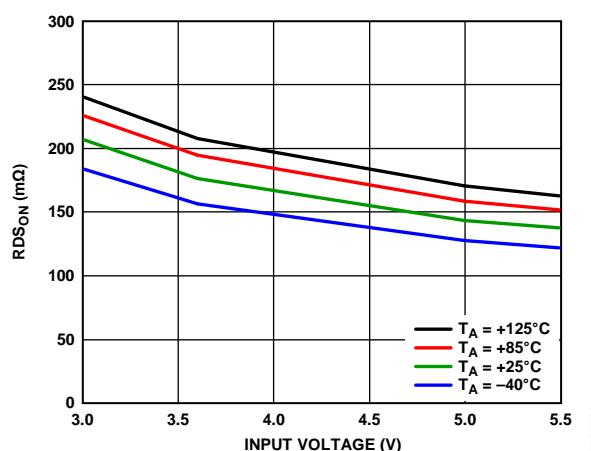

図 33. 様々な温度での入力電圧対 LFCSP 内にある PMOS の  $R_{DS_{ON}}$

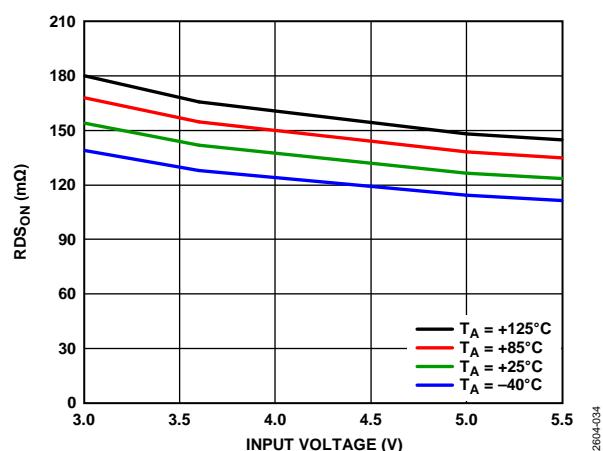

図 34. 様々な温度での入力電圧対 LFCSP 内にある NMOS の  $R_{DS_{ON}}$

## 動作原理

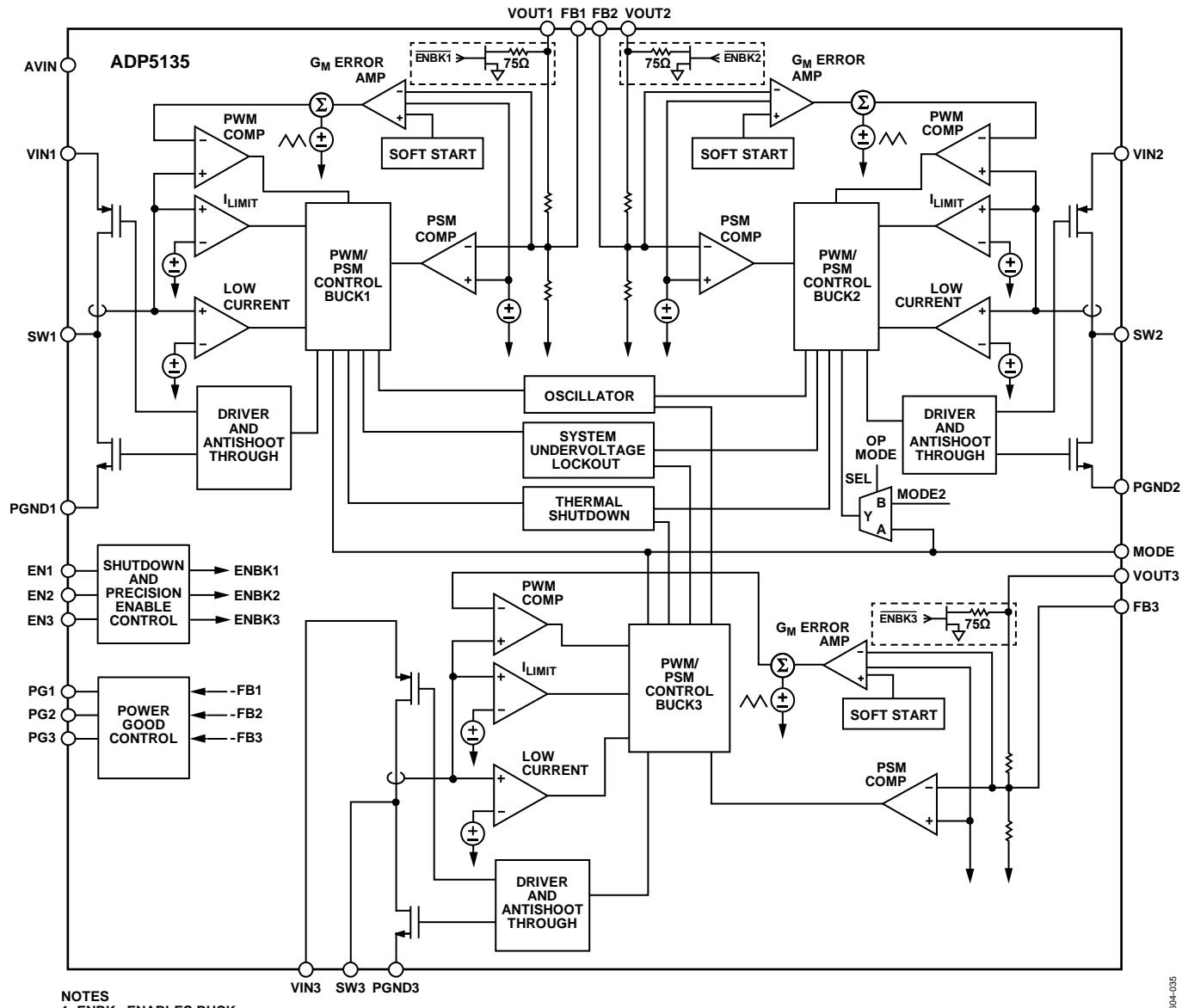

図 35. 詳細機能ブロック図

### パワーマネジメント・ユニット

ADP5135 は、3 個の降圧 DC/DC コンバータ(BUCK)を内蔵するマイクロパワーマネジメント・ユニット(マイクロ PMU)です。高いスイッチング周波数と小型の 24 ピン LFCSP パッケージにより、小型のパワーマネジメント・ソリューションを実現します。

これらの高性能レギュレータを  $\mu$ PMU に組み込むため、これらと一緒に動作可能にするシステム・コントローラが内蔵されています。

MODE ピンがハイ・レベルの場合、降圧レギュレータは強制 PWM モードで動作することができます。強制 PWM モードでは、降圧レギュレータのスイッチング周波数は常に一定になり、負荷電流によって変化しません。MODE ピンがロー・レベルの場合、スイッチング・レギュレータは自動 PWM/PSM モードで動作します。このモードでは、負荷電流が PSM 電流閾値を超える場

合、レギュレータは固定 PWM 周波数で動作します。負荷電流が PSM 電流閾値を下回ると、レギュレータは PSM になります。スイッチングがバースト実行されます。バーストの繰り返しレートは、負荷電流と出力コンデンサ値の関数になります。この動作モードでは、スイッチング電流損失と静止電流損失が小さくなります。自動 PWM/PSM モード変更は、各降圧レギュレータに対して独立に制御されます。BUCK1 と BUCK2 は内部クロックと同相で動作し、BUCK3 は逆相で動作します。

ADP5135 には、各レギュレータの起動を制御する個別のイネーブル・ピン(EN1～EN3)があります。レギュレータは、対応する ENx ピンにハイ・レベルが入力されると起動されます。EN1 は BUCK1 を、EN2 は BUCK2 を、EN3 は BUCK3 を、それぞれ制御します。

レギュレータの出力電圧は外付け抵抗分圧器を使って設定するか、オプションとして出荷時にデフォルト値に設定することができます(オーダー・ガイドのセクション参照)。

レギュレータがオンになると、出力電圧ランプ・レートがソフトスタート回路を使って制御されるため、出力コンデンサの充電による大きな突入電流を回避することができます。

### パワーグッド出力

パワーグッド出力は、各降圧チャンネルの出力電圧をモニタするために設けてあります。PGx ピンは、外付けレギュレータまたはその他の回路を駆動するプルアップ電流に接続します。この構成では、モニタ中のチャンネルがレギュレーション状態のとき PGx ピンがハイ・レベルになり、出力電圧が公称 VOUTx レベルの 85% を下回るとロー・レベルになります。PGx ピンは、故障モニタ用の LED を駆動することもできます。この構成では、例えば、出力電圧が公称 VOUTx レベルの 85% を下回ったときに、赤 LED から PGx ピンへ電流を流して LED を点灯させ、出力電圧がレギュレーション状態のとき LED をオフにします。

### 過熱保護

ジャンクション温度が 150 °C を超えると、サーマル・シャットダウン回路によって全レギュレータがオフになります。ジャンクション温度が極端に高くなる原因には、大電流動作、回路基板の設計不良、あるいは高い周囲温度などがあります。20°C のヒステリシスがあるため、サーマル・シャットダウンが発生すると、オンチップ温度が 130°C 未満に低下するまでレギュレータの動作は再開されません。サーマル・シャットダウン状態が解消すると、ソフトスタート制御でレギュレータが再起動します。

### 低電圧入力保護機能

バッテリの放電を防ぐために低電圧入力保護回路 (UVLO) を内蔵しています。AVIN の入力電圧が 2.45 V (最小値) の UVLO 閾値を下回ると、すべてのチャンネルがシャットダウンします。降圧レギュレータ・チャンネルでは、パワー・スイッチと同期

整流器がオフになります。AVIN の電圧が UVLO 閾値を上回ると、デバイスは再度イネーブルされます。

あるいは、5 V アプリケーションに適する高いレベルに UVLO を設定するか、または低電圧動作に適する低いレベルに UVLO を設定するデバイス・モデルを選択することができます。オーダー・ガイドのセクションに記載するデフォルト・オプション以外のオプションを持つデバイスを注文する場合は、最寄りのアナログ・デバイセズ販売代理店へご連絡ください。

過熱または UVLO が発生した場合、アクティブ・プルダウンがイネーブルされて(出荷時イネーブル設定の場合)、出力コンデンサが迅速に放電します。過熱が存在しなくなるか、または入力電源電圧が VPOR 電圧レベルを下回るまで、プルダウン抵抗は有効のままになります。VPOR は約 1 V (typ)です。

### 高精度イネーブルとシャットダウン制御

ADP5135 には、各レギュレータに対して個別のイネーブル・コントロール・ピンがあります。ENx ピンの電圧入力が V<sub>H\_EN</sub> レベルを上回ると、デバイスはシャットダウンを終了して、ADP5135 のハウスキーピング・ロックを起動します。V<sub>ENx</sub> レベルが高精度イネーブル閾値 (V<sub>ENR</sub>) を超えると、レギュレータが起動します。

V<sub>ENx</sub> が V<sub>ENR</sub> レベルを 80 mV (typ) 下回ると、レギュレータは停止し、すべての V<sub>ENx</sub> レベルが V<sub>L\_EN</sub> レベルを下回ると、デバイスはシャットダウン・モードになります。このモードでは、デバイスの消費電流は 1.5 μA 以下になります。

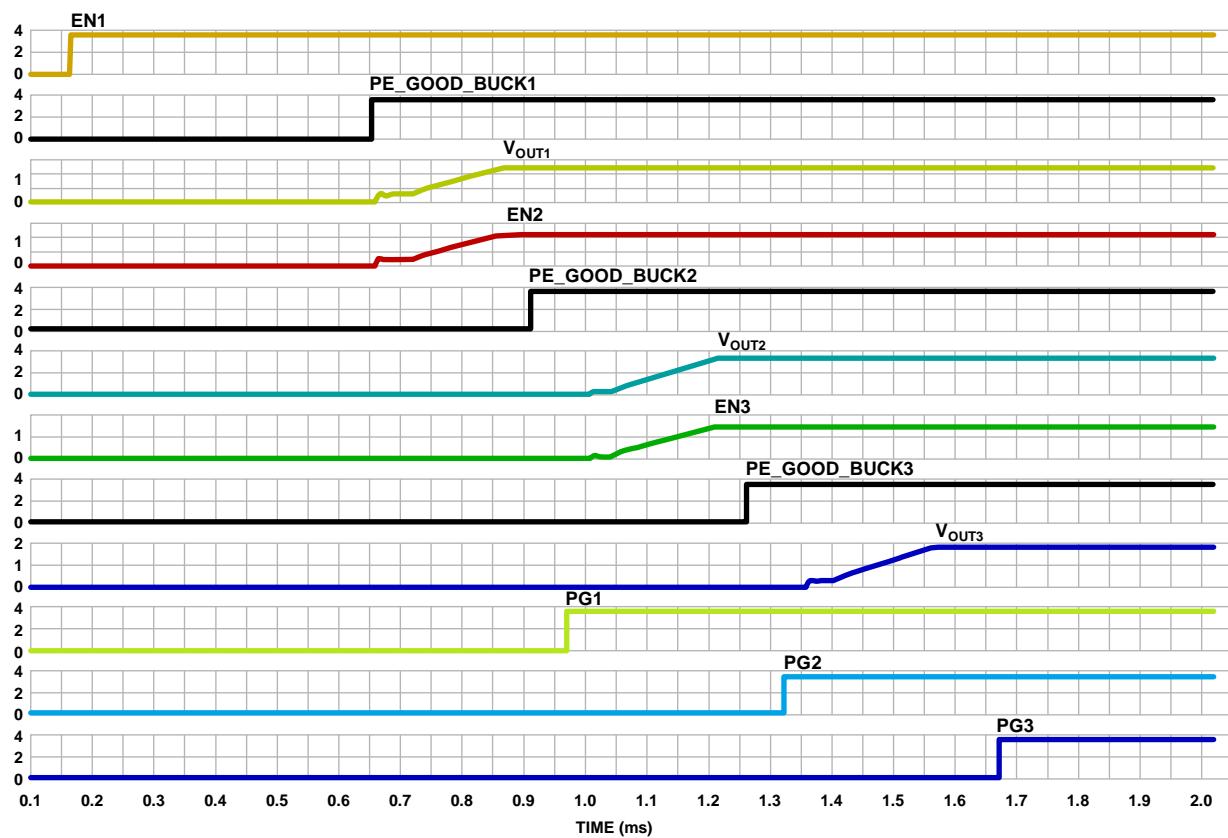

図 36 に、レギュレータがシーケンス動作中の ADP5135 の起動タイミングを示します。V<sub>OUT1</sub> は EN2 を、V<sub>OUT2</sub> は EN3 を、それぞれ制御します。すべてのレギュレータをモニタする個々のパワーグッド信号 (PGx) も示しております。

12604-036

図 36.ADP5135 のレギュレータ・シーケンス、高精度イネーブル (PE) 閾値、パワーグッド

## 降圧レギュレータ: BUCK1、BUCK2、BUCK3

降圧レギュレータでは、固定周波数と高速電流モードのアーキテクチャを採用しています。降圧レギュレータは、入力電圧 = 3.0 V～5.5 V で動作します。

降圧レギュレータの出力電圧は、抵抗を使って 0.8 V～3.8 V の範囲で設定できます。図 37 に BUCK1 について示します。R1 と R2 の比に帰還電圧を乗算して、出力電圧レベルが決定されます。例えば、R1 と R2 が同じ抵抗値の場合、出力電圧は 1.0 V に設定されます。出力電圧はオプションとして出荷時にデフォルト値に設定することもできます(オーダー・ガイドのセクション参照)。この場合、R1 と R2 は不要で、FB1 は未接続のまますることができます。すべての場合に VOUT1 は出力コンデンサへ接続する必要があります。FB1 は 0.5 V です。

図 37.BUCK1 の外部出力電圧設定

## 制御方式

降圧レギュレータは中負荷から重負荷に対して高効率で動作する固定周波数の電流モード PWM 制御方式のアーキテクチャを採用していますが、低負荷時にはパワーセーブモード(PSM)制御方式によってレギュレーションの電力損失を低減します。固定周波数の PWM モードで動作する場合、内蔵スイッチのデューティ・サイクルが調節されて、出力電圧が安定化されます。軽負荷時の PSM で動作するときは、出力電圧をヒステリシス方式で制御するため、出力電圧のリップルが大きくなります。コンバータがこの期間中にスイッチングを停止してアイドル・モードに入ることによって、変換効率を改善できます。

## PWM モード

PWM モードの場合、降圧レギュレータは内部発振器で設定される 3 MHz の固定周波数で動作します。各発振器サイクルの開始時に、PFET スイッチがオンになり、インダクタに正電圧が加わります。インダクタ内の電流は、電流検出信号がピーク電流閾値に達するまで増加します。この電流レベルで、PFET スイッチがオフになり、NFET 同期整流器がオンになり、インダクタに負電圧を加えて、インダクタ電流を減少させます。同期整流器は、残りのサイクルの間はオン状態を維持します。降圧レギュレータは、ピーク・インダクタ電流の閾値を調整することで、出力電圧を安定化します。

### パワーセーブモード (PSM)

降圧レギュレータは、負荷電流が PSM 電流閾値を下回ると、速やかに PSM モードに移行します。いずれかの降圧レギュレータが PSM になると、PWM レギュレーション・レベルにオフセットが加えられ、出力電圧が上昇します。出力電圧が PWM レギュレーションのレベルを約 1.5% 上回ると、PWM 動作はオフになります。この時点で、両パワー・スイッチがオフになり、降圧レギュレータがアイドル・モードになります。出力コンデンサは出力電圧が PWM レギュレーションの電圧レベルに下がるまで放電を続けます。そのレベルに達すると、デバイスがインダクタを駆動して出力電圧を閾値の上限値にまで戻します。このプロセスは、負荷電流が PSM 電流閾値を下回っている限り繰り返されます。

ADP5135 には、PSM と PWM の動作を制御する専用の MODE ピンがあります。MODE ピンをハイ・レベルにすると、全降圧レギュレータは PWM モードで動作し、ロー・レベルにすると、降圧レギュレータは自動 PSM/PWM で動作します。

### PSM 電流閾値

PSM 電流閾値は 100 mA に設定されています。降圧レギュレータは、入力電圧と出力電圧のレベルに関わらず、この電流を正確に制御できる方法を採用しています。これによって、PSM に入るときと終了するときの PSM 電流閾値間のヒステリシスもごく僅かです。PSM の電流閾値は、あらゆる負荷電流において優れた効率性を発揮するように最適化されています。

### 発振器/インダクタ・スイッチングの位相

すべての降圧レギュレータが PWM モードの場合、ADP5135 では 3 個の全降圧レギュレータが同じスイッチング周波数で動作します。

さらに、ADP5135 では、全降圧レギュレータが PWM モードの場合、BUCK3 が BUCK1 と BUCK2 に対して逆相で動作します。そのため、BUCK1 と BUCK2 の PFET が導通し始めてから正確に 1/2 クロック周期遅れて BUCK3 の PFET が導通を開始します。

### 短絡保護機能

降圧レギュレータは、ハード短絡で出力電流が暴走するのを防ぐ周波数フォールドバック機能を備えています。FB ピンの電圧が目標出力電圧の 1/2 を下回り、出力にハード短絡が生じる可能性があると、スイッチング周波数が内部発振器周波数の 1/2 まで低下します。スイッチング周波数が低下するとインダクタの放電時間が長くなるため、出力電流の暴走を防止することができます。

### 降圧レギュレータのソフトスタート

降圧レギュレータにはソフトスタート機能があります。この機能はスタートアップ時に制御された方法で出力電圧を上昇させて、入力突入電流を抑えます。バッテリまたはハイ・インピーダンス電源をコンバータの入力に接続しているときは、この機能によって入力の電圧低下を防止できます。

### 電流制限

各降圧レギュレータには、PFET スイッチを流れる正の電流と、同期整流器を流れる負の電流とを制限するための保護回路があります。パワー・スイッチの正電流制限値は、入力から出力へ流れる電流を制限します。負電流の制御では、インダクタ電流が反転して負荷から流れることを防止します。

### 100% デューティ動作

入力電圧が低下するか負荷電流が増大すると、降圧レギュレータは、PFET スイッチが 100% のデューティ時間オンになっていても出力電圧が所望の出力電圧を下回る限界に達します。この限界で、降圧レギュレータは PFET スイッチが 100% のデューティ時間オン状態を維持するモードに移行します。入力状態が再度変化して必要なデューティ・サイクルが低下すると、ただちに PWM レギュレーションを再開し、出力電圧のオーバーシュートを防ぎます。

### アクティブ・プルダウン抵抗

すべてのレギュレータには、オプションで出荷時設定可能なアクティブ・プルダウン抵抗があり、レギュレータをディスエーブルしたとき、これらの抵抗によりそれぞれの出力コンデンサが放電されます。プルダウン抵抗は、VOUTx と AGND との間に接続されます。レギュレータがオンになると、アクティブ・プルダウンはディスエーブルされます。プルダウン抵抗の typ 値は 75 Ω です。

## アプリケーション情報

### 降圧レギュレータ外付け部品の選択

アプリケーション回路内の外付け部品の選択を変えて、効率や過渡応答のような性能パラメータ間のトレードオフを行うことができます(図 1 参照)。

#### 帰還抵抗

調整可能モデルの場合、R1 と R2 の合計組み合わせ抵抗は 400 kΩ を超えることはできません(図 37 参照)。

#### インダクタ

ADP5135 の降圧レギュレータはスイッチング周波数が高いため、小型のチップ・インダクタを使用できます。最適性能を得るために、0.7 μH～3 μH のインダクタ値を使用してください。推奨インダクタを表 8 と表 9 に示します。

ピーク to ピークのインダクタ・リップル電流( $I_{RIPPLE}$ )は、次式で計算されます。

$$I_{RIPPLE} = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times L}$$

ここで、

$f_{SW}$  はスイッチング周波数。

L はインダクタ値です。

インダクタの定格最小 DC 電流値はそのピーク電流より大きい値にする必要があります。インダクタのピーク電流( $I_{PEAK}$ )は、次式を使って計算します。

$$I_{PEAK} = I_{LOAD(MAX)} + \frac{I_{RIPPLE}}{2}$$

インダクタの導通損失は、インダクタを流れる電流に起因しますが、これには関連する内部 DC 抵抗(DCR)があります。インダクタのサイズが大きければ DCR が小さくなり、インダクタの導通損失が小さくなります。インダクタのコア損失は、コアの材料の透磁率に関係しています。降圧レギュレータは高いスイッチング周波数を使用する DC/DC コンバータであるため、コア損失と EMI が低いシールド・フェライトのコア材の使用を推奨します。

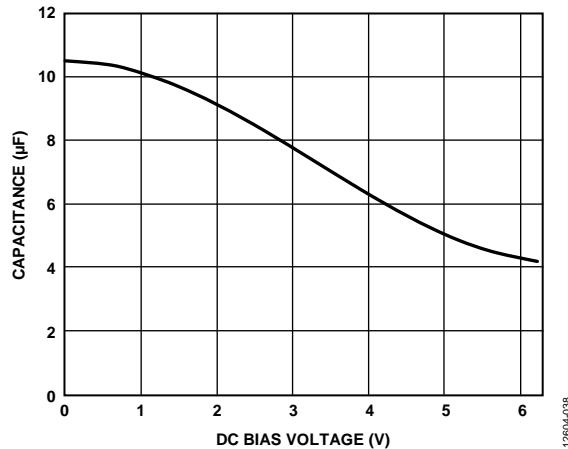

#### 出力コンデンサ

出力容量値が大きいと出力電圧リップルが小さくなり、負荷過渡応答が向上します。この値を選択するときは、出力電圧 DC バイアスに起因する容量損失を考慮することも重要です。

表 8.1.0 μH の推奨インダクタ

| Vendor            | Model          | Dimensions (mm) | $I_{SAT}$ (mA) <sup>1</sup> | DCR (mΩ) |

|-------------------|----------------|-----------------|-----------------------------|----------|

| Murata            | LQM2HPN1R0MJHL | 2.5 × 2.0 × 1.2 | 3500                        | 50       |

| Wurth Electronics | 74438323010    | 2.5 × 2.0 × 1.0 | 4000                        | 75       |

| Coilcraft®        | XFL4020-102ME  | 4.0 × 4.0 × 2.1 | 5100                        | 11.9     |

<sup>1</sup>  $I_{SAT}$  は飽和電流。

セラミック・コンデンサは様々な誘電体を使って製造されて、各々は温度と加えられる電圧に対して異なる動作をします。コンデンサは、必要とされる温度範囲と DC バイアス条件で最小容量を確保できる十分な誘電体を持つ必要があります。最適な性能を得るために、電圧定格値が 6.3 V または 10 V の X5R または X7R の誘電体を推奨します。Y5V と Z5U の誘電体は、温度特性や DC バイアス特性が劣るため、DC/DC コンバータには適していません。

温度、部品の許容誤差、電圧によるコンデンサの変動を考慮して、最悪時の容量を求めるときは、次式を使用します。

$$C_{EFF} = C_{OUT} \times (1 - TEMPCO) \times (1 - TOL)$$

ここで、

$C_{EFF}$  は動作電圧での実効容量。

TEMPCO は最悪時のコンデンサ温度係数です。

TOL は最悪時の部品許容誤差です。

この例では、−40°C～+85°C でのワーストケース温度係数(TEMPCO)を、X5R 誘電体では 15% と想定しています。図 38 に示すように、コンデンサの許容誤差(TOL)は 10%、かつ 1.8 V で  $C_{OUT} = 9.2 \mu\text{F}$  としています。

これらの値を式に代入すると、次のようになります。

$$C_{EFF} = 9.2 \mu\text{F} \times (1 - 0.15) \times (1 - 0.1) \approx 7.0 \mu\text{F}$$

降圧レギュレータの性能を保証するためには、コンデンサ動作に対する DC バイアス、温度、許容誤差の影響を各アプリケーションについて評価することが不可欠です。

図 38.DC バイアス電圧対容量

表 9.2.2  $\mu$ H の推奨インダクタ

| Vendor            | Model               | Dimensions (mm) | I <sub>SAT</sub> (mA) <sup>1</sup> | DCR (mΩ) |

|-------------------|---------------------|-----------------|------------------------------------|----------|

| Wurth Electronics | 74438335022         | 3.0 × 3.0 × 1.5 | 3500                               | 108      |

| TDK               | VLCF5020T-2R2N2R6-1 | 5.0 × 5.0 × 2.0 | 2620                               | 71       |

| Taiyo Yuden       | NP04S2B2R2N         | 5.0 × 5.0 × 2.0 | 2700                               | 42       |

| Ceilcraft         | XFLA020-222ME       | 4.0 × 4.0 × 2.1 | 3500                               | 23.5     |

<sup>1</sup> I<sub>SAT</sub> は飽和電流。

選択した出力コンデンサおよびインダクタの値でピーク to ピーク出力電圧リップルを計算するときは、次式を使用します。

$$V_{\text{RIPPLE}} = \frac{I_{\text{RIPPLE}}}{8 \times f_{\text{SW}} \times C_{\text{OUT}}} \approx \frac{V_{\text{IN}}}{(2\pi \times f_{\text{SW}})^2 \times L \times C_{\text{OUT}}}$$

次式に示すように、出力電圧リップルを低くするには、実効直列抵抗 (ESR) の値が低いコンデンサを使用すると良いでしょう。

$$ESR_{\text{COUT}} \leq \frac{V_{\text{RIPPLE}}}{I_{\text{RIPPLE}}}$$

温度や DC バイアスの影響を含め、安定性に必要な実効容量 C<sub>OUT</sub> は最小 7  $\mu$ F で最大 40  $\mu$ F です。

急速な負荷変動に対する安定性と応答を保証するためには、降圧レギュレータに 10  $\mu$ F の出力コンデンサが必要です。大きな負荷ステップを必要とするアプリケーションでは、PWM/PSM モードの開始／終了に 22  $\mu$ F の出力コンデンサを使用することができます。表 10 に推奨コンデンサのリストを示します。1 個またはすべての降圧レギュレータからプロセッサへ電源を供給するアプリケーションでは、ソフトウェアから制御しているため、動作状態を知ることができます。この状態では、動作状態に従ってプロセッサが MODE ピンを駆動できるため、出力コンデンサを 10  $\mu$ F から 4.7  $\mu$ F へ小さくすることができます。これは、レギュレータは PSM モードで動作する場合、大きな負荷変動がないと予測することができるためです。

### 入力コンデンサ

入力コンデンサの値が大きいと入力電圧リップルが小さくなり、過渡応答が向上します。入力コンデンサの最大電流は次式を使って計算します。

$$I_{\text{CIN}} \geq I_{\text{LOAD(MAX)}} \sqrt{\frac{V_{\text{OUT}}(V_{\text{IN}} - V_{\text{OUT}})}{V_{\text{IN}}}}$$

電源ノイズを小さくするため、降圧レギュレータの VINx ピンのできるだけ近くに入力コンデンサを接続してください。出力コンデンサの場合と同様、ESR が低いコンデンサの使用を推奨します。

温度や DC バイアスの影響を含め、安定性に必要な実効容量は

最小 3  $\mu$ F で最大 10  $\mu$ F です。表 11 と表 12 に推奨コンデンサのリストを示します。

表 10.22  $\mu$ F の推奨コンデンサ

| Vendor      | Type | Model               | Case Size | Voltage Rating (V) |

|-------------|------|---------------------|-----------|--------------------|

| Murata      | X5R  | GRM188R60G226MEA0D  | 0603      | 6.3                |

| TDK         | X5R  | C1608X5R0J226M080AC | 0603      | 6.3                |

| Taiyo Yuden | X5R  | LMK212BJ226MG-T     | 0805      | 10.0               |

表 11.10  $\mu$ F の推奨コンデンサ

| Vendor      | Type | Model           | Case Size | Voltage Rating (V) |

|-------------|------|-----------------|-----------|--------------------|

| Murata      | X5R  | GRM188R60J106   | 0603      | 6.3                |

| TDK         | X5R  | C1608JB0J106K   | 0603      | 6.3                |

| Taiyo Yuden | X5R  | JMK107BJ106MA-T | 0603      | 6.3                |

| Panasonic   | X5R  | ECJ1VB0J106M    | 0603      | 6.3                |

表 12.4.7  $\mu$ F の推奨コンデンサ

| Vendor      | Type | Model              | Case Size | Voltage Rating (V) |

|-------------|------|--------------------|-----------|--------------------|

| Murata      | X5R  | GRM188R60J475ME19D | 0402      | 6.3                |

| Taiyo Yuden | X5R  | JMK107BJ475        | 0402      | 6.3                |

| Panasonic   | X5R  | ECJ-0EB0J475M      | 0402      | 6.3                |

表 13.1.0  $\mu$ F の推奨コンデンサ

| Vendor      | Type | Model              | Case Size | Voltage Rating (V) |

|-------------|------|--------------------|-----------|--------------------|

| Murata      | X5R  | GRM155B30J105K     | 0402      | 6.3                |

| Murata      | X5R  | GRM155R61A105KE15D | 0402      | 10.0               |

| TDK         | X5R  | C1005JB0J105KT     | 0402      | 6.3                |

| Panasonic   | X5R  | ECJ0EB0J105K       | 0402      | 6.3                |

| Taiyo Yuden | X5R  | LMK105BJ105MV-F    | 0402      | 10.0               |

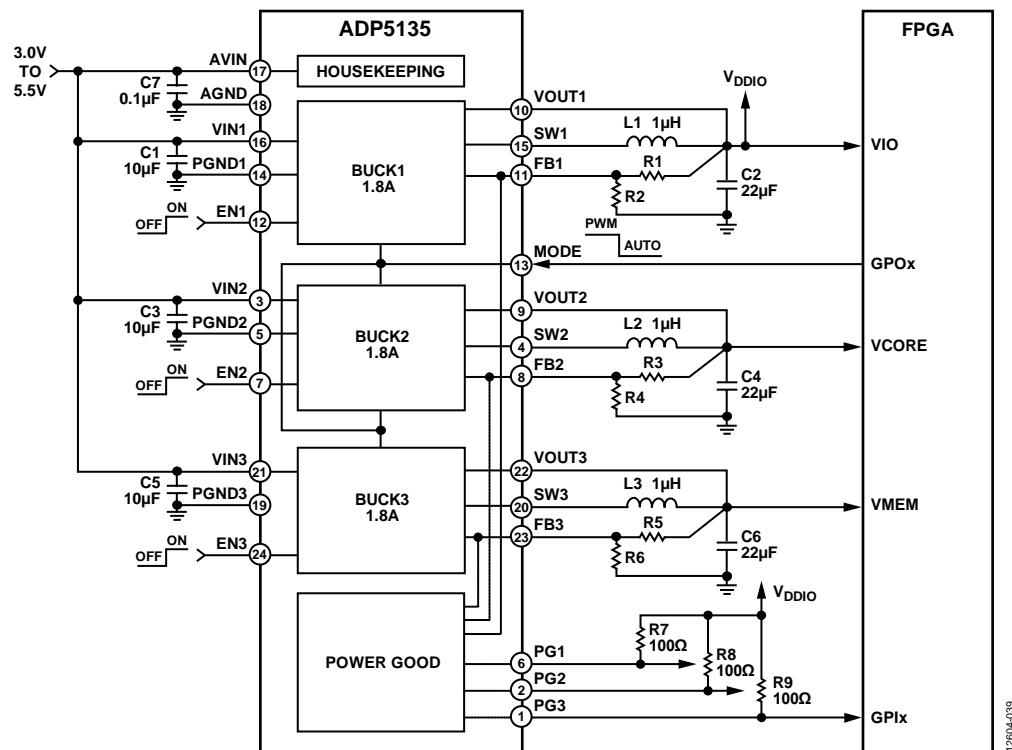

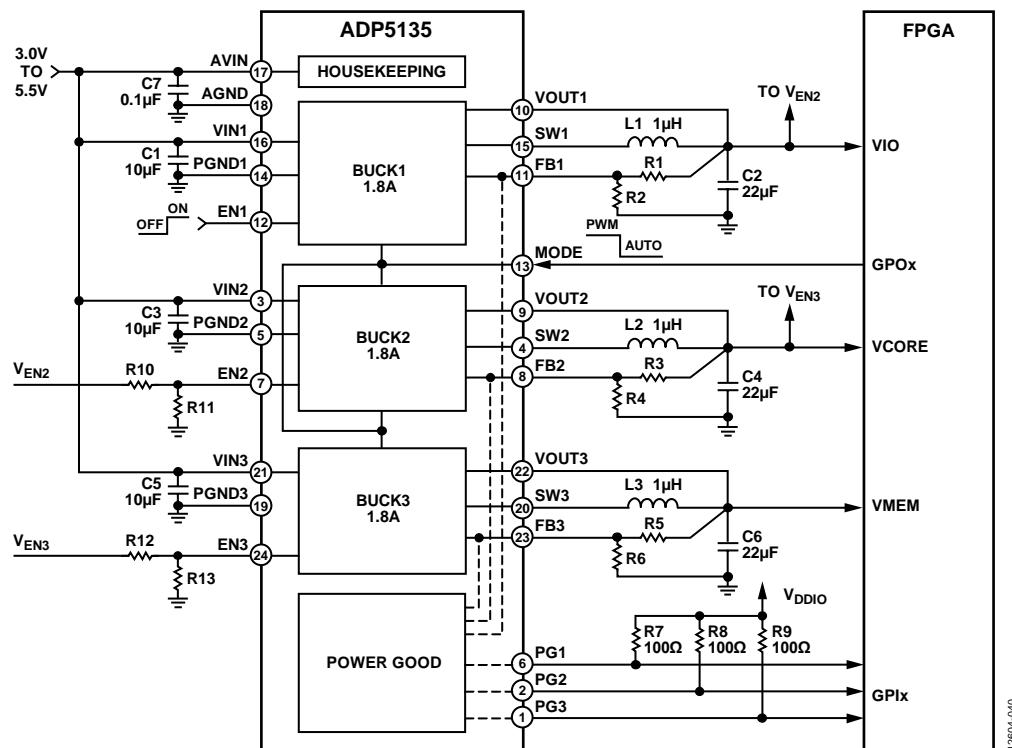

## 代表的なアプリケーション回路図

図 39.PSM/PWM 制御とパワーグッドを使用するプロセッサ・システム・パワーマネジメント

図 40.高精度イネーブル・ピン使用の ADP5135 調整可能出力電圧

図 41.高精度イネーブル・ピン使用の ADP5135 固定出力電圧

## 消費電力と熱についての考慮事項

ADP5135 は高効率の μPMU であるため、大部分の場合デバイス内で消費される電力は問題になりませんが、デバイスが高い周囲温度かつ最大負荷状態で動作する場合は、ジャンクション温度が最大許容動作温度 (125°C) に到達することがあります。

ジャンクション温度が 150°C を超えると、ADP5135 はすべてのレギュレータをオフにして、デバイスを冷却できるようにします。チップ温度が 130°C を下回ると、ADP5135 は通常動作を再開します。

このセクションでは、ADP5135 を確実に最大許容ジャンクション温度より下で動作させるために、デバイス消費電力を計算するガイドラインを示します。

ADP5135 上の各レギュレータの効率は次式で与えられます。

$$\eta = \frac{P_{OUT}}{P_{IN}} \times 100\% \quad (1)$$

ここで、

$\eta$  は効率。

$P_{OUT}$  は出力電力。

$P_{IN}$  は入力電力。

電力損失は次式で与えられます。

$$P_{LOSS} = P_{IN} - P_{OUT} \quad (2a)$$

または

$$P_{LOSS} = P_{OUT} (1 - \eta) / \eta \quad (2b)$$

消費電力は複数の方法で計算することができます。最も分りやすく実用的な方法は、入力とすべての出力での消費電力を測定することです。測定はワーストケース条件 (電圧、電流、温度) で行う必要があります。入力電力と出力電力との差がデバイスとインダクタの消費電力です。式 3 を使って、インダクタの消費電力を求め、この値から式 7 を使って ADP5135 降圧レギュレータの消費電力を計算してください。

消費電力を計算する 2 つ目の方法では、降圧レギュレータの効率カーブを使用します。降圧レギュレータの効率が既知の場合、式 2b を使って降圧レギュレータとインダクタの合計消費電力を求め、式 3 を使ってインダクタの消費電力を求め、次に式 7 を使って降圧コンバータの消費電力を計算します。3 個の降圧レギュレータの消費電力を加算して合計消費電力を求めます。

降圧レギュレータの効率カーブは代表値であるため、 $V_{IN}$ 、 $V_{OUT}$ 、 $I_{OUT}$  のすべての可能な組み合わせに対して提供されていない可能性があることに注意してください。これらの変動を考慮するため、降圧レギュレータの消費電力を計算する際に安全マージンを持たせることが必要です。

消費電力を計算する 3 つ目の方法は解析的方法であるため、式 8～式 11 で提供される降圧回路の消費電力をモデル化することが含まれます。

### 降圧レギュレータの消費電力

インダクタの消費電力はデバイスの外部であるため、チップ温度には影響を与えません。

インダクタの消費電力は次式で計算されます (コア消費電力を除く)。

$$P_L \approx I_{OUT1(RMS)}^2 \times DCR_L \quad (3)$$

ここで、

$I_{OUT1(RMS)}$  は降圧レギュレータの rms 負荷電流。

$DCR_L$  はインダクタの直列抵抗。

$$I_{OUT1(RMS)} = I_{OUT1} \times \sqrt{1 + \frac{r}{12}} \quad (4)$$

ここで、

$r$  はインダクタの正規化リップル電流。

$$r = V_{OUT1} \times (1 - D) / (I_{OUT1} \times L \times f_{sw}) \quad (5)$$

ここで、

$L$  はインダクタ値。

$f_{sw}$  はスイッチング周波数。

$D$  はデューティ・サイクル。

$$D = V_{OUT1} / V_{IN1} \quad (6)$$

降圧レギュレータの消費電力は次式で近似されます。

$$P_{LOSS} = P_{DBUCK} + P_L \quad (7)$$

ここで、

$P_{DBUCK}$  は ADP5135 降圧レギュレータの消費電力。

$P_L$  はインダクタの消費電力。

ADP5135 降圧レギュレータの消費電力  $P_{DBUCK}$  には、パワー・スイッチの導通損失、スイッチの消費電力、各チャンネルの遷移損失が含まれます。その他の損失源もありますが、これらはアプリケーションの熱的限界となっている高い出力負荷電流では一般に小さいものです。式 8 に、降圧レギュレータの消費電力を行う計算を示します。

$$P_{DBUCK} = P_{COND} + P_{SW} + P_{TRAN} \quad (8)$$

パワー・スイッチ導通損失は、内部抵抗  $RDS_{ON\_P}$  を持つ P チャンネル MOSFET パワー・スイッチと内部抵抗  $RDS_{ON\_N}$  を持つ N チャンネル MOSFET パワー・スイッチを流れる出力電流  $I_{OUT1}$  により発生します。道通損失は次式で求められます。

$$P_{COND} = [RDS_{ON\_P} \times D + RDS_{ON\_N} \times (1 - D)] \times I_{OUT1(RMS)}^2 \quad (9)$$

ここで、ジャンクション温度 25°C で、 $V_{IN1} = V_{IN2} = 3.6$  V のとき  $RDS_{ON\_P}$  は約 0.19 Ω、 $RDS_{ON\_N}$  は約 0.14 Ω です。 $V_{IN1} = V_{IN2} = 5.5$  V のときは、それぞれ 0.147 Ω と 0.122 Ω です。

スイッチング損失は、スイッチング周波数でパワー・デバイスがオン／オフになるときドライバを流れる電流に対応します。スイッチング損失は次式で与えられます。

$$P_{SW} = (C_{GATE\_P} + C_{GATE\_N}) \times V_{IN1}^2 \times f_{SW} \quad (10)$$

ここで、

$C_{GATE\_P}$  は P チャンネル MOSFET のゲート容量。

$C_{GATE\_N}$  は N チャンネル MOSFET のゲート容量。

ADP5135 の場合、合計 ( $C_{GATE\_P} + C_{GATE\_N}$ ) は約 150 pF になります。

遷移損失は、P チャンネル・パワーMOSFET が瞬時にオンまたはオフになることはできないので、SWx ノードがグラウンド付近から V<sub>OUT1</sub> 付近へ（さらに V<sub>OUT1</sub> からグラウンドへ）変化するために時間が必要です。遷移損失 (P<sub>TRAN</sub>) は次式で計算されます。

$$P_{TRAN} = V_{IN1} \times I_{OUT1} \times (t_{RISE} + t_{FALL}) \times f_{SW} \quad (11)$$

ここで、

$t_{RISE}$  と  $t_{FALL}$  はスイッチング・ノード SWx のそれぞれ立上がり時間と立下がり時間。ADP5135 の場合、SWx の立上がり時間と立下がり時間は 5 ns のオーダーです。

式 1～式 11 とそれぞれのパラメータを使ってコンバータ効率を計算する場合、これらの式はすべてのコンバータ損失を表すではないこと、および与えられたパラメータ値は代表値であることに注意してください。また、コンバータ性能は受動部品の選択とボード・レイアウトに依存するため、十分な安全余裕を計算に含める必要があります。

ADP5135 の合計消費電力は次のように簡単になります。

$$P_D = P_{DBUCK1} + P_{DBUCK2} + P_{DBUCK3} \quad (12)$$

## ジャンクション温度

ボード温度  $T_A$  が既知の場合、熱抵抗パラメータ  $\theta_{JA}$  を使ってジャンクション温度上昇を計算することができます。 $T_J$  は次式を使って  $T_A$  と  $P_D$  から計算されます。

$$T_J = T_A + (P_D \times \theta_{JA}) \quad (13)$$

LFCSP パッケージの熱抵抗値については表 6 を参照してください。考慮すべき非常に重要なファクタは、 $\theta_{JA}$  が 4 層、4 インチ × 3 インチ、2.5 オンスの銅、JEDEC 標準に準拠するプリント回路ボード(PCB)であり、実際のアプリケーションではサイズと層数が異なる可能性があります。デバイスから熱を除去するためには、使用する銅の量を増やすことが重要です。空気に露出している銅は、内部層で使用される銅より放熱が優れています。エクスポート・パッドは複数のビアを使ってグランド・プレーンにハンダ付けしてください。

ケース温度が測定可能な場合は、ジャンクション温度は次式で計算されます。

$$T_J = T_C + (P_D \times \theta_{JC}) \quad (14)$$

ここで、

$T_C$  はケース温度。

$\theta_{JC}$  はジャンクション—ケース間の熱抵抗（表 6 に示します）。

特定の周囲温度範囲に対するアプリケーションを設計する際には、すべてのチャンネルの消費電力による予想 ADP5135 消費電力 ( $P_D$ ) を式 8～式 12 を使って計算してください。この電力量計算から、ジャンクション温度  $T_J$  を式 13 により計算することができます。

コンバータの信頼度の高い動作は、ADP5135 の予測チップ・ジャンクション温度(式 14)が 125°C より低い場合にのみ実現することができます。信頼性と故障までの平均時間 (MTBF) は、ジャンクション温度の増加により大きな影響を受けます。製品の信頼性の詳細については、[www.analog.com/UG-311](http://www.analog.com/UG-311) に掲載する「[信頼性ハンドブック](#)」を参照してください。

## PCBレイアウトのガイドライン

レイアウトが悪いと、ADP5135 の性能に影響があり、EMI や電磁両立性 (EMC) の問題、グラウンド・バウンス、電圧損失などを引き起こします。また、レギュレーションや安定性に影響する場合もあります。優れたレイアウトは次の手順を使って実現できます。また、[ADP5135CP-EVALZ](#) ユーザー・ガイドも参照してください。

- 短いパターンを使用し、インダクタ、入力コンデンサ、出力コンデンサを IC の近くに配置します。これらの部品は高スイッチング周波数を伝送し、太いパターンはアンテナとして機能します。

- 出力電圧経路をインダクタや SWx ノードから一定の距離を置いてルーティングし、ノイズと電磁干渉を最小限に抑えます。

- 部品側のグラウンド・メタルのサイズを最大限大きくして、放熱性を高めます。

- VIN1、VIN2、VIN3、AVIN を一緒にして IC の近くに短いパターンで接続してください。

- 部品面のグラウンドへ接続してある複数のビアを持つグラウンド・プレーンを使って、敏感な回路ノードのノイズ干渉をさらに減らします。

- 最適性能を得るためにには、入力コンデンサをピンのすぐ近くに接続してください。すなわち、AVIN コンデンサは AVIN ピンと AGND ピンの間に、VIN1 コンデンサは VIN1 ピンと PGND1 ピンの間に、VIN2 コンデンサは VIN2 ピンと PGND2 ピンの間に、VIN3 コンデンサは VIN3 ピンと PGND3 ピンの間に、それぞれ配置してください。

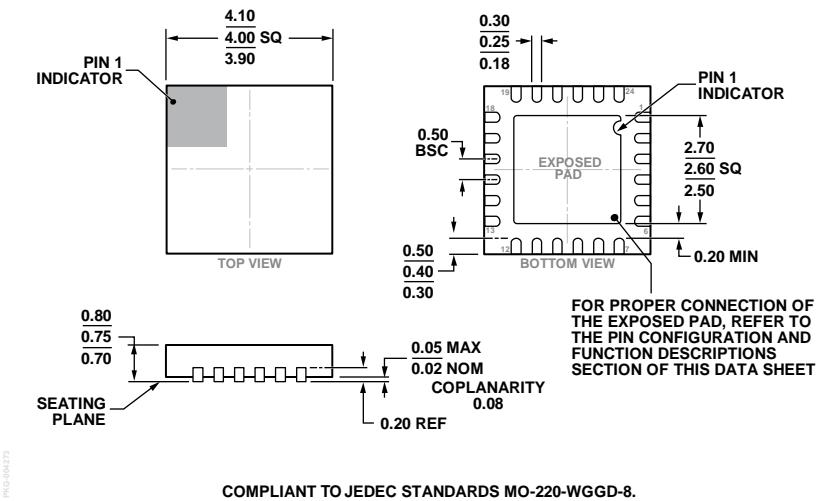

## 外形寸法

図 42. 24 ピン・リードフレーム・チップ・スケール・パッケージ[LFCSP\_WQ]

4 mm x 4 mm ボディ、極薄クワッド

(CP-24-15)

寸法: mm

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Output Voltage <sup>2</sup> | UVLO <sup>3</sup> | Active Pull-Down <sup>4</sup> | Package Description               | Package Option |

|--------------------|-------------------|-----------------------------|-------------------|-------------------------------|-----------------------------------|----------------|

| ADP5135ACPZ-R7     | -40°C to +125°C   | Adjustable                  | Mid               | Enabled on all channels       | 24-Lead LFCSP_WQ Evaluation Board | CP-24-15       |

| ADP5135CP-EVALZ    |                   |                             |                   |                               |                                   |                |

<sup>1</sup> Z = RoHS 準拠製品。

<sup>2</sup> その他のオプションについては、最寄りのアナログ・デバイセズ販売代理店へご連絡ください。その他のオプションとしては、BUCK1、BUCK2、BUCK3: 3.3 V、3.0 V、2.8 V、2.5 V、2.3 V、2.0 V、1.8 V、1.6 V、1.5 V、1.4 V、1.3 V、1.2 V、1.1 V、1.0 V、0.9 V、または調整可能があります。

<sup>3</sup> UVLO: ロー、ミドル、ハイ。記載するデフォルト・オプション以外のオプションを持つデバイスを注文する場合は、最寄りのアナログ・デバイセズ販売代理店へご連絡ください。

<sup>4</sup> BUCK1、BUCK2、BUCK3: アクティブ・プルダウン抵抗をイネーブルまたはディスエーブルに設定可能。