## データシート

**ADP5052**

### 特長

広い入力電圧範囲 : 4.5V~15V

全温度範囲にわたる出力精度 :  $\pm 1.5\%$

調整可能なスイッチング周波数 : 250kHz~1.4MHz

可変出力 / 固定出力オプション

パワー・レギュレーション

CH1, CH2 : プログラム可能な過電流保護 1.2A / 2.5A / 4A

同期整流式降圧スイッチング・レギュレータ (ローサイドの FET 外付)

CH3, CH4 : 1.2A の同期整流式降圧スイッチング・レギュレータ

CH5 : 200mA LDO レギュレータ

内部、小さな負荷用として、5.1V の LDO は常時動作

シングルの 8A 出力電源も可能 (CH1 と CH2 の並列カレント シェア動作)

0.8V スレッショルドで動作する高精度イネーブル機能

出力放電用ディスチャージスイッチ内蔵

FPWM または自動 PWM/PSM の選択機能

入力または出力の外部周波数同期機能

OVP/OCP 障害でのラッチオフ保護オプション

選択されたチャンネルでのパワーグッド・フラグ

UVLO、OCP、TSD 保護

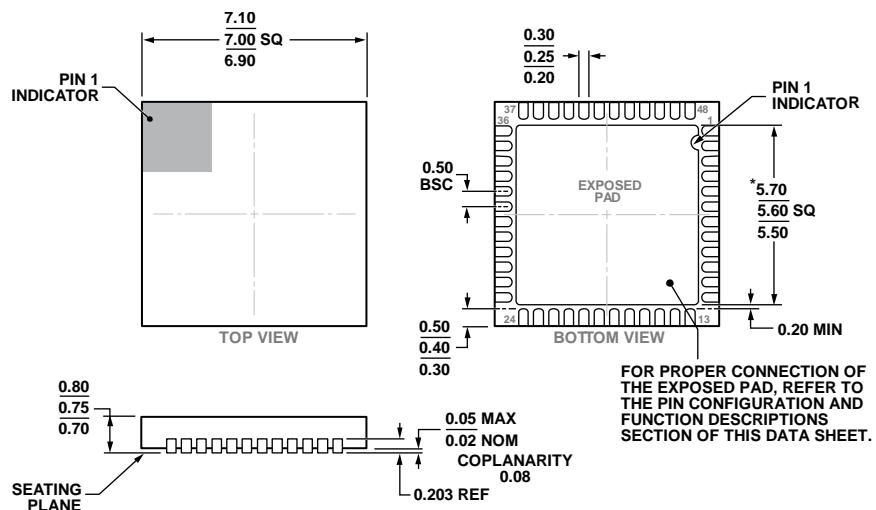

48 ピン LFCSP パッケージ(7 mm×7 mm)

-40°C~+125°C の接合温度定格

### アプリケーション

スマート・セル用基地局

FPGA およびプロセッサ・アプリケーション

警備/防犯装置

医療用アプリケーション

### 概要

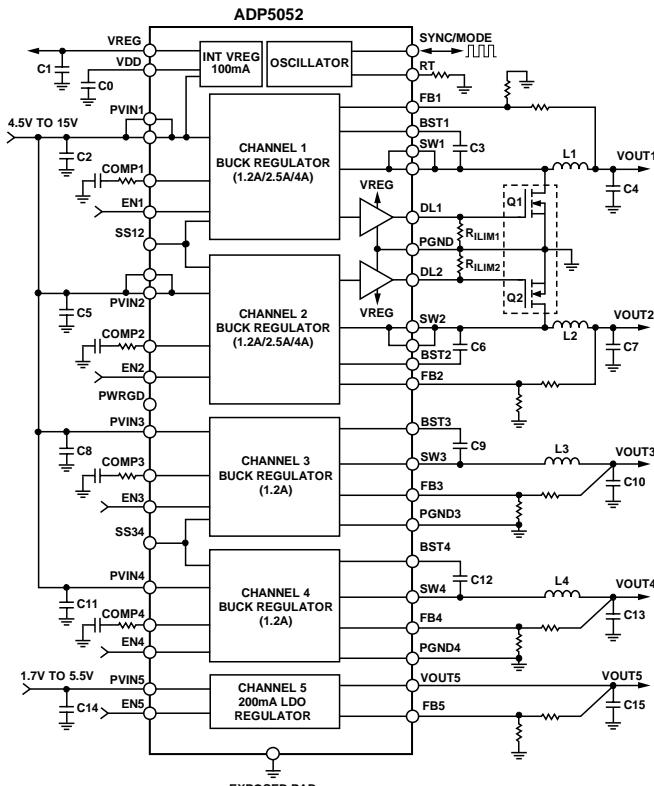

ADP5052 は、4つの高性能降圧スイッチング・レギュレータと 200mA のロー・ドロップアウト (LDO) レギュレータを、48 ピン LFCSP パッケージに収めており、高性能および省ボード・スペースの要求を満たします。このデバイスは、最大 15V までの高い入力電圧を、前段レギュレータ無しで、直接接続することができます。

チャンネル 1 とチャンネル 2 は、ハイサイド・パワー MOSFET とローサイド MOSFET ドライバを内蔵しています。効率を最適化したソリューションを提供し、1.2A、2.5A もしくは 4A のプログラム可能な出力過電流保護を提供するためには、外部 NFET を接続することができます。また、チャンネル 1 とチャンネル 2 を並列接続すれば、カレントシェア機能によりシングル出力で最大 8A までの電流供給ができます。

チャンネル 3 とチャンネル 4 は、1.2A の出力電流を供給する、ハイサイドとローサイドの両方の MOSFET を内蔵しています。

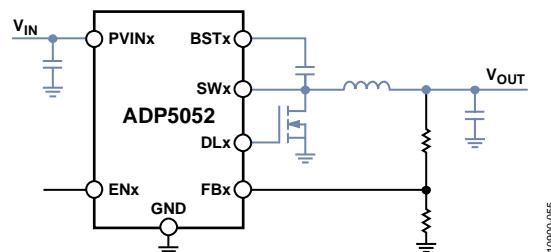

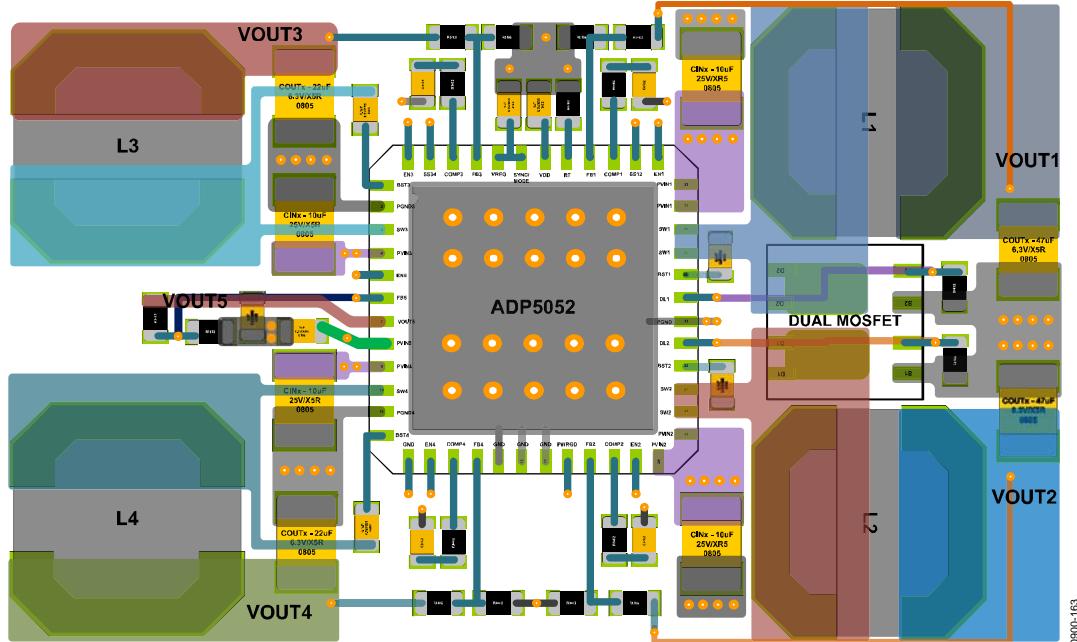

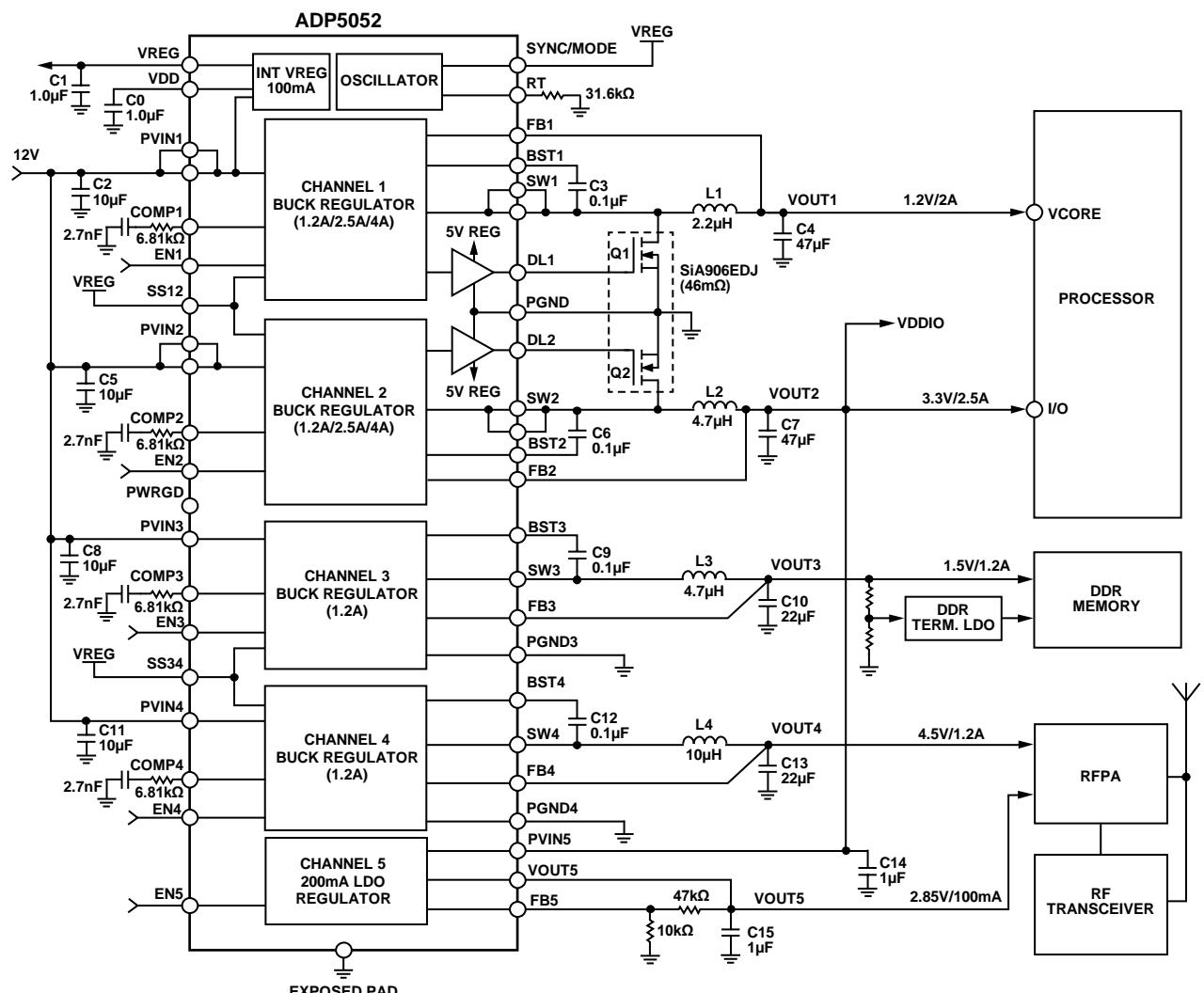

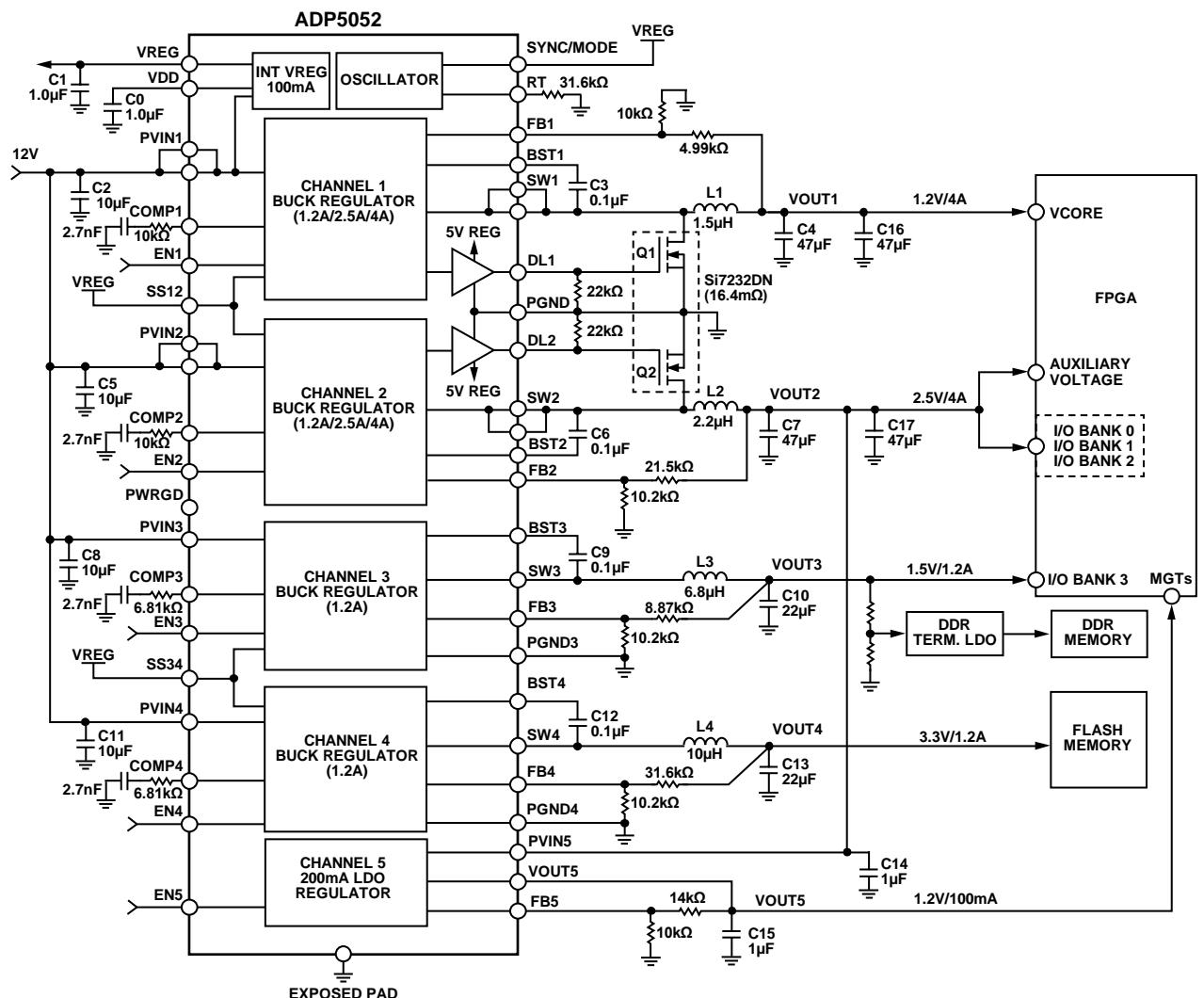

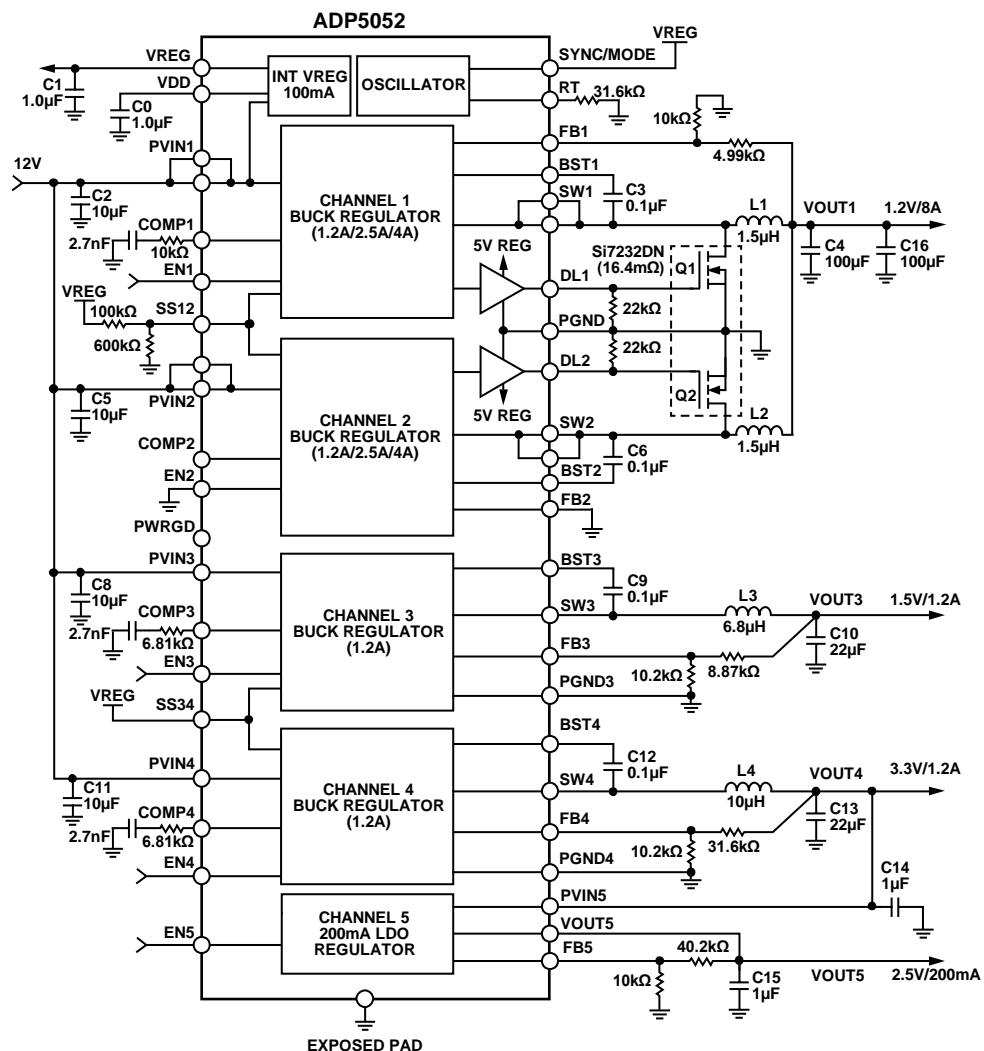

### 代表的なアプリケーション回路

図 1.

ADP5052 のスイッチング周波数は、デバイス自身でプログラムするか、もしくは外部クロックと同期させることも可能です。ADP5052 は、パワー・アップ・シーケンス、または UVLO スレッショルド調整を容易にするため、各チャンネルに高精度イネーブル・ピンを備えています。

ADP5052 に、内蔵されている汎用の LDO は、静止時消費電流が小さく、ロー・ドロップアウト電圧で、最大 200mA までの出力電流を供給できます。

表 1. ファミリー・モデル

| モデル名    | チャンネル数         | I <sup>2</sup> C | パッケージ       |

|---------|----------------|------------------|-------------|

| ADP5050 | 降圧 : 4、LDO : 1 | あり               | 48 ピン LFCSP |

| ADP5051 | 降圧:4、監視回路      | あり               | 48 ピン LFCSP |

| ADP5052 | 降圧 : 4、LDO : 1 | なし               | 48 ピン LFCSP |

| ADP5053 | 降圧:4、監視回路      | なし               | 48 ピン LFCSP |

## 目次

|                                        |    |

|----------------------------------------|----|

| 特長                                     | 1  |

| アプリケーション                               | 1  |

| 代表的なアプリケーション回路                         | 1  |

| 概要                                     | 1  |

| 改訂履歴                                   | 2  |

| 詳細な機能ブロック図                             | 3  |

| 仕様                                     | 4  |

| 降圧スイッチング・レギュレータの仕様                     | 5  |

| LDO レギュレータの仕様                          | 7  |

| 絶対最大定格                                 | 8  |

| 熱抵抗                                    | 8  |

| ESD の注意                                | 8  |

| ピン配置およびピン機能説明                          | 9  |

| 代表的な性能特性                               | 11 |

| 動作原理                                   | 17 |

| 降圧スイッチング・レギュレータの動作モード                  | 17 |

| PWM モード                                | 17 |

| PSM モード                                | 17 |

| 強制 PWM、自動 PWM/PSM モード                  | 17 |

| 調整可能および固定出力電圧                          | 17 |

| 内部レギュレータ (VREG と VDD)                  | 17 |

| 異なる電圧入力アプリケーション対応                      | 18 |

| ローサイド・デバイスの選択                          | 18 |

| ブートストラップ回路                             | 18 |

| アクティブ出力放電スイッチ                          | 18 |

| 高精度イネーブル                               | 18 |

| 発振器                                    | 18 |

| 位相シフト                                  | 19 |

| 同期入力/出力                                | 19 |

| ソフト・スタート                               | 19 |

| 並列動作                                   | 20 |

| 出力が充電されていた場合のスタートアップ                   | 20 |

| 電流制限保護機能                               | 20 |

| 周波数フォールドバック                            | 21 |

| 最大デューティー・サイクル下のパルス・スキップ・モード            | 21 |

| 瞬断による過負荷保護                             | 21 |

| ラッチオフによる保護                             | 21 |

| 短絡ラッチオフ・モード                            | 21 |

| 過電圧ラッチオフ・モード                           | 21 |

| 低電圧ロックアウト (UVLO)                       | 22 |

| 改訂履歴                                   |    |

| 2/14—Rev. 0 to Rev. A                  |    |

| Added Table 1; Renumbered Sequentially | 1  |

| Changes to Figure 13 and Figure 14     | 12 |

| Changes to Table 11                    | 24 |

| Updated Outline Dimensions             | 38 |

|                           |    |

|---------------------------|----|

| パワーグッド機能                  | 22 |

| サーマル・シャットダウン              | 22 |

| LDO レギュレータ                | 22 |

| アプリケーション情報                | 23 |

| ADIsimPower デザイン・ツール      | 23 |

| 可変出力電圧のプログラミング            | 23 |

| 電圧変換の制限                   | 23 |

| 電流制限の設定                   | 23 |

| ソフト・スタートの設定               | 24 |

| インダクタの選択                  | 24 |

| 出力コンデンサの選択                | 24 |

| 入力コンデンサの選択                | 25 |

| ローサイド・パワー・デバイスの選択         | 25 |

| UVLO 入力のプログラミング           | 25 |

| 補償用部品値の計算                 | 26 |

| 消費電力                      | 26 |

| 降圧スイッチング・レギュレータの消費電力      | 26 |

| 電力スイッチ導通損失 ( $P_{COND}$ ) | 26 |

| スイッチング損失 ( $P_{SW}$ )     | 26 |

| 遷移損失 ( $P_{TRAN}$ )       | 27 |

| サーマル・シャットダウン              | 27 |

| LDO レギュレータの消費電力           | 27 |

| ジャンクション温度                 | 27 |

| 設計例                       | 28 |

| スイッチング周波数の設定              | 28 |

| 出力電圧の設定                   | 28 |

| 電流制限値の設定                  | 28 |

| インダクタの選択                  | 28 |

| 出力コンデンサの選択                | 29 |

| ローサイド MOSFET の選択          | 29 |

| 補償ネットワークの設計               | 29 |

| ソフト・スタート時間の設定             | 29 |

| 入力コンデンサの選択                | 29 |

| 推奨される外付け部品                | 30 |

| 推奨回路基板のレイアウト              | 31 |

| 代表的なアプリケーション回路            | 32 |

| 工場でのプログラム可能なオプション         | 35 |

| 工場出荷時のデフォルト・オプション         | 37 |

| 外形寸法                      | 38 |

| オーダー・ガイド                  | 38 |

5/13—Revision 0:Initial Version

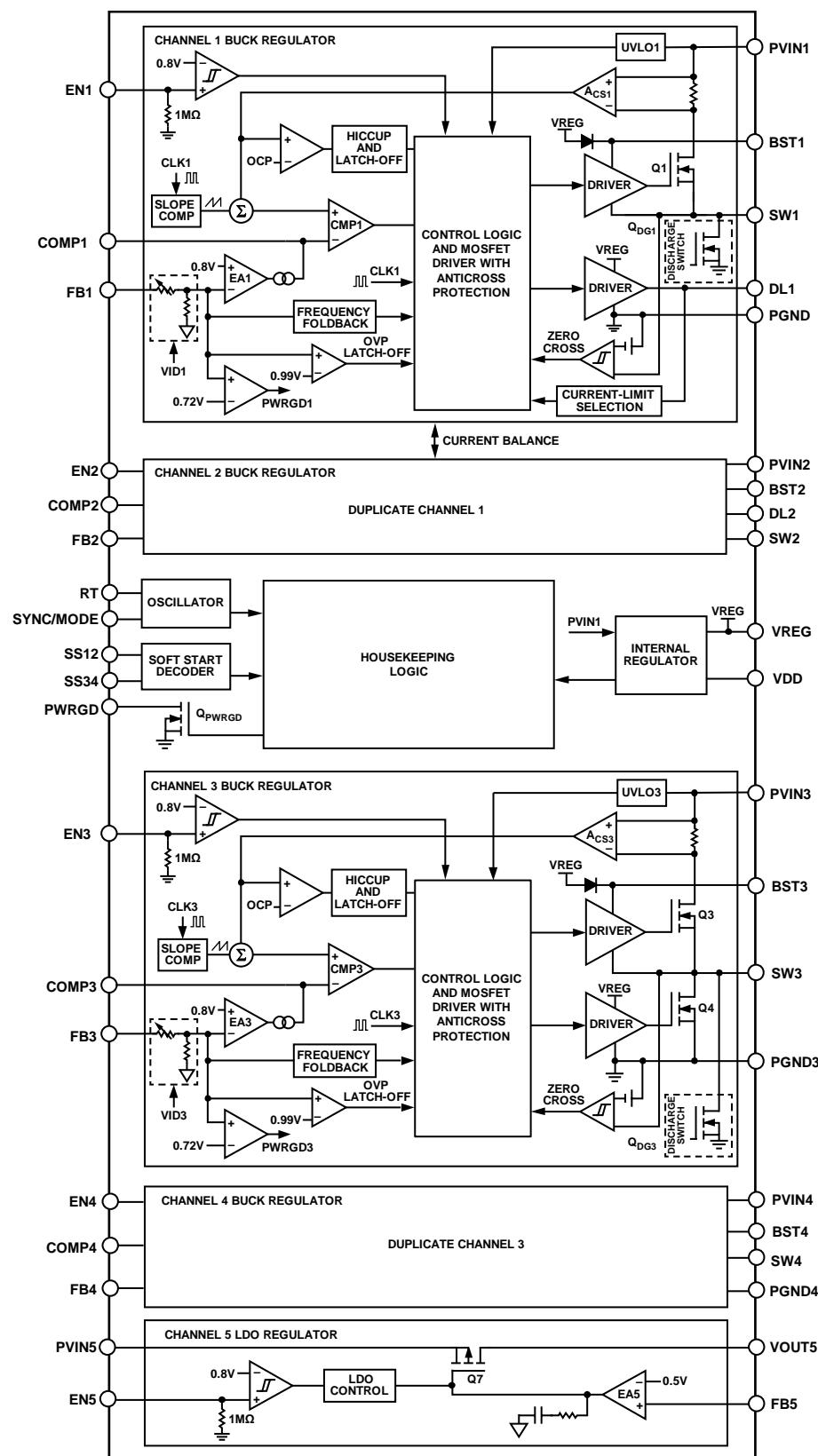

## 詳細な機能ブロック図

10900-202

図2.

## 仕様

最小もしくは最大の特性に関しては、 $V_{IN} = 12\text{ V}$ 、 $V_{VREG} = 5.1\text{ V}$ 、 $T_J = -40^\circ\text{C}$ から $+125^\circ\text{C}$ 。他は特に断りのない限り、 $T_A = 25^\circ\text{C}$ における代表特性。

表 2.

| Parameter                            | Symbol                                     | Min   | Typ        | Max        | Unit                | Test Conditions/Comments                            |

|--------------------------------------|--------------------------------------------|-------|------------|------------|---------------------|-----------------------------------------------------|

| INPUT SUPPLY VOLTAGE RANGE           | $V_{IN}$                                   | 4.5   |            | 15.0       | V                   | PVIN1, PVIN2, PVIN3, PVIN4 pins                     |

| QUIESCENT CURRENT                    |                                            |       |            |            |                     | PVIN1, PVIN2, PVIN3, PVIN4 pins                     |

| Operating Quiescent Current          | $I_{Q(4-BUCKS)}$<br>$I_{SHDN(4BUCKS+LDO)}$ |       | 4.8<br>25  | 6.25<br>65 | mA<br>$\mu\text{A}$ | No switching, all ENx pins high<br>All ENx pins low |

| UNDERVOLTAGE LOCKOUT                 | UVLO                                       |       |            |            |                     | PVIN1, PVIN2, PVIN3, PVIN4 pins                     |

| Rising Threshold                     | $V_{UVLO-RISING}$                          |       | 4.2        | 4.36       | V                   |                                                     |

| Falling Threshold                    | $V_{UVLO-FALLING}$                         | 3.6   | 3.78       |            | V                   |                                                     |

| Hysteresis                           | $V_{HYS}$                                  |       | 0.42       |            | V                   |                                                     |

| OSCILLATOR CIRCUIT                   |                                            |       |            |            |                     |                                                     |

| Switching Frequency                  | $f_{SW}$                                   | 700   | 740        | 780        | kHz                 | RT = 25.5 k $\Omega$                                |

| Switching Frequency Range            |                                            | 250   |            | 1400       | kHz                 |                                                     |

| SYNC 入力                              |                                            |       |            |            |                     |                                                     |

| Input Clock Range                    | $f_{SYNC}$                                 | 250   |            | 1400       | kHz                 |                                                     |

| Input Clock Pulse Width              |                                            |       |            |            |                     |                                                     |

| Minimum On Time                      | $t_{SYNC\_MIN\_ON}$                        | 100   |            |            | ns                  |                                                     |

| Minimum Off Time                     | $t_{SYNC\_MIN\_OFF}$                       | 100   |            |            | ns                  |                                                     |

| Input Clock High Voltage             | $V_{H(SYNC)}$                              | 1.3   |            |            | V                   |                                                     |

| Input Clock Low Voltage              | $V_{L(SYNC)}$                              |       |            | 0.4        | V                   |                                                     |

| VO Output                            |                                            |       |            |            |                     |                                                     |

| Clock Frequency                      | $f_{CLK}$                                  |       | $f_{SW}$   |            | kHz                 |                                                     |

| Positive Pulse Duty Cycle            | $t_{CLK\_PULSE\_DUTY}$                     |       | 50         |            | %                   |                                                     |

| Rise or Fall Time                    | $t_{CLK\_RISE\_FALL}$                      |       | 10         |            | ns                  |                                                     |

| High Level Voltage                   | $V_{H(SYNC\_OUT)}$                         |       | $V_{VREG}$ |            | V                   |                                                     |

| PRECISION ENABLING                   |                                            |       |            |            |                     | EN1, EN2, EN3, EN4, EN5 pins                        |

| High Level Threshold                 | $V_{TH\_H(EN)}$                            |       | 0.806      | 0.832      | V                   |                                                     |

| Low Level Threshold                  | $V_{TH\_L(EN)}$                            | 0.688 | 0.725      |            | V                   |                                                     |

| Pull-Down Resistor                   | $R_{PULL-DOWN(EN)}$                        |       | 1.0        |            | M $\Omega$          |                                                     |

| POWER GOOD                           |                                            |       |            |            |                     |                                                     |

| Internal Power-Good Rising Threshold | $V_{PWRGD(RISE)}$                          | 86.3  | 90.5       | 95         | %                   |                                                     |

| Internal Power-Good Hysteresis       | $V_{PWRGD(HYS)}$                           |       | 3.3        |            | %                   |                                                     |

| Internal Power-Good Falling Delay    | $t_{PWRGD\_FALL}$                          |       | 50         |            | $\mu\text{s}$       |                                                     |

| Rising Delay for PWRGD Pin           | $t_{PWRGD\_PIN\_RISE}$                     |       | 1          |            | ms                  |                                                     |

| Leakage Current for PWRGD Pin        | $I_{PWRGD\_LEAKAGE}$                       |       | 0.1        | 1          | $\mu\text{A}$       |                                                     |

| Output Low Voltage for PWRGD Pin     | $V_{PWRGD\_LOW}$                           |       | 50         | 100        | mV                  | $I_{PWRGD} = 1\text{ mA}$                           |

| INTERNAL REGULATORS                  |                                            |       |            |            |                     |                                                     |

| VDD Output Voltage                   | $V_{VDD}$                                  | 3.2   | 3.305      | 3.4        | V                   | $I_{VDD} = 10\text{ mA}$                            |

| VDD Current Limit                    | $I_{LIM\_VDD}$                             | 20    | 51         | 80         | mA                  |                                                     |

| VREG Output Voltage                  | $V_{VREG}$                                 | 4.9   | 5.1        | 5.3        | V                   | $I_{VREG} = 50\text{ mA}$                           |

| VREG Output Voltage                  | $V_{DROPOUT}$                              |       | 225        |            | mV                  |                                                     |

| VREG Current Limit                   | $I_{LIM\_VREG}$                            | 50    | 95         | 140        | mA                  |                                                     |

| THERMAL SHUTDOWN                     |                                            |       |            |            |                     |                                                     |

| Thermal Shutdown Threshold           | $T_{SHDN}$                                 |       | 150        |            | $^\circ\text{C}$    |                                                     |

| Thermal Shutdown Hysteresis          | $T_{HYS}$                                  |       | 15         |            | $^\circ\text{C}$    |                                                     |

## 降圧スイッチング・レギュレータの仕様

最小もしくは最大の特性に関しては、 $V_{IN} = 12$  V、 $V_{VREG} = 5.1$  V、すべてのチャンネルの  $f_{SW} = 600$  kHz、 $T_J = -40$  °C から +125 °C。他は特に断りのない限り、 $T_A = 25$  °C における代表特性。

表 3.

| Parameter                                | Symbol             | Min   | Typ                 | Max   | Unit             | Test Conditions/Comments                                 |

|------------------------------------------|--------------------|-------|---------------------|-------|------------------|----------------------------------------------------------|

| CHANNEL 1 SYNC BUCK REGULATOR            |                    |       |                     |       |                  |                                                          |

| FB1 Pin                                  |                    |       |                     |       |                  |                                                          |

| Fixed Output Options                     | $V_{OUT1}$         | 0.85  |                     | 1.60  | V                | Fuse trim                                                |

| Adjustable Feedback Voltage              | $V_{FB1}$          |       | 0.800               |       | V                |                                                          |

| Feedback Voltage Accuracy                | $V_{FB1(DEFAULT)}$ | -0.55 |                     | +0.55 | %                | $T_J = 25$ °C                                            |

|                                          |                    | -1.25 |                     | +1.0  | %                | $0^{\circ}\text{C} \leq T_J \leq 85^{\circ}\text{C}$     |

|                                          |                    | -1.5  |                     | +1.5  | %                | $-40^{\circ}\text{C} \leq T_J \leq +125^{\circ}\text{C}$ |

| Feedback Bias Current                    | $I_{FB1}$          |       |                     | 0.1   | $\mu\text{A}$    | Adjustable voltage                                       |

| SW1 Pin                                  |                    |       |                     |       |                  |                                                          |

| High-Side Power FET On Resistance        | $R_{DSON(1H)}$     |       | 100                 |       | $\text{m}\Omega$ | Pin-to-pin measurement                                   |

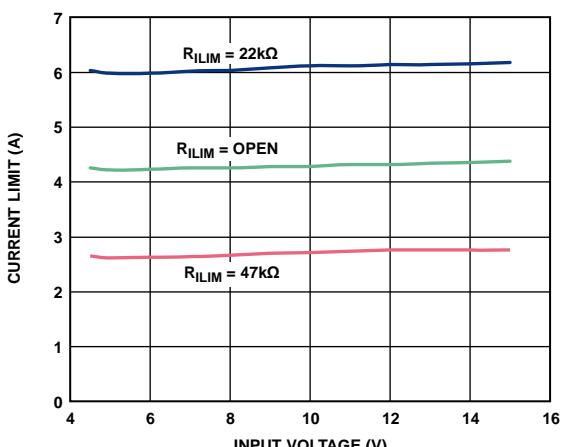

| Current-Limit Threshold                  | $I_{TH(ILIM1)}$    | 3.50  | 4.4                 | 5.28  | A                | $R_{ILIM1} = \text{floating}$                            |

|                                          |                    | 1.91  | 2.63                | 3.08  | A                | $R_{ILIM1} = 47$ k $\Omega$                              |

|                                          |                    | 4.95  | 6.44                | 7.48  | A                | $R_{ILIM1} = 22$ k $\Omega$                              |

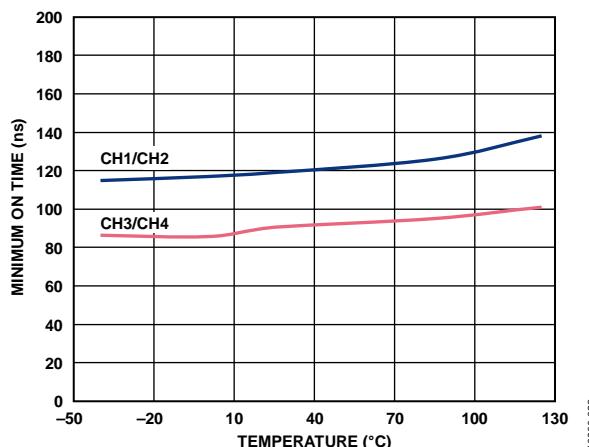

| Minimum On Time                          | $t_{MIN\_ON1}$     |       | 117                 | 155   | ns               | $f_{SW} = 250$ kHz to 1.4 MHz                            |

| Minimum Off Time                         | $t_{MIN\_OFF1}$    |       | 1/9 $\times t_{SW}$ |       | ns               | $f_{SW} = 250$ kHz to 1.4 MHz                            |

| Low-Side Driver, DL1 Pin                 |                    |       |                     |       |                  |                                                          |

| Rising Time                              | $t_{RISING1}$      |       | 20                  |       | ns               | $C_{ISS} = 1.2$ nF                                       |

| Falling Time                             | $t_{FALLING1}$     |       | 3.4                 |       | ns               | $C_{ISS} = 1.2$ nF                                       |

| Sourcing Resistor                        | $t_{SOURCING1}$    |       | 10                  |       | $\Omega$         |                                                          |

| Sinking Resistor                         | $t_{SINKING1}$     |       | 0.95                |       | $\Omega$         |                                                          |

| Error Amplifier (EA), COMP1 Pin          |                    |       |                     |       |                  |                                                          |

| EA Transconductance                      | $g_m1$             | 310   | 470                 | 620   | $\mu\text{s}$    |                                                          |

| Soft Start                               |                    |       |                     |       |                  |                                                          |

| Soft Start Time                          | $t_{SS1}$          |       | 2.0                 |       | ms               | SS12 connected to VREG                                   |

| Programmable Soft Start Range            |                    | 2.0   |                     | 8.0   | ms               |                                                          |

| Hiccup Time                              | $t_{HICCUP1}$      |       | 7 $\times t_{SS1}$  |       | ms               |                                                          |

| $C_{OUT}$ Discharge Switch On Resistance | $R_{DIS1}$         |       | 250                 |       | $\Omega$         |                                                          |

| CHANNEL 2 SYNC BUCK REGULATOR            |                    |       |                     |       |                  |                                                          |

| FB2 Pin                                  |                    |       |                     |       |                  |                                                          |

| Fixed Output Options                     | $V_{OUT2}$         | 3.3   |                     | 5.0   | V                | Fuse trim                                                |

| Adjustable Feedback Voltage              | $V_{FB2}$          |       | 0.800               |       | V                |                                                          |

| Feedback Voltage Accuracy                | $V_{FB2(DEFAULT)}$ | -0.55 |                     | +0.55 | %                | $T_J = 25$ °C                                            |

|                                          |                    | -1.25 |                     | +1.0  | %                | $0^{\circ}\text{C} \leq T_J \leq 85^{\circ}\text{C}$     |

|                                          |                    | -1.5  |                     | +1.5  | %                | $-40^{\circ}\text{C} \leq T_J \leq +125^{\circ}\text{C}$ |

| Feedback Bias Current                    | $I_{FB2}$          |       |                     | 0.1   | $\mu\text{A}$    | Adjustable voltage                                       |

| SW2 Pin                                  |                    |       |                     |       |                  |                                                          |

| High-Side Power FET On Resistance        | $R_{DSON(2H)}$     |       | 110                 |       | $\text{m}\Omega$ | Pin-to-pin measurement                                   |

| Current-Limit Threshold                  | $I_{TH(ILIM2)}$    | 3.50  | 4.4                 | 5.28  | A                | $R_{ILIM2} = \text{floating}$                            |

|                                          |                    | 1.91  | 2.63                | 3.08  | A                | $R_{ILIM2} = 47$ k $\Omega$                              |

|                                          |                    | 4.95  | 6.44                | 7.48  | A                | $R_{ILIM2} = 22$ k $\Omega$                              |

| Minimum On Time                          | $t_{MIN\_ON2}$     |       | 117                 | 155   | ns               | $f_{SW} = 250$ kHz to 1.4 MHz                            |

| Minimum Off Time                         | $t_{MIN\_OFF2}$    |       | 1/9 $\times t_{SW}$ |       | ns               | $f_{SW} = 250$ kHz to 1.4 MHz                            |

| Low-Side Driver, DL2 Pin                 |                    |       |                     |       |                  |                                                          |

| Rising Time                              | $t_{RISING2}$      |       | 20                  |       | ns               | $C_{ISS} = 1.2$ nF                                       |

| Falling Time                             | $t_{FALLING2}$     |       | 3.4                 |       | ns               | $C_{ISS} = 1.2$ nF                                       |

| Sourcing Resistor                        | $t_{SOURCING2}$    |       | 10                  |       | $\Omega$         |                                                          |

| Sinking Resistor                         | $t_{SINKING2}$     |       | 0.95                |       | $\Omega$         |                                                          |

| Error Amplifier (EA), COM2 Pin           |                    |       |                     |       |                  |                                                          |

| Parameter                                | Symbol             | Min   | Typ                 | Max   | Unit | Test Conditions/Comments                             |

|------------------------------------------|--------------------|-------|---------------------|-------|------|------------------------------------------------------|

| EA Transconductance                      | $g_{m2}$           | 310   | 470                 | 620   | μs   |                                                      |

| Soft Start                               |                    |       |                     |       |      |                                                      |

| Soft Start Time                          | $t_{SS2}$          |       | 2.0                 |       | ms   |                                                      |

| Programmable Soft Start Range            |                    | 2.0   |                     | 8.0   | ms   | SS12 connected to VREG                               |

| Hiccup Time                              | $t_{HICCUP2}$      |       | $7 \times t_{SS1}$  |       | ms   |                                                      |

| $C_{OUT}$ Discharge Switch On Resistance | $R_{DIS2}$         |       | 250                 |       | Ω    |                                                      |

| CHANNEL 3 SYNC BUCK REGULATOR            |                    |       |                     |       |      |                                                      |

| FB3 Pin                                  |                    |       |                     |       |      |                                                      |

| Fixed Output Options                     | $V_{OUT3}$         | 1.20  |                     | 1.80  | V    | Fuse trim                                            |

| Adjustable Feedback Voltage              | $V_{FB3}$          |       | 0.800               |       | V    |                                                      |

| Feedback Voltage Accuracy                | $V_{FB3(DEFAULT)}$ | -0.55 |                     | +0.55 | %    | $T_J = 25^\circ\text{C}$                             |

|                                          |                    | -1.25 |                     | +1.0  | %    | $0^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$     |

|                                          |                    | -1.5  |                     | +1.5  | %    | $-40^\circ\text{C} \leq T_J \leq +125^\circ\text{C}$ |

| Feedback Bias Current                    | $I_{FB3}$          |       |                     | 0.1   | μA   | Adjustable voltage                                   |

| SW3 Pin                                  |                    |       |                     |       |      |                                                      |

| High-Side Power FET On Resistance        | $R_{DSON(3H)}$     |       | 225                 |       | mΩ   | Pin-to-pin measurement                               |

| Low-Side Power FET On Resistance         | $R_{DSON(3L)}$     |       | 150                 |       | mΩ   | Pin-to-pin measurement                               |

| Current-Limit Threshold                  | $I_{TH(ILIM3)}$    | 1.7   | 2.2                 | 2.55  | A    |                                                      |

| Minimum On Time                          | $t_{MIN\_ON3}$     |       | 90                  | 120   | ns   | $f_{SW} = 250 \text{ kHz to } 1.4 \text{ MHz}$       |

| Minimum Off Time                         | $t_{MIN\_OFF3}$    |       | $1/9 \times t_{SW}$ |       | ns   | $f_{SW} = 250 \text{ kHz to } 1.4 \text{ MHz}$       |

| Error Amplifier (EA), COM3 Pin           |                    |       |                     |       |      |                                                      |

| EA Transconductance                      | $g_{m3}$           | 310   | 470                 | 620   | μs   |                                                      |

| Soft Start                               |                    |       |                     |       |      |                                                      |

| Soft Start Time                          | $t_{SS3}$          |       | 2.0                 |       | ms   |                                                      |

| Programmable Soft Start Range            |                    | 2.0   |                     | 8.0   | ms   | SS34 connected to VREG                               |

| Hiccup Time                              | $t_{HICCUP3}$      |       | $7 \times t_{SS1}$  |       | ms   |                                                      |

| $C_{OUT}$ Discharge Switch On Resistance | $R_{DIS3}$         |       | 250                 |       | Ω    |                                                      |

| CHANNEL 4 SYNC BUCK REGULATOR            |                    |       |                     |       |      |                                                      |

| FB4 Pin                                  |                    |       |                     |       |      |                                                      |

| Fixed Output Options                     | $V_{OUT4}$         | 2.5   |                     | 5.5   | V    | Fuse trim                                            |

| Adjustable Feedback Voltage              | $V_{FB4}$          |       | 0.800               |       | V    |                                                      |

| Feedback Voltage Accuracy                | $V_{FB4(DEFAULT)}$ | -0.55 |                     | +0.55 | %    | $T_J = 25^\circ\text{C}$                             |

|                                          |                    | -1.25 |                     | +1.0  | %    | $0^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$     |

|                                          |                    | -1.5  |                     | +1.5  | %    | $-40^\circ\text{C} \leq T_J \leq +125^\circ\text{C}$ |

| Feedback Bias Current                    | $I_{FB4}$          |       |                     | 0.1   | μA   |                                                      |

| SW4 Pin                                  |                    |       |                     |       |      |                                                      |

| High-Side Power FET On Resistance        | $R_{DSON(4H)}$     |       | 225                 |       | mΩ   | Pin-to-pin measurement                               |

| Low-Side Power FET On Resistance         | $R_{DSON(4L)}$     |       | 150                 |       | mΩ   | Pin-to-pin measurement                               |

| Current-Limit Threshold                  | $I_{TH(ILIM4)}$    | 1.7   | 2.2                 | 2.55  | A    |                                                      |

| Minimum On Time                          | $t_{MIN\_ON4}$     |       | 90                  | 120   | ns   | $f_{SW} = 250 \text{ kHz to } 1.4 \text{ MHz}$       |

| Minimum Off Time                         | $t_{MIN\_OFF4}$    |       | $1/9 \times t_{SW}$ |       | ns   | $f_{SW} = 250 \text{ kHz to } 1.4 \text{ MHz}$       |

| Error Amplifier (EA), COM4 Pin           |                    |       |                     |       |      |                                                      |

| EA Transconductance                      | $g_{m3}$           | 310   | 470                 | 620   | μs   |                                                      |

| Soft Start                               |                    |       |                     |       |      |                                                      |

| Soft Start Time                          | $t_{SS4}$          |       | 2.0                 |       | ms   |                                                      |

| Programmable Soft Start Range            |                    | 2.0   |                     | 8.0   | ms   | SS34 connected to VREG                               |

| Hiccup Time                              | $t_{HICCUP4}$      |       | $7 \times t_{SS4}$  |       | ms   |                                                      |

| $C_{OUT}$ Discharge Switch On Resistance | $R_{DIS4}$         |       | 250                 |       | Ω    |                                                      |

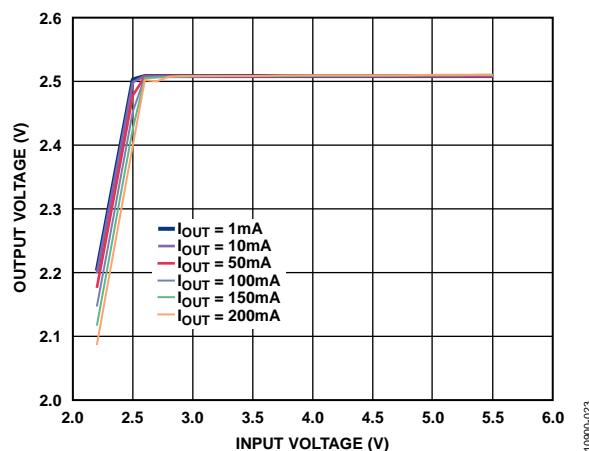

## LDO レギュレータの仕様

最小もしくは最大の特性に関しては、 $V_{IN5} = (V_{OUT5} + 0.5 \text{ V})$  または  $1.7 \text{ V}$  (どちらか大きい方) から  $5.5 \text{ V}$  ;  $C_{IN} = C_{OUT} = 1 \mu\text{F}$  ;  $T_J = -40^\circ\text{C}$  から  $+125^\circ\text{C}$ 。他は特に断りのない限り、 $T_A = 25^\circ\text{C}$  における代表特性。

表 4.

| Parameter                      | Min  | Typ              | Max               | Unit              | Test Conditions/Comments                                                                                              |

|--------------------------------|------|------------------|-------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------|

| INPUT SUPPLY VOLTAGE RANGE     | 1.7  |                  | 5.5               | V                 | $V_{VIN5}$ pin                                                                                                        |

| OPERATIONAL SUPPLY CURRENT     |      |                  |                   |                   |                                                                                                                       |

| Bias Current for LDO Regulator |      | 30<br>60<br>145  | 130<br>170<br>320 | $\mu\text{A}$     | $I_{OUT5} = 200 \mu\text{A}$<br>$I_{OUT5} = 10 \text{ mA}$<br>$I_{OUT5} = 200 \text{ mA}$                             |

| VOLTAGE FEEDBACK (FB5 PIN)     |      | 0.500            |                   | V                 |                                                                                                                       |

| Adjustable Feedback Voltage    | -1.0 |                  | +1.0              | %                 | $T_J = 25^\circ\text{C}$                                                                                              |

| Feedback Voltage Accuracy      | -1.6 |                  | +1.6              | %                 | $0^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$                                                                      |

|                                | -2.0 |                  | +2.0              | %                 | $-40^\circ\text{C} \leq T_J \leq +125^\circ\text{C}$                                                                  |

| DROPOUT VOLTAGE                |      | 80<br>100<br>180 |                   | $\text{mV}$       | $I_{OUT5} = 200 \text{ mA}$<br>$V_{OUT5} = 3.3 \text{ V}$<br>$V_{OUT5} = 2.5 \text{ V}$<br>$V_{OUT5} = 1.5 \text{ V}$ |

| CURRENT-LIMIT THRESHOLD        | 250  | 510              |                   | mA                | Specified from the output voltage drop to 90% of the specified typical value                                          |

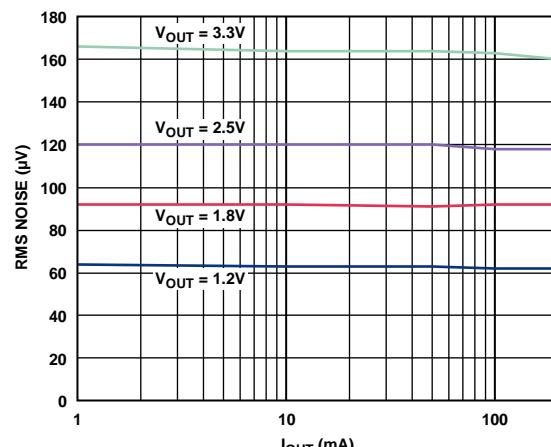

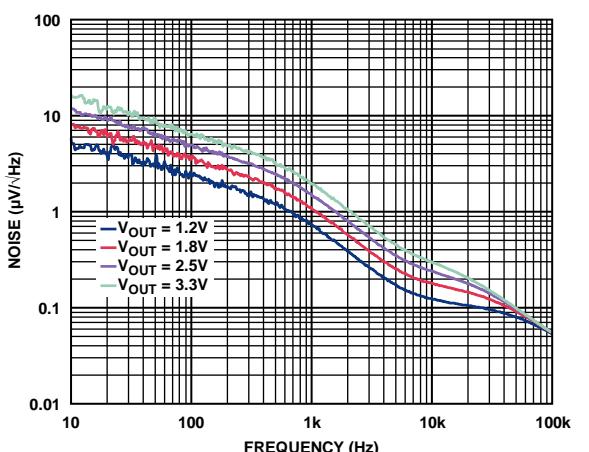

| OUTPUT NOISE                   |      | 92               |                   | $\mu\text{V rms}$ | 10 Hz to 100 kHz, $V_{VIN5} = 5 \text{ V}$ , $V_{OUT5} = 1.8 \text{ V}$                                               |

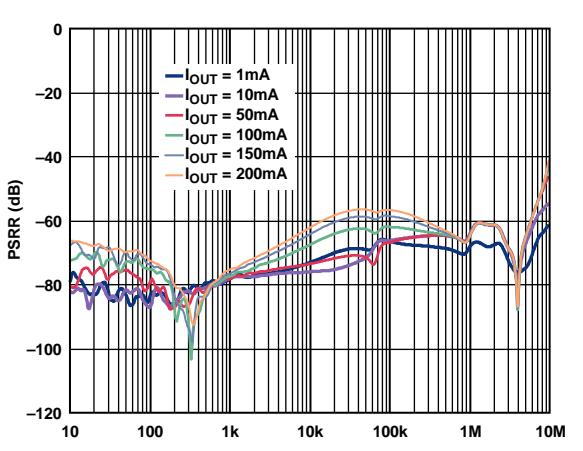

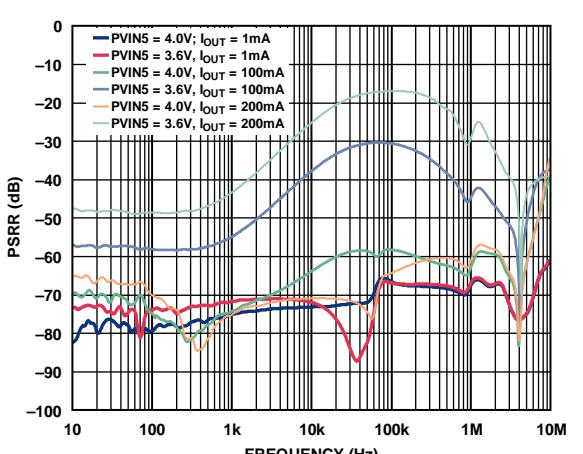

| POWER SUPPLY REJECTION RATIO   |      | 77<br>66         |                   | dB                | $V_{VIN5} = 5 \text{ V}$ , $V_{OUT5} = 1.8 \text{ V}$ , $I_{OUT5} = 1 \text{ mA}$<br>10 kHz<br>100 kHz                |

## 絶対最大定格

表 5.

| Parameter                              | Rating        |

|----------------------------------------|---------------|

| PVIN1 to PGND                          | -0.3 V~+18 V  |

| PVIN1 to PGND                          | -0.3 V~+18 V  |

| PVIN3 to PGND3                         | -0.3 V~+18 V  |

| PVIN4 to PGND4                         | -0.3 V~+18 V  |

| PVIN5 to GND                           | -0.3 V~+6.5 V |

| SW1 to PGND                            | -0.3 V~+18 V  |

| SW2 to PGND                            | -0.3 V~+18 V  |

| SW3 to PGND3                           | -0.3 V~+18 V  |

| SW4 to PGND4                           | -0.3 V~+18 V  |

| PGND to GND                            | -0.3 V~+0.3 V |

| PGND3 to GND                           | -0.3 V~+0.3 V |

| PGND4 to GND                           | -0.3 V~+0.3 V |

| BST1 to SW1                            | -0.3 V~+6.5 V |

| BST2 to SW2                            | -0.3 V~+6.5 V |

| BST3 to SW3                            | -0.3 V~+6.5 V |

| BST4 to SW4                            | -0.3 V~+6.5 V |

| DL1 to PGND                            | -0.3 V~+6.5 V |

| DL2 to PGND                            | -0.3 V~+6.5 V |

| SS12, SS34 to GND                      | -0.3 V~+6.5 V |

| EN1, EN2, EN3, EN4, EN5 to GND         | -0.3 V~+6.5 V |

| VREG to GND                            | -0.3 V~+6.5 V |

| SYNC/MODE to GND                       | -0.3 V~+6.5 V |

| VOUT5, FB5 to GND                      | -0.3 V~+6.5 V |

| RT to GND                              | -0.3 V~+3.6 V |

| PWRGD to GND                           | -0.3 V~+6.5 V |

| FB1, FB2, FB3, FB4 to GND <sup>1</sup> | -0.3 V~+3.6 V |

| FB2 to GND <sup>2</sup>                | -0.3 V~+6.5 V |

| FB4 to GND <sup>2</sup>                | -0.3 V~+7 V   |

| COMP1, COMP2, COMP3, COMP4 to GND      | -0.3 V~+3.6 V |

| VDD to GND                             | -0.3 V~+3.6 V |

| Storage Temperature Range              | -65°C~+150°C  |

| Operational Junction Temperature Range | -40°C~+125°C  |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作の節に記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

### 熱抵抗

$\theta_{JA}$  は最悪の条件、すなわち、回路基板に表面実装パッケージをハンダ付けした状態で規定しています。

表 6. 热抵抗

| Package Type | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|--------------|---------------|---------------|------|

| 48 ピン LFCSP  | 27.87         | 2.99          | °C/W |

### ESD の注意

**ESD (electrostatic discharge) sensitive device.**

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>1</sup> この定格は、ADP5052 が、可変出力電圧モード時に適用されます。

<sup>2</sup> この定格は、ADP5052 が、固定出力電圧モード時に適用されます。

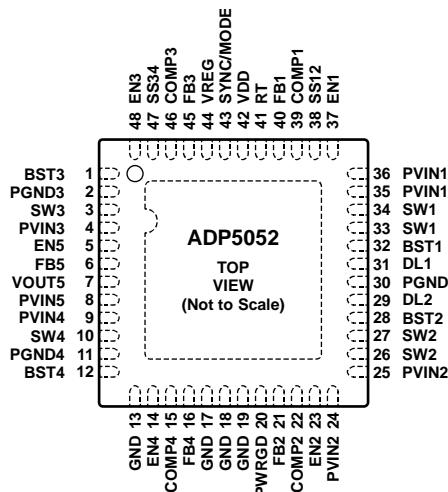

## ピン配置およびピン機能説明

## NOTES

1. THE EXPOSED PAD MUST BE CONNECTED AND SOLDERED TO AN EXTERNAL GROUND PLANE.

10900-002

図 3. ピン配置

表 7. ピン機能の説明

| Pin No. | Mnemonic | Description                                              |

|---------|----------|----------------------------------------------------------|

| 1       | BST3     | チャンネル3のハイサイドFET用電源。                                      |

| 2       | PGND3    | チャンネル3の電源グラウンド。                                          |

| 3       | SW3      | チャンネル3のスイッチング・ノード。                                       |

| 4       | PVIN3    | チャンネル3の電源入力。このピンとグラウンド間に、バイパス・コンデンサを接続してください。            |

| 5       | EN5      | チャンネル5のイネーブル入力。ターンオン・スレッショールドを設定するため、外部に抵抗分圧回路を取り付けて下さい。 |

| 6       | FB5      | チャンネル5のフィードバック・センス入力                                     |

| 7       | VOUT5    | チャンネル5の電源出力。                                             |

| 8       | PVIN5    | チャンネル5の電源入力。このピンとグラウンド間に、バイパス・コンデンサを接続してください。            |

| 9       | PVIN4    | チャンネル4の電源出力。このピンとグラウンド間に、バイパス・コンデンサを接続してください。            |

| 10      | SW4      | チャンネル4のスイッチング・ノード。                                       |

| 11      | PGND4    | チャンネル4の電源グラウンド。                                          |

| 12      | BST4     | チャンネル4のハイサイドFET用電源。                                      |

| 13      | GND      | このピンは内部テスト用です。グラウンドに接続してください。                            |

| 14      | EN4      | チャンネル4のイネーブル入力ターンオン・スレッショールドを設定するため、外部に抵抗分圧回路を取り付けて下さい。  |

| 15      | COMP4    | チャンネル4の誤差増幅器出力。このピンから、RCネットワークをグラウンドに接続して下さい。            |

| 16      | FB4      | チャンネル4のフィードバック・センス入力                                     |

| 17、19   | GND      | このピンは内部テスト用です。グラウンドに接続してください。                            |

| 20      | PWRGD    | パワーグッド信号出力。このオープンドレイン出力は、選択されたチャンネル用のパワーグッド出力です。         |

| 21      | FB2      | チャンネル2のフィードバック・センス入力                                     |

| 22      | COMP2    | チャンネル2の誤差増幅器出力。このピンから、RCネットワークをグラウンドに接続して下さい。            |

| 23      | EN2      | チャンネル2のイネーブル入力。ターンオン・スレッショールドを設定するため、外部に抵抗分圧回路を取り付けて下さい。 |

| Pin No. | Mnemonic  | Description                                                                                                                                                                                                                                                |

|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24、25   | PVIN2     | チャンネル2の電源入力。このピンとグラウンド間には、バイパス・コンデンサを接続してください。                                                                                                                                                                                                             |

| 26、27   | SW2       | チャンネル2のスイッチング・ノード。                                                                                                                                                                                                                                         |

| 28      | BST2      | チャンネル2のハイサイドFET用電源。                                                                                                                                                                                                                                        |

| 29      | DL2       | チャンネル2のローサイドFETゲート・ドライバ。チャンネル2用の電流制限スレッショールドをプログラムするため、このピンからグラウンドに対して抵抗を接続して下さい。                                                                                                                                                                          |

| 30      | PGND      | チャンネル1とチャンネル2用電力グラウンド。                                                                                                                                                                                                                                     |

| 31      | DL1       | チャンネル1用ローサイドFETゲート・ドライバ。チャンネル1用の電流制限スレッショールドをプログラムするため、このピンからグラウンドに対して抵抗を接続して下さい。                                                                                                                                                                          |

| 32      | BST1      | チャンネル1用ハイサイドFET用電源。                                                                                                                                                                                                                                        |

| 33、34   | SW1       | チャンネル1用スイッチング・ノード。                                                                                                                                                                                                                                         |

| 35、36   | PVIN1     | 5.1V内部VREGリニア・レギュレータと、チャンネル1降圧スイッチング・レギュレータ用電力入力このピンとグラウンド間には、バイパス・コンデンサを接続してください。                                                                                                                                                                         |

| 37      | EN1       | チャンネル1用イネーブル入力。ターンオン・スレッショールドを設定するため、外部に抵抗分圧回路を取り付けて下さい。                                                                                                                                                                                                   |

| 38      | SS12      | チャンネル1とチャンネル2のソフト・スタート時間をプログラムするために、VREGとグラウンド間に、抵抗分圧回路を接続して下さい（詳細は、ソフト・スタートセクション参照）。また、このピンは、チャンネル1とチャンネル2との並列動作を設定するためにも使われます（詳細は、並列動作セクション参照）。                                                                                                          |

| 39      | COMP1     | チャンネル1の誤差増幅器出力。このピンから、RCネットワークをグラウンドに接続して下さい。                                                                                                                                                                                                              |

| 40      | FB1       | チャンネル1のフィードバック・センス入力。                                                                                                                                                                                                                                      |

| 41      | RT        | スイッチング周波数をプログラムするために、RTピンとグラウンド間に抵抗を接続してください。スイッチング周波数範囲は、250 kHzから1.4 MHzです。詳細については、発振器セクションを参照してください。                                                                                                                                                    |

| 42      | VDD       | 内部3.3Vリニア・レギュレータ出力このピンとグラウンド間には、1μFのコンデンサを接続してください。                                                                                                                                                                                                        |

| 43      | SYNC/MODE | 同期入力/出力(SYNC)。外部クロックと内部スイッチング周波数とを同期する場合は、周波数250 kHzから1.4 MHzの範囲の外部クロック信号を入力して下さい。工場でのヒューズ調整を行う事で、このピンは、同期出力として構成することができます。<br>強制PWMもしくは自動PWM/PSM選択ピン(MODE)。このピンをロジック・ハイにすると、このデバイスは、強制PWM(FPWM)モードで動作します。このピンをロジック・ローにすると、このデバイスは、自動PWM/PSM切り替えモードで動作します。 |

| 44      | VREG      | 内部5.1Vリニア・レギュレータ出力。このピンとグラウンド間には、1μFのコンデンサを接続してください。                                                                                                                                                                                                       |

| 45      | FB3       | チャンネル3用フィードバック・センス入力                                                                                                                                                                                                                                       |

| 46      | COMP3     | チャンネル3用誤差増幅器出力。このピンから、RCネットワークをグラウンドに接続して下さい。                                                                                                                                                                                                              |

| 47      | SS34      | チャンネル3とチャンネル4のソフト・スタート時間をプログラムするために、VREGとグラウンド間に、抵抗分圧回路を接続して下さい（詳細は、ソフト・スタートセクション参照）。                                                                                                                                                                      |

| 48      | EN3       | チャンネル3のイネーブル入力。ターンオン・スレッショールドを設定するため、外部に抵抗分圧回路を取り付けて下さい。                                                                                                                                                                                                   |

|         | EPAD      | エクスポート・パッド（アナログ・グラウンド）。エクスポート・パッドは、外部のグラウンドに接続し、必ず半田付けしてください。                                                                                                                                                                                              |

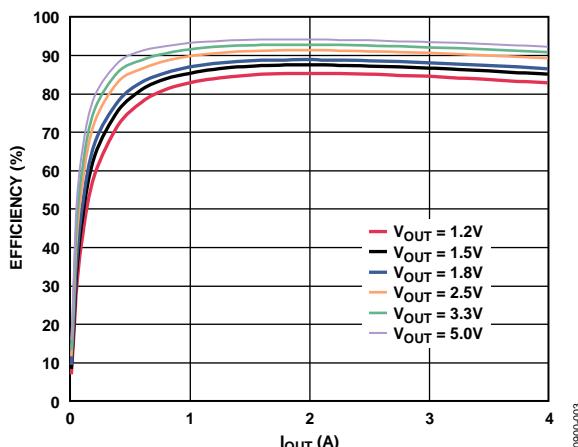

## 代表的な性能特性

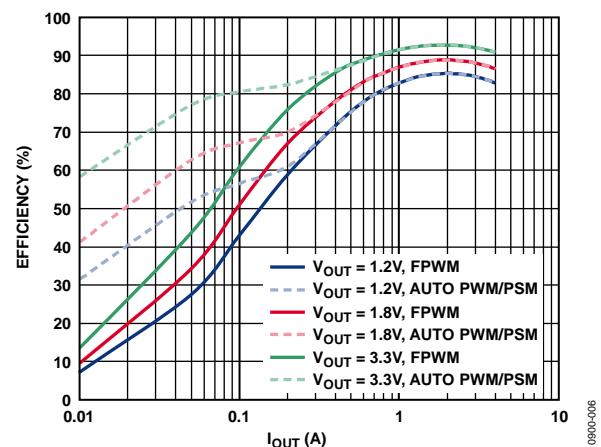

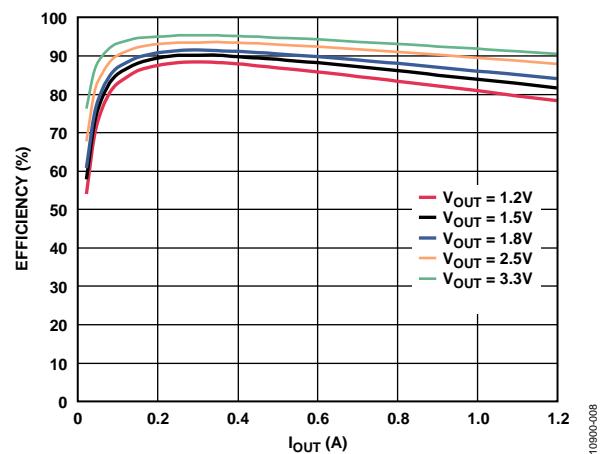

図4. チャンネル1/チャンネル2の効率カーブ  $V_{IN} = 12V$ ,  $f_{SW} = 600\text{ kHz}$ , FPWM モード

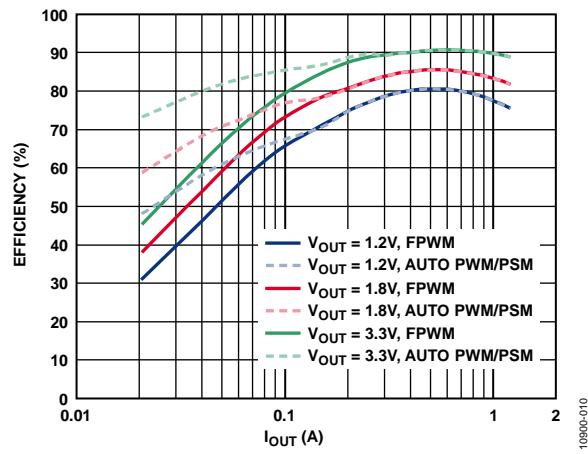

図7. チャンネル1/チャンネル2の効率カーブ  $V_{IN} = 12V$ ,  $f_{SW} = 600\text{ kHz}$ , FPWM モードと自動 PWM/PSM モード

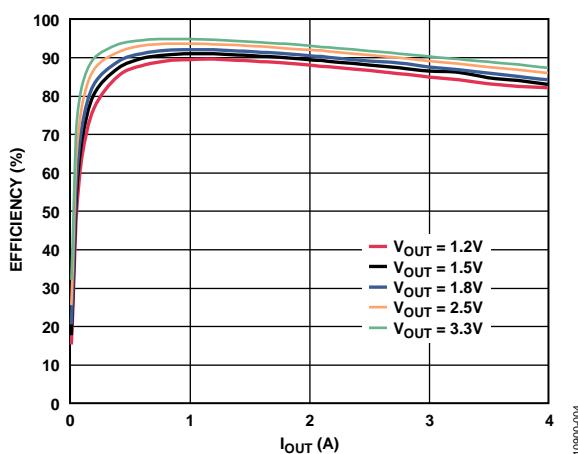

図5. チャンネル1/チャンネル2の効率カーブ  $V_{IN} = 5.0V$ ,  $f_{SW} = 600\text{ kHz}$ , FPWM モード

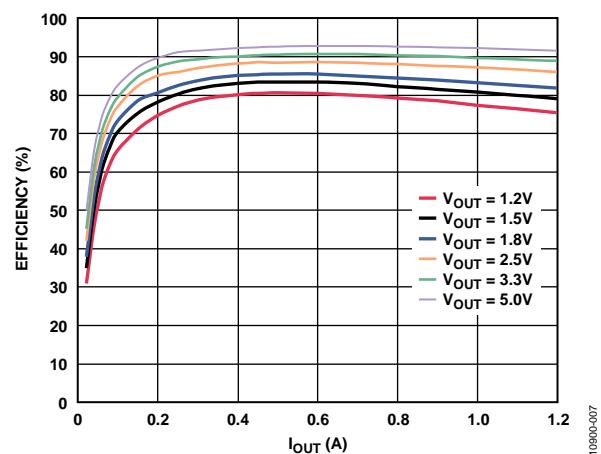

図8. チャンネル3/チャンネル4の効率カーブ  $V_{IN} = 12V$ ,  $f_{SW} = 600\text{ kHz}$ , FPWM モード

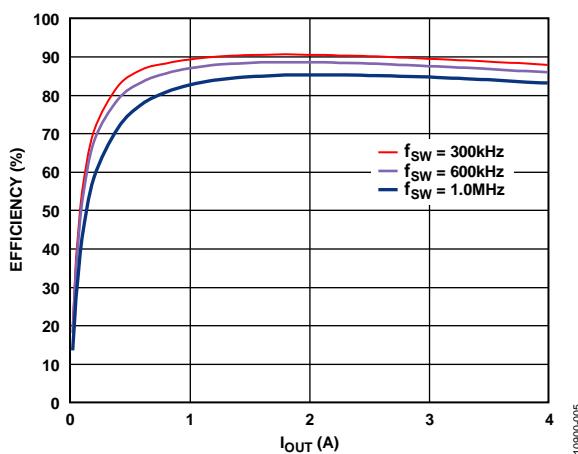

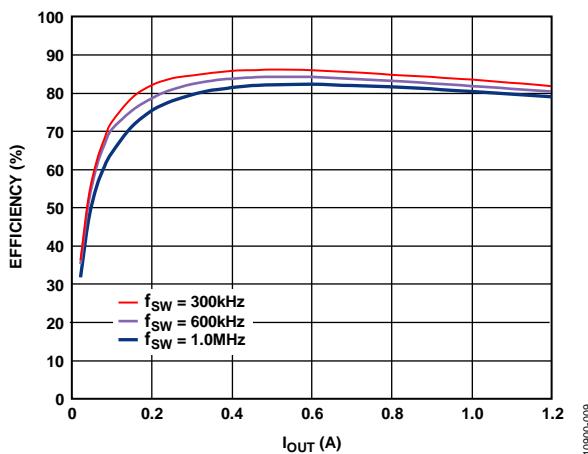

図6. チャンネル1/チャンネル2の効率カーブ  $V_{IN} = 12V$ ,  $f_{out} = 1.8V$ , FPWM モード

図9. チャンネル3/チャンネル4の効率カーブ  $V_{IN} = 5.0V$ ,  $f_{SW} = 600\text{ kHz}$ , FPWM モード

図 10. チャンネル 3/チャンネル 4 の効率カーブ  $V_{IN} = 12 \text{ V}$ 、

$V_{OUT} = 1.8 \text{ V}$ 、FPWM モード

図 11. チャンネル 3/チャンネル 4 の効率カーブ  $V_{IN} = 12 \text{ V}$ 、

$f_{SW} = 600 \text{ kHz}$ 、FPWM モードと自動 PWM/PSM モード

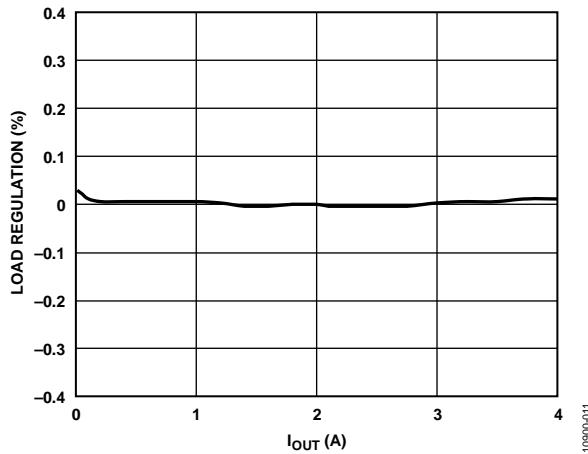

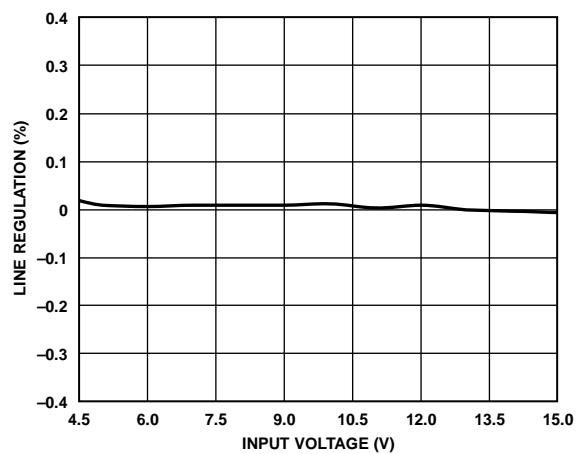

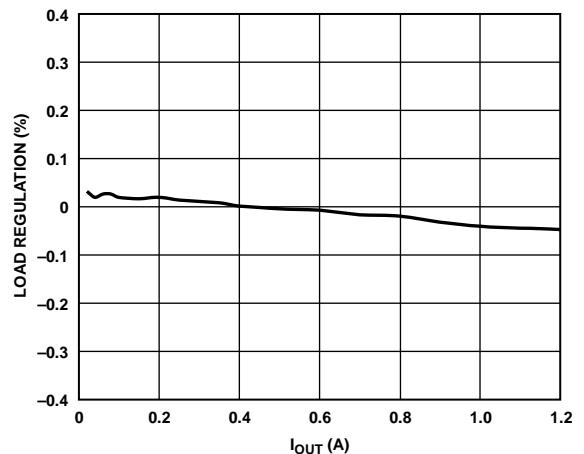

図 12. チャンネル 1 ロード・レギュレーション  $V_{IN} = 12 \text{ V}$ 、

$V_{OUT} = 3.3 \text{ V}$ 、 $f_{SW} = 600 \text{ kHz}$ 、FPWM モード

図 13. チャンネル 1 ライン・レギュレーション  $V_{OUT} = 3.3 \text{ V}$ 、

$I_{OUT} = 4 \text{ A}$ 、 $f_{SW} = 600 \text{ kHz}$ 、FPWM モード

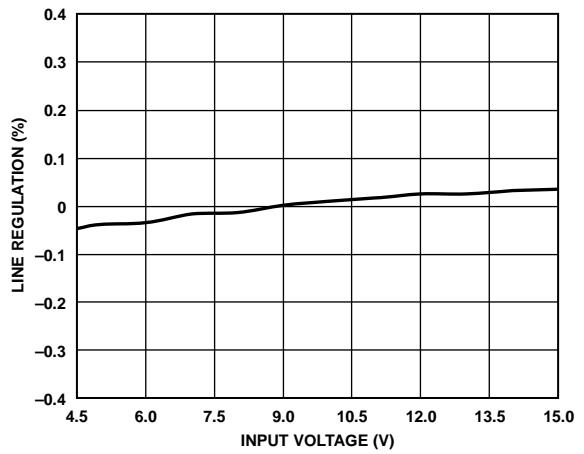

図 14. チャンネル 3 ロード・レギュレーション  $V_{IN} = 12 \text{ V}$ 、

$V_{OUT} = 3.3 \text{ V}$ 、 $f_{SW} = 600 \text{ kHz}$ 、FPWM モード

図 15. チャンネル 3 ライン・レギュレーション  $V_{OUT} = 3.3 \text{ V}$ 、

$I_{OUT} = 1 \text{ A}$ 、 $f_{SW} = 600 \text{ kHz}$ 、FPWM モード

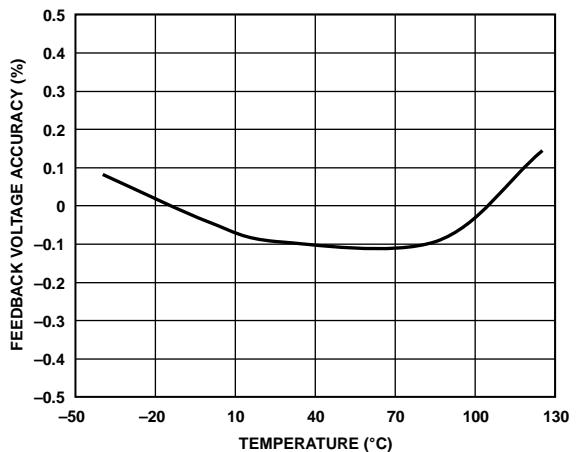

図 16.0.8V フィードバック電圧精度の温度特性

(チャンネル 1、可変出力品)

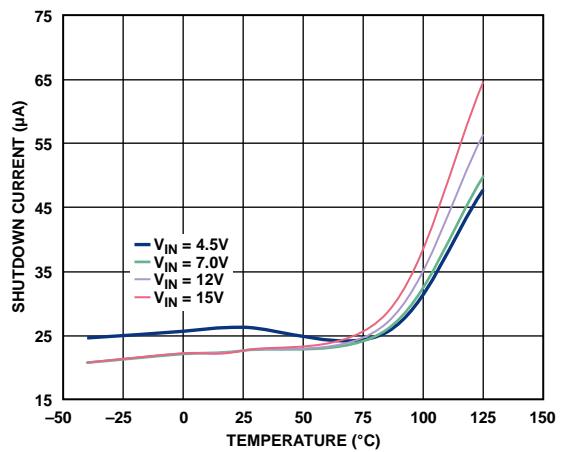

図 19.シャット・ダウン電流の温度特性

(EN1、EN2、EN3、EN4、EN5がローの時)

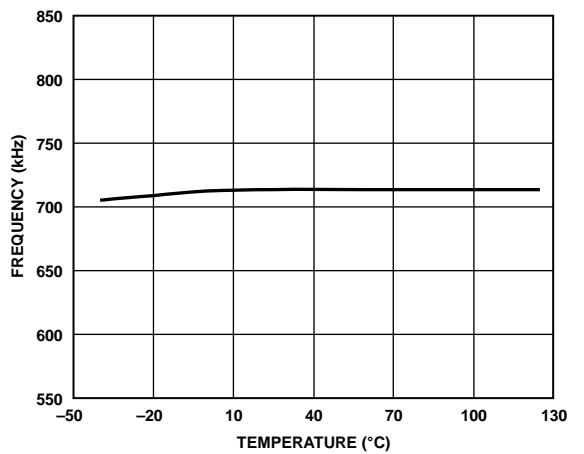

図 17.周波数の温度特性、 $V_{IN} = 12\text{ V}$

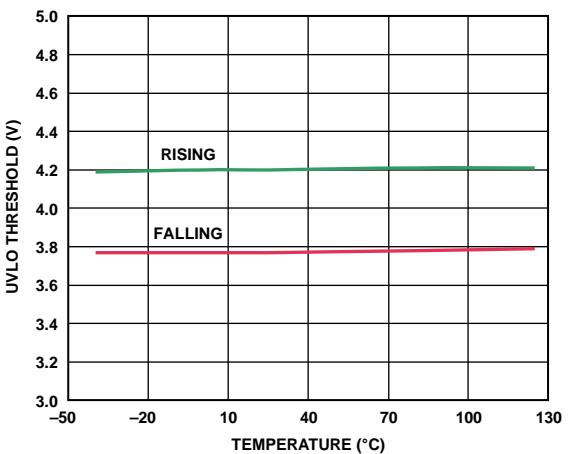

図 20.UVLO スレッショルドの温度特性

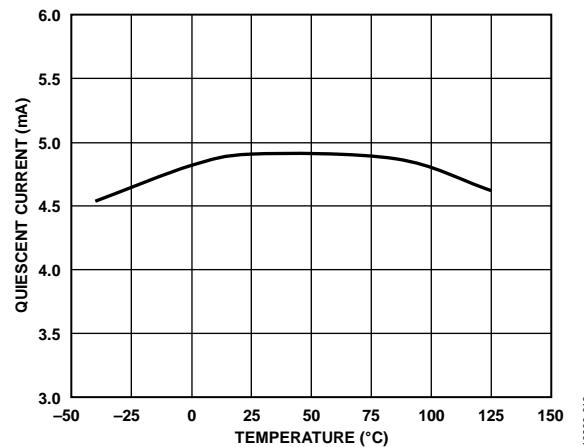

図 18.静止電流の温度特性

(PVIN1、PVIN2、PVIN3、PVIN4すべてを含む)

図 21.入力電圧 対 チャンネル 1/チャンネル 2 の電流制限値

図22.最小オン時間の温度特性

図25.出力負荷 対 チャンネル5 (LDO レギュレータ)

出力ノイズ

$V_{IN} = 5 \text{ V}$ ,  $C_{OUT} = 1 \mu\text{F}$ 図23.入力電圧 対 チャンネル5 (LDO レギュレータ) の

ライン・レギュレーション図26.チャンネル5

(LDO レギュレータ) のPSRRの周波数特性、

$V_{IN} = 5 \text{ V}$ ,  $V_{OUT} = 3.3 \text{ V}$ ,  $C_{OUT} = 1 \mu\text{F}$ 図24.チャンネル5 (LDO レギュレータ) 出力

ノイズ・スペクトラム

$V_{IN} = 5 \text{ V}$ ,  $C_{OUT} = 1 \mu\text{F}$ ,  $I_{OUT} = 10 \text{ mA}$ 図27.各種負荷電流及びドロップアウト電圧対する、

チャンネル5 (LDO レギュレータ) のPSRR、

$V_{OUT} = 3.3 \text{ V}$ ,  $C_{OUT} = 1 \mu\text{F}$

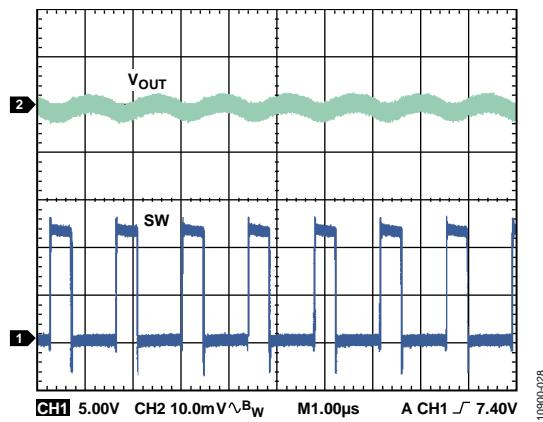

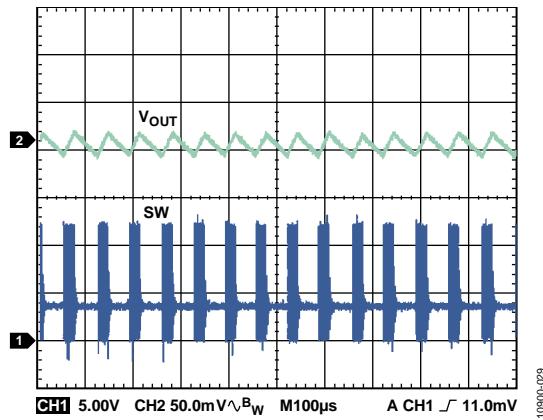

図28.高負荷時の安定状態波形。 $V_{IN} = 12 V$ ,  $V_{OUT} = 3.3 V$ ,  $I_{OUT} = 3A$ ,  $f_{SW} = 600\text{kHz}$ ,  $L = 4.7\mu\text{H}$ ,  $C_{OUT} = 47\mu\text{F} \times 2$ , FPWM モード

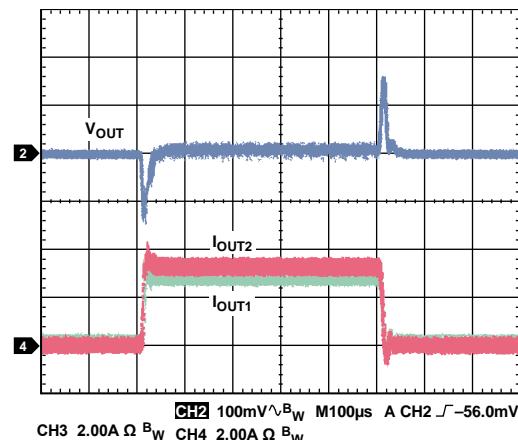

図31 チャンネル1/チャンネル2を並列動作時の負荷応答。

0Aから6A,  $V_{IN} = 12 V$ ,  $V_{OUT} = 3.3 V$ ,  $f_{SW} = 600\text{kHz}$ ,  $L = 4.7\mu\text{H}$ ,  $C_{OUT} = 47\mu\text{F} \times 4$

図29.低負荷時における安定状態波形。 $V_{IN} = 12 V$ ,  $V_{OUT} = 3.3 V$ ,  $I_{OUT} = 30\text{mA}$ ,  $f_{SW} = 600\text{kHz}$ ,  $L = 4.7\mu\text{H}$ ,  $C_{OUT} = 47\mu\text{F} \times 2$ , 自動PWM/PSMモード

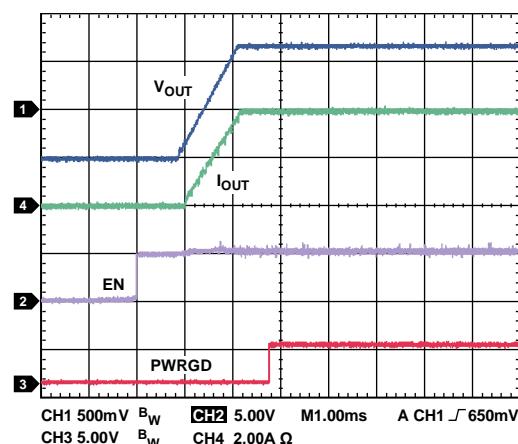

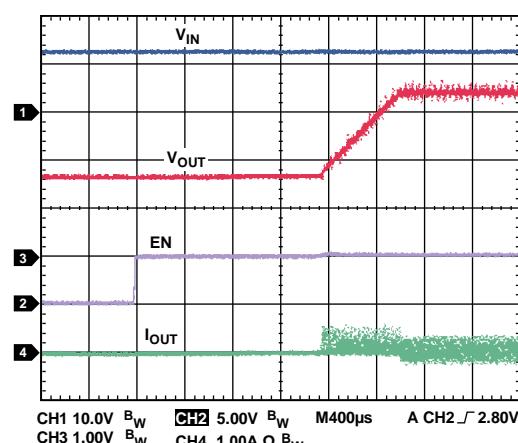

図32.チャンネル1/チャンネル2のソフト・スタート波形。4Aの抵抗負荷時。

$V_{IN} = 12 V$ ,  $V_{OUT} = 1.2 V$ ,  $f_{SW} = 600\text{kHz}$ ,  $L = 1\mu\text{H}$ ,  $C_{OUT} = 47\mu\text{F} \times 2$

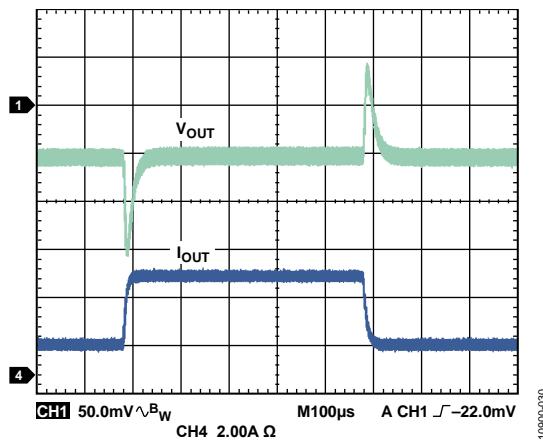

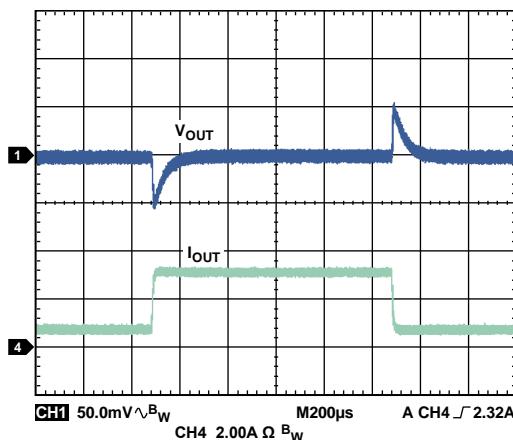

図30.チャンネル1/チャンネル2の負荷応答。1Aから4A,  $V_{IN} = 12 V$ ,  $V_{OUT} = 3.3 V$ ,  $f_{SW} = 600\text{kHz}$ ,  $L = 2.2\mu\text{H}$ ,  $C_{OUT} = 47\mu\text{F} \times 2$

図33.出力コンデンサに電荷が残っていた場合のスタートアップ。

$V_{IN} = 12 V$ ,  $V_{OUT} = 3.3 V$

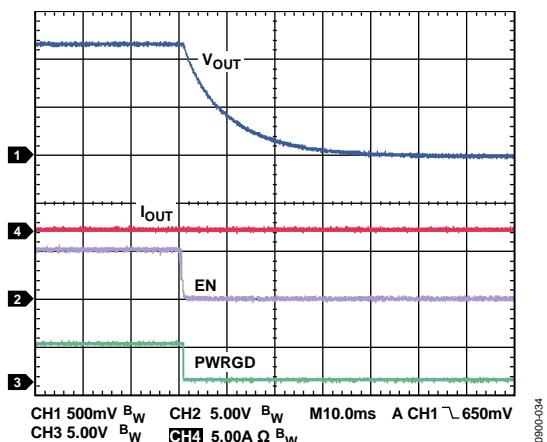

図 34. アクティブ出力放電によるチャンネル 1/チャンネル 2 の

シャット・ダウン波形。

$V_{IN} = 12 \text{ V}$ ,  $V_{OUT} = 1.2 \text{ V}$ ,  $f_{SW} = 600 \text{ kHz}$ ,  $L = 1 \mu\text{H}$ ,  $C_{OUT} = 47 \mu\text{F} \times 2$

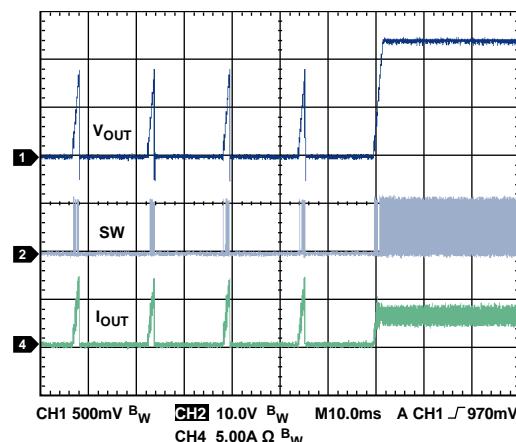

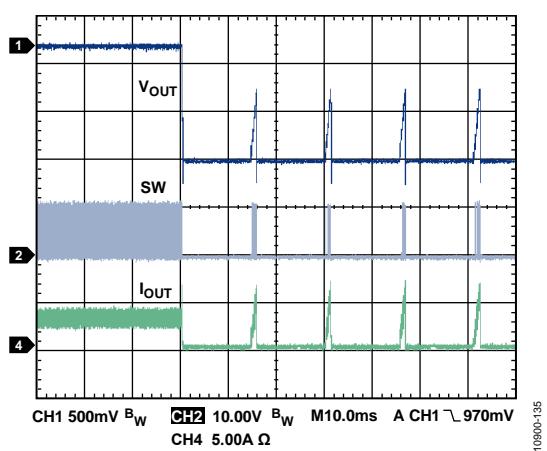

図 36. 出力短絡保護からの復帰時の波形。

$V_{IN} = 12 \text{ V}$ ,  $V_{OUT} = 1.2 \text{ V}$ ,

$f_{SW} = 600 \text{ kHz}$ ,  $L = 1 \mu\text{H}$ ,  $C_{OUT} = 47 \mu\text{F} \times 2$

図 35. 出力短絡保護へ移行時の波形。 $V_{IN} = 12 \text{ V}$ ,  $V_{OUT} = 1.2 \text{ V}$ ,

$f_{SW} = 600 \text{ kHz}$ ,  $L = 1 \mu\text{H}$ ,  $C_{OUT} = 47 \mu\text{F} \times 2$

## 動作原理

ADP5052 は、マイクロパワー・マネジメント・ユニットで、4つの高性能降圧スイッチング・レギュレータと 200mA の LDO を、48 ピン LFCSP パッケージに収めており、性能およびボード・スペースの要求をみたします。さらにシンプルかつ高効率なアプリケーションを実現するため、前段レギュレータ無しで、最大 15 V までの入力電圧を直接することができます。

### 降圧スイッチング・レギュレータの動作モード

#### PWM モード

パルス幅変調 (PWM) モードでは、ADP5052 の降圧スイッチング・レギュレータは、固定周波数で動作します。この周波数は、RT ピンによってプログラミングできる内部発振器で決まります。発振器からの信号における各サイクルのスタート時、ハイサイドの MOSFET がオンになります。正の電圧がインダクタに加えられます。電流検知用信号がハイサイド MOSFET をオフにするピーク・インダクタ電流スレッショールドを超えるまで、インダクタに流れる電流が増加します。このスレッショールドは、誤差増幅器の出力で設定します。

ハイサイド MOSFET がオフ状態のとき、発振器のクロック・パルスが次の新しいサイクルを開始するまで、インダクタに流れる電流は、ローサイド MOSFET を通じて減少してゆきます。ADP5052 の降圧スイッチング・レギュレータは、ピーク・インダクタ電流スレッショールドを調整することで、出力電圧を安定化します。

#### PSM モード

ADP5052 の降圧スイッチング・レギュレータは、さらなる高効率を達成するため、出力の負荷電流が PSM (パワー・セーブ・モード) スレッショールドを下回ると、周波数可変の PSM 動作へと滑らかに以降します。出力電圧がレギュレーションできる電圧以下になると、降圧スイッチング・レギュレータは PWM モードに入り、発振器を数サイクル分動作させて、出力電圧をレギュレーションできる電圧まで上昇させます。バースト間のアイドル時間では、MOSFET はオフになります。出力コンデンサが全出力電流を供給します。

PSM コンパレータは、インダクタに流れるピーク電流を表す情報を保つ内部補償ノードを監視しています。平均 PSM 電流スレッショールドは、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、インダクタおよびコンデンサの値に依存します。出力電圧は、時折レギュレーションできる電圧を下回ったり元に戻ったりするので、軽い負荷状態においては、PSM モードにおける出力電圧のリップルは、強制 PWM モードにおける出力電圧のリップルより大きくなります。

#### 強制 PWM、自動 PWM/PSM モード

この降圧スイッチング・レギュレータは、SYNC/MODE ピンを使って、常時 PWM モードで動作するように構成することができます。強制 PWM モード (FPWM) では、出力電流が PWM/PSM 切り替えスレッショールドを下回ったとしても、レギュレータは固定周波数で動作します。軽い負荷状態において、PWM モードの効率は、PSM モードに比べて低くなります。ローサイド MOSFET は、インダクタの電流が 0A を下回ってもオン状態を維持します。その結果 ADP5052 は電流連続モード (CCM) になります。

この降圧スイッチング・レギュレータは、SYNC/MODE ピンを使って、自動 PWM/PSM モードに構成することもできます。この自動 PWM/PSM モードでは、降圧スイッチング・レギュレータは出力電流の値に応じて、PWM モード、もしくは

PSM モードで動作します。平均出力電流が、PWM/PSM スレッショールドを下回った場合、降圧スイッチング・レギュレータは PSM モードになります。この PSM モードでは、レギュレータは高効率を維持するため、スイッチング周波数を下げて動作します。出力電流が 0A になると、ローサイド MOSFET はオフになります。この結果、レギュレータは電流不連続モード (DCM) になります。

SYNC/MODE ピンを VREG に接続すると、このデバイスは強制 PWM (FPWM) モードとして動作します。SYNC/MODE ピンをグラウンド接続すると、このデバイスは自動 PWM/PSM モードとして動作します。

#### 調整可能および固定出力電圧

ADP5052 は、工場でのヒューズ調整を行うことで、出力電圧を調整可能とするか、固定出力電圧にするかを設定することができます。出力電圧を調整可能な状態に設定した場合、必要な電圧を得るために、フィードバック基準電圧 (チャンネル 1 からチャンネル 4 の場合、0.8V、チャンネル 5 の場合は 0.5V) 端子に、抵抗分圧回路を取り付けてください。

固定出力電圧設定の場合、抵抗分圧回路が ADP5052 内部に取り付けられているため、フィードバック・ピン (FBx) を直接電圧出力に接続して下さい。表 8 に、各降圧スイッチング・レギュレータの各チャンネルにおける固定出力電圧範囲を示します。

表 8. 固定出力電圧範囲

| チャンネル   | 固定出力電圧範囲                          |

|---------|-----------------------------------|

| チャンネル 1 | 0.85 V~1.6 V、25 mV ステップ           |

| チャンネル 2 | 3.3 V~5.0 V、300mV または 200 mV ステップ |

| チャンネル 3 | 1.2 V~1.8 V、100 mV ステップ           |

| チャンネル 4 | 2.5 V~5.5 V、100 mV ステップ           |

出力電圧範囲は、工場でのヒューズ調整で設定できます。もし、この表とは違った出力電圧範囲が必要であれば、最寄りのアナログ・デバイス、もしくは販売代理店の営業担当者にご連絡ください。

#### 内部レギュレータ (VREG と VDD)

ADP5052 内部にある VREG レギュレータは、MOSFET ドライバ用バイアス電圧源として、MOSFET に安定した 5.1V を供給します。ADP5052 内部にある VDD レギュレータは、内部コントロール回路用電源として、安定した 3.3V を供給します。VREG とグラウンド間には  $1.0\mu F$  のセラミック・コンデンサを接続してください。VDD とグラウンド間にも、VREG とは別の  $1.0\mu F$  のセラミック・コンデンサを接続してください。PVIN1 に電圧がかかっている限り、内部の VREG と VDD レギュレータは動作しています。

内部の VREG レギュレータは、常に 5.1V の電圧で動作し、95mA の電流供給能力があるので、MOSFET を駆動する電流と、小さなシステムに必要な電流を賄うことができます。VREG レギュレータには、電流制限回路が含まれており、このデバイスに過負荷がかかったときに、VREG レギュレータ回路を保護します。

VDD レギュレータは、内部回路用であり、VREG と同じような目的に使うことは推奨されません。

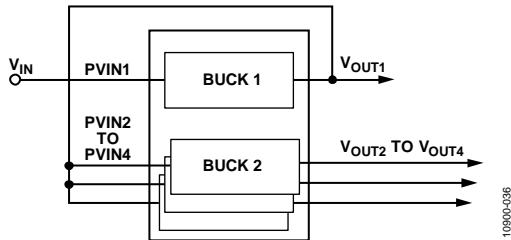

## 異なる電源電圧入力に対応

ADP5052 の 4 つの降圧スイッチング・レギュレータは、異なる電源電圧入力に対応できます。これは、4 つの降圧スイッチング・レギュレータの各々の入力端子に、異なる電圧源を接続できることを意味します。

PVIN1 ピンは、内部レギュレータと制御回路へ電圧を供給する電圧源になっています。従って、それぞれの降圧スイッチング・レギュレータに異なる電圧を与えることを考えているならば、PVIN1 ピンに与える電圧は、他のチャンネルが動作する前に、UVLO スレッショールドを超えるようにしなければなりません。

高精度イネーブルを使うと、PVIN1 ピンの電圧を監視し、PVIN1 電圧が十分高くなつて、他のレギュレータ出力が制御可能になるまで、それらのレギュレータの動作開始を遅らせることができます。詳細については、高精度イネーブルセクションを参照してください。

ADP5052 は、4 つの降圧スイッチング・レギュレータの直列接続による電圧供給にも対応しています。図 37 に示すように、PVIN2、PVIN3、そして PVIN4 には、チャンネル 1 の出力電圧を接続することができます。この構成では、チャンネル 1 の出力電圧は、PVIN2、PVIN3、そして PVIN4 の UVLO スレッショールドよりも高い電圧であることが必要です。

図 37. 直列接続による電力供給アプリケーション

## ローサイド・デバイスの選択

チャンネル 1 とチャンネル 2 の降圧スイッチング・レギュレータは、4A のハイサイド・パワーMOSFET とローサイド MOSFET ドライバを内蔵しています。ADP5052 に使用する N チャンネル MOSFET は、同期整流スイッチング・レギュレータとして動作可能なものを選択する必要があります。一般的には、低  $R_{DS(on)}$  の N チャンネル MOSFET を使うことで高効率を達成することができます。また、PCB 上の専有面積を節約するために、チャンネル 1 とチャンネル 2 用の 2 つの MOSFET が 1 つのパッケージに入っているものを推奨します。詳細については、ローサイド・パワー・デバイスの選択を参照してください。

## ブートストラップ回路

ADP5052 内部の各スイッチング・レギュレータには、ブートストラップ回路が内蔵されています。ブートストラップ回路は、 $0.1\mu\text{F}$  のセラミック・コンデンサ (X5R もしくは X7R) が必要で、ハイサイド MOSFET 用のゲート駆動電圧を供給するために、BSTx ピンと SWx ピンの間に接続してください。

## アクティブ出力放電スイッチ

ADP5052 内の降圧スイッチング・レギュレータは、スイッチング・ノードとグラウンド間に、放電用スイッチを内蔵しています。チャンネルをディスエーブルにするととき、そのチャンネルに内蔵されているスイッチをオンにします。これによって、出力コンデンサに貯まっている電荷を素早くの放電できます。チャンネル 1 からチャンネル 4 に内蔵されている、放電スイッチのオン抵抗の代表値は  $250\ \Omega$  です。全 4 つの降圧スイッチング・レギュレータの対する、各放電スイッチ機

能のイネーブルもしくはディスエーブルは、工場でのヒューズ調整で設定します。

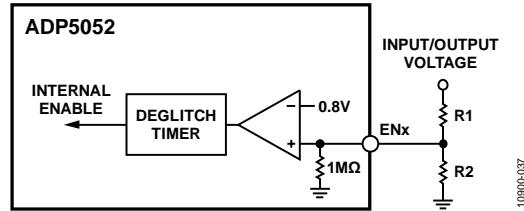

## 高精度イネーブル

ADP5052 は、LDO レギュレータを含む、各レギュレータのイネーブル制御ピンを持っています。イネーブル制御 (ENx) ピンは、基準電圧  $0.8\text{V}$  の高精度イネーブル回路として接続されています。ENx ピンの電圧が  $0.8\text{V}$  以上になると、レギュレータがイネーブルになります。ENx ピンの電圧が  $0.725\text{V}$  を下回ると、レギュレータはディスエーブルになります。ENx ピンが開放状態でエラーが起こることを防ぐために、内部には  $1\text{M}\Omega$  ブルダウント抵抗が取り付けられています。

高精度イネーブルのスレッショールド電圧を使えば、1 つのデバイスにおける各チャンネル出力のシーケンシングが可能になるだけではなく、複数の ADP5052 のチャンネル間、もしくは他の電源デバイスの電源投入シーケンスも可能になります。ENx ピンは、抵抗分圧回路を使って、プログラム可能な、UVLO 入力としても使うことができます (図 38 参照)。詳細については、UVLO 入力のプログラミングセクションを参照してください。

図 38.1 チャンネルに対する高精度イネーブル用回路図

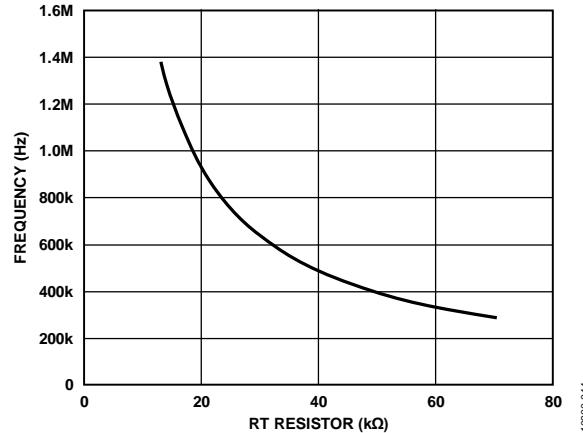

## 発振器

ADP5052 のスイッチング周波数 ( $f_{sw}$ ) は、RT ピンとグラウンド間に取り付ける抵抗の値によって、 $250\text{kHz}$  から  $1.4\text{MHz}$  まで設定できます。RT に接続する抵抗値は以下の式を使って計算できます。

$$R_{RT} (\text{k}\Omega) = [14,822/f_{sw} (\text{kHz})]^{1.081}$$

図 39 は、スイッチング周波数 ( $f_{sw}$ ) と RT ピンに接続する抵抗値との代表的な関係を示しています。スイッチング周波数が可変できるので、効率を重視するか、それとも回路専有面積を重視するかを選択し調整できます。

図 39. RT ピンの抵抗 対 スイッチング周波数

チャンネル 1 とチャンネル 3 に関しては、RT ピンを使って決めたマスター・スイッチング周波数の半分の周波数を持つ信号を与える事もできます。この設定は、工場でのヒューズ調整によって選択します。但し、マスター・スイッチング周波数が  $250\text{kHz}$  以下の場合、チャンネル 1 とチャンネル 3 へ半分の周波数を供給することは、推奨されません。

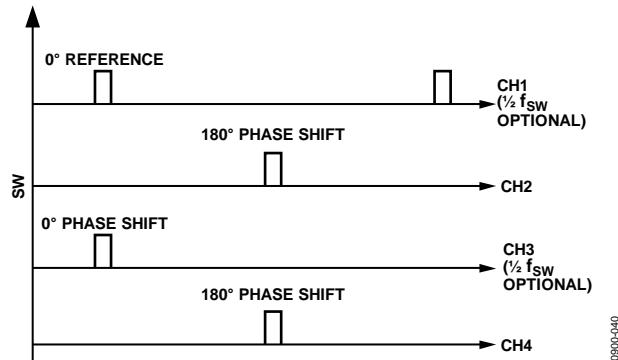

## 位相シフト

チャンネル1とチャンネル2、チャンネル3とチャンネル4は $180^\circ$ で位相シフトしています。従って、チャンネル3はチャンネル1とは位相が一致しており、さらにチャンネル4はチャンネル2とは位相が一致しています(図40参照)。この様な位相差を持たせることで、位相差を伴ったスイッチング動作をさせ、入力リップル電流とグラウンドノイズを減らせるため、EMIノイズ対策やビートノイズ対策などに効果があります。

図40. 4つの降圧スイッチング・レギュレータにおける位相シフト

## 同期入力/出力

ADP5052のスイッチング周波数は、250kHzから1.4MHzまでの範囲で、外部クロックと同期させることができます。ADP5052は、外部クロックがSYNC/MODEピンに与えられているかどうかを自動的に検知し、内部スイッチング・クロック周波数から外部クロックの周波数へ、なめらかに切り替えることができます。外部クロック信号が停止した時、デバイスは内部クロックでの動作に切り替わり、そのまま動作し続けます。

RTピンで設定される内部クロック信号の周波数は、外部クロックとの同期動作を成功させるため、外部クロック信号の周波数に近い値に設定しなければなりません。代表的なアプリケーションでは、2つの信号における周波数の差異は、 $\pm 15\%$ 以下にすることを推奨します。

SYNC/MODEピンは、工場でのヒューズ調整により同期クロック出力として構成することもできます。SYNC/MODEピンからは、RTピンに接続される抵抗によって決まる内部スイッチング周波数と等しく、かつ50%のデューティー比を持つクロック・パルスが outputされます。この信号は、チャンネル1のスイッチング・ノードで発生する同期クロックから、ある時間(スイッチング周期  $t_{sw}$  の約 15%)遅れて outputされます。

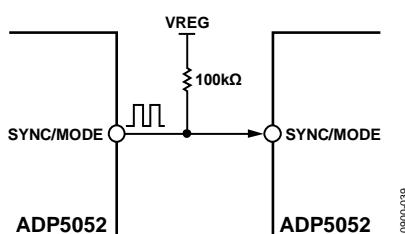

図41に2つのADP5052を周波数同期モードで使う場合の構成を示します。1つのADP5052は、もう1つのADP5052へのクロック出力源として構成されます。このとき、100kΩのプルアップ抵抗を使うことをお勧めします。これは

SYNC/MODEピンが開放状態になったときのエラーを防ぐためです。

図41. 2つのADP5052を同期モードで動作させる場合の構成

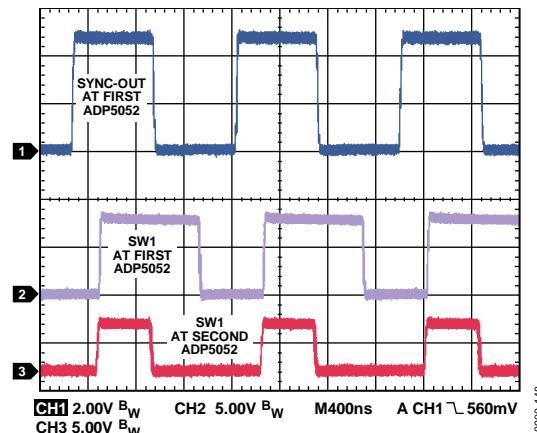

図41に示した構成では、第1のADP5052のチャンネル1と、第2のADP5052のチャンネル1との位相差は $0^\circ$ です(図42参照)。

図42. 2つのADP5052を同期モードで動作させたときの波形

## ソフト・スタート

ADP5052の降圧スイッチング・レギュレータは、ソフト・スタート回路を搭載しています。この回路によってスタートアップ時、出力電圧の上昇を制御することができ、それによって突入電流を制限します。SS12ピンとSS34ピンを直接VREGに接続すると、各レギュレータのソフト・スタート時間は、おおよそ2msに固定されます。

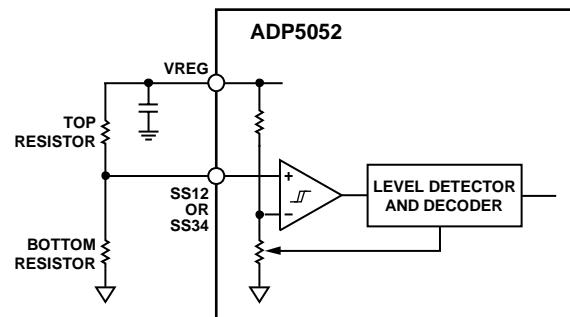

ソフト・スタート時間の値を、2ms、4msもしくは8msに設定したい場合、VREGピンとグラウンド間に抵抗分圧回路を設け、その電圧を、SS12ピンもしくはSS34ピンに与えて下さい(図43参照)。この構成は、特定のスタートアップ・シーケンスに対応する事が求められるアプリケーション、または大きな出力コンデンサを使ったアプリケーションにおいて必要になるかもしれません。

図43. ソフト・スタート用レベル検出回路

SS12 ピンは、チャンネル 1 とチャンネル 2 のソフト・スタート時間をプログラムできますが、抵抗値の選び方によっては、チャンネル 1 とチャンネル 2 の並列動作をさせることもできます。SS34 ピンは、チャンネル 3 とチャンネル 4 のソフト・スタート時間をプログラムできます。表 9 に、ソフト・スタート時間を設定するために必要な抵抗値の一覧を示します。

表 9. SS12 と SS34 Pin によって設定される、ソフト・スタート時間

| R <sub>TOP</sub> (kΩ) | R <sub>BOT</sub> (kΩ) | ソフト・スタート時間 |         | ソフト・スタート時間 |         |

|-----------------------|-----------------------|------------|---------|------------|---------|

|                       |                       | チャンネル 1    | チャンネル 2 | チャンネル 3    | チャンネル 4 |

| 0                     | N/A                   | 2 ms       | 2 ms    | 2 ms       | 2 ms    |

| 100                   | 600                   | 2 ms       | 並列動作    | 2 ms       | 4 ms    |

| 200                   | 500                   | 2 ms       | 8 ms    | 2 ms       | 8 ms    |

| 300                   | 400                   | 4 ms       | 2 ms    | 4 ms       | 2 ms    |

| 400                   | 300                   | 4 ms       | 4 ms    | 4 ms       | 4 ms    |

| 500                   | 200                   | 8 ms       | 2 ms    | 4 ms       | 8 ms    |

| 600                   | 100                   | 8 ms       | 並列動作    | 8 ms       | 2 ms    |

| N/A                   | 0                     | 8 ms       | 8 ms    | 8 ms       | 8 ms    |

## 並列動作

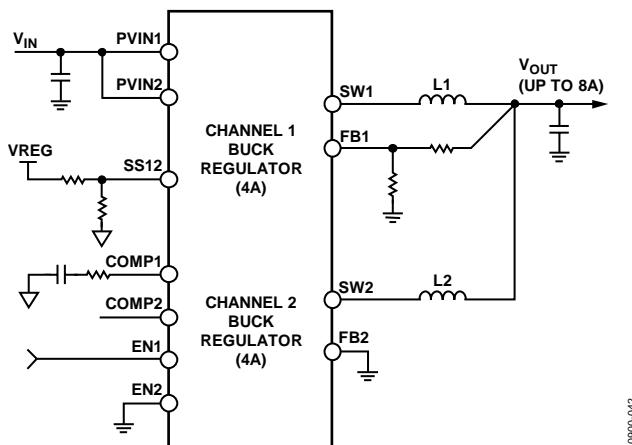

ADP5052 は、チャンネル 1 とチャンネル 2 とを 2 フェーズで並列動作させ、最大 8A の電流が供給できる単一電源にすることができます。チャンネル 1 とチャンネル 2 とを並列動作させ、単一電源として構成するには、次の手順を行って下さい (図 44 参照) :

- 図 44 に示してあるように、SS12 ピンを使って並列動作可能な設定にします。

- COMP2 ピンはオープンのままにしておきます。

- FB1 ピンを使って出力電圧を決めます。

- FB2 ピンをグラウンドに接続します。つまり FB2 は無視されます。

- EN2 ピンをグラウンドに接続します。つまり EN2 は無視されます。

図 44. チャンネル 1 とチャンネル 2 とを使った並列動作

チャンネル 1 とチャンネル 2 とを並列動作させる様に構成する場合、それぞれのチャンネルの設定は以下の様にして下さい。

- チャンネル 1 とチャンネル 2 との入力電圧と電流制限設定は、同じ値にして下さい。

- 両方のチャンネルとも、強制 PWM モードで動作させて下さい。

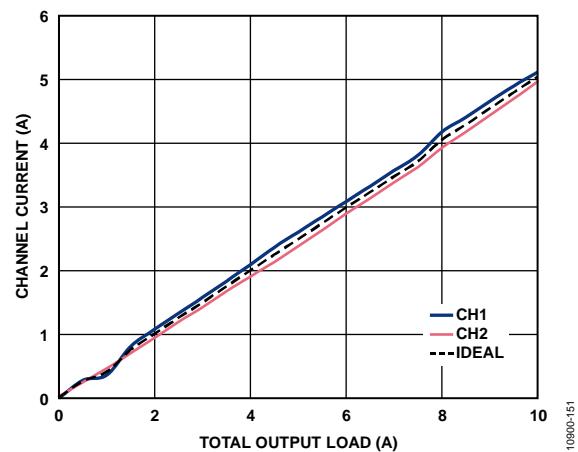

並列動作時の各チャンネルの電流バランスは、内部の制御ループによって自動調整されます。図 45 に、並列動作時の各チャンネルの代表的な電流バランスのマッチング特性を示します。

図 45. 並列動作構成時の電流バランス特性  $V_{IN} = 12\text{ V}$ 、 $V_{OUT} = 1.2\text{ V}$ 、 $f_{SW} = 600\text{ kHz}$ 、FPWM モード

## 出力に残存電圧があった場合のスタートアップ

ADP5052 の降圧スイッチング・レギュレータは、スタートアップ時にローサイド FET の破損を防ぐ為、充電された出力に対する (安全な) スタートアップ機能を備えています。レギュレータがオンになる前に、出力端子のコンデンサに電荷が残っていた場合、レギュレータは、逆向きの電流がインダクタに流れるのを防ぎます。逆電流を防ぐ期間は、ソフト・スタート用に設定された内部基準電圧が、充電された出力電圧によって生じる、フィードバック (FBx) ピンに与えられた電圧を超えるまでです。

## 電流制限保護機能

ADP5052 の降圧スイッチング・レギュレータ、ハイサイド MOSFET に流れる正電流の総量を制限する、電流制限保護機能を備えています。パワー・スイッチのピーク電流制限機能が、入力から出力へと流れる電流の総量を制限します。プログラマブルな電流制限スレッショールド設定機能を有しているので、小型インダクタを使った小電力アプリケーションにも対応できます。

チャンネル 1 用の電流制限スレッショールドを決めるには、DL1 ピンとグラウンド間に抵抗を接続して下さい。チャンネル 2 用の電流制限スレッショールドを決めるには、DL2 ピンとグラウンド間に、先ほどとは別の抵抗を接続して下さい。表 10 にチャンネル 1 とチャンネル 2 用の、電流制限スレッショールドを設定する為の抵抗値一覧を示します。

表 10. チャンネル 1 とチャンネル 2 のピーク電流制限スレッショールド設定

| R <sub>ILIM1</sub> または R <sub>ILIM2</sub> | 代表的なピーク電流制限スレッショールド |

|-------------------------------------------|---------------------|

| フローティング                                   | 4.4 A               |

| 47kΩ                                      | 2.63 A              |

| 22kΩ                                      | 6.44 A              |

ADP5052 の降圧スイッチング・レギュレータは、負電流制限保護回路も備えており、ローサイド MOSFET に流れる負電流を、ある電流値で制限します。

## 周波数フォールドバック

ADP5052 の降圧スイッチング・レギュレータは、出力が短絡したとき、出力電流が制御不能にならないように周波数フォールドバック機能を備えています。周波数フォールドバック機能は、以下の様にして実現されています：

- FBx ピンの端子電圧が、設定した電圧の半分の値まで下降した場合、スイッチング周波数が半分になります。

- FBx ピンの端子電圧が、設定した電圧の 4 分の 1 まで下降した場合、出力電流が半分になるようにスイッチング周波数を下げます。この時、スイッチング周波数  $f_{sw}$  は 4 分の 1 になります。

スイッチング周波数を下げることで、インダクタに流れる電流を下げるための時間が長くなり、同時にピーク電流レギュレーションを行っている間の電流リップルが大きくなります。この結果、平均電流を下げることができ、出力電流が制御不能になることを防ぎます。

## 最大デューティー・サイクル下のパルス・スキップ・モード

最大デューティー・サイクル下では、周波数フォールドバック機能によってレギュレーション状態を保ちます。例えば入力電圧が低下して、最大デューティー・サイクル状態に到達した場合、PWM 変調器は PWM パルスを 1 つずつ飛ばしてゆきます。その結果、周波数フォールドバックのスイッチング周波数は半分になります。さらにデューティー・サイクルが大きくなると、PWM 変調器は、PWM パルスを 2 つおきに飛ばして行きます。その結果、周波数フォールドバックのスイッチング周波数は 3 分の 1 になります。周波数フォールドバックは、有効最大デューティー・サイクルを大きくできます。それにより入力電圧と出力電圧とのドロップアウト電圧を下げることができます。

## 瞬断による過負荷保護

ADP5052 の降圧スイッチング・レギュレータは、過電流保護 (OCP) のため、瞬断モードを備えています。インダクタに流れる電流が、電流制限スレッショルドに到達すると、ハイサイド MOSFET はオフになります、ローサイド MOSFET は、次のスイッチングサイクルまでオフになります。

瞬断モードが動作状態で上記の現象が発生すると、過電流フォールト・カウンタの値が 1 つ増加します。もし過電流フォールト・カウンタの値が 15 かそれ以上になると、出力短絡状態であると見なされ、ハイサイドとローサイドの MOSFET の両方がオフになります。降圧スイッチング・レギュレータは、ソフト・スタートサイクルの 7 周期分に相当する期間、瞬断モードを維持します。その後ソフト・スタートを行ってリセットを試みます。出力短絡フォールト・カウンタがクリアされると、レギュレータが通常動作に復帰しますが、復帰出来ない場合、ソフト・スタート後も再度瞬断モードになります。

重い負荷が接続された状態では、最初のソフト・スタート期間のみ、瞬断による過負荷保護機能は動作せず、降圧スイッチング・レギュレータの動作できるようにします。重い負荷が接続された状態で瞬断モードから降圧スイッチング・レギュレータを確実に復帰させるには、細心の回路設計と適切な部品選択が必要であることに注意して下さい。4 つの降圧スイッチング・レギュレータ全ての瞬断モードのイネーブル/ディスエーブルは、工場でのヒューズ調整によって行う事ができます。瞬断モードがディスエーブルであっても、周波数フォールドバック機能が過電流保護として機能します。

## ラッチオフによる保護

ADP5052 の降圧スイッチング・レギュレータは、深刻な問題、例えば出力短絡や過電圧状態からデバイスを保護するため、オプションでラッチオフ・モードを持たせることができます。ラッチオフ・モードは、工場でのヒューズ調整でイネーブルにできます。

### 短絡ラッチオフ・モード

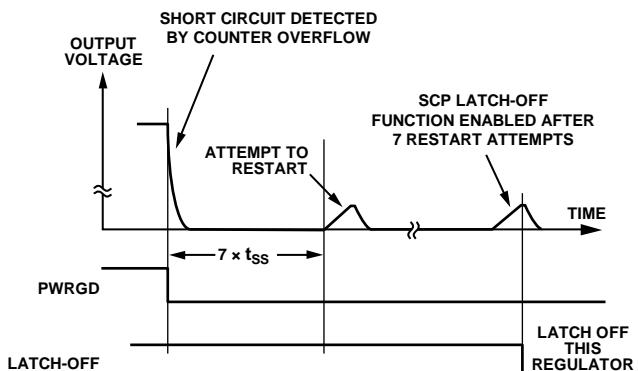

短絡ラッチオフ・モードは、工場でのヒューズ調整でイネーブルにできます。この時、4 つの降圧スイッチング・レギュレータに対して、全てオンにするかオフにするか、の選択になります。出力短絡ラッチオフ・モードがイネーブルであれば、ソフト・スタート後、保護回路が過剰な電流を検知した時、降圧スイッチング・レギュレータは瞬断モードに入り、リスタートを試みます。7 周期後でリスタートを試みた後、レギュレータのフォールト状態が続いている場合、レギュレータはシャット・ダウンします。このシャット・ダウン (ラッチオフ) 状態は、チャンネルが再びイネーブルになるか、チャンネルの電力供給が再開される事によってのみ、解除されます。出力短絡 (保護用) ラッチオフ・モードは、瞬断モードがディスエーブルでは動作しません。

図 46 に、短絡保護用ラッチオフ検知機能を示します。

図 46. 短絡ラッチオフ検出

### 過電圧ラッチオフ・モード

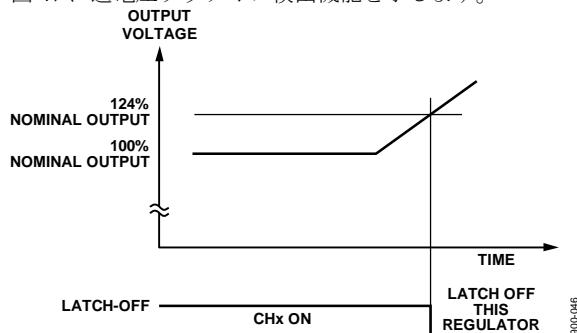

過電圧ラッチオフ・モードは、工場でのヒューズ調整でイネーブルにできます。この時、4 つの降圧スイッチング・レギュレータに対して、全てオンにするかオフにするか、の選択になります。過電圧ラッチオフ・モードの動作スレッショールドは、公称出力電圧の 124% に設定されます。出力電圧がこのスレッショールド電圧を超えると、保護回路が過電圧状態を検知し、レギュレータをシャット・ダウンさせます。このシャット・ダウン (ラッチオフ) 状態は、チャンネルが再びイネーブルになるか、チャンネルの電力供給が再開される事によってのみ、解除されます。

図 47 に過電圧ラッチオフ検出機能を示します。

図 47. 過電圧ラッチオフ検出

## 低電圧ロックアウト (UVLO)

低電圧ロックアウト回路は、ADP5052 内の各降圧スイッチング・レギュレータへの入力電圧を監視します。いずれかの入力端子 (PVIN1x) の電圧が 3.78V (代表値) を下回った場合、該当するチャンネルはオフ状態になります。入力電圧が 4.2V (代表値) にまで上昇すると、ソフト・スタート周期が起動し、ENx ピンがハイになった時に該当チャンネルがイネーブルになります。

チャンネル1 (PVIN1) のUVLO状態は、他のチャンネルの状態に比べて優先度が高く、他のチャンネルが動作する前に、PVIN1に電圧を与えるなければいけないことに注意して下さい。

## パワーグッド機能

ADP5052 は、オープンドレインのパワーグッド出力 (PWRGD ピン) を備えており、選択された降圧スイッチング・レギュレータが正常動作している時に、アクティブ・ハイとなります。デフォルトで、PWRGD ピンは、チャンネル 1 の出力電圧を監視しています。他のチャンネルに対しての、PWRGD ピンによる監視機能に関しては、ADP5052 の注文時に構成できます (詳細は表 20 参照)。

該当するチャンネルの公称出力電圧の 90.5% (代表値) 以上であれば、PWRGD ピンがロジック・ハイの状態になります。降圧スイッチング・レギュレータの出力電圧が、公称電圧の 87.2% (代表値) を下回り、その状態がおよそ 50 $\mu$ s 以上続いた場合、PWRGD ピンはロー状態になります。

PWRGD ピンの出力は、内部の PWRGD<sub>x</sub> 信号の論理和です。PWRGD ピンがハイになる前に、内部の PWRGD<sub>x</sub> 信号は 1ms の検証時間を必要としますが、1 つでも PWRGD<sub>x</sub> 信号がローになれば、PWRGD ピンの出力は遅滞なくローになります。チャンネル 1 からチャンネル 4 のうち、どのチャンネルの組み合わせによって PWRGD ピンを制御するのかは、工場でのヒューズ調整によって構成できます。デフォルトの PWRGD ピンの設定は、チャンネル 1 の出力の監視です。

## サーマル・シャットダウン

もし ADP5052 の接合温度が、150°C を超えた場合、サーマル・シャットダウン回路が、内部のリニア・レギュレータ以外の機能全てをオフにします。大電流動作や、不適切な回路基板設計、もしくは高い周囲温度によって、極端な接合温度の上昇を引き起します。サーマル・シャットダウン回路には、15°C のヒステリシスが設けられており、ADP5052 は、オンチップ温度が 135°C 以下にならないと、通常動作に復帰しません。サーマル・シャットダウンからデバイスが復帰すると、イネーブルになっている各チャンネルのソフト・スタートが起動します。

## LDO レギュレータ

ADP5052 には、低静止電流と低ドロップ・アウト電流を備えた、汎用 LDO レギュレータが内蔵されています。この LDO レギュレータは、最大で 200mA の電流容量があります。

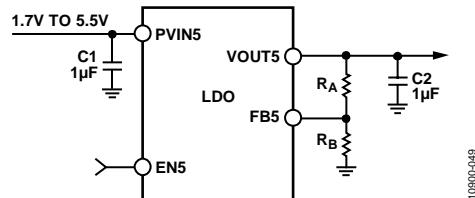

LDO レギュレータは、1.7V から 5.5V の入力電圧で動作します。入力電圧範囲が広いので、このデバイス内の降圧スイッチング・レギュレータのうち 1つから電圧を供給し、カスケード構成で動作させることができます。LDO の出力電圧は、外部の抵抗分圧回路によって設定できます（図 48 参照）。

図 48. 200mA の LDO レギュレータ

この LDO レギュレータは、優れた電源電圧変動除去比 (PSRR) を持っているので、入力と出力に小型  $1\mu\text{F}$  のセラミック・コンデンサを取り付けるだけで、ラインと負荷の変動があっても、優れた過渡応答特性を示します。

## アプリケーション情報

### ADIsimPower™ デザイン・ツール

ADP5052 は ADIsimPower™ デザイン・ツール・セットでの設計サポートに対応しています。ADIsimPower は、電源回路設計を行うためのツールを集めたソフトウェアで、設計目標に対して最適化された回路設計ができます。このソフトウェア・ツールを使えば、必要な回路図と部品表の作成ができ、その回路特性を瞬時に計算できます。ADIsimPower を使えば、IC の動作条件と外部部品の制約を考慮しながら、コスト、プリント基板上での専有面積と部品数を最適化できます。

ADIsimPower は、[www.analog.com/ADIsimPower](http://www.analog.com/ADIsimPower) から入手できます。また、このツール経由で、部品未実装ボードのリクエストができます。

### 可変出力電圧のプログラミング

ADP5052 の出力電圧の設定は、その出力電圧を外部に取り付けた抵抗で分圧し、分圧電圧を FBx ピンに接続することで行います。フィードバック・ピンのバイアス電流によって起こる出力電圧精度の低下を防ぐ為、分圧回路下側の抵抗値は、大きな値を選ばないようにして下さい。50kΩ 以下を推奨します。

出力電圧は、以下の式で設定できます。

$$V_{OUT} = V_{REF} \times (1 + (R_{TOP}/R_{BOT}))$$

ここで、

$V_{OUT}$  は、出力電圧

$V_{REF}$  は、フィードバック基準電圧：チャンネル 1 からチャンネル 4 は 0.8V。チャンネル 5 は 0.5V

$R_{TOP}$  は、 $V_{OUT}$  から FB に接続するフィードバック抵抗の値

$R_{BOT}$  は、FB からグラウンドに接続するフィードバック抵抗値

固定出力電圧オプションを選択している場合、抵抗分圧回路は必要ありません。オプションに無い固定出力電圧が必要であれば、アナログ・デバイセズの担当営業、もしくは代理店までご相談下さい。

### 電圧変換の制限

与えられた入力電圧によっては、最小オン時間と、最小オフ時間に制限があるため、出力電圧の上限と下限が存在します。

与えられた入力電圧に対する最小出力電圧とスイッチング周波数は、最小オン時間によって制限されます。チャンネル 1 とチャンネル 2 の最小オン時間は、117ns (代表値) で、チャンネル 3 とチャンネル 4 の最小オン時間は、90ns (代表値) です。接合温度が上昇すると、最小オン時間は長くなります。

チャンネル 1 とチャンネル 2 を強制 PWM モードで動作させると、最小オン時間の制限を超える、公称出力電圧が上昇する可能性があります。この問題を避けるため、スイッチング周波数を慎重に選択しなければなりません。

電流連続モード (CCM) で動作させる場合、与えられた入力電圧とスイッチング周波数での最小出力電圧は、以下の式で計算することができます。

$$V_{OUT\_MIN} = V_{IN} \times t_{MIN\_ON} \times f_{SW} - (R_{DS0N1} - R_{DS0N2}) \times I_{OUT\_MIN} \times t_{MIN\_ON} \times f_{SW} - (R_{DS0N2} + R_L) \times I_{OUT\_MIN} \quad (1)$$

ここで、

$V_{OUT\_MIN}$  は、最小出力電圧

$t_{MIN\_ON}$  は、最小オン時間

$f_{SW}$  は、スイッチング周波数

$R_{DS0N1}$  は、ハイサイド MOSFET のオン抵抗

$R_{DS0N2}$  は、ローサイド MOSFET のオン抵抗

$I_{OUT\_MIN}$  は、最小出力電流

$R_L$  は、出力インダクタの抵抗値

与えられた入力電圧とスイッチング周波数での最大出力電圧は、最小オフ時間と最大デューティー・サイクルによって制限されます。周波数フォールドバック機能がスイッチング周波数を低下させて、有効最大デューティー・サイクルの増加を手助けします。このため、入力電圧と出力電圧間のドロップアウト電圧を低くできます (詳細は、周波数フォールドバックセクション参照)。

与えられた入力電圧とスイッチング周波数での最大出力電圧は、以下の式で計算できます。

$$V_{OUT\_MAX} = V_{IN} \times (1 - t_{MIN\_OFF} \times f_{SW}) - (R_{DS0N1} - R_{DS0N2}) \times I_{OUT\_MAX} \times (1 - t_{MIN\_OFF} \times f_{SW}) - (R_{DS0N2} + R_L) \times I_{OUT\_MAX} \quad (2)$$

ここで、

$V_{OUT\_MAX}$  は、最大出力電圧

$t_{MIN\_OFF}$  は、最小オフ時間

$f_{SW}$  は、スイッチング周波数

$R_{DS0N1}$  は、ハイサイド MOSFET のオン抵抗

$R_{DS0N2}$  は、ローサイド MOSFET のオン抵抗

$I_{OUT\_MAX}$  は、最大出力電流

$R_L$  は、出力インダクタの抵抗値

式 1 と式 2 に示したように、スイッチング周波数を下げると、最小オン時間と最小オフ時間の制限を緩和できます。

### 電流制限の設定

ADP5052 のチャンネル 1 とチャンネル 2 は、3 つの電流制限レッショールドを選択できます。電流制限値を選択するとき、インダクタのピーク電流  $I_{PEAK}$  を超えないように注意して下さい。チャンネル 1 とチャンネル 2 の電流制限値の一覧を表 10 に示します。

## ソフト・スタートの設定

ADP5052 の降圧スイッチング・レギュレータは、ソフト・スタート回路を搭載しています。この回路によってスタートアップ時、出力電圧の上昇を制御することができ、それによって突入電流を制限します。ソフト・スタートの時間を 2 ms、4 ms または 8 ms に設定するには、SS12 または SS34 ピン、VREG ピンとグラウンド間に分圧抵抗を接続して下さい（ソフト・スタートセクション参照）。

## インダクタの選択

インダクタの値は、スイッチング周波数、入力電圧、出力電圧、そしてインダクタ・リップル電流によって決まります。インダクタの値が小さいと、高速な過渡応答を得られますが、大きなインダクタ・リップル電流により効率が低下します。インダクタの値が大きいと、リップル電流が小さくなり効率も改善しますが、結果として過渡応答が低速になります。従って、過渡応答と効率との間で妥協点を見いだす必要があります。ガイドラインとして、インダクタ・リップル電流  $\Delta I_L$  は、通常最大負荷電流の 30%から 50%程度に設定します。インダクタの値は次式で計算することができます。

$$L = [(V_{IN} - V_{OUT}) \times D] / (\Delta I_L \times f_{SW})$$

ここで、

$V_{IN}$  は入力電圧。

$V_{OUT}$  は出力電圧

$D$  は、デューティー・サイクル ( $D = V_{OUT}/V_{IN}$ )。

$\Delta I_L$  はインダクタ・リップル電流

$f_{SW}$  は、スイッチング周波数

ADP5052 は、内部の電流ループ内にスロープ補償回路を備えており、50%より大きなデューティー・サイクルになった時のサブハーモニック発振が起きないようになっています。

最大インダクタ電流は、以下の式を用いて計算して下さい。

$$I_{PEAK} = I_{OUT} + (\Delta I_L/2)$$

インダクタの飽和電流は、最大インダクタ電流よりも大きくなければなりません。高速飽和特性を持つフェライト・コアを使ったインダクタの場合、インダクタが飽和してしまうのを防ぐ為、そのインダクタの定格飽和電流が、降圧スイッチング・レギュレータの電流制限スレッショールドよりも大きいことを確認して下さい。

インダクタに流れる rms 電流値は次式で計算することができます。

$$I_{RMS} = \sqrt{I_{OUT}^2 + \frac{\Delta I_L^2}{12}}$$

シールドされたフェライト・コア材料は、コアの損失と EMI を低く抑えることができ、推奨できます。表 11 に推奨するインダクタの一覧を示します。

| ベンダー | 製品番号        | 値(μH) | $I_{SAT}$ (A) | $I_{RMS}$ (A) | DCR(mΩ) | サイズ       |

|------|-------------|-------|---------------|---------------|---------|-----------|

|      | XFL4020-472 | 4.7   | 2.7           | 5.0           | 52.2    | 4 × 4     |

|      | XAL4030-682 | 6.8   | 3.6           | 3.9           | 67.4    | 4 × 4     |

|      | XAL4040-103 | 10    | 3.0           | 3.1           | 84      | 4 × 4     |

|      | XAL6030-102 | 1.0   | 23            | 18            | 5.62    | 6 × 6     |

|      | XAL6030-222 | 2.2   | 15.9          | 10            | 12.7    | 6 × 6     |

|      | XAL6030-332 | 3.3   | 12.2          | 8.0           | 19.92   | 6 × 6     |

|      | XAL6060-472 | 4.7   | 10.5          | 11            | 14.4    | 6 × 6     |

|      | XAL6060-682 | 6.8   | 9.2           | 9.0           | 18.9    | 6 × 6     |

| TOKO | FDV0530-1R0 | 1.0   | 11.2          | 9.1           | 9.4     | 6.2 × 5.8 |

|      | FDV0530-2R2 | 2.2   | 7.1           | 7.0           | 17.3    | 6.2 × 5.8 |

|      | FDV0530-3R3 | 3.3   | 5.5           | 5.3           | 29.6    | 6.2 × 5.8 |

|      | FDV0530-4R7 | 4.7   | 4.6           | 4.2           | 46.6    | 6.2 × 5.8 |

## 出力コンデンサの選択

出力コンデンサは、電圧リップルとレギュレータの動的ループ特性の両方に影響を与えます。例えば、負荷がステップ状に遷移したり、負荷が突然重くなったりすると、制御ループがインダクタに十分な電流を流せるようになるまで、出力コンデンサは負荷に対して電流供給をしなければなりません。これにより、出力電圧にアンダーシュートが発生します。

要求されるアンダーシュート（電圧ドロップ）仕様を満たすために必要な出力コンデンサの値は、以下の式を使って計算できます。

$$C_{OUT\_UV} = \frac{K_{UV} \times \Delta I_{STEP}^2 \times L}{2 \times (V_{IN} - V_{OUT}) \times \Delta V_{OUT\_UV}}$$

ここで、

$K_{UV}$  は、係数（通常 2 に設定）

$\Delta I_{STEP}$  は、負荷ステップ

$\Delta V_{OUT\_UV}$  は、出力電圧の許容されるアンダーシュートの値

出力コンデンサの値が、レギュレータの動的ループ特性に影響を与えるもう一つの例は、負荷が突然出力から取り外され、インダクタに蓄えられたエネルギーが一気に出力コンデンサに流れ込む場合です。この時、出力電圧にオーバーシュートが発生します。

要求されるオーバーシュート仕様を満たすために必要な出力コンデンサの値は、以下の式を使って計算できます。

$$C_{OUT\_OV} = \frac{K_{OV} \times \Delta I_{STEP}^2 \times L}{(V_{OUT} + \Delta V_{OUT\_OV})^2 - V_{OUT}^2}$$

ここで、

$K_{OV}$  は、係数（通常 2 に設定）

$\Delta I_{STEP}$  は、負荷ステップ

$\Delta V_{OUT\_OV}$  は、出力電圧の許容されるオーバーシュートの値

表 11. 推奨インダクタ

| ベンダー      | 製品番号        | 値(μH) | $I_{SAT}$ (A) | $I_{RMS}$ (A) | DCR(mΩ) | サイズ   |

|-----------|-------------|-------|---------------|---------------|---------|-------|

| Coilcraft | XFL4020-102 | 1.0   | 5.4           | 11            | 10.8    | 4 × 4 |

|           | XFL4020-222 | 2.2   | 3.7           | 8.0           | 21.35   | 4 × 4 |

|           | XFL4020-332 | 3.3   | 2.9           | 5.2           | 34.8    | 4 × 4 |

出力電圧の電圧リップルは、出力コンデンサの ESR とそのコンデンサの値によって決まります。要求される出力電圧リップルを満たすコンデンサを選択するには、以下の式を用いて下さい。

$$C_{OUT\_RIPPLE} = \frac{\Delta I_L}{8 \times f_{SW} \times \Delta V_{OUT\_RIPPLE}}$$

$$R_{ESR} = \frac{\Delta V_{OUT\_RIPPLE}}{\Delta I_L}$$

ここで、

$\Delta I_L$  は、インダクタ・リップル電流

$f_{SW}$  は、スイッチング周波数

$\Delta V_{OUT\_RIPPLE}$  は、許容される出力電圧リップル値

$R_{ESR}$  は出力コンデンサの等価直列抵抗値

要求されるトランジエント特性と出力リップル特性を満足するよう、出力コンデンサの値、 $C_{OUT\_UV}$ 、 $C_{OUT\_OV}$ 、 $C_{OUT\_RIPPLE}$  はなるべく大きい値を選んで下さい。

選択したコンデンサの定格電圧は、出力電圧より高いものを選んで下さい。なお、出力コンデンサに流れる最小電流実効値の定格は、以下の式で決まります。

$$I_{C_{OUT\_rms}} = \frac{\Delta I_L}{\sqrt{12}}$$

### 入力コンデンサの選択

入力のデカッピング・コンデンサは、入力に含まれる高周波ノイズを低減し、電力を蓄える役割も果たします。セラミック・コンデンサを用い、必ず PVINx ピンのできるだけ近くに配置して下さい。入力コンデンサ、ハイサイド NFET、ローサイド NFET で形成されるループができるだけ小さくなるよう、部品を配置して下さい。入力コンデンサの定格電圧は、最大入力電圧よりも高くなればなりません。入力コンデンサの電流実効値の定格は、以下の式できる値より大きいことを確認して下さい。

$$I_{C_{IN\_rms}} = I_{OUT} \times \sqrt{D \times (1-D)}$$

ここで  $D$  は、デューティー・サイクル ( $D = V_{OUT}/V_{IN}$ ) です。

### ローサイド・パワー・デバイスの選択

チャンネル 1 とチャンネル 2 は、ローサイド MOSFET のドライバを内蔵しています。このドライバは、外付けのローサイド N チャンネル MOSTFET (NFET) を駆動します。この N チャンネル MOSFET の選択は、降圧スイッチング・レギュレータの性能に大きく影響を与えます。

MOSFET を選択する際、以下を満足するようにして下さい：

- ドレイン・ソース電圧は ( $V_{DS}$ ) は、 $1.2 \times V_{IN}$  より高いものを選んで下さい。

- ドレイン電流 ( $I_D$ ) は  $1.2 \times I_{LIMIT\_MAX}$  より大きいものを選んで下さい。ここで  $I_{LIMIT\_MAX}$  は、設計時に選んだ、最大電流制限スレッショールド値です。

- $V_{GS} = 4.5$  V で完全にオンになる MOSFET を選択して下さい。

- 全ゲート電荷量 ( $Q_g$  at  $V_{GS} = 4.5$  V) は、20nC 以下であることも必要です。 $Q_g$  特性が低いと、レギュレータの効率が高くなります。

ハイサイド MOSFET がオフになると、ローサイド MOSFET がインダクタに電流を供給します。低いデューティー・サイクルで動作するアプリケーションの場合、ローサイド MOSFET がより長い期間、電流を供給しなければなりません。高い効率を実現するためには、低いオン抵抗を持つ MOSFET をローサイド MOSFET として選択して下さい。ローサイド MOSFET の導通電力損失は、以下の式で計算できます：

$$P_{FET\_LOW} = I_{OUT}^2 \times R_{DSON} \times (1 - D)$$

ここで、

$R_{DSON}$  は、ローサイド MOSFET のオン抵抗

$D$  は、デューティー・サイクル ( $D = V_{OUT}/V_{IN}$ )。

表 12 に、各種電流制限設定において推奨される、デュアル MOSFET の一覧を示します。MOSFET 選択時、その MOSFET が電力損失による熱消費に耐えられるものを選んで下さい。

表 12. 推奨デュアル MOSFET

| ベンダー      | 製品番号      | $V_{DS}$ (V) | $I_D$ (A) | $R_{DSON}$ (mΩ) | $Q_g$ (nC) | サイズ   |

|-----------|-----------|--------------|-----------|-----------------|------------|-------|

| IR        | IRFHM8363 | 30           | 10        | 20.4            | 6.7        | 3 x 3 |

|           | IRLHS6276 | 20           | 3.4       | 45              | 3.1        | 2 x 2 |

| Fairchild | FDMA1024  | 20           | 5.0       | 54              | 5.2        | 2 x 2 |

|           | FDMDB3900 | 25           | 7.0       | 33              | 11         | 3 x 2 |

|           | FDMDB3800 | 30           | 4.8       | 51              | 4          | 3 x 2 |

|           | FDC6401   | 20           | 3.0       | 70              | 3.3        | 3 x 3 |

| Vishay    | Si7228DN  | 30           | 23        | 25              | 4.1        | 3 x 3 |

|           | Si7232DN  | 20           | 25        | 16.4            | 12         | 3 x 3 |

|           | Si7904BDN | 20           | 6         | 30              | 9          | 3 x 3 |

|           | Si5906DU  | 30           | 6         | 40              | 8          | 3 x 2 |

|           | Si5908DC  | 20           | 5.9       | 40              | 5          | 3 x 2 |

|           | SiA906EDJ | 20           | 4.5       | 46              | 3.5        | 2 x 2 |

| AOS       | AON7804   | 30           | 22        | 26              | 7.5        | 3 x 3 |

|           | AON7826   | 20           | 22        | 26              | 6          | 3 x 3 |

|           | AO6800    | 30           | 3.4       | 70              | 4.7        | 3 x 3 |

|           | AON2800   | 20           | 4.5       | 47              | 4.1        | 2 x 2 |

### UVLO 入力のプログラミング

高精度イネーブル入力は、図 38 に示すように、入力電圧の UVLO のスレッショールドをプログラムするために使うこともできます。内部  $1\text{M}\Omega$  のプルダウン抵抗の誤差によって引き起こされる入力電圧の精度低下を防ぐため、分圧回路下側の抵抗値が、非常に大きな値にならないか確認して下さい。抵抗値は、 $50\text{k}\Omega$  以下を推奨します。

高精度ターンオン・スレッショールド値は、0.8V です。 $V_{IN}$  start-up 電圧を、抵抗による分圧回路によって計算する場合、以下の式を用いて下さい。

$$V_{IN\_STARTUP} = (0.8 \text{ nA} + (0.8 \text{ V}/R_{BOT\_EN})) \times (R_{TOP\_EN} + R_{BOT\_EN})$$

ここで、

$R_{TOP\_EN}$  は、 $V_{IN}$  と EN 間に接続する抵抗

$R_{BOT\_EN}$  は、EN とグラウンド間に接続する抵抗

## 補償用部品値の計算

ピーク電流モード制御アーキテクチャの場合、電力段は、出力コンデンサと負荷抵抗に対して電流を供給する、電圧制御型電流源として簡略化できます。簡略化されたループには、1つのポールと、出力コンデンサの ESR によってできる 1 つのゼロができます。制御入力から出力への伝達関数は、以下の式で表されます。

$$G_{vd}(s) = \frac{V_{OUT}(s)}{V_{COMP}(s)} = A_{VI} \times R \times \frac{\left(1 + \frac{s}{2\pi \times f_z}\right)}{\left(1 + \frac{s}{2\pi \times f_p}\right)}$$

$$f_z = \frac{1}{2\pi \times R_{ESR} \times C_{OUT}}$$

$$f_p = \frac{1}{2\pi \times (R + R_{ESR}) \times C_{OUT}}$$

ここで、

$A_{VI} = 10 \text{ A/V}$  (チャンネル 1 またはチャンネル 2) もしくは、 $3.33 \text{ A/V}$  (チャンネル 3 またはチャンネル 4)

$R$  は、負荷抵抗

$R_{ESR}$  は、出力コンデンサの等価直列抵抗

$C_{OUT}$  は、出力コンデンサ

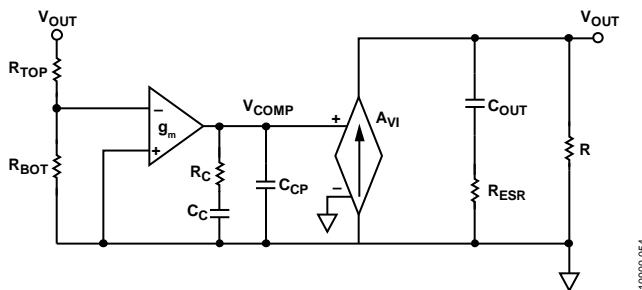

ADP5052 は、システム補償用の誤差増幅器として、トランスクンダクタンス増幅器を使っています。図 49 に、ピーク電流モード制御の小信号等価回路を示します。

図 49. ピーク電流モード制御の小信号等価回路

補償部品は  $R_C$  と  $C_C$  で、ゼロに対する寄与があります。 $R_C$  と、オプションの  $C_{CP}$  は、ポールに対する寄与があります。

クローズド・ループの伝達関数式は、以下の様になります。

$$T_V(s) = \frac{R_{BOT}}{R_{BOT} + R_{TOP}} \times \frac{-g_m}{C_C + C_{CP}} \times \frac{1 + R_C \times C_C \times s}{s \times \left(1 + \frac{R_C \times C_C \times C_{CP} \times s}{C_C + C_{CP}}\right)} \times G_{vd}(s)$$