## 特長

入力電圧範囲: 2.75 V~20 V

出力電圧範囲: 0.6 V~90%  $V_{IN}$

最大出力電流: 25 A 以上

電流モード・アーキテクチャ

電圧モードへ設定可能

全温度範囲での出力電圧精度:  $\pm 1\%$

電圧トラッキング

設定可能な周波数: 200 kHz~1.5 MHz

外部周波数同期入力

軽負荷での省電力モード

高精度イネーブル入力

ブルアップ抵抗内蔵のパワーグッド

調整可能なソフトスタート

プログラマブルな電流検出ゲイン

ブーストストラップ・ダイオードを内蔵

プリチャージ負荷でのスタートアップ

外部調整可能なスロープ補償

任意の出力コンデンサに対応

過電圧保護と過電流制限保護

熱過負荷保護機能

入力低電圧ロックアウト(UVLO)

16 ピンの 4 mm × 4 mm LFCSP パッケージ

ADIsimPower デザイン・ツールのサポート

## アプリケーション

シーケンシングとトラッキングを必要とする次のような中間バス・システムと POL システム

## 通信基地局とネットワーク 工業用および計装機器 医用および健康管理

## 概要

**ADP1851** は、一般的な 3.3 V~12 V (最大 20 V)の電圧入力で動作できる広い入力範囲を持つ DC/DC 同期整流降圧コントローラです。このデバイスは、デジタル負荷に対して高速なステップ応答を提供する谷電流検出による電流モードで動作します。このデバイスは、敏感な負荷に対して低ノイズと低クロストークで動作する電圧モード・コントローラとして構成することもできます。

**ADP1851** は、複数の出力電圧を必要とするシステム・アプリケーションに最適です。**ADP1851** は、スイッチング・デバイス間のビート周波数をなくする外部周波数同期機能を内蔵しています。また、電源間の正確なトラッキング機能も提供し、シンプルで強固なシーケンシングを可能にする高精度なイネーブル機能とパワーグッド機能を内蔵しています。

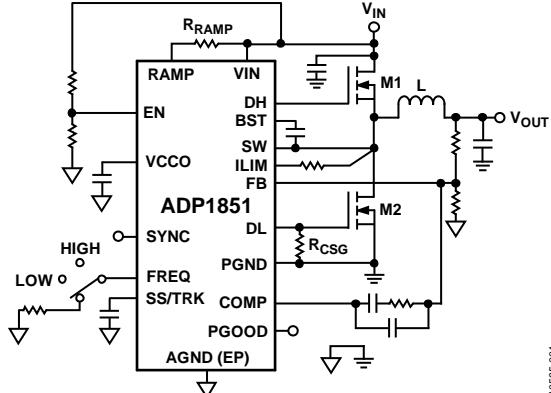

## 代表的な動作回路

四 1.

**ADP1851** は、高効率電力変換を可能にする高速で高ピーク電流のゲート駆動機能を提供します。このデバイスは、パルスをスキップして、スイッチング損失を削減し、軽い負荷とスタンバイ状態で効率を改善する省電力モードで動作するように設定することができます。

正確な電流制限機能により、狭い範囲の許容誤差内のデザインが可能になり、コンバータ全体を小型化し、コストを削減することができます。**ADP1851** は、 $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  の温度範囲で  $\pm 1\%$  許容誤差の高精度リファレンスを使って最小 0.6 V 出力までレギュレーションすることができます。

**ADP1851** は広い範囲の入力電圧を持つため、多様なシステム構成で最大の柔軟性を提供します。ループ補償、ソフトスタート、周波数設定、省電力モード、電流制限、電流検出ゲインはすべて、外付け部品を使って設定することができます。さらに、外付け **RAMP** 抵抗を使用すると、電流モードと電圧モードで最適なスロープと  $V_{IN}$  フィード・フォワードを選択して優れたライン除去比を実現することができます。ハイサイド・ドライバ用のリニア・レギュレータとブートストラップ・ダイオードを内蔵しています。

保護機能としては、低電圧ロックアウト、過電圧、過電流／短絡、温度上昇に対する保護機能を内蔵しています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。

※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                         |    |

|-------------------------|----|

| 特長                      | 1  |

| アプリケーション                | 1  |

| 概要                      | 1  |

| 代表的な動作回路                | 1  |

| 改訂履歴                    | 2  |

| 簡略化したブロック図              | 3  |

| 仕様                      | 4  |

| 絶対最大定格                  | 6  |

| ESD の注意                 | 6  |

| ピン配置およびピン機能説明           | 7  |

| 代表的な性能特性                | 9  |

| 動作原理                    | 11 |

| 制御アーキテクチャ               | 11 |

| 発振周波数                   | 11 |

| 外部周波数同期                 | 12 |

| PWM 動作モードとパルス・スキップ動作モード | 12 |

| 同期整流ダイオードとデッド・タイム       | 13 |

| 入力低電圧ロックアウト             | 13 |

| 内蔵のリニア・レギュレータ           | 13 |

| 過電圧保護機能                 | 13 |

| パワーグッド                  | 13 |

| 短絡保護機能と電流制限機能           | 14 |

|                        |    |

|------------------------|----|

| イネーブル／ディスエーブル制御        | 14 |

| 熱過負荷保護機能               | 14 |

| アプリケーション情報             | 15 |

| ADIsimPower デザイン・ツール   | 15 |

| 出力電圧の設定                | 15 |

| ソフトスタート                | 15 |

| 電流制限値の設定               | 15 |

| 電流制限の正確な検出             | 15 |

| 入力コンデンサの選択             | 15 |

| VIN ピン・フィルタ            | 16 |

| ブースト・コンデンサの選択          | 16 |

| インダクタの選択               | 16 |

| 出力コンデンサの選択             | 16 |

| MOSFET の選択             | 17 |

| ループ補償—電圧モード            | 18 |

| ループ補償—電流モード            | 19 |

| スイッチング・ノイズとオーバーシュートの削減 | 20 |

| 電圧のトラッキング              | 21 |

| PCB レイアウトのガイドライン       | 21 |

| 代表的な動作回路               | 22 |

| 外形寸法                   | 23 |

| オーダー・ガイド               | 23 |

## 改訂履歴

8/12—Revision 0: Initial Version

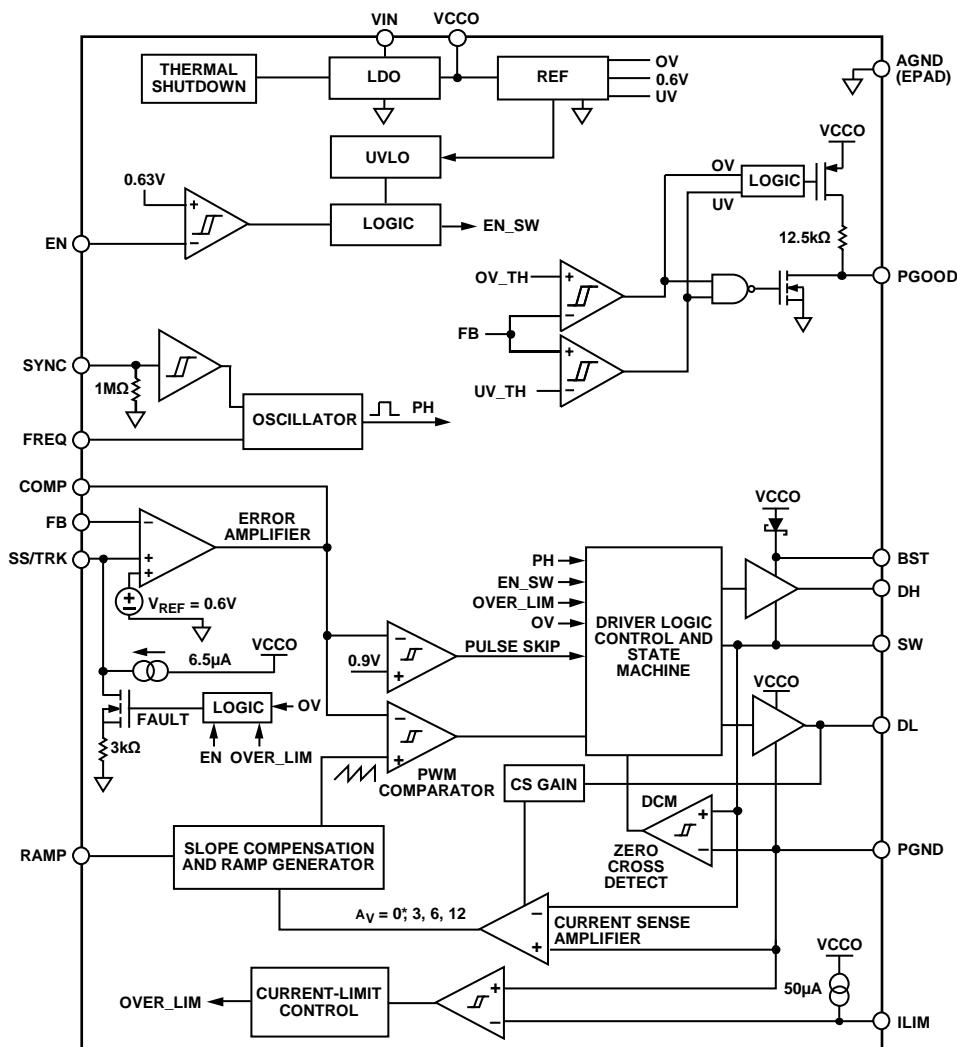

## 簡略化したブロック図

10595-02

図 2. 簡略化したブロック図

## 仕様

温度限界におけるすべての規定値、 $T_{JMIN}$ 、 $T_{JMAX}$  は、標準の統計的品質管理手法(SQC)を使う相関により保証。 $V_{IN} = 12$  V。特に指定がない限り、仕様は  $T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  に対して有効。Typ 値は  $T_A = 25^{\circ}\text{C}$  での値。

表 1.

| Parameter                                | Symbol                         | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                       | Min                              | Typ                              | Max                              | Unit    |

|------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------|----------------------------------|---------|

| POWER SUPPLY                             |                                |                                                                                                                                                                                                                                                                                                                                                |                                  |                                  |                                  |         |

| Input Voltage                            | $V_{IN}$                       |                                                                                                                                                                                                                                                                                                                                                | 2.75                             | 20                               |                                  | V       |

| Undervoltage Lockout Threshold           | $UVLO_{TRSH}$                  | $V_{IN}$ rising<br>$V_{IN}$ falling                                                                                                                                                                                                                                                                                                            | 2.55<br>2.35                     | 2.65<br>2.45                     | 2.75<br>2.50                     | V       |

| Undervoltage Lockout Hysteresis          | $UVLO_{HYST}$                  |                                                                                                                                                                                                                                                                                                                                                |                                  | 0.2                              |                                  | V       |

| Quiescent Current                        | $I_{IN}$                       | EN = $V_{IN} = 12$ V, $V_{COMP} = 0.6$ V in forced pulse-width modulation (PWM) mode (not switching), SYNC = VCCO<br>EN = $V_{IN} = 12$ V, $V_{COMP} = 0.6$ V in PSM mode, SYNC = AGND                                                                                                                                                         |                                  | 4.2                              | 5.7                              | mA      |

| Shutdown Current                         | $I_{IN\_SD}$                   | EN = AGND, $V_{IN} = 5.5$ V or 20 V                                                                                                                                                                                                                                                                                                            |                                  | 2.5                              |                                  | mA      |

|                                          |                                |                                                                                                                                                                                                                                                                                                                                                | 100                              | 200                              |                                  | $\mu$ A |

| ERROR AMPLIFIER                          |                                |                                                                                                                                                                                                                                                                                                                                                |                                  |                                  |                                  |         |

| FB Input Bias Current                    | $I_{FB}$                       |                                                                                                                                                                                                                                                                                                                                                | -100                             | +1                               | +100                             | nA      |

| Open-Loop Gain <sup>1</sup>              |                                |                                                                                                                                                                                                                                                                                                                                                |                                  | 80                               |                                  | dB      |

| Gain Bandwidth Product <sup>1</sup>      |                                |                                                                                                                                                                                                                                                                                                                                                |                                  | 20                               |                                  | MHz     |

| CURRENT SENSE AMPLIFIER GAIN             | $A_{CS}$                       | Current sense gain resistor connected between DL and PGND, $R_{CSG} = 47$ k $\Omega \pm 5\%$<br>Current sense gain resistor connected between DL and PGND, $R_{CSG} = 22$ k $\Omega \pm 5\%$<br>Default setting, $R_{CSG} = \text{open}$<br>Voltage mode operation, resistor connected between DL and PGND, $R_{CSG} = 100$ k $\Omega \pm 5\%$ | 2.6<br>5.2<br>10.5               | 3<br>6<br>12                     | 3.4<br>6.8<br>13.5               | V/V     |

|                                          |                                |                                                                                                                                                                                                                                                                                                                                                |                                  | 0                                |                                  | V/V     |

| OUTPUT CHARACTERISTICS                   |                                |                                                                                                                                                                                                                                                                                                                                                |                                  |                                  |                                  |         |

| Feedback Accuracy Voltage                | $V_{FB}$                       | $T_J = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$<br>$T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}$                                                                                                                                                                                                                    | 597<br>594                       | 600<br>600                       | 603<br>606                       | mV      |

| Line Regulation of PWM                   | $\Delta V_{FB}/\Delta V_{IN}$  |                                                                                                                                                                                                                                                                                                                                                |                                  |                                  | $\pm 0.015$                      | %/V     |

| Load Regulation of PWM <sup>1</sup>      | $V\Delta_{FB}/\Delta V_{COMP}$ | $V_{COMP}$ range = 0.9 V to 2.2 V                                                                                                                                                                                                                                                                                                              |                                  |                                  | $\pm 0.3$                        | %       |

| OSCILLATOR                               |                                |                                                                                                                                                                                                                                                                                                                                                |                                  |                                  |                                  |         |

| Frequency                                | $f_{OSC}$                      | $R_{FREQ} = 332$ k $\Omega$ to AGND<br>$R_{FREQ} = 78.7$ k $\Omega$ to AGND<br>$R_{FREQ} = 40.2$ k $\Omega$ to AGND<br>FREQ connected to AGND<br>FREQ connected to VCCO                                                                                                                                                                        | 170<br>720<br>1275<br>240<br>480 | 200<br>800<br>1500<br>300<br>600 | 230<br>880<br>1725<br>360<br>720 | kHz     |

| SYNC Input Frequency Range <sup>1</sup>  | $f_{SYNC}$                     | $R_{FREQ}$ range from 332 k $\Omega$ to 40.2 k $\Omega$                                                                                                                                                                                                                                                                                        | 170                              |                                  | 1725                             | kHz     |

| SYNC Input Pulse Width <sup>1</sup>      | $t_{SYNCMIN}$                  |                                                                                                                                                                                                                                                                                                                                                | 100                              |                                  |                                  | ns      |

| SYNC Pin Capacitance to AGND             | $C_{SYNC}$                     |                                                                                                                                                                                                                                                                                                                                                |                                  | 5                                |                                  | pF      |

| LINEAR REGULATOR                         |                                |                                                                                                                                                                                                                                                                                                                                                |                                  |                                  |                                  |         |

| VCCO Output Voltage                      |                                | $I_{VCCO} = 100$ mA                                                                                                                                                                                                                                                                                                                            | 4.7                              | 5.0                              | 5.3                              | V       |

| VCCO Load Regulation                     |                                | $I_{VCCO} = 0$ mA to 100 mA                                                                                                                                                                                                                                                                                                                    |                                  |                                  | 35                               | mV      |

| VCCO Line Regulation                     |                                | $V_{IN} = 5.5$ V to 20 V, $I_{VCCO} = 20$ mA                                                                                                                                                                                                                                                                                                   |                                  |                                  | 10                               | mV      |

| VCCO Current Limit <sup>1</sup>          |                                | VCCO drops to 4 V from 5 V                                                                                                                                                                                                                                                                                                                     |                                  |                                  | 350                              | mA      |

| VCCO Short-Circuit Current <sup>1</sup>  |                                | $V_{CCO} < 0.5$ V                                                                                                                                                                                                                                                                                                                              |                                  |                                  | 370                              | mA      |

| VIN to VCCO Dropout Voltage <sup>2</sup> | $V_{DROPOUT}$                  | $I_{VCCO} = 100$ mA, $V_{IN} \leq 5$ V                                                                                                                                                                                                                                                                                                         |                                  |                                  | 0.33                             | V       |

| LOGIC INPUTS                             |                                |                                                                                                                                                                                                                                                                                                                                                |                                  |                                  |                                  |         |

| EN Threshold Voltage                     |                                | EN rising                                                                                                                                                                                                                                                                                                                                      | 0.57                             | 0.63                             | 0.68                             | V       |

| EN Hysteresis                            |                                |                                                                                                                                                                                                                                                                                                                                                |                                  |                                  | 0.03                             | V       |

| EN Input Leakage Current                 | $I_{EN}$                       | $V_{IN} = 2.75$ V to 20 V                                                                                                                                                                                                                                                                                                                      |                                  | 1                                | 200                              | nA      |

| Parameter                                                | Symbol           | Test Conditions/Comments                                              | Min   | Typ  | Max   | Unit               |

|----------------------------------------------------------|------------------|-----------------------------------------------------------------------|-------|------|-------|--------------------|

| SYNC Logic Input Low                                     |                  |                                                                       |       |      | 1.3   | V                  |

| SYNC Logic Input High                                    |                  |                                                                       | 1.9   |      |       | V                  |

| SYNC Input Pull-Down Resistance                          | $R_{SYNC}$       |                                                                       |       | 1    |       | $M\Omega$          |

| GATE DRIVERS                                             |                  |                                                                       |       |      |       |                    |

| DH Rise Time                                             |                  | $C_{DH} = 3 \text{ nF}$ , $V_{BST} - V_{SW} = 5 \text{ V}$            |       | 16   |       | ns                 |

| DH Fall Time                                             |                  | $C_{DH} = 3 \text{ nF}$ , $V_{BST} - V_{SW} = 5 \text{ V}$            |       | 14   |       | ns                 |

| DL Rise Time                                             |                  | $C_{DL} = 3 \text{ nF}$                                               |       | 16   |       | ns                 |

| DL Fall Time                                             |                  | $C_{DL} = 3 \text{ nF}$                                               |       | 14   |       | ns                 |

| DH to DL Dead Time                                       |                  | External 3 nF connected to DH and DL                                  |       | 25   |       | ns                 |

| DH or DL Driver $R_{ON}$ , Sourcing Current <sup>1</sup> | $R_{ON\_SOURCE}$ | Sourcing 2 A with a 100 ns pulse                                      | 2     |      |       | $\Omega$           |

| DH or DL Driver $R_{ON}$ , Tempco                        | $T_{C_{RON}}$    | Sourcing 1 A with a 100 ns pulse, $V_{IN} = 3 \text{ V}$              | 2.3   |      |       | $\Omega$           |

| DH or DL Driver $R_{ON}$ , Sinking Current <sup>1</sup>  | $R_{ON\_SINK}$   | $V_{IN} = 3 \text{ V}$ or 12 V                                        | 0.3   |      |       | $^{\circ}\text{C}$ |

| DH Maximum Duty Cycle <sup>1</sup>                       |                  | Sinking 2 A with a 100 ns pulse                                       | 1.5   |      |       | $\Omega$           |

| Minimum DH On Time                                       |                  | Sinking 1 A with a 100 ns pulse, $V_{IN} = 3 \text{ V}$               | 2     |      |       | $\Omega$           |

| Minimum DH Off Time                                      |                  | $f_{OSC} = 300 \text{ kHz}$                                           | 90    |      |       | %                  |

| Minimum DL On Time                                       |                  | $f_{OSC} = 1500 \text{ kHz}$                                          | 50    |      |       | %                  |

| Minimum DH Off Time                                      |                  | $f_{OSC} = 200 \text{ kHz}$ to 1500 kHz                               |       | 85   |       | ns                 |

| Minimum DL Off Time                                      |                  | $f_{OSC} = 200 \text{ kHz}$ to 1500 kHz                               |       | 345  |       | ns                 |

| Minimum DL On Time                                       |                  | $f_{OSC} = 200 \text{ kHz}$ to 1500 kHz                               |       | 295  |       | ns                 |

| COMP VOLTAGE RANGE                                       |                  |                                                                       |       |      |       |                    |

| COMP Pulse Skip Threshold                                | $V_{COMP,THRES}$ | In pulse skip mode (PSM)                                              |       | 0.9  |       | V                  |

| COMP Clamp High Voltage                                  | $V_{COMP,HIGH}$  |                                                                       | 2.2   |      |       | V                  |

| THERMAL SHUTDOWN                                         |                  |                                                                       |       |      |       |                    |

| Thermal Shutdown Threshold                               | $T_{TMSD}$       |                                                                       |       | 155  |       | $^{\circ}\text{C}$ |

| Thermal Shutdown Hysteresis                              |                  |                                                                       |       | 20   |       | $^{\circ}\text{C}$ |

| OVERVOLTAGE AND POWER-GOOD THRESHOLDS                    |                  |                                                                       |       |      |       |                    |

| FB Overvoltage Threshold                                 | $V_{OV}$         | $V_{FB}$ rising                                                       | 0.630 | 0.65 | 0.670 | V                  |

| FB Overvoltage Hysteresis                                |                  |                                                                       |       | 18   |       | mV                 |

| FB Undervoltage Threshold                                | $V_{UV}$         | $V_{FB}$ falling                                                      | 0.525 | 0.55 | 0.575 | V                  |

| FB Undervoltage Hysteresis                               |                  |                                                                       |       | 15   |       | mV                 |

| SOFT START/TRACK                                         |                  |                                                                       |       |      |       |                    |

| SS/TRK Output Current                                    | $I_{SS}$         | During startup                                                        | 4.6   | 6.5  | 8.4   | $\mu\text{A}$      |

| SS/TRK Pull-Down Resistor                                |                  | During a fault condition                                              |       | 3    |       | $k\Omega$          |

| SS/TRK Input Voltage Range <sup>1</sup>                  |                  |                                                                       | 0     | 5    |       | V                  |

| FB to SS/TRK Offset                                      |                  | $V_{SS/TRK} = 0.1 \text{ V}$ to 0.6 V; offset = $V_{FB} - V_{SS/TRK}$ | -10   |      | +10   | mV                 |

| PGOOD                                                    |                  |                                                                       |       |      |       |                    |

| PGOOD Pull-Up Resistor                                   | $R_{PGOOD}$      | Internal pull-up resistor to $V_{CCO}$                                |       | 12.5 |       | $k\Omega$          |

| PGOOD Delay                                              |                  |                                                                       |       | 12   |       | $\mu\text{s}$      |

| Overvoltage or Undervoltage Minimum Duration             |                  | Minimum duration required to trigger the PGOOD signal                 |       | 10   |       | $\mu\text{s}$      |

| ILIM Threshold Voltage <sup>1</sup>                      |                  | Relative to PGND                                                      | -5    | 0    | +5    | mV                 |

| ILIM Output Current                                      |                  | $ILIM = PGND$                                                         | 45    | 50   | 55    | $\mu\text{A}$      |

| Current Sense Blanking Period                            |                  | After DL goes high; current limit is not sensed during this period    |       | 100  |       | ns                 |

| INTEGRATED RECTIFIER (BOOST DIODE) RESISTANCE            |                  | At 20 mA forward current                                              |       | 16   |       | $\Omega$           |

| ZERO CURRENT CROSS OFFSET (SW TO PGND) <sup>1</sup>      |                  | In pulse skip mode only; $f_{OSC} = 300 \text{ kHz}$                  | 0     | 2    | 4     | mV                 |

<sup>1</sup> デザインで保証します。<sup>2</sup>  $V_{IN} < 5.5 \text{ V}$  の場合は  $V_{IN}$  と  $V_{CCO}$  を接続してください。

## 絶対最大定格

表 2.

| Parameter                                         | Rating                 |

|---------------------------------------------------|------------------------|

| VIN, EN, RAMP                                     | 21 V                   |

| FB, COMP, SS/TRK, FREQ, SYNC, VCCO, PGOOD         | -0.3 V to +6 V         |

| ILIM, SW to PGND                                  | -0.3 V to +21 V        |

| BST, DH to PGND                                   | -0.3 V to +28 V        |

| DL to PGND                                        | -0.3 V to VCCO + 0.3 V |

| BST to SW                                         | -0.3 V to +6 V         |

| BST to PGND, 20 ns Transients                     | 32 V                   |

| SW to PGND, 20 ns Transients                      | 25 V                   |

| DL, SW, ILIM to PGND, 20 ns Negative Transients   | -8 V                   |

| PGND to AGND                                      | -0.3 V to +0.3 V       |

| PGND to AGND, 20 ns Transients                    | -8 V to +4 V           |

| $\theta_{JA}$ (Natural Convection) <sup>1,2</sup> | 40°C/W                 |

| Operating Junction Temperature Range <sup>3</sup> | -40°C to +125°C        |

| Storage Temperature Range                         | -65°C to +150°C        |

| Maximum Soldering Lead Temperature                | 260°C                  |

<sup>1</sup> エクスポートド・パッドを PCB へ接続して測定。

<sup>2</sup> パッケージのジャンクション—周囲間熱抵抗( $\theta_{JA}$ )は、多層 PCB を使用して計算またはシミュレーション。

<sup>3</sup> デバイスのジャンクション温度( $T_J$ )は、周囲温度( $T_A$ )、デバイス消費電力( $P_D$ )、パッケージのジャンクション—周囲間熱抵抗( $\theta_{JA}$ )に依存します。最大ジャンクション温度は、式  $T_J = T_A + P_D \times \theta_{JA}$  を使って周囲温度と消費電力から計算。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

絶対最大定格は、組み合わせではなく個別に適用されます。特に注記がない限り、すべての電圧は AGND を基準にします。

### ESD の注意

|                                                                                   |                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。 |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

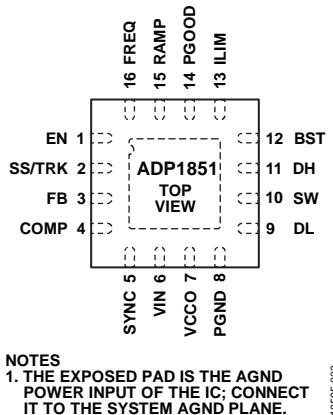

## ピン配置およびピン機能説明

図 3. ピン配置

表 3. ピン機能の説明

| ピン番号 | 記号     | 説明                                                                                                                                                                                                                                    |

|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | EN     | イネーブル入力。ENをハイ・レベルにするとコントローラがターンオンし、ロー・レベルにするとコントローラがターンオフします。自動スタートアップを行うときは、ENとV <sub>IN</sub> を接続します。高精度UVLOの場合、V <sub>IN</sub> とAGNDの間に適切なサイズの抵抗分圧器を接続し、中点をこのピンへ接続します。                                                             |

| 2    | SS/TRK | ソフトスタート／トラッキング入力。SS/TRKとAGNDとの間にコンデンサを接続して、ソフトスタート時間を設定します。このノードは、6.5 μAの電流源を介してVCCOへ内部でプルアップされています。このピンをスタートアップ時に外部電圧のトラッキング用のTRK入力として使います。                                                                                          |

| 3    | FB     | 出力電圧帰還入力。このピンを抵抗分圧器を介して出力へ接続します。                                                                                                                                                                                                      |

| 4    | COMP   | 補償ノード。誤差アンプの出力。COMPとFBの間に抵抗／コンデンサ(RC)回路を接続して、レギュレーション制御ループを補償します。                                                                                                                                                                     |

| 5    | SYNC   | 外部周波数同期入力。このピンには、FREQピンで設定される内部発振周波数f <sub>osc</sub> に近い周波数の外部クロック信号を入力します。コントローラは、周期的クロック信号がSYNCで検出されたとき、またはSYNCがハイ・レベルのとき(VCCOへ接続)、強制PWMモードで動作します。このときのスイッチング周波数は1×SYNC周波数になります。SYNCがロー・レベルまたはフローティングのとき、コントローラはパルス・スキップ・モードで動作します。 |

| 6    | VIN    | 入力電圧。メイン電源へ接続します。このピンとAGNDのできるだけ近くに接続した1 μF以上のセラミック・コンデンサでバイパスしてください。                                                                                                                                                                 |

| 7    | VCCO   | 内蔵低ドロップアウト(LDO)レギュレータの出力。内部回路とゲート・ドライバはVCCOから給電されます。VCCOとAGNDの間に接続した1 μF以上のセラミック・コンデンサでバイパスしてください。VCCO出力は、ENがロー・レベルのときでもアクティブのままでです。V <sub>IN</sub> が5.5 V以下の動作では、VINをVCCOへ接続することができます。LDOを他の補助システム負荷の電源として使用しないでください。                |

| 8    | PGND   | 電源グラウンド。内蔵ドライバのグラウンド。SWとPGNDの間で差動電流が検出されます。                                                                                                                                                                                           |

| 9    | DL     | ローサイド同期整流子ゲート・ドライバ出力。電流モードで電流検出アンプのゲインを設定するとき、または電圧モード制御を設定するとき、DLとPGNDの間に抵抗を接続します。このピンは、合計入力容量最大20 nFのMOSFETを駆動することができます。                                                                                                            |

| 10   | SW     | パワー・スイッチ・ノード／電流検出アンプ入力。このピンをハイサイドNチャンネルMOSFETのソースとローサイドNチャンネルMOSFETのドレインへ接続します。SWとPGNDの間で差動電流が検出されます。                                                                                                                                 |

| 11   | DH     | ハイサイド・スイッチ・ゲート・ドライバ出力。このピンは、合計入力容量最大20 nFのMOSFETを駆動することができます。                                                                                                                                                                         |

| 12   | BST    | ハイサイド内蔵ドライバのポートストラップされた上側レール。BSTとSWの間に0.1 μF～0.22 μFの値を持つ積層セラミック・コンデンサ(MLCC)を接続してください。内蔵ブースト・ダイオード整流子をVCCOとBSTの間に接続します。                                                                                                               |

| 13   | ILIM   | 電流制限検出コンパレータの反転入力。ILIMとSWとの間に抵抗を接続して、電流制限オフセットを設定します。正確な電流制限検出の場合、ローサイドMOSFETのソースでILIMを電流検出抵抗へ接続してください。                                                                                                                               |

| 14   | PGOOD  | パワーグッド表示。PGOODはオープン・ドレインのパワーグッド・インジケータ・ロジック出力で、PGOODとVCCOの間に12.5 kΩの内蔵抵抗が接続されています。                                                                                                                                                    |

| 15   | RAMP   | スロープ補償のプログラマブルな電流設定。RAMPとV <sub>IN</sub> の間に抵抗を接続します。RAMPの電圧は、動作時0.2 Vです。このピンは、コントローラのディスエーブル中は高インピーダンスになります。                                                                                                                         |

| ピン番号 | 記号             | 説明                                                                                                                                                 |

|------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 16   | FREQ           | 内蔵発振周波数 $f_{osc}$ 。FREQ と AGND の間に抵抗を 1 本接続して、200 kHz~1.5 MHz の動作周波数を設定します。既定 300 kHz の場合 FREQ と AGND を接続します。600 kHz 動作周波数の場合は FREQ と VCCO を接続します。 |

|      | EPAD<br>(AGND) | エクスボーズド・パッド(アナログ・グラウンド)。エクスボーズド・パッドはこの IC の AGND 電源入力です。エクスボーズド・パッドはシステム AGND プレーンに接続します。                                                          |

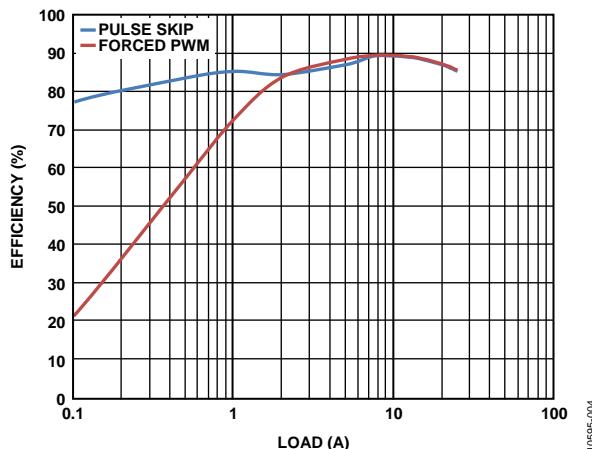

## 代表的な性能特性

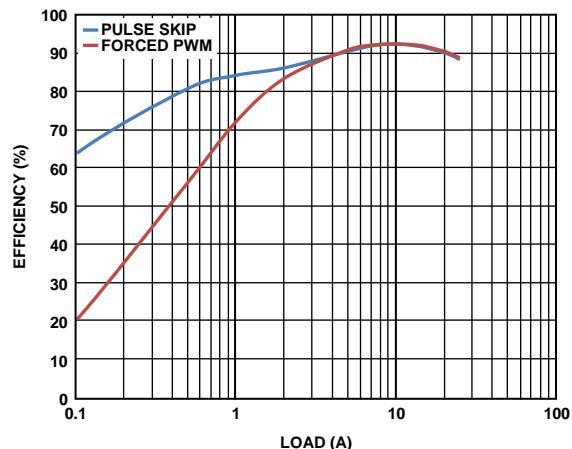

図 4. 効率のプロット、 $12 \text{ V}_{\text{IN}} \rightarrow 1.8 \text{ V}_{\text{OUT}}$ 、600 kHz

(回路については図 34 参照)

図 7. 効率のプロット、 $12 \text{ V}_{\text{IN}} \rightarrow 3.3 \text{ V}_{\text{OUT}}$ 、300 kHz

(回路については図 35 参照)

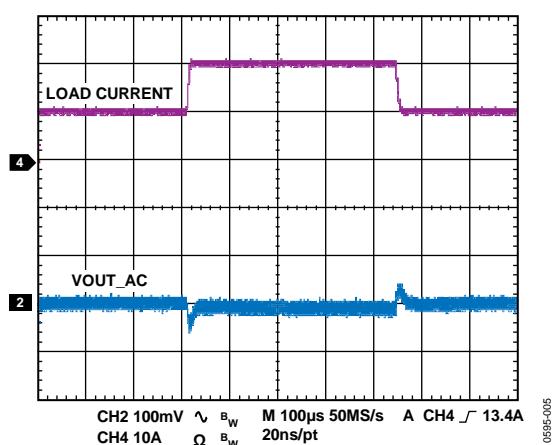

図 5.  $10 \text{ A} \rightarrow 20 \text{ A}$  の負荷ステップ、 $12 \text{ V}_{\text{IN}} \rightarrow 1.8 \text{ V}_{\text{OUT}}$

600 kHz、電流モード

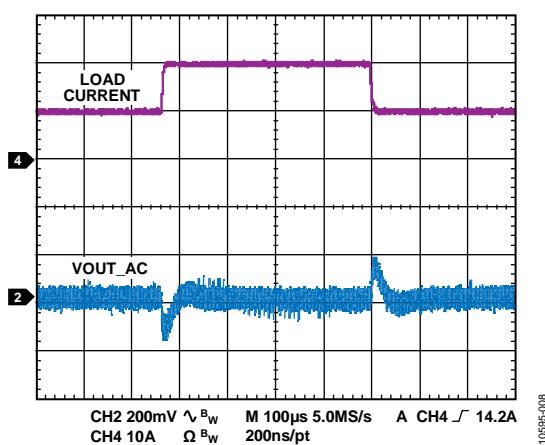

図 8.  $10 \text{ A} \rightarrow 20 \text{ A}$  の負荷ステップ、 $12 \text{ V}_{\text{IN}} \rightarrow 3.3 \text{ V}_{\text{OUT}}$

300 kHz、電圧モード

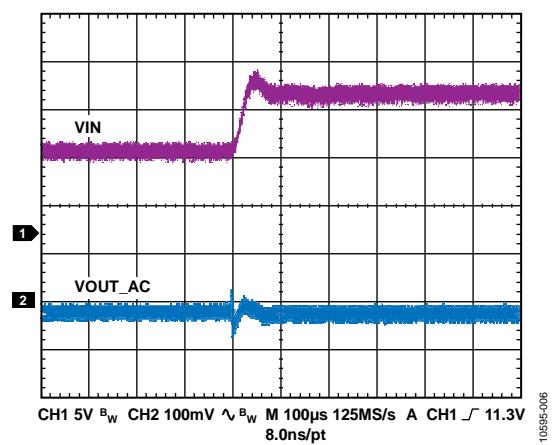

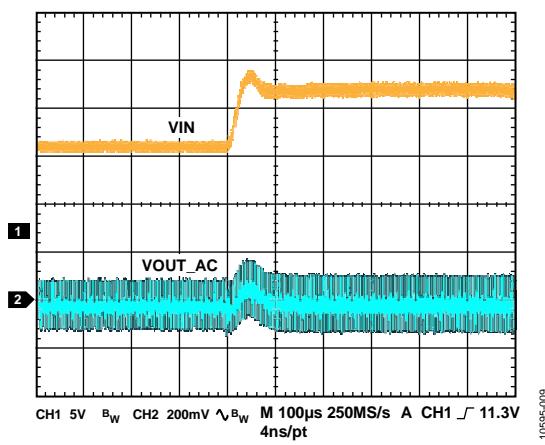

図 6.  $9 \text{ V} \rightarrow 15 \text{ V}$  のライン・ステップ

$1.8 \text{ V}_{\text{OUT}}$ 、20 A 負荷、電流モード

図 9.  $9 \text{ V} \rightarrow 15 \text{ V}$  のライン・ステップ

$3.3 \text{ V}_{\text{OUT}}$ 、15 A 負荷、電圧モード

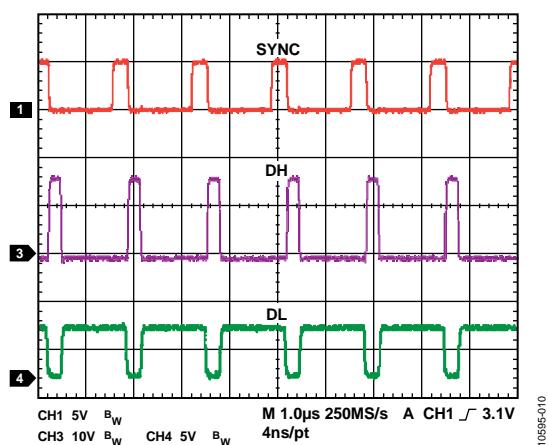

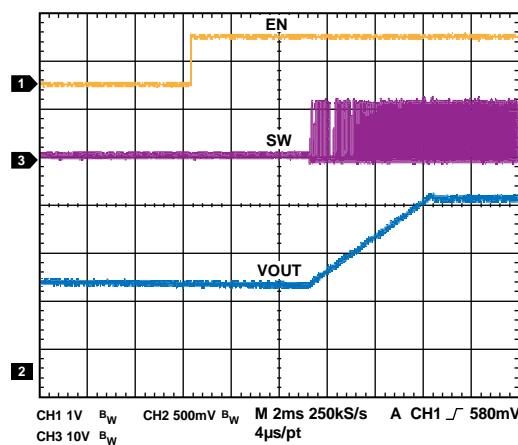

図 10. 外部周波数同期、 $f_{SYNC} = 600$  kHz図 13. プリチャージ出力でのソフトスタート

1.8 V<sub>OUT</sub>強制 PWM モード

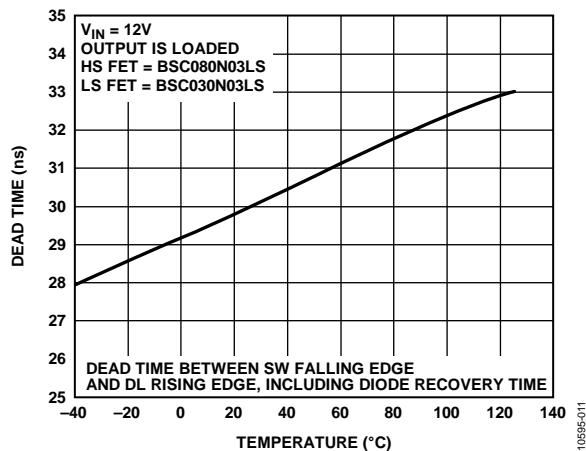

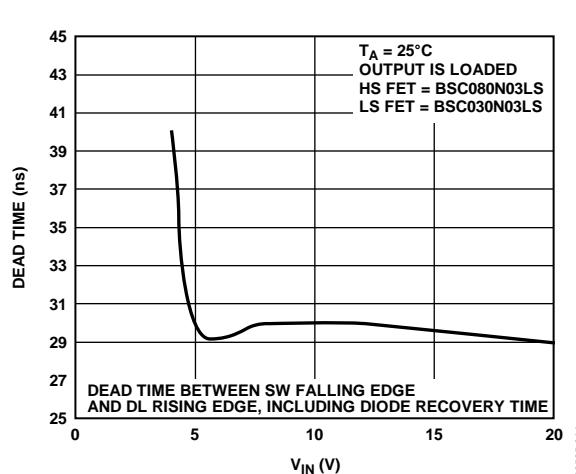

図 11. デッド・タイムの温度特性

図 14. V<sub>IN</sub>対デッド・タイム

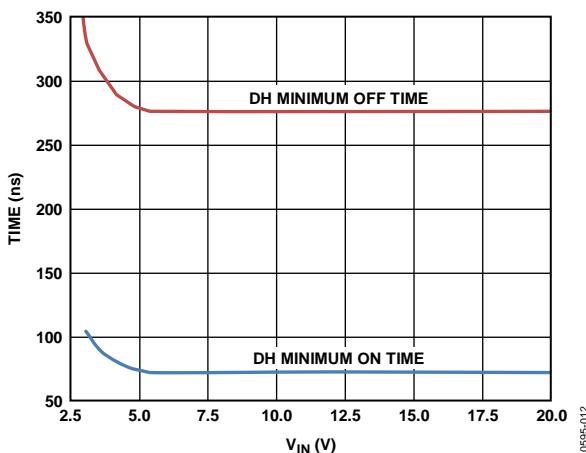

図 12. DH 最小オフ時間とオフ時間

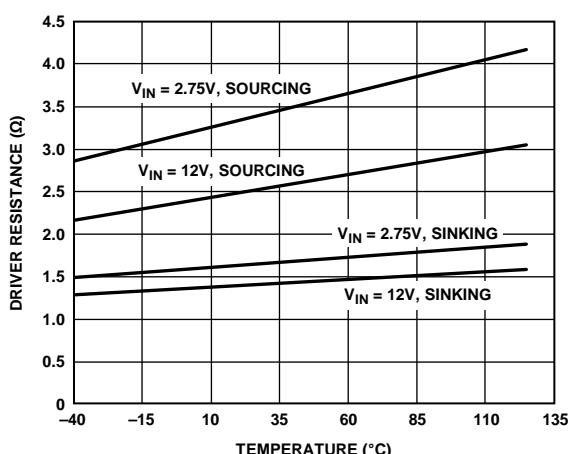

図 15. ドライバ抵抗の温度特性

## 動作原理

ADP1851 は、外付け N チャンネル・パワー MOSFET に対するドライバとブートストラップ機能を内蔵した、固定周波数、降圧、同期整流スイッチング・コントローラです。電流モード制御ループは、電圧モードに設定することもできます。このコントローラは、軽負荷時に強制 PWM モードと省電力のパルス・スキップ・モードを選択することができます。ADP1851 は、プログラマブルなソフトスタート、出力過電圧保護、プログラマブルな電流制限、パワーグッド、トラッキング機能を内蔵しています。このコントローラは、200 kHz~1.5 MHz のスイッチング周波数で動作することができます。このスイッチング周波数は抵抗で設定するか、または外部クロックに同期させることができます。

## 制御アーキテクチャ

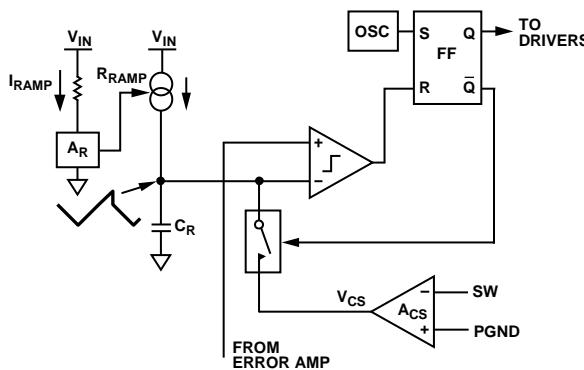

ADP1851 は、固定周波数のエミュレートしたピーク電流モード PWM 制御アーキテクチャを採用しています。インダクタ電流は、外付けローサイド MOSFET の  $R_{DS(on)}$  の両端に発生する電圧降下、またはローサイド MOSFET ソースと電源グラウンドの間に直列に接続した検出抵抗の両端に発生する電圧降下により検出されます。電流はスイッチング・サイクルのオフ区間で検出され、内蔵電流検出アンプでコンディショニングされます。

電流検出アンプのゲインは、コントローラのパワーアップ初期化時のデバイスがスイッチングを開始する前に、3 V/V、6 V/V、または 12 V/V に設定することができます。DL と PGND の間に、47 k $\Omega$  抵抗を接続するとゲイン=3 V/V に、22 k $\Omega$  抵抗を接続するとゲイン=6 V/V に、それぞれ設定されます。抵抗を接続しないと、ゲイン=12 V/V に設定されます。

電流検出アンプの出力信号は保持され、次のスイッチング・サイクルの DH オン時間にエミュレートされた電流ランプに加算され、PWM コンパレータに入力されます(図 16 参照)。この信号は、誤差アンプからの COMP 信号と比較され、PWM パルスを発生するフリップフロップをリセットします。DL と PGND の間に 100 k $\Omega$  抵抗を接続して電圧モード制御を選択すると、電流検出信号を加算しないで、エミュレートされた電流ランプが PWM コンパレータに加えられます。

図 16. 簡略化した制御アーキテクチャ

図 16 に示すように、エミュレートされた電流ランプが IC 内部で発生されますが、RAMP ピンを使って設定することができます。 $V_{IN}$  と RAMP ピン間に接続する適切な値抵抗を選択すると、所望のスロープ補償値を設定することができます。同時に、 $V_{IN}$  フィード・フォワード機能も提供することができます。コントローラ・ロジックにより貫通動作を防止して、内蔵ドライバと外付け MOSFET の相互導通を制限します。

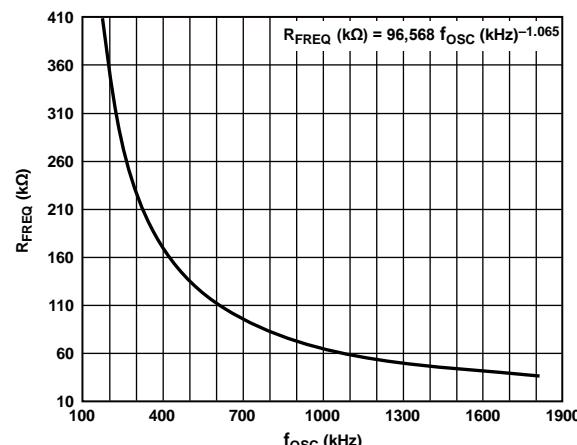

## 発振周波数

200 kHz~1.5 MHz の内部発振周波数は、FREQ ピンの外付け抵抗  $R_{FREQ}$  で設定します。幾つかの一般的な  $f_{osc}$  値を表 4 に示し、図 17 に関係を示します。例えば、78.7 k $\Omega$  抵抗で発振周波数 800 kHz が設定されます。FREQ と AGND を接続するか、または FREQ と VCCO を接続すると、発振周波数はそれぞれ 300 kHz または 600 kHz に設定されます。表 4 に示していない他の周波数に対しては、 $R_{FREQ}$  値と  $f_{osc}$  は図 17 から求めることができます。あるいは次の経験式を使ってこれらの値を計算することができます。

$$D_{SDC}(k\Omega) = 96,568 \times f_{osc}(kHz)^{-1.065}$$

表 4. 発振周波数の設定

| R <sub>FREQ</sub> | f <sub>osc</sub> (Typical) |

|-------------------|----------------------------|

| 332 k $\Omega$    | 200 kHz                    |

| 78.7 k $\Omega$   | 800 kHz                    |

| 60.4 k $\Omega$   | 1000 kHz                   |

| 51 k $\Omega$     | 1200 kHz                   |

| 40.2 k $\Omega$   | 1500 kHz                   |

| FREQ to AGND      | 300 kHz                    |

| FREQ to VCCO      | 600 kHz                    |

図 17. f<sub>osc</sub> 対 R<sub>FREQ</sub>

## 外部周波数同期

ADP1851 のスイッチング周波数は、外部クロック信号を SYNC ピンに接続することにより、外部クロックと同期させることができます。FREQ ピンの抵抗で設定される内部発振周波数は、外部クロック周波数に近い値に設定する必要があります。このため、外部クロック周波数は設定された内部クロックの 0.85~1.3 倍で変化することができます。得られるスイッチング周波数は、外部 SYNC 周波数の 1 倍になります。外部周波数同期では、ADP1851 は PWM モードで動作します。

外部クロックが最初の SYNC エッジで検出されると、内部発振器がリセットされて、クロック制御が SYNC へ移ります。SYNC エッジが、PWM 出力の後続クロックをトリガするようになります。DH の立ち上がりエッジは対応する SYNC エッジの約 100 ns 後に発生し、周波数は外部信号にロックされます。外部 SYNC 信号が動作中になくなると、ADP1851 は内部発振器に戻ります。SYNC 機能を使う場合、SYNC 信号が失われたときに ADP1851 が PWM モードの動作を続けるように、SYNC と VCCO の間にプルアップ抵抗を接続することが推奨されます。

## PWM 動作モードとパルス・スキップ動作モード

SYNC ピンは共用ピンです。SYNC を VCCO すなわちハイ・レベルに接続すると、PWM モードがイネーブルされます。SYNC がグラウンドすなわちフローティングのままの場合、パルス・スキップ・モードがイネーブルされます。SYNC をロー・レベルからハイ・レベルへまたはハイ・レベルからロー・レベルへスイッチングすると、コントローラはそれぞれ強制 PWM モードからパルス・スキップ・モードへまたはパルス・スキップ・モードから強制 PWM モードへ 2 クロック・サイクルで変化します。

表 5.動作モード

| SYNC Pin     | Mode of Operation |

|--------------|-------------------|

| Low          | Pulse skip mode   |

| High         | Forced PWM mode   |

| No Connect   | Pulse skip mode   |

| Clock Signal | Forced PWM mode   |

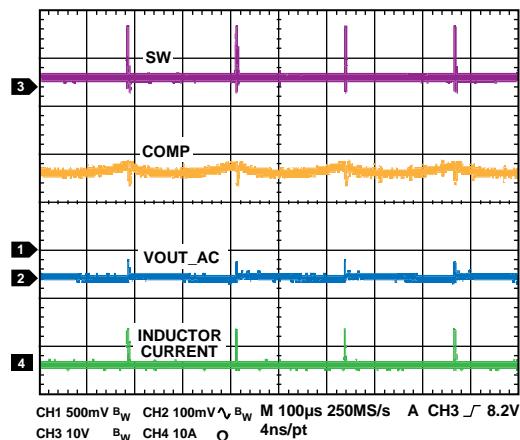

ADP1851 は、コントローラが PWM パルスをスキップできるようにするパルス・スキップ検出回路を内蔵しているため、軽負荷時にスイッチング周波数を下げることができます。このときの出力リップルは、固定周波数強制 PWM モードでのリップルより大きくなります。図 18 に、軽負荷時のパルス・スキップ・モードでの ADP1851 の動作を示します。軽負荷時のパルス・スキップ周波数は、インダクタ、出力容量、出力負荷、入力電圧、出力電圧に依存します。

図 18. 軽負荷時のパルス・スキップ・モードの例

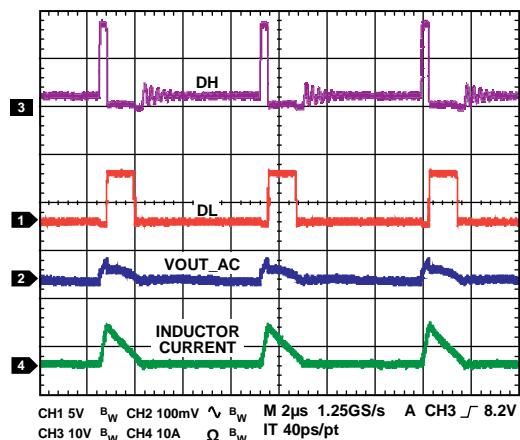

出力負荷がパルス・スキップ閾値電流より大きい場合、すなわち  $V_{COMP}$  が 0.9 V の閾値に到達した場合、ADP1851 はパルス・スキップ動作モードを抜け出して、固定周波数不連続道通モード(DCM)に入ります(図 19 参照)。負荷がさらに増加すると、ADP1851 は連続道通モード(CCM)を開始します。

図 19. 不連続道通モード(DCM)波形の例

強制 PWM モードでは、ADP1851 はすべての負荷で CCM 動作になるため、インダクタ電流は常に連続です。

## 同期整流ダイオードとデッド・タイム

ADP1851 では、貫通防止回路が DH—SW 間電圧と DL—PGND 間電圧をモニタし、ローサイド・ドライバとハイサイド・ドライバを調節して、ハイサイド MOSFET とローサイド MOSFET の間の相互導通または貫通を防止するように、ブレーク・ビフォア・マーク・スイッチングを確実に行なうようにします。このブレーク・ビフォア・マーク・スイッチングはデッド・タイムと呼ばれ、固定ではなく、MOSFET のターンオンおよびターンオフ速度に依存します。入力容量約 3 nF の中サイズの MOSFET を使う代表的なアプリケーション回路では、デッド・タイムは約 25 ns (typ) です。高速なダイオード回復時間を持つ小型で高速な MOSFET を使う場合、デッド・タイムは最小 13 ns になります。

## 入力低電圧ロックアウト

VIN ピンのバイアス入力電圧が 2.65 V (typ) の低電圧ロックアウト (UVLO) 閾値を下回ると、スイッチ・ドライバは非アクティブになります。EN がハイ・レベルになると、コントローラはスイッチングを開始して、VIN ピン電圧が UVLO 閾値を超えます。

## 内蔵のリニア・レギュレータ

内蔵リニア・レギュレータは、低ドロップアウト (LDO) VCCO です。VCCO は内部制御回路をパワーアップさせ、ゲート・ドライバに電源を供給します。200 mA 以上の出力電流能力を保証しているため、一般的なロジック閾値の MOSFET を最大 1.5 MHz で駆動するゲート駆動要求に対しては十分な能力です。VCCO は常にアクティブで、EN 信号でシャットダウンできませんが、温度上昇保護が動作すると、LDO はコントローラと一緒にディスエーブルされます。VCCO と AGND の間に 1  $\mu$ F 以上のコンデンサを接続してバイパスしてください。

LDO がゲート駆動電流を供給しているため、各スイッチング・サイクルでドライバがスイッチし、ブースト・コンデンサが再充電されるごとに、VCCO にはシャープな過渡電流が発生します。LDO は、過負荷故障なしでこれらの過渡電流を処理できるように最適化されています。ゲート駆動が負荷になっているため、VCCO 出力を他の外部補助システム負荷に使用することは推奨できません。

LDO には、予測される最大ゲート駆動負荷を上回る電流制限機能が内蔵されています。この電流制限機能には、短絡故障時にさらに VCCO 電流を制限する短絡フォールドバック機能も含まれています。

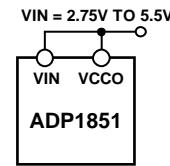

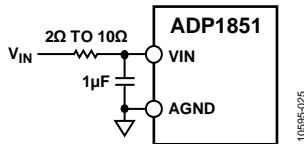

入力電圧が 5.5 V より低い場合には、VIN と VCCO を接続して LDO をバイパスして、ドロップアウト電圧を小さくすることができます(図 20 参照)。ただし、入力範囲が 4 V~7 V の場合は、VIN と VCCO を接続して LDO をバイパスすることはできません。これは、7 V 入力が VCCO ピンの最大電圧定格を超えるためです。この場合には、LDO を使って内蔵ドライバを駆動してください。ただし、VIN が 5 V より低い場合にはドロップアウトが生じることに注意してください。

図 20.  $V_{IN} < 5.5$  V での構成

## 過電圧保護機能

ADP1851 は、FB ノードで出力過電圧を検出する回路を内蔵しています。FB 電圧  $V_{FB}$  が過電圧閾値を上回ると、ハイサイド N チャンネル MOSFET (NMOSFET) がターンオフし、ローサイド NMOSFET がターンオンして、 $V_{FB}$  が低電圧閾値を下回るまで続けます。この動作は、クローバー過電圧保護と呼ばれています。過電圧状態が続くと、コントローラは帰還電圧を過電圧閾値と低電圧閾値の間に維持し、出力はレギュレーション電圧の typ 値で+8%および-8%以内にレギュレーションされます。過電圧が発生すると、SS/TRK ノードは 3 k $\Omega$  の内蔵プルダウン抵抗を通じて放電されます。FB の電圧が低電圧閾値を下回ると、ソフトスタート・シーケンスが再度開始されます。図 21 に、PSM での過電圧保護機能を示します。

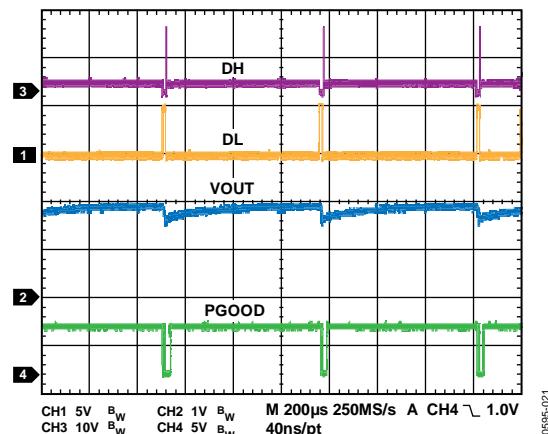

図 21. PSM モードでの過電圧保護機能、 $V_{OUT}$  を 2.0 V へ接続

## パワーグッド

PGOOD ピンはオープン・ドレインの NMOSFET です。内蔵 12.5 k $\Omega$  プルアップ抵抗が PGOOD と VCCO の間に接続されています。PGOOD は通常動作時に内部で VCCO にプルアップされていて、トリガされたときはアクティブ・ローです。帰還電圧  $V_{FB}$  が過電圧閾値を上回るか、または低電圧閾値を下回ると、12  $\mu$ s の遅延後に PGOOD 出力がグラウンドへプルダウンされます。PGOOD がアクティブになるためには、過電圧状態または低電圧状態が少なくとも 10  $\mu$ s 間続く必要があります。熱過負荷状態が検出された場合にも、PGOOD 出力はアクティブになります。

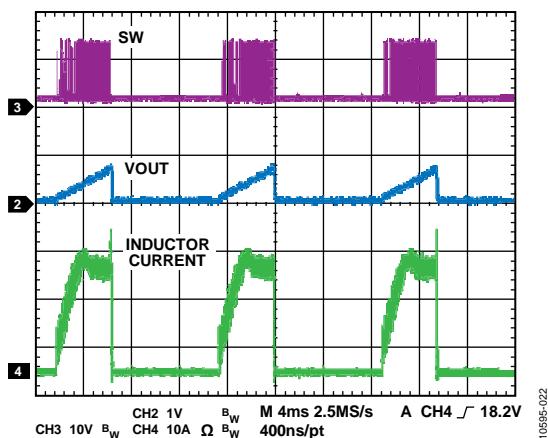

## 短絡保護機能と電流制限機能

出力が短絡した場合、または出力電流が 8 連続サイクル間電流制限設定抵抗(ILIM と SW の間)により設定された電流制限値を超えた場合、ADP1851 はハイサイド・ドライバとローサイド・ドライバをシャットオフし、10 ms ごとにソフトスタート・シーケンスを再起動します。これはヒップ・モードと呼ばれます。SS ノードは、過電流または短絡発生時に内蔵 3 kΩ 抵抗を通してゼロへ放電します。図 22 に、高電流アプリケーション回路での ADP1851 が output 短絡時に電流制限ヒップ・モードを維持することを示します。

図 22. 電流制限ヒップ・モード、30 A 電流制限

## イネーブル/ディスエーブル制御

EN ピンを使って、ADP1851 コントローラをイネーブルまたはディスエーブルします。イネーブル閾値精度は 0.63 V (typ) です。EN の電圧が閾値電圧を上回ると、コントローラがイネーブルされて、内部発振器、リファレンス、設定値、ソフトスタート周期を初期化した後に通常動作が開始されます。EN の電圧が閾値電圧を 30 mV (ヒステリシス typ 値) 下回ると、ADP1851 のドライバと内部コントローラ回路がターンオフされます。初期設定値はまだ有効であるため、VIN ピンの電源がオン/オフされるまでは、コントローラを再イネーブルしても設定値は変わりません。さらに、EN 信号は VCCO の LDO レギュレータをシャットダウンしないため、V<sub>IN</sub> が UVLO 閾値を上回っているとき常にアクティブです。

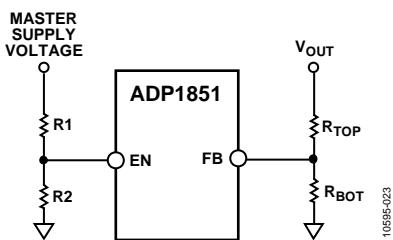

電源シーケンシングを開始させる目的で、マスター電源と EN ピンの間に適切な抵抗分圧器を接続することにより ADP1851 のスタートアップを設定することができます(図 23 参照)。例えば、マスター電源からの所望のスタートアップ電圧が 10 V の場合、R1 と R2 はそれぞれ 156 kΩ と 10 kΩ に設定することができます。

図 23. オプションのパワーアップ・シーケンシング回路

## 熱過負荷保護機能

ADP1851 はチップのジャンクション温度を検出する温度センサーを内蔵しています。ADP1851 のジャンクション温度が約 155°C に到達すると、ADP1851 はサーマル・シャットダウンして、コンバータがターンオフし、SS/TRK ピンは内蔵 3 kΩ 抵抗を通してゼロに放電します。同時に、VCCO はゼロに放電します。ジャンクション温度が 135°C を下回ると、ADP1851 はソフトスタート・シーケンスの後に通常動作に戻ります。

## アプリケーション情報

### ADIsimPower デザイン・ツール

ADP1851 は、ADIsimPower™ デザイン・ツール・セットによりサポートされています。ADIsimPower は、特定のデザイン目標に対して最適化された電源デザインを生成するツールのコレクションです。このツールを使うと、フル回路図、部品表、数分で性能計算を生成することができます。ADIsimPower は、動作条件、IC の制限、実際のすべての外付け部品を考慮して、コスト、面積、効率、部品数についてデザインを最適化することができます。ADIsimPower ツールは

<http://www.analog.com/jp/ADIsimPower> から提供しており、ユーザーはこのツールを使って部品未実装ボードを要求することができます。

### 出力電圧の設定

出力電圧は、出力と FB との間に接続する抵抗分圧器を使って設定されます。R<sub>BOT</sub> に対しては、1 kΩ~20 kΩ の抵抗を使用してください。次式を使って出力電圧を設定する R<sub>TOP</sub> を選択します。

$$D_{FAB} = D_{4AF} \left( \frac{H_{AGF} - H_{SA}}{H_{FA}} \right)$$

ここで、

R<sub>TOP</sub> はハイサイド分圧器抵抗。

R<sub>BOT</sub> はローサイド分圧器抵抗。

V<sub>OUT</sub> はレギュレーションされた出力電圧。

V<sub>FB</sub> は帰還レギュレーション閾値の 0.6 V。

### ソフトスタート

ソフトスタート時間は、SS と AGND の間に外付けコンデンサを接続して設定します。ソフトスタート機能は、入力突入電流を制限し、出力オーバーシュートを防止します。EN をイネーブルすると、6.5 μA の電流源がコンデンサの充電を開始し、SS の電圧が 0.6 V に到達するとレギュレーション電圧に到達します。ソフトスタート時間は次式で近似されます。

$$f_{BE} = \frac{0.6}{6.5 \mu A} 5_{BE}$$

SS ピンは、VCCO に等しい最終電圧に到達します。

コントローラがディスエーブルされると、例えば EN をロー・レベルにするか、または過電流制限状態が発生すると、ソフトスタート・コンデンサが内蔵 3 kΩ プルダウン抵抗を通して放電します。

### 電流制限値の設定

電流制限コンパレータは、負荷電流を求めるためにローサイド MOSFET の両端の電圧を測定します。

電流制限値は、外付け電流制限抵抗 R<sub>ILIM</sub> を ILIM と SW の間に接続して設定します。電流検出ピン ILIM は、公称 50 μA の電流をこの外付け抵抗に供給します。この電流により、R<sub>ILIM</sub> に 50 μA の電流を乗算したオフセット電圧が発生します。電流検出エレメント R<sub>CS</sub> (ローサイド MOSFET、R<sub>DSON</sub>) の電圧降下がこのオフセット電圧以上の場合、ADP1851 は電流制限イベントの発生を表示します。

$$D_{ILIM} = \frac{1.06 \times ;_{BE} \times D_{SE}}{50 \mu A}$$

ここで、I<sub>LPK</sub> はピーク・インダクタ電流。

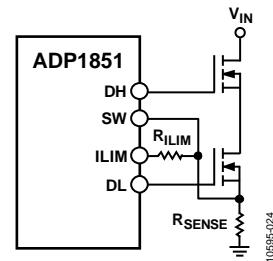

### 電流制限の正確な検出

MOSFET の R<sub>DSON</sub> は、温度範囲に対して 50% 以上変化することがあります。ローサイド MOSFET のソースから PGND へ電流検出抵抗を接続すると、電流制限の正確な検出を行うことができます。電流検出抵抗の電力定格がアプリケーションに対して十分であることを確認してください。図 24 に正確な電流制限検出の例を示します。

図 24. 電流制限の正確な検出

### 入力コンデンサの選択

ハイサイド・スイッチ MOSFET のドレインの近くに配置した 2 個の並列コンデンサを使ってください(十分大きな電流定格のバルク・コンデンサ 1 個と 10 μF のセラミック・デカップリング・コンデンサ)。

リップル電流定格に基づいて入力バルク・コンデンサを選択します。特定の負荷に対して要求される最小入力容量は、次式で求めます。

$$C_{IN} = \frac{;_A \times \theta(1 - \theta)}{(H_{BB} - ;_A \times 6D_{ED}) X_H}$$

ここで、

I<sub>0</sub> は出力電流。

D はデューティ・サイクル。

V<sub>PP</sub> は所望の入力リップル電圧。

R<sub>ESR</sub> は、コンデンサの等価直列抵抗。

## VIN ピン・フィルタ

ローパス・フィルタを VIN ピンに接続することが推奨されます。2 Ω~10 Ω の抵抗を VIN に直列に接続し、VIN と AGND の間に 1 μF のセラミック・コンデンサを接続すると、スイッチング・レギュレータから発生する不要なグリッチを効果的に除去するローパス・フィルタが構成されます。大型の MOSFET を駆動するときは、入力電流が 100 mA より大きくなることに注意してください。10 Ω 抵抗を流れる 100 mA 電流により 1 V の電圧降下が発生し、これは、VCCO と同じ降下になります。この場合、抵抗値を小さくすることが必要です。

図 25.入力フィルタの構成

## ブースト・コンデンサの選択

SW ピンと BST ピンの間にブースト・コンデンサを接続して、スイッチング時にハイサイド・ドライバへ電流を供給してください。0.1 μF~0.22 μF の値を持つセラミック・コンデンサを選択してください。

## インダクタの選択

大部分のアプリケーションでは、インダクタ・リップル電流が最大 DC 出力負荷電流の 20%~40% になるようにインダクタ値を選択してください。

次式を使ってインダクタ値を選択します。

$$L = \frac{H_{\text{sw}} - H_{\text{AGF}}}{X_L \times \Delta I_L} \times \frac{H_{\text{AGF}}}{H_{\text{sw}}}$$

ここで、

$L$  はインダクタ値。

$V_{\text{IN}}$  は入力電圧。

$V_{\text{OUT}}$  は出力電圧。

$f_{\text{sw}}$  はスイッチング周波数。

$\Delta I_L$  はピーク to ピークのインダクタ・リップル電流。

インダクタのデータシートにより、インダクタの飽和電流がデザインのピーク・インダクタ電流より大きいことを確認してください。

## 出力コンデンサの選択

出力での最大許容スイッチング・リップルに対して、次式の値より大きい出力コンデンサを選択します。

$$C_{\text{AGF}} \geq \frac{\Delta I_L}{8 X_L} \times \frac{1}{\sqrt{\Delta H_{\text{AGF}}^2 - \Delta I_L^2 \times (D_{\text{ED}}^2 - (4 X_L \times \Delta I_L)^2)}}$$

ここで、

$\Delta I_L$  はインダクタ・リップル電流。

$\Delta V_{\text{OUT}}$  はターゲット最大出力リップル電圧。

$R_{\text{ESR}}$  は出力コンデンサの等価直列抵抗(またはすべての出力コンデンサ ESR の並列接続)。

$L_{\text{ESL}}$  は出力コンデンサの等価直列インダクタンス(またはすべてのコンデンサの並列接続 ESL)。

スイッチング周波数での出力コンデンサのインピーダンスにリップル電流を乗算して出力電圧リップルを求めます。このインピーダンスは、容量インピーダンス、公称寄生特性、等価直列抵抗(ESR)、等価直列インダクタンス(ESL)の和で構成されています。

通常、コンデンサ・インピーダンスは ESR により支配されます。電解コンデンサやポリマー・コンデンサのようなコンデンサの最大 ESR 定格は、メーカーのデータシートに記載されているため、出力リップルは次のように簡単になります。

$$\Delta H_{\text{AGF}} \geq \Delta I_L \times D_{\text{ED}}$$

電解コンデンサはタイプ、サイズ、形状に応じて 5 nH~20 nH オーダーの大きな ESL を持ちます。PCB パターンも ESR と ESL に影響しますが、コンデンサのデータシートの最大 ESR 定格を使うと、ESL の測定が不要になる程度の余裕が得られます。

ESR と ESL のインピーダンスがスイッチング周波数で小さい出力コンデンサの場合、例えば出力コンデンサが並列 MLCC コンデンサのバンクの場合、容量インピーダンスが支配的なため、出力容量は次式の値より大きくなります。

$$C_{\text{AGF}} \geq \frac{\Delta I_L}{8 \Delta H_{\text{AGF}} \times X_L} \quad (1)$$

出力コンデンサのリップル電流定格が最大インダクタ・リップル電流より大きいことを確認してください。

負荷開放時の出力電圧オーバーシュート条件を満たすためには、出力容量は次式の値より大きい必要があります。

$$C_{\text{AGF}} \geq \frac{\Delta I_L \times \Delta V_{\text{OVERSHOOT}}^2}{(H_{\text{AGF}} + \Delta H_{\text{AHTDE AAF}})^2 - H_{\text{OOF}}^2} \quad (2)$$

ここで、 $\Delta V_{\text{OVERSHOOT}}$  は最大許容オーバーシュート。

式 1 または式 2 で与えられる最大出力容量を選択してください。

## MOSFET の選択

MOSFET の選択は直接 DC/DC コンバータの性能に影響を与えます。低いオン抵抗を持つ MOSFET の  $I^2R$  損失は小さく、小さいゲート電荷を持つ場合はスイッチング損失が小さくなります。MOSFET は MOSFET で消費される電力により MOSFET のチップ温度が高くなり過ぎないように小さい熱抵抗を持つ必要があります。

ハイサイド MOSFET はオン時に負荷電流を流すため、コンバータの大部分のスイッチング損失を発生させます。一般に、MOSFET のオン抵抗が低いほど、ゲート電荷が大きくなり、逆も成り立ちます。このため、2 つの損失が釣り合ったハイサイド MOSFET を選択することが重要です。ハイサイド MOSFET の伝導損失は、次式で求められます。

$$B_5 = (\zeta_{A36(D^2E)})^2 \times D_{DEA@}$$

ここで、 $R_{DSON}$  は MOSFET のオン抵抗。

ゲート充電損失は次式で近似されます。

$$B_9 \approx H_{H_I} \times C_9 \times X_H$$

ここで、

$V_{PV}$  はゲート・ドライバの電源電圧。

$Q_G$  は、MOSFET の合計ゲート電荷。

ゲート充電電力損失は MOSFET ではなく、ADP1851 内蔵ドライバで発生することに注意してください。総合電源効率を計算する際にこの電力損失を考慮する必要があります。

ハイサイド MOSFET のスイッチング損失は次式で近似されます。

$$B_F \approx \frac{H_{@} \times ;_{A36} \times (f_D + f_S) \times X_H}{2}$$

ここで、

$P_T$  はハイサイド MOSFET スイッチング損失電力。

$t_R$  はハイサイド MOSFET 充電時の立上がり時間。

$t_F$  はハイサイド MOSFET 放電時の立下がり時間。

$t_R$  と  $t_F$  は次式で計算できます。

$$f_D \approx \frac{C_{9H}}{;_{6DHHD\_DE@}}$$

$$f_S \approx \frac{C_{9H}}{;_{6DHHD\_83>>}}$$

ここで、

$Q_{GSW}$  はスイッチング時の MOSFET のゲート電荷で、MOSFET データシートに記載されています。

$I_{DRIVER\_RISE}$  と  $I_{DRIVER\_FALL}$  は、ADP1851 内蔵ゲート・ドライバからのドライバ電流出力。

$Q_{GSW}$  がデータシートに記載されてない場合は、次式で近似できます。

$$C_{9H} \approx C_{9G} + \frac{C_{GE}}{2}$$

ここで、 $Q_{GD}$  と  $Q_{GS}$  は MOSFET データシートに記載されているゲートードレイン間電荷とゲートーソース間電荷。

$I_{DRIVER\_RISE}$  と  $I_{DRIVER\_FALL}$  は次式で計算できます。

$$;_{6DHHD\_DE@} \approx \frac{H_{66} - H_{EB}}{D_{A@_EAGD57} + D_{93F7}}$$

$$;_{6DHHD\_83>>} \approx \frac{H_{EB}}{D_{A@_E@_E} + D_{93F7}}$$

ここで、

$V_{DD}$  はドライバに対する入力電源電圧で、入力電圧に応じて 2.75 V ~ 5 V の範囲。

$V_{SP}$  は MOSFET がフル導通するスイッチング・ポイント。この電圧は MOSFET データシートに記載されるゲート電荷グラフから求めることができます。

$R_{ON\_SOURCE}$  は ADP1851 内蔵ドライバのオン抵抗で、MOSFET を充電するとき表 1 で与えられます。

$R_{ON\_SINK}$  は ADP1851 内蔵ドライバのオン抵抗で、MOSFET が放電するとき表 1 で与えられます。

$R_{GATE}$  は MOSFET のオン・ゲート抵抗で、MOSFET データシートに記載されています。外付けゲート抵抗を追加する場合、この外付け抵抗を  $R_{GATE}$  へ加算してください。

ハイサイド MOSFET の合計消費電力は、次のように道通損失とスイッチング損失の和になります。

$$B_{;E} \approx B_5 + B_F$$

同期整流子すなわちローサイド MOSFET は、ハイサイド MOSFET がオフのとき、インダクタ電流を流します。ローサイド MOSFET のスイッチング損失は小さいため、計算では無視することができます。入力電圧が高く出力電圧が低い場合は、ローサイド MOSFET が大部分の時間電流を流します。したがって、高い効率を実現するためには、ローサイド MOSFET が低いオン抵抗を持つよう最適化することが不可欠です。損失が MOSFET 定格を超える場合または 1 個の MOSFET で可能な値より低い抵抗が必要とされる場合には、複数のローサイド MOSFET を並列に接続します。ローサイド MOSFET の道通損失は次式で表されます。

$$B_{;E} \approx (\zeta_{A36(D^2E)})^2 \times D_{DE@}$$

ハイサイド・スイッチのターンオフとローサイド・スイッチのターンオンの間に、ローサイド MOSFET のボディ・ダイオードに出力電流が流れたとき、デッド・タイムと呼ばれる時間内に追加電力損失が発生します。ボディ・ダイオードの電力損失は次式で与えられます。

$$B_{4A6K6;A67} = H_8 \times f_6 \times X_H \times ;_A$$

ここで、

$V_F$  はボディ・ダイオードの順方向電圧降下で、0.7 V (typ)。

$t_D$  は ADP1851 のデッド・タイムで、入力容量  $C_{ISS}$  が約 3 nF の中サイズの MOSFET を駆動する場合 25 ns (typ)。

デッド・タイムは固定ではありません。その実効値はゲート駆動抵抗と  $C_{ISS}$  により変わるために、 $P_{BODYDIODE}$  は高負荷電流デザインと低電圧デザインで大きくなります。

このため、ローサイド MOSFET の電力損失は次式で与えられます。

$$B_{>E} = B_{5,E} \# B_{BA6K6;A67}$$

MOSFET のオン抵抗  $R_{DS(ON)}$  は、温度上昇とともに大きくなり、温度係数(typ)は 0.4%/°C です。MOSFET のジャンクション温度 ( $T_J$ ) は周囲温度より高くなります。

$$T_J = T_A + \theta_{JA} \times P_D$$

ここで、

$T_A$  は周囲温度。

$\theta_{JA}$  は MOSFET パッケージの熱抵抗。

$P_D$  は MOSFET の合計電力損失。

## ループ補償—電圧モード

DL と PGND の間に 100 kΩ 抵抗を接続して、コントローラを電圧モード動作に設定します。1.5 V 以下の電圧モードに対して可能な最大ランプ振幅を選択してください。ランプ電圧は、 $V_{IN}$  と RAMP ピンの間に次の抵抗値を接続して設定します。

$$D_{DB?B} = \frac{H_{\#} - 0.2 \text{ V}}{100 \text{ pF} \times X_H \times H_{DB?B}}$$

RAMP ピンの電圧は固定 0.2 V で、RAMP に流れる電流は 10 μA ~160 μA である必要があります。次の条件を満たしていることを確認してください。

$$10 \mu\text{A} \leq \frac{H_{\#} - 0.2 \text{ V}}{D_{R3?B}} \leq 160 \mu\text{A} \quad (3)$$

例えば、入力電圧=12 V の場合、 $R_{RAMP}$  は 73.8 kΩ 以上である必要があります。

LC フィルタ・デザインが完全であるとすると、帰還制御システムを補償することができます。一般に、アルミニウム電解コンデンサは高い ESR を持ちますが、複数のアルミニウム電解コンデンサを並列接続すると、実効 ESR が小さくなるので、Type III 補償が必要になります。さらに、セラミック・コンデンサの ESR は非常に小さいので(数 mΩ)、Type III 補償が優れた選択肢になります。

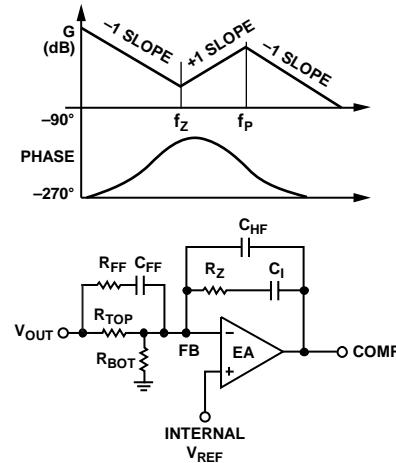

## Type III 補償

10595-026

図 26.Type III 補償

出力コンデンサの ESR ゼロ周波数がクロスオーバー周波数の 1/2 より大きい場合、Type III を図 26 のように使います。

出力 LC フィルタの共振周波数を次のように計算します。

$$X_5 = \frac{1}{2 \sqrt{5}} \quad (4)$$

スイッチング周波数の 1/10 のクロスオーバー周波数を選択します。

$$X_A = \frac{X_5}{10} \quad (5)$$

極とゼロ点を次のように設定します。

$$X = X_S = \frac{1}{2} X_A \quad (6)$$

$$X_{\#} = X_S = \frac{X_A}{4} = \frac{X}{40} = \frac{1}{2\pi D_L 5} \quad (7)$$

または

$$X = X_S = \frac{X_5}{2} = \frac{1}{2\pi D_L 5} \quad (8)$$

式 7 または式 8 の低いほうのゼロ周波数を使います。補償抵抗  $R_Z$  を次のように計算します。

$$D_L = \frac{D_{FAB} H_{DB?B} X_{\#} X_A}{H_{\#} X_5^2} \quad (9)$$

次に、 $C_L$  を計算します。

$$5 = \frac{1}{2\pi D_L X_{\#}} \quad (10)$$

誤差アンプの出力電流駆動能力は有限であるため、 $C_L$  は 10 nF 以下である必要があります。 $C_L$  が 10 nF より大きい場合は、大きな  $R_{TOP}$  を選択して、 $C_L$  が 10 nF 以下になるまで  $R_Z$  と  $C_L$  を再計算します。

$C_{HF} \ll C_L$  であるため、 $C_{HF}$  を次のように計算します。

$A_{CS}$ は電流検出アンプのゲイン。

$V_{COMP MAX}$ はCOMPピンの最大電圧。

$t_{ON}$ はハイサイド・ドライバ(DH)のオン時間。

電流検出エレメントを使用する場合、 $R_{DS0N}$ を電流検出エレメントの抵抗値 $R_{CS}$ で置き換えてください。

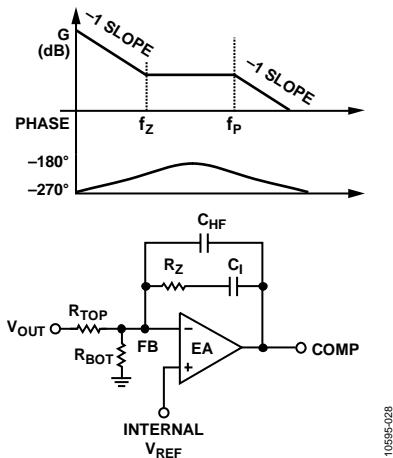

### Type II 補償

図 28.Type II 補償

Type II 補償の場合、図 28 の回路を使用してください。補償抵抗 $R_Z$ は次式を使って計算します。

$$D_L = D_{FAB} \times D_E \times 2\pi \times 5_{AGF} \times X_A \quad (13)$$

ここで、

$f_{CO}$ は $f_{SW}$ の1/10。

$R_S = A_{CS} \times R_{DS0N\_MIN}$

$A_{CS}$ は、電流検出アンプ・ゲイン3V/V、6V/V、または12V/Vで、DLとPGNDの間に接続するゲイン抵抗で設定されます。

電流を電流検出抵抗 $R_{CS}$ で検出する場合、 $R_S$ は次のようにになります。

$$D_E = 3_{SE} \times D_{CE}$$

次に、補償コンデンサを選択して、ゼロ点補償 $f_{ZI}$ をクロスオーバー周波数の1/5以下またはLC共振周波数の1/2以下に設定します。

$$X_I = \frac{X_A}{5} = \frac{X}{50} = \frac{1}{2\pi D_L 5} \quad (14)$$

または

$$X_{\#} = \frac{X_5}{2} = \frac{1}{2\pi D_L 5} \quad (15)$$

式 14 の  $C_I$ について解くと、

$$5_{\#} = \frac{25}{\pi D_L X} \quad (16)$$

式 15 の  $C_I$ について解くと、

$$5_{\#} = \frac{1}{\pi D_L X_5} \quad (17)$$

式 16 または式 17 から大きい方の  $C_I$  値を使います。誤差アンプの出力電流駆動能力は有限であるため、 $C_I$  は 10 nF 以下である必要があります。 $C_I$  が 10 nF より大きい場合は、大きな  $R_{TOP}$  を選択して、 $C_I$  が 10 nF 以下になるまで  $R_Z$  と  $C_I$  を再計算します。次に、高い周波数の極  $f_{PI}$  を  $f_{SW}$  の 1/2 に選択します。

$$X_{B\#} = \frac{1}{2} X_H \quad (18)$$

$C_{HF} \ll C_I$  であるため、

$$X_{B\#} = \frac{1}{2\pi D_L 5} \quad (19)$$

式 18 と式 19 を組み合わせて、 $C_{HF}$ について解くと

$$5_{\#} = \frac{1}{\pi X_H D_L} \quad (20)$$

正確な補償が必要な場合には、[ADIsimPower](#) デザイン・ツールを使用してください。

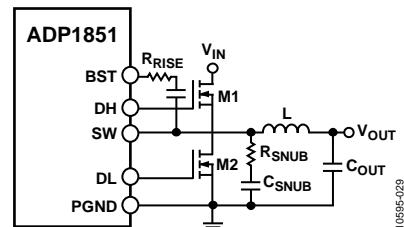

### スイッチング・ノイズとオーバーシュートの削減

電圧リングとノイズを小さくするためには、高電流アプリケーションでは SW と PGND の間に RC スナバを接続することが推奨されます(図 29 参照)。

大部分のアプリケーションでは、 $R_{SNUB}$  は 2 Ω~4 Ω (typ)、 $C_{SNUB}$  は 1.2 nF~3 nF (typ) です。

RC スナバ回路部品のサイズは、消費電力を処理できるように適切に選択する必要があります。 $R_{SNUB}$  での消費電力は、

$$R_{E2G4} = H_{E2}^2 \times 5_{E2G4} \times X$$

大部分のアプリケーションでは、 $R_{SNUB}$  の部品サイズは 0805 で十分です。RC スナバ回路は電圧オーバーシュートを小さくすることはできません。図 29 に  $R_{RISE}$  で示す抵抗を BST ピンに使用すると、オーバーシュートの削減に役立ち、一般に 2 Ω~4 Ω の値が使用されます。2 Ω~4 Ω (typ) の抵抗をゲート・ドライバに直列に接続することも、オーバーシュートの削減に役立ちます。ゲート抵抗を接続する場合、 $R_{RISE}$  は不要です。

図 29.スナバ回路を使用するアプリケーション回路

## 電圧のトラッキング

ADP1851 は、マスター電圧に追従する(トラッキングする)機能を内蔵しています。すべてのトラッキング構成で、与えられた動作条件に対して出力を最小 0.6 V に設定することができます。

ADP1851 では、同時トラッキングと比例トラッキングの 2 種類のトラッキング構成が可能です。

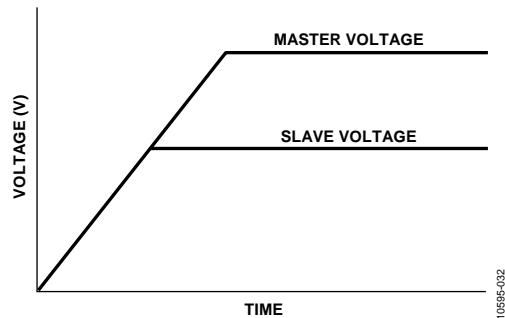

### 同時トラッキング

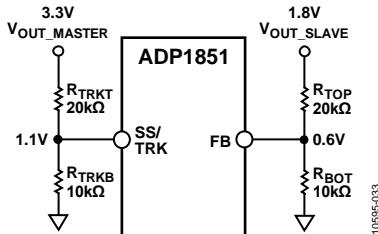

多くの一般的なアプリケーションは、コアと I/O 電圧との間のシーケンシングで使用される同時トラッキングおよび同様のアプリケーションです。図 30 に示すように、同時トラッキングでは、スレーブ出力がレギュレーション電圧に到達するまで、出力電圧のランプ・レートをマスターとスレーブ間で一致させます。スレーブの SS/TRK 入力をマスター電圧からの抵抗分圧器(スレーブ FB ピンで使用される分圧器と同じ)に接続します。これにより、スレーブ電圧はマスター電圧と強制的に一致させられます。同時トラッキングの場合、 $R_{TRKT} = R_{TOP}$ かつ  $R_{TRKB} = R_{BOT}$ に設定します(図 31 参照)。

図 30. 同時トラッキング

図 31. 同時トラッキング回路の例

マスター電圧に対するスレーブ出力電圧の比は、次式のように 2 つの分圧器の関数になります。

$$\frac{H_{AGF\_E-3H7}}{H_{AGF\_?3H7D}} = \frac{\left(1 + \frac{D_{FAB}}{D_{4AF}}\right)}{\left(1 + \frac{D_{FD-F}}{D_{TD-4}}\right)}$$

マスター電圧が上昇すると、スレーブ電圧も同じように上昇します。最終的に、スレーブ電圧がレギュレーション電圧に到達すると、内蔵リファレンス電圧がレギュレーションを引き継ぎますが、SS/TRK 入力が上昇を続ける間は、出力電圧の制御を停止しています。

SS/TRK ピン電圧を 0.6 V(typ)のリファレンス電圧  $V_{FB}$  に近づきさせ過ぎて、出力電圧精度を損なわないように、スレーブ・チャンネルの SS/TRK 電圧の最終値を  $V_{FB}$  より少なくとも 30 mV 高いことを確認してください。

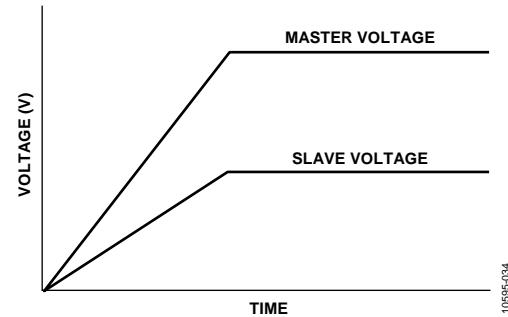

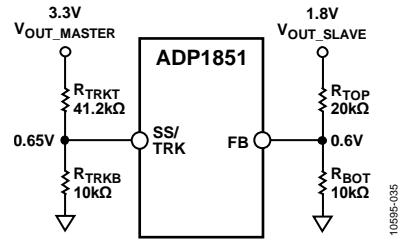

### 比例トラッキング

比例トラッキングでは、図 32 と図 33 に示すように、出力電圧をマスター電圧の整数分の 1 に制限します。スレーブ・チャンネルの最終 SS/TRK 電圧は、 $V_{FB}$  より少なくとも 30 mV 高く設定する必要があります。

図 32. 比例トラッキング

図 33. 比例トラッキング回路の例

### PCB レイアウトのガイドライン

同期整流降圧コントローラのボード・レイアウト推奨事項は [AN-1119](#) アプリケーション・ノートに記載してあります。

## 代表的な動作回路

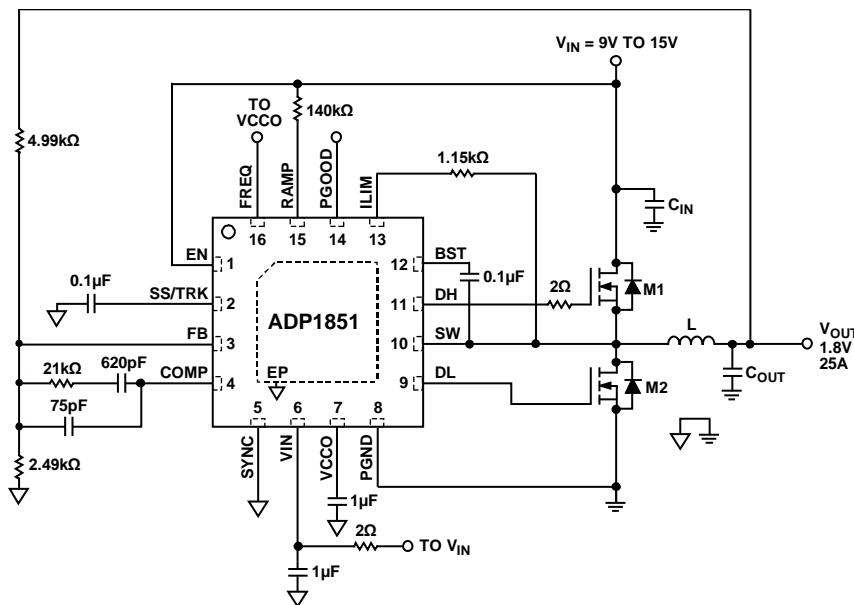

図 34. 電流モードで動作する 25 A 回路

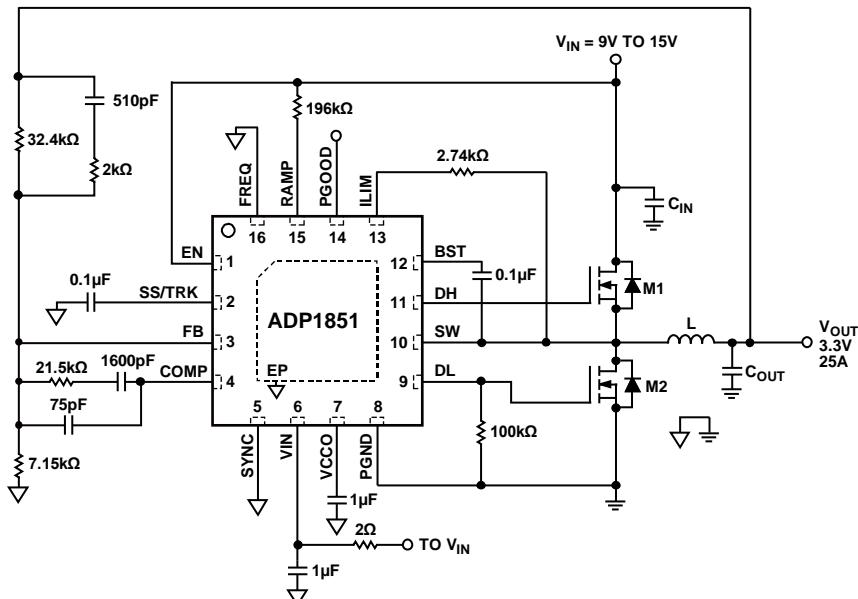

図 35. 電圧モードで動作する 25 A 回路

## 外形寸法

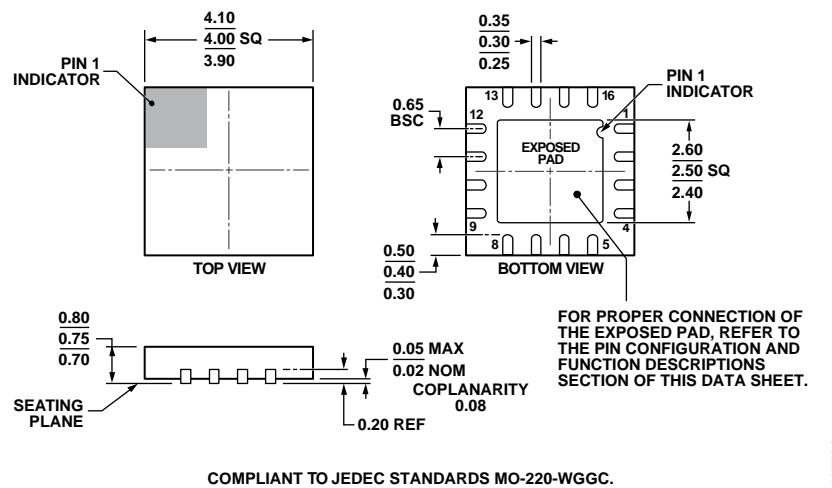

図 36.16 ピン・リードフレーム・チップ・スケール・パッケージ[LFCSP\_WQ]

4 mm x 4 mm ボディ、極薄クワッド

(CP-16-26)

寸法: mm

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                              | Package Option |

|--------------------|-------------------|--------------------------------------------------|----------------|

| ADP1851ACPZ-R7     | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-16-26       |

| ADP1851-EVALZ      |                   | Evaluation Board: 1.8 V, 25 A Output             |                |

<sup>1</sup> Z = RoHS 準拠製品。