# シグナル・シグナル・スイッチ4個内蔵の 500 mAロード・スイッチ

## データシート

ADP1190A

### 特長

低い入力電圧範囲: 1.4 V~3.6 V

ロード・スイッチ

低 RDS<sub>ON</sub>: 3.6 V で 65 mΩ

連続動作電流: 500 mA

4 個の SPST ノーマル・オープン・シグナル・スイッチを内蔵

1.8 V で RDS<sub>ON,S</sub> = 3 Ω

シグナル・スイッチの RDS<sub>ON</sub> を一定にするためチャージ・ポンプを内蔵

出力放電抵抗 (R<sub>DIS</sub>): ロード・スイッチ出力側と各アナログ・シグナル・スイッチ出力で 215 Ω

制御ロジックにレベル・シフトを内蔵し、1.2 V ロジックで動作可能

超低シャットダウン電流: 0.7 μA

超小型 1.2 mm × 1.6 mm × 0.5 mm、12 ポール、0.4 mm ピッチの WLCSP パッケージを採用

### アプリケーション

携帯電話

SIM カード切断スイッチ

デジタル・カメラおよびオーディオ機器

ポータブル型およびバッテリ駆動の装置

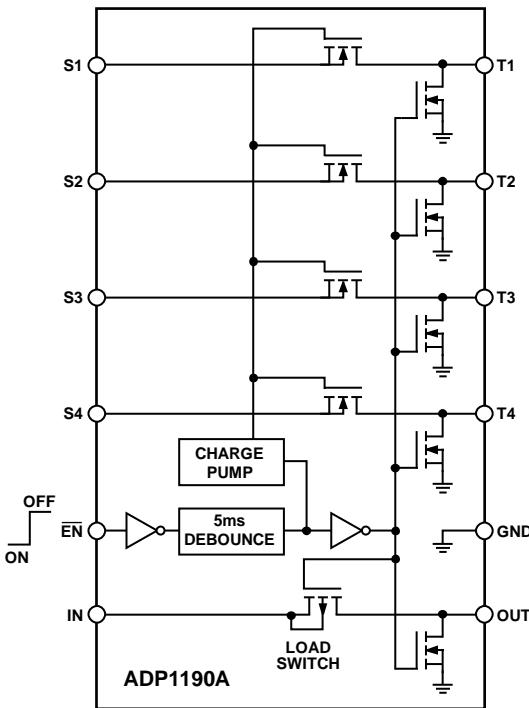

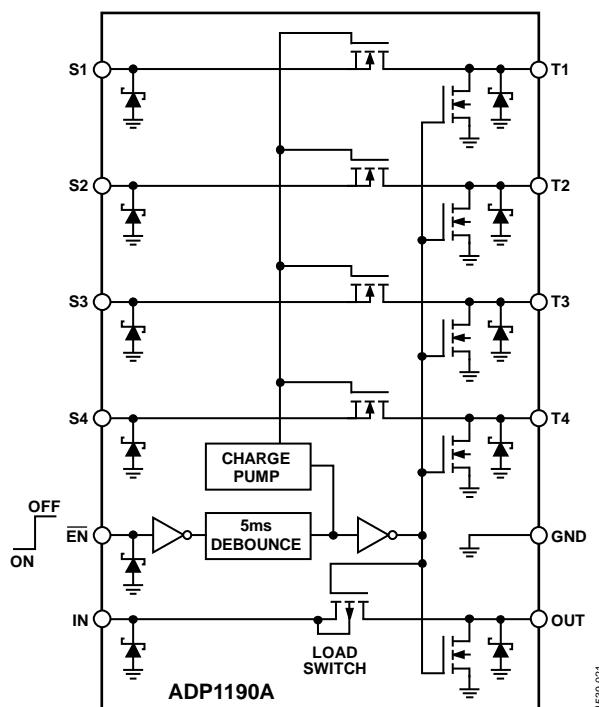

### 機能ブロック図

11539-001

図 1.

### 概要

ADP1190A は、1.4 V~3.6 V で動作するようにデザインされた 4 個のシグナル・スイッチを内蔵するハイサイドロード・スイッチです。このロード・スイッチは、バッテリ寿命を延ばすための電源領域アイソレーションを提供します。このロード・スイッチは、500 mA までの連続負荷電流をサポートし、消費電力を小さくする低いオン抵抗を持つ P チャンネル MOSFET で構成されています。ロード・スイッチと組み合わせて、チャージ・ポンプから制御されるノーマル・オープンの 3 Ω 単極単投 (SPST) シグナル・スイッチを 4 個内蔵しています。

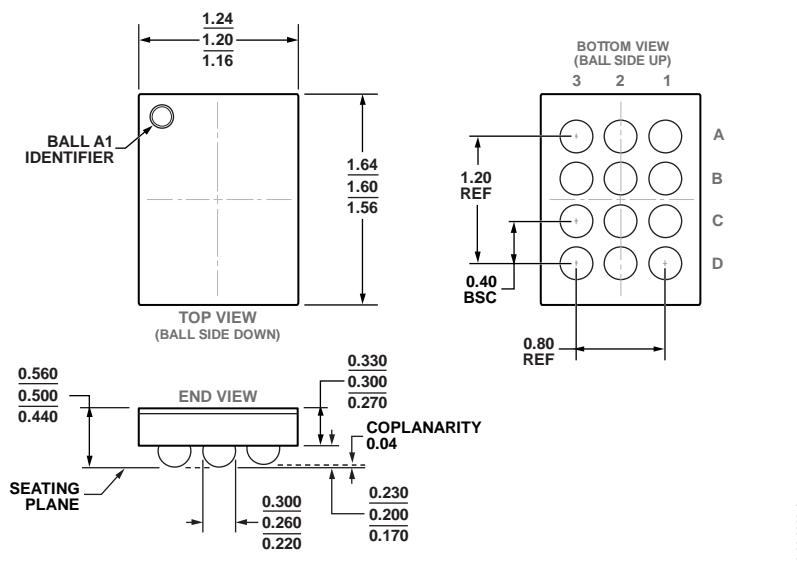

ADP1190A は、優れた動作性能の外に、0.50 mm<sup>2</sup> 以下の面積と 0.50 mm の高さにより、プリント回路ボード(PCB)の所要スペースが最小で済みます。ADP1190A は、超小型の 1.2 mm × 1.6 mm × 0.5 mm、12 ポール、0.4 mm ピッチの WLCSP パッケージを採用しています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|          |   |               |    |

|----------|---|---------------|----|

| 特長       | 1 | ピン配置およびピン機能説明 | 5  |

| アプリケーション | 1 | 代表的な性能特性      | 6  |

| 機能ブロック図  | 1 | 動作原理          | 9  |

| 概要       | 1 | 外形寸法          | 11 |

| 改訂履歴     | 2 | オーダー・ガイド      | 11 |

| 仕様       | 3 |               |    |

| 絶対最大定格   | 4 |               |    |

| 熱データ     | 4 |               |    |

| 熱抵抗      | 4 |               |    |

| ESD の注意  | 4 |               |    |

## 改訂履歴

9/13—Revision 0: Initial Version

## 仕様

特に指定がない限り、 $V_{IN} = 1.8 \text{ V}$ 、 $V_{EN} = V_{IN}$ 、 $I_{LOAD} = 200 \text{ mA}$ 、 $C_{IN} = C_{OUT} = 1 \mu\text{F}$ 、 $T_A = 25^\circ\text{C}$ 。

表 1.

| Parameter                                     | Symbol               | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Min  | Typ | Max  | Unit             |

|-----------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------------------|

| INPUT VOLTAGE RANGE                           | $V_{IN}$             | $T_J = -40^\circ\text{C}$ to $+85^\circ\text{C}$                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.4  | 3.6 |      | V                |

| EN INPUT                                      |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |     |      |                  |

| EN Input Threshold                            | $V_{EN\_TH}$         | $1.4 \text{ V} < V_{IN} < 1.8 \text{ V}$ , $T_J = -40^\circ\text{C}$ to $+85^\circ\text{C}$ (active low)<br>$1.8 \text{ V} \leq V_{IN} \leq 3.6 \text{ V}$ , $T_J = -40^\circ\text{C}$ to $+85^\circ\text{C}$ (active low)                                                                                                                                                                                                                                                                  | 0.35 | 1.2 |      | V                |

| Logic High Voltage                            | $V_{IH}$             | $1.4 \text{ V} \leq V_{IN} \leq 3.6 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.45 | 1.2 |      | V                |

| Logic Low Voltage                             | $V_{IL}$             | $1.4 \text{ V} \leq V_{IN} \leq 3.6 \text{ V}$ (chip enable)                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.2  |     | 0.35 | V                |

| CURRENT                                       |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |     |      |                  |

| Shutdown Current                              | $I_{OFF}$            | $\overline{EN} = V_{IN}$ or open<br>$\overline{EN} = V_{IN}$ or open, $T_J = -40^\circ\text{C}$ to $+85^\circ\text{C}$                                                                                                                                                                                                                                                                                                                                                                      |      | 0.7 |      | $\mu\text{A}$    |

| Analog Switch Off Current                     | $I_{A\_OFF}$         | Into S1, $\overline{EN} = V_{IN}$                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | 2   |      | $\mu\text{A}$    |

| 0.2                                           |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |     |      | $\mu\text{A}$    |

| LOAD SWITCH, $V_{IN}$ TO $V_{OUT}$ RESISTANCE | $R_{DS_{ON\_L}}$     | $V_{IN} = 3.6 \text{ V}$ , $I_{LOAD} = 200 \text{ mA}$ , $\overline{EN} = \text{GND}$<br>$V_{IN} = 2.5 \text{ V}$ , $I_{LOAD} = 200 \text{ mA}$ , $\overline{EN} = \text{GND}$<br>$V_{IN} = 1.8 \text{ V}$ , $I_{LOAD} = 200 \text{ mA}$ , $\overline{EN} = \text{GND}$ , $T_J = -40^\circ\text{C}$ to $+85^\circ\text{C}$                                                                                                                                                                  | 65   |     |      | $\text{m}\Omega$ |

| SIGNAL SWITCH RESISTANCE                      | $R_{DS_{ON\_S}}$     | Maximum value of analog input sweep<br>$V_{IN} = 3.6 \text{ V}$ , $I_{LOAD} = 10 \text{ mA}$ , $\overline{EN} = \text{GND}$<br>$V_{IN} = 2.5 \text{ V}$ , $I_{LOAD} = 10 \text{ mA}$ , $\overline{EN} = \text{GND}$<br>$V_{IN} = 1.8 \text{ V}$ , $I_{LOAD} = 10 \text{ mA}$ , $\overline{EN} = \text{GND}$<br>$V_{IN} = 3.6 \text{ V}$ , $I_{LOAD} = 10 \text{ mA}$ , $\overline{EN} = \text{GND}$<br>$V_{IN} = 1.8 \text{ V}$ , $I_{LOAD} = 10 \text{ mA}$ , $\overline{EN} = \text{GND}$ | 3    |     |      | $\Omega$         |

| RDS Flatness                                  |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3    |     |      | $\Omega$         |

|                                               |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3    |     |      | $\Omega$         |

|                                               |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.2  |     |      | $\Omega$         |

|                                               |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.2  |     |      | $\Omega$         |

| SIGNAL SWITCH INPUT CAPACITANCE               | $C_{IN}$             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10   |     |      | $\text{pF}$      |

| OUTPUT DISCHARGE RESISTANCE                   | $R_{DIS}$            | At the output side of the load switch and each analog signal switch output, T1, T2, T3, and T4                                                                                                                                                                                                                                                                                                                                                                                              | 215  |     |      | $\Omega$         |

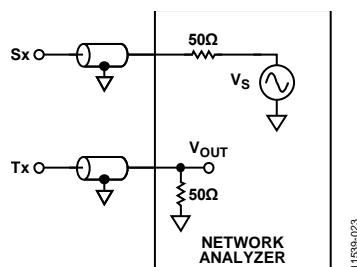

| -3 dB BANDWIDTH                               | $BW_{-3 \text{ dB}}$ | $V_{IN} = 3.3 \text{ V}$ , $R_{LOAD} = 50 \Omega$ , $C_{LOAD} = 5 \text{ pF}$                                                                                                                                                                                                                                                                                                                                                                                                               | 50   |     |      | MHz              |

| $V_{OUT}$ TIME                                |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |     |      |                  |

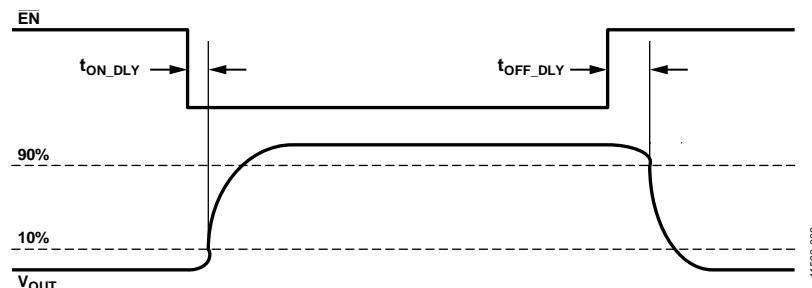

| Turn-On Delay Time                            | $t_{ON\_DLY}$        | $I_{LOAD} = 200 \text{ mA}$ , $\overline{EN} = \text{GND}$ , $C_{LOAD} = 0.1 \mu\text{F}$                                                                                                                                                                                                                                                                                                                                                                                                   | 5    |     |      | ms               |

| Turn-Off Delay Time                           | $t_{OFF\_DLY}$       | $V_{IN} = 3.6 \text{ V}$ , $I_{LOAD} = 200 \text{ mA}$ , $\overline{EN} = 1.5 \text{ V}$ , $C_{LOAD} = 0.1 \mu\text{F}$                                                                                                                                                                                                                                                                                                                                                                     | 2    |     |      | $\mu\text{s}$    |

タイミング図

図 2. タイミング図

## 絶対最大定格

表 2.

| Parameter                                               | Rating                    |

|---------------------------------------------------------|---------------------------|

| V <sub>IN</sub> to GND                                  | -0.3 V to +4.0 V          |

| V <sub>OUT</sub> to GND                                 | -0.3 V to V <sub>IN</sub> |

| Sx to GND                                               | -0.3 V to +4.0 V          |

| Tx to GND                                               | -0.3 V to +4.0 V          |

| EN to GND                                               | -0.3 V to +4.0 V          |

| Continuous Load Switch Current<br>T <sub>A</sub> = 25°C | ±1 A                      |

| T <sub>A</sub> = 85°C                                   | ±500 mA                   |

| Continuous Diode Current                                | -50 mA                    |

| Storage Temperature Range                               | -65°C to +150°C           |

| Junction Temperature                                    | 150°C                     |

| Operating Temperature Range                             | -40°C to +125°C           |

| Junction Temperature Range                              | -40°C to +85°C            |

| Ambient Temperature Range                               | -40°C to +85°C            |

| Soldering Conditions                                    | JEDEC J-STD-020           |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

## 熱データ

絶対最大定格は、組み合わせではなく個別に適用されます。ジャンクション温度を超えると ADP1190A は損傷を受けることがあります。周囲温度をモニタしても、ジャンクション温度(T<sub>J</sub>)が規定温度範囲内にあることを保証できません。消費電力が大きくかつ熱抵抗が高いアプリケーションでは、最大周囲温度を下げる必要があります。

中程度の消費電力で、PCB の熱抵抗が低いアプリケーションでは、ジャンクション温度が規定値内にある限り、最大周囲温度はこの最大値を超えても問題はありません。デバイスの T<sub>J</sub> は、周囲温度 (T<sub>A</sub>)、デバイス消費電力 (P<sub>D</sub>)、パッケージのジャンクション—周囲間熱抵抗 ( $\theta_{JA}$ ) に依存します。

最大 T<sub>J</sub> は次式を使って T<sub>A</sub> と P<sub>D</sub> から計算されます。

$$T_J = T_A + (P_D \times \theta_{JA})$$

パッケージのジャンクション—周囲間の熱抵抗( $\theta_{JA}$ ) は 4 層ボードを使用したモデルと計算に基づいています。ジャンクション—周囲間の熱抵抗は、アプリケーションとボード・レイアウトに強く依存します。最大消費電力が大きいアプリケーションでは、ボードの熱設計に注意が必要です。 $\theta_{JA}$  の値は、PCB の材料、レイアウト、環境条件に応じて変わります。 $\theta_{JA}$  の既定値は、4 層、4 インチ × 3 インチの回路ボードに基づきます。ボード構造については JESD51-7 と JESD51-9 を参照してください。その他の情報については、[AN-617](#) アプリケーション・ノート「Wafer Level Chip Scale Package」を参照してください。

$\Psi_{JB}$  はジャンクション—ボード間サーマル・キャラクタライゼーション・パラメータであり、単位は°C/W です。パッケージの  $\Psi_{JB}$  は、4 層ボードを使ったモデルと計算に基づいています。

JESD51-12 「Guidelines for Reporting and Using Electronic Package Thermal Information」には、サーマル・キャラクタライゼーション・パラメータは熱抵抗と同じではないと記載されています。 $\Psi_{JB}$  は、熱抵抗 ( $\theta_{JB}$ ) の場合のように 1 つのパスではなく、複数のサーマル・パスを経由する成分を表します。したがって、 $\Psi_{JB}$  サーマル・パスには、パッケージ上面からの対流、パッケージからの放射、実際のアプリケーションで  $\Psi_{JB}$  を有効にしているファクタが含まれます。最大 T<sub>J</sub> は次式を使ってボード温度 (T<sub>B</sub>) と P<sub>D</sub> から計算されます。

$$T_J = T_B + (P_D \times \Psi_{JB})$$

$\Psi_{JB}$  の詳細については、JESD51-8 と JESD51-12 を参照してください。

## 熱抵抗

$\theta_{JA}$  と  $\Psi_{JB}$  はワーストケース条件で規定。すなわち表面実装パッケージの場合、デバイスを回路ボードにハンダ付けした状態で規定。

表 3. 热抵抗

| Package Type  | $\theta_{JA}$ | $\Psi_{JB}$ | Unit |

|---------------|---------------|-------------|------|

| 12-Ball WLCSP | 130           | 29.2        | °C/W |

## ESD の注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

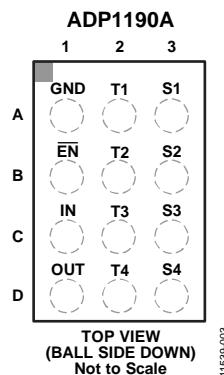

## ピン配置およびピン機能説明

図 3. ピン配置

表 4. ピン機能の説明

| ピン番号 | 記号  | 説明                                                      |

|------|-----|---------------------------------------------------------|

| A1   | GND | グラウンド。                                                  |

| B1   | EN  | アクティブ・ローのイネーブル入力。                                       |

| C1   | IN  | 入力電圧。                                                   |

| D1   | OUT | ロード・スイッチ出力電圧。                                           |

| A2   | T1  | チャンネル1 アナログ・スイッチ。ピン A2 と SIM カード・ソケット(アクティブ放電あり)を接続します。 |

| B2   | T2  | チャンネル2 アナログ・スイッチ。ピン B2 と SIM カード・ソケット(アクティブ放電あり)を接続します。 |

| C2   | T3  | チャンネル3 アナログ・スイッチ。ピン C2 と SIM カード・ソケット(アクティブ放電あり)を接続します。 |

| D2   | T4  | チャンネル4 アナログ・スイッチ。ピン D2 と SIM カード・ソケット(アクティブ放電あり)を接続します。 |

| A3   | S1  | チャンネル1 アナログ・スイッチ。ピン A3 をマイクロコントローラへ接続します。               |

| B3   | S2  | チャンネル2 アナログ・スイッチ。ピン B3 をマイクロコントローラへ接続します。               |

| C3   | S3  | チャンネル3 アナログ・スイッチ。ピン C3 をマイクロコントローラへ接続します。               |

| D3   | S4  | チャンネル4 アナログ・スイッチ。ピン D3 をマイクロコントローラへ接続します。               |

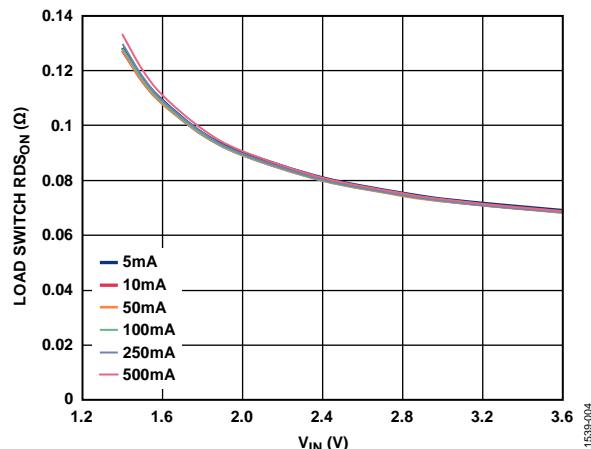

## 代表的な性能特性

特に指定がない限り、 $V_{IN} = 1.8\text{ V}$ 、 $V_{EN} = V_{IN}$ 、 $I_{LOAD} = 200\text{ mA}$ 、 $C_{IN} = C_{OUT} = 1\text{ }\mu\text{F}$ 、 $T_A = 25^\circ\text{C}$ 。

図 4. 様々な負荷電流での入力電圧 ( $V_{IN}$ ) 対ロード・スイッチ  $RDS_{ON}$

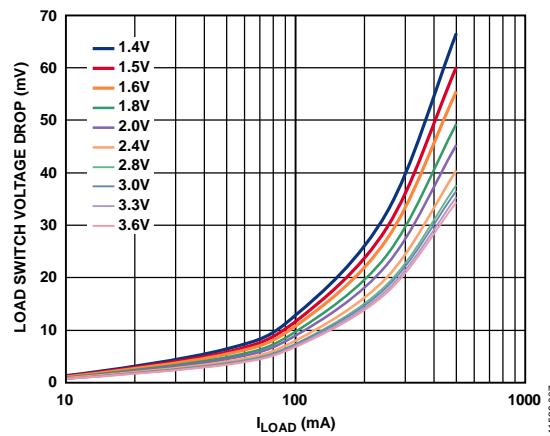

図 7. 様々な入力電圧での負荷電流 ( $I_{LOAD}$ ) 対

ロード・スイッチ電圧降下

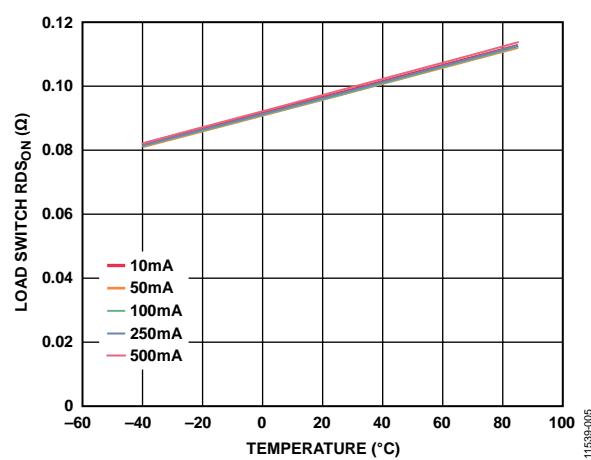

図 5. 様々な負荷電流でのロード・スイッチ  $RDS_{ON}$  の温度特性

$V_{IN} = 1.8\text{ V}$

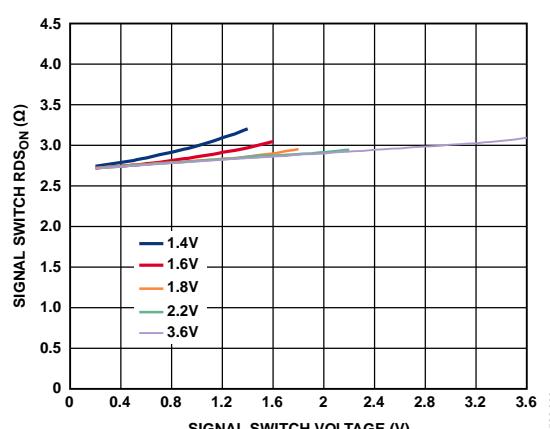

図 8. 様々な入力電圧でのシグナル・スイッチ電圧対

シグナル・スイッチ  $RDS_{ON}$

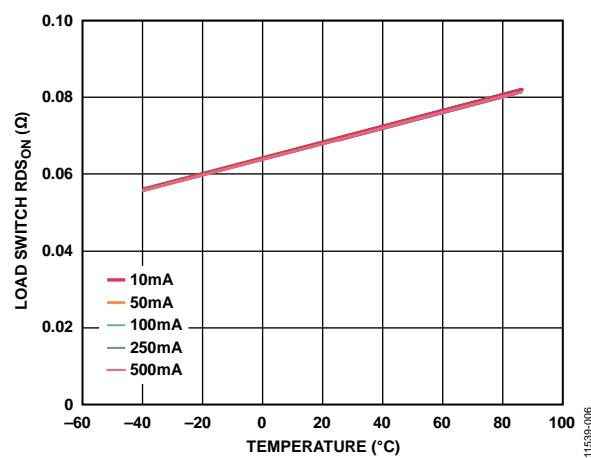

図 6. 様々な負荷電流でのロード・スイッチ  $RDS_{ON}$  の温度特性

$V_{IN} = 3.6\text{ V}$

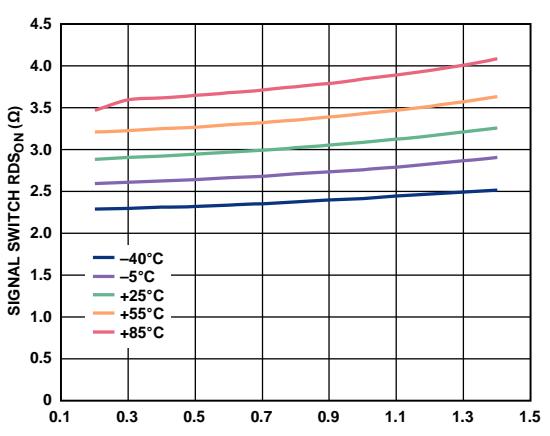

図 9. 様々な温度でのシグナル・スイッチ電圧対

シグナル・スイッチ  $RDS_{ON}$

$V_{IN} = 1.4\text{ V}$

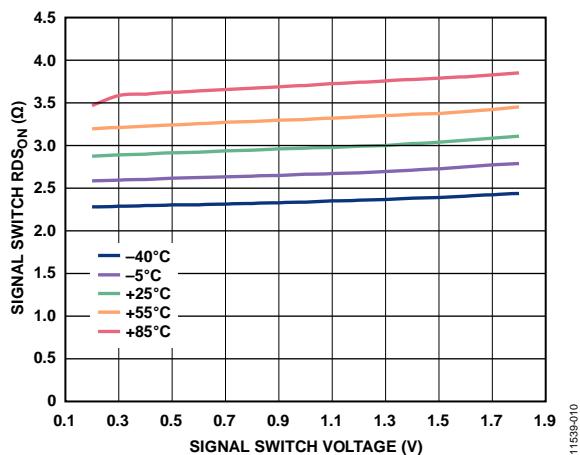

図 10. 様々な温度でのシグナル・スイッチ電圧対シグナル・スイッチ RDS<sub>ON</sub>

$V_{IN} = 1.8\text{ V}$

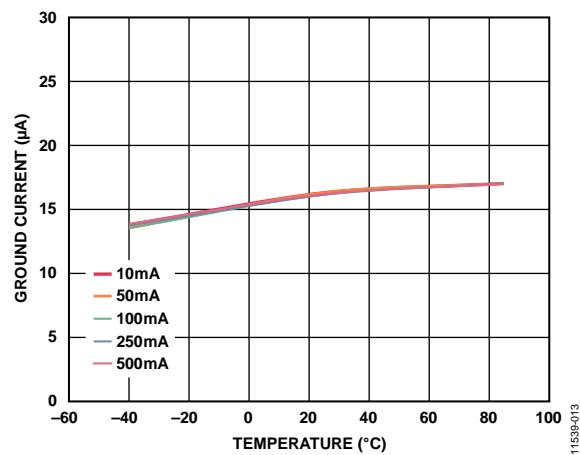

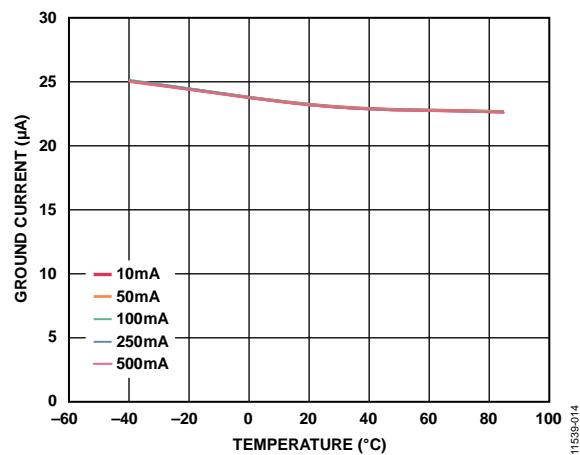

図 13. 様々な負荷電流でのグラウンド電流の温度特性

$V_{IN} = 1.8\text{ V}$

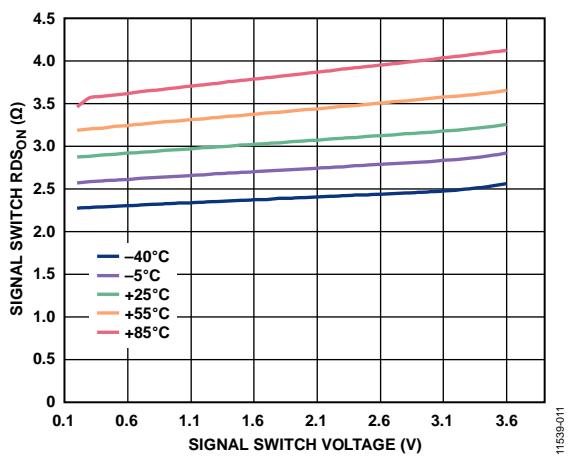

図 11. 様々な温度でのシグナル・スイッチ電圧対シグナル・スイッチ RDS<sub>ON</sub>

$V_{IN} = 3.6\text{ V}$

図 14. 様々な負荷電流でのグラウンド電流の温度特性

$V_{IN} = 3.6\text{ V}$

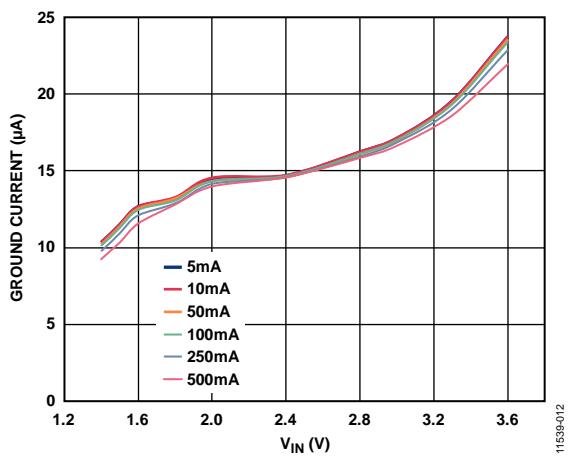

図 12. 様々な負荷電流での入力電圧 ( $V_{IN}$ )対グラウンド電流

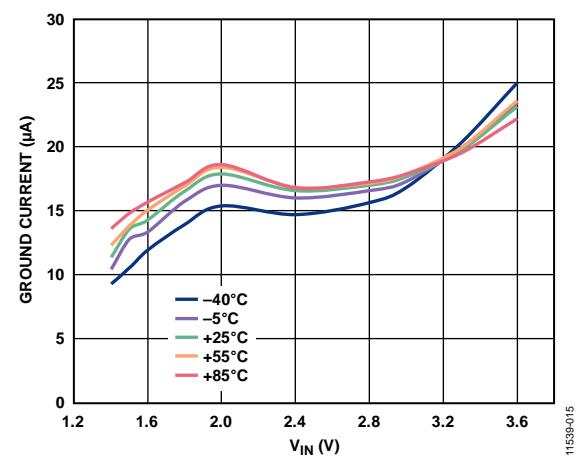

図 15. 様々な温度での入力電圧 ( $V_{IN}$ )対無負荷グラウンド電流

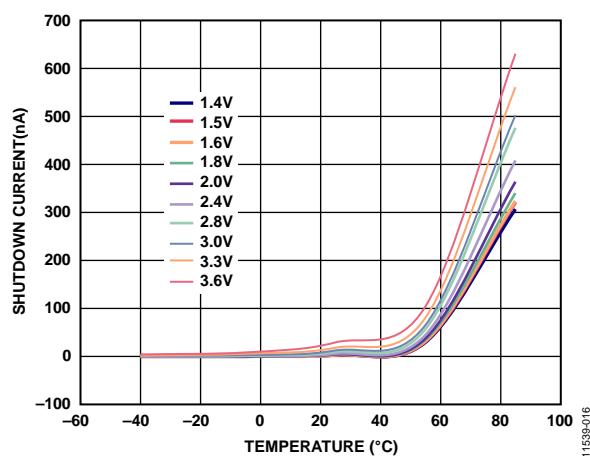

図 16. 様々な入力電圧でのシャットダウン電流の温度特性

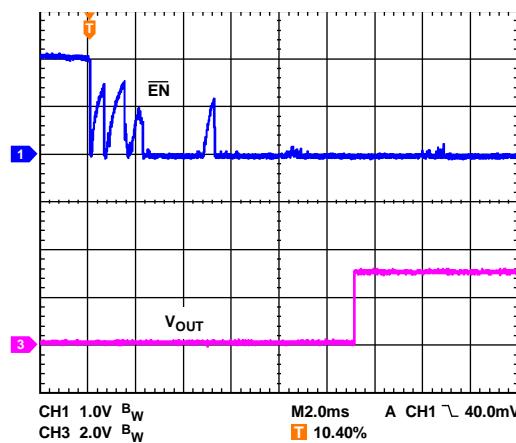

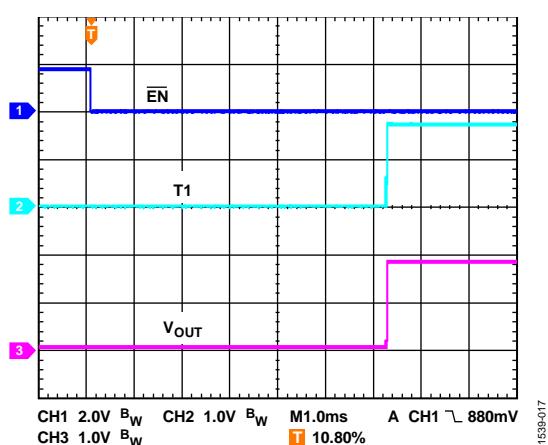

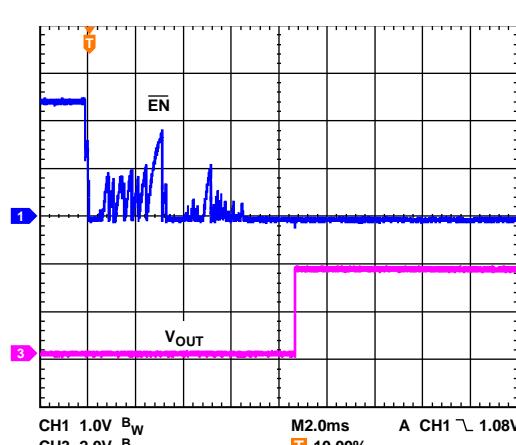

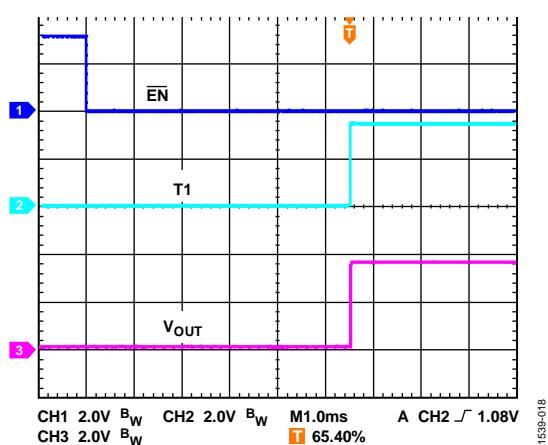

図 19. イネーブルのデバウンス動作、 $V_{IN} = 1.8\text{ V}$ 図 17. ターンオン遅延時間、 $V_{IN} = 1.8\text{ V}$ 、50 mA 負荷図 20. イネーブルのデバウンス動作、 $V_{IN} = 3.6\text{ V}$ 図 18. ターンオン遅延時間、 $V_{IN} = 3.6\text{ V}$ 、100 mA 負荷

## 動作原理

ADP1190Aは、4個のシグナル・スイッチを内蔵するハイサイドロード・スイッチです。ロード・スイッチとシグナル・スイッチは、EN ピンをロー・レベルにするとターンオンします。デバイスをディスエーブルすると、T1~T4 ピンは $215\Omega$ の公称抵抗でアクティブにプルダウンされます。ENには、機械的なENスイッチと組み合わせて使用するために5 ms のデバウンス・カウンタが設けてあります。すなわち、ENが5 ms間ロー・レベルを維持した後にデバイスがイネーブルされます。このタイムアウトの前にENが変化すると、カウンタがリセットされて、新しい5 msのカウントが開始されます。

信号パスは、 $3\Omega$ のオン抵抗を持つNチャンネル MOSFETで構成されています。ブレーク・ビフォア・メーク・ロジック制御により、アクティブ・プルダウンが確実にオフした後に、信号パスをイネーブルすることが保証されます。

また、ADP1190AはNチャンネル MOSFETのゲートに安定化電圧を供給するチャージ・ポンプを内蔵しているため、様々な入力電圧と温度に対して安定なシグナル・スイッチ・オン抵抗を実現しています。

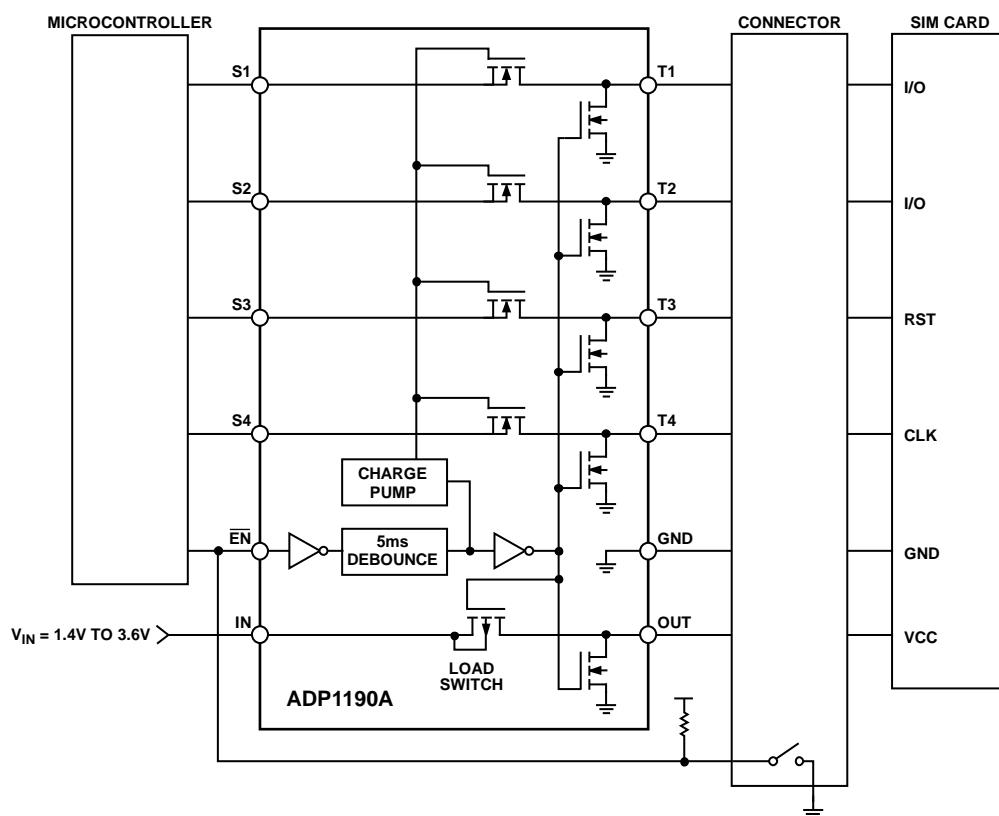

図 21. ESD 保護デバイス付きのブロック図

11539-021

11539-022

図 22. 代表的なアプリケーション図

11539-023

図 23. 帯域幅測定のセットアップ

## 外形寸法

図 24.12 ボール・ウェハー・レベル・チップ・スケール・パッケージ[WLCSP]

(CB-12-10)

寸法: mm

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                            | Package Option | Branding |

|--------------------|-------------------|------------------------------------------------|----------------|----------|

| ADP1190AACBZ-R7    | -40°C to +85°C    | 12-Ball Wafer Level Chip Scale Package [WLCSP] | CB-12-10       | LNW      |

<sup>1</sup> Z = RoHS 準拠製品。