## 特長

EIA RS-485規格に準拠

データレート: 30 Mbps

5 V単電源動作

バス同相モード範囲: -7 V～+12 V

高速低消費電力のBiCMOS

サーマル・シャットダウン保護機能を内蔵

短絡保護機能

ドライバ伝搬遅延: 10 ns

レシーバ伝搬遅延: 15 ns

パワーオフ時に出力でハイ・インピーダンスを維持

LTC1485のアップグレード製品

## アプリケーション

低消費電力のRS-485システム

DTE-DCE間インターフェース

パケット・スイッチング

LAN

データ・コンセントレーション

データ・マルチプレクサ

ISDN

## 概要

ADM1485は、マルチポイント・バス伝送線による高速双方向データ通信に最適な差動ライン・トランシーバです。平衡伝送線向けにデザインされ、RS-485規格とRS-422 EIA規格に準拠しています。このデバイスは、差動ライン・ドライバと差動ライン・レシーバを内蔵しています。ドライバとレシーバは独立にイネーブルすることができます。ディスエーブルされると、出力はスリー・ステートになります。

ADM1485は5 V単電源で動作します。バスの輻輳または出力の短絡により発生する消費電力の増加をサーマル・シャットダウン回路により防止します。故障状態で、大幅な温度上昇が内部ドライバ回路で検出されると、この機能によりドライバ出力がハイ・インピーダンス状態にされます。

最大32個のトランシーバを同じバスに接続できますが、同時に1個のドライバだけをイネーブルすることができます。したがって、残りのディスエーブルされたドライバがバスの負荷にならないようにすることが重要です。このため、ADM1485ドライバはディスエーブル時とパワーダウン時にハイ出力インピーダンスになります。

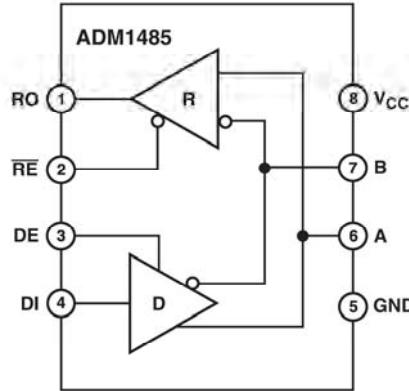

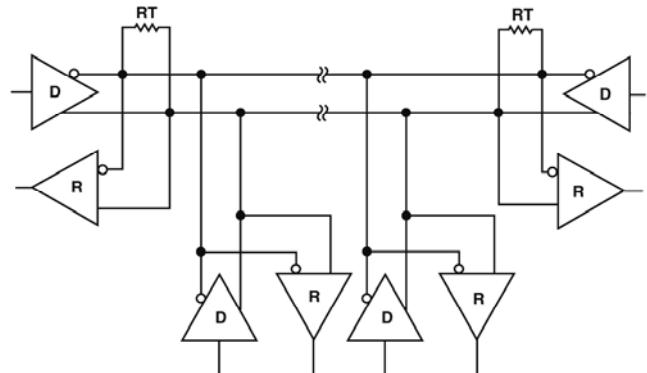

**機能ブロック図

8ピン**

この機能により、トランシーバを使用しない場合の負荷効果が小さくなります。ドライバ出力のハイ・インピーダンスは、-7 V～+12 Vの同相モード電圧の全範囲で維持されます。

レシーバはフェイル・セーフ機能を持っているため、入力の未接続(フローティング)時にロジックはハイ出力レベルになります。

ADM1485は、低消費電力 CMOSと高速スイッチング・バイポーラ技術との高度なミックス技術プロセスであるBiCMOSで製造されています。すべての入力と出力には、ESD保護機能が付いています。すべてのドライバ出力は、高い電流ソース /シンク能力を持っています。エピタキシャル層を使ってラッチアップから保護しています。

ADM1485は極めて高速なスイッチング速度を持っています。最小のドライバ伝搬遅延を持つため、最大5 Mbpsのデータ・レートでの送信が可能であるとともに、低スルーにより EMI 干渉が少なくなっています。

各デバイスとも商用温度範囲と工業温度範囲の仕様で、PDIP、SOIC、または小型MSOPパッケージを採用しています。

## ADM1485-仕様 (特に指定がない限り、 $V_{CC} = 5 \text{ V} \pm 5\%$ 、すべての仕様は $T_{MIN} \sim T_{MAX}$ で規定)

| Parameter                                                | Min  | Typ | Max       | Unit          | Test Conditions/Comments                                          |

|----------------------------------------------------------|------|-----|-----------|---------------|-------------------------------------------------------------------|

| DRIVER                                                   |      |     |           |               |                                                                   |

| Differential Output Voltage, $V_{OD}$                    |      |     | 5.0       | V             | $R = \infty$ , Test Circuit 1                                     |

|                                                          | 2.0  | 5.0 | 5.0       | V             | $V_{CC} = 5 \text{ V}$ , $R = 50 \Omega$ (RS-422), Test Circuit 1 |

|                                                          | 1.5  | 5.0 | 5.0       | V             | $R = 27 \Omega$ (RS-485), Test Circuit 1                          |

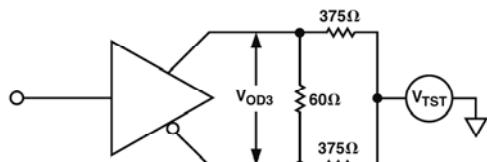

| $V_{OD3}$                                                | 1.5  | 5.0 | 5.0       | V             | $V_{TST} = -7 \text{ V}$ to $+12 \text{ V}$ , Test Circuit 2      |

| $\Delta  V_{OD} $ for Complementary Output States        |      |     | 0.2       | V             | $R = 27 \Omega$ or $50 \Omega$ , Test Circuit 1                   |

| Common-Mode Output Voltage $V_{OC}$                      |      |     | 3         | V             | $R = 27 \Omega$ or $50 \Omega$ , Test Circuit 1                   |

| $\Delta  V_{OD} $ for Complementary Output States        |      |     | 0.2       | V             | $R = 27 \Omega$ or $50 \Omega$                                    |

| Output Short-Circuit Current ( $V_{OUT} = \text{High}$ ) | 35   | 250 | 250       | mA            | $-7 \text{ V} \leq V_o \leq +12 \text{ V}$                        |

| Output Short-Circuit Current ( $V_{OUT} = \text{Low}$ )  | 35   | 250 | 250       | mA            | $-7 \text{ V} \leq V_o \leq +12 \text{ V}$                        |

| CMOS Input Logic Threshold Low, $V_{INL}$                |      |     | 0.8       | V             |                                                                   |

| CMOS Input Logic Threshold High, $V_{INH}$               | 2.0  | 2.0 | $\pm 1.0$ | $\mu\text{A}$ |                                                                   |

| Logic Input Current (DE, DI)                             |      |     |           |               |                                                                   |

| RECEIVER                                                 |      |     |           |               |                                                                   |

| Differential Input Threshold Voltage, $V_{TH}$           | -0.2 | 70  | +0.2      | V             | $-7 \text{ V} \leq V_{CM} \leq +12 \text{ V}$                     |

| Input Voltage Hysteresis, $\Delta V_{TH}$                |      |     |           | mV            | $V_{CM} = 0 \text{ V}$                                            |

| Input Resistance                                         | 12   |     |           | k $\Omega$    | $-7 \text{ V} \leq V_{CM} \leq +12 \text{ V}$                     |

| Input Current (A, B)                                     |      |     | 1         | mA            | $V_{IN} = +12 \text{ V}$                                          |

|                                                          |      |     | -0.8      | mA            | $V_{IN} = -7 \text{ V}$                                           |

| CMOS Input Logic Threshold Low, $V_{INL}$                |      |     | 0.8       | V             |                                                                   |

| CMOS Input Logic Threshold High, $V_{INH}$               | 2.0  | 2.0 | $\pm 1$   | $\mu\text{A}$ |                                                                   |

| Logic Enable Input Current ( $\overline{RE}$ )           |      |     | 0.8       | V             |                                                                   |

| CMOS Output Voltage Low, $V_{OL}$                        |      |     | $\pm 1$   | $\mu\text{A}$ |                                                                   |

| CMOS Output Voltage High, $V_{OH}$                       | 4.0  | 4.0 | 0.4       | V             | $I_{OUT} = +4.0 \text{ mA}$                                       |

| Short-Circuit Output Current                             | 7    | 7   | 85        | mA            | $I_{OUT} = -4.0 \text{ mA}$                                       |

| Three-State Output Leakage Current                       |      |     | $\pm 1.0$ | $\mu\text{A}$ | $V_{OUT} = \text{GND}$ or $V_{CC}$                                |

|                                                          |      |     |           |               | $0.4 \text{ V} \leq V_{OUT} \leq 2.4 \text{ V}$                   |

| POWER SUPPLY CURRENT                                     |      |     |           |               |                                                                   |

| $I_{CC}$ (Outputs Enabled)                               |      | 1.0 | 2.2       | mA            | Digital Inputs = GND or $V_{CC}$                                  |

| $I_{CC}$ (Outputs Disabled)                              |      | 0.6 | 1         | mA            | Digital Inputs = GND or $V_{CC}$                                  |

仕様は予告なく変更されることがあります。

## タイミング仕様 (特に指定がない限り、 $V_{CC} = 5 \text{ V} \pm 5\%$ 、すべての仕様は $T_{MIN} \sim T_{MAX}$ で規定)

| Parameter                                            | Min | Typ | Max | Unit | Test Conditions/Comments                                                   |

|------------------------------------------------------|-----|-----|-----|------|----------------------------------------------------------------------------|

| DRIVER                                               |     |     |     |      |                                                                            |

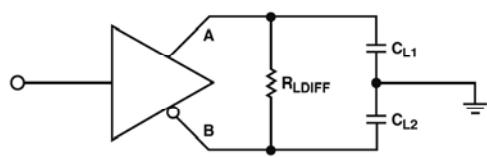

| Propagation Delay Input to Output $t_{PLH}, t_{PHL}$ | 2   | 10  | 15  | ns   | $R_{LDIFF} = 54 \Omega, C_{L1} = C_{L2} = 100 \text{ pF}$ , Test Circuit 3 |

| Driver O/P to $\overline{O}/P$ $t_{SKREW}$           |     | 1   | 5   | ns   | $R_{LDIFF} = 54 \Omega, C_{L1} = C_{L2} = 100 \text{ pF}$ , Test Circuit 3 |

| Driver Rise/Fall Time $t_R, t_F$                     |     | 8   | 15  | ns   | $R_{LDIFF} = 54 \Omega, C_{L1} = C_{L2} = 100 \text{ pF}$ , Test Circuit 3 |

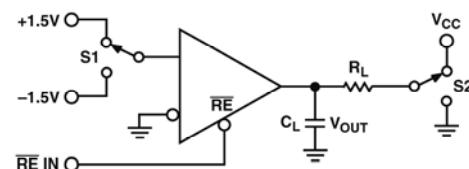

| Driver Enable to Output Valid                        |     | 10  | 25  | ns   | $R_L = 110 \Omega, C_L = 50 \text{ pF}$ , Test Circuit 4                   |

| Driver Disable Timing                                |     | 10  | 25  | ns   | $R_L = 110 \Omega, C_L = 50 \text{ pF}$ , Test Circuit 4                   |

| Matched Enable Switching                             |     | 0   | 2   | ns   | $R_L = 110 \Omega, C_L = 50 \text{ pF}$ , Test Circuit 4*                  |

| $ t_{AZH} - t_{BZL} ,  t_{BZH} - t_{AZL} $           |     |     |     |      |                                                                            |

| Matched Disable Switching                            |     | 0   | 2   | ns   | $R_L = 110 \Omega, C_L = 50 \text{ pF}$ , Test Circuit 4*                  |

| $ t_{AHZ} - t_{BLZ} ,  t_{BHZ} - t_{ALZ} $           |     |     |     |      |                                                                            |

| RECEIVER                                             |     |     |     |      |                                                                            |

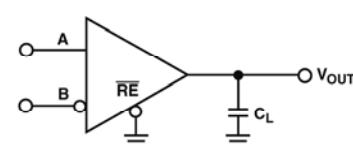

| Propagation Delay Input to Output $t_{PLH}, t_{PHL}$ | 8   | 15  | 30  | ns   | $C_L = 15 \text{ pF}$ , Test Circuit 5                                     |

| Skew $ t_{PLH} - t_{PHL} $                           |     |     | 5   | ns   | $C_L = 15 \text{ pF}$ , Test Circuit 5                                     |

| Receiver Enable $t_{EN1}$                            |     | 5   | 20  | ns   | $C_L = 15 \text{ pF}, R_L = 1 \text{ k}\Omega$ , Test Circuit 6            |

| Receiver Disable $t_{EN2}$                           |     | 5   | 20  | ns   | $C_L = 15 \text{ pF}, R_L = 1 \text{ k}\Omega$ , Test Circuit 6            |

| Tx Pulse Width Distortion                            |     | 1   |     | ns   |                                                                            |

| Rx Pulse Width Distortion                            |     | 1   |     | ns   |                                                                            |

\*キャラクタライゼーションにより保証。

仕様は予告なく変更されることがあります。

**絶対最大定格\***(特に指定がない限り、 $T_A = 25^\circ\text{C}$ )

|                                      |                            |

|--------------------------------------|----------------------------|

| $V_{CC}$                             | -0.3 V to +7 V             |

| Inputs                               |                            |

| Driver Input (DI)                    | -0.3 V to $V_{CC} + 0.3$ V |

| Control Inputs (DE, $\bar{RE}$ )     | -0.3 V to $V_{CC} + 0.3$ V |

| Receiver Inputs (A, B)               | -9 V to +14 V              |

| Outputs                              |                            |

| Driver Outputs (A, B)                | -9 V to +14 V              |

| Receiver Output                      | -0.5 V to $V_{CC} + 0.5$ V |

| Power Dissipation 8-Lead MSOP        | 900 mW                     |

| $\theta_{JA}$ , Thermal Impedance    | 206°C/W                    |

| Power Dissipation 8-Lead PDIP        | 500 mW                     |

| $\theta_{JA}$ , Thermal Impedance    | 130°C/W                    |

| Power Dissipation 8-Lead SOIC        | 450 mW                     |

| $\theta_{JA}$ , Thermal Impedance    | 170°C/W                    |

| Operating Temperature Range          |                            |

| Commercial (J Version)               | 0°C to 70°C                |

| Industrial (A Version)               | -40°C to +85°C             |

| Storage Temperature Range            | -65°C to +150°C            |

| Lead Temperature (Soldering, 10 sec) | 300°C                      |

| Vapor Phase (60 sec)                 | 215°C                      |

| Infrared (15 sec)                    | 220°C                      |

\* 上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

表 I.送信

| Inputs |    | Outputs |   |

|--------|----|---------|---|

| DE     | DI | B       | A |

| 1      | 1  | 0       | 1 |

| 1      | 0  | 1       | 0 |

| 0      | X  | Z       | Z |

表 II.受信

| $\bar{RE}$ | Inputs        |    | Outputs |

|------------|---------------|----|---------|

|            | A-B           | RO |         |

| 0          | $\geq +0.2$ V | 1  |         |

| 0          | $\leq -0.2$ V | 0  |         |

| 0          | Inputs Open   | 1  |         |

| 1          | X             | Z  |         |

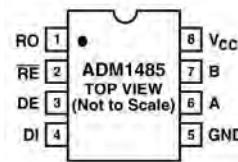

**ピン機能の説明**

| Pin No. | 記号         | 機能                                                                                                                |

|---------|------------|-------------------------------------------------------------------------------------------------------------------|

| 1       | RO         | レシーバ出力。イネーブルされると、(A-B) > 200 mVの場合、RO = ハイ・レベルになります。(A-B) < 200 mVの場合、RO = ロー・レベルになります。                           |

| 2       | $\bar{RE}$ | レシーバ出力イネーブル。ロー・レベルになると、レシーバ出力ROがイネーブルされます。ハイ・レベルになると、ハイ・インピーダンス状態になります。                                           |

| 3       | DE         | ドライバ出力イネーブル。ハイ・レベルになると、ドライバ差動出力 A と B がイネーブルされます。ロー・レベルになると、ハイ・インピーダンス状態になります。                                    |

| 4       | DI         | ドライバ入力。ドライバがイネーブルされた場合、DIにロー・レベルを入力すると、A はロー・レベルに、B はハイ・レベルに、それなります。DIにハイ・レベルを入力すると、A はハイ・レベルに、B はロー・レベルに、それなります。 |

| 5       | GND        | グラウンド接続、0 V。                                                                                                      |

| 6       | A          | 非反転レシーバ入力 A / ドライバ出力 A。                                                                                           |

| 7       | B          | 反転レシーバ入力 B / ドライバ出力 B。                                                                                            |

| 8       | $V_{CC}$   | 電源、5 V ± 5%。                                                                                                      |

**ピン配置****オーダー・ガイド**

| Model            | Temperature Range | Package Option | Branding |

|------------------|-------------------|----------------|----------|

| ADM1485JN        | 0°C to 70°C       | N-8            |          |

| ADM1485JR        | 0°C to 70°C       | R-8            |          |

| ADM1485JR-REEL   | 0°C to 70°C       | R-8            |          |

| ADM1485JR-REEL7  | 0°C to 70°C       | R-8            |          |

| ADM1485AN        | -40°C to +85°C    | N-8            |          |

| ADM1485AR        | -40°C to +85°C    | R-8            |          |

| ADM1485AR-REEL   | -40°C to +85°C    | R-8            |          |

| ADM1485AR-REEL7  | -40°C to +85°C    | R-8            |          |

| ADM1485ARM       | -40°C to +85°C    | RM-8           | M42      |

| ADM1485ARM-REEL  | -40°C to +85°C    | RM-8           | M42      |

| ADM1485ARM-REEL7 | -40°C to +85°C    | RM-8           | M42      |

| ADM1485ARZ*      |                   |                |          |

| ADM1485ARZ-REEL  |                   |                |          |

| ADM1485ARZ-REEL7 |                   |                |          |

| ADM1485JCHIPS    |                   | DIE            |          |

\*Z = 鉛フリー・デバイス。

**ESDの注意**

ESD (静電気放電)に敏感なデバイスです。4000 Vにもなる静電気は人体や装置に蓄積され、検出されずに放電することがあります。ADM1485は当社独自のESD保護回路を内蔵していますが、高エネルギーの静電放電が発生すると、デバイスが永久的な損傷を受けることがあります。このため、性能低下または機能損失を防止するために、ESDに対する適切な注意が必要です。

## ADM1485 テスト回路

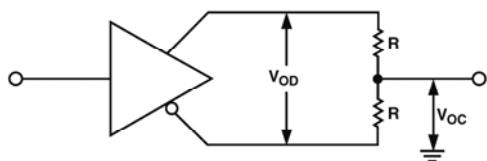

テスト回路 1. ドライバ電圧測定

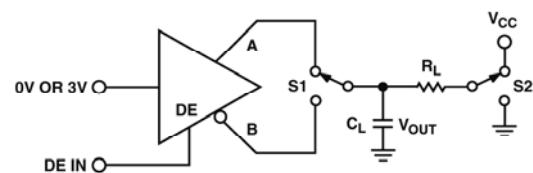

テスト回路 4. ドライバ · イネーブル/ディスエーブル

テスト回路 2. ドライバ電圧測定

テスト回路 5. レシーバ伝搬遅延

テスト回路 3. ドライバ伝搬遅延

テスト回路 6. レシーバ · イネーブル/ディスエーブル

## スイッチング特性

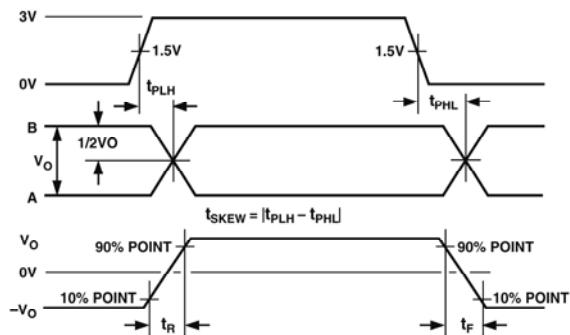

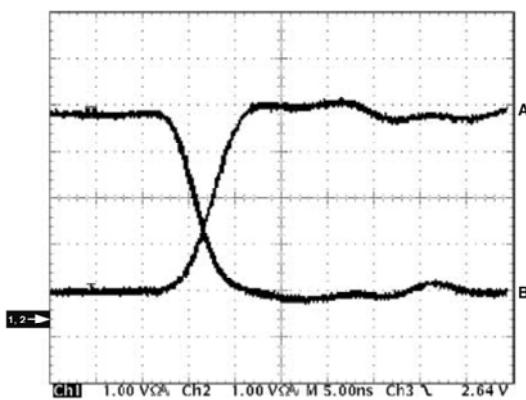

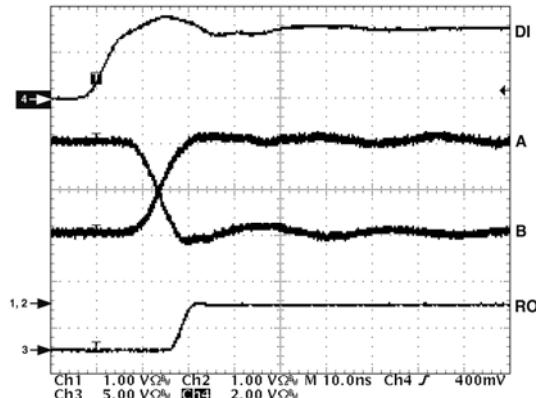

図1. ドライバ伝搬遅延、立上がり/立下がりタイミング

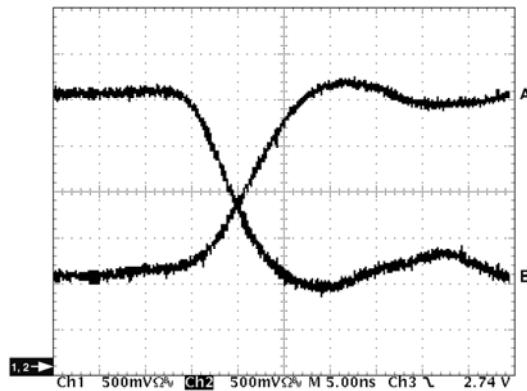

図3. レシーバ伝搬遅延

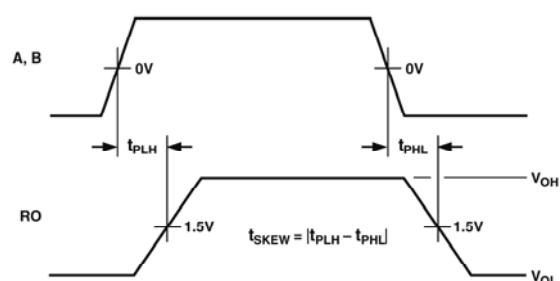

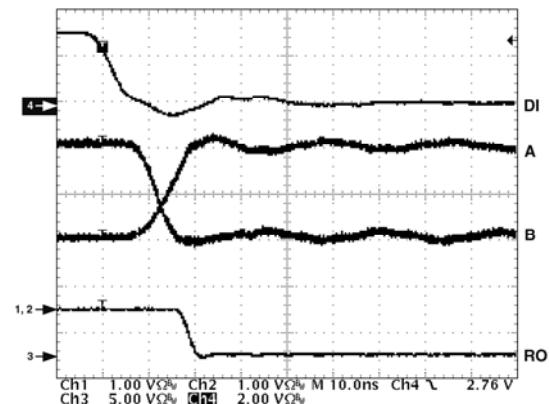

図2. ドライバ · イネーブル/ディスエーブル · タイミング

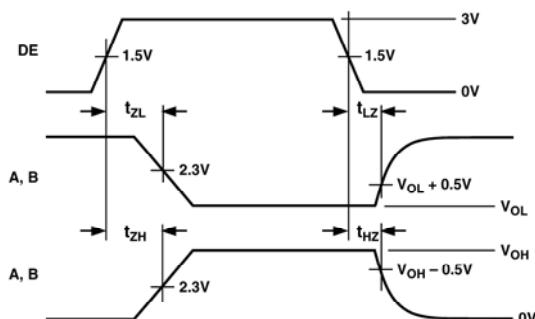

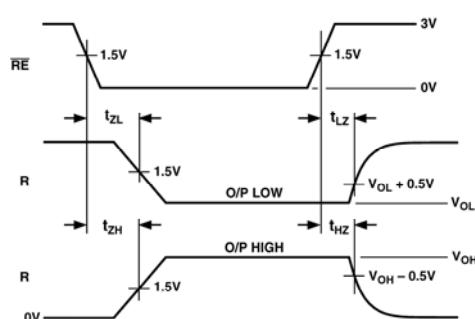

図4. レシーバ · イネーブル/ディスエーブル · タイミング

## 代表的な性能特性

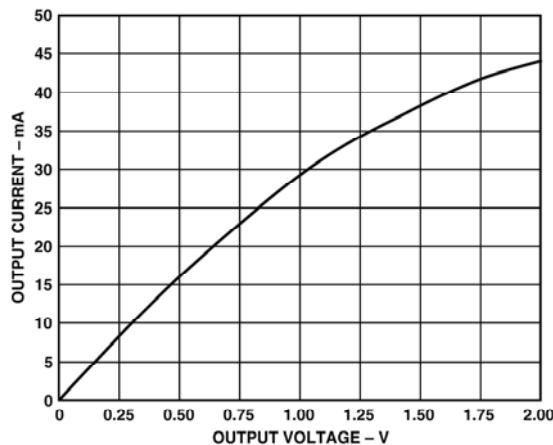

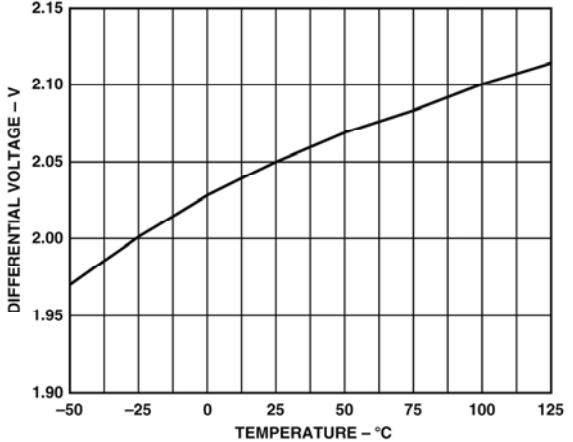

特性 1. レシーバ出力ロー・レベル電圧対出力電流

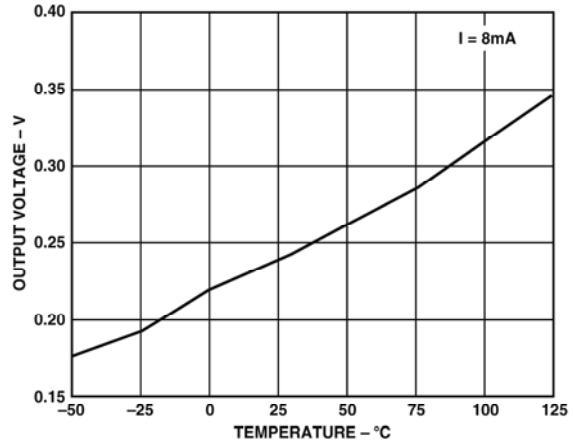

特性 4. レシーバ出力ロー・レベル電圧の温度特性

特性 2. レシーバ出力ハイ・レベル電圧対出力電流

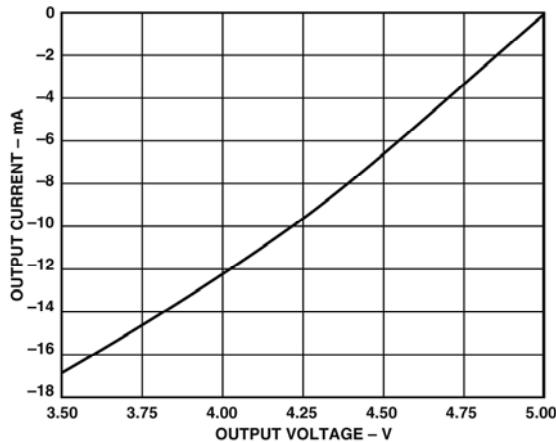

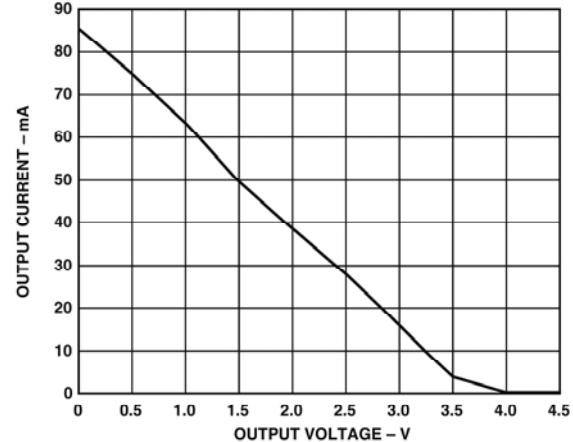

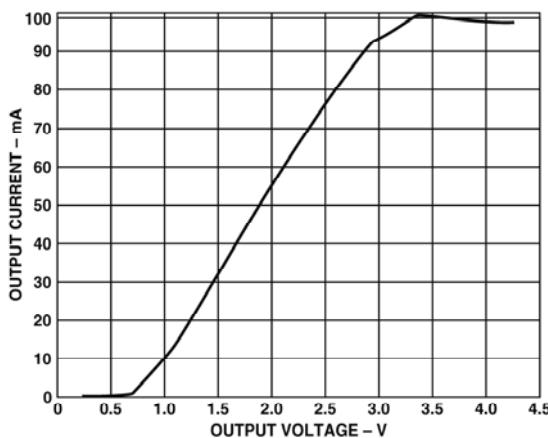

特性 5. ドライバ差動出力電圧対出力電流

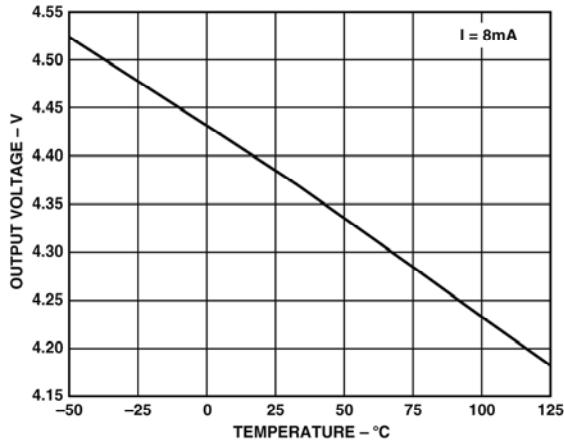

特性 3. レシーバ出力ハイ・レベル電圧の温度特性

特性 6. ドライバ差動出力電圧の温度特性、R<sub>L</sub> = 26.8 Ω

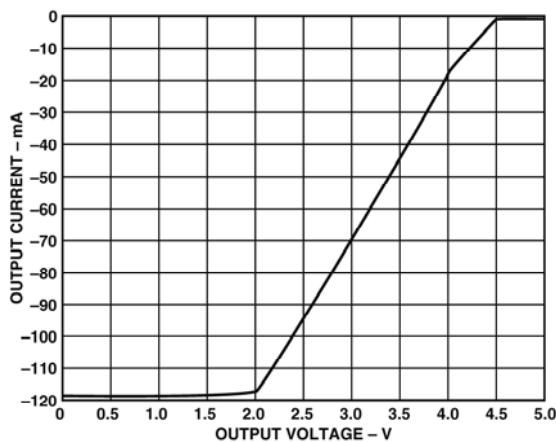

特性 7. ドライバ出力ロー・レベル電圧対出力電流

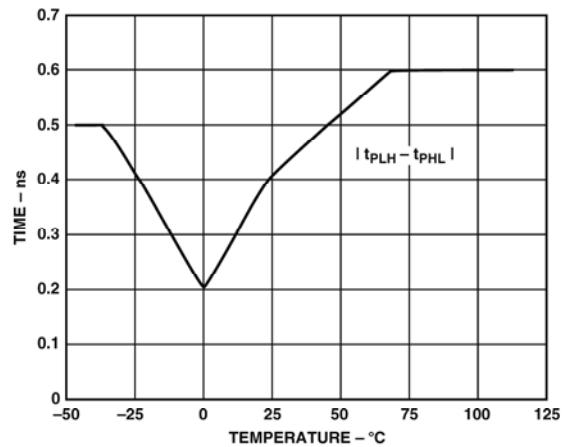

特性 10.Rxスキーの温度特性

特性 8. ドライバ出力高電圧対出力電流

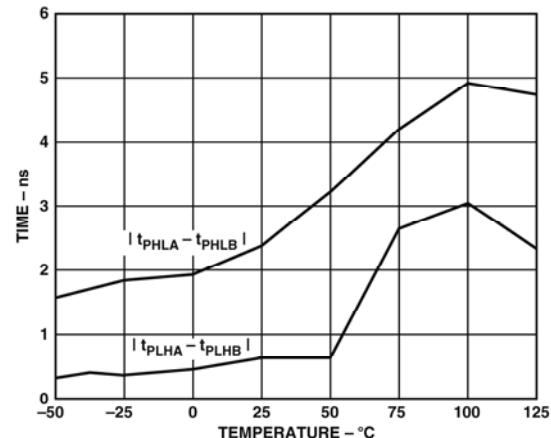

特性 11.Tx スキーの温度特性

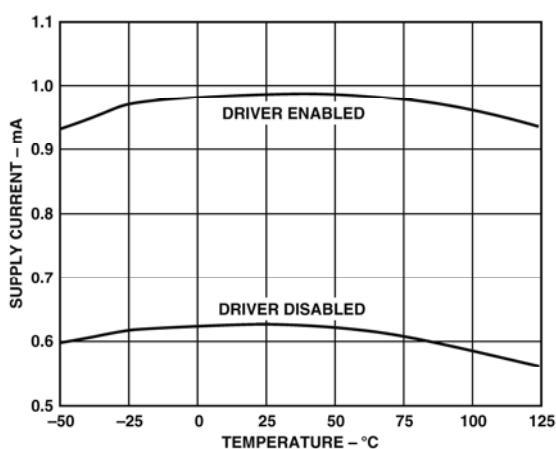

特性9.電源電流の温度特性

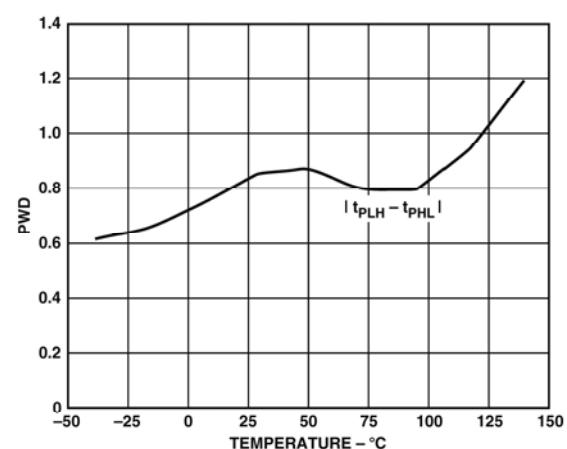

特性 12.Txパルス幅歪み

特性 13.無負荷時のドライバ差動出力

特性 16. ドライバ/レシーバ伝搬遅延

ハイ・レベルからロー・レベル

特性 14.負荷時のドライバ差動出力

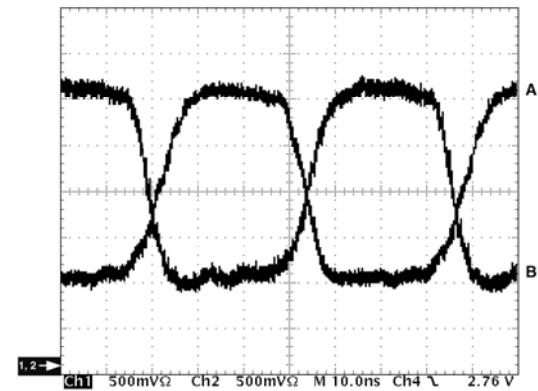

特性 17. 30 Mbpsでのドライバ出力

特性 15. ドライバ/レシーバ伝搬遅延

ロー・レベルからハイ・レベル

## アプリケーション情報

### 差動データ伝送

差動データ伝送は、ノイズの多い環境で長距離を高いレートでデータを高信頼で伝送させる場合に使用されます。差動伝送では、グラウンド・シフトの影響と伝送線上で同相モード電圧として現れるノイズ信号が相殺されます。差動データ伝送で使用されるトランシーバの電気的特性を規定する主なEIA規格は2つあります。

RS-422規格は、最大10 Mボアのデータレートと最大4000フィートのライン長を規定しています。1個のドライバが、最大10個のレシーバを接続した伝送線を駆動することができます。

RS-485規格は、真のマルチポイント通信に対応するために規定されました。この規格はRS-422のすべての条件を満たすかそれ以上ですが、最大32 個のドライバと32 個のレシーバを1本のバスに接続できるようにしています。-7 V～+12 Vの拡張同相モード範囲が規定されています。RS-422 規格と RS-485 規格との間の最も大きな違いは、ドライバをディスエーブルできることで、このために複数(実際32 )のドライバが1本の伝送線に接続できるようになります。同時にイネーブルできるドライバは1個だけですが、

RS-485 規格には伝送線上での衝突の場合にデバイスの安全性を保証する規定が追加されています。

表III.RS-422とRS-485 インターフェース規格の比較

| Specification                     | RS-422       | RS-485        |

|-----------------------------------|--------------|---------------|

| Transmission Type                 | Differential | Differential  |

| Maximum Cable Length              | 4000 ft.     | 4000 ft.      |

| Minimum Driver Output Voltage     | ± 2 V        | ± 1.5 V       |

| Driver Load Impedance             | 100 Ω        | 54 Ω          |

| Receiver Input Resistance         | 4 kΩ min     | 12 kΩ min     |

| Receiver Input Sensitivity        | ± 200 mV     | ± 200 mV      |

| Receiver Input Voltage Range      | -7 V to +7 V | -7 V to +12 V |

| No. of Drivers/Receivers per Line | 1/10         | 32/32         |

### ケーブルとデータレート

RS-485 通信で使用される伝送線はツイストペア線です。ツイストペア・ケーブルは同相モード・ノイズを相殺させる性質を持ち、各ワイヤーを流れる電流から発生する磁界を相殺させるため、ペアの実効インダクタンスが小さくなります。

ADM1485は、マルチポイント伝送線を使った双方向データ通信向けにデザインされています。マルチポイント伝送回路の代表的なアプリケーションを図5に示します。RS-485 伝送線上には、最大32 個のトランシーバを接続することができます。特定の時間に送信ができるドライバは1個だけですが、複数のレシーバを同時にイネーブルすることができます。

どの伝送線でも、反射を小さくすることが重要です。これは、ラインの特性インピーダンスに等しい抵抗を使ってラインの両端を終端することにより実現されます。本線から分岐する支線はできるだけ短くする必要があります。適切に終端された伝送線は、ドライバから純抵抗に見えます。

図5. 代表的な RS-485 回路

### サーマル・シャットダウン

ADM1485はサーマル・シャットダウン回路を内蔵しており、故障時に消費電力が大きくなり過ぎないように保護しています。ドライバ出力を低インピーダンス電源に短絡させると、大きなドライバ電流が流れます。温度検出回路がチップ温度上昇を検出して、ドライバ出力をディスエーブルします。この温度検出回路は、チップ温度が150°C に到達したとき、ドライバ出力をディスエーブルするようにデザインされています。デバイスが冷えて温度140°Cになると、ドライバは再イネーブルされます。

### 伝搬遅延

ADM1485は非常に小さい伝搬遅延を持つため、最大ボア・レートの動作を保証します。ドライバのバランスが優れているため、歪みのない伝送を保証します。

もう1つの重要な規定は、相補出力間のスキュー対策です。スキューが大きいと、システムのノイズ耐性が損なわれるため、電磁干渉(EMI)が大きくなります。

### レシーバの断線とフェルセーフ

レシーバ入力にはフェイルセーフ機能が内蔵されていて、入力がフローティングまたは断線したときに、レシーバのロジック・ハイ・レベルを保証しています。

## 外形寸法

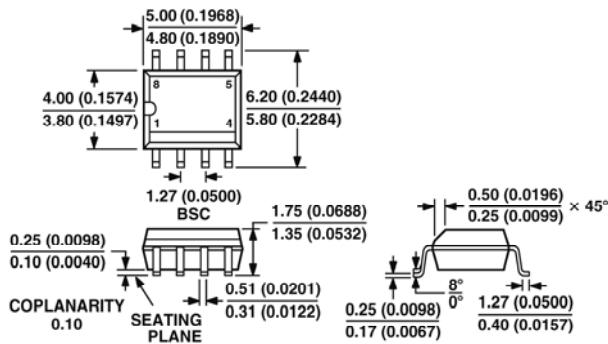

8ピン標準スモール・アウトライン・パッケージ[SOIC]

ナロー・ボディ

(R-8)

寸法: mm (インチ)

COMPLIANT TO JEDEC STANDARDS MS-012AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

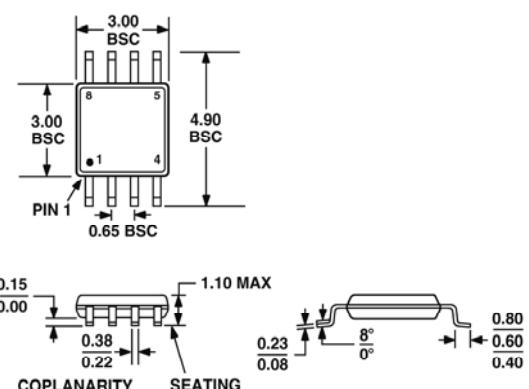

8ピン・ミニ・スモール・アウトライン・パッケージ[MSOP]

(RM-8)

寸法: mm

COMPLIANT TO JEDEC STANDARDS MO-187AA

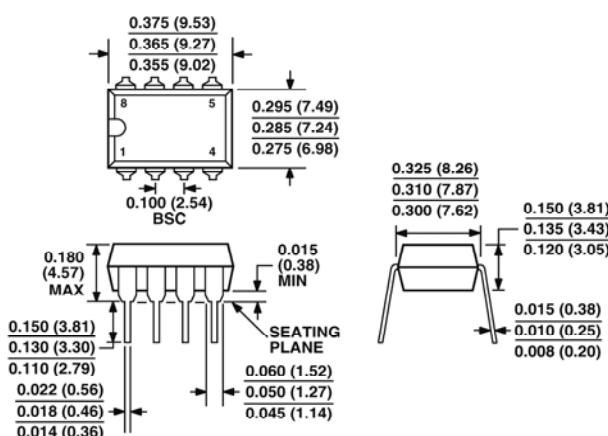

8ピン・プラスチック・デュアルインラインパッケージ [PDIP]

(N-8)

寸法: インチ (mm)

COMPLIANT TO JEDEC STANDARDS MO-095AA

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

**改訂履歷**

| <u>Location</u>                                        | <u>Page</u> |

|--------------------------------------------------------|-------------|

| <b>9/03—Data Sheet changed from REV. D to REV. E.</b>  |             |

| Change to SPECIFICATIONS .....                         | 2           |

| Changes to ORDERING GUIDE .....                        | 3           |

| Updated OUTLINE DIMENSIONS .....                       | 9           |

| <b>7/03—Data Sheet changed from REV. C to REV. D.</b>  |             |

| Changes to SPECIFICATIONS .....                        | 2           |

| Changes to ABSOLUTE MAXIMUM RATINGS .....              | 3           |

| Updated ORDERING GUIDE .....                           | 3           |

| <b>1/03—Data Sheet changed from REV. B to REV. C.</b>  |             |

| Change to SPECIFICATIONS .....                         | 2           |

| Change to ORDERING GUIDE .....                         | 3           |

| <b>12/02—Data Sheet changed from REV. A to REV. B.</b> |             |

| Deleted Q-8 Package .....                              | Universal   |

| Edits to FEATURES .....                                | 1           |

| Edits to GENERAL DESCRIPTION .....                     | 1           |

| Edits, additions to SPECIFICATIONS .....               | 2           |

| Edits, additions to ABSOLUTE MAXIMUM RATINGS .....     | 3           |

| Additions to ORDERING GUIDE .....                      | 3           |

| TPCs updated and reformatted .....                     | 5           |

| Addition of 8-Lead MSOP Package .....                  | 9           |

| Update to OUTLINE DIMENSIONS .....                     | 9           |