## ADG5204

## 特長

ラッチアップ保護機能を内蔵

オフ時ソース容量: 3 pF

オフ時ドレイン容量: 26 pF

チャージ・インジェクション: -0.6 pC

低リーク: 85°C で最大 0.4 nA

両電源動作:  $\pm 9 \text{ V} \sim \pm 22 \text{ V}$

単電源動作: 9 V ~ 40 V

最大電源電圧定格: 48 V

$\pm 15 \text{ V}$ ,  $\pm 20 \text{ V}$ ,  $+12 \text{ V}$ ,  $+36 \text{ V}$  電源で仕様規定

アナログ信号範囲:  $V_{SS} \sim V_{DD}$

## アプリケーション

自動テスト装置

データ・アクイジション

計装機器

航空電子機器

オーディオとビデオ・スイッチング

通信システム

## 概要

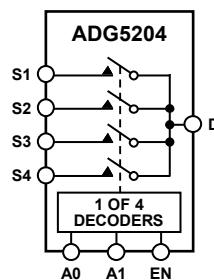

ADG5204は、4チャンネルで構成されたCMOSアナログ・マルチプレクサです。

これらのスイッチは、極めて小さい容量とチャージ・インジェクションを持つため、低グリッヂと高速なセトリングを必要とするデータ・アクイジションとサンプル・アンド・ホールドのアプリケーションに最適なソリューションになっています。このデバイスは、高速なスイッチング速度と広い信号帯域幅の組み合わせにより、ビデオ信号スイッチングにも適しています。ADG5204は、ラッチアップを防止するトレンチ・プロセスを採用してデザインされています。絶縁トレンチによりpチャンネルとnチャンネルのトランジスタを分離することにより、厳しい過電圧状態でもラッチアップを防止します。

ADG5204は、3ビットのバイナリ・アドレス・ラインA0、A1、ENによる指定に基づき、4入力の内の1つを共通出力Dに接続します。ENピンをロジック0にすると、デバイスがディスエーブルされます。各スイッチはオンのとき等しく両方向に導通し、入力信号範囲は電源電圧まで可能です。オフ状態では、電源電圧までの信号レベルを阻止します。各スイッチは、ブレーク・ビフォア・メーク・スイッチング動作を行います。

## 機能ブロック図

図 1.

## 製品のハイライト

- トレンチ・アイソレーションによりラッチアップから保護します。

絶縁トレンチにより p チャンネルと n チャンネルのトランジスタを分離することにより、厳しい過電圧状態でもラッチアップを防止します。

- 極めて小さい容量と 1 pC 以下のチャージ・インジェクション。

- 両電源動作。

アナログ信号がバイポーラであるアプリケーションに対しては、ADG5204 は  $\pm 22 \text{ V}$  までの両電源で動作することができます。

- 単電源動作。

アナログ信号がユニポーラであるアプリケーションに対しては、ADG5204 は 40 V までの単電源で動作することができます。

- 3 V ロジック互換のデジタル入力。

$V_{INH} = 2.0 \text{ V}$ ,  $V_{INL} = 0.8 \text{ V}$ 。

- $V_L$  ロジック電源が不要。

## 目次

|                                         |   |                     |    |

|-----------------------------------------|---|---------------------|----|

| 特長 .....                                | 1 | 絶対最大定格 .....        | 8  |

| アプリケーション .....                          | 1 | ESDの注意 .....        | 8  |

| 機能ブロック図 .....                           | 1 | ピン配置およびピン機能説明 ..... | 9  |

| 概要 .....                                | 1 | 真理値表 .....          | 9  |

| 製品のハイライト .....                          | 1 | 代表的な性能特性 .....      | 10 |

| 改訂履歴 .....                              | 2 | テスト回路 .....         | 14 |

| 仕様 .....                                | 3 | 用語 .....            | 16 |

| $\pm 15\text{ V}$ 両電源 .....             | 3 | トレンチ・アイソレーション ..... | 17 |

| $\pm 20\text{ V}$ 両電源 .....             | 4 | アプリケーション情報 .....    | 18 |

| 12 V単電源 .....                           | 5 | 外形寸法 .....          | 19 |

| 36 V単電源 .....                           | 6 | オーダー・ガイド .....      | 19 |

| チャンネルあたりの連続電流、S <sub>x</sub> またはD ..... | 7 |                     |    |

## 改訂履歴

5/11—Revision 0: Initial Version

# 仕様

## ±15 V両電源

特に指定がない限り、 $V_{DD} = 15 \text{ V} \pm 10\%$ 、 $V_{SS} = -15 \text{ V} \pm 10\%$ 、 $\text{GND} = 0 \text{ V}$ 。

表 1.

| Parameter                                             | 25°C          | -40°C to +85°C | -40°C to +125°C           | Unit                                                            | Test Conditions/Comments                                                                                                                                                                                                                             |

|-------------------------------------------------------|---------------|----------------|---------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                         |               |                |                           |                                                                 |                                                                                                                                                                                                                                                      |

| Analog Signal Range                                   |               |                |                           |                                                                 |                                                                                                                                                                                                                                                      |

| On Resistance, $R_{ON}$                               | 160<br>200    | 250            | 280                       | $V_{max}$<br>$\Omega_{typ}$<br>$\Omega_{max}$<br>$\Omega_{typ}$ | $V_S = \pm 10 \text{ V}, I_S = -1 \text{ mA}$ , see Figure 24<br>$V_{DD} = +13.5 \text{ V}, V_{SS} = -13.5 \text{ V}$<br>$V_S = \pm 10 \text{ V}, I_S = -1 \text{ mA}$                                                                               |

| On-Resistance Match Between Channels, $\Delta R_{ON}$ | 4.5           |                |                           |                                                                 |                                                                                                                                                                                                                                                      |

| On-Resistance Flatness, $R_{FLAT(ON)}$                | 8<br>38<br>50 | 9              | 10<br>70                  | $\Omega_{max}$<br>$\Omega_{typ}$<br>$\Omega_{max}$              | $V_S = \pm 10 \text{ V}, I_S = -1 \text{ mA}$                                                                                                                                                                                                        |

| LEAKAGE CURRENTS                                      |               |                |                           |                                                                 |                                                                                                                                                                                                                                                      |

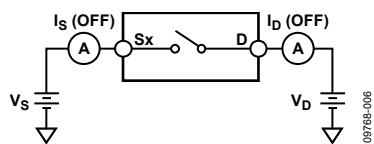

| Source Off Leakage, $I_S(\text{Off})$                 | 0.01<br>0.1   | 0.2            | 0.4                       | nA typ<br>nA max                                                | $V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$<br>$V_S = V_D = \pm 10 \text{ V}, V_D = \mp 10 \text{ V}$ , see Figure 23                                                                                                                       |

| Drain Off Leakage, $I_D(\text{Off})$                  | 0.01<br>0.1   | 0.4            | 1.2                       | nA typ<br>nA max                                                | $V_S = V_D = \pm 10 \text{ V}, V_D = \mp 10 \text{ V}$ , see Figure 23                                                                                                                                                                               |

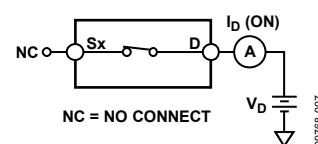

| Channel On Leakage, $I_D, I_S(\text{On})$             | 0.02<br>0.2   | 0.5            | 1.2                       | nA typ<br>nA max                                                | $V_S = V_D = \pm 10 \text{ V}$ , see Figure 26                                                                                                                                                                                                       |

| DIGITAL INPUTS                                        |               |                |                           |                                                                 |                                                                                                                                                                                                                                                      |

| Input High Voltage, $V_{INH}$                         |               |                | 2.0                       | $V_{min}$                                                       |                                                                                                                                                                                                                                                      |

| Input Low Voltage, $V_{INL}$                          |               |                | 0.8                       | $V_{max}$                                                       |                                                                                                                                                                                                                                                      |

| Input Current, $I_{INL}$ or $I_{INH}$                 | 0.002         |                | $\pm 0.1$                 | $\mu A_{typ}$<br>$\mu A_{max}$<br>$pF_{typ}$                    | $V_{IN} = V_{GND}$ or $V_{DD}$                                                                                                                                                                                                                       |

| Digital Input Capacitance, $C_{IN}$                   | 3             |                |                           |                                                                 |                                                                                                                                                                                                                                                      |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                  |               |                |                           |                                                                 |                                                                                                                                                                                                                                                      |

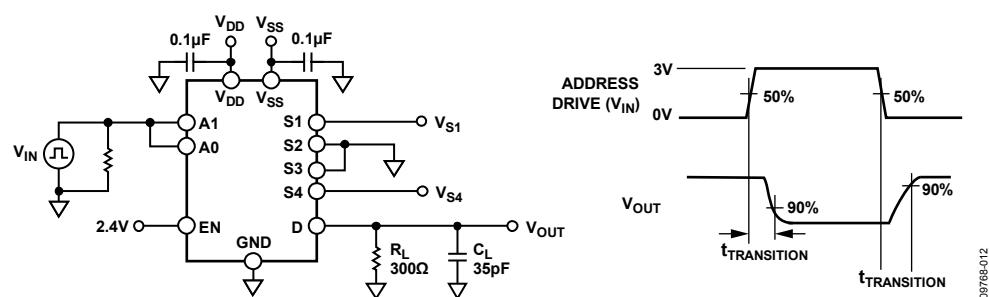

| Transition Time, $t_{TRANSITION}$                     | 175<br>230    | 285            | 320                       | ns typ<br>ns max                                                | $R_L = 300 \Omega, C_L = 35 \text{ pF}$<br>$V_S = 10 \text{ V}$ , see Figure 29                                                                                                                                                                      |

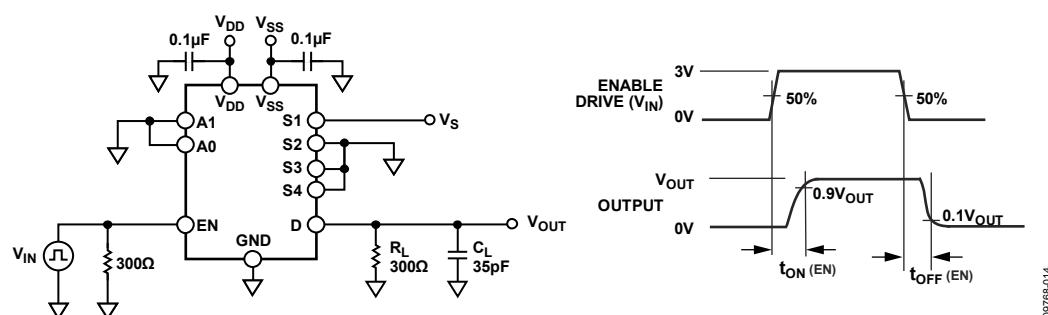

| $t_{ON}$ (EN)                                         | 155<br>205    | 255            | 285                       | ns typ<br>ns max                                                | $R_L = 300 \Omega, C_L = 35 \text{ pF}$<br>$V_S = 10 \text{ V}$ , see Figure 31                                                                                                                                                                      |

| $t_{OFF}$ (EN)                                        | 150<br>175    | 200            | 215                       | ns typ<br>ns max                                                | $R_L = 300 \Omega, C_L = 35 \text{ pF}$<br>$V_S = 10 \text{ V}$ , see Figure 31                                                                                                                                                                      |

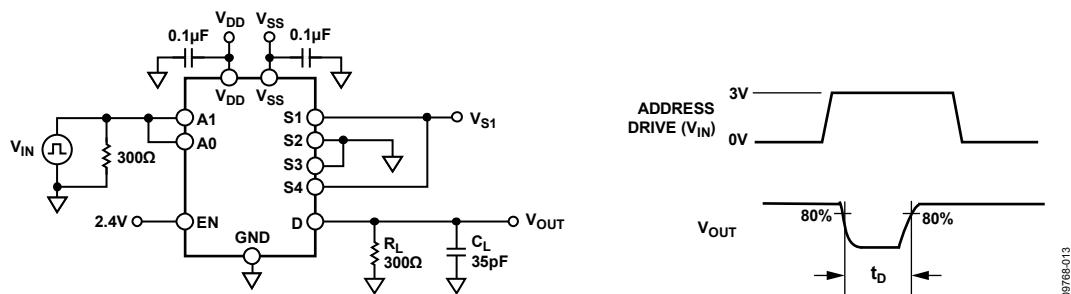

| Break-Before-Make Time Delay, $t_D$                   | 80            |                | 30                        | ns min<br>pC typ<br>dB typ                                      | $R_L = 300 \Omega, C_L = 35 \text{ pF}$<br>$V_{S1} = V_{S2} = 10 \text{ V}$ , see Figure 30<br>$V_S = 0 \text{ V}, R_S = 0 \Omega, C_L = 1 \text{ nF}$ , see Figure 32<br>$R_L = 50 \Omega, C_L = 5 \text{ pF}, f = 100 \text{ kHz}$ , see Figure 25 |

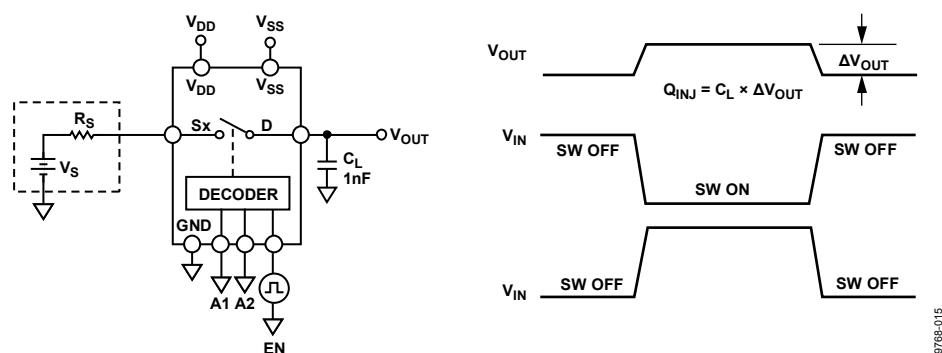

| Charge Injection, $Q_{INJ}$                           | -0.6          |                |                           |                                                                 | $R_L = 50 \Omega, C_L = 5 \text{ pF}, f = 1 \text{ MHz}$ , see Figure 28                                                                                                                                                                             |

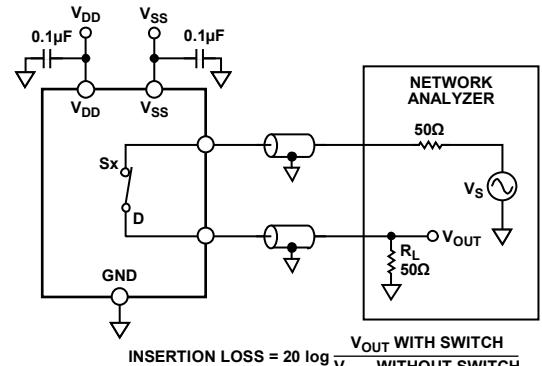

| Off Isolation                                         | -80           |                |                           |                                                                 | $R_L = 50 \Omega, C_L = 5 \text{ pF}$ , see Figure 27                                                                                                                                                                                                |

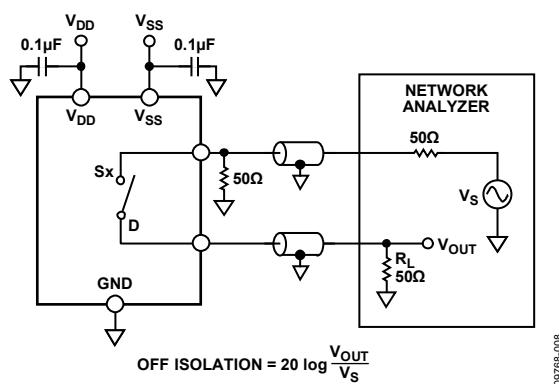

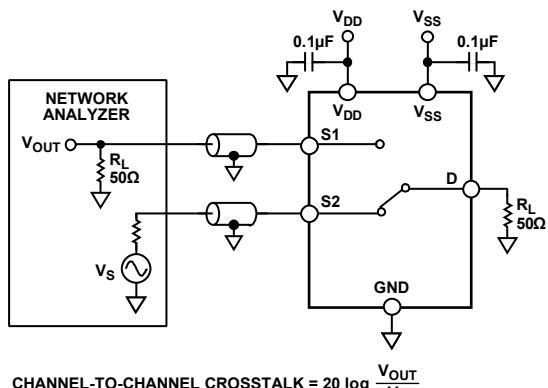

| Channel-to-Channel Crosstalk                          | -80           |                |                           |                                                                 | $R_L = 50 \Omega, C_L = 5 \text{ pF}, f = 1 \text{ MHz}$ , see Figure 27                                                                                                                                                                             |

| -3 dB Bandwidth                                       | 136           |                |                           |                                                                 | $R_L = 50 \Omega, C_L = 5 \text{ pF}, f = 1 \text{ MHz}$ , see Figure 27                                                                                                                                                                             |

| Insertion Loss                                        | -6.8          |                |                           |                                                                 | $V_S = 0 \text{ V}, f = 1 \text{ MHz}$                                                                                                                                                                                                               |

| $C_S(\text{Off})$                                     | 3             |                |                           |                                                                 | $V_S = 0 \text{ V}, f = 1 \text{ MHz}$                                                                                                                                                                                                               |

| $C_D(\text{Off})$                                     | 26            |                |                           |                                                                 | $V_S = 0 \text{ V}, f = 1 \text{ MHz}$                                                                                                                                                                                                               |

| $C_D, C_S(\text{On})$                                 | 30            |                |                           |                                                                 | $V_S = 0 \text{ V}, f = 1 \text{ MHz}$                                                                                                                                                                                                               |

| POWER REQUIREMENTS                                    |               |                |                           |                                                                 |                                                                                                                                                                                                                                                      |

| $I_{DD}$                                              | 45<br>55      |                |                           | $\mu A_{typ}$<br>$\mu A_{max}$                                  | $V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$<br>Digital inputs = 0 V or $V_{DD}$                                                                                                                                                             |

| $I_{SS}$                                              | 0.001         |                | 70<br>1<br>$\pm 9/\pm 22$ | $\mu A_{typ}$<br>$\mu A_{max}$<br>$V_{min/max}$                 | Digital inputs = 0 V or $V_{DD}$<br>$GND = 0 \text{ V}$                                                                                                                                                                                              |

| $V_{DD}/V_{SS}$                                       |               |                |                           |                                                                 |                                                                                                                                                                                                                                                      |

<sup>1</sup> 設計上保証しますが、出荷テストは行いません。

**±20 V両電源**

特に指定がない限り、 $V_{DD} = +20 \text{ V} \pm 10\%$ 、 $V_{SS} = -20 \text{ V} \pm 10\%$ 、GND = 0 V。

表 2.

| Parameter                                             | 25°C          | -40°C to +85°C | -40°C to +125°C     | Unit                                                         | Test Conditions/Comments                                                                                                                                           |

|-------------------------------------------------------|---------------|----------------|---------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                         |               |                |                     |                                                              |                                                                                                                                                                    |

| Analog Signal Range                                   |               |                |                     |                                                              |                                                                                                                                                                    |

| On Resistance, $R_{ON}$                               | 140<br>160    | 200            | 230                 | $\Omega$ max<br>$\Omega$ typ<br>$\Omega$ max<br>$\Omega$ typ | $V_S = \pm 15 \text{ V}, I_S = -1 \text{ mA}$ , see Figure 24<br>$V_{DD} = +18 \text{ V}, V_{SS} = -18 \text{ V}$<br>$V_S = \pm 15 \text{ V}, I_S = -1 \text{ mA}$ |

| On-Resistance Match Between Channels, $\Delta R_{ON}$ | 4.5           |                |                     |                                                              |                                                                                                                                                                    |

| On-Resistance Flatness, $R_{FLAT(ON)}$                | 8<br>33<br>45 | 9              | 10                  | $\Omega$ max<br>$\Omega$ typ<br>$\Omega$ max                 | $V_S = \pm 15 \text{ V}, I_S = -1 \text{ mA}$                                                                                                                      |

| LEAKAGE CURRENTS                                      |               |                |                     |                                                              |                                                                                                                                                                    |

| Source Off Leakage, $I_S$ (Off)                       | 0.01<br>0.1   | 0.2            | 0.4                 | nA typ<br>nA max                                             | $V_{DD} = +22 \text{ V}, V_{SS} = -22 \text{ V}$<br>$V_S = \pm 15 \text{ V}, V_D = \mp 15 \text{ V}$ , see Figure 23                                               |

| Drain Off Leakage, $I_D$ (Off)                        | 0.01<br>0.1   | 0.4            | 1.2                 | nA typ<br>nA max                                             | $V_S = \pm 15 \text{ V}, V_D = \mp 15 \text{ V}$ , see Figure 23                                                                                                   |

| Channel On Leakage, $I_D, I_S$ (On)                   | 0.02<br>0.2   | 0.5            | 1.2                 | nA typ<br>nA max                                             | $V_S = V_D = \pm 15 \text{ V}$ , see Figure 26                                                                                                                     |

| DIGITAL INPUTS                                        |               |                |                     |                                                              |                                                                                                                                                                    |

| Input High Voltage, $V_{INH}$                         |               |                | 2.0                 | V min                                                        |                                                                                                                                                                    |

| Input Low Voltage, $V_{INL}$                          |               |                | 0.8                 | V max                                                        |                                                                                                                                                                    |

| Input Current, $I_{INL}$ or $I_{INH}$                 | 0.002         |                | $\pm 0.1$           | $\mu\text{A}$ typ<br>$\mu\text{A}$ max                       | $V_{IN} = V_{GND}$ or $V_{DD}$                                                                                                                                     |

| Digital Input Capacitance, $C_{IN}$                   | 3             |                |                     | pF typ                                                       |                                                                                                                                                                    |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                  |               |                |                     |                                                              |                                                                                                                                                                    |

| Transition Time, $t_{TRANSITION}$                     | 160<br>215    | 260            | 290                 | ns typ<br>ns max                                             | $R_L = 300 \Omega, C_L = 35 \text{ pF}$<br>$V_S = 10 \text{ V}$ , see Figure 29                                                                                    |

| $t_{ON}$ (EN)                                         | 150<br>185    | 225            | 255                 | ns typ<br>ns max                                             | $R_L = 300 \Omega, C_L = 35 \text{ pF}$<br>$V_S = 10 \text{ V}$ , see Figure 31                                                                                    |

| $t_{OFF}$ (EN)                                        | 150<br>175    | 195            | 210                 | ns typ<br>ns max                                             | $R_L = 300 \Omega, C_L = 35 \text{ pF}$<br>$V_S = 10 \text{ V}$ , see Figure 31                                                                                    |

| Break-Before-Make Time Delay, $t_D$                   | 75            |                | 30                  | ns min<br>pC typ                                             | $R_L = 300 \Omega, C_L = 35 \text{ pF}$<br>$V_{SI} = V_{S2} = 10 \text{ V}$ , see Figure 30                                                                        |

| Charge Injection, $Q_{INJ}$                           | -0.6          |                |                     | dB typ                                                       | $V_S = 0 \text{ V}, R_S = 0 \Omega, C_L = 1 \text{ nF}$ , see Figure 32                                                                                            |

| Off Isolation                                         | -80           |                |                     | dB typ                                                       | $R_L = 50 \Omega, C_L = 5 \text{ pF}, f = 100 \text{ kHz}$ , see Figure 25                                                                                         |

| Channel-to-Channel Crosstalk                          | -80           |                |                     | dB typ                                                       | $R_L = 50 \Omega, C_L = 5 \text{ pF}, f = 1 \text{ MHz}$ , see Figure 28                                                                                           |

| -3 dB Bandwidth                                       | 150           |                |                     | MHz typ                                                      | $R_L = 50 \Omega, C_L = 5 \text{ pF}$ , see Figure 27                                                                                                              |

| Insertion Loss                                        | -6            |                |                     | dB typ                                                       | $R_L = 50 \Omega, C_L = 5 \text{ pF}, f = 1 \text{ MHz}$ , see Figure 27                                                                                           |

| $C_S$ (Off)                                           | 3             |                |                     | pF typ                                                       | $V_S = 0 \text{ V}, f = 1 \text{ MHz}$                                                                                                                             |

| $C_D$ (Off)                                           | 26            |                |                     | pF typ                                                       | $V_S = 0 \text{ V}, f = 1 \text{ MHz}$                                                                                                                             |

| $C_D, C_S$ (On)                                       | 30            |                |                     | pF typ                                                       | $V_S = 0 \text{ V}, f = 1 \text{ MHz}$                                                                                                                             |

| POWER REQUIREMENTS                                    |               |                |                     |                                                              |                                                                                                                                                                    |

| $I_{DD}$                                              | 50            |                |                     | $\mu\text{A}$ typ                                            | $V_{DD} = +22 \text{ V}, V_{SS} = -22 \text{ V}$                                                                                                                   |

|                                                       | 70            |                |                     | $\mu\text{A}$ max                                            | Digital inputs = 0 V or $V_{DD}$                                                                                                                                   |

| $I_{SS}$                                              | 0.001         |                | 110                 | $\mu\text{A}$ typ<br>$\mu\text{A}$ max                       | Digital inputs = 0 V or $V_{DD}$                                                                                                                                   |

| $V_{DD}/V_{SS}$                                       |               |                | 1<br>$\pm 9/\pm 22$ | V min/max                                                    | GND = 0 V                                                                                                                                                          |

<sup>1</sup> 設計上保証しますが、出荷テストは行いません。

## 12 V单電源

特に指定がない限り、 $V_{DD} = 12 \text{ V} \pm 10\%$ 、 $V_{SS} = 0 \text{ V}$ 、 $\text{GND} = 0 \text{ V}$ 。

表 3.

| Parameter                                             | 25°C             | -40°C to +85°C | -40°C to +125°C | Unit                                                  | Test Conditions/Comments                                                                                                                                                       |

|-------------------------------------------------------|------------------|----------------|-----------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                         |                  |                |                 |                                                       |                                                                                                                                                                                |

| Analog Signal Range                                   |                  |                |                 |                                                       |                                                                                                                                                                                |

| On Resistance, $R_{ON}$                               | 340<br>500<br>5  | 610            | 700             | V max<br>$\Omega$ typ<br>$\Omega$ max<br>$\Omega$ typ | $V_S = 0 \text{ V}$ to 10 V, $I_S = -1 \text{ mA}$ , see Figure 24<br>$V_{DD} = 10.8 \text{ V}$ , $V_{SS} = 0 \text{ V}$<br>$V_S = 0 \text{ V}$ to 10 V, $I_S = -1 \text{ mA}$ |

| On-Resistance Match Between Channels, $\Delta R_{ON}$ | 20<br>145<br>280 | 21             | 22              | $\Omega$ max<br>$\Omega$ typ<br>$\Omega$ max          | $V_S = 0 \text{ V}$ to 10 V, $I_S = -1 \text{ mA}$                                                                                                                             |

| On-Resistance Flatness, $R_{FLAT(ON)}$                |                  | 335            | 370             |                                                       |                                                                                                                                                                                |

| LEAKAGE CURRENTS                                      |                  |                |                 |                                                       |                                                                                                                                                                                |

| Source Off Leakage, $I_S$ (Off)                       | 0.01             |                |                 | nA typ                                                | $V_{DD} = 13.2 \text{ V}$ , $V_{SS} = 0 \text{ V}$                                                                                                                             |

|                                                       | 0.1              | 0.2            | 0.4             | nA max<br>nA typ                                      | $V_S = 1 \text{ V}/10 \text{ V}$ , $V_D = 10 \text{ V}/1 \text{ V}$ , see Figure 23                                                                                            |

| Drain Off Leakage, $I_D$ (Off)                        | 0.01             |                |                 |                                                       |                                                                                                                                                                                |

|                                                       | 0.1              | 0.4            | 1.2             | nA max<br>nA typ                                      | $V_S = 1 \text{ V}/10 \text{ V}$ , $V_D = 10 \text{ V}/1 \text{ V}$ , see Figure 23                                                                                            |

| Channel On Leakage, $I_D$ , $I_S$ (On)                | 0.02<br>0.2      | 0.5            | 1.2             | nA max                                                | $V_S = V_D = 1 \text{ V}/10 \text{ V}$ , see Figure 26                                                                                                                         |

| DIGITAL INPUTS                                        |                  |                |                 |                                                       |                                                                                                                                                                                |

| Input High Voltage, $V_{INH}$                         |                  |                | 2.0             | V min                                                 |                                                                                                                                                                                |

| Input Low Voltage, $V_{INL}$                          |                  |                | 0.8             | V max                                                 |                                                                                                                                                                                |

| Input Current, $I_{INL}$ or $I_{INH}$                 | 0.002            |                | $\pm 0.1$       | $\mu\text{A}$ typ<br>$\mu\text{A}$ max                | $V_{IN} = V_{GND}$ or $V_{DD}$                                                                                                                                                 |

| Digital Input Capacitance, $C_{IN}$                   | 3                |                |                 | pF typ                                                |                                                                                                                                                                                |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                  |                  |                |                 |                                                       |                                                                                                                                                                                |

| Transition Time, $t_{TRANSITION}$                     | 240<br>350       | 445            | 515             | ns typ<br>ns max                                      | $R_L = 300 \Omega$ , $C_L = 35 \text{ pF}$<br>$V_S = 8 \text{ V}$ , see Figure 29                                                                                              |

| $t_{ON}$ (EN)                                         | 250<br>335       | 420            | 485             | ns typ<br>ns max                                      | $R_L = 300 \Omega$ , $C_L = 35 \text{ pF}$<br>$V_S = 8 \text{ V}$ , see Figure 31                                                                                              |

| $t_{OFF}$ (EN)                                        | 160<br>195       | 220            | 240             | ns typ<br>ns max                                      | $R_L = 300 \Omega$ , $C_L = 35 \text{ pF}$<br>$V_S = 8 \text{ V}$ , see Figure 31                                                                                              |

| Break-Before-Make Time Delay, $t_D$                   | 140              |                | 60              | ns typ<br>ns min                                      | $R_L = 300 \Omega$ , $C_L = 35 \text{ pF}$<br>$V_{S1} = V_{S2} = 8 \text{ V}$ , see Figure 30                                                                                  |

| Charge Injection, $Q_{INJ}$                           | -1.2             |                |                 | pC typ                                                | $V_S = 6 \text{ V}$ , $R_S = 0 \Omega$ , $C_L = 1 \text{ nF}$ , see Figure 32                                                                                                  |

| Off Isolation                                         | -80              |                |                 | dB typ                                                | $R_L = 50 \Omega$ , $C_L = 5 \text{ pF}$ , $f = 1 \text{ MHz}$ , see Figure 25                                                                                                 |

| Channel-to-Channel Crosstalk                          | -80              |                |                 | dB typ                                                | $R_L = 50 \Omega$ , $C_L = 5 \text{ pF}$ , $f = 1 \text{ MHz}$ , see Figure 28                                                                                                 |

| -3 dB Bandwidth                                       | 106              |                |                 | MHz typ                                               | $R_L = 50 \Omega$ , $C_L = 5 \text{ pF}$ , $f = 1 \text{ MHz}$ , see Figure 27                                                                                                 |

| Insertion Loss                                        | -11              |                |                 | dB typ                                                | $R_L = 50 \Omega$ , $C_L = 5 \text{ pF}$ , $f = 1 \text{ MHz}$ , see Figure 27                                                                                                 |

| $C_S$ (Off)                                           | 3.5              |                |                 | pF typ                                                | $V_S = 6 \text{ V}$ , $f = 1 \text{ MHz}$                                                                                                                                      |

| $C_D$ (Off)                                           | 29               |                |                 | pF typ                                                | $V_S = 6 \text{ V}$ , $f = 1 \text{ MHz}$                                                                                                                                      |

| $C_D$ , $C_S$ (On)                                    | 33               |                |                 | pF typ                                                | $V_S = 6 \text{ V}$ , $f = 1 \text{ MHz}$                                                                                                                                      |

| POWER REQUIREMENTS                                    |                  |                |                 |                                                       |                                                                                                                                                                                |

| $I_{DD}$                                              | 40               |                |                 | $\mu\text{A}$ typ<br>$\mu\text{A}$ max                | $V_{DD} = 13.2 \text{ V}$<br>Digital inputs = 0 V or $V_{DD}$                                                                                                                  |

| $V_{DD}$                                              |                  |                | 65<br>9/40      | V min/max                                             | GND = 0 V, $V_{SS} = 0 \text{ V}$                                                                                                                                              |

<sup>1</sup> 設計上保証しますが、出荷テストは行いません。

## 36 V单電源

特に指定がない限り、 $V_{DD} = 36 \text{ V} \pm 10\%$ 、 $V_{SS} = 0 \text{ V}$ 、 $\text{GND} = 0 \text{ V}$ 。

表 4.

| Parameter                                             | 25°C               | -40°C to +85°C | -40°C to +125°C | Unit                                         | Test Conditions/Comments                                                                                                                                                       |

|-------------------------------------------------------|--------------------|----------------|-----------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                         |                    |                |                 |                                              |                                                                                                                                                                                |

| Analog Signal Range                                   |                    |                | 0 V to $V_{DD}$ | V max                                        |                                                                                                                                                                                |

| On Resistance, $R_{ON}$                               | 150<br>170         | 215            | 245             | $\Omega$ typ<br>$\Omega$ max<br>$\Omega$ typ | $V_S = 0 \text{ V}$ to 30 V, $I_S = -1 \text{ mA}$ , see Figure 24<br>$V_{DD} = 32.4 \text{ V}$ , $V_{SS} = 0 \text{ V}$<br>$V_S = 0 \text{ V}$ to 30 V, $I_S = -1 \text{ mA}$ |

| On-Resistance Match Between Channels, $\Delta R_{ON}$ | 4.5                |                |                 | $\Omega$ typ                                 |                                                                                                                                                                                |

| On-Resistance Flatness, $R_{FLAT(ON)}$                | 8<br>35<br>50      | 9<br>60        | 10<br>65        | $\Omega$ max<br>$\Omega$ typ<br>$\Omega$ max | $V_S = 0 \text{ V}$ to 30 V, $I_S = -1 \text{ mA}$                                                                                                                             |

| LEAKAGE CURRENTS                                      |                    |                |                 |                                              |                                                                                                                                                                                |

| Source Off Leakage, $I_S$ (Off)                       | 0.01               |                |                 | nA typ                                       | $V_{DD} = 39.6 \text{ V}$ , $V_{SS} = 0 \text{ V}$                                                                                                                             |

| Drain Off Leakage, $I_D$ (Off)                        | 0.1<br>0.01        | 0.2            | 0.4             | nA max<br>nA typ                             | $V_S = 1 \text{ V}/30 \text{ V}$ , $V_D = 30 \text{ V}/1 \text{ V}$ , see Figure 23                                                                                            |

| Channel On Leakage, $I_D$ , $I_S$ (On)                | 0.1<br>0.02<br>0.2 | 0.4<br>0.5     | 1.2<br>1.2      | nA max<br>nA typ<br>nA max                   | $V_S = 1 \text{ V}/30 \text{ V}$ , $V_D = 30 \text{ V}/1 \text{ V}$ , see Figure 23<br>$V_S = V_D = 1 \text{ V}/30 \text{ V}$ , see Figure 26                                  |

| DIGITAL INPUTS                                        |                    |                |                 |                                              |                                                                                                                                                                                |

| Input High Voltage, $V_{INH}$                         |                    |                | 2.0             | V min                                        |                                                                                                                                                                                |

| Input Low Voltage, $V_{INL}$                          |                    |                | 0.8             | V max                                        |                                                                                                                                                                                |

| Input Current, $I_{INL}$ or $I_{INH}$                 | 0.002              |                | $\pm 0.1$       | $\mu\text{A}$ typ<br>$\mu\text{A}$ max       | $V_{IN} = V_{GND}$ or $V_{DD}$                                                                                                                                                 |

| Digital Input Capacitance, $C_{IN}$                   | 3                  |                |                 | pF typ                                       |                                                                                                                                                                                |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                  |                    |                |                 |                                              |                                                                                                                                                                                |

| Transition Time, $t_{TRANSITION}$                     | 180<br>250         | 275            | 305             | ns typ<br>ns max                             | $R_L = 300 \Omega$ , $C_L = 35 \text{ pF}$<br>$V_S = 18 \text{ V}$ , see Figure 29                                                                                             |

| $t_{ON}$ (EN)                                         | 170<br>220         | 251            | 285             | ns typ<br>ns max                             | $R_L = 300 \Omega$ , $C_L = 35 \text{ pF}$<br>$V_S = 18 \text{ V}$ , see Figure 31                                                                                             |

| $t_{OFF}$ (EN)                                        | 170<br>210         | 215            | 220             | ns typ<br>ns max                             | $R_L = 300 \Omega$ , $C_L = 35 \text{ pF}$<br>$V_S = 18 \text{ V}$ , see Figure 31                                                                                             |

| Break-Before-Make Time Delay, $t_D$                   | 80                 |                | 30              | ns typ<br>ns min                             | $R_L = 300 \Omega$ , $C_L = 35 \text{ pF}$<br>$V_{SI} = V_{S2} = 18 \text{ V}$ , see Figure 30                                                                                 |

| Charge Injection, $Q_{INJ}$                           | -0.6               |                |                 | pC typ                                       | $V_S = 18 \text{ V}$ , $R_S = 0 \Omega$ , $C_L = 1 \text{ nF}$ , see Figure 32                                                                                                 |

| Off Isolation                                         | -80                |                |                 | dB typ                                       | $R_L = 50 \Omega$ , $C_L = 5 \text{ pF}$ , $f = 1 \text{ MHz}$ , see Figure 25                                                                                                 |

| Channel-to-Channel Crosstalk                          | -80                |                |                 | dB typ                                       | $R_L = 50 \Omega$ , $C_L = 5 \text{ pF}$ , $f = 1 \text{ MHz}$ , see Figure 28                                                                                                 |

| -3 dB Bandwidth                                       | 136                |                |                 | MHz typ                                      | $R_L = 50 \Omega$ , $C_L = 5 \text{ pF}$ , see Figure 27                                                                                                                       |

| Insertion Loss                                        | -6.7               |                |                 | dB typ                                       | $R_L = 50 \Omega$ , $C_L = 5 \text{ pF}$ , $f = 1 \text{ MHz}$ , see Figure 27                                                                                                 |

| $C_S$ (Off)                                           | 3                  |                |                 | pF typ                                       | $V_S = 18 \text{ V}$ , $f = 1 \text{ MHz}$                                                                                                                                     |

| $C_D$ (Off)                                           | 26                 |                |                 | pF typ                                       | $V_S = 18 \text{ V}$ , $f = 1 \text{ MHz}$                                                                                                                                     |

| $C_D$ , $C_S$ (On)                                    | 30                 |                |                 | pF typ                                       | $V_S = 18 \text{ V}$ , $f = 1 \text{ MHz}$                                                                                                                                     |

| POWER REQUIREMENTS                                    |                    |                |                 |                                              |                                                                                                                                                                                |

| $I_{DD}$                                              | 85<br>100          |                | 130<br>9/40     | $\mu\text{A}$ typ<br>$\mu\text{A}$ max       | $V_{DD} = 39.6 \text{ V}$<br>Digital inputs = 0 V or $V_{DD}$                                                                                                                  |

| $V_{DD}$                                              |                    |                |                 | V min/max                                    | $GND = 0 \text{ V}$ , $V_{SS} = 0 \text{ V}$                                                                                                                                   |

<sup>1</sup> 設計上保証しますが、出荷テストは行いません。

## チャンネルあたりの連続電流、S<sub>x</sub>またはD

表 5.

| Parameter                                                                                                                                                                   | 25°C         | 85°C       | 125°C      | Unit             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|------------|------------------|

| CONTINUOUS CURRENT, S <sub>x</sub> OR D PINS<br>V <sub>DD</sub> = +15 V, V <sub>SS</sub> = -15 V<br>TSSOP ( $\theta_{JA}$ = 112.6°C/W)<br>LFCSP ( $\theta_{JA}$ = 30.4°C/W) | 24.5<br>35.7 | 7.5<br>7.7 | 2.8<br>2.8 | mA max<br>mA max |

| V <sub>DD</sub> = +20 V, V <sub>SS</sub> = -20 V<br>TSSOP ( $\theta_{JA}$ = 112.6°C/W)<br>LFCSP ( $\theta_{JA}$ = 30.4°C/W)                                                 | 26<br>37     | 7.5<br>7.7 | 2.8<br>2.8 | mA max<br>mA max |

| V <sub>DD</sub> = 12 V, V <sub>SS</sub> = 0 V<br>TSSOP ( $\theta_{JA}$ = 112.6°C/W)<br>LFCSP ( $\theta_{JA}$ = 30.4°C/W)                                                    | 18<br>28     | 7<br>7.7   | 2.8<br>2.8 | mA max<br>mA max |

| V <sub>DD</sub> = 36 V, V <sub>SS</sub> = 0 V<br>TSSOP ( $\theta_{JA}$ = 112.6°C/W)<br>LFCSP ( $\theta_{JA}$ = 30.4°C/W)                                                    | 30<br>41     | 7.7<br>7.7 | 2.8<br>2.8 | mA max<br>mA max |

## 絶対最大定格

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

表 6.

| Parameter                                                      | Rating                                                                                   |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------|

| $V_{DD}$ to $V_{SS}$                                           | 48 V                                                                                     |

| $V_{DD}$ to GND                                                | -0.3 V to +48 V                                                                          |

| $V_{SS}$ to GND                                                | +0.3 V to -48 V                                                                          |

| Analog Inputs <sup>1</sup>                                     | $V_{SS} - 0.3 \text{ V}$ to $V_{DD} + 0.3 \text{ V}$ or<br>30 mA, whichever occurs first |

| Digital Inputs <sup>1</sup>                                    | $V_{SS} - 0.3 \text{ V}$ to $V_{DD} + 0.3 \text{ V}$ or<br>30 mA, whichever occurs first |

| Peak Current, Sx or D Pins                                     | 81 mA (pulsed at 1 ms,<br>10% duty cycle maximum)                                        |

| Continuous Current, Sx or D <sup>2</sup>                       | Data + 15%                                                                               |

| Operating Temperature Range                                    | -40°C to +125°C                                                                          |

| Storage Temperature Range                                      | -65°C to +150°C                                                                          |

| Junction Temperature                                           | 150°C                                                                                    |

| Thermal Impedance, $\theta_{JA}$                               |                                                                                          |

| 16-Lead TSSOP, $\theta_{JA}$ Thermal Impedance (4-Layer Board) | 112.6°C/W                                                                                |

| 16-Lead LFCSP, $\theta_{JA}$ Thermal Impedance (4-Layer Board) | 30.4°C/W                                                                                 |

| Reflow Soldering Peak Temperature, Pb Free                     | 260(+0/-5)°C                                                                             |

<sup>1</sup> Sx ピンと D ピンでの過電圧は内部ダイオードでクランプされます。電流は、規定された最大定格に制限してください。

<sup>2</sup> 表 5 を参照してください。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

同時に複数の絶対最大定格条件を適用することはできません。

### ESD の注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

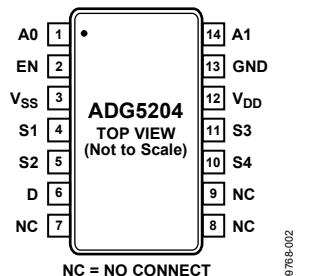

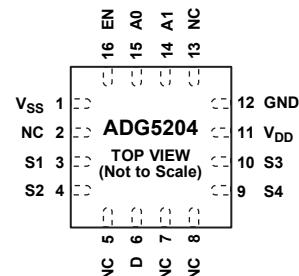

## ピン配置およびピン機能説明

図 2.TSSOP のピン配置

図 3.LFCSP のピン配置

表 7. ピン機能の説明

| ピン番号             |            | 記号              | 説明                                                                                                                    |

|------------------|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------|

| TSSOP            | LFCSP      |                 |                                                                                                                       |

| 1                | 15         | A0              | ロジック・コントロール入力。                                                                                                        |

| 2                | 16         | EN              | アクティブ・ハイのデジタル入力。このピンがロー・レベルのとき、デバイスはディスエーブルされるため、すべてのスイッチがターンオフします。<br>このピンがハイ・レベルのとき、Ax ロジック入力によりターンオンするスイッチが指定されます。 |

| 3                | 1          | V <sub>ss</sub> | 負電源電位。                                                                                                                |

| 4                | 3          | S1              | ソース・ピン。入力または出力。                                                                                                       |

| 5                | 4          | S2              | ソース・ピン。入力または出力。                                                                                                       |

| 6                | 6          | D               | ドレイン・ピン。入力または出力。                                                                                                      |

| 7~9              | 2、5、7、8、13 | NC              | 未接続。これらのピンはオープンです。                                                                                                    |

| 10               | 9          | S4              | ソース・ピン。入力または出力。                                                                                                       |

| 11               | 10         | S3              | ソース・ピン。入力または出力。                                                                                                       |

| 12               | 11         | V <sub>dd</sub> | 正電源電位。                                                                                                                |

| 13               | 12         | GND             | グラウンドリファレンス(0 V)。                                                                                                     |

| 14               | 14         | A1              | ロジック・コントロール入力。                                                                                                        |

| N/A <sup>1</sup> | EP         | エクスポートード・パッド    | エクスポートード・パッド。エクスポートード・パッドは内部で接続されています。ハンダ接続の信頼性と熱能力を向上させるために、このパッドをサブストレート V <sub>ss</sub> にハンダ付けすることが推奨されます。         |

<sup>1</sup> N/A=適用なし。

## 真理値表

表 8.

| EN | A1             | A0             | S1  | S2  | S3  | S4  |

|----|----------------|----------------|-----|-----|-----|-----|

| 0  | X <sup>1</sup> | X <sup>1</sup> | Off | Off | Off | Off |

| 1  | 0              | 0              | On  | Off | Off | Off |

| 1  | 0              | 1              | Off | On  | Off | Off |

| 1  | 1              | 0              | Off | Off | On  | Off |

| 1  | 1              | 1              | Off | Off | Off | On  |

<sup>1</sup> X = don't care。

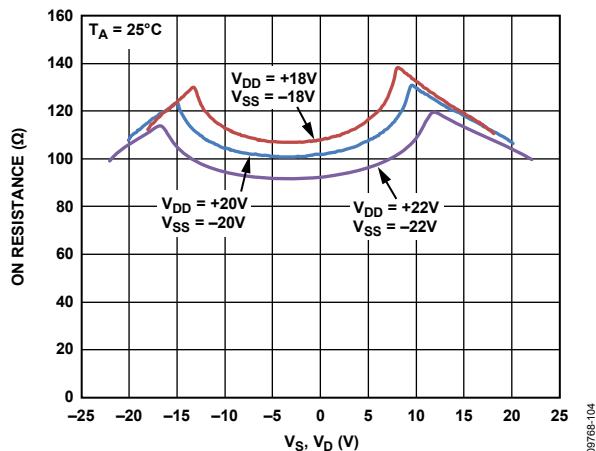

## 代表的な性能特性

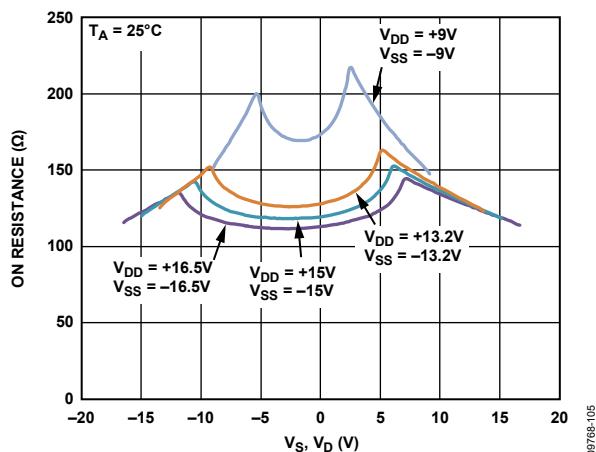

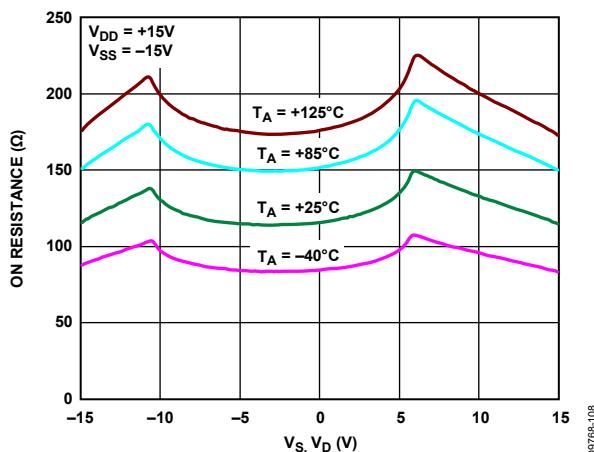

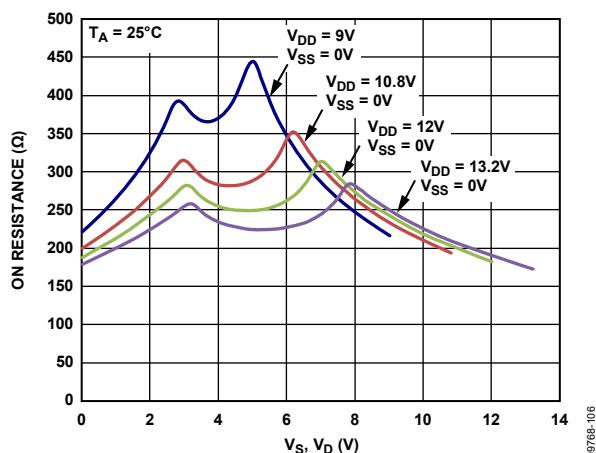

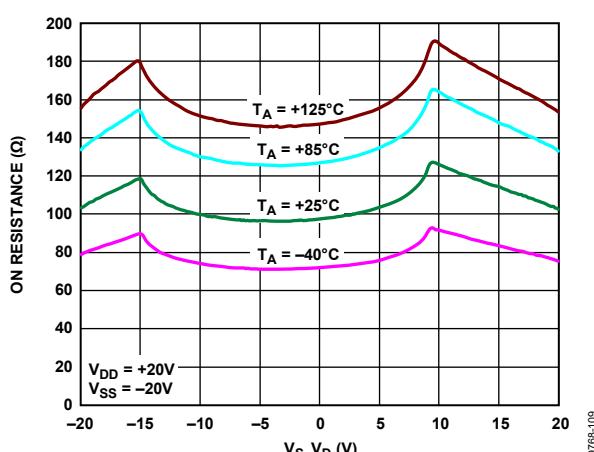

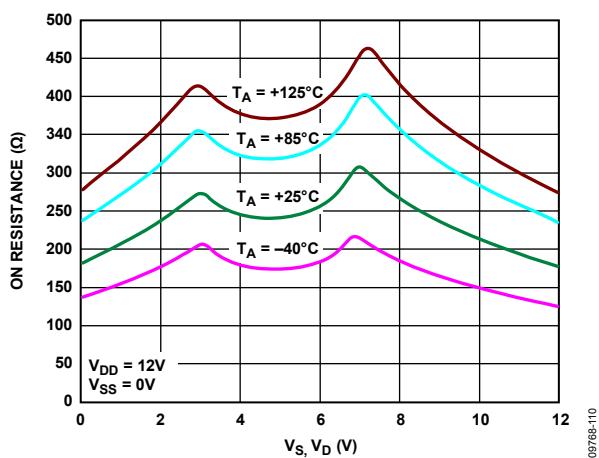

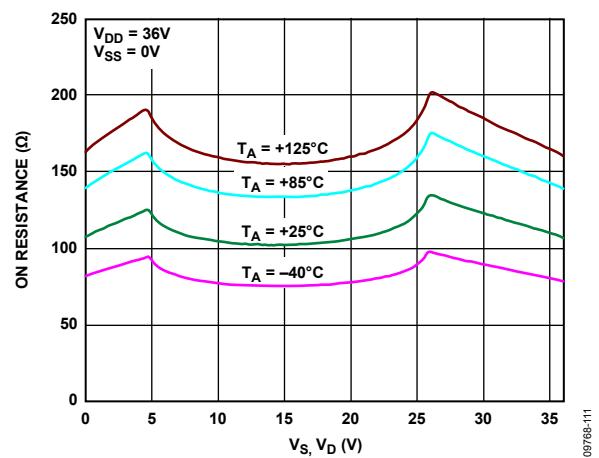

図 4. $V_S$  または  $V_D$  の関数としての  $R_{ON}$ 、両電源図 7. $V_S$  または  $V_D$  の関数としての  $R_{ON}$ 、単電源図 5. $V_S$  または  $V_D$  の関数としての  $R_{ON}$ 、両電源図 8. $V_S$  または  $V_D$  の関数としての様々な温度での  $R_{ON}$

±15 V 両電源図 6. $V_S$  または  $V_D$  の関数としての  $R_{ON}$ 、単電源図 9. $V_S$  または  $V_D$  の関数としての様々な温度での  $R_{ON}$

±20 V 両電源

図 10.  $V_S$  または  $V_D$  の関数としての様々な温度での  $R_{ON}$

12 V 単電源

図 11.  $V_S$  または  $V_D$  の関数としての様々な温度での  $R_{ON}$

36 V 単電源

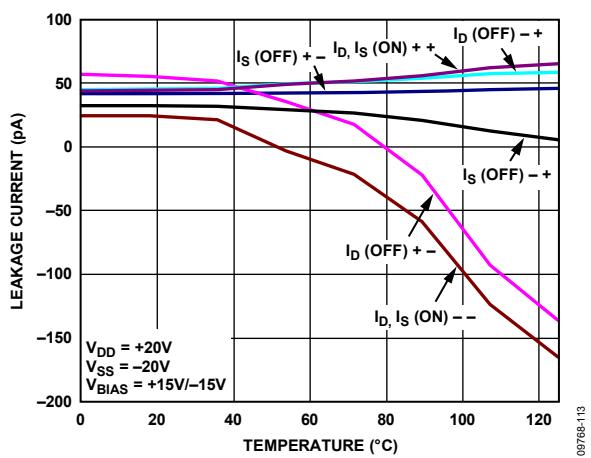

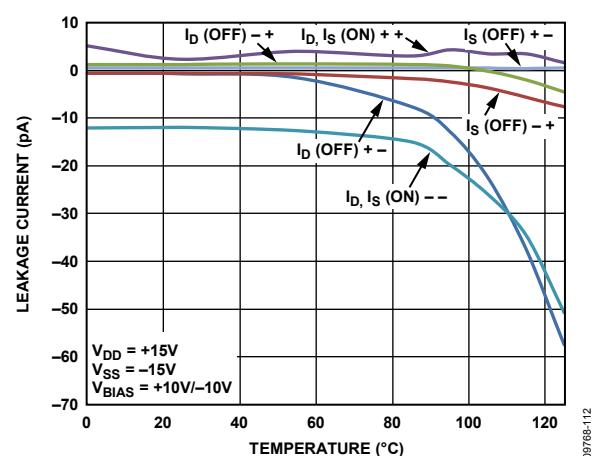

図 13. リーク電流の温度特性、 $\pm 20V$  両電源

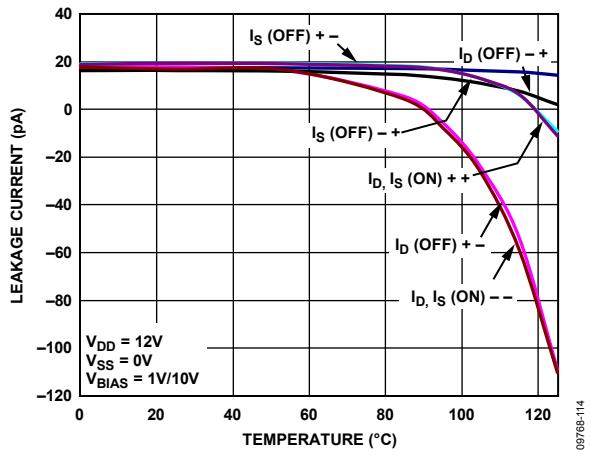

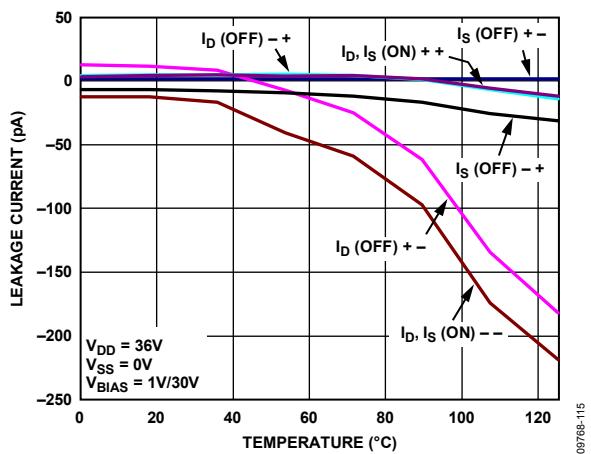

図 14. リーク電流の温度特性、12 V 単電源

図 12. リーク電流の温度特性、 $\pm 15V$  両電源

図 15. リーク電流の温度特性、36 V 単電源

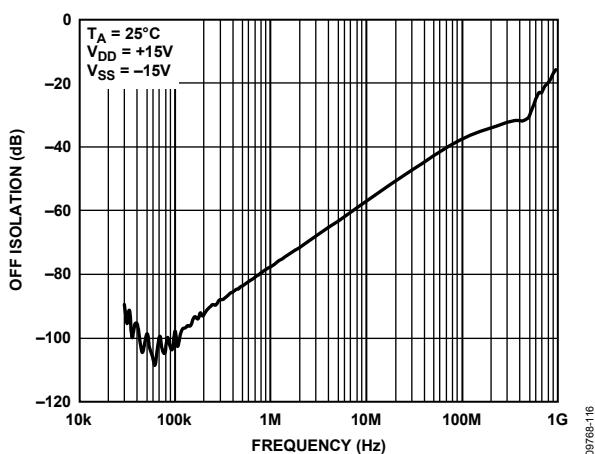

図 16.オフ時アイソレーションの周波数特性、 $\pm 15\text{ V}$ 両電源

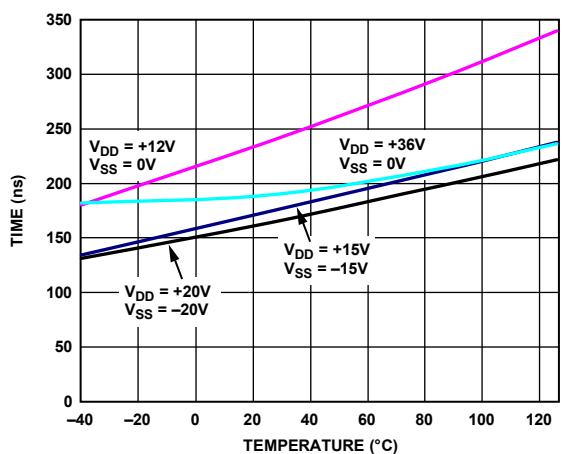

図 19.変化時間の温度特性

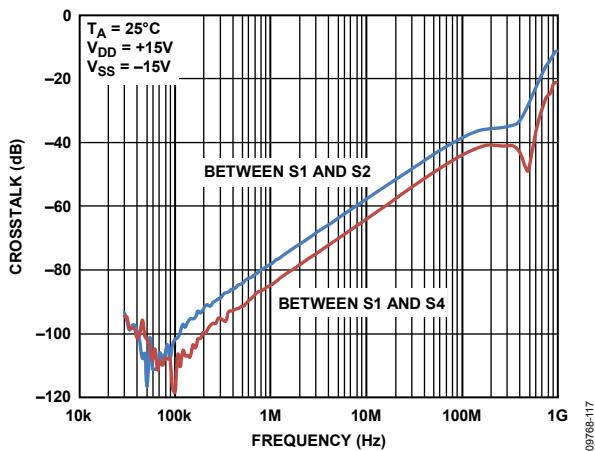

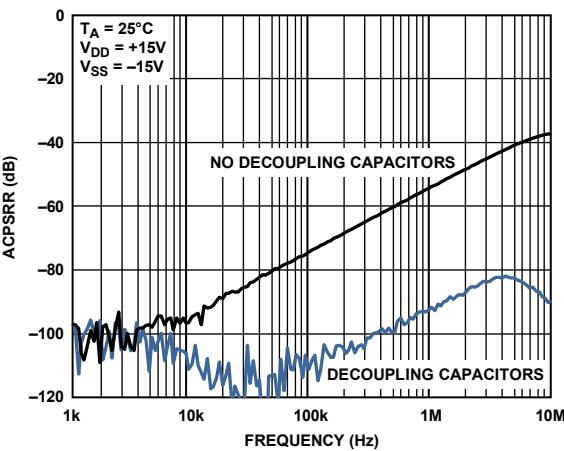

図 17.クロストークの周波数特性、 $\pm 15\text{ V}$ 両電源図 20.ACPSRR の周波数特性、 $\pm 15\text{ V}$ 両電源

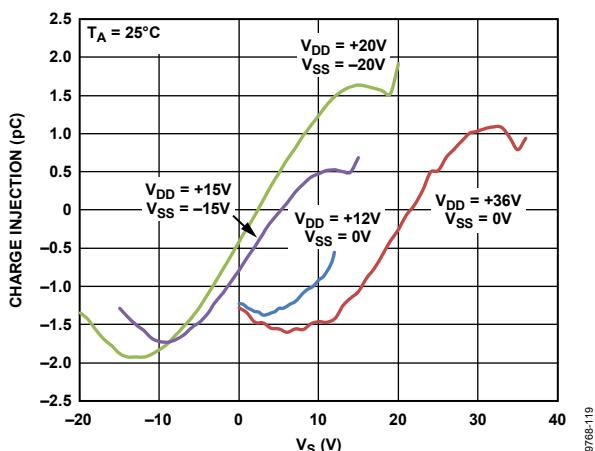

図 18.ソース電圧対チャージ・インジェクション

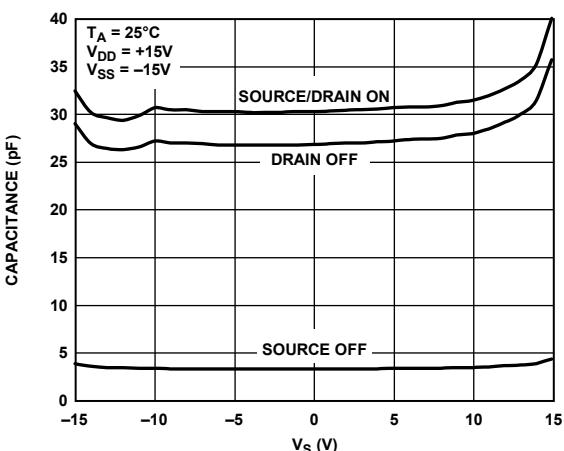

図 21.ソース電圧対容量、両電源

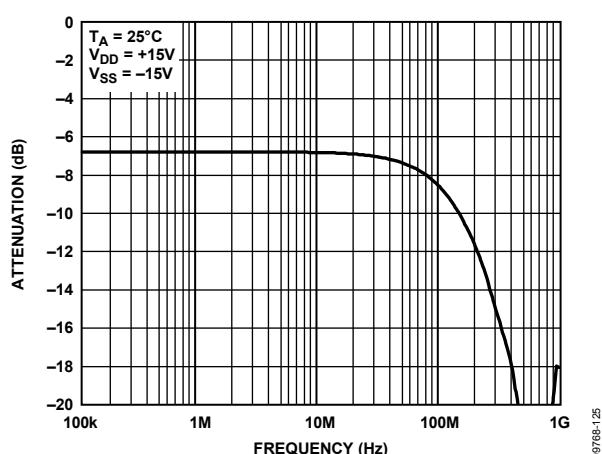

図 22. 帯域幅

## テスト回路

図 23. オフ時リーケ

図 26. オン時リーケ

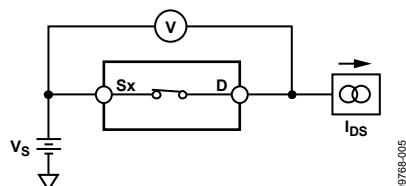

図 24. オン抵抗

図 27. 帯域幅

図 25. オフ時アイソレーション

図 28. チャンネル間クロストーク

図 29. アドレス—出力間のスイッチング時間

図 30. ブレーク・ビフォア・メーク時間遅延、t<sub>D</sub>

図 31. イネーブル—出力間のスイッチング遅延

図 32. チャージ・インジェクション

## 用語

|                                                   |                                                                                                                    |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| <b>I<sub>DD</sub></b>                             | <b>C<sub>IN</sub></b>                                                                                              |

| 正の電源電流。                                           | デジタル入力容量。                                                                                                          |

| <b>I<sub>SS</sub></b>                             | <b>t<sub>TRANSITION</sub></b>                                                                                      |

| 負電源電流。                                            | あるアドレス状態から別のアドレス状態へ切り替わるときのデジタル入力の 50%/90% ポイントとスイッチ・オン状態との間の遅延時間。                                                 |

| <b>V<sub>D</sub>、V<sub>S</sub></b>                | <b>t<sub>ON (EN)</sub></b>                                                                                         |

| D、S ピンのアナログ電圧。                                    | デジタル・コントロール入力の入力から出力スイッチ・オンまでの遅延。図 31 を参照してください。                                                                   |

| <b>R<sub>ON</sub></b>                             | <b>t<sub>OFF (EN)</sub></b>                                                                                        |

| D-S 間の抵抗                                          | デジタル・コントロール入力の入力から出力スイッチ・オフまでの遅延。図 31 を参照してください。                                                                   |

| <b>R<sub>FLAT(ON)</sub></b>                       | <b>チャージ・インジェクション</b>                                                                                               |

| 平坦性は、仕様で規定されたアナログ信号範囲におけるオン抵抗の最大値と最小値の差として定義されます。 | スイッチング時にデジタル入力からアナログ出力へ伝達されるグリッヂ・インパルスの大きさ。                                                                        |

| <b>I<sub>s (Off)</sub></b>                        | <b>オフ時アイソレーション</b>                                                                                                 |

| スイッチ・オフ時のソース・リーク電流。                               | 「オフ」状態のスイッチを通過する不要信号の大きさ。                                                                                          |

| <b>I<sub>d (Off)</sub></b>                        | <b>クロストーク</b>                                                                                                      |

| スイッチ・オフ時のドレイン・リーク電流。                              | 寄生容量に起因して 1 つのチャンネルから別のチャンネルに伝達される不要信号の大きさ。                                                                        |

| <b>I<sub>d</sub>、I<sub>s (On)</sub></b>           | <b>帯域幅</b>                                                                                                         |

| スイッチ・オン時のチャンネル・リーク電流。                             | 出力が 3 dB 減衰する周波数。                                                                                                  |

| <b>V<sub>INL</sub></b>                            | <b>オン応答</b>                                                                                                        |

| ロジック 0 の最大入力電圧。                                   | 「オン」状態にあるスイッチの周波数応答。                                                                                               |

| <b>V<sub>INH</sub></b>                            | <b>挿入損失</b>                                                                                                        |

| ロジック 1 の最小入力電圧。                                   | スイッチのオン抵抗に起因する損失。                                                                                                  |

| <b>I<sub>INL</sub>、I<sub>INH</sub></b>            | <b>ACPSRR (AC 電源除去比)</b>                                                                                           |

| デジタル入力の入力電流。                                      | 出力信号振幅の変調振幅に対する比。ACPSRR は、電源電圧ピンに現れるノイズとスプリアス信号がスイッチ出力へ混入するのを防止するデバイスの能力を表します。デバイスの DC 電圧が、0.62 V p-p の正弦波で変調されます。 |

| <b>C<sub>s (Off)</sub></b>                        |                                                                                                                    |

| スイッチ・オフ時のソース容量。グラウンドを基準として測定。                     |                                                                                                                    |

| <b>C<sub>d (Off)</sub></b>                        |                                                                                                                    |

| スイッチ・オフ時のドレイン容量。グラウンドを基準として測定。                    |                                                                                                                    |

| <b>C<sub>d (On)</sub>、C<sub>s (On)</sub></b>      |                                                                                                                    |

| スイッチ・オン時の容量。グラウンドを基準として測定。                        |                                                                                                                    |

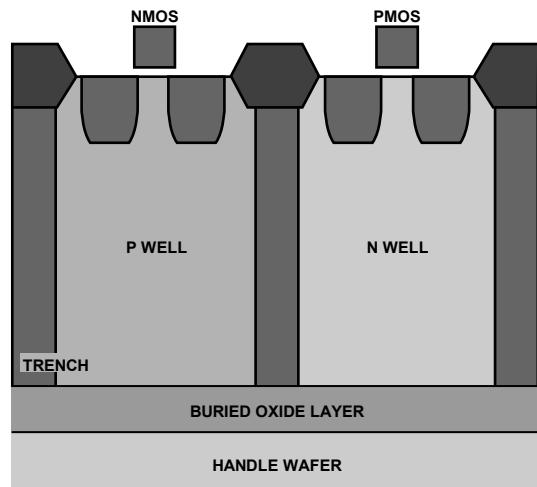

## トレンチ・アイソレーション

ADG5204 では、各 CMOS スイッチの NMOS ドラフトと PMOS ドラフトの間に絶縁酸化物層(トレンチ)が設けてあります。接合で絶縁されたスイッチ内の複数のドラフト間に発生する寄生接合がなくなるため、ラッチアップを完全に防止したスイッチが得られます。

接合アイソレーションでは、PMOS ドラフトと NMOS ドラフトの N ウエルと P ウエルが、通常動作では逆バイアスされるダイオードを形成しますが、過電圧状態では、このダイオードが順方向バイアスされるようになります。2 個のドラフトによりシリコン制御整流子(SCR)タイプの回路が形成されるため、電流が大幅に増幅されて、ラッチアップが発生します。トレンチ・アイソレーションでは、このダイオードがなくなるため、ラッチアップのないスイッチが実現できます。

図 33. トレンチ・アイソレーション

09768-004

## アプリケーション情報

ADG52xx ファミリーのスイッチ/マルチプレクサは、ラッチアップが発生しやすい計装、工業用、車載、航空宇宙、その他の厳しい環境に対して強固なソリューションを提供します。ラッチアップは、デバイス故障に至る高電流状態を発生させて、電源をオフにするまで継続します。ADG5204 高電圧マルチプレクサは、9 V～40 V の単電源動作と $\pm 9$  V～ $\pm 22$  V の両電源動作が可能です。

## 外形寸法

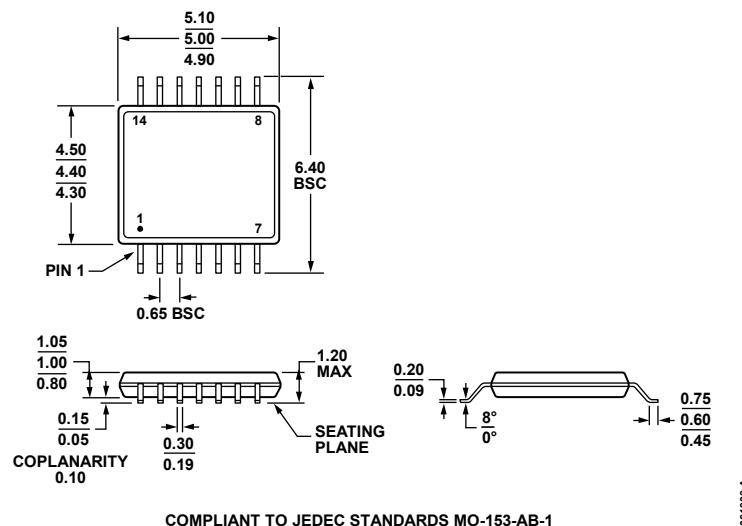

図 34.14 ピン薄型シルリンク・スモール・アウトライン・パッケージ[TSSOP]

(RU-14)

寸法: mm

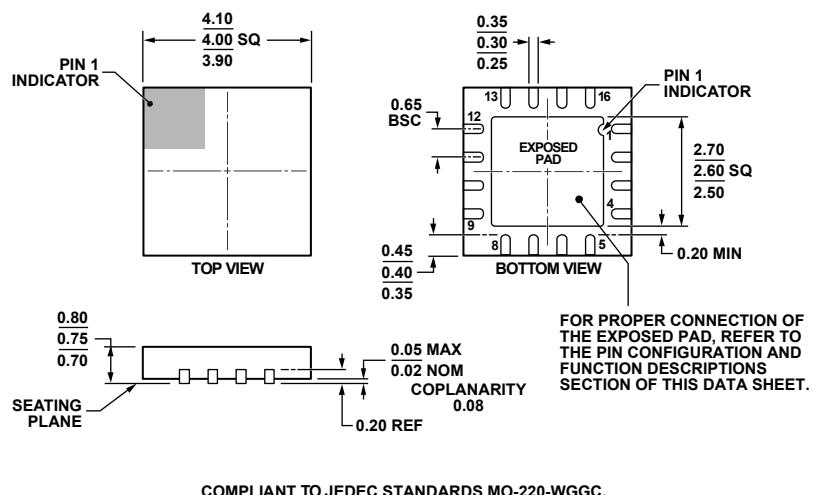

図 35.16 ピン・リードフレーム・チップ・スケール・パッケージ[LFCSP\_WQ]

4 mm x 4 mm ボディ、極薄クワッド

(CP-16-17)

寸法: mm

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                               | Package Option |

|--------------------|-------------------|---------------------------------------------------|----------------|

| ADG5204BRUZ        | -40°C to +125°C   | 14-Lead Thin Shrink Small Outline Package [TSSOP] | RU-14          |

| ADG5204BRUZ-RL7    | -40°C to +125°C   | 14-Lead Thin Shrink Small Outline Package [TSSOP] | RU-14          |

| ADG5204BCPZ-RL7    | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ]  | CP-16-17       |

<sup>1</sup> Z = RoHS 準拠製品。