## 特長

$V_{CC1} = 2.5 \text{ V} \sim 5.5 \text{ V}$  でレール to レールをフル規定

入力コモン・モード電圧:  $-0.2 \text{ V} \sim V_{CC1} + 0.2 \text{ V}$

低グリッチの LVDS 互換出力ステージ

伝搬遅延: 1.6 ns

2.5 V で 37 mW

シャットダウン・ピンを装備

1本のピンでヒステリシスとラッチを制御

電源除去比: 60 dB 以上

動作温度範囲:  $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$

## アプリケーション

高速計装機器

クロックとデータの信号再生

ロジック・レベルのシフトまたは変換

パルス分光学

高速ライン・レシーバ

スレッシュショールド検出

ピークおよびゼロ交差検出器

高速トリガー回路

パルス幅変調器

電流/電圧制御発振器

自動テスト装置(ATE)

## 概要

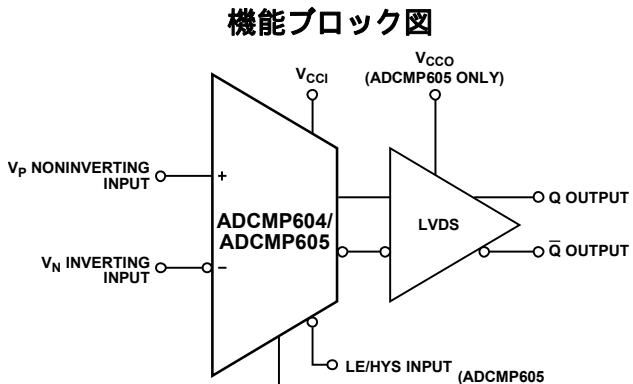

ADCMP604/ADCMP605 は、アナログ・デバイセズの独自なプロセスである XFCB2 で製造された非常に高速なコンパレータです。これらのコンパレータは、非常に融通性があり、使い易くデザインされています。 $V_{EE} - 0.5\text{ V} \sim V_{CCI} + 0.2\text{ V}$  の入力範囲、低ノイズ、LVDS 互換の出力ドライバ、調整可能なヒステリシスおよび/またはシャットダウン入力付きの TTL/CMOS ラッチ入力などの機能を持っています。

これらのデバイスは、1 ps の rms ランダム・ジッタ(RJ)で 1.5 ns の伝搬遅延を提供します。オーバードライブとスルーレートの分散は、50 ps (typ)以下です。

义 1.

05916-001

柔軟な電源方式を採用しているため、これらのデバイスは 2.5 V の単電源では -0.5 V ~ +2.7 V の入力信号レンジで、5.5 V までの正電源では -0.5 V ~ +5.7 V の入力信号レンジで、それぞれ動作することができます。ADCMP605 では入力電源と出力電源を別にすることことができ、電源シーケンスの制約がないため、広い入力信号範囲をサポートすると同時に、出力振幅の独立な制御と省電力が可能です。

LVDS 互換の出力ステージは、標準 LVDS 入力を駆動するようにデザインされています。コンパレータ入力ステージでは、大きな入力オーバードライブに対して強力な保護機能を提供し、有効な入力信号レンジを超えても出力は位相反転しません。ADCMP605 では、ユニークな 1 本のピンによる制御オプションとして、ラッチ機能とプログラマブル・ヒステリシス機能も提供しています。

ADCMP604 は 6 ピンの SC70 パッケージを、ADCMP605 は 12 ピンの LFCSP パッケージを、それぞれ採用しています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。

※日本語データシートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

©2006-2007 Analog Devices, Inc. All rights reserved.

## 目次

|               |   |                     |    |

|---------------|---|---------------------|----|

| 特長            | 1 | アプリケーション情報          | 10 |

| アプリケーション      | 1 | 電源/グラウンドのレイアウトとバイパス | 10 |

| 機能ブロック図       | 1 | LVDS 互換の出力ステージ      | 10 |

| 概要            | 1 | ラッチ機能のイネーブル/ディスエーブル | 10 |

| 改訂履歴          | 2 | 性能の最適化              | 10 |

| 仕様            | 3 | コンパレータ伝搬遅延の分散       | 11 |

| 電気的特性         | 3 | コンパレータのヒステリシス       | 11 |

| タイミング情報       | 5 | クロスオーバーのバイアス・ポイント   | 12 |

| 絶対最大定格        | 6 | 最小入力スルーレート条件        | 12 |

| 熱抵抗           | 6 | 代表的なアプリケーション回路      | 13 |

| ESD の注意       | 6 | 外形寸法                | 14 |

| ピン配置およびピン機能説明 | 7 | オーダー・ガイド            | 14 |

| 代表的な性能特性      | 8 |                     |    |

## 改訂履歴

### 8/07—Rev. 0 to Rev. A

|                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------|----|

| Changes to Features and General Description                                                         | 1  |

| Changes to Electrical Characteristics Section                                                       | 3  |

| Changes to Table 3                                                                                  | 6  |

| Changes to Layout                                                                                   | 7  |

| Changes to Figure 8                                                                                 | 8  |

| Changes to Figure 14                                                                                | 9  |

| Changes to Power/Ground Layout and Bypassing Section, and Using/Disabling the Latch Feature Section | 10 |

| Changes to Comparator Hysteresis Section                                                            | 11 |

| Changes to Crossover Bias Points Section                                                            | 12 |

| Changes to Ordering Guide                                                                           | 14 |

### 10/06—Revision 0: Initial Version

# 仕様

## 電気的特性

特に指定がない限り、 $V_{CCI} = V_{CCO} = 2.5$  V、 $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、typ 値は  $T_A = 25^\circ\text{C}$  での値。

表 1.

| Parameter                                        | Symbol               | Conditions                                                           | Min   | Typ             | Max       | Unit          |

|--------------------------------------------------|----------------------|----------------------------------------------------------------------|-------|-----------------|-----------|---------------|

| DC INPUT CHARACTERISTICS                         |                      |                                                                      |       |                 |           |               |

| Voltage Range                                    | $V_P, V_N$           | $V_{CCI} = 2.5$ V to 5.5 V                                           | -0.5  | $V_{CCI} + 0.2$ |           | V             |

| Common-Mode Range                                |                      | $V_{CCI} = 2.5$ V to 5.5 V                                           | -0.2  | $V_{CCI} + 0.2$ |           | V             |

| Differential Voltage                             |                      | $V_{CCI} = 2.5$ V to 5.5 V                                           |       | $V_{CCI}$       |           | V             |

| Offset Voltage                                   | $V_{OS}$             |                                                                      | -5.0  | +5.0            |           | mV            |

| Bias Current                                     | $I_P, I_N$           |                                                                      | -5.0  | $\pm 2$         | +5.0      | $\mu\text{A}$ |

| Offset Current                                   |                      |                                                                      | -2.0  |                 | +2.0      | $\mu\text{A}$ |

| Capacitance                                      | $C_P, C_N$           |                                                                      |       | 1               |           | pF            |

| Resistance, Differential Mode                    |                      | -0.1 V to $V_{CCI}$                                                  | 200   | 750             | 7500      | k $\Omega$    |

| Resistance, Common Mode                          |                      | -0.5 V to $V_{CCI} + 0.5$ V                                          | 100   | 370             | 4000      | k $\Omega$    |

| Active Gain                                      | $A_V$                |                                                                      |       | 62              |           | dB            |

| Common-Mode Rejection Ratio                      | CMRR                 | $V_{CCI} = 2.5$ V, $V_{CCO} = 2.5$ V,<br>$V_{CM} = -0.2$ V to +2.7 V | 50    |                 |           | dB            |

|                                                  |                      | $V_{CCI} = 2.5$ V, $V_{CCO} = 5.0$ V                                 | 50    |                 |           | dB            |

| Hysteresis                                       |                      | $R_{HYS} = \infty$                                                   |       | <0.1            |           | mV            |

| LATCH ENABLE PIN CHARACTERISTICS (ADCMP605 ONLY) |                      |                                                                      |       |                 |           |               |

| $V_{IH}$                                         |                      | Hysteresis is shut off                                               | 2.0   |                 | $V_{CCO}$ | V             |

| $V_{IL}$                                         |                      | Latch mode guaranteed                                                | -0.2  | +0.4            | +0.8      | V             |

| $I_{IH}$                                         |                      | $V_{IH} = V_{CCO} + 0.2$ V                                           | -6    |                 | +6        | $\mu\text{A}$ |

| $I_{IL}$                                         |                      | $V_{IL} = 0.4$ V                                                     | -0.1  |                 | +0.1      | mA            |

| HYSTERESIS MODE AND TIMING (ADCMP605 ONLY)       |                      |                                                                      |       |                 |           |               |

| Hysteresis Mode Bias Voltage                     |                      | Current sink -1 $\mu\text{A}$                                        | 1.145 | 1.25            | 1.40      | V             |

| Minimum Resistor Value                           |                      | Hysteresis = 120 mV                                                  | 30    |                 | 110       | k $\Omega$    |

| Hysteresis Current                               |                      | Hysteresis = 120 mV                                                  | -25   |                 | -8        | $\mu\text{A}$ |

| Latch Setup Time                                 | $t_S$                | $V_{OD} = 50$ mV                                                     |       | -2              |           | ns            |

| Latch Hold Time                                  | $t_H$                | $V_{OD} = 50$ mV                                                     |       | 2.7             |           | ns            |

| Latch-to-Output Delay                            | $t_{PLOH}, t_{PLOL}$ | $V_{OD} = 50$ mV                                                     |       | 20              |           | ns            |

| Latch Minimum Pulse Width                        | $t_{PL}$             | $V_{OD} = 50$ mV                                                     |       | 24              |           | ns            |

| SHUTDOWN PIN CHARACTERISTICS (ADCMP605 ONLY)     |                      |                                                                      |       |                 |           |               |

| $V_{IH}$                                         |                      | Comparator is operating                                              | 2.0   |                 | $V_{CCO}$ | V             |

| $V_{IL}$                                         |                      | Shutdown guaranteed                                                  | -0.2  | +0.4            | +0.6      | V             |

| $I_{IH}$                                         |                      | $V_{IH} = V_{CCO}$                                                   | -6    |                 | +6        | $\mu\text{A}$ |

| $I_{IL}$                                         |                      | $V_{IL} = 0$ V                                                       |       |                 | -0.1      | mA            |

| Sleep Time                                       | $t_{SD}$             | 10% output swing                                                     |       | 1.4             |           | ns            |

| Wake-Up Time                                     | $t_H$                | $V_{OD} = 50$ mV, output valid                                       |       | 25              |           | ns            |

| DC OUTPUT CHARACTERISTICS                        |                      | $V_{CCI} = V_{CCO} = 2.5$ V to 5.0 V (ADCMP604)                      |       |                 |           |               |

| Differential Output Voltage Level                | $V_{OD}$             | $V_{CCO} = 2.5$ V to 5.0 V (ADCMP605)                                | 245   | 350             | 445       | mV            |

| $\Delta V_{OD}$                                  |                      | $R_{LOAD} = 100 \Omega$                                              |       |                 | 50        | mV            |

| Common-Mode Voltage                              | $V_{OCI}$            | $R_{LOAD} = 100 \Omega$                                              | 1.125 |                 | 1.375     | V             |

| Peak-to-Peak Common-Mode Output                  | $V_{OC(p-p)}$        | $R_{LOAD} = 100 \Omega$                                              |       |                 | 50        | mV            |

# ADCMP604/ADCMP605

| Parameter                                           | Symbol              | Conditions                                                                                       | Min  | Typ  | Max | Unit          |

|-----------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------|------|------|-----|---------------|

| AC PERFORMANCE <sup>1</sup>                         |                     |                                                                                                  |      |      |     |               |

| Rise Time/Fall Time                                 | $t_R, t_F$          | 10% to 90%                                                                                       |      | 600  |     | ps            |

| Propagation Delay                                   | $t_{PD}$            | $V_{CCI} = V_{CCO} = 2.5 \text{ V to } 5.0 \text{ V}$ ,<br>$V_{OD} = 50 \text{ mV}$              |      | 1.6  |     | ns            |

| Propagation Delay Skew—Rising to Falling Transition | $t_{PINSKEW}$       | $V_{CCI} = V_{CCO} = 2.5 \text{ V, } V_{OD} = 10 \text{ mV}$                                     |      | 3.0  |     | ns            |

| Propagation Delay Skew—Q to QB                      |                     | $V_{CCI} = V_{CCO} = 2.5 \text{ V to } 5.0 \text{ V}$                                            |      | 70   |     | ps            |

| Overdrive Dispersion                                |                     | $V_{CCI} = V_{CCO} = 2.5 \text{ V to } 5.0 \text{ V}$                                            |      | 70   |     | ps            |

| Common-Mode Dispersion                              |                     | $10 \text{ mV} < V_{OD} < 125 \text{ mV}$                                                        |      | 1.6  |     | ns            |

| Input Bandwidth                                     |                     | $V_{CM} = -0.2 \text{ V to } V_{CCI} + 0.2 \text{ V}$                                            |      | 250  |     | ps            |

| Minimum Pulse Width                                 | $PW_{MIN}$          | $V_{CCI} = V_{CCO} = 2.5 \text{ V to } 5.0 \text{ V}$ ,<br>$PW_{OUT} = 90\% \text{ of } PW_{IN}$ |      | 500  |     | MHz           |

|                                                     |                     |                                                                                                  |      | 1.3  |     | ns            |

| POWER SUPPLY                                        |                     |                                                                                                  |      |      |     |               |

| Input Supply Voltage Range                          | $V_{CCI}$           |                                                                                                  | 2.5  | 5.5  |     | V             |

| Output Supply Voltage Range                         | $V_{CCO}$           |                                                                                                  | 2.5  | 5.0  |     | V             |

| Positive Supply Differential (ADCMP605)             | $V_{CCI} - V_{CCO}$ | Operating                                                                                        | -3   | +3   |     | V             |

|                                                     | $V_{CCI} - V_{CCO}$ | Nonoperating                                                                                     | -5.0 | +5.0 |     | V             |

| Positive Supply Current (ADCMP604)                  | $I_{VCCI/VCCO}$     | $V_{CCI} = V_{CCO} = 2.5 \text{ V to } 5.0 \text{ V}$                                            | 15   | 21   |     | mA            |

| Input Section Supply Current (ADCMP605)             | $I_{VCCI}$          | $V_{CCI} = 2.5 \text{ V to } 5.5 \text{ V}$                                                      | 1.6  | 3.0  |     | mA            |

| Output Section Supply Current (ADCMP605)            | $I_{VCCO}$          | $V_{CCO} = 2.5 \text{ V to } 5.0 \text{ V}$                                                      | 15   | 23   |     | mA            |

| Power Dissipation                                   | $P_D$               | $V_{CCI} = V_{CCO} = 2.5 \text{ V}$                                                              | 37   | 55   |     | mW            |

|                                                     |                     | $V_{CCI} = V_{CCO} = 5.0 \text{ V}$                                                              | 95   | 120  |     | mW            |

| Power Supply Rejection Ratio                        | $PSRR$              | $V_{CCI} = V_{CCO} = 2.5 \text{ V to } 5.0 \text{ V}$                                            | -50  |      |     | dB            |

| Shutdown Mode $I_{CCI}$                             |                     | $V_{CCI} = V_{CCO} = 2.5 \text{ V to } 5.0 \text{ V}$                                            |      | 0.92 | 1.1 | mA            |

| Shutdown Mode $I_{CCO}$                             |                     | $V_{CCI} = V_{CCO} = 2.5 \text{ V to } 5.0 \text{ V}$                                            | -30  |      | +30 | $\mu\text{A}$ |

<sup>1</sup> 特に指定のない限り、 $V_{OD} = 50 \text{ mV}$ 、 $V_{CM} = 1.25 \text{ V}$ 、 $V_{CCI} = V_{CCO} = 2.5 \text{ V}$ 、50 MHz の  $V_{IN} = 100 \text{ mV}$  方波入力。

## タイミング情報

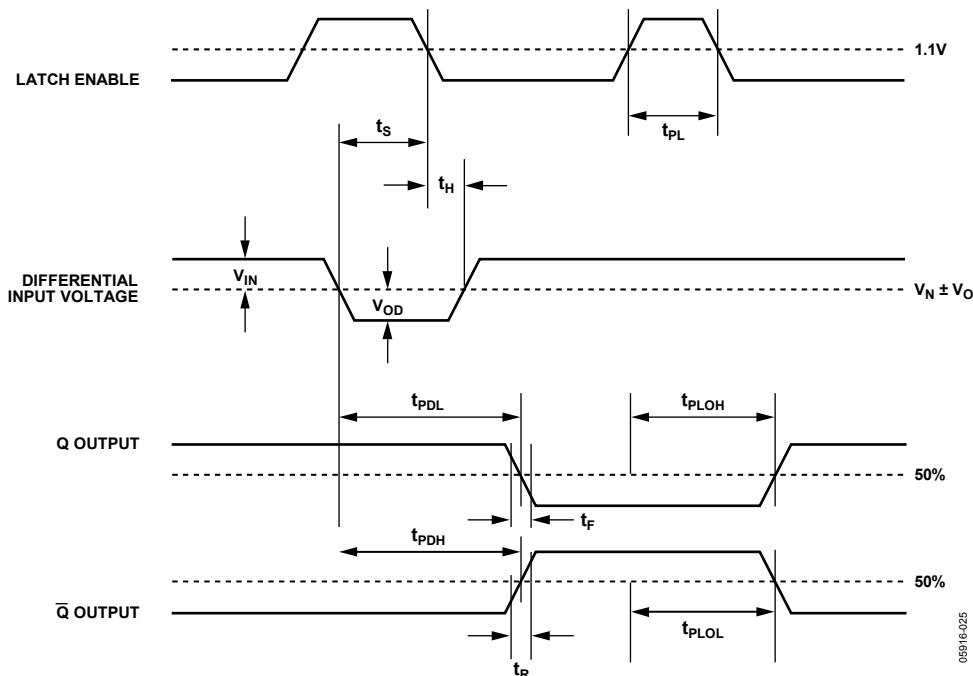

図2に、ADCMP604/ADCMP605のラッチ・タイミング関係を示します。表2に、図2に示す回路の周波数応答を示します。

図2.システム・タイミング図

表2.タイミング説明

| Symbol     | Timing                            | Description                                                                                                                                                             |

|------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{PDH}$  | Input-to-Output High Delay        | Propagation delay measured from the time the input signal crosses the reference ( $\pm$ the input offset voltage) to the 50% point of an output low-to-high transition. |

| $t_{PDL}$  | Input-to-Output Low Delay         | Propagation delay measured from the time the input signal crosses the reference ( $\pm$ the input offset voltage) to the 50% point of an output high-to-low transition. |

| $t_{PLOH}$ | Latch Enable-to-Output High Delay | Propagation delay measured from the 50% point of the latch enable signal low-to-high transition to the 50% point of an output low-to-high transition.                   |

| $t_{PLOL}$ | Latch Enable-to-Output Low Delay  | Propagation delay measured from the 50% point of the latch enable signal low-to-high transition to the 50% point of an output high-to-low transition.                   |

| $t_H$      | Minimum Hold Time                 | Minimum time after the negative transition of the latch enable signal that the input signal must remain unchanged to be acquired and held at the outputs.               |

| $t_{PL}$   | Minimum Latch Enable Pulse Width  | Minimum time that the latch enable signal must be high to acquire an input signal change.                                                                               |

| $t_s$      | Minimum Setup Time                | Minimum time before the negative transition of the latch enable signal occurs that an input signal change must be present to be acquired and held at the outputs.       |

| $t_R$      | Output Rise Time                  | Amount of time required to transition from a low to a high output as measured at the 20% and 80% points.                                                                |

| $t_f$      | Output Fall Time                  | Amount of time required to transition from a high to a low output as measured at the 20% and 80% points.                                                                |

| $V_{OD}$   | Voltage Overdrive                 | Difference between the input voltages, $V_A$ and $V_B$ .                                                                                                                |

## 絶対最大定格

表 3.

| Parameter                                                           | Rating                             |

|---------------------------------------------------------------------|------------------------------------|

| Supply Voltages                                                     |                                    |

| Input Supply Voltage (V <sub>CCI</sub> to GND)                      | -0.5 V to +6.0 V                   |

| Output Supply Voltage (V <sub>CCO</sub> to GND)                     | -0.5 V to +6.0 V                   |

| Positive Supply Differential (V <sub>CCI</sub> - V <sub>CCO</sub> ) | -6.0 V to +6.0 V                   |

| Input Voltages                                                      |                                    |

| Input Voltage                                                       | -0.5 V to V <sub>CCI</sub> + 0.5 V |

| Differential Input Voltage                                          | ±(V <sub>CCI</sub> + 0.5 V)        |

| Maximum Input/Output Current                                        | ±50 mA                             |

| Shutdown Control Pin                                                |                                    |

| Applied Voltage (S <sub>DN</sub> to GND)                            | -0.5 V to V <sub>CCO</sub> + 0.5 V |

| Maximum Input/Output Current                                        | ±50 mA                             |

| Latch/Hysteresis Control Pin                                        |                                    |

| Applied Voltage (HYS to GND)                                        | -0.5 V to V <sub>CCO</sub> + 0.5 V |

| Maximum Input/Output Current                                        | ±50 mA                             |

| Output Current                                                      | ±50 mA                             |

| Temperature                                                         |                                    |

| Operating Temperature Range, Ambient                                | -40°C to +125°C                    |

| Operating Temperature, Junction                                     | 150°C                              |

| Storage Temperature Range                                           | -65°C to +150°C                    |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

### 熱抵抗

θ<sub>JA</sub> はワーストケース条件で規定。すなわち表面実装パッケージの場合、デバイスを回路ボードにハンダ付けした状態で規定。

表 4. 热抵抗

| Package Type               | θ <sub>JA</sub> <sup>1</sup> | Unit |

|----------------------------|------------------------------|------|

| 6-Lead SC70 (KS-6)         | 426                          | °C/W |

| 12-Lead LFCSP_VQ (CP-12-1) | 62                           | °C/W |

<sup>1</sup>自然空冷で測定。

### ESD の注意

ESD ( 静電放電 ) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

## ピン配置およびピン機能説明

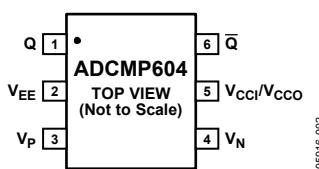

図 3.ADCMP604 のピン配置

表 5.ADCMP604 のピン機能説明(6 ピン SC70)

| ピン番号 | 記号                | 説明                                                                          |

|------|-------------------|-----------------------------------------------------------------------------|

| 1    | Q                 | 非反転出力。非反転入力のアナログ電圧 $V_P$ が反転入力のアナログ電圧 $V_N$ より大きいとき、Q はハイ・レベルになります。         |

| 2    | $V_{EE}$          | 負の電源電圧。                                                                     |

| 3    | $V_P$             | 非反転アナログ入力。                                                                  |

| 4    | $V_N$             | 反転アナログ入力。                                                                   |

| 5    | $V_{CCI}/V_{CCO}$ | 入力セクションの電源/出力セクションの電源。 $V_{CCI}$ と $V_{CCO}$ は共用ピン。                         |

| 6    | $\bar{Q}$         | 反転出力。非反転入力のアナログ電圧 $V_P$ が反転入力のアナログ電圧 $V_N$ より大きいとき、 $\bar{Q}$ はロー・レベルになります。 |

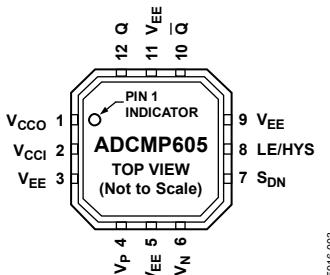

図 4.ADCMP605 のピン配置

表 6.ADCMP605 のピン機能説明(12 ピン LFCSP\_VQ)

| ピン番号           | 記号        | 説明                                                                                                                                                  |

|----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | $V_{CCO}$ | 出力セクションの電源。                                                                                                                                         |

| 2              | $V_{CCI}$ | 入力セクションの電源。                                                                                                                                         |

| 3, 5, 9, 11    | $V_{EE}$  | 負の電源電圧。                                                                                                                                             |

| 4              | $V_P$     | 非反転アナログ入力。                                                                                                                                          |

| 6              | $V_N$     | 反転アナログ入力。                                                                                                                                           |

| 7              | $S_{DN}$  | シャットダウン。このピンをロー・レベルにすると、デバイスがシャットダウンします。                                                                                                            |

| 8              | LE/HYS    | ラッチ/ヒステリシス制御。抵抗によるバイアスまたは電流でヒステリシスを調整します。ラッチのときは、ロー・レベルにします。                                                                                        |

| 10             | $\bar{Q}$ | 反転出力。コンパレータが比較モードで、かつ非反転入力 $V_P$ のアナログ電圧が反転入力 $V_N$ のアナログ電圧より大きい場合、 $\bar{Q}$ はロー・レベルになります。                                                         |

| 12             | Q         | 非反転出力。コンパレータが比較モードで、かつ非反転入力 $V_P$ のアナログ電圧が反転入力 $V_N$ のアナログ電圧より大きい場合、Q はハイ・レベル。                                                                      |

| ヒート・シンク<br>パドル | $V_{EE}$  | パッケージの金属裏面は、 $V_{EE}$ に電気的に接続されています。ピン 3、ピン 5、ピン 9、ピン 11 が十分な電気的接続を提供するため、フローティングにしておくことができます。熱的および/または機械的な安定性が必要な場合には、アプリケーション・ボードにハンダ接続することもできます。 |

## 代表的な性能特性

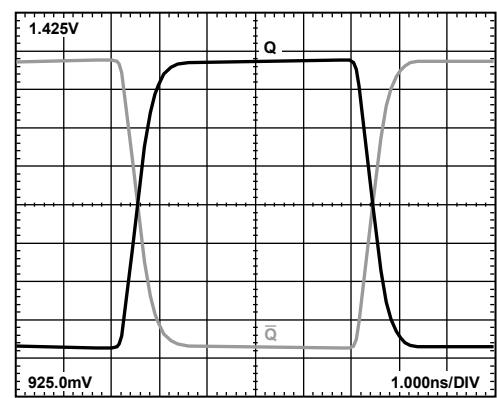

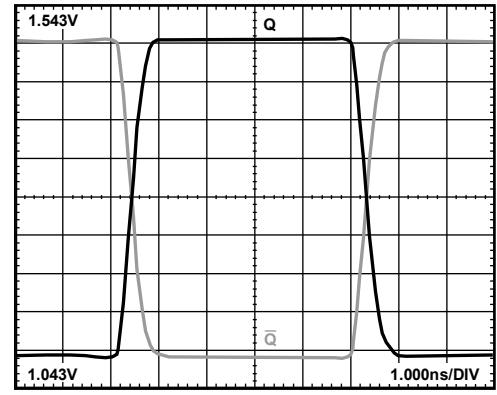

特に指定がない限り、 $V_{CCI} = V_{CCO} = 2.5$  V、 $T_A = 25^\circ\text{C}$ 。

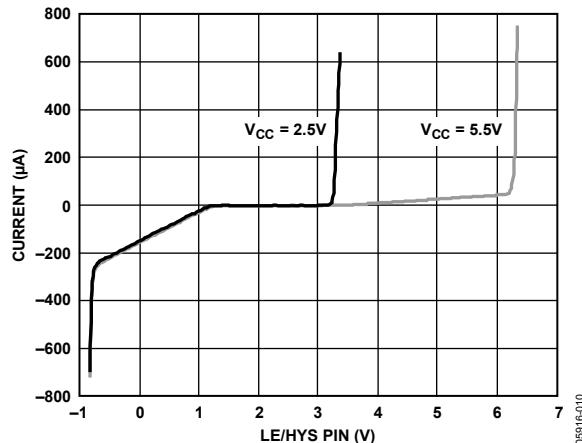

図 5.LE/HYS ピンの電流対電圧

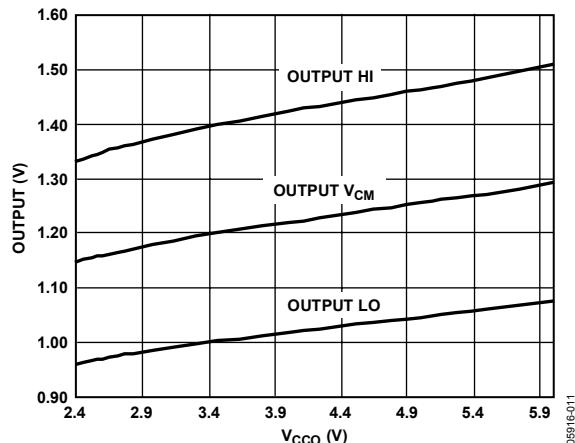

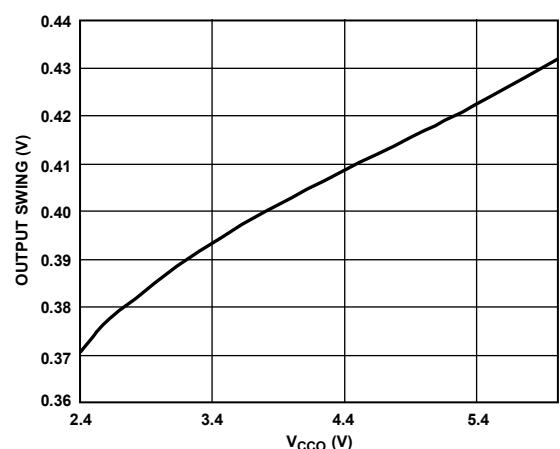

図 8.LVDS 出力レベル対  $V_{CCO}$  (V)

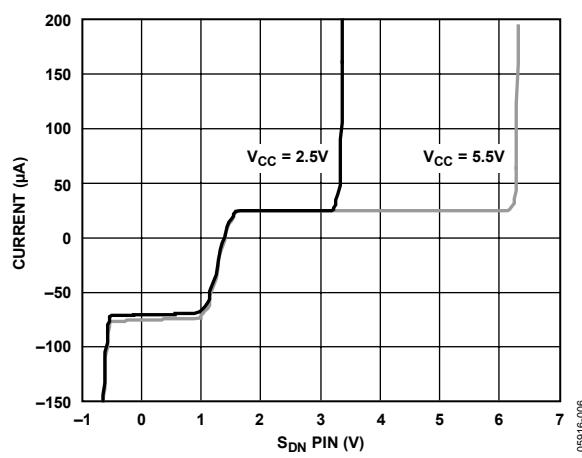

図 6.S\_DN ピンの電流対電圧

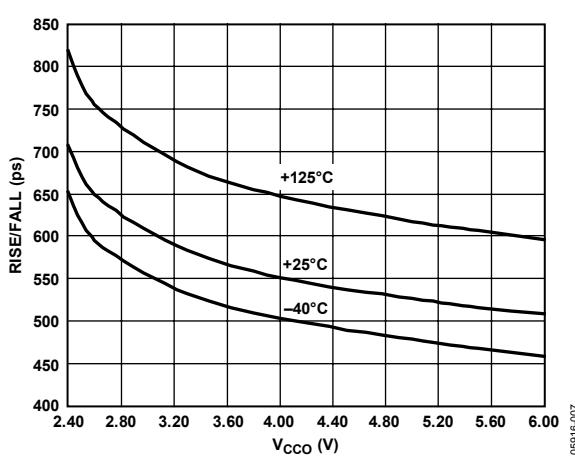

図 9.LVDS 出力立ち上がり/立ち下がり時間対  $V_{CCO}$  (V)

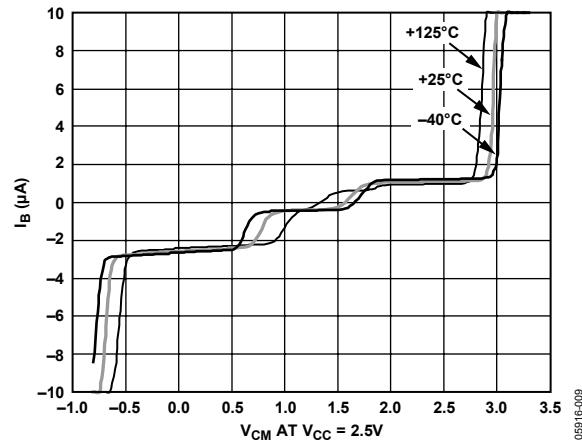

図 7.入力バイアス電流対入力コモン・モード電圧

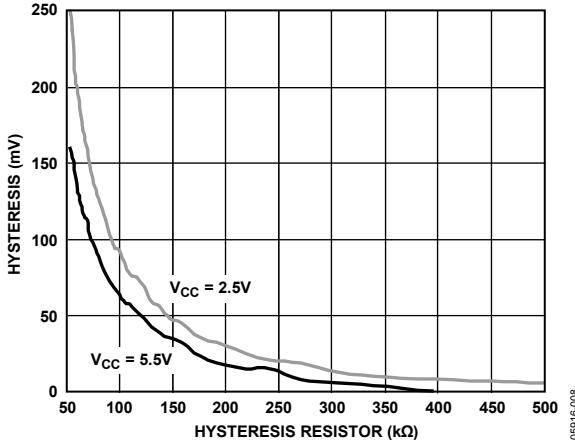

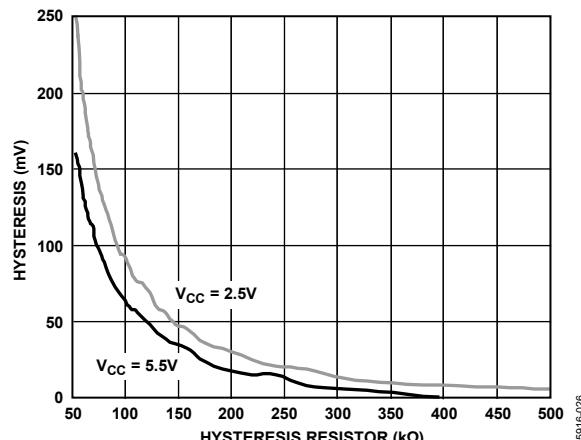

図 10.ヒステリシス対ヒステリシス抵抗

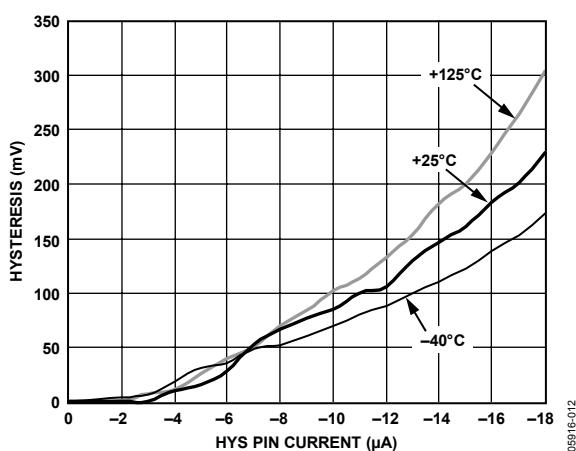

図 11. ヒステリシス対 HYS ピン電流

図 14. LVDS 出力振幅対  $V_{CCO}$  (V)

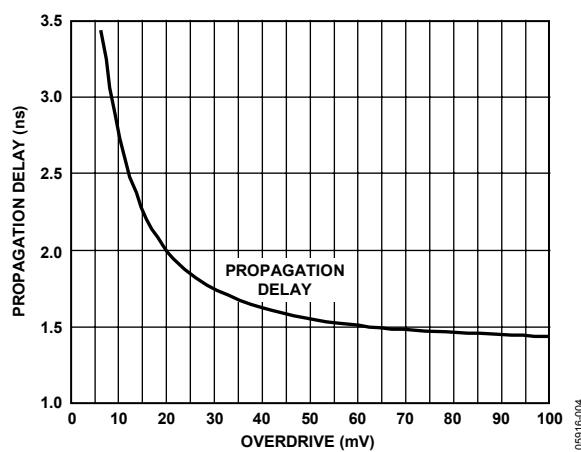

図 12. 伝搬遅延対入力オーバードライブ

図 15. 50 MHz 出力電圧波形、 $V_{CCO} = 2.5$  V

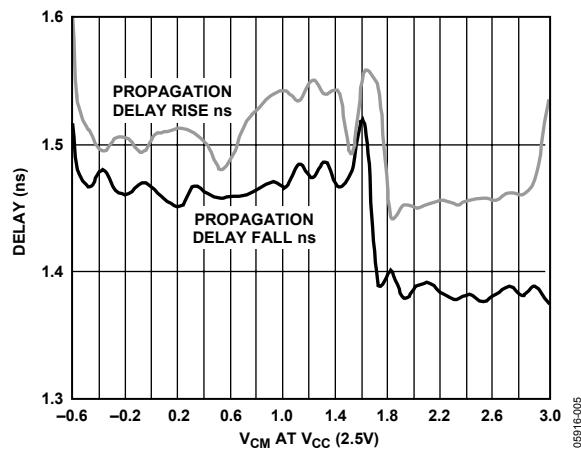

図 13. 伝搬遅延対入力コモン・モード電圧

図 16. 50 MHz 出力電圧波形、 $V_{CCO} = 5.5$  V

## アプリケーション情報

### 電源/グラウンドのレイアウトとバイパス

ADCMP604/ADCMP605 コンパレータは非常に高速なデバイスです。このデバイスでは、出力ステージは低ノイズですが、規定の性能を実現するためには適切な高速デザイン技術を使うことが不可欠です。コンパレータは補償を行っていないアンプであるため、任意の位相の帰還があると、発振または不要なヒステリシスが発生することがあります。非常に重要なことは、低インピーダンスの電源プレーンを使うことです。特に出力電源プレーン( $V_{CCO}$ )とグラウンド・プレーン(GND)が重要です。個々の電源プレーンには、多層ボードの一部を使うことが推奨されます。スイッチング電流に対して低いインダクタンスのリターン・パスを用意すると、対象アプリケーションで可能な最適性能が得られます。

入力電源と出力電源を適切にバイパスすることも重要です。複数の高品質  $0.01 \mu F$  のバイパス・コンデンサを  $V_{CCI}$  と  $V_{CCO}$  の各電源ピンのできるだけ近くに接続して、十分な数のピアを使って GND プレーンへ接続する必要があります。これらの内の少なくとも 1 つは出力電流のリターン・パスを短くするように配置して、電流がグラウンドから  $V_{CCI}$  と  $V_{CCO}$  の各ピンへ戻るようにする必要があります。高周波バイパス・コンデンサは、インダクタンスと ESR が最小であるものを注意深く選択する必要があります。寄生レイアウト・インダクタンスも厳しく制御して、高周波でのバイパス効果を大きくする必要があります。

パッケージで許容できる場合で、かつ入力電源と出力電源が別々に接続されている場合は( $V_{CCI} \neq V_{CCO}$ )、これらの各電源を別々に GND プレーンへ確実にバイパスしてください。これらの電源ピンは相互に接続しないでください。回路ボード・レイアウトが 2 つの電源間の結合を小さくするようにデザインされていて、各電源とグラウンド・プレーンとの間にバイパス容量を追加できるようにしてある場合は、GND プレーンにより、 $V_{CCI}$  プレーンと  $V_{CCO}$  プレーンを分離することが推奨されます。これにより、入力/出力電源を分離したときの性能が向上します。入力電源と出力電源が単電源動作用に接続されている場合は( $V_{CCI} = V_{CCO}$ )、2 つの電源間の結合を避けることはできませんが、ボード上の配置を注意深く行うと、入力から出力リターン電流を遠ざけることに役立ちます。

### LVDS 互換の出力ステージ

規定の伝搬遅延分散性能は、寄生容量負荷を最小規定値以下にしたときにのみ実現されます。ADCMP604 と ADCMP605 の出力は、標準 LVDS 互換入力を直接駆動するようにデザインされています。

### ラッチ機能のイネーブル/ディスエーブル

ラッチ入力は融通性の高いデザインになっています。このピンは、フローティングのままにしておくか、または任意の標準 TTL/CMOS デバイスによりロー・レベルに駆動して高速ラッチとして使用することができます。さらに、このピンは、公称  $1.25 \text{ V}$  のバイアス電圧または約  $70 \text{ k}\Omega$  の入力抵抗を持つヒステリシス制御ピンとして使うこともできます。この機能を使うと、抵抗または安価な CMOS DAC を使って、コンパレータ・ヒステリシスを容易に制御することができます。このピンをハイ・レベルに駆動した場合、またはこのピンをフローティングにした場合、すべてのヒステリシスがディスエーブルされます。

オープン・ドレイン、オープン・コレクタ、またはスリーボード・ステート・ドライバをヒステリシス制御抵抗または電流源に並列接続すると、ヒステリシス制御およびラッチ・モードと一緒に使うことができます。

このプログラマブルなヒステリシス機能のため、ラッチ・ピンのロジック・スレッショールドは、 $V_{CCO}$  に無関係に約  $1.1 \text{ V}$  になります。

### 性能の最適化

すべての高速コンパレータと同様に、規定の性能を実現するためには、適切なデザインとレイアウト技術が不可欠です。浮遊容量、インダクタンス、電源とグラウンドの誘導性インピーダンス、またはその他のレイアウト問題は、規定性能に深刻な影響を与えることがあります。発振が生ずることもあります。入力と出力の伝送線の大きな不連続性は、規定のパルス幅分散性能に制約を与えることがあります。ソース・インピーダンスは可能な限り小さくする必要があります。高いソース・インピーダンスとコンパレータの寄生入力容量との組み合わせにより、入力の帯域幅が低下して、全体の応答性能が低下することがあります。大きな抵抗からの熱ノイズにより、スルーレートが小さい入力信号で容易にジッタが発生し、インピーダンスが高いと、不要な混入が発生し易くなります。

## コンパレータ伝搬遅延の分散

ADCMP604/ADCMP605 コンパレータは、 $5 \text{ mV} \sim V_{\text{CC1}} - 1 \text{ V}$  の広範囲な入力オーバードライブ範囲で伝搬遅延分散を小さくするようにデザインされています。伝搬遅延分散は、オーバードライブまたはスルーレートの大きさの変化(すなわち入力信号がスイッチング・スレッショールドを超える程度と速度)から発生する伝搬遅延の変動です。

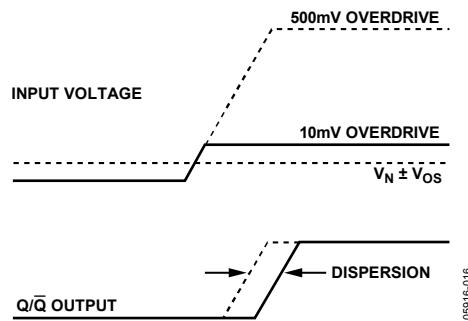

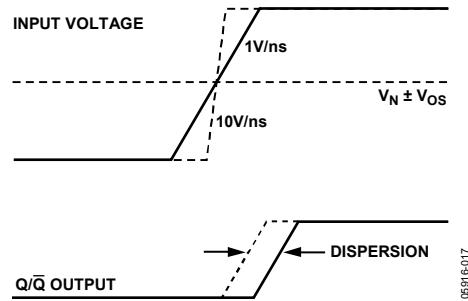

伝搬遅延分散は、データ通信、自動テスト/計測、計測機器などの高速で時間に厳しいアプリケーションで重要な仕様です。また、パルス分光学、原子力計測機器、医用画像などのイベント駆動型アプリケーションでも重要な仕様です。分散は、入力オーバードライブ状態が変化したときの伝搬遅延の変動として定義されます(図 17 および図 18)。

ADCMP604/ADCMP605 の分散は、オーバードライブが  $10 \text{ mV}$  から  $125 \text{ mV}$  へ変化したとき  $1.6 \text{ ns}$  (typ) 以下です。この仕様は正と負の信号に適用されます。これは、立ち上がり入力、立ち下がり入力、非常に小さい出力スキューリーに対して、ADCMP604 と ADCMP605 の遅延を非常に厳密に一致させているためです。

図 17. 伝搬遅延—オーバードライブ分散

図 18. 伝搬遅延—スルーレート分散

## コンパレータのヒステリシス

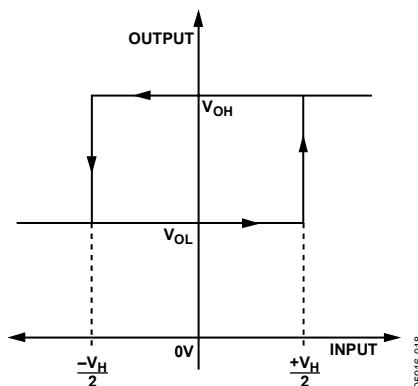

コンパレータにヒステリシスを追加することは、ノイズの多い環境の場合に、または差動入力振幅が比較的小さいか、または低速変化する場合に必要となることがあります。図 19 に、ヒステリシスを持つコンパレータの伝達関数を示します。入力電圧がスレッショールドの下の領域から正の方向へスレッショールド(この例では  $0 \text{ V}$ )に近づき、入力が  $+V_{\text{H}}/2$  を通過するときコンパレータがロー・レベルからハイ・レベルへ変化し、新しいスイッチング・スレッショールドは  $-V_{\text{H}}/2$  になります。入力がスレッショールドの下の領域で負方向へ新しいスレッショールド  $-V_{\text{H}}/2$  を通過するまで、コンパレータはそのハイ・レベル状態を維持します。この方法では、 $0 \text{ V}$  入力を中心とするノイズまたは帰還出力信号は  $\pm V_{\text{H}}/2$  で挟まれた領域を超えない限り、コンパレータの状態を変えることはありません。

図 19. コンパレータ・ヒステリシスの伝達関数

ヒステリシスをコンパレータへ導入する通常の技術では、出力から入力へ正の帰還を行います。この方法での1つの制約は、出力ロジック・レベルに応じてヒステリシス量が変化して、ヒステリシスがスレッショールドを中心として対称にならないことです。外付け帰還回路も大きな寄生を導入して、高速性能を低下させ、発振を生ずることもあります。

この ADCMP605 コンパレータは、精度と安定性を大幅に向上させるプログラマブルなヒステリシス機能を提供します。LE/HYS ピンと GND ピンに外付けプルダウン抵抗または電流源を接続すると、予測可能かつ安定した方法でヒステリシス量を変えることができます。LE/HYS ピンを解放またはハイ・レベルにすると、ヒステリシスがなくなります。このピンを使って可能な最大ヒステリシスは約  $160 \text{ mV}$  です。図 20 に外付け抵抗値の関数としてのヒステリシスを、図 11 に電流の関数としてのヒステリシスを、それぞれ示します。

ヒステリシス・コントロール・ピンには、全ヒステリシス制御範囲で  $70\text{ k}\Omega \pm 20\%$  の直列抵抗を介して 1.25 V のバイアス電圧が加わります。この方法でヒステリシスを加える利点は、精度と安定性を向上させ、部品数を削減し、融通性を大きくすることです。HYS ピンに外付けのバイパス・コンデンサを使用することは推奨しません。これは、デバイスのジッタ性能を低下させて、ラッチ機能を損なうことがあるためです。ラッチ機能のイネーブル/ディスエーブルのセクションに説明したように、ヒステリシス制御とラッチ機能は両立します。

図 20. ヒステリシス対  $R_{\text{HYS}}$  制御抵抗

## クロスオーバーのバイアス・ポイント

オペアンプとコンパレータでは、このタイプのレール to レール入力は 2 つのフロントエンドを持っています。あるデバイスは  $V_{\text{CC1}}$  レールの近くで動作し、他のデバイスは  $V_{\text{EE}}$  レール近くで動作します。コモン・モード・レンジ内のある既定のポイントでクロスオーバーが発生します。このポイントは通常  $V_{\text{CC1}}/2$  であり、バイアス電流の方向が反転するためオフセット電圧と電流の測定値が変化します。

## 最小入力スルーレート条件

定格の負荷容量と通常の優れた PCB デザインでは、性能の最適化のセクションで説明したように、これらのコンパレータは任意の入力スルーレートで安定し、ヒステリシスがありません。入力ステージからの広帯域ノイズは、他の多くの高速コンパレータで発生する大きなチャタリングがあるときに観測されます。容量負荷が接続されたとき、またはバイパスが不十分なときに、発振が観測されます。この発振は、コンパレータの広いゲイン帯域幅とパッケージおよび PCB の帰還寄生との組み合わせに起因します。多くのアプリケーションでは、チャタリングは害になりません。

## 代表的なアプリケーション回路

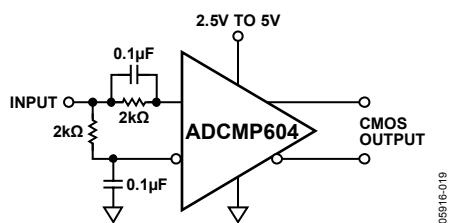

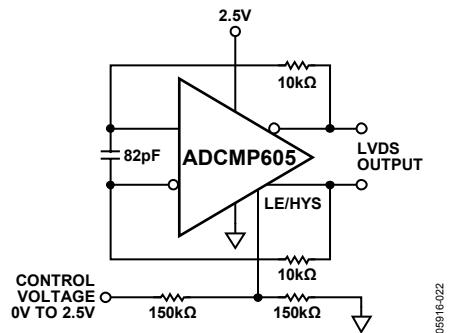

図 21.セルフバイアス、50%スライサ

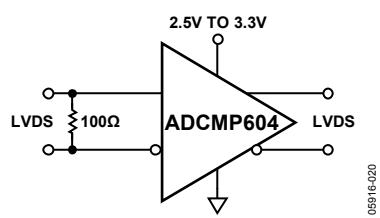

図 22.LVDS レピータ

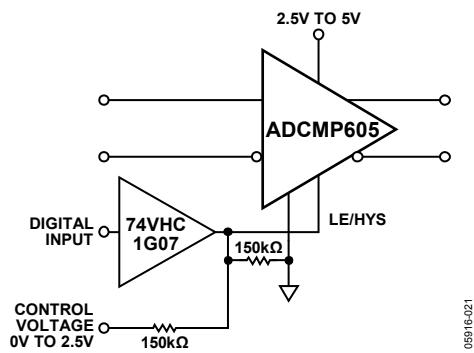

図 25.発振器とパルス幅変調器

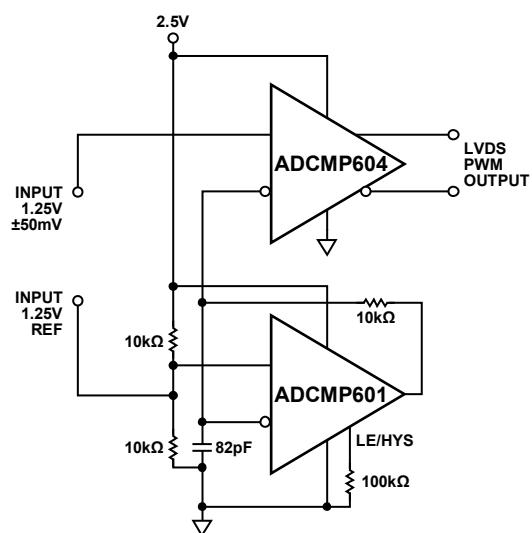

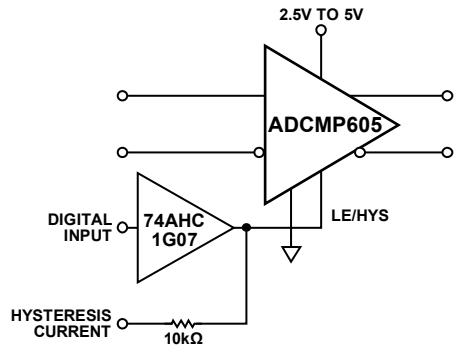

図 23.ラッチによるヒステリシス調整

図 26.ラッチによるヒステリシス調整

図 24.電圧制御発振器

## 外形寸法

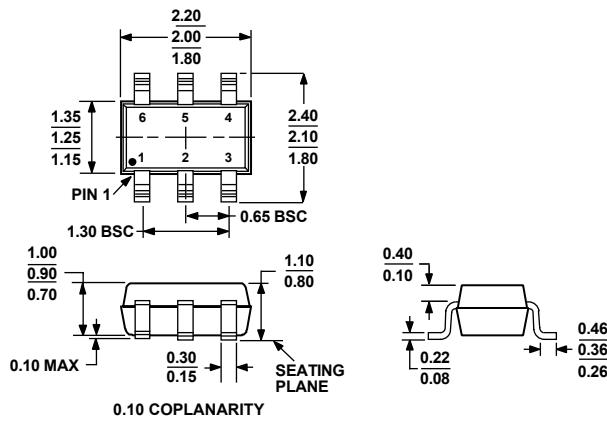

図 27.6 ピン薄型シュリンク・スモール・アウトライン・トランジスタ・パッケージ(SC70)

(KS-6)

寸法: mm

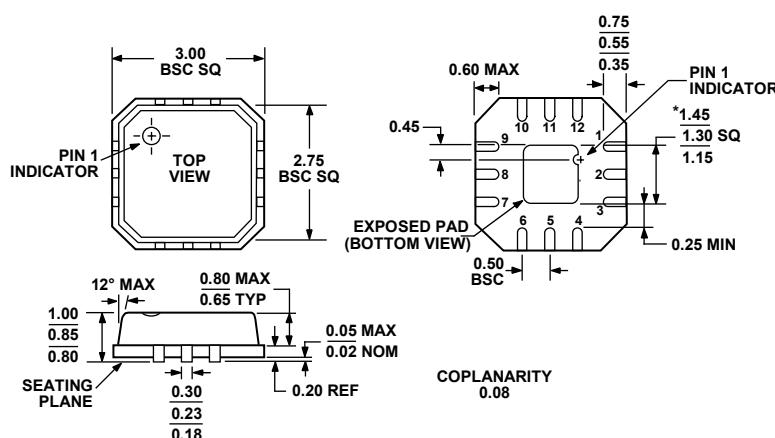

図 28.12 ピン・リードフレーム・チップ・スケール・パッケージ(LFCSP\_VQ)

3 mm × 3 mm ボディ、極薄クワッド

(CP-12-1)

寸法: mm

## オーダー・ガイド

| Model                           | Temperature Range | Package Description                                        | Package Option | Branding |

|---------------------------------|-------------------|------------------------------------------------------------|----------------|----------|

| ADCMP604BKSZ-R2 <sup>1</sup>    | -40°C to +125°C   | 6-Lead Thin Shrink Small Outline Transistor Package (SC70) | KS-6           | G0Q      |

| ADCMP604BKSZ-REEL7 <sup>1</sup> | -40°C to +125°C   | 6-Lead Thin Shrink Small Outline Transistor Package (SC70) | KS-6           | G0Q      |

| ADCMP604BKSZ-RL <sup>1</sup>    | -40°C to +125°C   | 6-Lead Thin Shrink Small Outline Transistor Package (SC70) | KS-6           | G0Q      |

| ADCMP605BCPZ-WP <sup>1</sup>    | -40°C to +125°C   | 12-Lead Lead Frame Chip Scale Package (LFCSP_VQ)           | CP-12-1        | G0K      |

| ADCMP605BCPZ-R2 <sup>1</sup>    | -40°C to +125°C   | 12-Lead Lead Frame Chip Scale Package (LFCSP_VQ)           | CP-12-1        | G0K      |

| ADCMP605BCPZ-R7 <sup>1</sup>    | -40°C to +125°C   | 12-Lead Lead Frame Chip Scale Package (LFCSP_VQ)           | CP-12-1        | G0K      |

| EVAL-ADCMP605BCPZ <sup>1</sup>  |                   | Evaluation Board                                           |                |          |

<sup>1</sup> Z = RoHS 準拠製品。