# OVP/EMI 保護、高精度、低ノイズ、 低バイアス電流のオペ・アンプ

## データシート

## ADA4177-1/ADA4177-2/ADA4177-4

### 特長

低オフセット電圧:  $60 \mu\text{V}$  (max) @  $25^\circ\text{C}$  (8 ピンおよび

14 ピン SOIC)

オフセット電圧の低ドリフト:  $1 \mu\text{V}/^\circ\text{C}$  (max) (8 ピンおよび

14 ピン SOIC)

低入力バイアス電流:  $1 \text{nA}$  (max) @  $25^\circ\text{C}$

低い電圧ノイズ密度:  $8 \text{nV}/\sqrt{\text{Hz}}$  (typ) @  $1 \text{kHz}$

大きい信号電圧ゲイン ( $A_{v0}$ ): 全電源電圧範囲および全動作温度

範囲にわたり  $100 \text{dB}$  (min)

電源電圧レールを  $32 \text{V}$  上回るまたは下回る電圧に対する入力過

電圧保護

EMI フィルタ内蔵

除去比:  $70 \text{dB}$  (typ) @  $1000 \text{MHz}$

除去比:  $90 \text{dB}$  (typ) @  $2400 \text{MHz}$

レール to レール出力振幅

超低電源電流: アンプあたり  $500 \mu\text{A}$  (typ)

広帯域幅:

ゲイン帯域幅積 ( $A_v = +100$ ):  $3.5 \text{MHz}$  (typ)

ユニティゲイン・クロスオーバー ( $A_v = +1$ ):  $3.5 \text{MHz}$  (typ)

-3 dB 帯域幅 ( $A_v = +1$ ):  $6 \text{MHz}$  (typ)

デュアル電源動作

$\pm 5 \text{V} \sim \pm 15 \text{V}$  で仕様規定、 $\pm 2.5 \text{V} \sim \pm 18 \text{V}$  で動作

ユニティゲイン安定

位相反転なし

### アプリケーション

無線基地局の制御回路

光ネットワーク制御回路

計測器

センサーと制御

熱電対、抵抗温度検出器 (RTD)、ストレイン・ゲージ、シャ

ント電流計測

高精度フィルタ

### 概要

ADA4177-1 (シングル・チャンネル)、ADA4177-2 (デュアル・

チャンネル)、ADA4177-4 (クワッド・チャンネル) の各アンプ

には、低オフセット電圧 ( $2 \mu\text{V}$  typ)、低温度ドリフト ( $1 \mu\text{V}/^\circ\text{C}$  max)、

低入力バイアス電流、低ノイズ、低消費電流 ( $500 \mu\text{A}$  typ) という特長があります。出力は  $1000 \text{pF}$  を超える容量性負荷

に対して、外部補償なしで安定的に動作します。

ADA4177-1/ADA4177-2/ADA4177-4 の入力は、いずれかの電源

電圧を  $32 \text{V}$  上回る信号に対する入力保護機能と、 $1000 \text{MHz}$  での

70 dB の電磁干渉 (EMI) 除去比により、高精度オペ・アンプの

信頼性に関する新たな基準を打ち立てます。

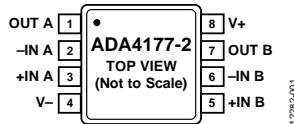

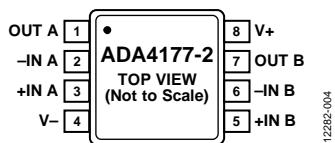

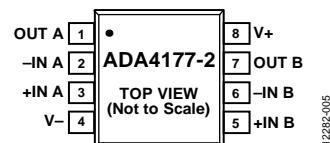

### ピン接続図

図 1. ADA4177-2

このオペ・アンプのアプリケーションとして、センサーのシグナル・コンディショニング (熱電対、RTD、ストレイン・ゲージ)、

プロセス制御のフロントエンド・アンプ、光／無線伝送システム

の高精度ダイオード・パワー測定を挙げることができます。

ADA4177-2 と ADA4177-4 は工業用温度範囲  $-40 \sim +125^\circ\text{C}$  で動作

します。ADA4177-1 と ADA4177-2 は 8 ピン SOIC パッケージ

と 8 ピン MSOP パッケージを採用しています。ADA4177-4 は 14

ピ�の TSSOP パッケージまたは 14 ピンの SOIC パッケージを採

用しています。

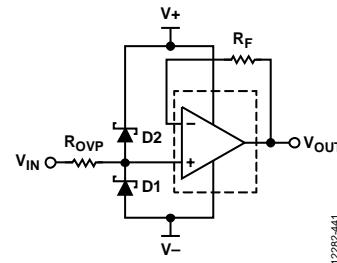

図 2. 過電圧の電流制限、電圧フォロアの構成

表 1. 各世代の保護機能付き入力オペ・アンプの進化<sup>1</sup>

| Gen. 1,<br>OVP<br>(10 V) | Gen. 2,<br>OVP (25 V) | Gen. 3,<br>OVP (32 V) | Gen. 4<br>EMI Filters                      | Gen. 5,<br>OVP (32 V)<br>+ EMI |

|--------------------------|-----------------------|-----------------------|--------------------------------------------|--------------------------------|

| OP191                    | ADA4091-2             | ADA4096-2             | AD8657                                     | ADA4177-1                      |

| OP291                    | ADA4091-4             | ADA4096-4             | AD8659                                     | ADA4177-2                      |

| OP491                    | ADA4092-4             |                       | AD8546<br>AD8548<br>ADA4661-2<br>ADA4666-2 | ADA4177-4                      |

<sup>1</sup> Gen. は世代 (Generation) の略。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                          |    |

|--------------------------|----|

| 特長                       | 1  |

| アプリケーション                 | 1  |

| 概要                       | 1  |

| ピン接続図                    | 1  |

| 改訂履歴                     | 2  |

| 仕様                       | 3  |

| 電気的特性、 $\pm 5\text{ V}$  | 3  |

| 電気的特性、 $\pm 15\text{ V}$ | 5  |

| 絶対最大定格                   | 7  |

| 最大消費電力                   | 7  |

| 熱抵抗                      | 7  |

| ESD に関する注意               | 7  |

| ピン配置およびピン機能の説明           | 8  |

| 代表的な性能特性                 | 11 |

## 改訂履歴

## 4/15 - Rev. B から Rev. C

|                                                        |    |

|--------------------------------------------------------|----|

| ADA4177-1 を追加                                          | 全体 |

| 図 2 を削除。ナンバリング変更                                       | 1  |

| 表 1 を変更                                                | 1  |

| 図 5、図 6、表 7 を追加、ナンバリング変更                               | 9  |

| 図 16、図 17、図 19、図 20 を変更                                | 12 |

| 図 26 を変更                                               | 14 |

| 図 34、図 35、図 37、図 39 を変更                                | 16 |

| 図 46、図 47、図 49、図 50 を変更                                | 17 |

| 図 59、図 62 を変更                                          | 19 |

| 図 63、図 65、図 66、図 68 を変更                                | 20 |

| 図 69、図 72 を変更                                          | 21 |

| 図 75、図 78 を変更                                          | 22 |

| 図 77、図 80 を追加                                          | 22 |

| 図 81～図 83 を追加                                          | 23 |

| 「動作原理」セクションを変更                                         | 24 |

| 「入力保護回路」セクション、「正側電源ピンの過電圧電流を制限する」セクションを変更              | 26 |

| 「ADA4177-1/ADA4177-2/ADA4177-4 をコンパレータとして使用する」セクションを変更 | 27 |

| オーダー・ガイドを変更                                            | 31 |

## 1/15 - Rev. A から Rev. B

|                  |    |

|------------------|----|

| ADA4177-4 を追加    | 全体 |

| レイアウトを変更         | 全体 |

| 図 2 を追加。ナンバリング変更 | 1  |

|                                              |    |

|----------------------------------------------|----|

| 動作原理                                         | 24 |

| アプリケーション情報                                   | 25 |

| アクティブ過電圧保護                                   | 25 |

| 正側電源ピンの過電圧電流の出力を制限する                         | 26 |

| EMI 保護                                       | 27 |

| 自己加熱                                         | 27 |

| ADA4177-1/ADA4177-2/ADA4177-4 をコンパレータとして使用する | 27 |

| 出力の位相反転                                      | 28 |

| 適切なプリント回路基板 (PCB) レイアウト                      | 28 |

| 外形寸法                                         | 29 |

| オーダー・ガイド                                     | 31 |

|                          |    |

|--------------------------|----|

| 「特長」セクション、「概要」セクションを変更   | 1  |

| 表 2 を変更                  | 3  |

| 表 3 を変更                  | 5  |

| 表 5 を変更                  | 7  |

| 図 6、図 7、表 7 を追加。ナンバリング変更 | 9  |

| 図 10、図 13 を追加            | 10 |

| 図 15、図 18 を置換            | 11 |

| 図 14、図 16、図 17、図 19 を追加  | 11 |

| 図 20、図 21、図 23、図 24 を変更  | 12 |

| 図 32、図 33 を変更            | 14 |

| 図 38、図 41 を変更            | 15 |

| 図 58、図 61 を変更            | 18 |

| 図 62、図 65、図 66 を変更       | 19 |

| 図 69、図 72 を変更            | 20 |

| 図 87 のキャプションを変更          | 25 |

| 外形寸法を更新                  | 27 |

| 図 93、図 94 を追加            | 28 |

| オーダー・ガイドを変更              | 29 |

## 10/14—Rev. 0 から Rev. A

|                                                                     |   |

|---------------------------------------------------------------------|---|

| 表 3 の Large Signal Voltage Gain パラメータ、Test Conditions/Comments 列を変更 | 5 |

|---------------------------------------------------------------------|---|

## 10/14—Revision 0: 初版

## 仕様

## 電気的特性、±5 V

特に指定のない限り、 $V_{SY} = \pm 5.0$  V、 $V_{CM} = 0$  V、 $T_A = 25$  °C。

表 2.

| Parameter                                                                             | Symbol                   | Test Conditions/Comments                                                                                                                                                                                                                                      | Min  | Typ   | Max   | Unit  |    |

|---------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|-------|----|

| INPUT CHARACTERISTICS                                                                 |                          |                                                                                                                                                                                                                                                               |      |       |       |       |    |

| Offset Voltage<br>8-Lead SOIC and 14-Lead SOIC                                        | $V_{OS}$                 | $-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$                                                                                                                                                                                                            | 2    | 60    | 120   | μV    |    |

| 8-Lead MSOP                                                                           |                          |                                                                                                                                                                                                                                                               | 3    | 120   | 200   | μV    |    |

| 14-Lead TSSOP                                                                         |                          |                                                                                                                                                                                                                                                               | 3    | 150   | 300   | μV    |    |

| Offset Voltage Matching<br>8-Lead SOIC<br>8-Lead MSOP                                 |                          |                                                                                                                                                                                                                                                               |      | 40    | 110   | μV    |    |

| Offset Voltage Drift<br>8-Lead SOIC and 14-Lead SOIC<br>8-Lead MSOP and 14-Lead TSSOP | $\Delta V_{OS}/\Delta T$ | $-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$                                                                                                                                                                                                            |      | 1     | 1.6   | μV/°C |    |

| Input Bias Current                                                                    | $I_B$                    | $-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$                                                                                                                                                                                                            | -1   | -0.4  | +1    | nA    |    |

| Input Offset Current                                                                  | $I_{OS}$                 | $-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$                                                                                                                                                                                                            | -2   | -0.75 | 0.1   | +2    | nA |

| Input Voltage Range                                                                   | $IVR$                    | $-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$                                                                                                                                                                                                            | -1.5 | -1.5  | +0.75 | nA    |    |

| Overshoot Current Limit <sup>1</sup>                                                  | $I_{OVF}$                | $5 \text{ V} < V_{CM} < 37 \text{ V}$<br>$-37 \text{ V} < V_{CM} < -5 \text{ V}$                                                                                                                                                                              | 12   | 10    | 12    | mA    |    |

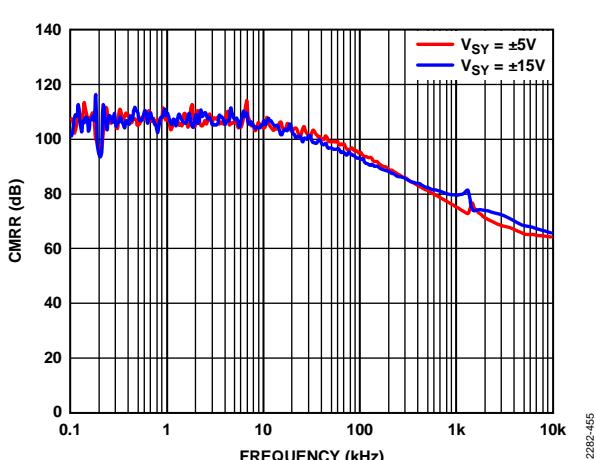

| Common-Mode Rejection Ratio                                                           | $CMRR$                   | $V_{CM} = -3.5 \text{ V to } +3.5 \text{ V}$<br>$-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$                                                                                                                                                            | 122  | 130   | 120   | dB    |    |

| Large Signal Voltage Gain                                                             | $A_{VO}$                 | $R_L = 2 \text{ k}\Omega, V_{OUT} = -4.5 \text{ V to } +4.5 \text{ V}$<br>$-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$<br>$R_L = 10 \text{ k}\Omega, V_{OUT} = -4.5 \text{ V to } +4.5 \text{ V}$<br>$-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$ | 108  | 110   | 115   | dB    |    |

| Input Capacitance                                                                     | $C_{INDM}$               | Differential mode                                                                                                                                                                                                                                             |      | 1     | 1     | pF    |    |

|                                                                                       | $C_{INCM}$               | Common mode                                                                                                                                                                                                                                                   |      | 1     | 1     | pF    |    |

| Input Resistance                                                                      | $R_{DIFF}$               | Differential mode                                                                                                                                                                                                                                             |      | 4     | 4     | MΩ    |    |

|                                                                                       | $R_{CM}$                 | Common mode                                                                                                                                                                                                                                                   |      | 100   | 100   | GΩ    |    |

| OUTPUT CHARACTERISTICS                                                                |                          |                                                                                                                                                                                                                                                               |      |       |       |       |    |

| Output Voltage<br>High                                                                | $V_{OH}$                 | $I_{LOAD} = 1 \text{ mA}$<br>$-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$                                                                                                                                                                               | 4.95 | 4.90  | 4.80  | V     |    |

|                                                                                       |                          | $I_{LOAD} = 7 \text{ mA}$<br>$-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$                                                                                                                                                                               | 4.75 | 4.75  | 4.75  | V     |    |

| Low                                                                                   | $V_{OL}$                 | $I_{LOAD} = 1 \text{ mA}$<br>$-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$                                                                                                                                                                               |      |       | -4.95 | V     |    |

|                                                                                       |                          | $I_{LOAD} = 7 \text{ mA}$<br>$-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$                                                                                                                                                                               |      |       | -4.90 | V     |    |

| Output Current                                                                        | $I_{OUT}$                | $V_{DROPOUT} < 1 \text{ V}$                                                                                                                                                                                                                                   | 25   | 25    | 25    | mA    |    |

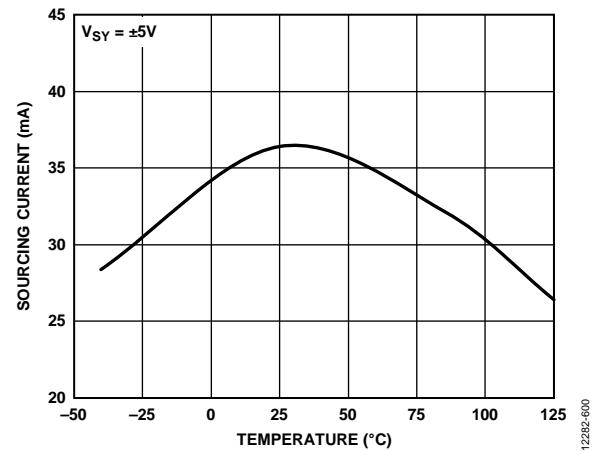

| Short-Circuit Current<br>Sourcing                                                     | $I_{SC}$                 | $T_A = 25^{\circ}\text{C}$                                                                                                                                                                                                                                    |      | 36    | 48    | mA    |    |

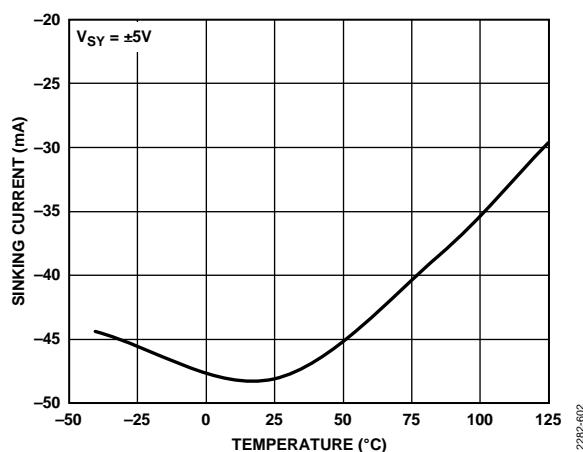

| Sinking                                                                               |                          |                                                                                                                                                                                                                                                               |      | 48    | 48    | mA    |    |

| Closed-Loop Output Impedance                                                          | $Z_{OUT}$                | $f = 1 \text{ kHz}, A_V = +1$                                                                                                                                                                                                                                 |      | 0.11  | 0.11  | Ω     |    |

| Parameter                             | Symbol              | Test Conditions/Comments                                                                                                         | Min        | Typ        | Max | Unit                                                         |

|---------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------|------------|------------|-----|--------------------------------------------------------------|

| POWER SUPPLY                          |                     |                                                                                                                                  |            |            |     |                                                              |

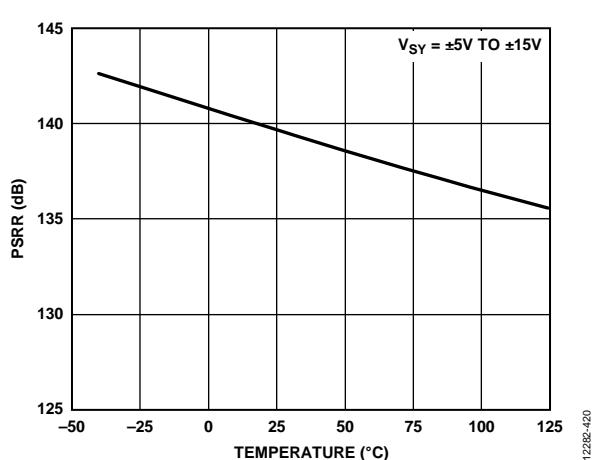

| Power Supply Rejection Ratio          | PSRR                | $V_S = \pm 2.5 \text{ V to } \pm 18 \text{ V}$<br>$-40^\circ\text{C} < T_A < +125^\circ\text{C}$                                 | 125<br>120 | 145        |     | dB                                                           |

| Supply Current per Amplifier          | $I_{SY}$            | $V_{OUT} = 0 \text{ V}$<br>$-40^\circ\text{C} < T_A < +125^\circ\text{C}$                                                        |            | 500<br>600 | 560 | $\mu\text{A}$<br>$\mu\text{A}$                               |

| DYNAMIC PERFORMANCE                   |                     |                                                                                                                                  |            |            |     |                                                              |

| Slew Rate                             | SR                  | $R_L = 2 \text{ k}\Omega$                                                                                                        |            | 1.5        |     | $\text{V}/\mu\text{s}$                                       |

| Settling Time                         | $t_s$               | $V_{IN} = 1 \text{ V step}, R_L = 2 \text{ k}\Omega, A_v = -1$<br>$V_{IN} = 1 \text{ V step}, R_L = 2 \text{ k}\Omega, A_v = +1$ |            | 1.8<br>3.5 |     | $\mu\text{s}$<br>$\mu\text{s}$                               |

| To 0.1%                               |                     |                                                                                                                                  |            |            |     |                                                              |

| To 0.01%                              |                     |                                                                                                                                  |            |            |     |                                                              |

| Gain Bandwidth Product                | GBP                 | $V_{IN} = 10 \text{ mV p-p}, R_L = 2 \text{ k}\Omega, A_v = +100$                                                                |            | 3.5        |     | MHz                                                          |

| Unity-Gain Crossover                  | UGC                 | $V_{IN} = 10 \text{ mV p-p}, R_L = 2 \text{ k}\Omega, A_v = +1$                                                                  |            | 3.5        |     | MHz                                                          |

| $-3 \text{ dB}$ Closed-Loop Bandwidth | $f_{-3 \text{ dB}}$ | $V_{IN} = 10 \text{ mV p-p}, R_L = 2 \text{ k}\Omega, A_v = +1$                                                                  |            | 6          |     | MHz                                                          |

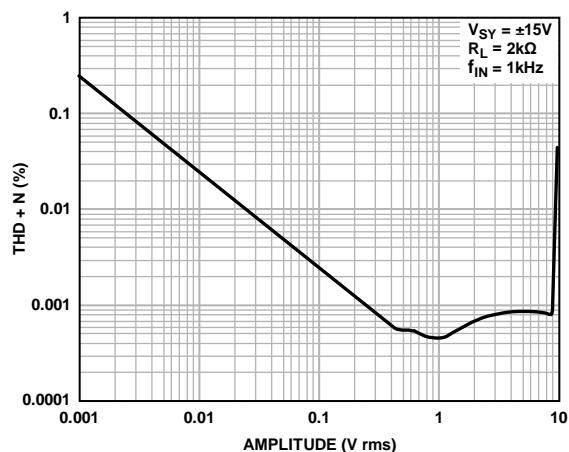

| Total Harmonic Distortion Plus Noise  | THD + N             | $V_{IN} = 1 \text{ V rms}, R_L = 2 \text{ k}\Omega, A_v = +1, f = 1 \text{ kHz}$                                                 |            | 0.003      |     | %                                                            |

| EMI Rejection of $+IN_x$              | EMIRR               | $V_{IN} = 200 \text{ mV p-p}$                                                                                                    |            | 70<br>90   |     | $\text{dB}$<br>$\text{dB}$                                   |

| $f = 1000 \text{ MHz}$                |                     |                                                                                                                                  |            |            |     |                                                              |

| $f = 2400 \text{ MHz}$                |                     |                                                                                                                                  |            |            |     |                                                              |

| NOISE PERFORMANCE                     |                     |                                                                                                                                  |            |            |     |                                                              |

| Voltage Noise                         | $e_{n \text{ p-p}}$ | 0.1 Hz to 10 Hz                                                                                                                  |            | 175        |     | $\text{nV p-p}$                                              |

| Voltage Noise Density                 | $e_n$               | $f = 10 \text{ Hz}$<br>$f = 1 \text{ kHz}$                                                                                       |            | 10<br>8    |     | $\text{nV}/\sqrt{\text{Hz}}$<br>$\text{nV}/\sqrt{\text{Hz}}$ |

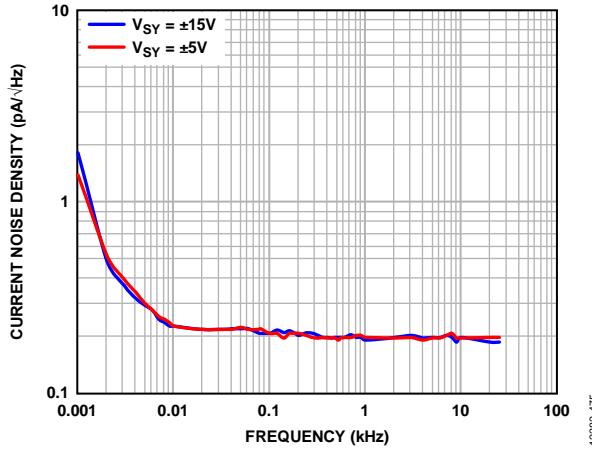

| Current Noise Density                 | $i_n$               | $f = 1 \text{ kHz}$                                                                                                              |            | 0.2        |     | $\text{pA}/\sqrt{\text{Hz}}$                                 |

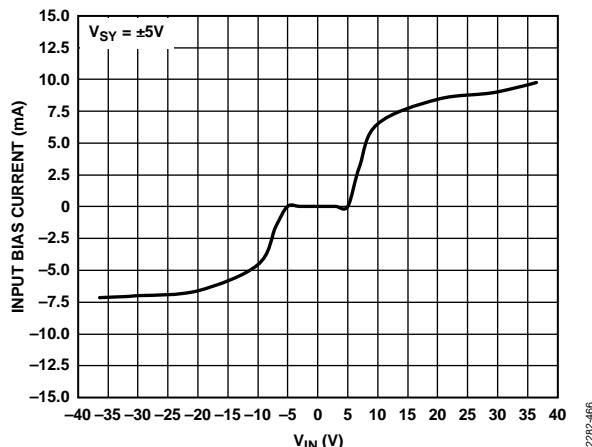

<sup>1</sup> すべての入力に 500 ms にわたって電源電圧を 32 V 上回る電圧を印加。過電圧保護された入力範囲にわたる入力バイアス電流と入力電圧の関係については、図 71 を参照してください。

## 電気的特性、±15 V

特に指定のない限り、 $V_{SY} = \pm 15$  V、 $V_{CM} = 0$  V、 $T_A = 25^\circ C$ 。

表 3.

| Parameter                                                                             | Symbol                   | Test Conditions/Comments                                                                                                                                                                  | Min   | Typ    | Max   | Unit            |

|---------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------|-----------------|

| INPUT CHARACTERISTICS                                                                 |                          |                                                                                                                                                                                           |       |        |       |                 |

| Offset Voltage<br>8-Lead SOIC and 14-Lead SOIC                                        | $V_{OS}$                 | $-40^\circ C < T_A < +125^\circ C$                                                                                                                                                        | 2     | 60     | 120   | $\mu V$         |

| 8-Lead MSOP                                                                           |                          | $-40^\circ C < T_A < +125^\circ C$                                                                                                                                                        | 3     | 120    | 200   | $\mu V$         |

| 14-Lead TSSOP                                                                         |                          | $-40^\circ C < T_A < +125^\circ C$                                                                                                                                                        | 3     | 150    | 300   | $\mu V$         |

| Offset Voltage Matching<br>8-Lead SOIC<br>8-Lead MSOP                                 | $\Delta V_{OS}/\Delta T$ | $-40^\circ C < T_A < +125^\circ C$                                                                                                                                                        |       | 40     | 110   | $\mu V^\circ C$ |

| Offset Voltage Drift<br>8-Lead SOIC and 14-Lead SOIC<br>8-Lead MSOP and 14-Lead TSSOP |                          |                                                                                                                                                                                           |       | 1      | 1.6   | $\mu V^\circ C$ |

| Input Bias Current                                                                    | $I_B$                    | $-40^\circ C < T_A < +125^\circ C$                                                                                                                                                        | -1    | -0.3   | +1    | nA              |

| Input Offset Current                                                                  | $I_{OS}$                 | $-40^\circ C < T_A < +125^\circ C$                                                                                                                                                        | -2    | +2     |       | nA              |

| Input Voltage Range                                                                   | $IVR$                    | $-40^\circ C < T_A < +125^\circ C$                                                                                                                                                        | -0.75 | 0.1    | +0.75 | nA              |

| Overvoltage Current Limit <sup>1</sup>                                                | $I_{OVP}$                | $15 V < V_{CM} < 47 V$<br>$-47 V < V_{CM} < -15 V$                                                                                                                                        | 12    | 10     |       | mA              |

| Common-Mode Rejection Ratio                                                           | $CMRR$                   | $V_{CM} = -13.5 V$ to $+13.5 V$<br>$-40^\circ C < T_A < +125^\circ C$                                                                                                                     | 128   | 130    |       | dB              |

| Large Signal Voltage Gain                                                             | $A_{VO}$                 | $R_L = 2 k\Omega$ , $V_{OUT} = -14.2 V$ to $+14.2 V$<br>$-40^\circ C < T_A < +125^\circ C$<br>$R_L = 10 k\Omega$ , $V_{OUT} = -14.5 V$ to $+14.5 V$<br>$-40^\circ C < T_A < +125^\circ C$ | 110   | 114    |       | dB              |

| Input Capacitance                                                                     | $C_{INDM}$               | Differential mode                                                                                                                                                                         |       | 1      |       | pF              |

|                                                                                       | $C_{INCM}$               | Common mode                                                                                                                                                                               |       | 1      |       | pF              |

| Input Resistance                                                                      | $R_{DIFF}$               | Differential mode                                                                                                                                                                         |       | 4      |       | MΩ              |

|                                                                                       | $R_{CM}$                 | Common mode                                                                                                                                                                               |       | 130    |       | GΩ              |

| OUTPUT CHARACTERISTICS                                                                |                          |                                                                                                                                                                                           |       |        |       |                 |

| Output Voltage<br>High                                                                | $V_{OH}$                 | $I_{LOAD} = 1 mA$<br>$-40^\circ C < T_A < +125^\circ C$                                                                                                                                   | 14.95 |        |       | V               |

|                                                                                       |                          | $I_{LOAD} = 7 mA$<br>$-40^\circ C < T_A < +125^\circ C$                                                                                                                                   | 14.90 |        |       | V               |

|                                                                                       |                          |                                                                                                                                                                                           | 14.80 |        |       | V               |

|                                                                                       |                          |                                                                                                                                                                                           | 14.75 |        |       | V               |

| Low                                                                                   | $V_{OL}$                 | $I_{LOAD} = 1 mA$<br>$-40^\circ C < T_A < +125^\circ C$                                                                                                                                   |       | -14.95 |       | V               |

|                                                                                       |                          | $I_{LOAD} = 7 mA$<br>$-40^\circ C < T_A < +125^\circ C$                                                                                                                                   |       | -14.90 |       | V               |

|                                                                                       |                          |                                                                                                                                                                                           |       | -14.80 |       | V               |

|                                                                                       |                          |                                                                                                                                                                                           |       | -14.75 |       | V               |

| Output Current                                                                        | $I_{OUT}$                | $V_{DROPOUT} < 1 V$                                                                                                                                                                       |       | 25     |       | mA              |

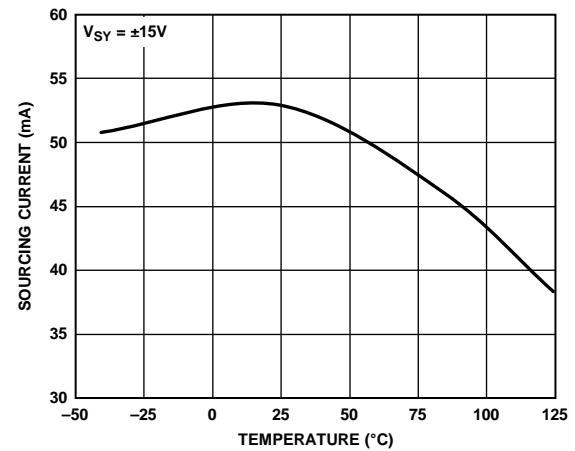

| Short-Circuit Current<br>Sourcing                                                     | $I_{SC}$                 | $T_A = 25^\circ C$                                                                                                                                                                        |       | 53     |       | mA              |

| Sinking                                                                               |                          |                                                                                                                                                                                           |       | 65     |       | mA              |

| Closed-Loop Output Impedance                                                          | $Z_{OUT}$                | $f = 1 kHz$ , $A_v = +1$                                                                                                                                                                  |       | 0.08   |       | Ω               |

| Parameter                              | Symbol              | Test Conditions/Comments                                                                                                         | Min        | Typ        | Max | Unit                                                         |

|----------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------|------------|------------|-----|--------------------------------------------------------------|

| POWER SUPPLY                           |                     |                                                                                                                                  |            |            |     |                                                              |

| Power Supply Rejection Ratio           | PSRR                | $V_S = \pm 2.5 \text{ V to } \pm 18 \text{ V}$<br>$-40^\circ\text{C} < T_A < +125^\circ\text{C}$                                 | 125<br>120 | 145        |     | dB                                                           |

| Supply Current per Amplifier           | $I_{SY}$            | $V_{OUT} = 0 \text{ V}$<br>$-40^\circ\text{C} < T_A < +125^\circ\text{C}$                                                        |            | 500<br>620 | 580 | $\mu\text{A}$<br>$\mu\text{A}$                               |

| DYNAMIC PERFORMANCE                    |                     |                                                                                                                                  |            |            |     |                                                              |

| Slew Rate                              | SR                  | $R_L = 2 \text{ k}\Omega$                                                                                                        |            | 1.5        |     | $\text{V}/\mu\text{s}$                                       |

| Settling Time                          | $t_s$               | $V_{IN} = 10 \text{ V p-p}, R_L = 2 \text{ k}\Omega, A_v = -1$<br>$V_{IN} = 10 \text{ V p-p}, R_L = 2 \text{ k}\Omega, A_v = -1$ |            | 5.5<br>7.5 |     | $\mu\text{s}$<br>$\mu\text{s}$                               |

| To 0.1%                                |                     |                                                                                                                                  |            |            |     |                                                              |

| To 0.01%                               |                     |                                                                                                                                  |            |            |     |                                                              |

| Gain Bandwidth Product                 | GBP                 | $V_{IN} = 10 \text{ mV p-p}, R_L = 2 \text{ k}\Omega, A_v = +100$                                                                |            | 3.5        |     | MHz                                                          |

| Unity-Gain Crossover                   | UGC                 | $V_{IN} = 10 \text{ mV p-p}, R_L = 2 \text{ k}\Omega, A_v = +1$                                                                  |            | 3.5        |     | MHz                                                          |

| $-3 \text{ dB}$ Closed-Loop Bandwidth  | $f_{-3 \text{ dB}}$ | $V_{IN} = 10 \text{ mV p-p}, R_L = 2 \text{ k}\Omega, A_v = +1$                                                                  |            | 6          |     | MHz                                                          |

| Total Harmonic Distortion Plus Noise   | THD + N             | $V_{IN} = 1 \text{ V rms}, A_v = +1, R_L = 2 \text{ k}\Omega, f = 1 \text{ kHz}$                                                 |            | 0.002      |     | %                                                            |

| EMI Rejection of $+IN_x$               | EMIRR               | $V_{IN} = 200 \text{ mV p-p}$                                                                                                    |            | 70<br>90   |     | dB<br>dB                                                     |

| f = 1000 MHz                           |                     |                                                                                                                                  |            |            |     |                                                              |

| f = 2400 MHz                           |                     |                                                                                                                                  |            |            |     |                                                              |

| NOISE PERFORMANCE                      |                     |                                                                                                                                  |            |            |     |                                                              |

| Voltage Noise                          | $e_{n \text{ p-p}}$ | 0.1 Hz to 10 Hz                                                                                                                  |            | 175        |     | $\text{nV p-p}$                                              |

| Voltage Noise Density                  | $e_n$               | $f = 10 \text{ Hz}$<br>$f = 1 \text{ kHz}$                                                                                       |            | 10<br>8    |     | $\text{nV}/\sqrt{\text{Hz}}$<br>$\text{nV}/\sqrt{\text{Hz}}$ |

| Current Noise Density                  | $i_n$               | $f = 1 \text{ kHz}$                                                                                                              |            | 0.2        |     | $\text{pA}/\sqrt{\text{Hz}}$                                 |

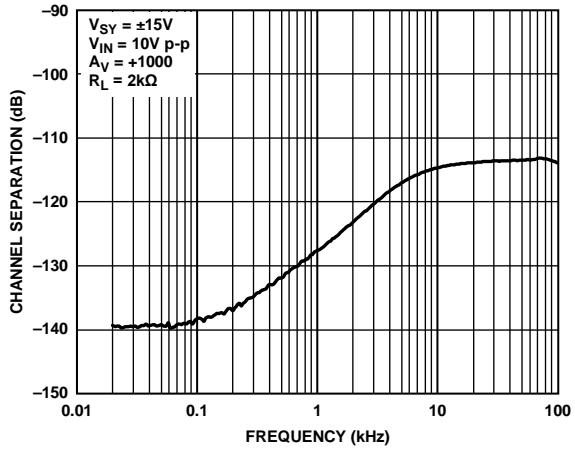

| MULTIPLE AMPLIFIERS CHANNEL SEPARATION | $C_S$               | $f = 1 \text{ kHz}$                                                                                                              |            | 127        |     | dB                                                           |

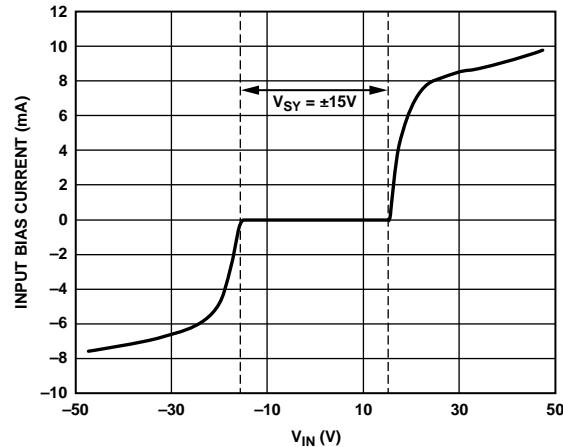

<sup>1</sup>すべての入力に 500 ms にわたって電源電圧を 32 V 上回る電圧を印加。過電圧保護された入力範囲にわたる入力バイアス電流と入力電圧の関係については、図 74 を参照してください。

## 絶対最大定格

表 4.

| Parameter                                               | Rating                                    |

|---------------------------------------------------------|-------------------------------------------|

| Supply Voltage                                          | 36 V                                      |

| Input Voltage                                           | $V_{SY} \pm 32$ V                         |

| Differential Input Voltage                              | $\pm V_{SY}$                              |

| Output Short-Circuit Duration to GND                    | See the Maximum Power Dissipation section |

| Storage Temperature Range                               | -65°C to +150°C                           |

| Operating Temperature Range                             | -40°C to +125°C                           |

| Junction Temperature Range                              | -65°C to +150°C                           |

| Lead Temperature, Soldering (10 sec) <sup>1</sup>       | 300°C                                     |

| ESD                                                     |                                           |

| Human Body Model (HBM) <sup>2</sup>                     | 4 kV                                      |

| Field Induced Charged Device Model (FICDM) <sup>3</sup> | 1250 V                                    |

| Machine Model (MM)                                      | 200 V                                     |

<sup>1</sup> 適用規格 IPC/JEDEC J-ST8-020D。<sup>2</sup> 適用規格 ESDA/JEDEC JS-001-2011。<sup>3</sup> 適用規格 JESD22-C101 (JEDEC の ESD FICDM 規格)。

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。製品を長時間絶対最大定格状態に置くと、製品の信頼性に影響を与えることがあります。

## 最大消費電力

ADA4177-1/ADA4177-2/ADA4177-4 は、最大 65 mA の短絡出力電流を駆動できます。ただし、使用可能な出力負荷の駆動電流は、デバイス・パッケージで許容されている最大消費電力によって制限されます。絶対最大ジャンクション温度は 150 °C です（表 4 を参照）。ジャンクション温度は、次式で見積もることができます。

$$T_J = P_D \times \theta_{JA} + T_A$$

ここで、

$T_J$  はダイのジャンクション温度。 $P_D$  はパッケージの消費電力。 $\theta_{JA}$  はパッケージの熱抵抗。 $T_A$  は周囲温度。

パッケージ内の消費電力 ( $P_D$ ) は、静止消費電力と出力段トランジスタの消費電力との和になります。次式で計算できます。

$$P_D = (V_{SY} \times I_{SY}) + (V_{SY} - V_{OUT}) \times I_{LOAD}$$

ここで、

$V_{SY}$  は電源レール。 $I_{SY}$  は静止電流。 $V_{OUT}$  はアンプの出力。 $I_{LOAD}$  は出力負荷。

デバイスの最大ジャンクション温度である 150 °C を超えないようにしてください。ジャンクション温度の上限を超えると、パラメータ性能が低下したり、デバイスが破損したりすることがあります。詳細については、技術資料 MS-2251 のデータシートの奥深さ - 絶対最大定格と熱抵抗を参照してください。

## 熱抵抗

ジャンクション温度と周囲温度の間の熱抵抗 ( $\theta_{JA}$ ) は最も厳しい条件、すなわち、回路基板に表面実装パッケージをハンダ付けした状態で仕様規定されています。

表 5. 热抵抗

| Package Type  | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|---------------|---------------|---------------|------|

| 8-Lead MSOP   | 190           | 44            | °C/W |

| 8-Lead SOIC   | 158           | 43            | °C/W |

| 14-Lead TSSOP | 240           | 43            | °C/W |

| 14-Lead SOIC  | 115           | 36            | °C/W |

## ESD に関する注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することができます。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

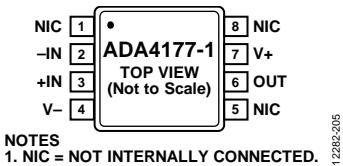

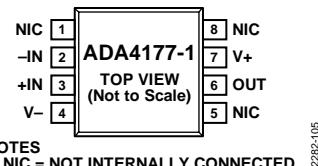

## ピン配置およびピン機能の説明

図 3.8 ピン MSOP ピン配置、ADA4177-1

図 4.8 ピン SOIC ピン配置、ADA4177-1

表 6. ADA4177-1 ピン機能の説明

| ピン番号  | 記号  | 説明          |

|-------|-----|-------------|

| 1、5、8 | NIC | 内部では未接続     |

| 2     | -IN | 反転入力チャンネル。  |

| 3     | +IN | 非反転入力チャンネル。 |

| 4     | V-  | 負電源電圧。      |

| 6     | OUT | 出力チャンネル。    |

| 7     | V+  | 正電源電圧。      |

図 5.8 ピン MSOP ピン配置、ADA4177-2

図 6.8 ピン SOIC ピン配置、ADA4177-2

表 7. ADA4177-2 ピン機能の説明

| ピン番号 | 記号    | 説明            |

|------|-------|---------------|

| 1    | OUT A | 出力チャンネル A。    |

| 2    | -IN A | 反転入力チャンネル A。  |

| 3    | +IN A | 非反転入力チャンネル A。 |

| 4    | V-    | 負電源電圧。        |

| 5    | +IN B | 非反転入力チャンネル B。 |

| 6    | -IN B | 反転入力チャンネル B。  |

| 7    | OUT B | 出力チャンネル B。    |

| 8    | V+    | 正電源電圧。        |

# データシート

ADA4177-1/ADA4177-2/ADA4177-4

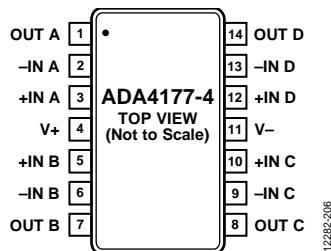

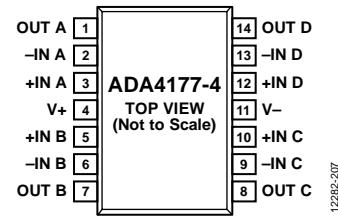

図 7.14 ピン TSSOP ピン配置、ADA4177-4

図 8.14 ピン SOIC ピン配置、ADA4177-4

表 8. ADA4177-4 ピン機能の説明

| ピン番号 | 記号    | 説明            |

|------|-------|---------------|

| 1    | OUT A | 出力チャンネル A。    |

| 2    | -IN A | 反転入力チャンネル A。  |

| 3    | +IN A | 非反転入力チャンネル A。 |

| 4    | V+    | 正電源電圧。        |

| 5    | +IN B | 非反転入力チャンネル B。 |

| 6    | -IN B | 反転入力チャンネル B。  |

| 7    | OUT B | 出力チャンネル B。    |

| 8    | OUT C | 出力チャンネル C。    |

| 9    | -IN C | 反転入力チャンネル C。  |

| 10   | +IN C | 非反転入力チャンネル C。 |

| 11   | V-    | 負電源電圧。        |

| 12   | +IN D | 非反転入力チャンネル D。 |

| 13   | -IN D | 反転入力チャンネル D。  |

| 14   | OUT D | 出力チャンネル D。    |

## 代表的な性能特性

特に指定のない限り、周囲温度 ( $T_A$ ) = 25° C。

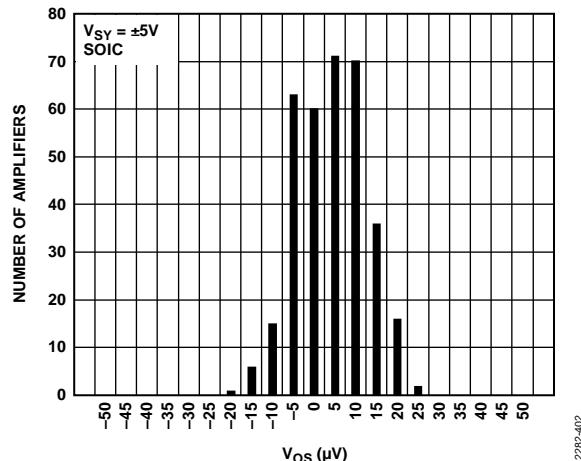

12282-402

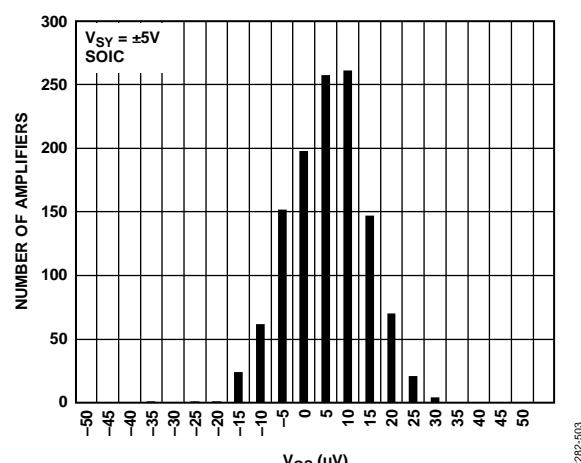

図 9. 入力オフセット電圧 ( $V_{OS}$ ) の分布、 $V_{SY} = \pm 5$  V、8 ピン SOIC

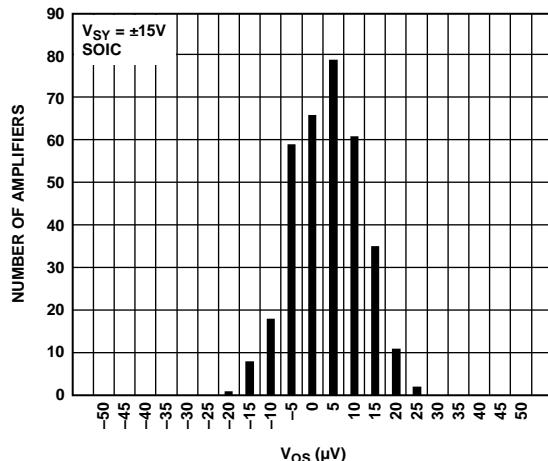

12282-403

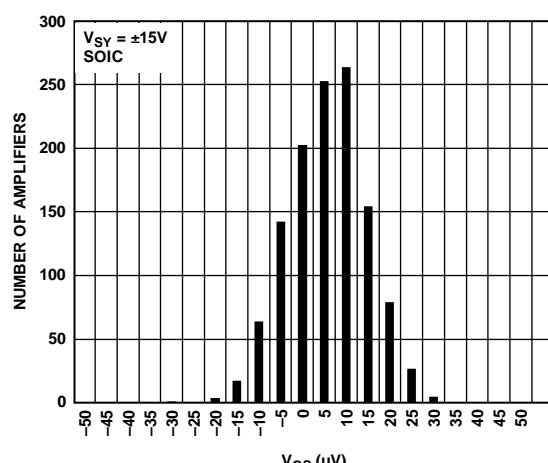

図 12. 入力オフセット電圧 ( $V_{OS}$ ) の分布、 $V_{SY} = \pm 15$  V、8 ピン SOIC

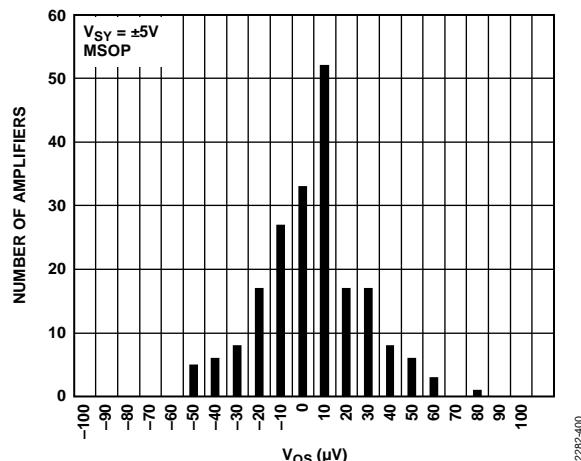

12282-400

図 10. 入力オフセット電圧 ( $V_{OS}$ ) の分布、 $V_{SY} = \pm 5$  V、8 ピン MSOP

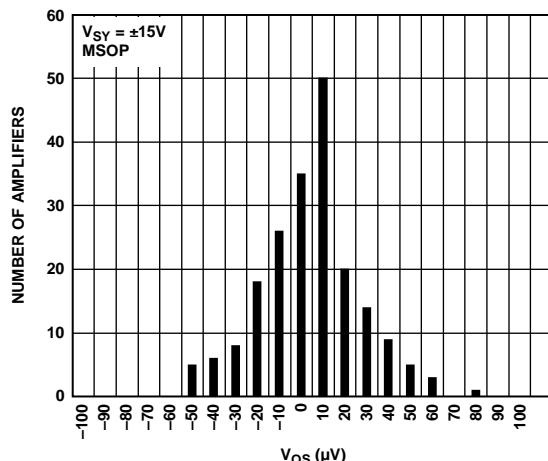

12282-401

図 13. 入力オフセット電圧 ( $V_{OS}$ ) の分布、 $V_{SY} = \pm 15$  V、8 ピン MSOP

12282-503

図 11. 入力オフセット電圧 ( $V_{OS}$ ) の分布、 $V_{SY} = \pm 5$  V、14 ピン SOIC

12282-504

図 14. 入力オフセット電圧 ( $V_{OS}$ ) の分布、 $V_{SY} = \pm 15$  V、14 ピン SOIC

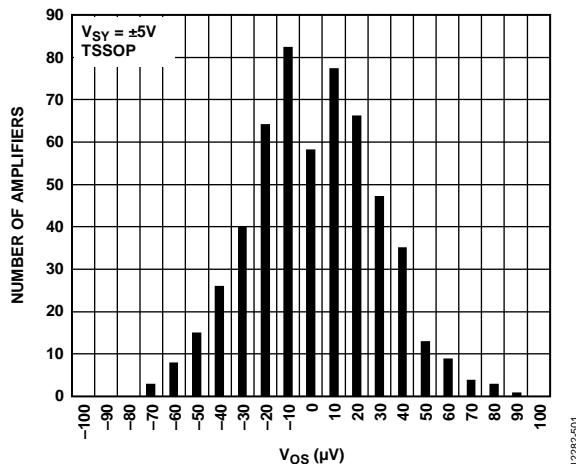

図 15. 入力オフセット電圧 ( $V_{OS}$ ) の分布、 $V_{SY} = \pm 5V$ 、

14 ピン TSSOP

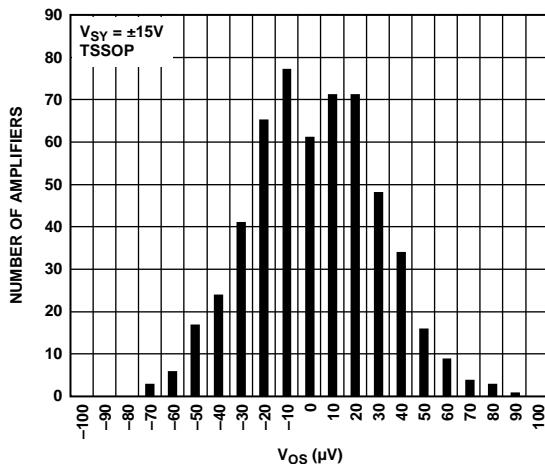

図 18. 入力オフセット電圧 ( $V_{OS}$ ) の分布、 $V_{SY} = \pm 15V$ 、

14 ピン TSSOP

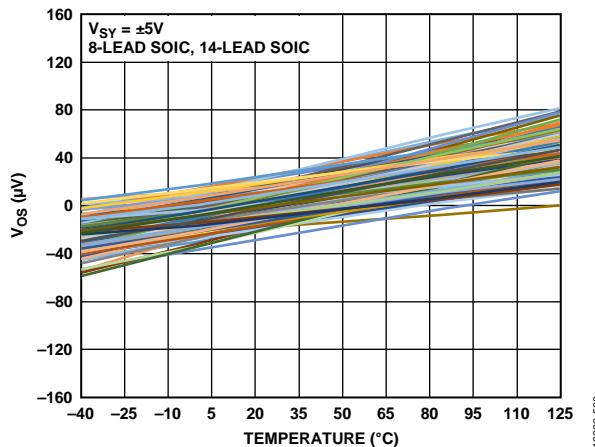

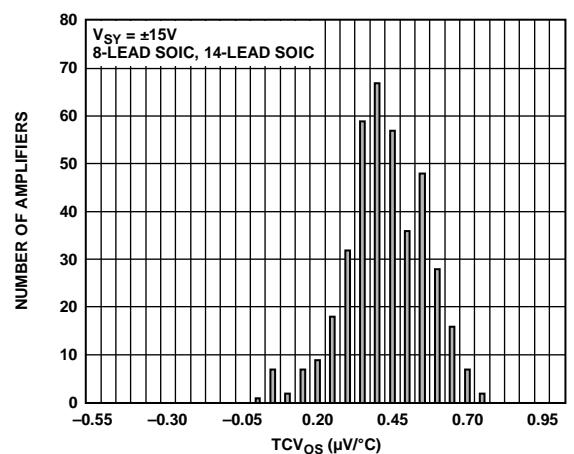

図 16. 入力オフセット電圧 ( $V_{OS}$ ) と温度の関係、 $V_{SY} = \pm 5V$ 、

8 ピン SOIC および 14 ピン SOIC

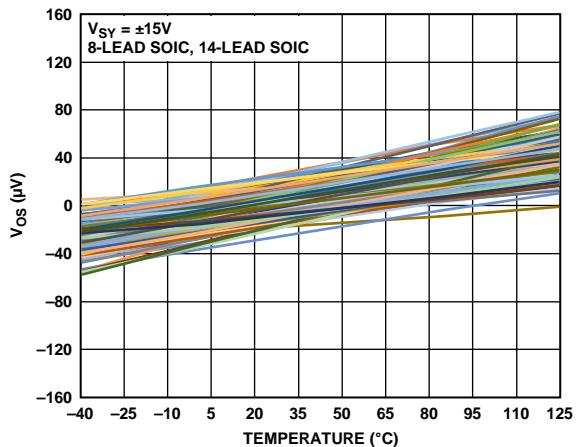

図 19. 入力オフセット電圧 ( $V_{OS}$ ) と温度の関係、 $V_{SY} = \pm 15V$ 、

8 ピン SOIC および 14 ピン SOIC

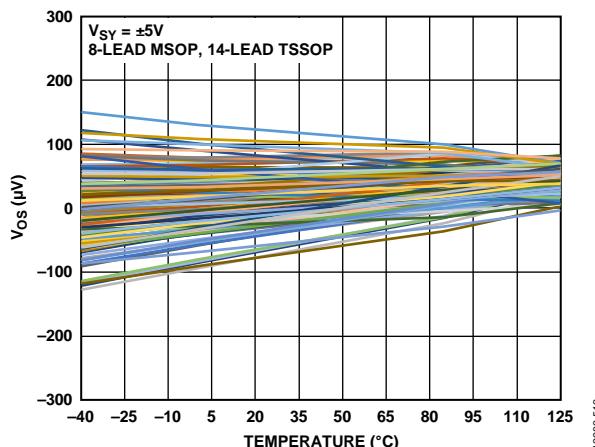

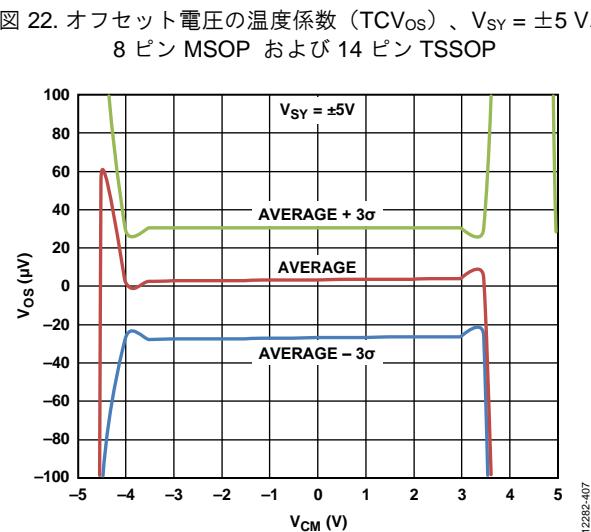

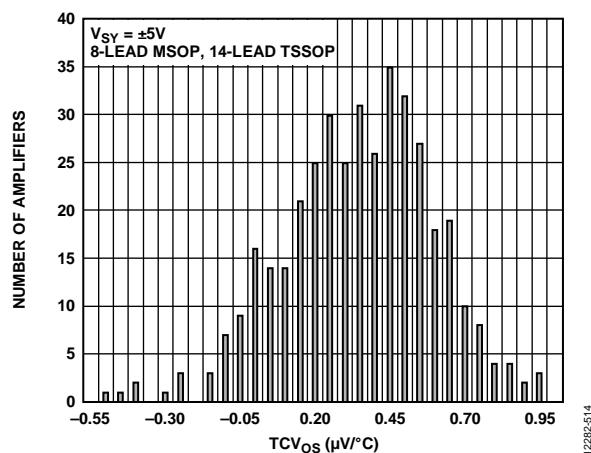

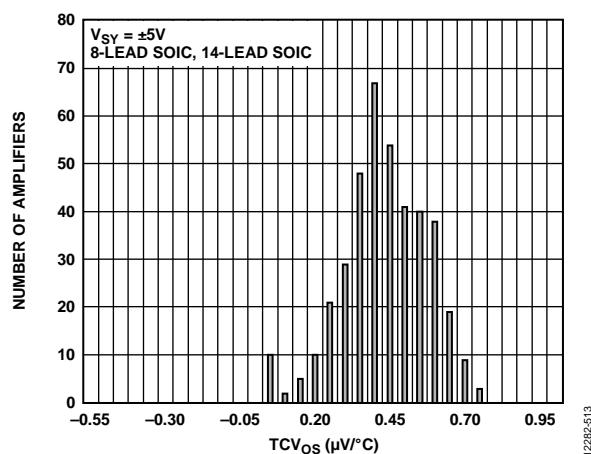

図 17. 入力オフセット電圧 ( $V_{OS}$ ) と温度の関係、 $V_{SY} = \pm 5V$ 、

8 ピン MSOP および 14 ピン TSSOP

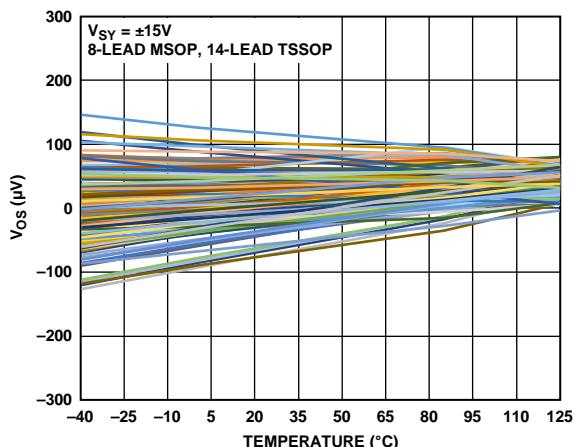

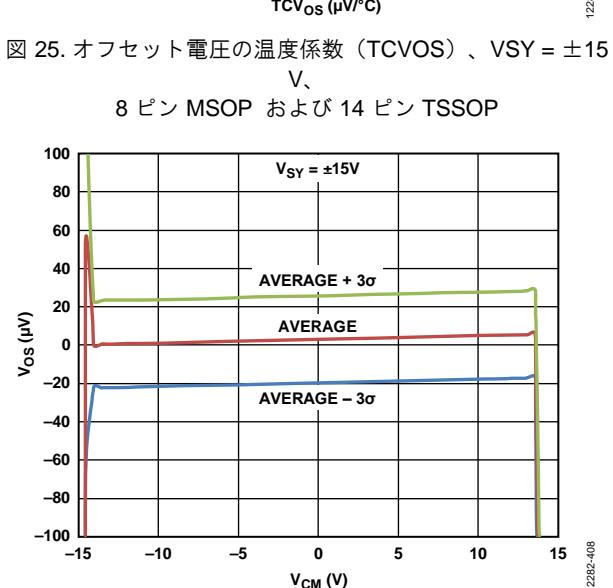

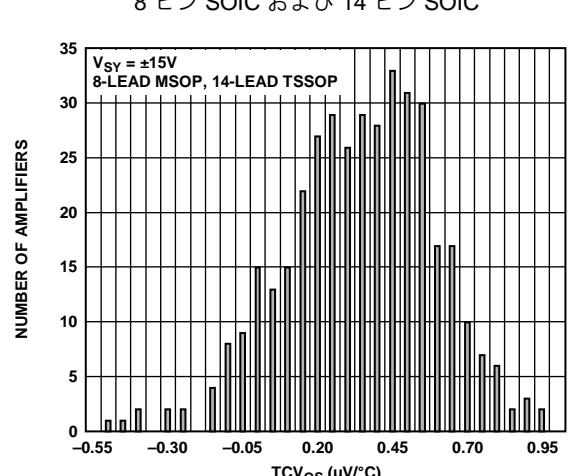

図 20. 入力オフセット電圧 ( $V_{OS}$ ) と温度の関係、 $V_{SY} = \pm 15V$ 、

8 ピン MSOP および 14 ピン TSSOP

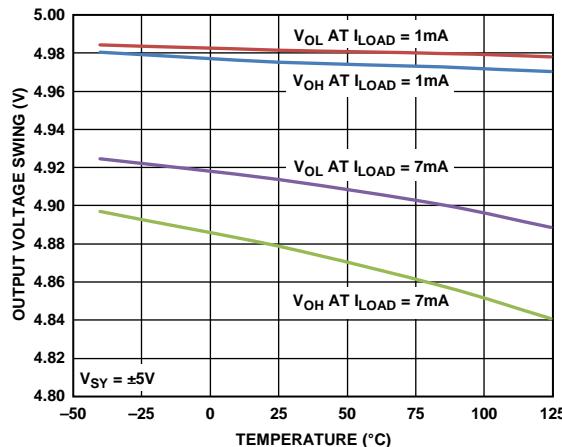

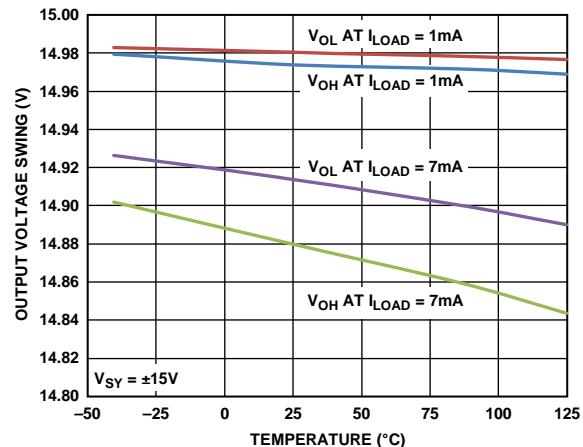

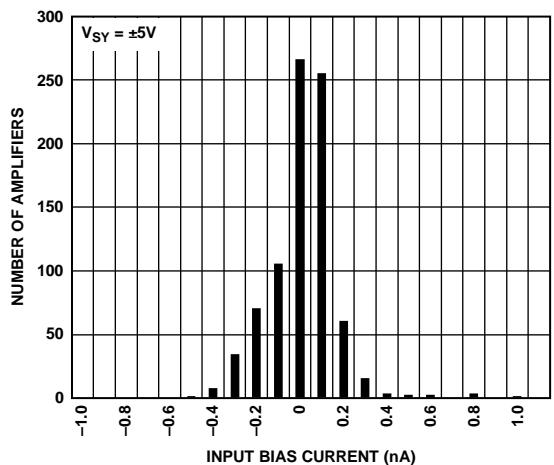

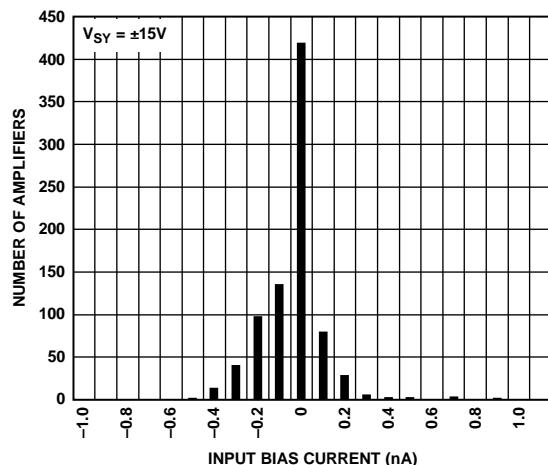

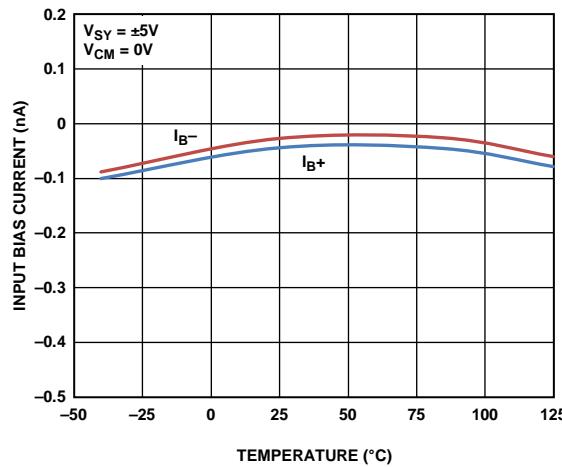

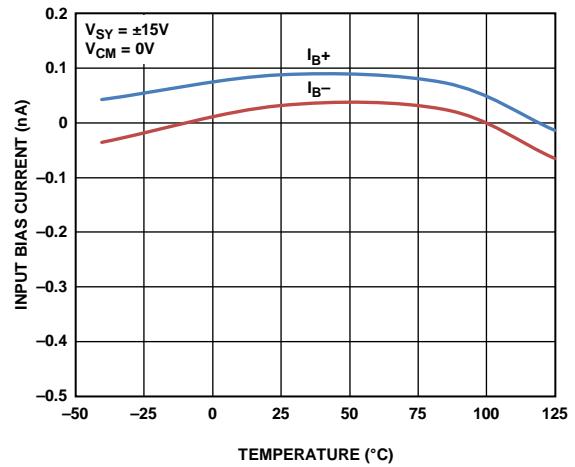

図 27. 出力電圧振幅と温度の関係、 $V_{SY} = \pm 5 \text{ V}$ 図 30. 出力電圧振幅と温度の関係、 $V_{SY} = \pm 15 \text{ V}$ 図 28. 入力バイアス電流の分布、 $V_{SY} = \pm 5 \text{ V}$ 図 31. 入力バイアス電流の分布、 $V_{SY} = \pm 15 \text{ V}$ 図 29. 入力バイアス電流 ( $I_B$ ) と温度の関係、 $V_{SY} = \pm 5 \text{ V}$ 図 32. 入力バイアス電流 ( $I_B$ ) と温度の関係、 $V_{SY} = \pm 15 \text{ V}$

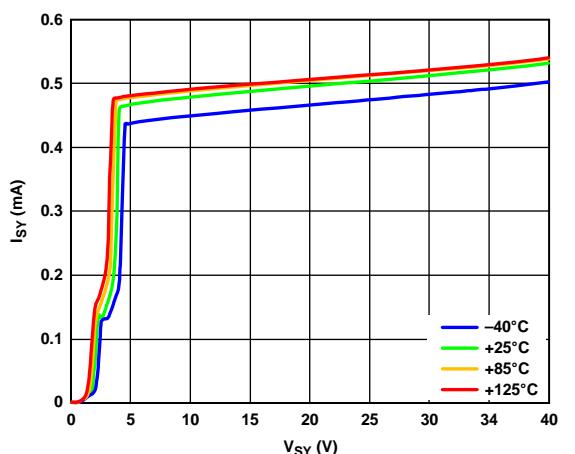

図 33. アンプあたりの電源電流 ( $I_{SY}$ ) と電源電圧 ( $V_{SY}$ ) の関係

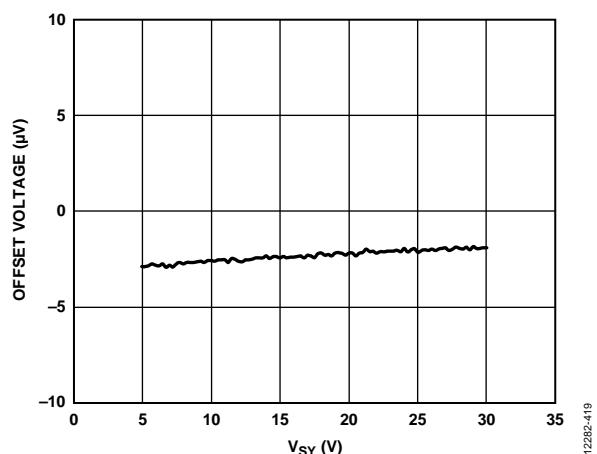

図 36. オフセット電圧 ( $V_{OS}$ ) と電源電圧 ( $V_{SY}$ ) の関係

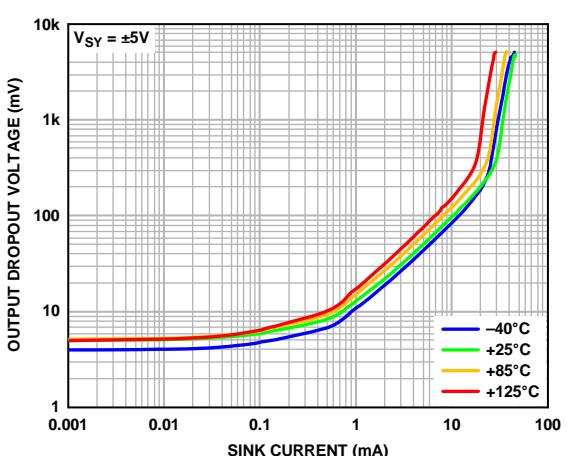

図 34. 出力ドロップアウト電圧とシンク電流の関係、 $V_{SY} = \pm 5\text{V}$

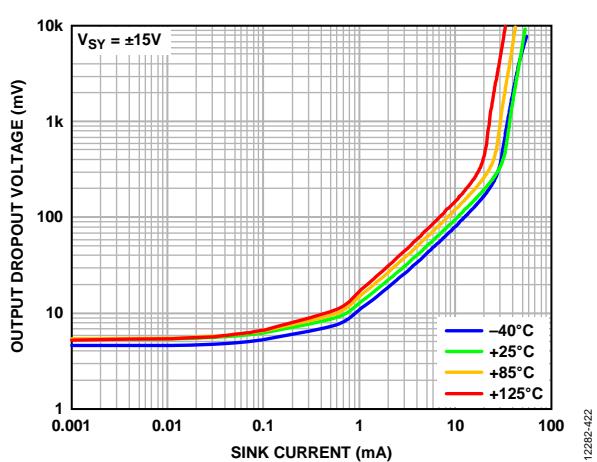

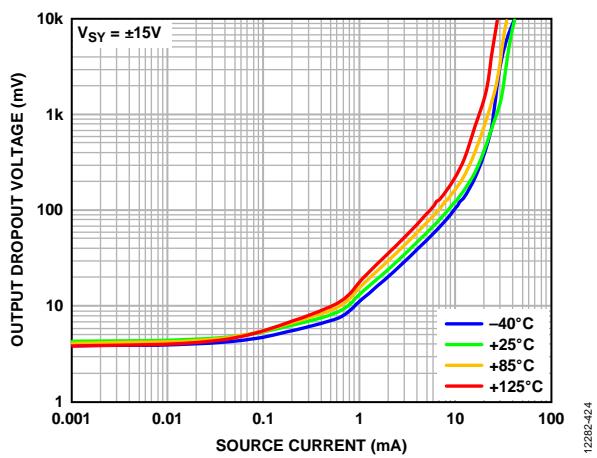

図 37. 出力ドロップアウト電圧とシンク電流の関係、 $V_{SY} = \pm 15\text{V}$

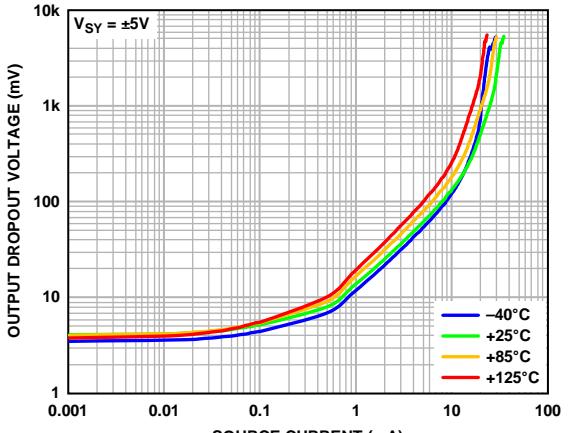

図 35. 出力ドロップアウト電圧とソース電流の関係、 $V_{SY} = \pm 5\text{V}$

図 38. 出力ドロップアウト電圧とソース電流の関係、 $V_{SY} = \pm 15\text{V}$

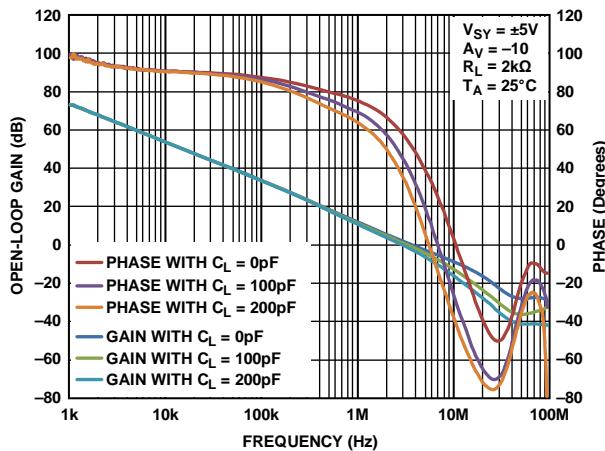

図 39. オープンループ・ゲインと位相の周波数特性、

$V_{SY} = \pm 5V$

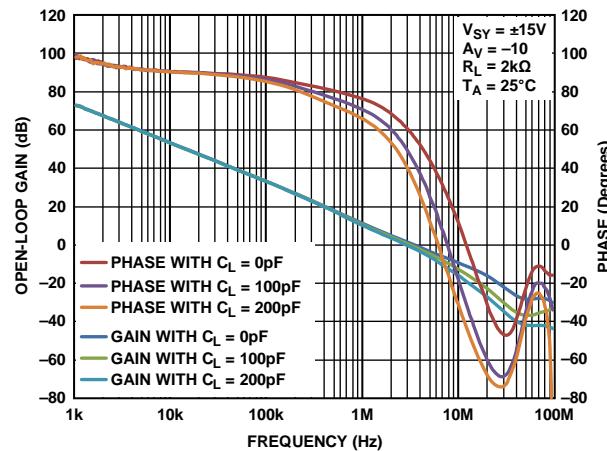

図 42. オープンループ・ゲインと位相の周波数特性、

$V_{SY} = \pm 15V$

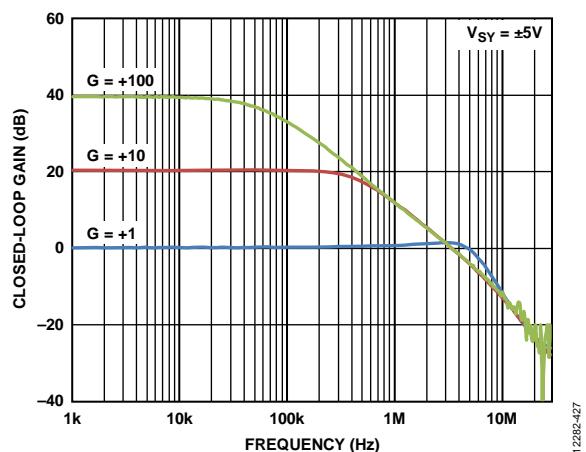

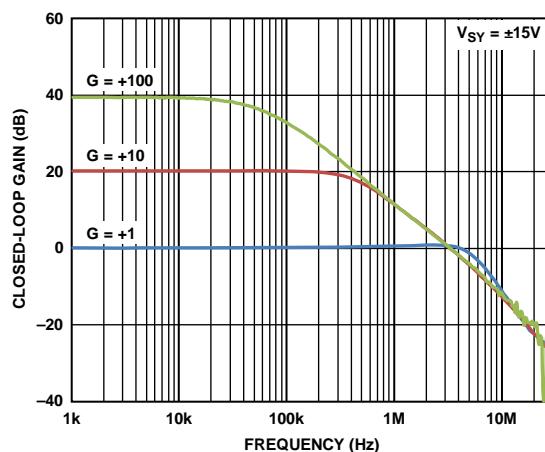

図 40. クローズドループ・ゲインの周波数特性、 $V_{SY} = \pm 5V$

図 43. クローズドループ・ゲインの周波数特性、 $V_{SY} = \pm 15V$

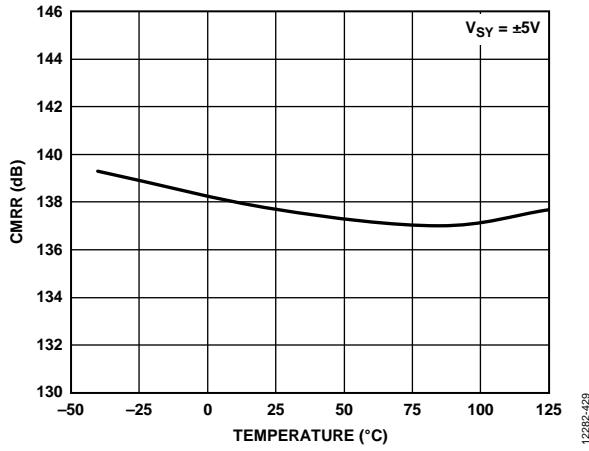

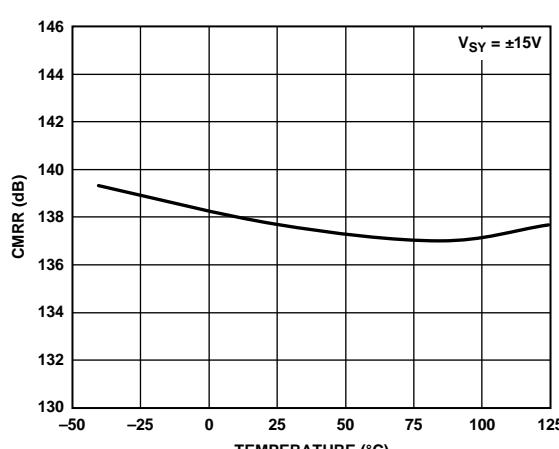

図 41. 同相ノイズ除去比 (CMRR) と温度の関係、 $V_{SY} = \pm 5V$

図 44. 同相ノイズ除去比 (CMRR) と温度の関係、 $V_{SY} = \pm 15V$

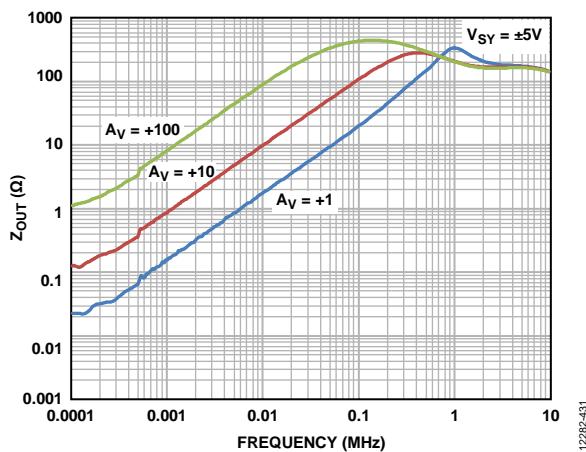

図 45. 出力インピーダンス ( $Z_{\text{OUT}}$ ) の周波数特性、 $V_{\text{SY}} = \pm 5$  V

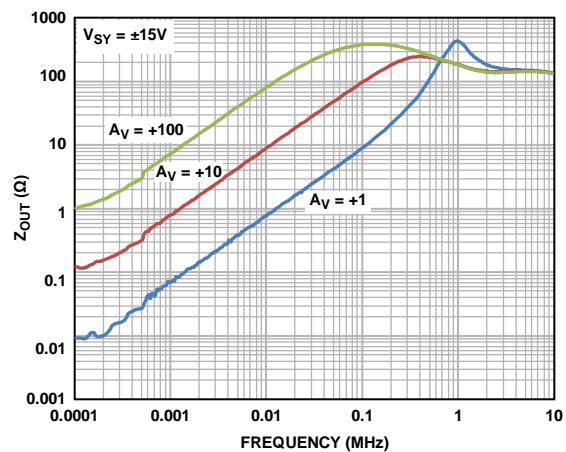

図 48. 出力インピーダンス ( $Z_{\text{OUT}}$ ) の周波数特性、 $V_{\text{SY}} = \pm 15$  V

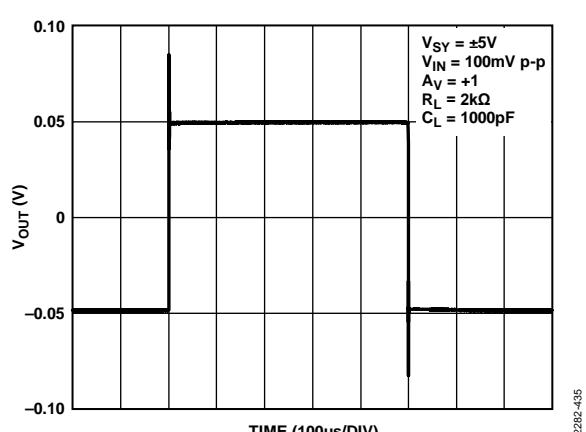

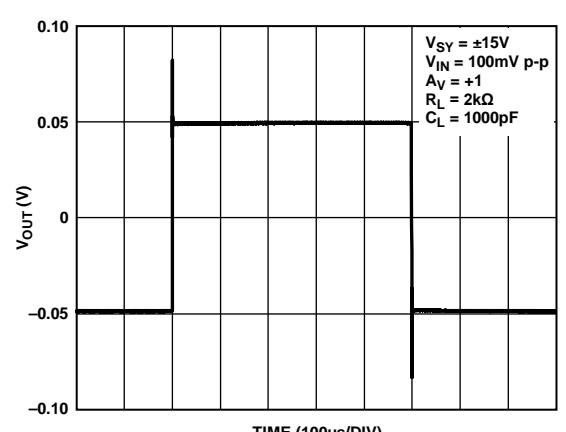

12282-431

12282-432

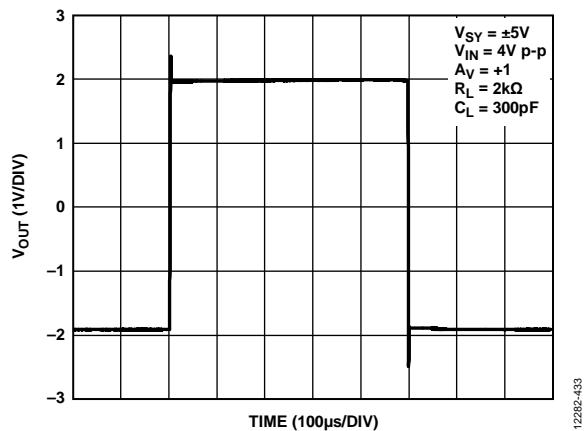

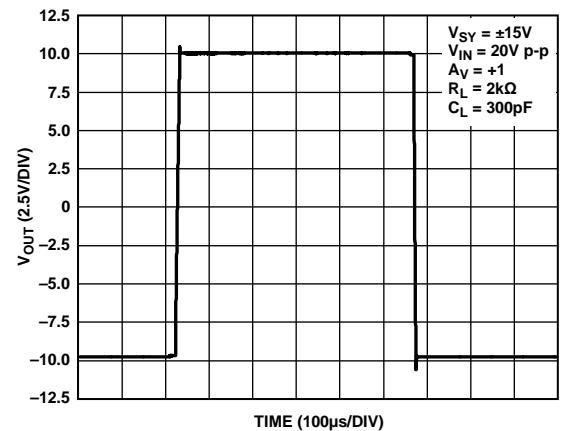

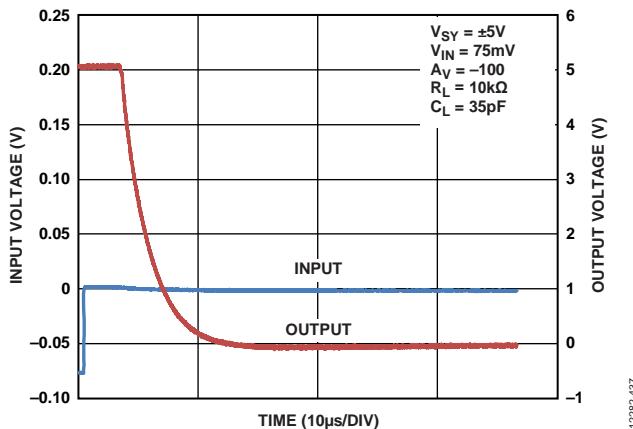

12282-435

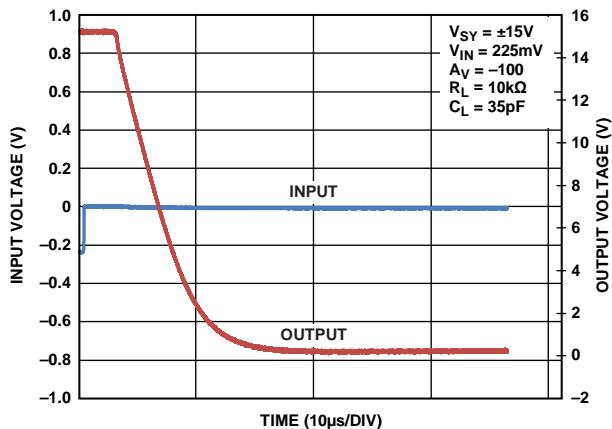

12282-436

12282-437

12282-438

12282-439

12282-440

12282-420

12282-455

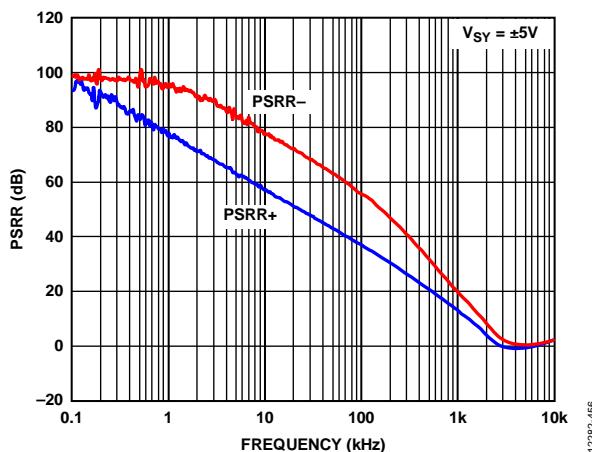

図 57. 電源電圧変動除去比（PSRR）の周波数特性、

$V_{SY} = \pm 5\text{ V}$

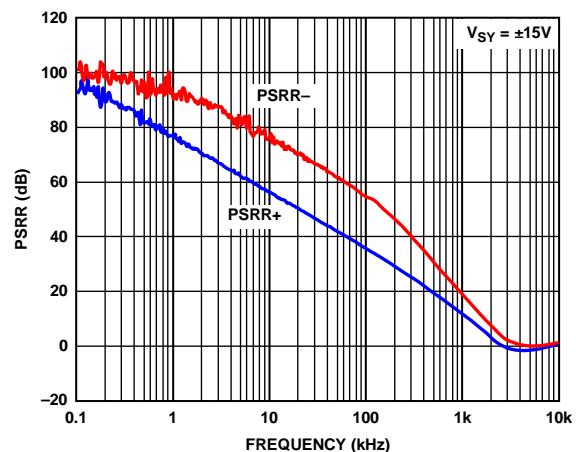

図 60. 電源電圧変動除去比（PSRR）の周波数特性、

$V_{SY} = \pm 15\text{ V}$

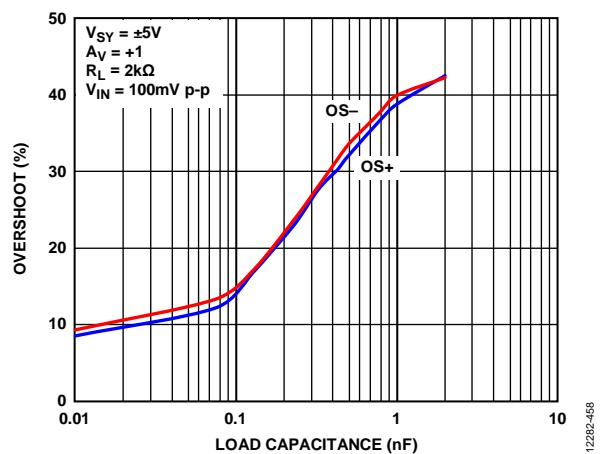

図 58. 小信号オーバーシュートと負荷容量の関係、

$V_{SY} = \pm 5\text{ V}$

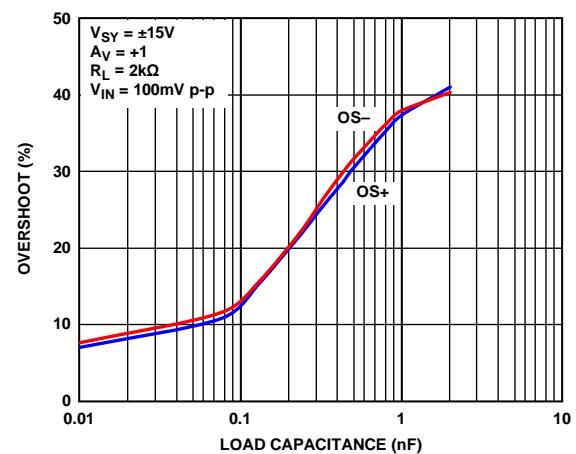

図 61. 小信号オーバーシュートと負荷容量の関係、

$V_{SY} = \pm 15\text{ V}$

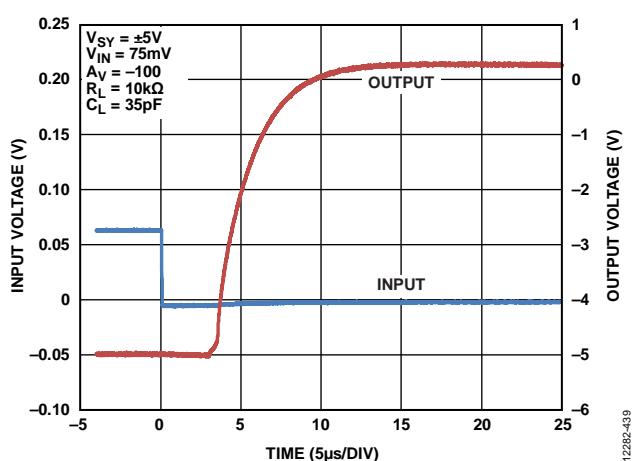

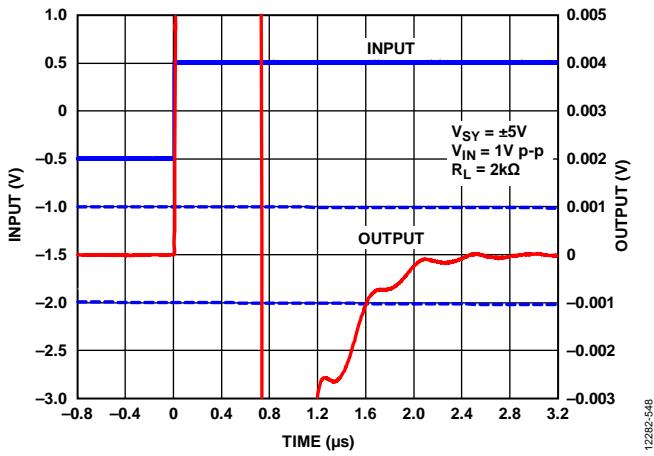

図 59. 0.1 % への立上がりセトリング・タイム、

$V_{SY} = \pm 5\text{ V}$

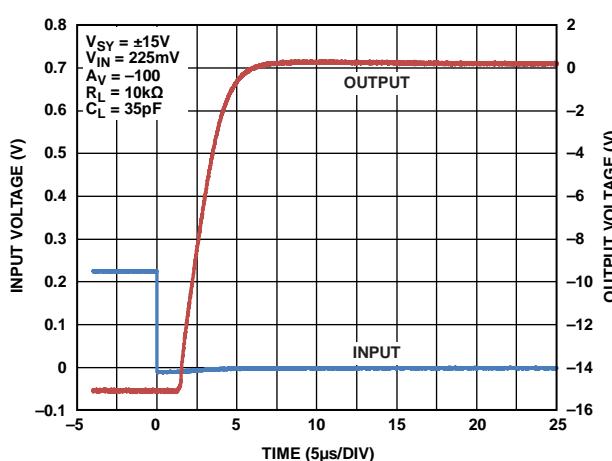

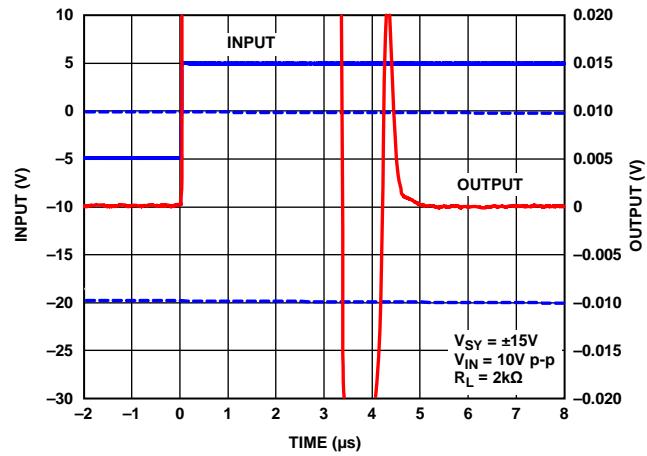

図 62. 0.1 % への立上がりセトリング・タイム、

$V_{SY} = \pm 15\text{ V}$

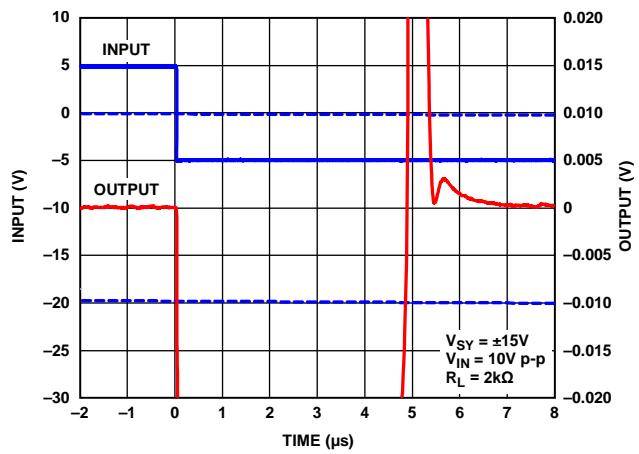

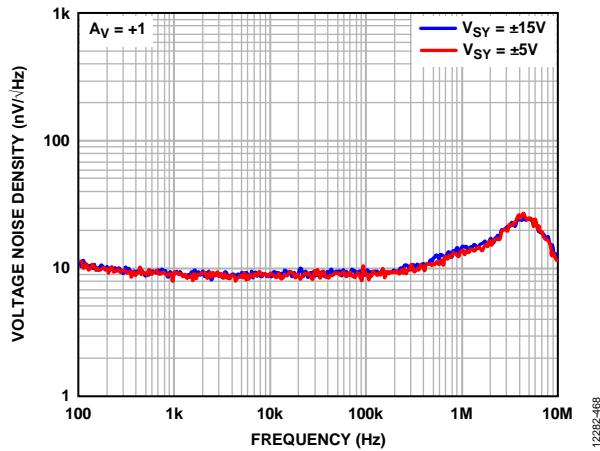

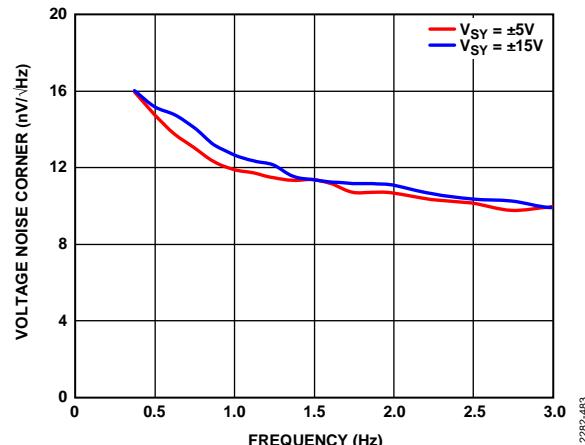

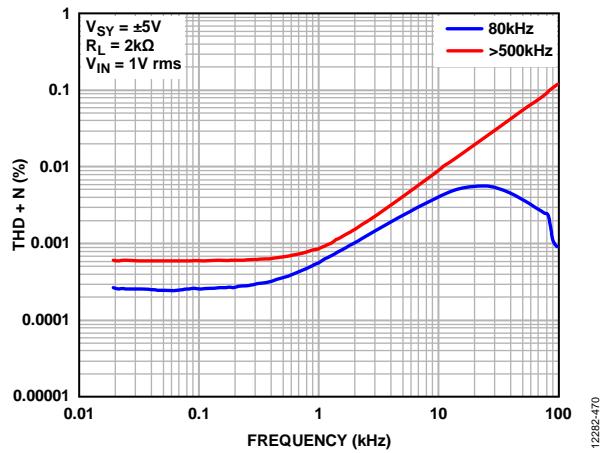

図 63. 0.1 % への立下がりセトリング・タイム、 $V_{SY} = \pm 5V$ 図 66. 0.1 % への立下がりセトリング・タイム、 $V_{SY} = \pm 15V$ 図 64. 低電圧ノイズ密度の周波数特性、

$V_{SY} = \pm 5V$  および  $V_{SY} = \pm 15V$ 図 67. 電圧ノイズ・コーナーの周波数特性、

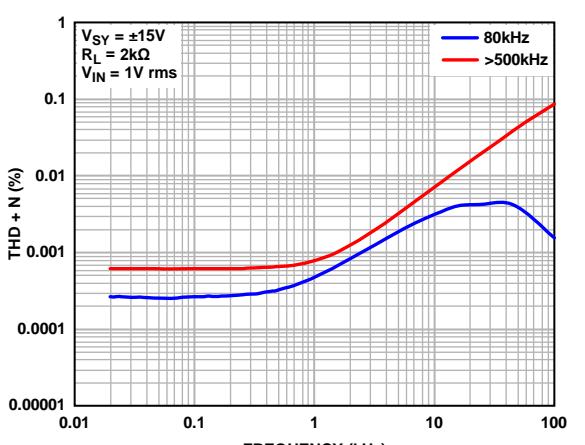

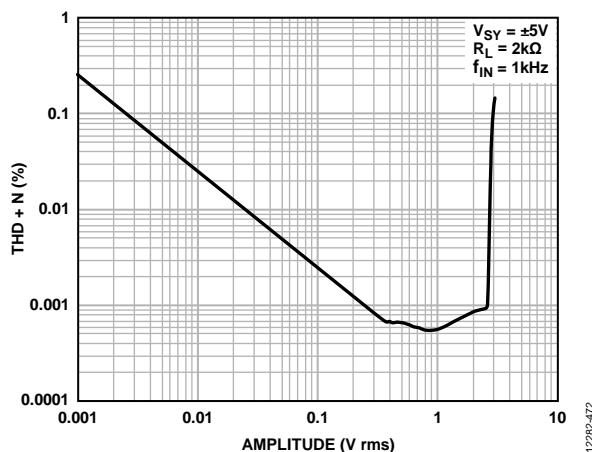

$V_{SY} = \pm 5V$  および  $V_{SY} = \pm 15V$ 図 65. THD + N の周波数特性、 $V_{SY} = \pm 5V$ 図 68. THD + N の周波数特性、 $V_{SY} = \pm 15V$

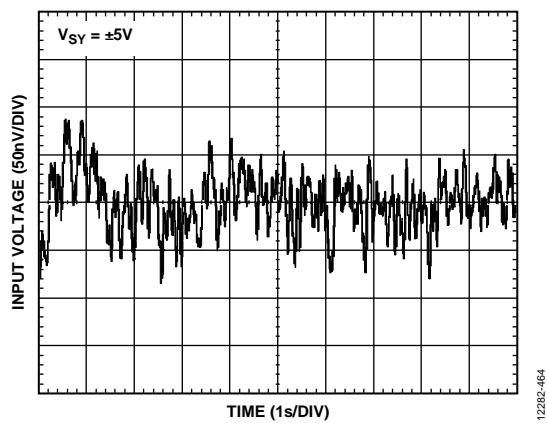

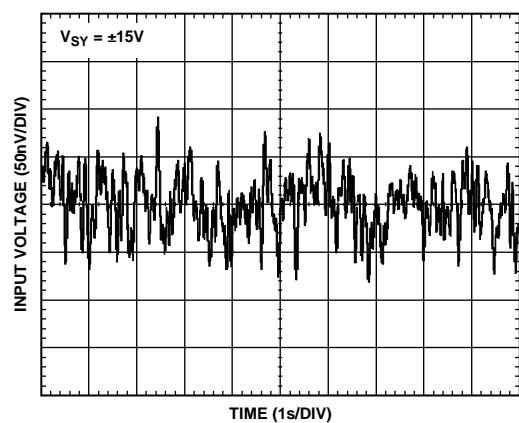

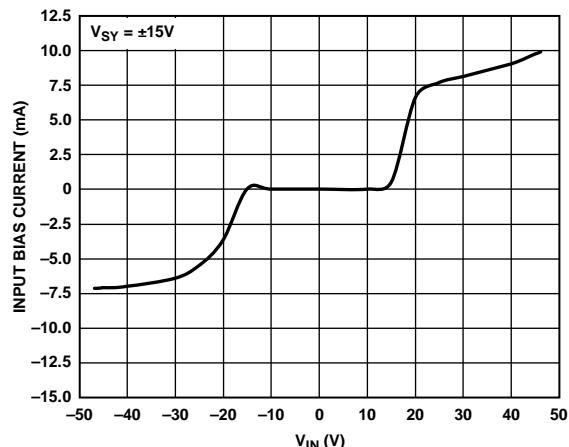

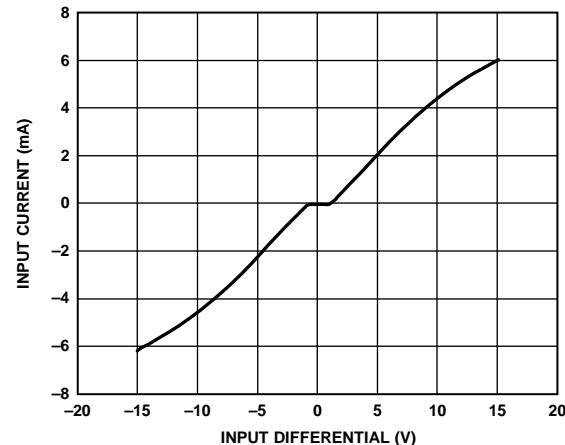

図 69. THD + N と振幅の関係、 $V_{SY} = \pm 5V$ 図 72. THD + N と振幅の関係、 $V_{SY} = \pm 15V$ 図 70. 0.1 Hz ~ 10 Hz ノイズ、 $V_{SY} = \pm 5V$ 図 73. 0.1 Hz ~ 10 Hz ノイズ、 $V_{SY} = \pm 15V$ 図 71. 入力バイアス電流と入力電圧 ( $V_{IN}$ ) の関係、

入力過電圧範囲を含む ( $V_{SY} = \pm 5V$  超)図 74. 入力バイアス電流と入力電圧 ( $V_{IN}$ ) の関係、

入力過電圧範囲を含む ( $V_{SY} = \pm 15V$  超)

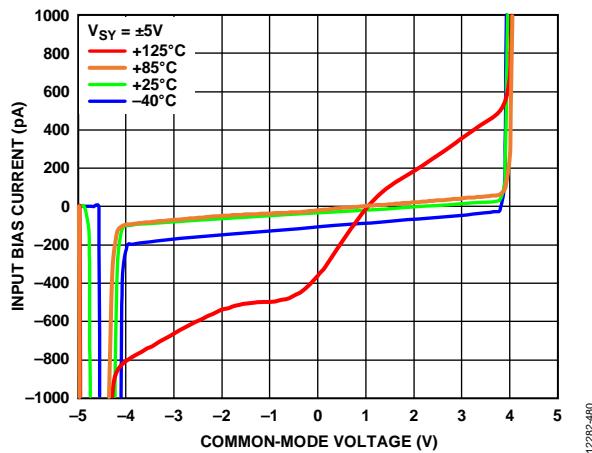

図 75. 各種温度での入力バイアス電流とコモンモード電圧 ( $V_{CM}$ ) の関係、 $V_{SY} = \pm 5V$

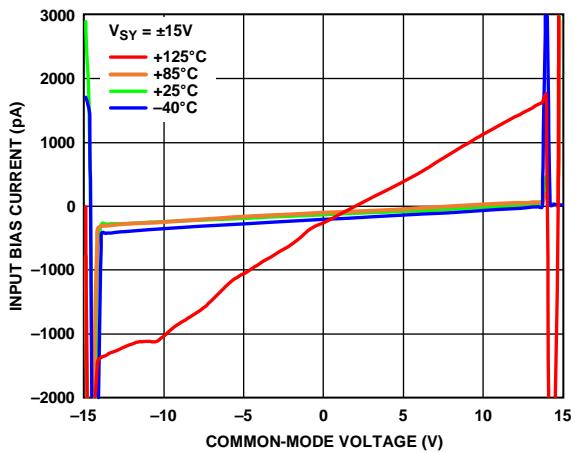

図 78. 各種温度での入力バイアス電流とコモンモード電圧 ( $V_{CM}$ ) の関係、 $V_{SY} = \pm 15V$

図 76. 電流ノイズ密度の周波数特性、 $V_{SY} = \pm 5V$  および  $V_{SY} = \pm 15V$

図 79. チャンネル・セパレーションの周波数特性、 $V_{SY} = \pm 15V$

図 77. 出力短絡ソース電流と温度の関係、 $V_{SY} = \pm 5V$

図 80. 出力短絡ソース電流と温度の関係、 $V_{SY} = \pm 15V$

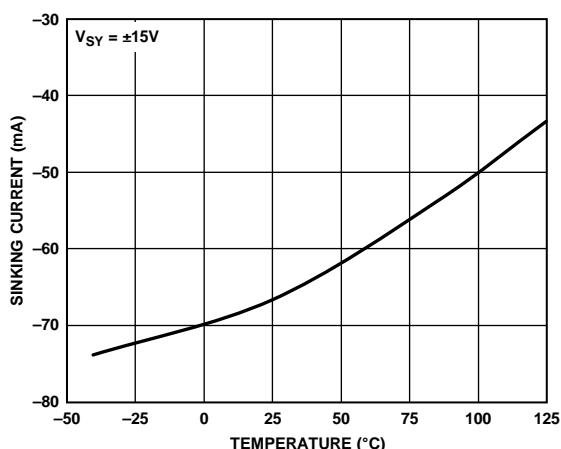

図 81. 出力短絡シンク電流と温度の関係、 $V_{SY} = \pm 5\text{ V}$

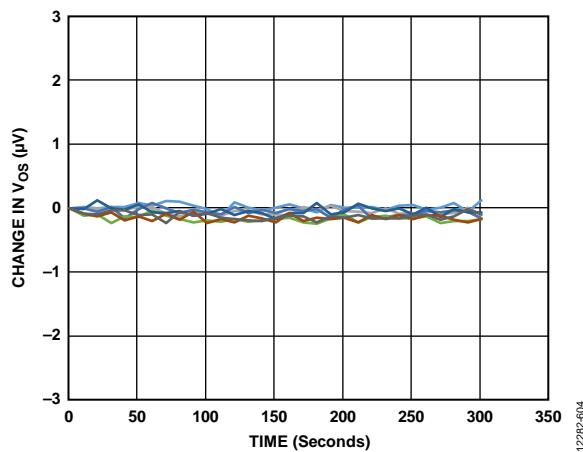

図 82. オフセット電圧の短時間のドリフト

図 82. オフセット電圧の短時間のドリフト

## 動作原理

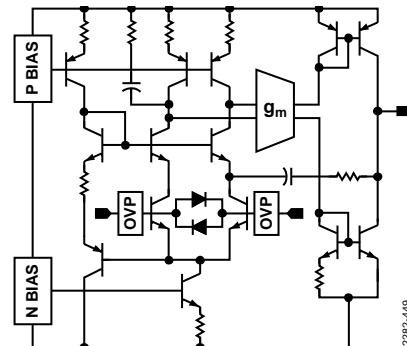

ADA4177-1/ADA4177-2/ADA4177-4 は、入力過電圧保護 (OVP) と入力 EMI フィルタリングの両方の機能を実装し、2 nA (max) の低バイアス電流を維持するとともに、レール to レール出力動作が可能な高精度バイポーラ・オペ・アンプです。図 84 に、入力バイアス電流を最小限に抑えるためにスーパー  $\beta$  のバイポーラ入力トランジスタとバイアス電流相殺回路を使用したメイン・アンプの概念図を示します。過電圧状態時にスーパー  $\beta$  入力デバイスを損傷から保護できるように、入力はカスコード接続されています。カスコード接続された入力は、プライマリ・ゲイン段を構成するアクティブ負荷に供給されます。バッファ付きのトランジスタ (g<sub>m</sub>) 段は、差動電圧を差動電流に変換して出力段を駆動します。レール to レール出力は、25 °C で負荷が 1 mA の場合、最大 50 mV までスイングします (正側電源が 15 V の場合、V<sub>OH</sub> で確保される室温上限値は 14.95 V)。

図 84. 概念図

12282-449

## アプリケーション情報

### アクティブ過電圧保護

ADA4177-1/ADA4177-2/ADA4177-4 は、アクティブ過電圧保護回路を使用して、正側電源電圧を 32 V 上回る電圧、または負側電源電圧を 32 V 下回る電圧で入力が駆動されたときにデバイスを損傷から保護します。ADA4177-1/ADA4177-2/ADA4177-4 は、入力を損傷から保護するだけではなく、入力ノイズも軽減します。

### 一般的な保護方法

#### 外付けの直列入力抵抗を追加する

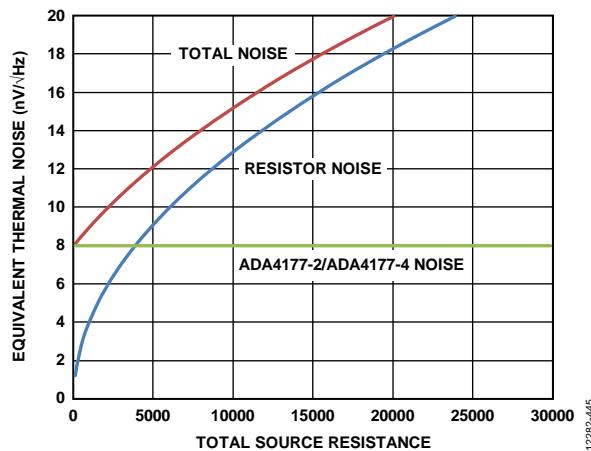

オペ・アンプに入力過電圧の保護回路がない場合、入力電圧が電源電圧を上回るまたは下回る電圧に遷移すると、過度な入力電流が発生し、オペ・アンプが損傷することがあります。これを回避するには、入力に直列抵抗を追加します。いずれかのレールに対して 30 V を上回る過渡電圧からオペ・アンプを保護するには、入力電流を 5 mA に制限して、入力に 6 kΩ 直列抵抗を追加します。ただし、直列抵抗を追加することで、熱ノイズが発生するというトレードオフが存在します。6 kΩ の直列抵抗では 10 nV/√Hz の熱ノイズが発生します。これにより、抵抗からの直交熱ノイズとオペ・アンプ・ノイズが追加されます。

$$N_{TOTAL} = \sqrt{N_{OPAMP}^2 + N_{RESISTOR}^2}$$

ここで、

$N_{OPAMP}$  はオペ・アンプのノイズ。

$N_{RESISTOR}$  は抵抗によって発生した熱ノイズ。

直列抵抗からの付加的な熱ノイズが ADA4177-1/ADA4177-2/ADA4177-4 の熱ノイズ (8 nV/√Hz) に追加されると、6 kΩ の直列抵抗は合計 12 nV/√Hz の熱ノイズを発生するので、熱ノイズが 70 % 増加することになります。図 85 に、追加のソース抵抗のノイズがアンプ入力の合計ノイズにどのように追加されるかを示します。ソース抵抗が大きいほど、合計ノイズが大きくなります。ADA4177-1/ADA4177-2/ADA4177-4 には、過電圧状態用の入力保護回路が内蔵されているため、ノイズのトレードオフを回避できます。

図 85. 等価熱ノイズと合計ソース抵抗の関係

### 外部クランプ・ダイオードを追加する

高精度オペ・アンプには、低オフセット電圧 ( $V_{OS}$ ) および高同相ノイズ除去比 (CMRR) という特性があります。これらの特性により、システム・キャリブレーションが簡素化され、動的誤差が最小限に抑えられます。静電放電 (ESD) が発生する場合にこれらの仕様を維持するため、バイポーラ・オペ・アンプには、通常、内部クランプ・ダイオードと小さい制限抵抗が入力に対して直列接続されています。ただし、これらのコンポーネントは、入力がレール出力を超えるような故障状態には対処できません。このような場合は、一般的にシステム設計者がクランプ・ダイオード (D1 と D2) を直列抵抗 ( $R_{OVP}$ ) とともに追加します (図 86 を参照)。

図 86. 高精度アンプ入力を過電圧状態から保護するための一般的な方法

$V_{IN}$  での信号源が、オペ・アンプの電源電圧よりダイオード 1 つ分の電圧だけ高い値まで駆動されると、 $R_{OVP}$  によって故障電流が制限されます。ショットキー・ダイオードの順方向ニード電圧は 200 mV で、これは代表的な小信号ダイオードよりも低い値です。そのため、すべての過電圧電流は、外部ダイオード (D1 および D2) を通じてシャントされます。代表的なショットキー・ダイオードの逆方向リーケ電流は、逆電圧レベルによって大幅に変化します。このためオペ・アンプの非反転入力がスイングすると、D1 および D2 のリーケ電流が一致せず、差が  $R_{OVP}$  を通過し、電圧降下が発生します。 $R_{OVP}$  での電圧降下は  $V_{OS}$  の変動として現れるので、CMRR 性能が大幅に低下します。ADA4177-1/ADA4177-2/ADA4177-4 には、過電圧状態に対する入力保護回路が内蔵されているため、性能の低下を回避できます。

### 入力保護回路

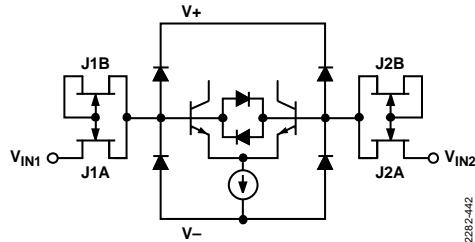

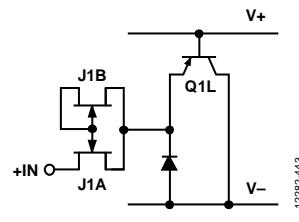

ADA4177-1/ADA4177-2/ADA4177-4 の入力は、一般的な設計手法で見られるトレードオフなしで過電圧保護機能を提供します。入力の概念図を図 87 に示します。

図 87. ADA4177-1/ADA4177-2/ADA4177-4 の入力の概念図

J1A、J1B、J2A、J2B は、従来の保護方法での直列抵抗の代わりとなる空乏モードの接合型電界効果トランジスタ (JFET) です。通常動作時に ADA4177-1/ADA4177-2/ADA4177-4 の入力バイアス電流は、チャンネルをピンチ・オフすることなく J1A および J2A のトランジスタを流れます。最高のノイズ性能を実現するには、J1A と J2A の抵抗 ( $R_{DS(on)}$ ) を低くする必要があります(約 300 Ω)。いずれかの入力がダイオードの値を超えてレールを上回る場合、大電流が J1A または J2A に流れるので、チャンネルがピンチ・オフし、抵抗が増大します。図 88 に、FET チャンネルがピンチした場合の正側の過電圧特性と負側の過電圧特性を示します。

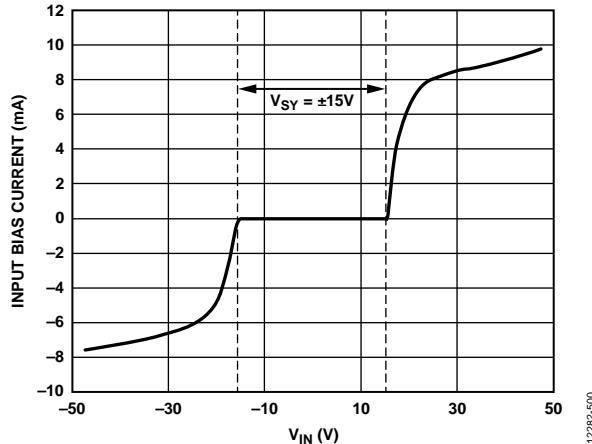

図 88. 正側の過電圧および負側の過電圧印加時の入力バイアス電流、 $V_{SY} = \pm 15$  V、電圧フォロアの構成

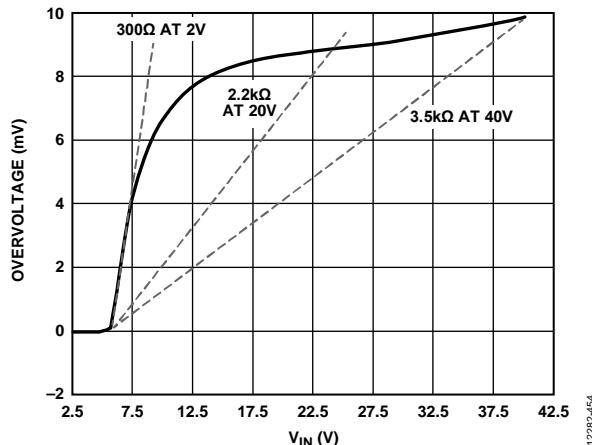

図 89 に、2 V、20 V、40 V の過電圧での測定で示された、JFET の実効抵抗が指数関数的に増加する様子を示します。過電圧が 2 V から 40 V に増加するのに伴い、抵抗が 300 Ω から 3.5 kΩ に増加しています (11 倍)。

図 89. 過電圧と入力電圧 ( $V_{IN}$ ) の関係、電圧フォロアの構成

## 正側電源ピンの過電圧電流の出力を制限する

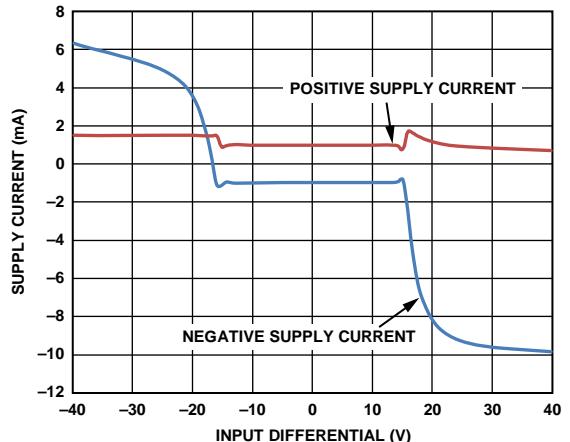

システムの正側電源は 8 mA の大きい過電圧電流をシンクできないため (図 88 を参照)、過電圧時にこの電流を低減して正側レールに流すように設計されています。図 90 に示しているように、Q1L はラテラル PNP トランジスタで、エミッタとベースがクランプ・ダイオードとして機能して過電圧電流を V<sub>+</sub> ピンから V<sub>-</sub> ピンにルーティングするとともに、Q1L の  $\beta$  を介してこの電流を低減します。エミッタ電流が 8 mA の場合、Q1L の  $\beta$  の値は約 8 になるので、正側電源に注入される電流は 1/8 に低減します。

図 90. 過電圧保護回路

図 91 に、入力電圧が電源電圧を超えた場合 (過電圧状態) の正側の電源電流と負側の電源電流を示します。Q1L のコレクタにより電流は V<sub>-</sub> に出力されるため、過電圧時の V<sub>+</sub> 端子の電流は反転しません。

図 91. 電源電流と入力差動電圧の関係、 $V_+ = +15$  V および  $V_- = -15$  V、ユニティ・ゲインで構成された回路

負の過電圧トランジエントが予期される場合は、デバイスに電流が入力されたり、電源電圧を変化させることなく、V<sub>-</sub> を駆動する負側の電圧源がソース電流を処理できるようにする必要があります。

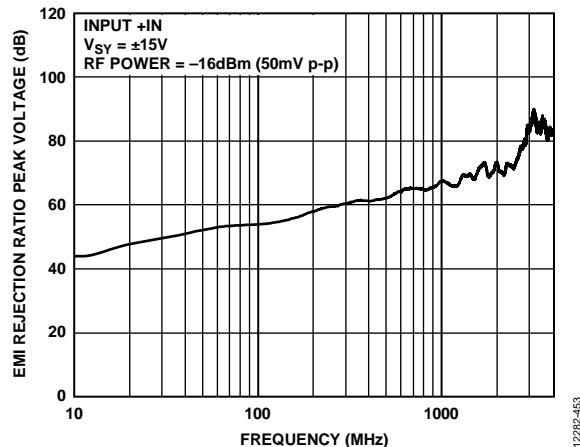

## EMI 保護

ADA4177-1/ADA4177-2/ADA4177-4 の入力は、高周波 EMI からも保護されます。EMI 保護機能を備えていないオペ・アンプでは、オペ・アンプの帯域外の信号が敏感なアンプ入力に入り込み、アンプを通過する際に整流されて DC オフセット上の AC フィードスルーとして現れます。入力フィルタを使用しない場合、これらのオフセットは比較的大きくなります。これらのオフセットは電磁干渉除去比 (EMIRR) と呼ばれます。アンプの EMIRR は次のように定義されます。

$$EMIRR = 20 \times \log \left( \frac{100 \text{ mV}}{\Delta V_{OS}} \right)$$

ここで、

通常、テストに使用するピーク to ピーク入力は 100 mV です。 $\Delta V_{OS}$  は、入力信号によるオペ・アンプのオフセットの変化です。

図 92 に、ADA4177-1/ADA4177-2/ADA4177-4 の入力 EMI 保護を示します。

図 92. EMI 除去比のピーク電圧と周波数の関係

## 自己加熱

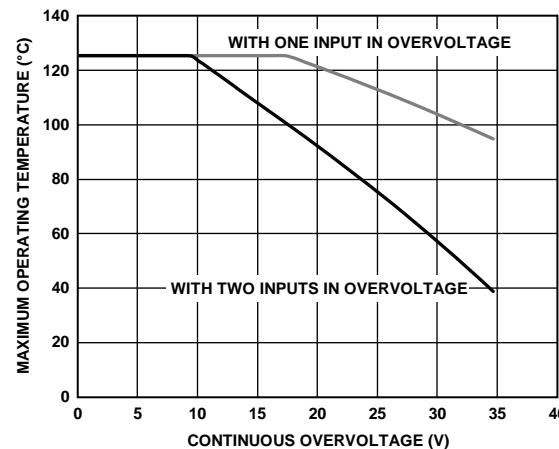

過電圧状態時に ADA4177-1/ADA4177-2/ADA4177-4 は、実装されているパッケージの熱抵抗 ( $\theta_{JA}$ ) に応じて熱を放散するので、ダイが加熱されます。規定の動作ジャンクション温度がデバイス保護温度である 150 °C を超えないようにしてください。長時間にわたって過熱状態にしておくと、一部の動作仕様が、確保された規定値から逸脱することがあります。

図 88 に示しているように ADA4177-1/ADA4177-2/ADA4177-4 の入力は、15 V の過電圧時に約 8 mA シンクされます。この状態で ADA4177-1/ADA4177-2/ADA4177-4 の消費電力は 120 mW です。パッケージの  $\theta_{JA}$  が 100 °C/W の場合、ジャンクション温度はパッケージとジャンクションの周囲温度から約 12 °C 上昇します。このような場合は、動作時の周囲温度を 12 °C 下げて絶対最大動作温度を 113 °C にします (125 °C - 12 °C)。ジャンクション温度が絶対最大ジャンクション温度である 125 °C を超える場合は、入力に直列抵抗を追加して過電圧電流をさらに下げます。図 93 に、 $\theta_{JA} = 150 \text{ }^{\circ}\text{C}/\text{W}$  での最大動作温度と連続過電圧の関係を示します。

図 93. 1 つの入力および 2 つの入力の最大動作温度と連続過電圧の関係 ( $\theta_{JA} = 150 \text{ }^{\circ}\text{C}/\text{W}$ )

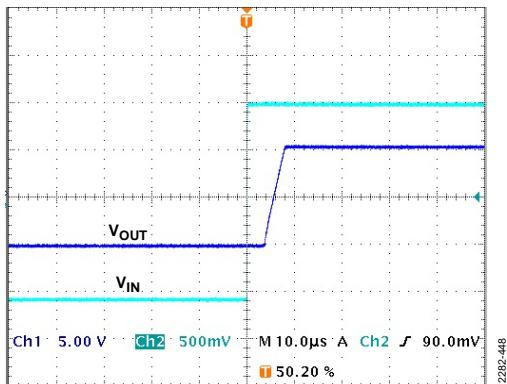

## ADA4177-1/ADA4177-2/ADA4177-4 をコンパレータとして使用する

比較的小さな入力インピーダンスを許容できるのであれば、ADA4177-1/ADA4177-2/ADA4177-4 をコンパレータとして使用することができます。つまり、入力差動ペアはダイオードでクラインプされますが、過電圧保護回路は差動動作に制限を加えます。図 94 に、±15 V 電源での入力電流と入力差動電圧の関係を示します。

図 94. 土 15 V 電源での入力電流と入力差動電圧の関係

図 95 に、ADA4177-1/ADA4177-2/ADA4177-4 を使用したグラウンドを基準とするコンパレータ回路の入出力を示します。電源電圧は ±5 V です。-INx 入力はグラウンドに接続され、正入力は土 1 V にステップされます。正側および負側の回復時間は、約 4 μs です。

図 95.  $\pm 5\text{ V}$  電源および $\pm 1\text{ V}$  入力ステップで ADA4177-1/ADA4177-2/ADA4177-4 をコンパレータとして使用。電圧フォロアの構成

## 出力の位相反転

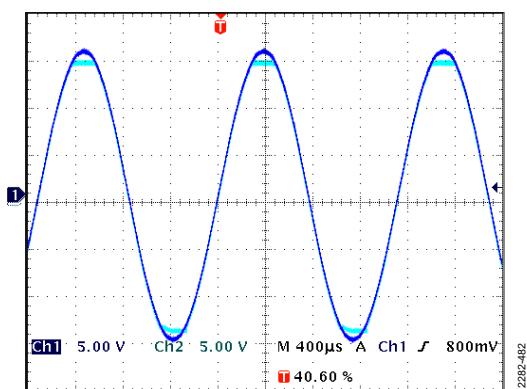

位相反転とは、アンプ伝達関数での極性変化のことを意味します。入力に加えられる電圧が最大コモンモード電圧より大きくなると、多くのオペ・アンプで位相反転が発生します。場合によっては、位相反転によりアンプに恒久的な損傷が生じることがあります。帰還ループでは、システム・ロックアップまたは装置の損傷が発生します。ADA4177-1/ADA4177-2/ADA4177-4 では、入力電圧が電源電圧を超える場合でも、位相反転の問題は発生しません。

図 96. 過電圧状態での位相反転なしの出力

## 適切なプリント回路基板 (PCB) レイアウト

ADA4177-1/ADA4177-2/ADA4177-4 は高精度デバイスです。PCB レベルで最適性能を実現するためには、基板レイアウトのデザインに注意を払う必要があります。

リーク電流が発生しないように、基板表面をクリーンにして湿気をなくす必要があります。表面をコーティングすると、表面の湿気の蓄積が少なくなり、湿度バリアが構成されて、基板上の寄生抵抗が小さくなります。

電源パターンを短くし、電源を適切にバイパスすると、高負荷で AC 信号を駆動する場合などに出力電流変動による電源の乱れが小さくなります。バイパス・コンデンサをデバイス電源ピンのできるだけ近くに接続します。浮遊容量は、アンプの出力と入力において問題になります。カップリングを最小限に抑えるため、信号パターンは電源ラインから少なくとも 5 mm 離してください。

基板上での温度勾配により、ハンダ付けポイントおよび異金属が接触する他のポイントでゼーベック電圧の不一致が発生して熱電圧の誤差が発生します。これらの熱電対効果を小さくするため、熱源による両端での温度上昇が等しくなるように抵抗の向きを調節してください。可能な場合は、入力信号経路に一致する個数とタイプの部品を使用して、熱電対接合の個数とタイプと一致させます。例えば、抵抗値ゼロのようなダミー部品を使用して、反対側の入力経路の実抵抗に一致させます。一致する部品は互いに近づけて配置し、同じ向きに配置する必要があります。同じ長さのリードを使用して、熱伝導の平衡状態を維持させます。PCB 上の発熱源をアンプ入力回路からできるだけ離します。

グラウンド・プレーンの使用も推奨されます。グラウンド・プレーンにより、EMI ノイズが低減し、回路基板全体にわたって温度が一定に保たれます。

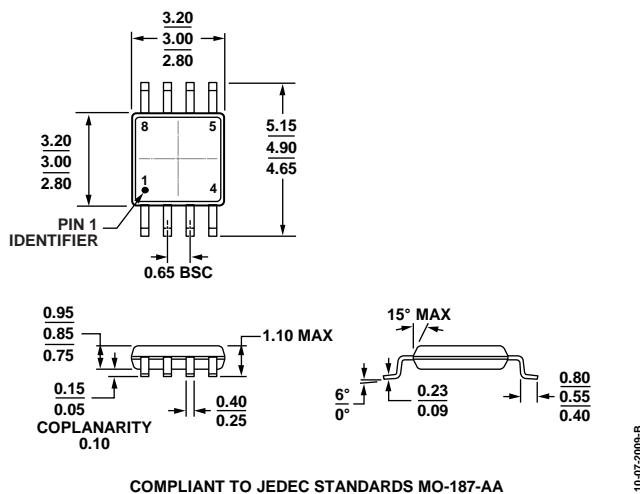

## 外形寸法

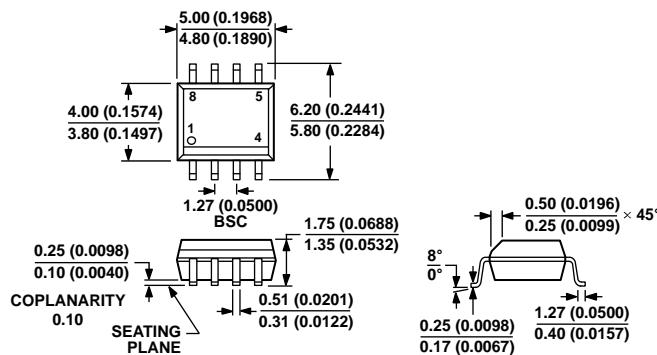

図 97. 8 ピン、ミニ・スモール・アウトライン・パッケージ [MSOP]

(RM-8)

寸法単位: mm

図 98. 8 ピン、標準スモール・アウトライン・パッケージ [SOIC\_N]

ナロー・ボディ (R-8)

寸法単位: mm (括弧内はインチ)

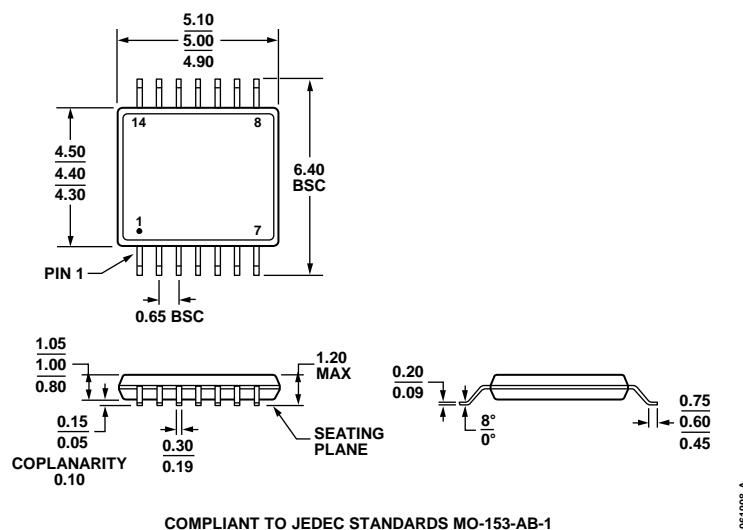

図 99. 14 ピン、薄型シュリンク・スモール・アウトライン・パッケージ [TSSOP]

(RU-14)

寸法単位: mm

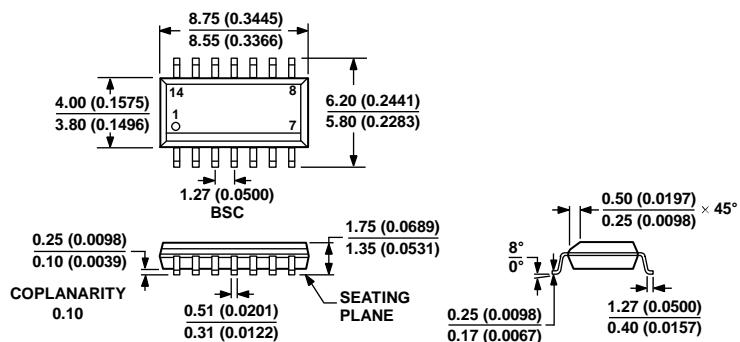

図 100. 14 ピン、標準スモール・アウトライン・パッケージ [SOIC\_N]

ワイド・ボディ (R-14)

寸法単位: mm (括弧内はインチ)

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                               | Package Option | Branding |

|--------------------|-------------------|---------------------------------------------------|----------------|----------|

| ADA4177-1ARMZ      | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]          | RM-8           | A3E      |

| ADA4177-1ARMZ-R7   | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]          | RM-8           | A3E      |

| ADA4177-1ARMZ-RL   | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]          | RM-8           | A3E      |

| ADA4177-1ARZ       | -40°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N]    | R-8            |          |

| ADA4177-1ARZ-R7    | -40°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N]    | R-8            |          |

| ADA4177-1ARZ-RL    | -40°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N]    | R-8            |          |

| ADA4177-2ARMZ      | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]          | RM-8           | A36      |

| ADA4177-2ARMZ-R7   | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]          | RM-8           | A36      |

| ADA4177-2ARMZ-RL   | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]          | RM-8           | A36      |

| ADA4177-2ARZ       | -40°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N]    | R-8            |          |

| ADA4177-2ARZ-R7    | -40°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N]    | R-8            |          |

| ADA4177-2ARZ-RL    | -40°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N]    | R-8            |          |

| ADA4177-4ARUZ      | -40°C to +125°C   | 14-Lead Thin Shrink Small Outline Package [TSSOP] | RU-14          |          |

| ADA4177-4ARUZ-R7   | -40°C to +125°C   | 14-Lead Thin Shrink Small Outline Package [TSSOP] | RU-14          |          |

| ADA4177-4ARUZ-RL   | -40°C to +125°C   | 14-Lead Thin Shrink Small Outline Package [TSSOP] | RU-14          |          |

| ADA4177-4ARZ       | -40°C to +125°C   | 14-Lead Standard Small Outline Package [SOIC_N]   | R-14           |          |

| ADA4177-4ARZ-R7    | -40°C to +125°C   | 14-Lead Standard Small Outline Package [SOIC_N]   | R-14           |          |

| ADA4177-4ARZ-RL    | -40°C to +125°C   | 14-Lead Standard Small Outline Package [SOIC_N]   | R-14           |          |

<sup>1</sup> Z = RoHS 準拠製品。