### 特長

1.8 V のアナログおよびデジタル・コア電源電圧

-3 dB、0 dB、+3 dB、+6 dB ゲインを持つ相関ダブル・サンプラー(CDS)

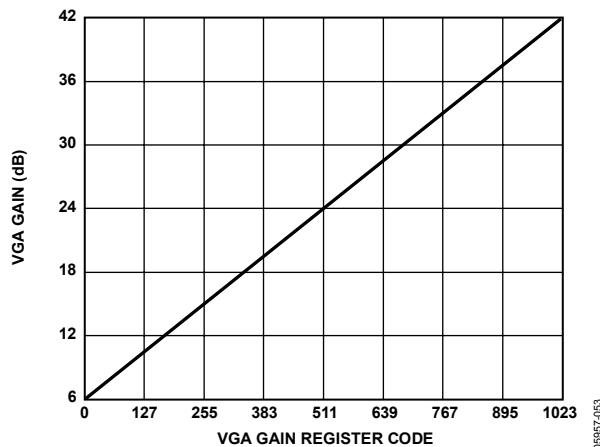

可変ゲイン 6 dB~42 dB の 10 ビット・アンプ(VGA)

65 MHz の 14 ビット A/D コンバータ

可変レベル制御付きの黒レベル・クランプ

必要な全タイミング・ジェネレータを内蔵

65 MHz で 240 ps 分解能の *Precision Timing™* コアを採用

3 V の水平ドライバと RG ドライバを内蔵

シャッタおよびシステム・サポート用の汎用出力(GPO)

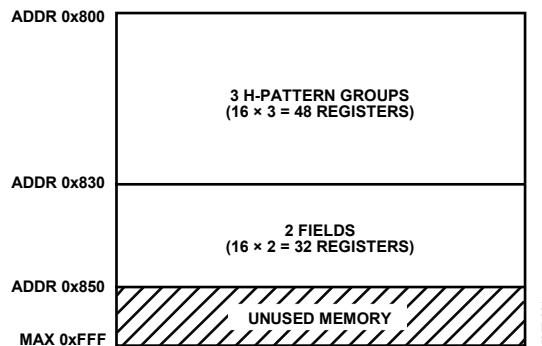

7 mm × 7 mm の 48 ピン LFCSP パッケージを採用

LDO レギュレータ回路を内蔵

### アプリケーション

業務用 HDTV ビデオ・カメラ

業務用/ハイエンド・デジタル・カメラ

放送用カメラ

工業用高速カメラ

### 概要

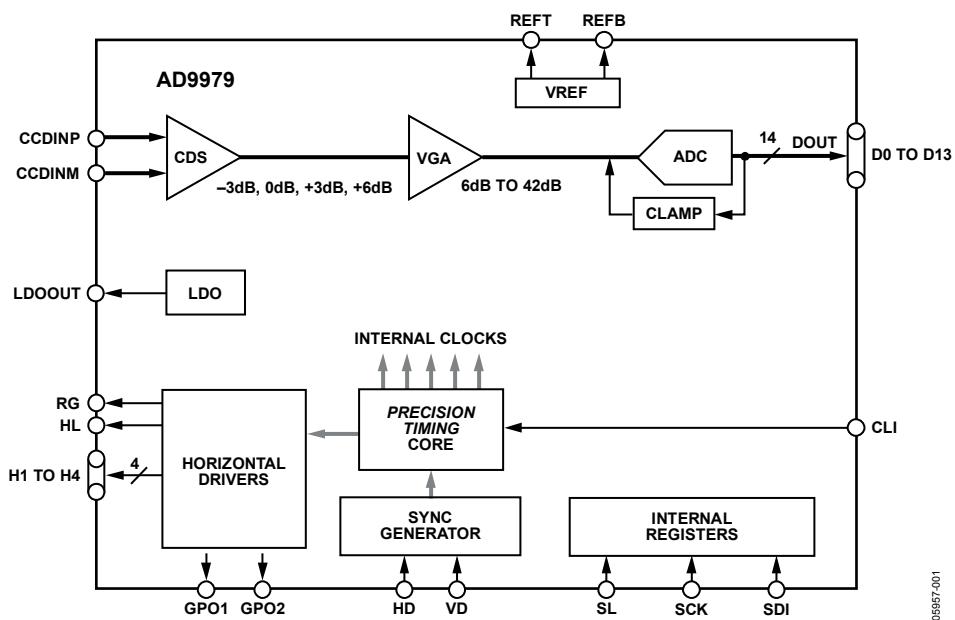

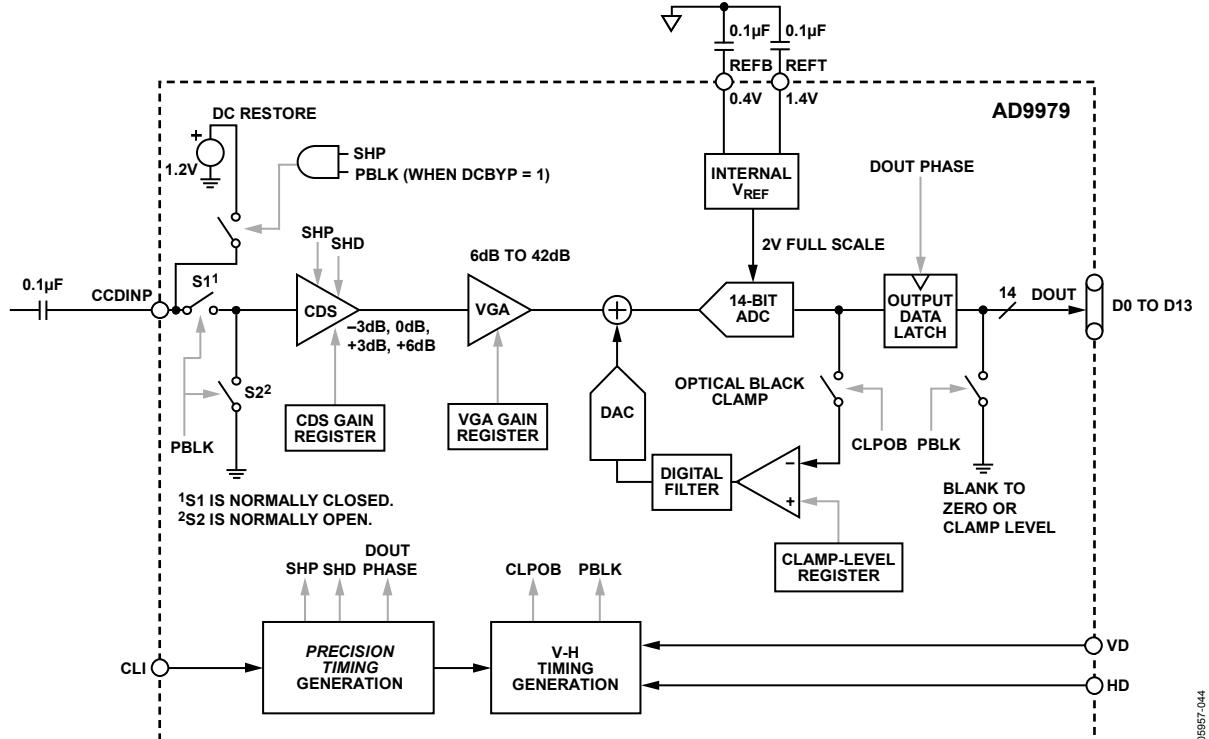

AD9979 は、高速デジタル・ビデオ・カメラ・アプリケーション向けの高集積 CCD 信号プロセッサです。最大 65 MHz のピクセル・レートを持つ AD9979 は、A/D コンバータを持つアナログ・フロント・エンドとプログラマブルなタイミング・ドライバから構成されています。Precision Timing コアの使用により、高速クロックの調整が 65 MHz 動作時に 240 ps の分解能で可能です。

アナログ・フロント・エンドには、黒レベル・クランプ機能、CDS、VGA、65 MSPS の 14 ビット A/D コンバータ(ADC)が内蔵されています。タイミング・ドライバは、RG、HL、H1~H4 の高速 CCD クロック・ドライバを提供します。動作は、3 線式シリアル・インターフェースを介して設定します。

AD9979 は省スペース 7 mm × 7 mm の 48 ピン LFCSP パッケージを採用し、-25°C~+85°C の動作温度範囲で仕様が規定されています。

### 機能ブロック図

図 1.

05957-001

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。

※日本語データシートは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2007-2009 Analog Devices, Inc. All rights reserved.

## 目次

|                             |    |                         |    |

|-----------------------------|----|-------------------------|----|

| 特長                          | 1  | フィールド全体—H パターンの組み合わせ    | 23 |

| アプリケーション                    | 1  | モード・レジスタ                | 24 |

| 概要                          | 1  | 水平タイミング・シーケンスの例         | 26 |

| 機能ブロック図                     | 1  | 汎用出力(GPO)               | 27 |

| 改訂履歴                        | 2  | GP ルックアップ・テーブル(LUT)     | 30 |

| 仕様                          | 3  | アナログ・フロントエンドの説明と動作      | 31 |

| タイミング仕様                     | 4  | アプリケーション情報              | 35 |

| デジタル仕様                      | 5  | 推奨パワーアップ・シーケンス          | 35 |

| アナログ仕様                      | 6  | スタンバイ・モード動作             | 37 |

| 絶対最大定格                      | 7  | CLI 周波数の変更              | 37 |

| 熱抵抗                         | 7  | 回路構成                    | 38 |

| ESD の注意                     | 7  | グラウンド接続とデカップリングの推奨事項    | 38 |

| ピン配置およびピン機能説明               | 8  | 3 線式シリアル・インターフェースのタイミング | 40 |

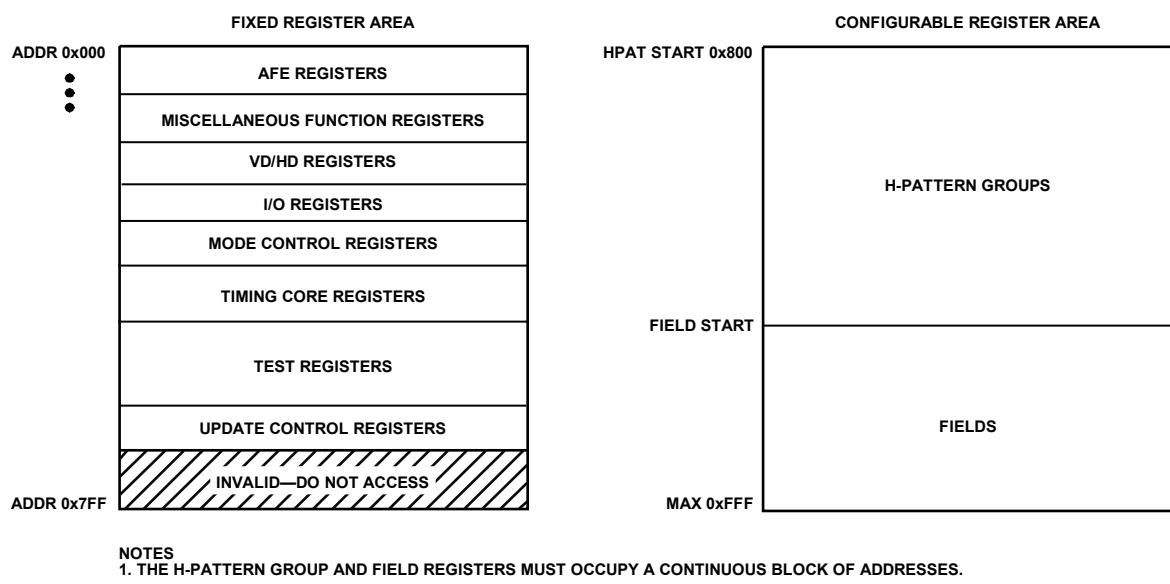

| 代表的な性能特性                    | 10 | 内部レジスタのレイアウト            | 41 |

| 等価入出力回路                     | 11 | 新しいレジスタ値の更新             | 42 |

| 動作原理                        | 12 | 全レジスタの一覧                | 43 |

| プログラマブルなタイミングの発生            | 13 | 外形寸法                    | 54 |

| Precision Timing 高速タイミング・コア | 13 | オーダー・ガイド                | 54 |

| 水平クランピングとブランкиング            | 16 |                         |    |

## 改訂履歴

### 6/09—Rev. Sp0 to Rev. A

|                                                                                                             |    |

|-------------------------------------------------------------------------------------------------------------|----|

| Changes to Table 1                                                                                          | 3  |

| Changes to Table 2                                                                                          | 4  |

| Changes to Table 3                                                                                          | 5  |

| Changes to Figure 2                                                                                         | 6  |

| Changes to Table 5 and Thermal Resistance Section                                                           | 7  |

| Changes to Figure 3 and Table 7                                                                             | 8  |

| Changes to Figure 22                                                                                        | 16 |

| Added GP_LINE_MODE Name, Table 16                                                                           | 28 |

| Changes to Figure 42                                                                                        | 31 |

| Added Example Register Settings for Power-Up Section                                                        | 36 |

| Changes to Additional Restriction Section                                                                   | 37 |

| Changes to Table 22, 3 V System Compatibility Section, and Grounding and Decoupling Recommendations Section | 38 |

| Changes to Table 33                                                                                         | 51 |

| Changes to Table 34                                                                                         | 52 |

| Added Exposed Paddle Notation to Outline Dimensions                                                         | 54 |

### 2/07—Revision Sp0: Initial Version

# 仕様

表 1.

| Parameter                                                | Min | Typ  | Max  | Unit |

|----------------------------------------------------------|-----|------|------|------|

| TEMPERATURE RANGE                                        |     |      |      |      |

| Operating                                                | -25 |      | +85  | °C   |

| Storage                                                  | -65 |      | +150 | °C   |

| POWER SUPPLY VOLTAGE                                     |     |      |      |      |

| AVDD (AFE, Timing Core)                                  | 1.6 | 1.8  | 2.0  | V    |

| RGVDD (RG, HL Drivers)                                   | 2.7 | 3.3  | 3.6  | V    |

| HVDD (H1 to H4 Drivers)                                  | 2.7 | 3.3  | 3.6  | V    |

| DVDD (Internal Digital Supply)                           | 1.6 | 1.8  | 2.0  | V    |

| DRVDD (Parallel Data Output Drivers)                     | 1.6 | 3.0  | 3.6  | V    |

| IOVDD (I/O Supply Without the Use of LDO)                | 1.6 | 1.8  | 3.6  | V    |

| POWER SUPPLY CURRENTS—65 MHz OPERATION                   |     |      |      |      |

| AVDD (1.8 V)                                             | 48  |      |      | mA   |

| RGVDD (3.3 V, 20 pF RG Load, 20 pF HL Load)              | 8   |      |      | mA   |

| HVDD <sup>1</sup> (3.3 V, 200 pF Total Load on H1 to H4) | 40  |      |      | mA   |

| DVDD (1.8 V)                                             | 13  |      |      | mA   |

| DRVDD (3.0 V)                                            | 4   |      |      | mA   |

| IOVDD (1.8 V)                                            | 2   |      |      | mA   |

| POWER SUPPLY CURRENTS—STANDBY MODE OPERATION             |     |      |      |      |

| Reference Standby                                        | 10  |      |      | mA   |

| Total Shutdown                                           | 0.5 |      |      | mA   |

| LDO <sup>2</sup>                                         |     |      |      |      |

| IOVDD (I/O Supply When Using LDO)                        | 2.5 | 3.0  | 3.6  | V    |

| Output Voltage                                           | 1.8 | 1.85 | 1.9  | V    |

| Output Current                                           | 60  |      |      | mA   |

| CLOCK RATE (CLI)                                         | 10  | 65   |      | MHz  |

<sup>1</sup> HVDD (または RGVDD) 電源の合計消費電力は次式で近似できます。

$$HVDD \text{ の合計消費電力} = [C_{LOAD} \times HVDD \times \text{レーザル周波数}] \times HVDD$$

ここで、 $C_{LOAD}$  は全 H 出力から見た合計容量。

容量負荷および/または HVDD 電源を削減すると、消費電力が小さくなります。

<sup>2</sup> LDO を使って AVDD と DVDD のみに電源を供給できます。

## タイミング仕様

特に指定がない限り、 $C_L = 20 \text{ pF}$ 、 $AVDD = DVDD = 1.8 \text{ V}$ 、 $f_{CLI} = 65 \text{ MHz}$ 。

表 2.

| Parameter                                                                                     | Symbol        | Min                    | Typ | Max                    | Unit   | Comments      |

|-----------------------------------------------------------------------------------------------|---------------|------------------------|-----|------------------------|--------|---------------|

| MASTER CLOCK (CLI)                                                                            |               |                        |     |                        |        |               |

| CLI Clock Period                                                                              | $t_{CONV}$    | 15.38                  |     |                        | ns     |               |

| CLI High/Low Pulse Width                                                                      | $t_{ADC}$     | 6.9                    | 7.7 | 8.9                    | ns     |               |

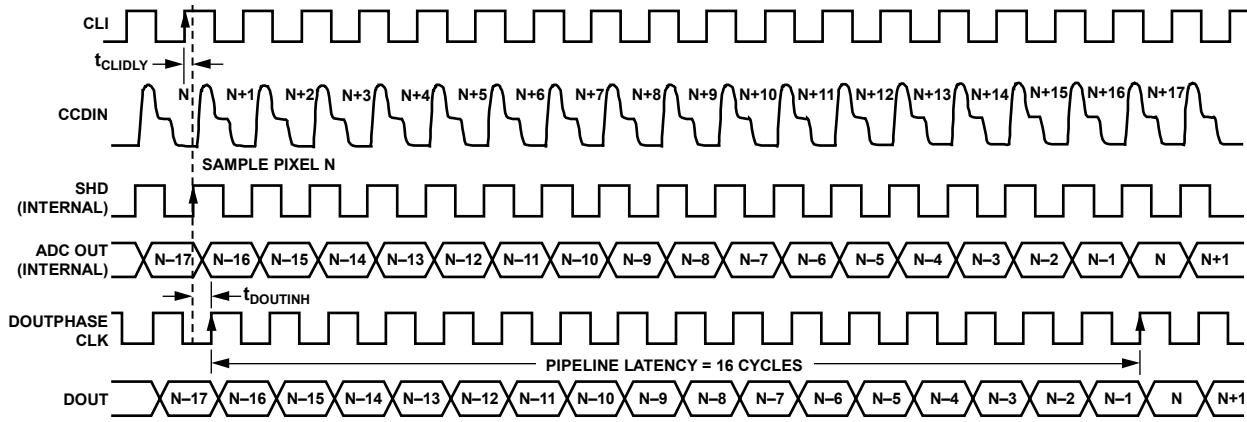

| Delay from CLI Rising Edge to Internal Pixel Position 0                                       | $t_{CLIDLY}$  |                        | 5   |                        | ns     |               |

| AFE                                                                                           |               |                        |     |                        |        |               |

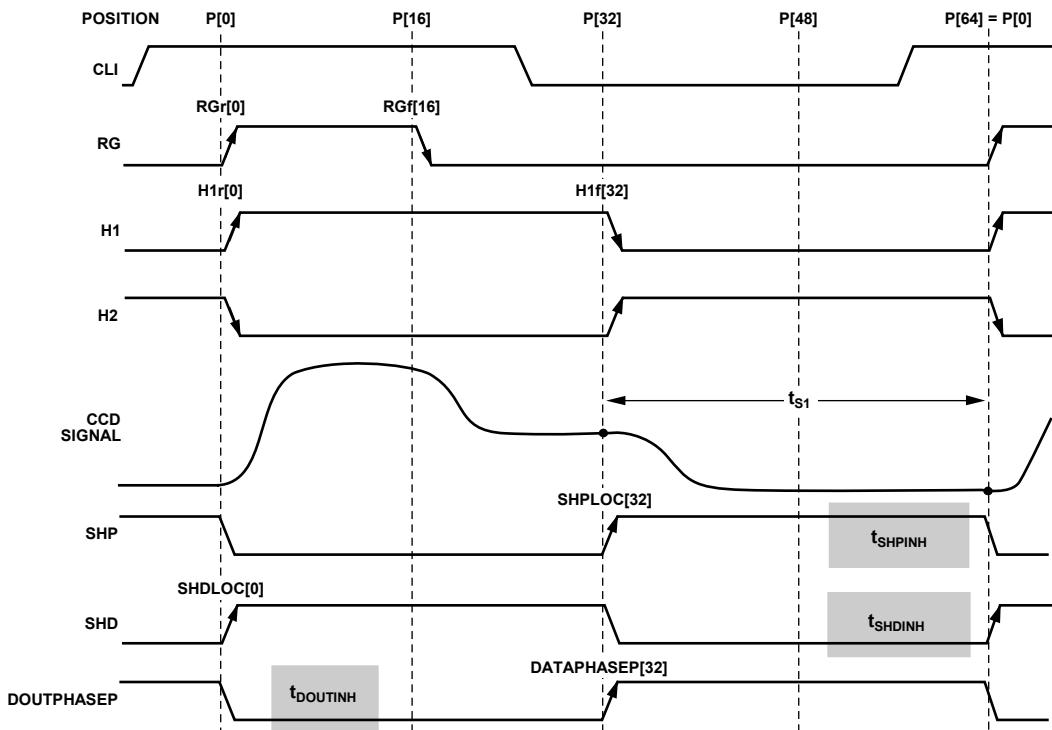

| SHP Rising Edge to SHD Rising Edge                                                            | $t_{S1}$      | 6.9                    | 7.7 | 8.5                    | ns     | See Figure 19 |

| AFE Pipeline Delay                                                                            |               |                        | 16  |                        | Cycles | See Figure 20 |

| CLPOB Pulse Width (Programmable) <sup>1</sup>                                                 | $t_{COB}$     | 2                      | 20  |                        | Pixels |               |

| HD Pulse Width                                                                                |               | $t_{CONV}$             |     |                        | ns     |               |

| VD Pulse Width                                                                                |               | 1 HD period            |     |                        | ns     |               |

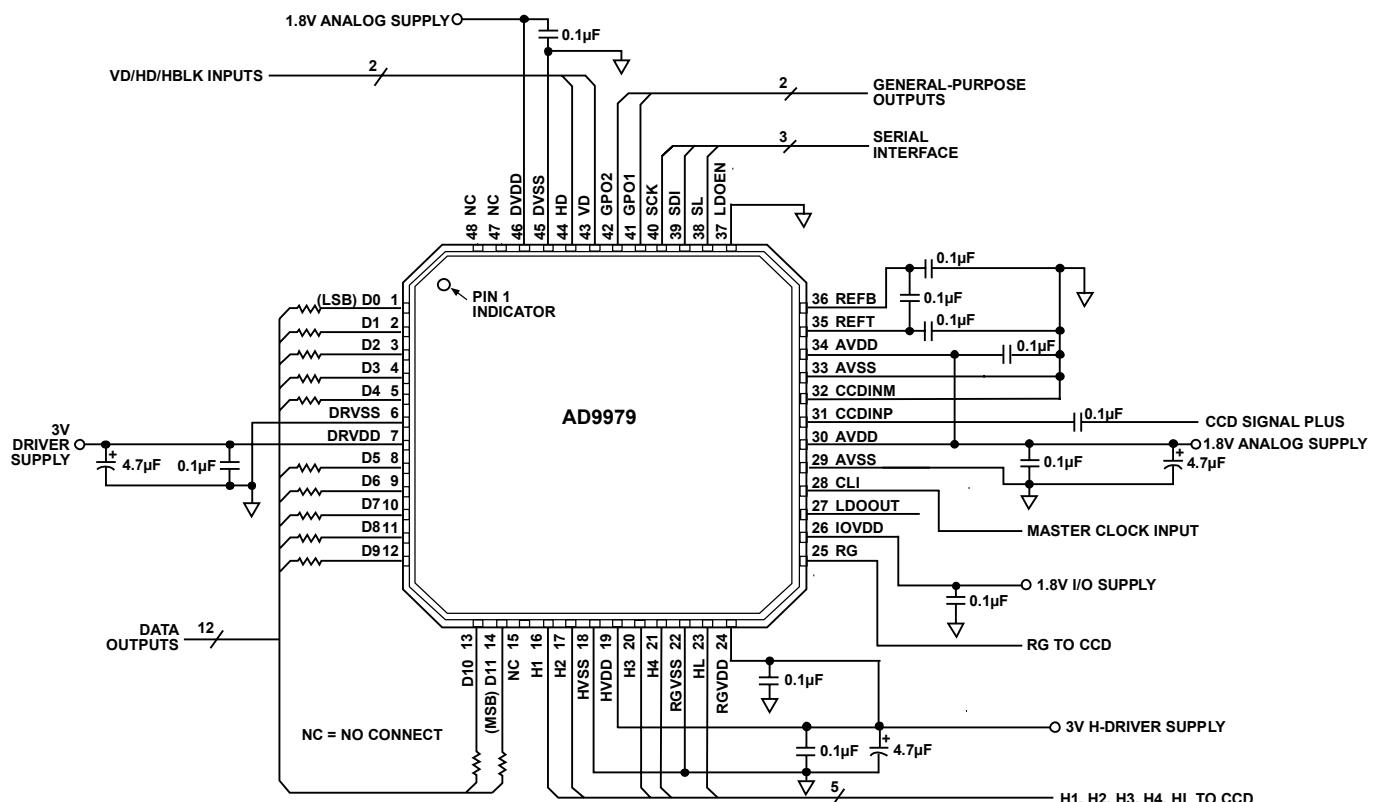

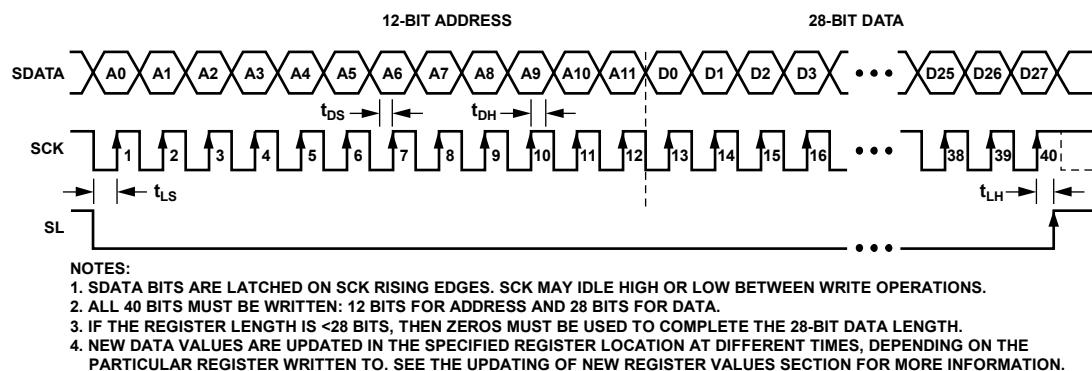

| SERIAL INTERFACE                                                                              |               |                        |     |                        |        |               |

| Maximum SCK Frequency                                                                         | $f_{SCLK}$    | 40                     |     |                        | MHz    |               |

| SL to SCK Setup Time                                                                          | $t_{LS}$      | 10                     |     |                        | ns     |               |

| SCK to SL Hold Time                                                                           | $t_{LH}$      | 10                     |     |                        | ns     |               |

| SDATA Valid to SCK Rising Edge Setup                                                          | $t_{DS}$      | 10                     |     |                        | ns     |               |

| SCK Falling Edge to SDATA Valid Hold                                                          | $t_{DH}$      | 10                     |     |                        | ns     |               |

| H-COUNTER RESET SPECIFICATIONS                                                                |               |                        |     |                        |        |               |

| HD Pulse Width                                                                                |               | $t_{CONV}$             |     |                        | ns     |               |

| VD Pulse Width                                                                                |               | 1 HD period            |     |                        | ns     |               |

| VD Falling Edge to HD Falling Edge                                                            | $t_{VDHD}$    | 0                      |     | VD period - $t_{CONV}$ | ns     |               |

| HD Falling Edge to CLI Rising Edge                                                            | $t_{HDCLI}$   | 3                      |     | $t_{CONV} - 2$         | ns     |               |

| CLI Rising Edge to SHPLOC (Internal Sample Edge)                                              | $t_{CLISHP}$  | 3                      |     | $t_{CONV} - 2$         | ns     |               |

| TIMING CORE SETTING RESTRICTIONS                                                              |               |                        |     |                        |        |               |

| Inhibited Region for SHP Edge Location <sup>2</sup> (See Figure 19)                           | $t_{SHPINH}$  | 50                     |     | 64/0                   |        | Edge location |

| Inhibited Region for SHP or SHD with Respect to H-Clocks(See Figure 19) <sup>3, 4, 5, 6</sup> |               |                        |     |                        |        |               |

| RETIME = 0, MASK = 0                                                                          | $t_{SHDINH}$  | $H \times NEGLOC - 15$ |     | $H \times NEGLOC - 0$  |        | Edge location |

| RETIME = 0, MASK = 1                                                                          | $t_{SHDINH}$  | $H \times POSLOC - 15$ |     | $H \times POSLOC - 0$  |        | Edge location |

| RETIME = 1, MASK = 0                                                                          | $t_{SHPINH}$  | $H \times NEGLOC - 15$ |     | $H \times NEGLOC - 0$  |        | Edge location |

| RETIME = 1, MASK = 1                                                                          | $t_{SHPINH}$  | $H \times POSLOC - 15$ |     | $H \times POSLOC - 0$  |        | Edge location |

| Inhibited Region for DOUTPHASE Edge Location (See Figure 19)                                  | $t_{DOUTINH}$ | $SHDLOC + 0$           |     | $SHDLOC + 15$          |        | Edge location |

<sup>1</sup> 最小 CLPOB パルス幅は理論的動作の場合。良いクランプ性能を得るためにには、これより幅の広いパルスの使用が推奨されます。

<sup>2</sup> スレーブ動作モードの場合に適用。H カウンタ・リセットが正常に動作するためには、SHP のインヒビット領域が  $t_{CLISHP}$  のタイミング条件を満たす必要があります。

<sup>3</sup> 0x34[2:0] HxBLKRETIME ビットをイネーブルすると、SHD ロケーションのインヒビット領域が SHP ロケーションのインヒビット領域に変わります。

<sup>4</sup> シーケンス・レジスタ 0x09[23:21]の HBLK マスキング・レジスタに 0 を設定すると、H エッジ・リファレンスが  $H \times NEGLOC$  になります。

<sup>5</sup> SHP/SHD インヒビット領域を持つ H クロック信号は、HCLK モード(モード 1 = H1, モード 2 = H1, H2、モード 3 = H1, H3)に依存します。

<sup>6</sup> これらの仕様は、H1POL、H2POL、RGPOL、HLPOL のすべてに 1 を設定した場合(デフォルト設定)に適用されます。

## デジタル仕様

特に指定がない限り、 $IOVDD = 1.6 \text{ V} \sim 3.6 \text{ V}$ 、 $RGVDD = HVDD = 2.7 \text{ V} \sim 3.6 \text{ V}$ 、 $C_L = 20 \text{ pF}$ 、 $t_{MIN} \sim t_{MAX}$ 。

表 3.

| Parameter                                    | Symbol      | Min           | Typ | Max           | Unit          | Test Conditions/<br>Comments |  |

|----------------------------------------------|-------------|---------------|-----|---------------|---------------|------------------------------|--|

| LOGIC INPUTS                                 |             |               |     |               |               |                              |  |

| High Level Input Voltage                     | $V_{IH}$    | IOVDD – 0.6   |     | 0.6           | V             |                              |  |

| Low Level Input Voltage                      | $V_{IL}$    |               |     |               | V             |                              |  |

| High Level Input Current                     | $I_{IH}$    | 10            |     | 10            | $\mu\text{A}$ |                              |  |

| Low Level Input Current                      | $I_{IL}$    |               |     |               | $\mu\text{A}$ |                              |  |

| Input Capacitance                            | $C_{IN}$    | 10            |     | 10            | pF            |                              |  |

| LOGIC OUTPUTS                                |             |               |     |               |               |                              |  |

| High Level Output Voltage                    | $V_{OH}$    | IOVDD – 0.5   |     | 0.5           | V             | $I_{OH} = 2 \text{ mA}$      |  |

| Low Level Output Voltage                     | $V_{OL}$    |               |     |               | V             | $I_{OL} = 2 \text{ mA}$      |  |

| CLI INPUT (CLI_BIAS = 0)                     |             |               |     |               |               |                              |  |

| High Level Input Voltage                     | $V_{IHCLI}$ | IOVDD/2 + 0.5 |     | IOVDD/2 – 0.5 | V             |                              |  |

| Low Level Input Voltage                      | $V_{ILCLI}$ |               |     |               | V             |                              |  |

| H-DRIVER OUTPUTS                             |             |               |     |               |               |                              |  |

| High Level Output Voltage at Maximum Current | $V_{OH}$    | HVDD – 0.5    |     | 0.5           | V             |                              |  |

| Low Level Output Voltage at Maximum Current  | $V_{OL}$    |               |     |               | V             |                              |  |

| Maximum Output Current (Programmable)        |             | 30            |     | 30            | mA            |                              |  |

| Maximum Load Capacitance                     |             | 100           |     |               | pF            |                              |  |

## アナログ仕様

特に指定がない限り、AVDD = 1.8 V、f<sub>CLL</sub> = 65 MHz、代表値タイミング仕様、t<sub>MIN</sub>~t<sub>MAX</sub>。

表 4.

| Parameter                               | Min  | Typ        | Max  | Unit    | Test Conditions/Comments                   |

|-----------------------------------------|------|------------|------|---------|--------------------------------------------|

| CDS <sup>1</sup>                        |      |            |      |         |                                            |

| Allowable CCD Reset Transient           |      | 0.5        | 0.8  | V       |                                            |

| CDS Gain Accuracy                       |      |            |      |         |                                            |

| -3.0 dB CDS Gain                        | -3.7 | -3.2       | -2.7 | dB      |                                            |

| 0 dB CDS Gain (Default)                 | -0.9 | -0.4       | +0.1 | dB      |                                            |

| +3 dB CDS Gain                          | +1.9 | +2.4       | +2.9 | dB      |                                            |

| +6 dB CDS Gain                          | +4.3 | +4.8       | +5.3 | dB      |                                            |

| Maximum Input Voltage                   |      |            |      |         |                                            |

| -3 dB CDS Gain                          |      | 1.4        |      | V p-p   | VGA gain = 6.3 dB, Code 15 (default value) |

| 0 dB CDS Gain (Default)                 |      | 1.0        |      | V p-p   |                                            |

| +3 dB CDS Gain                          |      | 0.7        |      | V p-p   |                                            |

| +6 dB CDS Gain                          |      | 0.5        |      | V p-p   |                                            |

| Allowable Optical Black Pixel Amplitude |      |            |      |         |                                            |

| 0 dB CDS Gain (Default)                 | -100 |            | +200 | mV      |                                            |

| +6 dB CDS Gain                          | -50  |            | +100 | mV      |                                            |

| VARIABLE GAIN AMPLIFIER (VGA)           |      |            |      |         |                                            |

| Gain Control Resolution                 |      | 1024       |      | Steps   |                                            |

| Gain Monotonicity                       |      | Guaranteed |      |         |                                            |

| Low Gain Setting                        |      | 6          |      | dB      | VGA Code 15 (default)                      |

| Maximum Gain Setting                    |      | 42         |      | dB      | VGA Code 1023                              |

| BLACK LEVEL CLAMP                       |      |            |      |         |                                            |

| Clamp Level Resolution                  |      | 1024       |      | Steps   |                                            |

| Minimum Clamp Level (Code 0)            |      | 0          |      | LSB     | Measured at ADC output                     |

| Maximum Clamp Level (Code 1023)         |      | 1023       |      | LSB     | Measured at ADC output                     |

| ANALOG-TO-DIGITAL CONVERTER (ADC)       |      |            |      |         |                                            |

| Resolution                              | 14   |            |      | Bits    |                                            |

| Differential Nonlinearity (DNL)         | -1.0 | ± 0.5      | +1.2 | LSB     |                                            |

| No Missing Codes                        |      | Guaranteed |      |         |                                            |

| Integral Nonlinearity (INL)             |      | 5          | 16   | LSB     |                                            |

| Full-Scale Input Voltage                |      | 2.0        |      | V       |                                            |

| VOLTAGE REFERENCE                       |      |            |      |         |                                            |

| Reference Top Voltage (REFT)            |      | 1.4        |      | V       |                                            |

| Reference Bottom Voltage (REFB)         |      | 0.4        |      | V       |                                            |

| SYSTEM PERFORMANCE                      |      |            |      |         |                                            |

| VGA Gain Accuracy                       |      |            |      |         | Specifications include entire signal chain |

| Low Gain (Code 15)                      | 5.1  | 5.6        | 6.1  | dB      | 0 dB CDS gain (default)                    |

| Maximum Gain (Code 1023)                | 41.3 | 41.8       | 42.3 | dB      | Gain = (0.0359 × code) + 5.1 dB            |

| Peak Nonlinearity, 500 mV Input Signal  |      | 0.1        | 0.4  | %       | 12 dB total gain applied                   |

| Total Output Noise                      |      | 2          |      | LSB rms | AC grounded input, 6 dB gain applied       |

| Power Supply Rejection (PSR)            |      | 45         |      | dB      | Measured with step change on supply        |

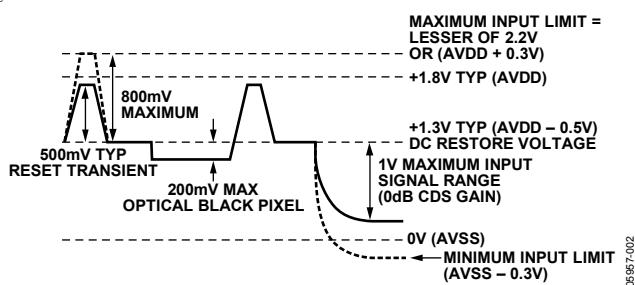

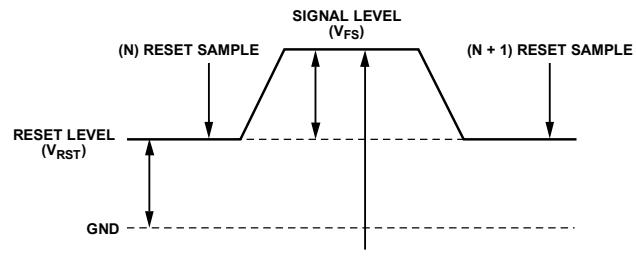

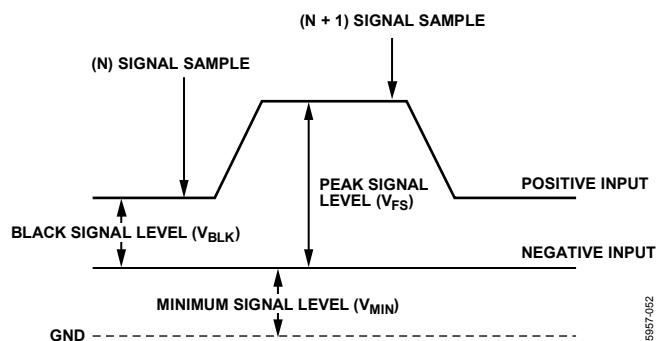

<sup>1</sup> 入力信号特性は図 2 のように定義します。

図 2. 入力信号特性

# 絶対最大定格

表 5.

| Parameter                  | With Respect To | Rating                  |

|----------------------------|-----------------|-------------------------|

| AVDD                       | AVSS            | -0.3 V to +2.2 V        |

| DVDD                       | DVSS            | -0.3 V to +2.2 V        |

| DRVDD                      | DRVSS           | -0.3 V to +3.9 V        |

| IOVDD                      | DVSS            | -0.3 V to +3.9 V        |

| HVDD                       | HVSS            | -0.3 V to +3.9 V        |

| RGVDD                      | RGVSS           | -0.3 V to +3.9 V        |

| Any VSS                    | Any VSS         | -0.3 V to +0.3 V        |

| RG Output                  | RGVSS           | -0.3 V to RGVDD + 0.3 V |

| H1 to H4, HL Output        | HVSS            | -0.3 V to HVDD + 0.3 V  |

| SCK, SL, SDI               | DVSS            | -0.3 V to IOVDD + 0.3 V |

| REFT, REFB, CCDINM, CCDINP | AVSS            | -0.2 V to AVDD + 0.2 V  |

| Junction Temperature       |                 | 150°C                   |

| Lead Temperature (10 sec)  |                 | 350°C                   |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

## 熱抵抗

$\theta_{JA}$  は、4層プリント回路ボード(PCB)を使い、露出パドルをボードにハンダ付けして測定。

表 6.

| Package Type               | $\theta_{JA}$ | Unit |

|----------------------------|---------------|------|

| 48-Lead, 7 mm × 7 mm LFCSP | 25.8          | °C/W |

## ESD の注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

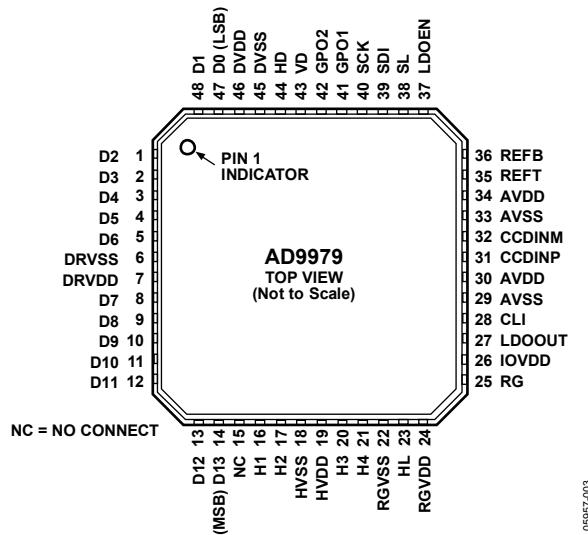

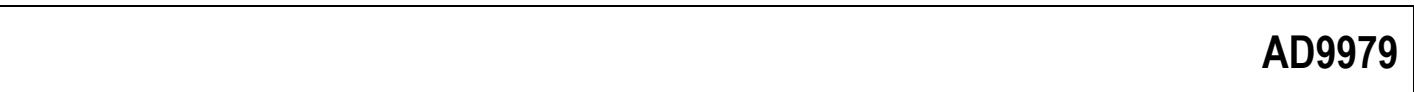

## ピン配置およびピン機能説明

図 3. ピン配置

表 7. ピン機能の説明

| ピン番号 | 記号        | タイプ <sup>1</sup> | 説明                                       |

|------|-----------|------------------|------------------------------------------|

| 1    | D2        | DO               | データ出力                                    |

| 2    | D3        | DO               | データ出力                                    |

| 3    | D4        | DO               | データ出力                                    |

| 4    | D5        | DO               | データ出力                                    |

| 5    | D6        | DO               | データ出力                                    |

| 6    | DRVSS     | P                | デジタル・ドライバのグラウンド                          |

| 7    | DRVDD     | P                | デジタル・ドライバの電源(1.8 V または 3 V)              |

| 8    | D7        | DO               | データ出力                                    |

| 9    | D8        | DO               | データ出力                                    |

| 10   | D9        | DO               | データ出力                                    |

| 11   | D10       | DO               | データ出力                                    |

| 12   | D11       | DO               | データ出力                                    |

| 13   | D12       | DO               | データ出力                                    |

| 14   | D13 (MSB) | DO               | データ出力                                    |

| 15   | NC        |                  | 未使用                                      |

| 16   | H1        | DO               | CCD 水平クロック 1                             |

| 17   | H2        | DO               | CCD 水平クロック 2                             |

| 18   | HVSS      | P                | H1~H4 ドライバのグラウンド                         |

| 19   | HVDD      | P                | H1~H4 ドライバの電源(3 V)                       |

| 20   | H3        | DO               | CCD 水平クロック 3                             |

| 21   | H4        | DO               | CCD 水平クロック 4                             |

| 22   | RG/VSS    | P                | RG ドライバ・グラウンド                            |

| 23   | HL        | DO               | CCD 最終水平クロック                             |

| 24   | RGVDD     | P                | RG ドライバ電源(3 V)                           |

| 25   | RG        | DO               | CCD リセット・ゲート・クロック                        |

| 26   | IOVDD     | P                | デジタル I/O 電源(1.8 V または 3 V)/LDO 入力電圧(3 V) |

| ピン番号 | 記号       | タイプ <sup>1</sup> | 説明                                               |

|------|----------|------------------|--------------------------------------------------|

| 27   | LDOOUT   | P                | LDO 出力電圧(1.8 V)                                  |

| 28   | CLI      | DI               | マスター・クロック入力                                      |

| 29   | AVSS     | P                | AFE 用アナログ・グラウンド                                  |

| 30   | AVDD     | P                | AFE 用アナログ電源 (1.8 V)                              |

| 31   | CCDINP   | AI               | CCD 信号正の入力                                       |

| 32   | CCDINM   | AI               | CCD 信号負の入力; 通常 AVSS へ接続                          |

| 33   | AVSS     | P                | AFE 用アナログ・グラウンド                                  |

| 34   | AVDD     | P                | AFE 用アナログ電源 (1.8 V)                              |

| 35   | REFT     | AO               | リファレンス電圧上側デカップリング(1.0 $\mu$ F で AVSS へデカップリング)   |

| 36   | REFB     | AO               | リファレンス電圧下側デカップリング(1.0 $\mu$ F で AVSS へデカップリング)   |

| 37   | LDOEN    | DI               | LDO 出力イネーブル; 3 V = LDO をイネーブル、GND = LDO をディスエーブル |

| 38   | SL       | DI               | 3 線式シリアル・ロード                                     |

| 39   | SDI      | DI               | 3 線式シリアル・データ入力                                   |

| 40   | SCK      | DI               | 3 線式シリアル・クロック                                    |

| 41   | GPO1     | DIO              | 汎用入力/出力 1                                        |

| 42   | GPO2     | DIO              | 汎用入力/出力 2                                        |

| 43   | VD       | DI               | 垂直同期パルス                                          |

| 44   | HD       | DI               | 水平同期パルス                                          |

| 45   | DVSS     | P                | デジタル・グラウンド                                       |

| 46   | DVDD     | P                | デジタル電源(1.8 V)                                    |

| 47   | D0 (LSB) | DO               | データ出力                                            |

| 48   | D1       | DO               | データ出力                                            |

|      | EPAD     |                  | 露出パッドは GND へ接続する必要があります。                         |

<sup>1</sup> AI = アナログ入力、AO = アナログ出力、DI = デジタル入力、DO = デジタル出力、DIO = デジタル入力/出力、P = 電源。

## 代表的な性能特性

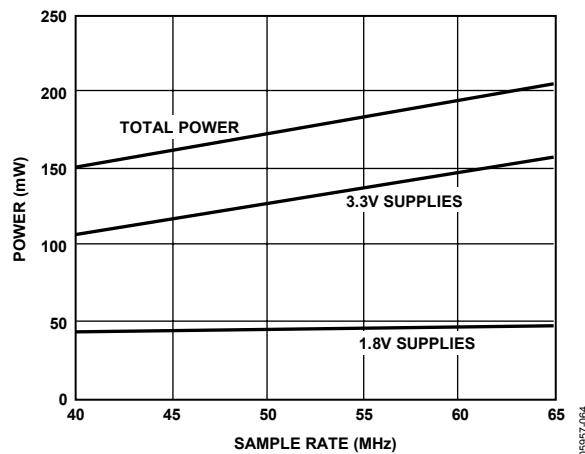

図 4.消費電力対サンプル・レート

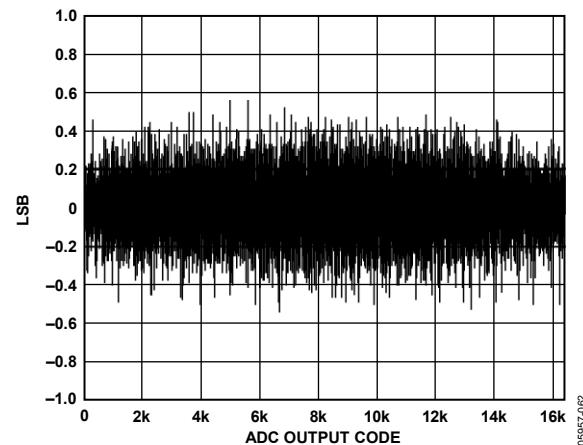

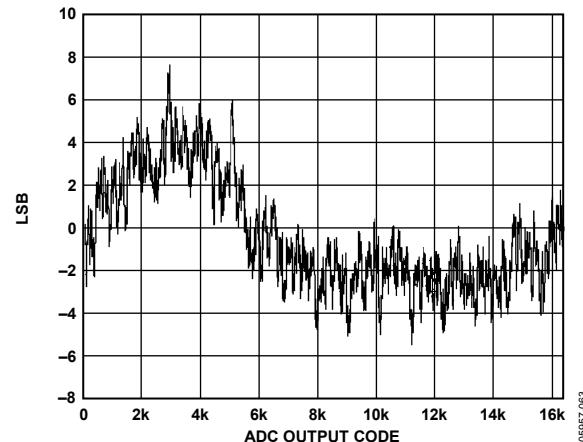

図 6.微分非直線性(DNL)

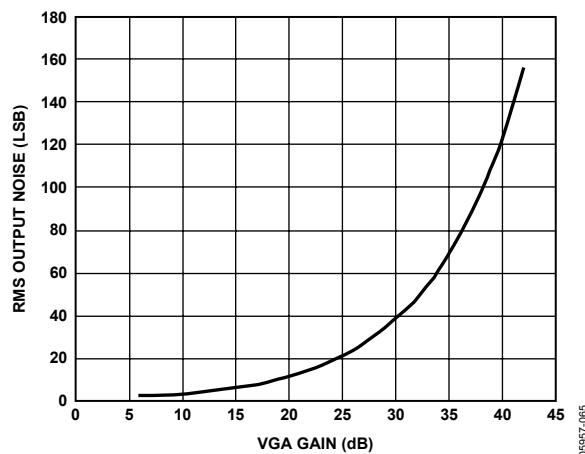

図 5.RMS 出力ノイズ対 VGA ゲイン

図 7.システム積分非直線性(INL)

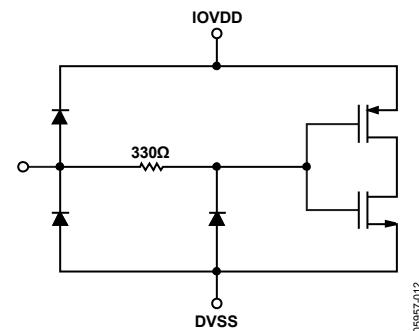

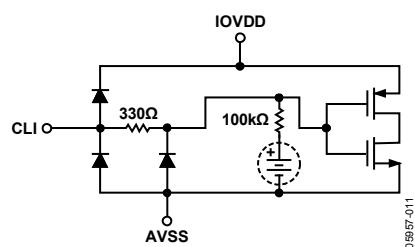

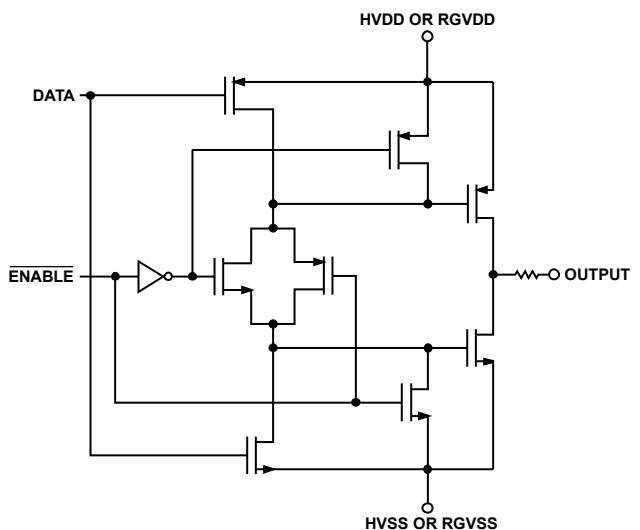

## 等価入出力回路

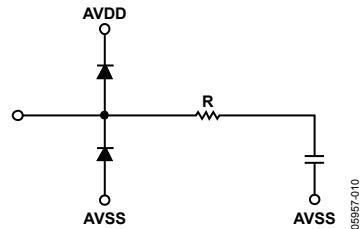

図 8.CCD 入力

図 10. デジタル入力

図 9.CLI 入力、レジスタ 0x15[0] =1 でバイアス回路をイネーブル

図 11.H1~H4、HL、RG の各出力

## 動作原理

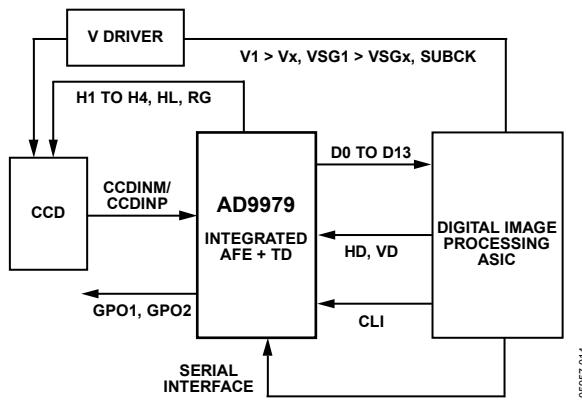

図 12. 代表的なアプリケーション

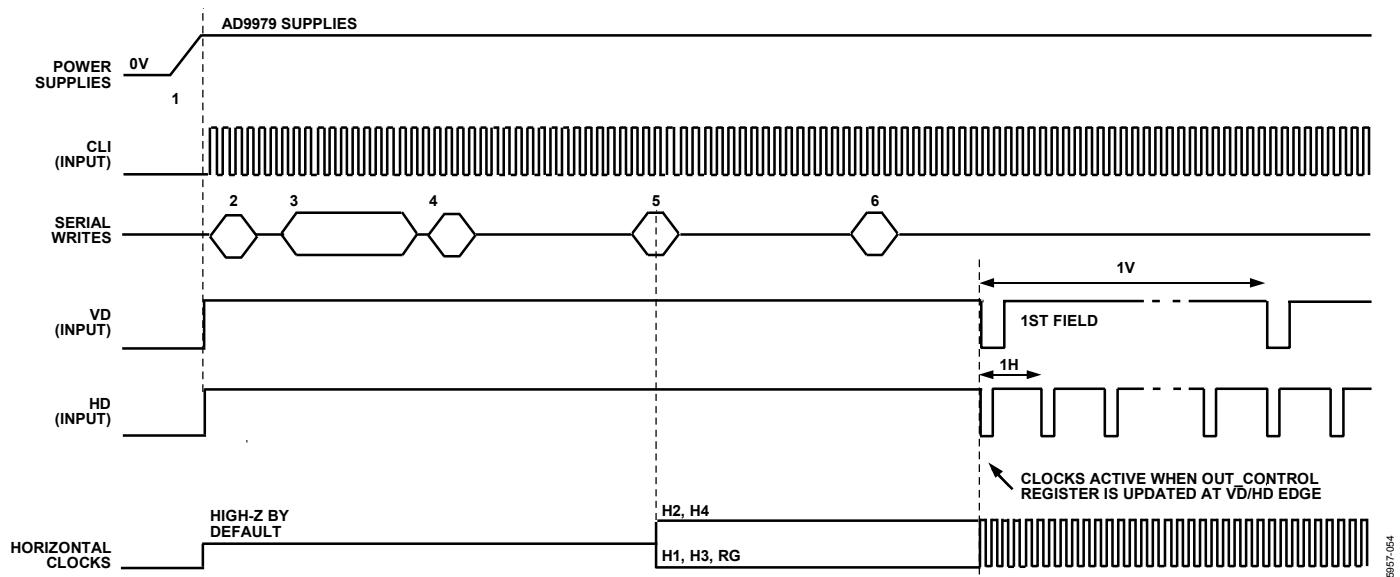

図 12 に、AD9979 の一般的なアプリケーション回路を示します。CCD 出力は AD9979 の AFE 回路により処理され、この AFE 回路は CDS、VGA、黒レベル・クランプ、ADC から構成されています。デジタル化されたピクセル情報はデジタル・イメージ・プロセッサ・チップに送られ、このチップはポスト処理と圧縮を実行します。CCD を動作させるためには、システム ASIC から 3 線式シリアル・インターフェースを介してすべての CCD タイミング・パラメータを AD9979 に書き込む必要があります。イメージ・プロセッサまたは外部水晶発振器から供給されるシステム・マスター・クロック(CLI)から、AD9979 は CCD の水平クロックおよびすべての内部 AFE クロックを発生します。

すべての AD9979 クロックは、VD 入力と HD 入力に同期しています。AD9979 のすべての水平パルス(CLPOB、PBLK、HBLK)は、内部で発生/設定されます。

AD9979 には H1~H4 と RG に対する H ドライバが内蔵されているため、これらのクロックを直接 CCD に接続することができます。AD9979 では 3 V の H 駆動電圧をサポートしています。

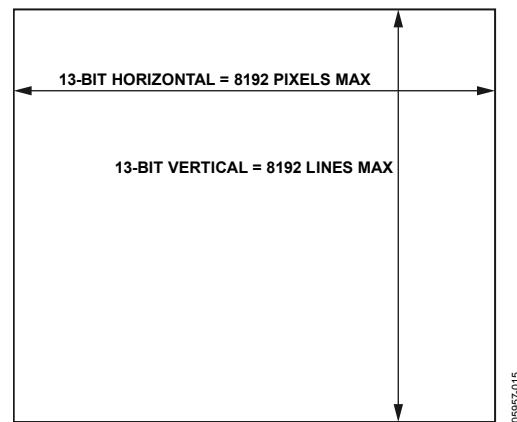

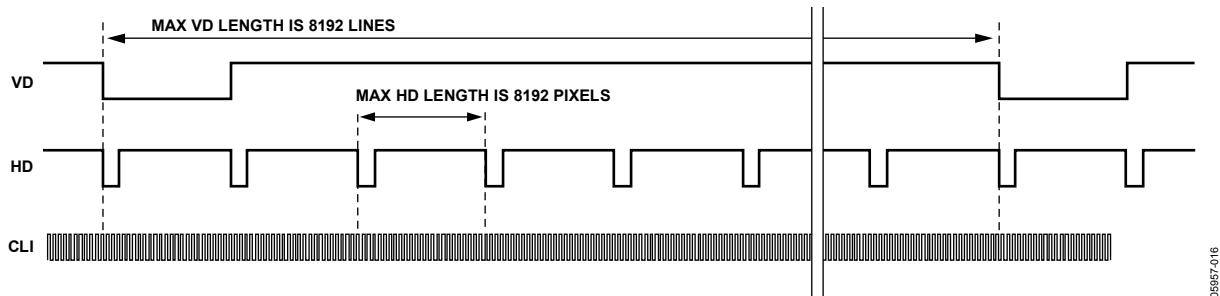

図 13 と図 14 に、AD9979 の水平カウンタと垂直カウンタの最大サイズを示します。これらのカウンタは、内部のすべての水平クロックと垂直クロックを制御し、ライン・ロケーションとピクセル・ロケーションを指定します。最大 HD 長は 8191 ピクセル/ラインで、最大 VD 長は 8192 ライン/フィールドです。

図 13. 垂直カウンタと水平カウンタの最大サイズ

図 14. 最大 VD 長と最大 HD 長

# プログラマブルなタイミングの発生

## PRECISION TIMING 高速タイミング・コア

AD9979はPrecision Timingコアを使って柔軟な高速タイミング信号を発生します。このコアは、CCDとAFEのタイミング発生の基盤となり、リセット・ゲート(RG)、水平ドライバ(HL)のH1~H4、SHP/SHDサンプル・クロックを発生します。独自アーキテクチャの採用により、水平CCD読み出しとAFE相關ダブル・サンプリングを高精度で制御することにより、システム設計者の代わりにイメージ品質の最適化を行います。

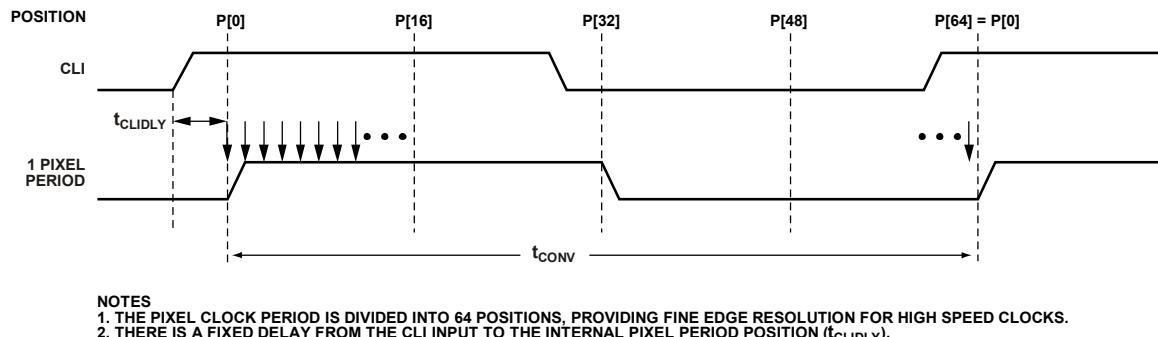

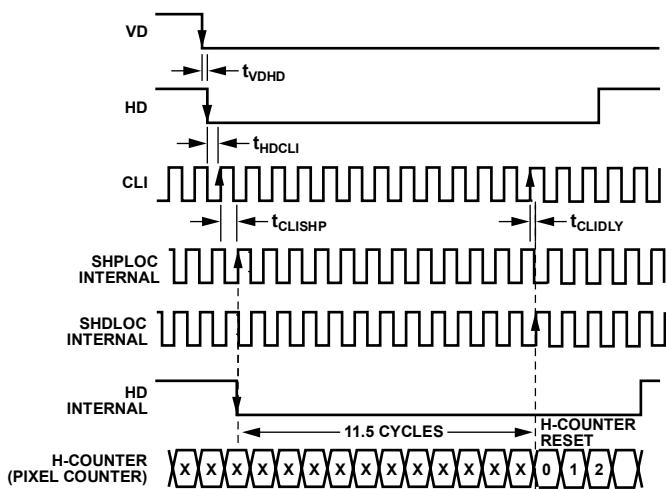

### タイミング分解能

Precision Timingコアはマスター・クロック入力(CLI)を基準として使います。このクロックは、CCDピクセル・クロック周波数と同じにすることが推奨されます。図15に、内部タイミング・コアがマスター・クロック周期を64ステップ(エッジ・ポジション数)に分割する方法を示します。したがって、Precision Timingコアのエッジ分解能は $t_{CLI}/64$ になります(CLI入力の使い方については、アプリケーション情報のセクション参照)。

65 MHzのCLI周波数の場合、Precision Timingコアのエッジ分解能は約240 psになります。1×システム・クロックが使用できない場合は、CLIDIVIDEレジスタ(アドレス0x0D)に書き込みを行って、2×リファレンス・クロックを使うことができます。この場合、AD9979はCLI周波数を内部で2分周します。

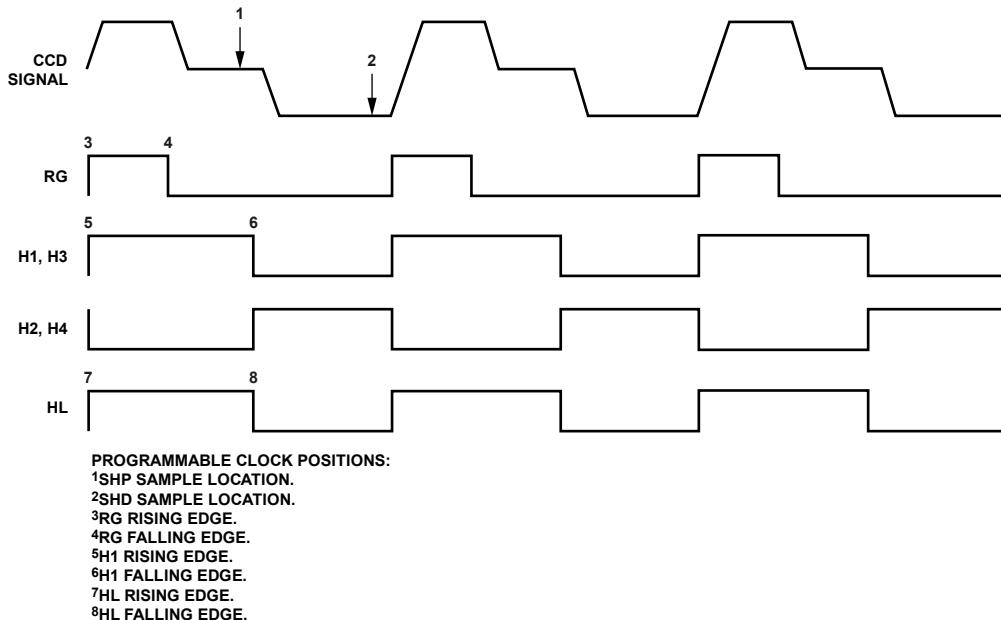

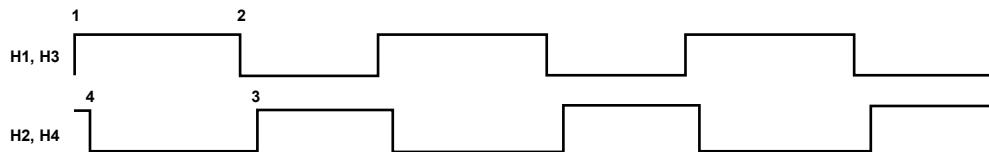

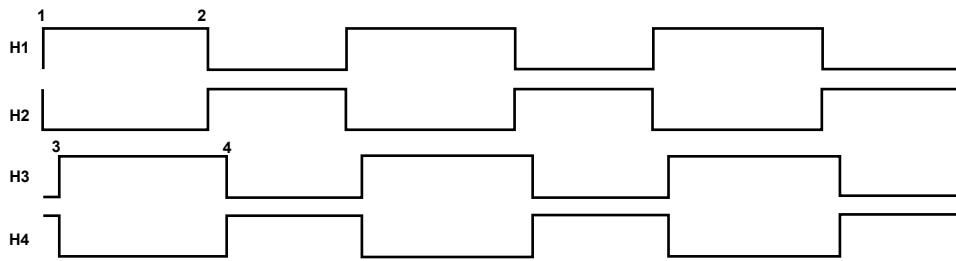

### 高速クロックのプログラマブル性

図16に、高速クロックRG、HL、H1~H4、SHP、SHDの発生方法を示します。RGパルスは、プログラマブルな立ち上がりエッジと立ち下がりエッジを持ち、極性制御を使って反転することができます。水平クロックHL、H1、H2は、別々のプログラマブルな立ち上がりと立ち下がりエッジと極性制御を持っています。AD9979には、その他のHCLKモード・プログラマブル性もあります(表8参照)。

各エッジ・ロケーション・レジスタは6ビット幅で、64個の有効エッジ・ロケーションを使用することができます。図19に、全高速クロック信号のデフォルト・タイミング・ロケーションを示します。

図15.CLIマスター・クロック入力からの高速クロック分解能

図16.高速クロックのプログラマブル・ロケーション(HCLKMODE = 1)

H1 TO H4 PROGRAMMABLE LOCATIONS:

1H1 RISING EDGE.

2H1 FALLING EDGE.

3H2 RISING EDGE.

4H2 FALLING EDGE.

図 17.HCLK モード 2 動作

05957-019

H1 TO H4 PROGRAMMABLE LOCATIONS:

1H1 RISING EDGE.

2H1 FALLING EDGE.

3H3 RISING EDGE.

4H3 FALLING EDGE.

図 18.HCLK モード 3 動作

05957-020

05957-021

## NOTES

- ALL SIGNAL EDGES ARE FULLY PROGRAMMABLE TO ANY OF THE 64 POSITIONS WITHIN 1 PIXEL PERIOD. TYPICAL POSITIONS FOR EACH SIGNAL ARE SHOWN. HCLK MODE 1 IS SHOWN.

- CERTAIN POSITIONS MUST BE AVOIDED FOR EACH SIGNAL, SHOWN ABOVE AS INHIBIT REGIONS.

- IF A SETTING IN THE INHIBIT REGION IS USED, AN UNSTABLE PIXEL SHIFT CAN OCCUR IN THE HBLK LOCATION OR AFE PIPELINE.

図 19.高速タイミングのデフォルト・ロケーション

表 8.HCLK モード(レジスタ・アドレス 0x23、ビット[7:5]で選択)

| HCLK Mode         | Register Value          | Description                                                                                      |

|-------------------|-------------------------|--------------------------------------------------------------------------------------------------|

| Mode 1            | 001                     | H1 edges are programmable; H3 = H1, H2 = H4 = inverse of H1.                                     |

| Mode 2            | 010                     | H1 edges are programmable; H3 = H1.<br>H2 edges are programmable; H4 = H2.                       |

| Mode 3            | 100                     | H1 edges are programmable; H2 = inverse of H1.<br>H3 edges are programmable; H4 = inverse of H3. |

| Invalid Selection | 000, 011, 101, 110, 111 | Invalid register settings.                                                                       |

表 9. 水平クロック、RG、駆動およびサンプル制御のレジスタ・パラメータ

| Name            | Length | Range                   | Description                                                        |

|-----------------|--------|-------------------------|--------------------------------------------------------------------|

| Polarity        | 1 bit  | High/low                | Polarity control for H1/H3 and RG; 0 = no inversion, 1 = inversion |

| Positive Edge   | 6 bits | 0 to 63 edge location   | Positive edge location for H1/H3 and RG                            |

| Negative Edge   | 6 bits | 0 to 63 edge location   | Negative edge location for H1/H3 and RG                            |

| Sample Location | 6 bits | 0 to 63 sample location | Sampling location for SHP and SHD                                  |

| Drive Control   | 3 bits | 0 to 7 current steps    | Drive current for H1 to H4 and RG outputs (4.3 mA steps)           |

図 20.AFE データ出力のパイプライン遅延

05957-022

## H ドライバと RG 出力

AD9979 はプログラマブルなタイミング・ポジションの他に、HL、RG、H1~H4 の各出力に対する出力ドライバも内蔵しています。これらのドライバは、CCD 入力を直接駆動できる十分な能力を持っています。H ドライバ電流と RG ドライバ電流は、駆動強度コントロール・レジスタ(アドレス 0x35)を使って、特定の負荷に対して最適な立ち上がり/立ち下がり時間に調整することができます。レジスタを使って、4.3 mA ステップで駆動強度を調節します。最小設定値 0 はオフ状態なわちスリー・ステートに対応し、最大設定値 7 は 30.1 mA に対応します。

## デジタル・データ出力

AD9979 ではシステムの柔軟性を高くするため、DOUTPHASEN と DOUTPHASEP(アドレス 0x37、ビット[11:0])を使って、新しい各ピクセル・データ値の開始ロケーションを選択しています。0~63 のエッジ・ロケーションを設定することができます。レジスタ 0x37 は、マスター・クロック入力 CLI を基準とするデータ出力の開始ロケーションと DOUTPHASEX クロックの立ち上がりエッジを指定します。

AD9979 のパイプライン遅延を図 20 に示します。CCD 入力が SHD によりサンプルされてからデータが出力されるまでに 16 サイクルの遅延があります。

## 水平クランピングとブランкиング

AD9979 の水平クランピングとブランкиング・パルスは、さまざまなアプリケーションに合わせて設定することができます。CLPOB、PBLK、HBLK の各フィールドの各領域は個別に制御することができます。この機能を使うと、さまざまなイメージ転送タイミングと高速なライン・シフトが可能になるため、黒レベルへのピクセル・クランピングとブランкиング・パターンを読み出しの各ステージで変更することができます。

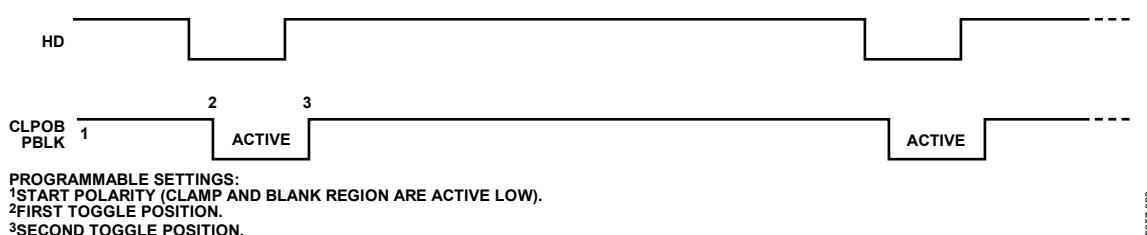

### 独立した CLPOB と PBLK のパターン

AFE 水平タイミングは CLPOB と PBLK から構成されています(図 21 参照)。これら 2 つの信号は、表 10 に示すレジスタを使って独立に設定されます。CLPOB (PBLK) 信号のスタート極性は CLPOB\_POL (PBLK\_POL) で、このパルスの最初および 2 番目のトグル・ポジションはそれぞれ CLPOBx\_TOG1 (PBLKx\_TOG1) と CLPOBx\_TOG2 (PBLKx\_TOG2) です。両信号はアクティブ・ローであり、これに従って設定する必要があります。

各 H パターン CLPOB0、CLPOB1、PBLK0、PBLK1 に対して、CLPOB と PBLK の別々の 2 つのパターンを設定することができます。CLPOB\_PAT フィールド・レジスタと PBLK\_PAT フィールド・レジスタは、2 つのパターンのいずれを各フィールドで使用するかを指定します。

図 32 に、シーケンス変化ポジションにより読み出しフィールドがさまざまな領域に分割される方法を示します。さまざまな H パターンを各領域に割り当てることにより、

CLPOB 信号と PBLK 信号が垂直タイミングの各変化で変化することができます。

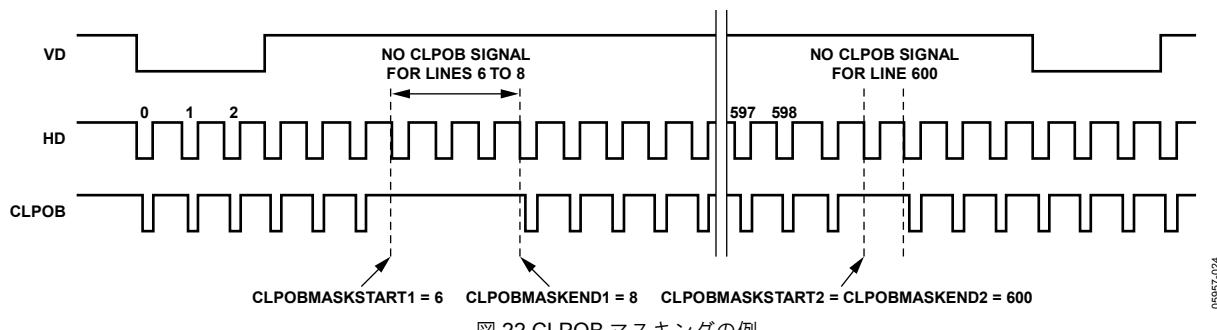

### CLPOB と PBLK のマスキング領域

さらに、AD9979 では既存のパターン設定を変更することなく、フィールド内のあるラインで、CLPOB 信号と PBLK 信号をディスエーブルすることができます。CLPOB と PBLK には 3 セットの開始レジスタと終了レジスタがあります。これらを使うと各信号に対して最大 3 個のマスキング領域を設けることができます。

たとえば、CLPOB マスキングを使うときは、CLPOBMASKSTARTx レジスタと CLPOBMASKENDx レジスタを設定して、CLPOB パターンを無視するフィールド内の開始ラインと終了ラインを指定します。図 22 に、この機能を示します。

マスキング・レジスタはある H パターンに特定ではなく、タイミングの全既存フィールドに対して常にアクティブです。CLPOB と PBLK のマスキング機能をディスエーブルするときは、これらのレジスタに最大値 0xFFFF を設定します。

パワーアップ時に CLPOB と PBLK のマスキングをディスエーブルするときは、CLPOBMASKSTARTx (PBLKMASKSTARTx) に 8191 を、CLPOBMASKENDx (PBLKMASKENDx) に 0 を、それぞれ設定することが推奨されます。これにより、さまざまなレジスタ更新イベントで発生する偶発的なマスキングを防止することができます。

図 21. クランプおよびプリブランク・パルスの配置

図 22. CLPOB マスキングの例

表 10. CLPOB レジスタと PBLK レジスタ

| Name            | Length  | Range                    | Description                                                               |

|-----------------|---------|--------------------------|---------------------------------------------------------------------------|

| CLPOB0_TOG1     | 13 bits | 0 to 8191 pixel location | First CLPOB0 toggle position within the line for each V-sequence.         |

| CLPOB0_TOG2     | 13 bits | 0 to 8191 pixel location | Second CLPOB0 toggle position within the line for each V-sequence.        |

| CLPOB1_TOG1     | 13 bits | 0 to 8191 pixel location | First CLPOB1 toggle position within the line for each V-sequence.         |

| CLPOB1_TOG2     | 13 bits | 0 to 8191 pixel location | Second CLPOB1 toggle position within the line for each V-sequence.        |

| CLPOB_POL       | 9 bits  | High/low                 | Starting polarity of CLPOB for each V-sequence[8:0] (in field registers). |

| CLPOB_PAT       | 9 bits  | 0 to 9 settings          | CLPOB pattern selection for each V-sequence[8:0] (in field registers).    |

| CLPOBMASKSTARTx | 13 bits | 0 to 8191 pixel location | CLPOB mask start position. Three values available (in field registers).   |

| CLPOBMASKENDx   | 13 bits | 0 to 8191 pixel location | CLPOB mask end position. Three values available (in field registers).     |

| PBLK0_TOG1      | 13 bits | 0 to 8191 pixel location | First PBLK0 toggle position within the line for each V-sequence.          |

| PBLK0_TOG2      | 13 bits | 0 to 8191 pixel location | Second PBLK0 toggle position within the line for each V-sequence.         |

| PBLK1_TOG1      | 13 bits | 0 to 8191 pixel location | First PBLK1 toggle position within the line for each V-sequence.          |

| PBLK1_TOG2      | 13 bits | 0 to 8191 pixel location | Second PBLK1 toggle position within the line for each V-sequence.         |

| PBLK_POL        | 9 bits  | High/low                 | Starting polarity of PBLK for each V-sequence[8:0] (in field registers).  |

| PBLK_PAT        | 9 bits  | 0 to 9 settings          | PBLK pattern selection for each V-sequence[8:0] (in field registers).     |

| PBLKMASKSTARTx  | 13 bits | 0 to 8191 pixel location | PBLK mask start position. Three values available (in field registers).    |

| PBLKMASKENDx    | 13 bits | 0 to 8191 pixel location | PBLK mask end position. Three values available (in field registers).      |

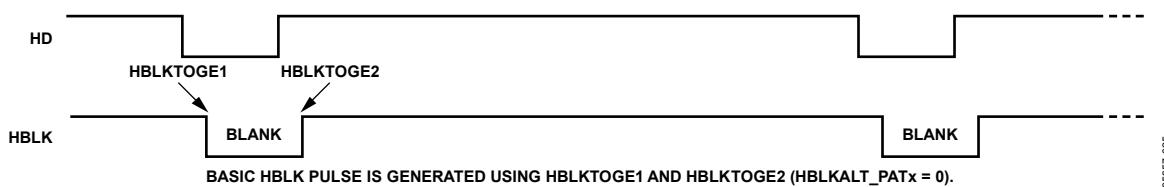

図 23.一般的な水平ブランкиング・パルスの配置(HBLKMODE = 0)

図 24.HBLK マスキングの制御

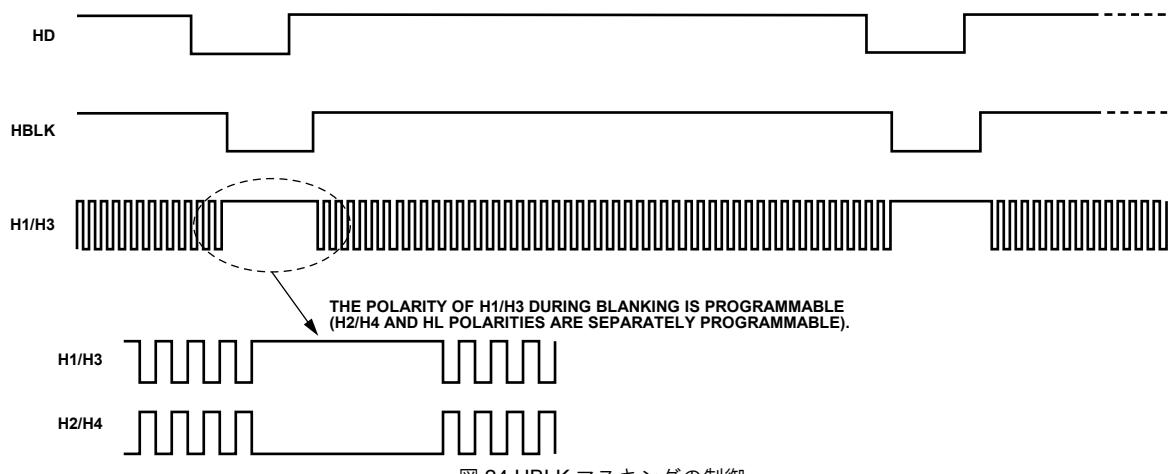

## 個別の HBLK パターン

図 23 に示すプログラマブルな HBLK タイミングは、CLPOB および PBLK と同じですが、スタート極性制御がありません。トグル・ポジションは、ブランкиング区間の開始ポジションと停止ポジションのみを指定します。さらに図 24 に示すように、H1/H3、H2/H4、HL に対する極性制御 HBLKMASK があり、これによりブランкиング区間での水平クロック信号の極性が指定されます。HBLKMASK をハイ・レベルに設定すると、ブランкиング区間で H1=H3=ロー・レベル、かつ H2=H4=ハイ・レベルになります。CLPOB 信号と PBLK 信号の場合と同様に、各 H パターン・グループに HBLK レジスタがあるため、さまざまな垂直タイミング・シーケンスでユニークなブランкиング信号を使うことができます。

AD9979 は、HBLK 動作に対して 3 種類のモードをサポートしています。HBLK モード 0 では、基本動作をサポートし、特別な HBLK パターンに対する幾つかのサポートを提供します。HBLK モード 1 では、ピクセル・ミキシング HBLK 動作をサポートします。HBLK モード 2 では、高度な HBLK 動作をサポートします。次のセクシ

ョンでは各モードについて説明します。レジスタ名は、表 11 に記載します。

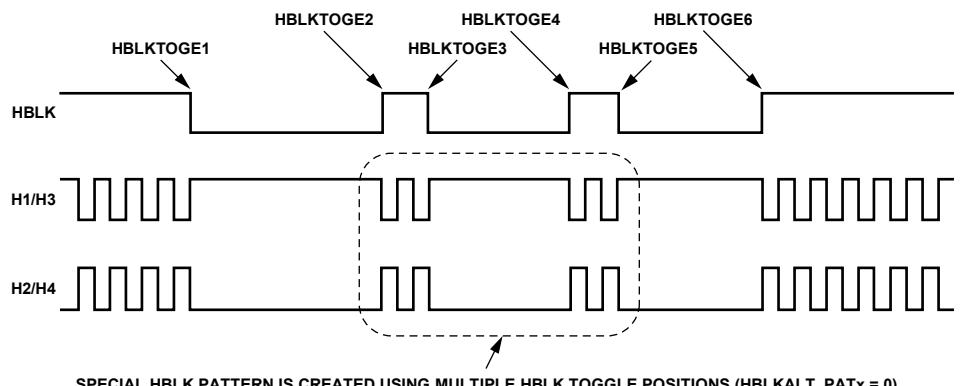

## HBLK モード 0 動作

HBLK には 6 個のトグル・ポジションがあります。通常、2 個のトグル・ポジションのみを使用して標準 HBLK インターバルを発生しますが、追加トグル・ポジションを使って、特別な HBLK パターンを発生することができます(図 25 参照)。このパターン例では、6 個のすべてのトグル・ポジションを使って、HBLK インターバルで追加 2 グループのパルスを発生しています。トグル・ポジションを変更することにより、さまざまなパターンを発生することができます。

偶数ラインと奇数ラインに対して別々のトグル・ポジションがあります。変更が不要な場合には、HBLKTOGE<sub>x</sub> レジスタと HBLKTOGO<sub>x</sub> レジスタへ同じ値をロードしてください。

0997-027

図 25. 特別な HBLK パターンの発生

表 11. HBLK パターン・レジスタ

| Name        | Length  | Range                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|---------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HBLKMODE    | 2 bits  | 0 to 2                   | Enables different HBLK toggle position operation.<br>0 = normal mode. Six toggle positions are available for even and odd lines. If even/odd alternation is not need, set the toggle positions for the even/odd the same.<br>1 = pixel mixing mode. Instead of only six toggle positions, use the HBLKSTART, HBLKEND, HBLKLEN, and HBLKREP registers, along with HBLKTOGO <sub>x</sub> and HBLKTOGE <sub>x</sub> . If even/odd alternation is not need, set the even/odd toggles the same.<br>2 = advanced HBLK mode. It divides HBLK interval into six different repeat areas. It uses HBLKSTARTA, HBLKSTARTB, HBLKSTARTC, and RAxHyREPA/RAxHyREPB/RAxHyREPC registers.<br>3 = test mode. Do not access. |

| HBLKSTART   | 13 bits | 0 to 8191 pixel location | Start location for HBLK in HBLK Mode 1 and HBLK Mode 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| HBLKEND     | 13 bits | 0 to 8191 pixel location | End location for HBLK in HBLK Mode 1 and HBLK Mode 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| HBLKLEN     | 13 bits | 0 to 8191 pixels         | HBLK length in HBLK Mode 1 and HBLK Mode 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| HBLKREP     | 13 bits | 0 to 8191 repetitions    | Number of HBLK repetitions in HBLK Mode 1 and HBLK Mode 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| HBLKMASK_H1 | 1 bit   | High/low                 | Masking polarity for H1/H3 during HBLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| HBLKMASK_H2 | 1 bit   | High/low                 | Masking polarity for H2/H4 during HBLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| HBLKMASK_HL | 1 bit   | High/low                 | Masking polarity for HL during HBLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Name                      | Length  | Range                    | Description                                                                                                                                                                                                                                                                     |

|---------------------------|---------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HBLKTOGO1                 | 13 bits | 0 to 8191 pixel location | First HBLK toggle position for odd lines in HBLK Mode 0 and HBLK Mode 1.                                                                                                                                                                                                        |

| HBLKTOGO2                 | 13 bits | 0 to 8191 pixel location | Second HBLK toggle position for odd lines in HBLK Mode 0 and HBLK Mode 1.                                                                                                                                                                                                       |

| HBLKTOGO3                 | 13 bits | 0 to 8191 pixel location | Third HBLK toggle position for odd lines in HBLK Mode 0 and HBLK Mode 1.                                                                                                                                                                                                        |

| HBLKTOGO4                 | 13 bits | 0 to 8191 pixel location | Fourth HBLK toggle position for odd lines in HBLK Mode 0 and HBLK Mode 1.                                                                                                                                                                                                       |

| HBLKTOGO5                 | 13 bits | 0 to 8191 pixel location | Fifth HBLK toggle position for odd lines in HBLK Mode 0 and HBLK Mode 1.                                                                                                                                                                                                        |

| HBLKTOGO6                 | 13 bits | 0 to 8191 pixel location | Sixth HBLK toggle position for odd lines in HBLK Mode 0 and HBLK Mode 1.                                                                                                                                                                                                        |

| HBLKTOGE1                 | 13 bits | 0 to 8191 pixel location | First HBLK toggle position for even lines in HBLK Mode 0 and HBLK Mode 1.                                                                                                                                                                                                       |

| HBLKTOGE2                 | 13 bits | 0 to 8191 pixel location | Second HBLK toggle position for even lines in HBLK Mode 0 and HBLK Mode 1.                                                                                                                                                                                                      |

| HBLKTOGE3                 | 13 bits | 0 to 8191 pixel location | Third HBLK toggle position for even lines in HBLK Mode 0 and HBLK Mode 1.                                                                                                                                                                                                       |

| HBLKTOGE4                 | 13 bits | 0 to 8191 pixel location | Fourth HBLK toggle position for even lines in HBLK Mode 0 and HBLK Mode 1.                                                                                                                                                                                                      |

| HBLKTOGE5                 | 13 bits | 0 to 8191 pixel location | Fifth HBLK toggle position for even lines in HBLK Mode 0 and HBLK Mode 1.                                                                                                                                                                                                       |

| HBLKTOGE6                 | 13 bits | 0 to 8191 pixel location | Sixth HBLK toggle position for even lines in HBLK Mode 0 and HBLK Mode 1.                                                                                                                                                                                                       |

| RAxHyREPz <sup>1</sup>    | 12 bits | 0 to 15 HCLK pulses      | HBLK Mode 2 even field Repeat Area x. Number of Hy repetitions for HBLKSTARTz even lines. <sup>2</sup><br>Bits[3:0]: number of Hy pulses following HBLKSTARTA.<br>Bits[7:4]: number of Hy pulses following HBLKSTARTB.<br>Bits[11:8]: number of Hy pulses following HBLKSTARTC. |

| HBLKSTARTA                | 13 bits | 0 to 8191 pixel location | HBLK Repeat Area Start Position A for HBLK Mode 2.                                                                                                                                                                                                                              |

| HBLKSTARTB                | 13 bits | 0 to 8191 pixel location | HBLK Repeat Area Start Position B for HBLK Mode 2.                                                                                                                                                                                                                              |

| HBLKSTARTC                | 13 bits | 0 to 8191 pixel location | HBLK Repeat Area Start Position C for HBLK Mode 2.                                                                                                                                                                                                                              |

| HBLKALT_PATx <sup>3</sup> | 3 bits  | 0 to 5 even repeat area  | HBLK Mode 2 odd field Repeat Area x pattern. Selected from even field repeat areas. <sup>4</sup>                                                                                                                                                                                |

<sup>1</sup> 変数 x は 0~5 で繰り返し領域を表します。変数 y は水平ドライバ 1 または 2 を表します。変数 z は HBLK モード 2、A、B または C の HBLK 繰り返し領域開始位置を表します。

<sup>2</sup> HBLKALT\_PATx を使って指定された奇数ライン。

<sup>3</sup> 変数 x は繰り返し領域を表し、0~5 です。

<sup>4</sup> RAxHyREPz を使って指定された偶数ライン。注 1 も参照。

05957-028

図 26. HBLK モード 1 を使用した HBLK 繰り返しパターン(レジスタ値=1)

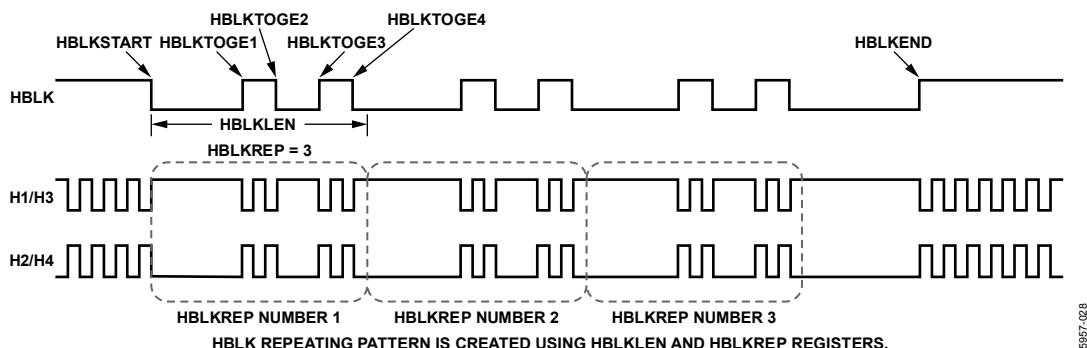

## HBLK モード 1 動作

HBLKMODE に 1 を設定すると、HBLK 信号の複数繰り返し機能をイネーブルすることができます。このモードでは、HBLKSTART、HBLKEND、HBLKLEN、HBLKREP のレジスタ・セットと 6 個のトグル・ポジションとの組み合わせにより HBLK パターンが発生されます(図 26 参照)。

## HBLK ライン切り替えの発生

HBLK モード 0 と HBLK モード 1 では、別々のトグル・ポジションが使用可能な偶数ラインと奇数ライン上の HBLK トグル・ポジションを切り替える機能を提供します。偶数/奇数ラインの切り替えが不要な場合には、偶数ライン(HBLKTOGE<sub>x</sub>)と奇数(HBLKTOGO<sub>x</sub>)ラインのレジスタに同じ値をロードします。

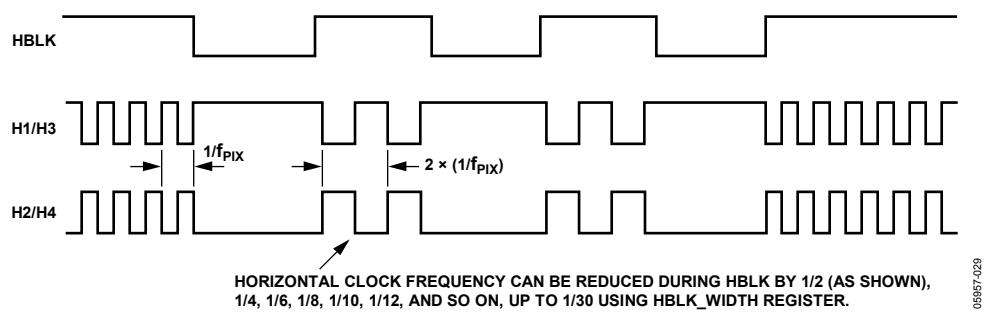

### HBLK 区間中の水平クロック幅の増加

HBLK モード 0 と HBLK モード 1 では、HBLK インターバルで H1~H4 のパルス幅を広げることができます。図 27 に示すように、水平クロック周波数を倍率 1/2、1/4、1/6、1/8、1/10、1/12、...、1/30 で小さくすることができます (表 12 参照)。この機能をイネーブルするときは、HCLK\_WIDTH レジスタ(アドレス 0x34、ビット[7:4])に、1~15 の値を設定します。このレジスタに 0 を設定すると、HCLK 幅機能がディスエーブルされます。

周波数の低下は HBLK 領域内にある H1~H4 パルスでのみ発生します。

HCLK\_WIDTH 機能は一般に、特別な HBLK パターンと組み合わせて使用されて、CCD 内で垂直と水平のミキシングを発生させます。

HCLK 幅機能は HBLK モード 0 と HBLK モード 1 でのみ使用可能で、HBLK モード 2 では使用できないことに注意してください。

表 12.HCLK 幅レジスタ

| Name       | Length | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCLK_WIDTH | 4 bits | <p>Controls H1 to H4 width during HBLK as a fraction of pixel rate.</p> <p>0 = same frequency as pixel rate</p> <p>1 = 1/2 pixel frequency, that is, doubles the HCLK pulse width</p> <p>2 = 1/4 pixel frequency</p> <p>3 = 1/6 pixel frequency</p> <p>4 = 1/8 pixel frequency</p> <p>5 = 1/10 pixel frequency</p> <p>6 = 1/12 pixel frequency</p> <p>7 = 1/14 pixel frequency</p> <p>8 = 1/16 pixel frequency</p> <p>9 = 1/18 pixel frequency</p> <p>10 = 1/20 pixel frequency</p> <p>11 = 1/22 pixel frequency</p> <p>12 = 1/24 pixel frequency</p> <p>13 = 1/26 pixel frequency</p> <p>14 = 1/28 pixel frequency</p> <p>15 = 1/30 pixel frequency</p> |

図 27.HBLK インターバルでの広い水平クロック・パルスの発生

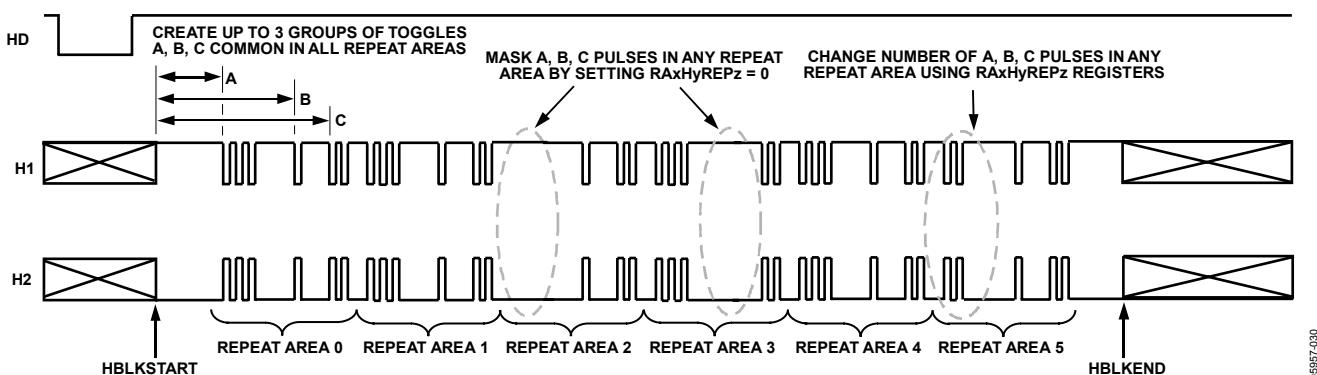

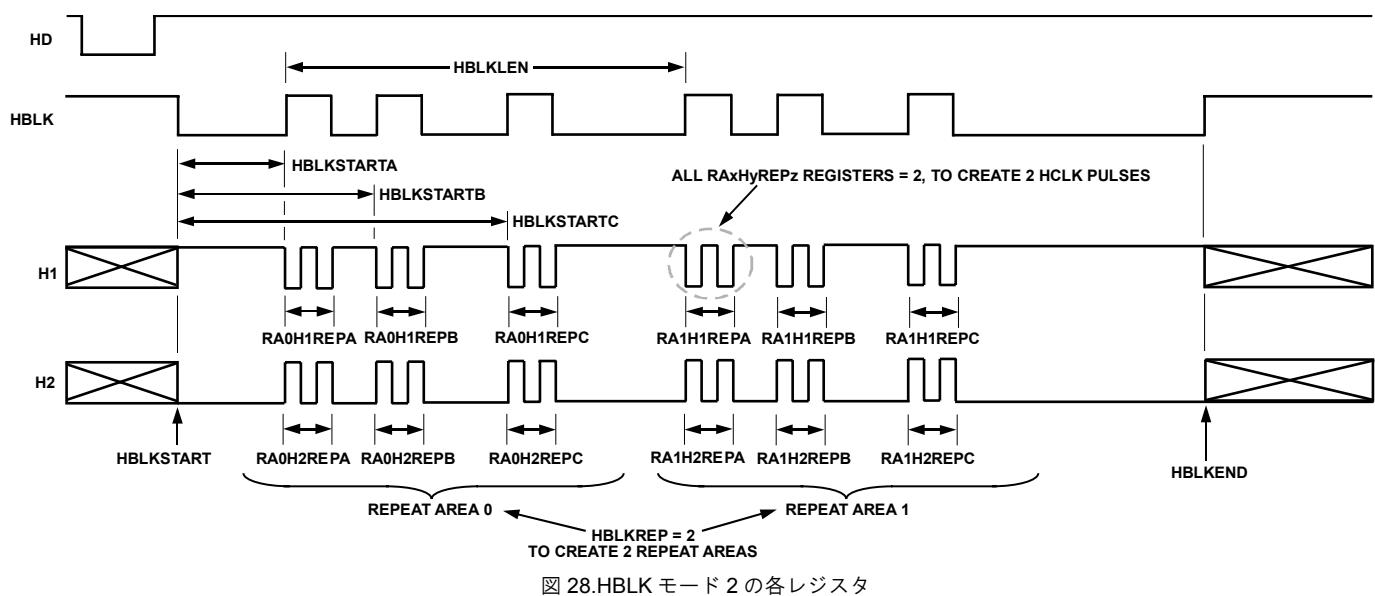

## HBLK モード 2 動作

HBLK モード 2 では、さらに高度な HBLK パターン動作が可能です。不均一な間隔を持つ複数領域の HCLK パルスが必要な場合、HBLK モード 2 を使います。別々のセットのレジスタを使うと、HBLK モード 2 では HBLK 領域を 6 個の領域に分割することができます(表 11 参照)。図 28 に示すように、各繰り返し領域ではトグル・ポジション HBLKSTARTA、HBLKSTARTB、HBLKSTARTC の 1 つの共通グループを使いますが、RAxHyREPz を使うことにより、各 HBLKSTARTA、HBLKSTARTB、HBLKSTARTC ポジションの後ろのトグル数を各繰り返し領域でユニークにすることができます(ここで、x は繰り返し領域 0~5 を、y は水平ドライバ 1 または 2 を、z は HBLK モード 2 での HBLK 繰り返し領域開始ポジション A、B、または C を、それぞれ表します)。図 29 に示すように、RAxH1REPA/RAxH1REPB/RAxH1REPC レジスタまたは RAxH2REPA/RAxH2REPB/RAxH2REPC レジスタに 0 を設定すると、特定の繰り返し領域で HCLK グループが現れないようにマスクされます。図 28 に、使用される 2 個の繰り返し領域のみを示します(最大 6 個が使用可能です)。H1 と H2 に対して繰り返し領域の繰り返し数を別々に設定することができますが、一般に H1 と H2 に同じ値が使用されます。

図 28 に例を示します。

RA0H1REPA/RA0H1REPB/RA0H1REPC =

RA0H2REPA/RA0H2REPB/RA0H2REPC =

RA1H1REPA/RA1H1REPB/RA1H1REPC =

RA1H2REPA/RA1H2REPB/RA1H2REPC = 2。

さらに、HBLK モード 2 では、偶数ラインと奇数ライン上でさまざまな HBLK パターンが可能です。

HBLKSTARTA、HBLKSTARTB、HBLKSTARTC、および RAxH1REPA/RAxH1REPB/RAxH1REPC と RAxH2REPA/RAxH2REPB/RAxH2REPC により、偶数ラインの動作が指定されます。奇数ラインを別に制御するときは、偶数ラインで使われる繰り返し領域を再指定することにより、HBLKALT\_PATx レジスタを使って奇数ライン上に最大 6 個の繰り返し領域を指定します。新しいパターンを使うことはできませんが、偶数ライン上で定義済みの繰り返し領域の指定を奇数ラインに対して変更して高度な CCD 動作を行うことができます。

05957-031

05957-030

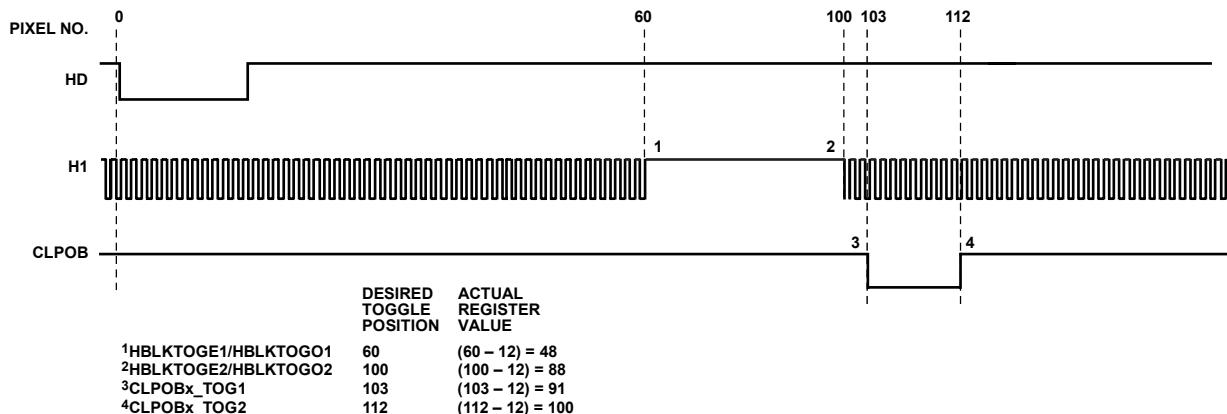

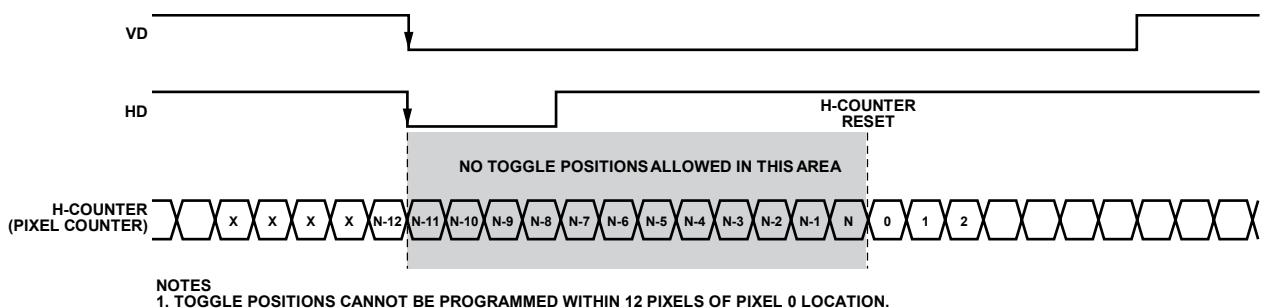

## HBLK, PBLK, CLPOB のトグル・ポジション

AD9979 では、内部水平ピクセル・カウンタを使って HBLK、PBLK、CLPOB のトグル・ポジションを決めています。HD の立ち下がりエッジから 12 CLI 周期が経過するまで水平カウンタが 0 にリセットされません。レジスタ・トグル・ポジションを指定するときには、この 12 サイクルのパイプライン遅延を考慮する必要があります。たとえば、CLPOB<sub>x</sub>\_TOGy = 100 で、パイプライン遅延を考慮しないと、最終トグル・ポジションは 112 になります。正しいトグル・ポジションを取得するためには、トグル・ポジション・レジスタを所望トグル・ポジションより 12だけ小さい値に設定する必要があります。たとえば、所望トグル・ポジションが 100 の場合、CLPOB<sub>x</sub>\_TOGy を 88(= 100 - 12)に設定する必要があります。

す。図 53 に、HD の立ち下がりエッジに対する 12 サイクルのパイプライン遅延を示します。

トグル・ポジションは、HD の立ち下がりエッジから水平カウンタがリセットされるまでの 12 サイクルの遅延中に設定できないことに注意してください。この制約の例については、図 31 を参照してください。

図 30.所望トグル・ポジションを得るためのレジスタ設定の例

0597-032

図 31.トグル・ポジション配置の制約

0597-033

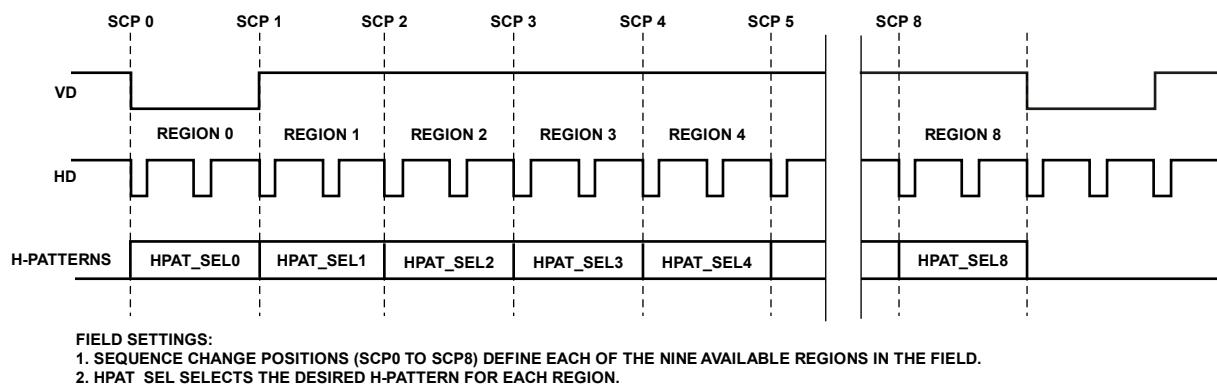

## フィールド全体—H パターンの組み合わせ

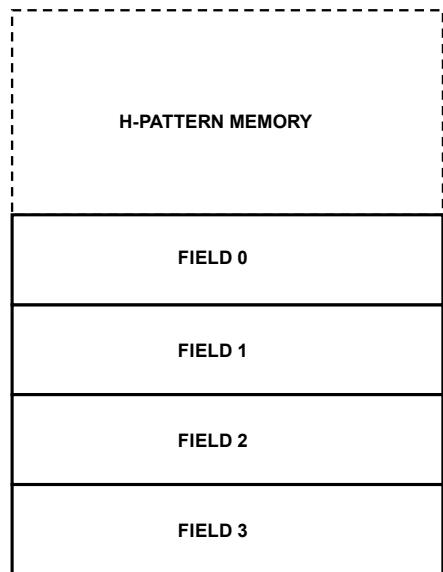

H パターンを生成した後は、これらを組み合わせてさまざまな読み出し・フィールドを生成します。1つのフィールドは SCP レジスタで指定される最大 7 個の領域から構成され、各領域内で H パターン・グループ(最大 32 グループ)を選択することができます。H パターンを制御するレジスタは、フィールド・レジスタ内に配置されています。表 13 に、フィールド・レジスタを示します。

## H パターンの選択

H パターンは HPAT メモリ内に格納されています(表 33 参照)。まず、必要とする H パターン・グループ数を決め(最大 32)、次に HPAT\_SELx レジスタを使ってフィールドの各領域で出力する H パターン・グループを選択します。図 32 に、HPAT\_SELx レジスタと SCPx レジスタの使い方を示します。SCPx レジスタは、各領域のライン境界を生成します。

図 32. フィールド全体を領域に分割

表 13. フィールド・レジスタ

| Name                           | Length  | Range                 | Description                                                          |

|--------------------------------|---------|-----------------------|----------------------------------------------------------------------|

| SCPx                           | 13 bits | 0 to 8191 line number | Sequence change position for each region; selects an individual line |

| HPAT_SELx                      | 5 bits  | 0 to 31 H-patterns    | Selected H-pattern for each region of the field                      |

| CLPOB_POL                      | 9 bits  | High/low              | CLPOB start polarity settings for each region of the field           |

| CLPOB_PAT                      | 9 bits  | 0 to 9 patterns       | CLPOB pattern selector for each region of the field                  |

| CLPOBMASKSTARTx, CLPOBMASKENDx | 13 bits | Number of lines       | CLPOB mask positions for up to three masking configurations          |

| PBLK_POL                       | 9 bits  | High/low              | PBLK start polarity settings for each region of the field            |

| PBLK_PAT                       | 9 bits  | 0 to 9 patterns       | PBLK pattern selector for each region of the field                   |

| PBLKMASKSTARTx, PBLKMASKENDx,  | 13 bits | Number of lines       | PBLK mask positions for up to three masking configurations           |

## モード・レジスタ

AD9979 の最終フィールドのタイミングを選択するときは、モード・レジスタを使います。一般に、すべてのフィールドと H パターン・グループ情報は、スタートアップ時に AD9979 に書き込まれます。動作時にモード・レジスタを使うと、システムの電流条件を満たすフィールド・タイミングの組み合わせを選択することができます。モード・レジスタと設定済みタイミングの組み合わせを使う利点は、カメラ動作時にシステム書き込み条件を大幅に削減することです。カメラ動作モードを変更する場合、各カメラ・モード変更によるすべての垂直タイミング情報を書き込む代わりに、数回のレジスタ書き込みで済みます。

基本静止画カメラ・アプリケーションでは、水平タイミングの 5 個のフィールドが必要です。すなわち、ドロフト・モード動作に 1 個、オートフォーカスに 1 個、静止画読み出しに 3 個、それぞれ必要とされます。AD9979 では、5 個のフィールドのすべてのレジスタ・タイミング情報がスタートアップ時にロードされます。その後、カメラ動作中に、カメラの使い方に応じて、使用するフィールド・タイミングをモード・レジスタを使って選択します。

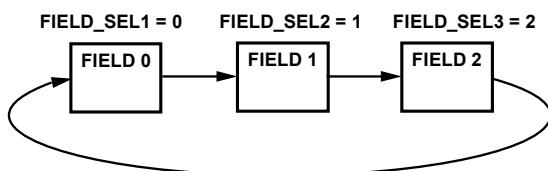

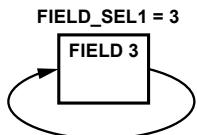

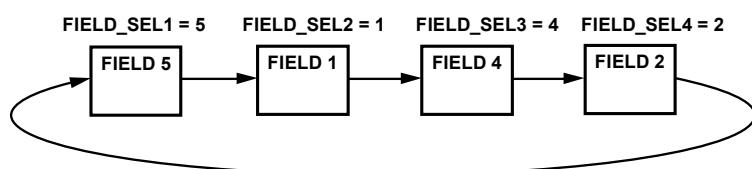

AD9979 では、最大 31 個の設定済みフィールド・グループから FIELD\_SELx レジスタを使って選択する最大 7 個のフィールド・シーケンスをサポートしています。

FIELDNUM が 1 より大きい場合、AD9979 はフィールド 1 から開始して、各 VD の開始で各フィールド N へインクリメントさせます。

図 33 に、モード設定の設定値例を示します。この例は、メモリに格納されているフィールド・グループ 0 ~ 3 の 4 個のフィールド・グループの場合です。

表 14. モード・レジスタ

| Name       | Length | Range                    | Description                                                 |

|------------|--------|--------------------------|-------------------------------------------------------------|

| HPATNUM    | 5 bits | 0 to 31 H-pattern groups | Total number of H-pattern groups starting at Address 0x800  |

| FIELDNUM   | 3 bits | 0 to 7 fields            | Total number of applied fields (1 = single-field operation) |

| FIELD_SEL1 | 5 bits | 0 to 31 field groups     | Selected first field                                        |

| FIELD_SEL2 | 5 bits | 0 to 31 field groups     | Selected second field                                       |

| FIELD_SEL3 | 5 bits | 0 to 31 field groups     | Selected third field                                        |

| FIELD_SEL4 | 5 bits | 0 to 31 field groups     | Selected fourth field                                       |

| FIELD_SEL5 | 5 bits | 0 to 31 field groups     | Selected fifth field                                        |

| FIELD_SEL6 | 5 bits | 0 to 31 field groups     | Selected sixth field                                        |

| FIELD_SEL7 | 5 bits | 0 to 31 field groups     | Selected seventh field                                      |

## EXAMPLE 1:

TOTAL FIELDS = 3, FIRST FIELD = FIELD 0, SECOND FIELD = FIELD 1, THIRD FIELD = FIELD 2

## EXAMPLE 2:

TOTAL FIELDS = 1, FIRST FIELD = FIELD 3

## EXAMPLE 3:

TOTAL FIELDS = 4, FIRST FIELD = FIELD 5, SECOND FIELD = FIELD 1, THIRD FIELD = FIELD 4, FOURTH FIELD = FIELD 2

09957.035

図 33. モード設定の例

## 水平タイミング・シーケンスの例

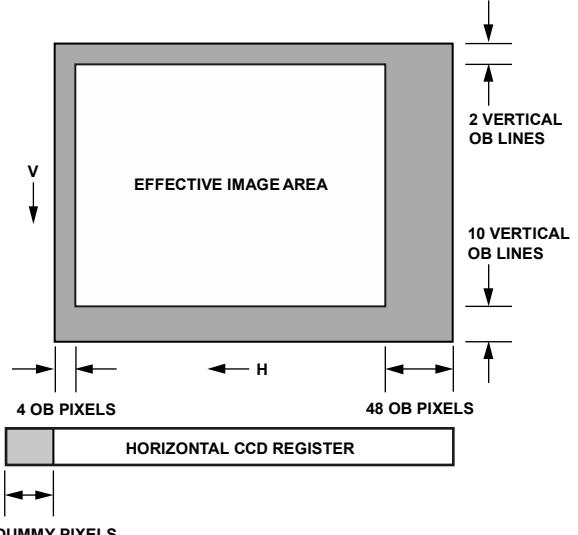

図34に、CCDレイアウトの例を示します。水平レジスタには28個のダミー・ピクセルが格納されており、CCDからクロック駆動される各ライン上でこれらのダミー・ピクセルが使用されます。垂直方向では、読み出しの前に10本の光学黒(OB)ラインと読み出しの後に2本のOBラインがあります。水平方向には、前側に4個のOBピクセル、後ろ側に48個のOBピクセルがあります。

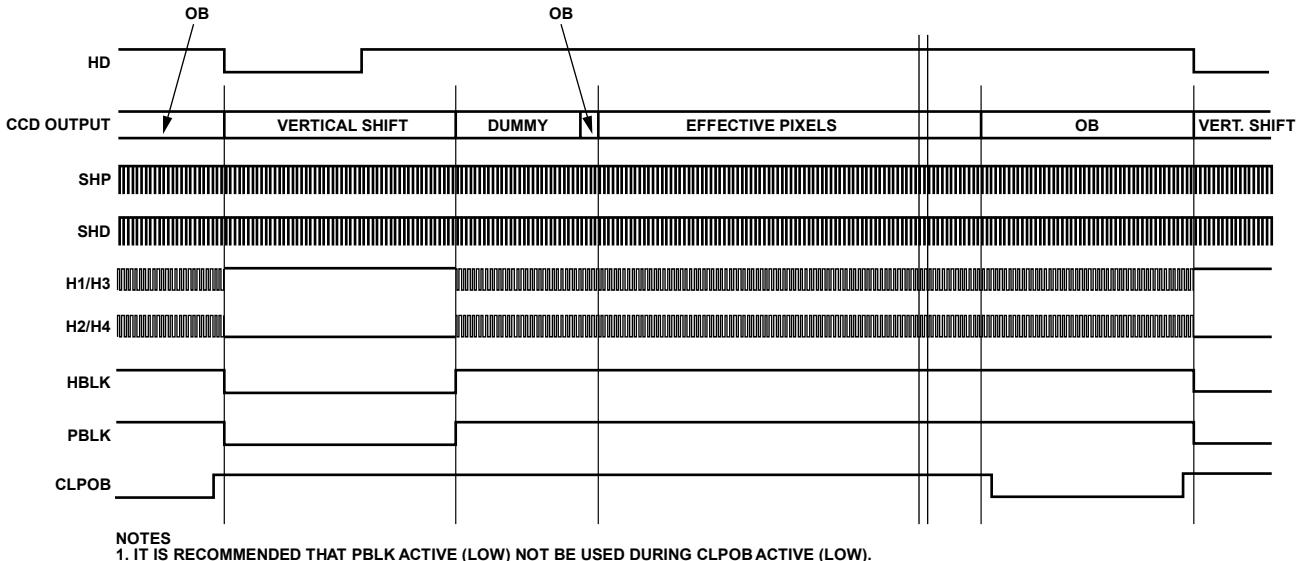

図35に、実効ピクセルの読み出し時に使う基本シーケンス・レイアウトを示します。各ラインの終わりの48個のOBピクセルは、CLPOB信号に対して使います。PBLKはオプションで、HBLK時にデジタル出力をブランクにするときに使われることがあります。HBLKは垂直シフト・インターバルで使われます。

PBLKはCDS入力のアイソレーションに使われるため(アナログ・フロントエンドの説明と動作のセクション参照)、PBLK信号はCLPOB動作時に使うことはできません。PBLK時に発生するオフセット動作の変化は、CLPOB回路の精度に影響を与えます。

HBLK、CLPOB、PBLKの各パラメータは、Vシーケンス・レジスタに書き込まれます。シールドOBライン全体でクランプする別のシーケンスを追加するなどの、さらに複雑なクランプ方式を使うことができます。このためには、OBラインを出力するために別のVシーケンスを構成する必要があります。

CLPOBマスク・レジスタは、クランプ・シーケンスのセットアップに影響を与えずに、数ライン上のCLPOBをディスエーブルする際にも役立ちます。重要なことは、有効なOBピクセルでのみCLPOBを使うことです。垂直プランギングまたはSGライン・タイミングのようなフレーム・タイミングの他の部分で、CCDは有効なOBピクセルを出力しません。このタイミングで発生するCLPOBパルスはすべてクランプ動作で誤差を発生させるため、画像の黒レベルが変化します。

図34.CCD設定の例

05957-036

図35.水平シーケンスの例

## 汎用出力(GPO)

AD9979 には、機械的シャッタ、ストロボ/フラッシュ、CCD バイアス・セレクト信号、または汎用(GP)信号を使用するその他の外付け部品を制御するプログラマブルな出力があります。最大 2 本のトグルとして使える GP 信号が 2 本あり、これらは GPO1 と GPO2 として設定することができます。これらのピンは双方向で、CLPOB、PBLK、内部高速信号(出力として使用)、HBLK 外部制御(入力として使用)の表示に使うことができます。このセクションで説明したレジスタを表 16 に示します。

### プライマリ・フィールド・カウンタ

AD9979 は、GPO 出力信号を使う際に複数のフィールドをカウントするために使用するプライマリ・フィールド・カウンタを内蔵しています。このカウンタは、各 VD サイクルでインクリメントされます。プライマリ・カウンタには次の動作を含む複数の動作モードがあり、アドレス 0x50 から制御されます。

- 起動カウンタ(シングル・カウント)

- RapidShot(繰り返しカウント)

- ShotTimer(遅延カウント)

- アイドル強制

プライマリ・カウンタは、GP トグル・ポジションの配置を制御します。さらに、プライマリ・カウンタと組み合わせて RapidShot 機能を使う場合、このカウンタは複数の露光/読み出しサイクルに必要なだけ自動的に繰り返します。

### GP トグル

各 GPO は出力として設定された場合、プログラマブルなトグル・ポジションから得られた結果を信号として出力します。GP 信号は互いに独立しているため、GP プロトコル・レジスタ(アドレス 0x52)を経由してプライマリ・フィールド・カウンタを使って、特定の VD 区間または VD 区間の全範囲にリンクすることができます。GP トグルはフィールド・カウンタに対応させられるため、RapidShot や ShotDelay のようなフィールド・カウンタの特性を受け継ぎます。GP トグルを使うときは、

- トグル・ポジションを設定します(アドレス 0x54～アドレス 0x59)

- プロトコルを設定します(アドレス 0x52)

- カウンタ・パラメータを設定します(アドレス 0x51)

- カウンタを起動します(アドレス 0x50)

プロトコル 1(カウンタへの対応なし)の場合は、ステップ 3 とステップ 4 をスキップします。

これらの 4 ステップで、GP 信号を多くの共通タスクを実行するように設定することができます。プロトコルの選択を注意深く行って、プライマリ・カウンタを使用すると、GP 信号をシステム動作で効率良く使うことができます。

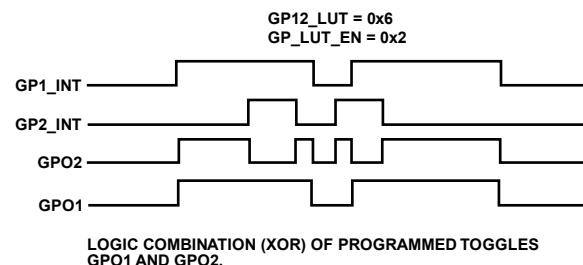

1 本の GPO と 1 個のフィールド・カウンタを使った GPO アプリケーションのシンプルな幾つかの例を次に示します。これらの例は、ビルディング・ブロックとしてさらに複雑な GPO 動作に使うことができます。さらに、特定の GPO 信号を 4 入力 LUT を経由して渡して、これらの組み合わせロジックを実現することもできます。たとえば、GPO1 と GPO2 を XOR ルックアップ・テーブルを介して入力し、その結果を GPO1、GPO2、または両方を使って出力することができます。さらに、GPO1 または GPO2 は元のトグルを出力することもできます。

表 15. プライマリ・フィールド・カウンタ・レジスタ(アドレス 0x50 とアドレス 0x51)

| Name           | Length | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRIMARY_ACTION | 3 bits | 0x0 = idle (no counter action). GPO signals still can be controlled using polarity or GPx_PROTOCOL = 1.<br>0x1 = activate counter. Single cycle of counter from 1 to counter maximum value; then returns to idle state.<br>0x2 = RapidShot. After reaching maximum counter value, counter wraps and repeats until reset.<br>0x3 = ShotTimer. Active single cycle of counter after added delay of N fields (use PRIMARY_DELAY register).<br>0x4 = test mode only.<br>0x5 = test mode only.<br>0x6 = test mode only.<br>0x7 = force to idle. |

| PRIMARY_MAX    | 4 bits | Primary counter maximum value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PRIMARY_DELAY  | 4 bits | ShotTimer. Number of fields to delay before the next primary count starts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

表 16.GPO レジスタ(アドレス 0x52～アドレス 0x59)

| Name                           | Length  | Range         | Description                                                                                                                                                                                                   |

|--------------------------------|---------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP1_PROTOCOL                   | 2 bits  | 0 to 3        | 0x0 = idle.                                                                                                                                                                                                   |

| GP2_PROTOCOL                   | 2 bits  | 0 to 3        | 0x1 = manual, no counter association.<br>0x2 = link to primary counter.<br>0x3 = primary repeat. Allows GP signals to repeat with RapidShot.                                                                  |

| GP_LINE_MODE                   | 2 bits  | Off/on        | Enables general-purpose output signals on every line.<br>0 = disable.<br>1 = enable.                                                                                                                          |

| GPx_POL <sup>1</sup>           | 2 bits  | Low/high      | Starting polarity for general-purpose signals. Only updated during PROTOCOL = 1.                                                                                                                              |

| GPO_OUTPUT_EN                  | 2 bits  | Off/on        | 0 = disable GPOx. Output pins are in high-Z state (default).<br>1 = enable GPO1 to GPO2 outputs (1 bit per output).                                                                                           |

| SEL_GPOx <sup>1</sup>          | 2 bits  | 0 to 3        | Select signal for GPO output.<br>0 = use GP toggles.<br>1 = use CLPOB.<br>2 = use PBLK.<br>3 = use high speed timing signal.                                                                                  |

| SEL_HS_GPOx <sup>1</sup>       | 2 bits  | 0 to 3        | Select GPO output high speed timing signal used.<br>0 = use delayed CLI.<br>1 = use delayed ADC output latch clock.<br>2 = use delayed SHD sample clock.<br>3 = use delayed SHP sample clock.                 |

| HBLK_EXT                       | 1 bit   | Off/on        | 1 = enable external HBLK signal to be input to GPO2 pin.                                                                                                                                                      |

| GP_LUT_EN                      | 2 bits  |               | 0 = disabled.                                                                                                                                                                                                 |

| GP12_LUT                       | 4 bits  | Logic setting | Desired logic to be realized on GPO1 combined with GPO2. Example logic settings for GP12_LUT:<br>0x6 = GPO1 XOR GPO2 (See Figure 41).<br>0x7 = GPO1 NAND GPO2.<br>0x8 = GPO1 AND GPO2.<br>0xE = GPO1 OR GPO2. |

| GPTx_TOGy_FIELD <sup>1,2</sup> | 4 bits  | 0 to 15       | Field of activity, relative to primary counter for toggle.                                                                                                                                                    |

| GPTx_TOGy_LINE <sup>1,2</sup>  | 13 bits | 0 to 8191     | Line of activity for toggle.                                                                                                                                                                                  |

| GPTx_TOGy_PIXEL <sup>1,2</sup> | 13 bits | 0 to 8191     | Pixel of activity for toggle.                                                                                                                                                                                 |

<sup>1</sup> 変数 x は汎用出力を表し、1 または 2 です。<sup>2</sup> 変数 y はトグルを表し、1 または 2 です。

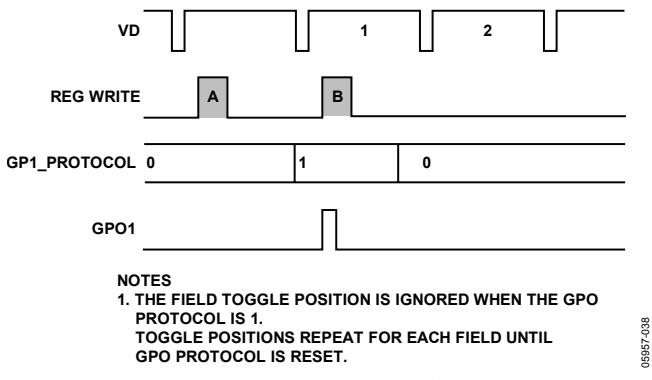

## シングル・フィールド・トグル

シングル・フィールド・トグルは、レジスタ書き込みの後にフィールド内で開始されます。フィールド内には最大2個のトグルが存在することができます。GPx\_PROTOCOL = 1に設定すると、このモードが設定されます。このモードでは、フィールド・トグル設定値を1に設定する必要があります。GPx\_PROTOCOLまでの各フィールドのトグル繰り返しは0に設定されます。GPx\_PROTOCOLは再度開始される前に1フィールドの間0にリセットする必要があります。

### 準備

GPトグル・ポジションは使用前に何時でも設定することができます。たとえば、

```

0x054 ← 0x000A001

0x055 ← 0x0002000

0x056 ← 0x000000F

```

### 詳細

- A) Field 0: 0x052 ← 0x0000001

B) Field 1: 0x052 ← 0x00000000

図 36.GP1\_PROTOCOL = 1 を使用する

シングル・フィールド・トグル

## スケジュール・トグル

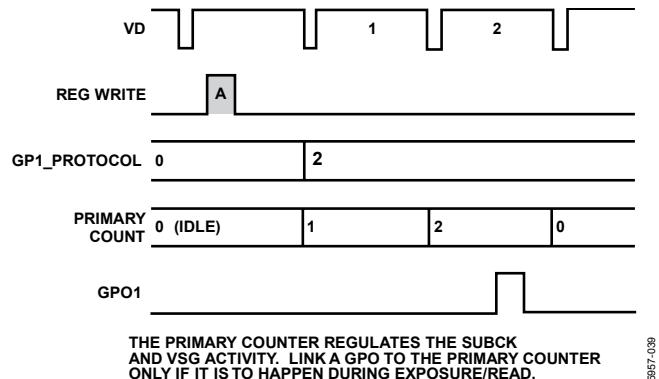

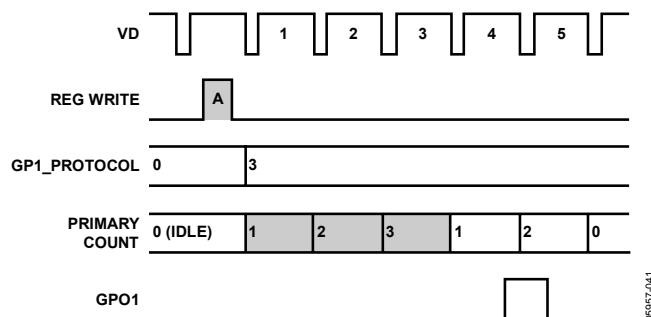

スケジュール・トグルは、次のフィールドで発生するようになります。たとえば、フィールド1に1個のトグルが存在し、次のトグルがフィールド3に存在することができます。GPx\_PROTOCOL = 2でこのモードを設定すると、GPOはプライマリ・フィールド・カウンタに従うことが指示されます。

### 準備

GPトグル・ポジションは使用前に何時でも設定することができます。たとえば、

```

0x054 ← 0x00C4002

0x055 ← 0x0004000

0x056 ← 0x00000B3

```

### 詳細

- A) Field 0: 0x050 ← 0x0000001

0x052 ← 0x0000002

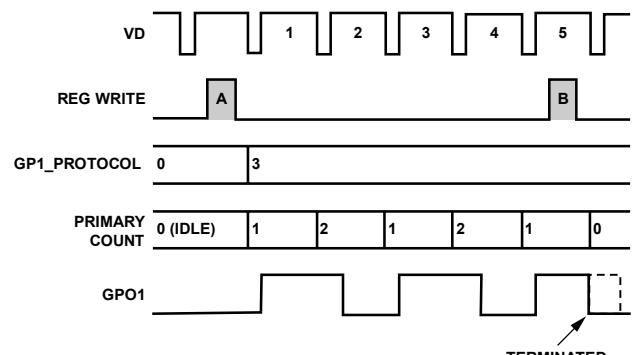

図 37.GP1\_PROTOCOL = 2 を使用するスケジュール・トグル

## RapidShot シーケンス

RapidShot技術は、スケジュール・トグルの連続繰り返しを提供します。スケジュール・トグルの場合と同様に、パルスが複数のフィールドにわたって機能することができます。GPx\_PROTOCOL = 3にするとこのモードが設定され、GPOはプライマリ・フィールド・カウンタに従うことが指示されます。GPx\_PROTOCOLは再起動される前に、1フィールド間0にリセットされる必要があります。

### 準備

GPOトグル・ポジションは使用前に何時でも設定することができます。たとえば、

```

0x051 ← 0x0000002

0x054 ← 0x000A001

0x055 ← 0x0004000

0x056 ← 0x000000F

0x052 ← 0x0000003

```

### 詳細

- A) Field 0: 0x050 ← 0x0000002

B) Field 2: 0x050 ← 0x0000007

図 38.GP1\_PROTOCOL = 3 を使用する RapidShot トグル動作

## ShotTimer シーケンス

ShotTimer 技術は、スケジュール・トグルの内部遅延を提供します。遅延はフィールド数で表されます。

### 準備

GP トグル・ポジションは使用前に何時でも設定することができます。たとえば、

```

0x051 ← 0x00000032

0x054 ← 0x000A001

0x055 ← 0x0004000

0x056 ← 0x000000F

0x052 ← 0x0000002

```

### 詳細

A) Field 0: 0x050 ← 0x00000003

図 39.GP1\_PROTOCOL = 3 を使用する ShotDelay トグル動作

## GP ルックアップ・テーブル(LUT)

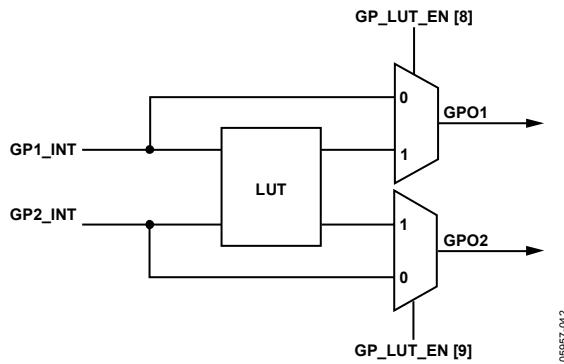

AD9979 は、GP が出力に設定されたとき、連続する GP 信号の各対に対する LUT を内蔵しています。GPO1 対からの外部 GPO 出力には、LUT の結果または元の GPO 内部信号を出力することができます。

図 40.GPO1 信号と GPO2 信号の内部 LUT

アドレス 0x52 は、LUT の動作を制御し、結果を受け取る信号を指定します。各 4 ビット・レジスタにより、GPO1 と GPO2 の任意のロジック結合を実現することができます。表 17 に、GP12\_LUT[13:10]のレジスタ値を指定する方法を示します。XOR、NAND、AND、OR の結果を示していますが、任意の 4 ビット組み合わせが可能です。XOR ゲーティングのシンプルな例を図 41 に示します。

表 17.GPO1 値と GPO2 値による LUT 出力

| GPO2 | GPO1 | LUT |      |     |    |

|------|------|-----|------|-----|----|

|      |      | XOR | NAND | AND | OR |

| 0    | 0    | 0   | 1    | 0   | 0  |

| 0    | 1    | 1   | 1    | 0   | 1  |

| 1    | 0    | 1   | 1    | 0   | 1  |

| 1    | 1    | 0   | 0    | 1   | 1  |

図 41. GPO1 XOR GPO2 の LUT 例

## フィールド・カウンタと GPO の制約

1. 使い方に影響するフィールド・カウンタと GPO 信号の既知の制約の一覧を次に示します。

2. フィールド・カウンタ・トリガー(アドレス 0x50)は、各 VD 区間の開始時にセルフリセットされます。このため、このアドレスに対するシーケンシャルな書き込みの間には、1VD 区間が必要です。

3. プロトコルを 1 に設定すると、各フィールドに対するトグルが、プロトコルがアイドルに設定されるまで繰り返されます。

## アナログ・フロントエンドの説明と動作

図 42. アナログ・フロント・エンドの機能ブロック図

05957-044

AD9979 の信号処理チェーンを図 42 に示します。各処理ステップは、生の CCD ピクセル・データから高品質イメージを得るために不可欠です。

### DC の再生

CCD 出力信号の大きな DC オフセットを小さくするために、DC 再生回路を外付けの 0.1μF の直列カッピング・コンデンサと組み合わせて使います。この回路は CCD 信号の DC レベルを約 1.2 V に再生して、AD9979 の 1.8 V のコア電源電圧と互換性を持つようにします。DC 再生スイッチは SHP サンプル・パルス時間アクティブになります。

オプションの PBLK 信号を使って大きな信号振幅を CCD 入力からアイソレーションするときは、DC 再生回路をディスエーブルすることができます(アナログ・プリプランキングのセクション参照)。アドレス 0x00 のビット 6 により、PBLK インターバルで DC 再生をアクティブにするか否かが制御されます(表 24 参照)。

### アナログ・プリプランキング

CCD プランキング・インターバルまたはサブストレート・クロック・インターバルで、AD9979 への CCD 入力信号振幅が推奨入力範囲を超えて大きくなることがあります。PBLK 信号を使って、大きな信号振幅から CDS 入力をアイソレーションすることができます。図 42 に示すように、PBLK がアクティブのとき(ロー・レベル)、CDS 入力が CCDIN<sub>x</sub> ピンからアイソレーションされ(S1 がオープン)、内部でグラウンドに短絡されます(S2 がクローズ)。

PBLK のアクティブ時に、すべてゼロ出力または設定されているクランプ・レベルとなるように ADC 出力を設定することができます。

PBLK の間 CDS 入力が短絡されるので、PBLK パルスと同じアクティブ時間中に CLPOB パルスを使えないことに注意してください。

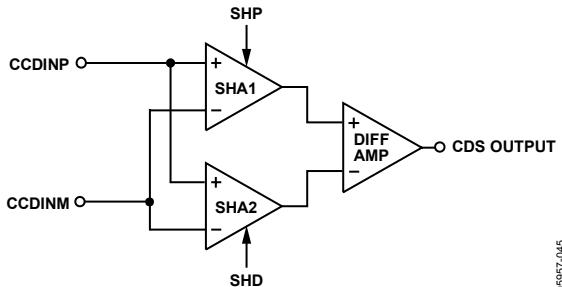

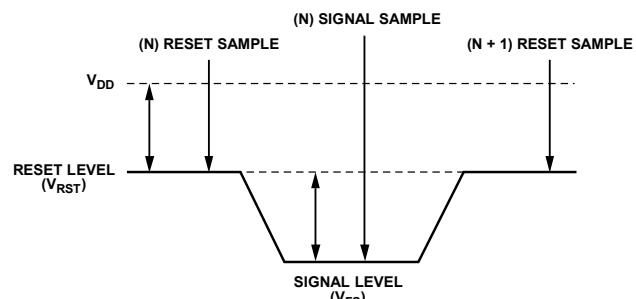

### 関連ダブル・サンプラ(CDS)

CDS 回路は各 CCD ピクセルを 2 回サンプルしてビデオ情報を取り出し、低周波数ノイズを除去します。図 19 に示すタイミング図に、内部で発生された 2 個の CDS クロック(SHP と SHD)を使って、それぞれリファレンス・レベルと CCD 信号レベルをサンプルする方法を示します。SHP と SHD のサンプリング・エッジの配置は、アドレス 0x36 にある SHPLOC レジスタと SHDLOC レジスタにより指定されます。これら 2 クロック信号の配置は、CCD から最適な性能を取り出すために重要です。

CDS ゲインは 4 ステップで可変であり、CDSGAIN(アドレス 0x04)を使って、-3 dB、0 dB(デフォルト)、+3 dB、+6 dB に設定されます(表 24 参照)。+3 dB と+6 dB の設定を使うとノイズ性能が向上しますが、これらの設定では入力範囲が小さくなります(表 4 参照)。

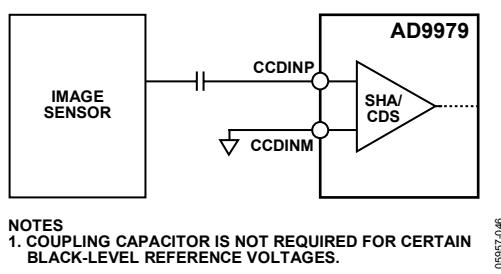

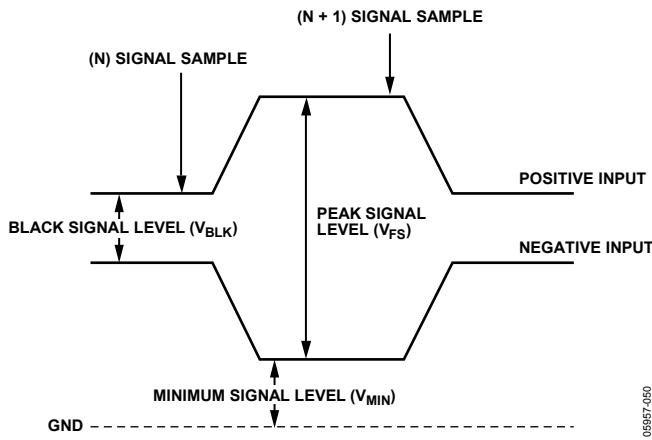

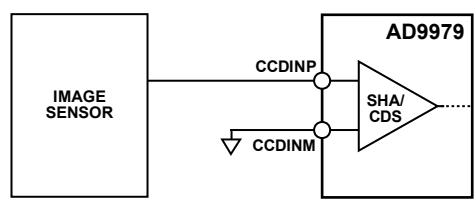

## 入力構成

CDS回路は各CCDピクセルを2回サンプルしてビデオ情報を取り出し、低周波数ノイズを除去します(図43参照)。CDSでは反転CDSモード、非反転CDSモード、SHAモードの3種類の構成が可能です。CDSMODE(アドレス0x00[9:8])を使って、使用する構成を選択します(表24参照)。

図43.CDSのブロック図(概念図)

## 反転CDSモード

この構成では、CCDからの信号がCDSシステム(CCDINP)の正入力に入力され、負側(CCDINM)はグラウンドに接続されます(図44参照)。この構成のCDSMODE設定値は0x00です。従来型CCDアプリケーションでは、AD9979のDC再生回路を使ってAVDD電源レベルより低い約1.5Vにリセット・レベルを設定して、この構成を使います。最大サチレーション・レベルは、リセット・レベルより1.0V下になります(図45と表18参照)。1.4Vの最大サチレーション電圧は、CDSの最小ゲイン設定を使って実現することもできます。

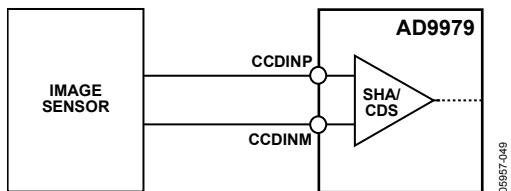

図44.シングル入力のCDS構成

図45.従来型の反転CDS信号

表18.反転電圧レベル

| Signal Level   | Symbol    | Min            | Typ            | Max      | Unit |