# 低消費電力の18 MHz 可変ゲイン・アンプ

## データシート

AD8338

### 特長

電圧制御ゲイン範囲: 0 dB~80 dB

ゲイン= 40 dB で電源電流 3 mA

低周波(LF) 18 MHz まで動作

電源電圧範囲: 3.0 V~5.0 V

低ノイズ: 80 dB ゲインで 4.5 nV/√Hz

フル差動信号パス

オフセット補正機能(ヌル・オフセット)

内蔵リファレンス電圧: 1.5 V

16 ピン LFCSP パッケージを採用

自動ゲイン制御機能

高ダイナミックレンジ信号に対する広いゲイン範囲

### アプリケーション

誘導性テレメタリ・システムのフロント・エンド

超音波信号レシーバ

ADC 駆動用の信号圧縮

AGC アンプ

### 概要

AD8338 は、フル差動信号パス、低消費電力、低ノイズ、周波数に対して安定したゲインを必要とするアプリケーションを対象とする可変ゲイン・アンプ(VGA)です。入力は差動ですが、必要に応じてシングルエンド・ソースからこのデバイスを駆動することができます。

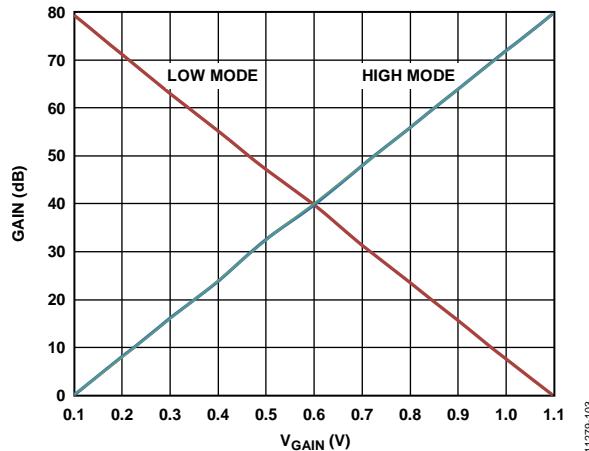

基本ゲイン関数は、GAIN ピンに加えられる電圧で制御される、デシベル・リニアな関数です。公称ゲイン範囲は、0.1 V~1.1 V の制御電圧に対して 0 dB~80 dB であり、スロープは 12.5 mV/dB です。公称ゲイン範囲は、VGA に対する電流入力である INPD ピンと INMD ピンを直接使用して上下にシフトすることができます。例えば、50 Ω 抵抗で INPD ピンと INMD ピンを使って駆動すると、ゲイン範囲は上に 20 dB シフトします。すなわち、20 dB~100 dB になり、デバイスの入力換算ノイズが 1.5 nV/√Hz に低下します。さらに、MODE ロジック・ピンを使ってゲイン・スロープを反転させることができます。

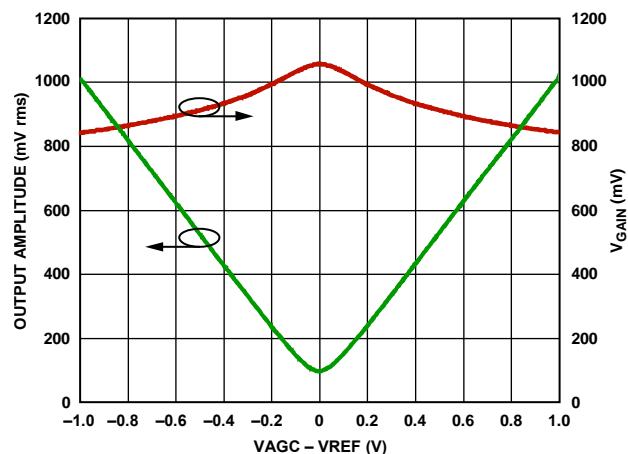

AD8338 には、入力オフセット補正と自動ゲイン制御(AGC)を可能にする回路ブロックが追加されています。DC オフセット電圧はオフセット補正回路で除去されます。この補正回路は、外付けコンデンサでコーナー周波数を設定できるハイパス・フィルタのように動作します。AGC 機能は AD8338 のゲインを変化させて、RMS 出力電圧を一定に維持します。VREF ピンの電圧を基準として VAGC ピンへ外部から加える電圧により出力 RMS 振幅が設定されます。DETO ピンとグラウンドとの間のコンデンサにより AGC 回路の応答時間が設定されます。

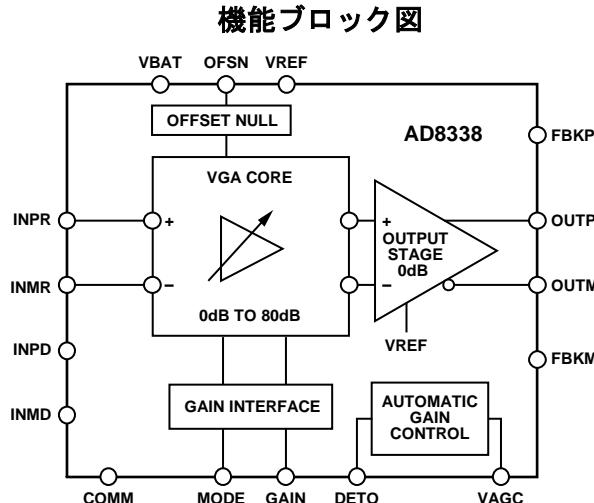

図 1.

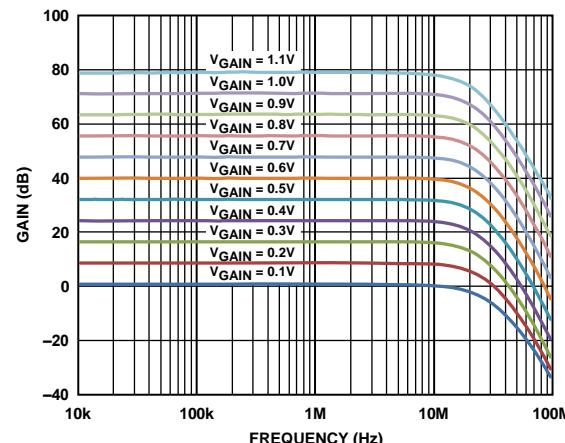

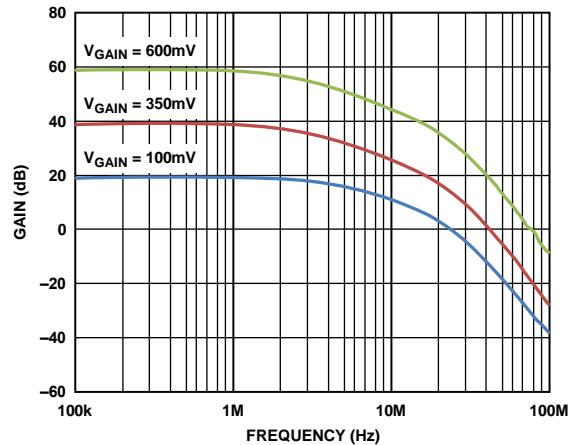

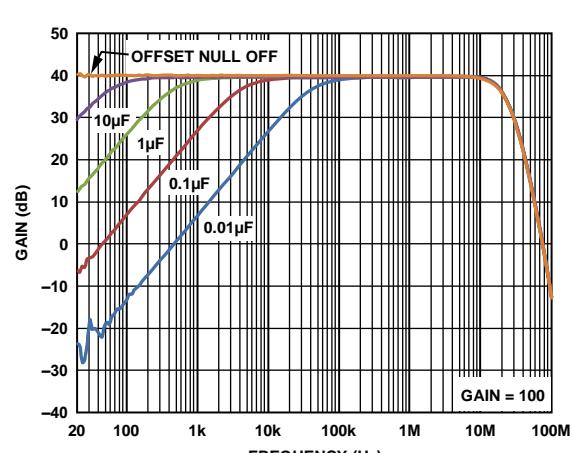

図 2. ゲインの周波数特性

11279-001

11279-005

AD8338 は、VGA コアの内部加算ノードと出力アンプに対するアクセスを提供することにより多才な機能を提供します。数個の外付け受動部品を追加すると、デバイスのゲイン、帯域幅、入力インピーダンス、ノイズ・プロファイルをアプリケーションに合わせてカスタマイズすることができます。

AD8338 は、3.0 V~5.0 V の単電源電圧を使用するため、非常に電源効率がよく、中心ゲインでの静止電流はわずか 3 mA で済みます。AD8338 は、3 mm × 3 mm の RoHS 準拠 16 ピン LFCSP パッケージを採用し、-40°C~+85°C の工業用温度範囲で仕様が規定されています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|               |   |

|---------------|---|

| 特長            | 1 |

| アプリケーション      | 1 |

| 概要            | 1 |

| 機能ブロック図       | 1 |

| 改訂履歴          | 2 |

| 仕様            | 3 |

| AC 仕様         | 3 |

| 絶対最大定格        | 4 |

| 熱抵抗           | 4 |

| ESD の注意       | 4 |

| ピン配置およびピン機能説明 | 5 |

|                           |    |

|---------------------------|----|

| 代表的な性能特性                  | 6  |

| 動作原理                      | 12 |

| はじめに                      | 12 |

| ゲイン関数の説明                  | 16 |

| 出力同相モード電圧の調整              | 17 |

| アプリケーション情報                | 18 |

| シンプルなオン・オフ・キーイング(OOK)レシーバ | 18 |

| AD8338 と ADC とのインターフェース   | 19 |

| 外形寸法                      | 20 |

| オーダー・ガイド                  | 20 |

## 改訂履歴

## 11/13—Rev. 0 to Rev. A

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| Changes to Features Section, Applications Section, and General Descriptions Section | 1  |

| Changes to Table 1                                                                  | 3  |

| Changes to Pin 13 and Pin 14 Descriptions                                           | 5  |

| Added Conditions to Typical Performance Characteristics;                            |    |

| Changes to Figure 4 and Figure 5; Changes to Figure 6, Figure 7, Figure 8 Captions  | 6  |

| Changes to Figure 12 and Figure 13                                                  | 7  |

| Changes to Figure 18 and Figure 19                                                  | 8  |

| Changes to Figure 22                                                                | 9  |

| Changes to Figure 35 and Figure 36                                                  | 11 |

| Replaced Theory of Operation Section                                                | 12 |

| Changes to Figure 50                                                                | 18 |

| Changes to Ordering Guide                                                           | 20 |

## 4/13—Revision 0: Initial Version

## 仕様

## AC 仕様

特に指定がない限り、 $V_{BAT} = 3.0\text{ V}$ 、 $T_A = 25^\circ\text{C}$ 、 $OUTP$  と  $OUTM$  で  $C_L = 2\text{ pF}$ 、 $R_L = \infty$ 、MODE ピン=ハイ・レベル、 $R_{IN} = 2 \times 500\text{ }\Omega$ 、 $V_{GAIN} = 0.6\text{ V}$ 、差動動作。

表 1.

| Parameter                            | Test Conditions/Comments                                                                        | Min  | Typ  | Max  | Unit                   |

|--------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|------------------------|

| INPUT INTERFACE                      | INPD, INMD, INPR, INMR pins                                                                     |      |      |      |                        |

| Input Voltage Range                  |                                                                                                 | 3    |      |      | V p-p                  |

| –3 dB Bandwidth                      |                                                                                                 | 18   |      |      | MHz                    |

| Input Resistance                     | Standard configuration using the INPR and INMR inputs                                           | 0.8  | 1    | 1.2  | k $\Omega$             |

| Input Capacitance                    |                                                                                                 |      | 2    |      | pF                     |

| OUTPUT INTERFACE                     | OUTP and OUTM pins                                                                              |      |      |      |                        |

| Small Signal Bandwidth               | $V_{GAIN} = 0.6\text{ V}$                                                                       | 18   |      |      | MHz                    |

| Peak Slew Rate                       | $V_{GAIN} = 0.6\text{ V}$                                                                       | 50   |      |      | V/ $\mu\text{s}$       |

| Peak-to-Peak Output Swing            | Differential output                                                                             | 2.8  |      |      | V p-p                  |

| Common-Mode Voltage                  |                                                                                                 | 1.5  |      |      | V                      |

| Input-Referred Voltage Noise         |                                                                                                 |      |      |      |                        |

| Using Internal Resistors             | $V_{GAIN} = 1.1\text{ V}$                                                                       | 4.5  |      |      | nV/ $\sqrt{\text{Hz}}$ |

|                                      | $V_{GAIN} = 0.6\text{ V}$                                                                       | 15   |      |      | nV/ $\sqrt{\text{Hz}}$ |

|                                      | $V_{GAIN} = 0.1\text{ V}$                                                                       | 150  |      |      | nV/ $\sqrt{\text{Hz}}$ |

|                                      | $V_{GAIN} = 1.1\text{ V}$                                                                       | 1.5  |      |      | nV/ $\sqrt{\text{Hz}}$ |

| Using External 47 $\Omega$ Resistors |                                                                                                 |      |      |      |                        |

| Offset Voltage                       | RTO, $V_{GAIN} = 0.1\text{ V}$ , offset null enabled                                            | –10  |      | +10  | mV                     |

|                                      | RTO, $V_{GAIN} = 0.6\text{ V}$ , offset null enabled                                            | –10  |      | +10  | mV                     |

|                                      | RTO, $V_{GAIN} = 0.1\text{ V}$ , offset null disabled                                           | –50  |      | +50  | mV                     |

|                                      | RTO, $V_{GAIN} = 0.6\text{ V}$ , offset null disabled                                           | –200 |      | +200 | mV                     |

| POWER SUPPLY                         |                                                                                                 |      |      |      |                        |

| $V_{BAT}$                            |                                                                                                 | 3.0  |      | 5.0  | V                      |

| $I_{VBAT}$                           | Min gain, $V_{GAIN} = 0.1\text{ V}$                                                             |      | 6.0  | 8.0  | mA                     |

|                                      | Mid gain, $V_{GAIN} = 0.6\text{ V}$                                                             |      | 3.0  | 3.8  | mA                     |

|                                      | Max gain, $V_{GAIN} = 1.1\text{ V}$                                                             |      | 4.5  | 6.0  | mA                     |

| GAIN CONTROL                         |                                                                                                 |      |      |      |                        |

| Gain Range                           | Standard configuration using the INPR and INMR inputs                                           | 0    |      | 80   | dB                     |

| Gain Span                            |                                                                                                 |      | 80   |      | dB                     |

| Gain Voltage                         | $V_{GAIN}$ relative to COMM                                                                     | 0.1  |      | 1.1  | V                      |

| Gain Slope                           |                                                                                                 | 77   | 80   | 83   | dB/V                   |

|                                      |                                                                                                 | 12   | 12.5 | 13   | mV/dB                  |

| Gain Accuracy                        | Standard configuration using the INPR and INMR inputs; $0.1\text{ V} < V_{GAIN} < 1.1\text{ V}$ | –2   | +0.5 | +2   | dB                     |

| VREF REFERENCE OUTPUT                |                                                                                                 |      |      |      |                        |

| Output Voltage                       |                                                                                                 |      | 1.5  |      | V                      |

| Output Current                       |                                                                                                 |      | 5    |      | mA                     |

| Accuracy                             |                                                                                                 |      | 2    |      | %                      |

| DETO OUTPUT CURRENT                  |                                                                                                 |      | ±10  |      | $\mu\text{A}$          |

| MODE INPUT                           |                                                                                                 |      |      |      |                        |

| Logic High                           |                                                                                                 | 2.5  |      | VBAT | V                      |

| Logic Low                            |                                                                                                 | COMM |      | 0.6  | V                      |

| AGC CONTROL                          | $MODE = 0\text{ V}$                                                                             |      |      |      |                        |

| Maximum Target Amplitude             | Expected rms output value for target = $V_{AGC} - V_{REF} = 1.0\text{ V}$                       |      | 1.0  |      | V rms                  |

## 絶対最大定格

表 2.

| Parameter                                                                    | Rating           |

|------------------------------------------------------------------------------|------------------|

| VBAT to COMM                                                                 | -0.3 V to +5.5 V |

| INPR, INPD, INMD, INMR, MODE, GAIN, FBKM, FBKP, OUTM, OUTP, VAGC, VREF, OFSN | COMM to VBAT     |

| Operating Temperature Range                                                  | -40°C to +85°C   |

| Storage Temperature Range                                                    | -65°C to +150°C  |

| Maximum Junction Temperature                                                 | 150°C            |

| Lead Temperature (Soldering, 10 sec)                                         | 300°C            |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

### 熱抵抗

表 3. 热抵抗

| Package Type  | $\theta_{JA}$ | Unit |

|---------------|---------------|------|

| 16-Lead LFCSP | 48.75         | °C/W |

### ESD の注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

## ピン配置およびピン機能説明

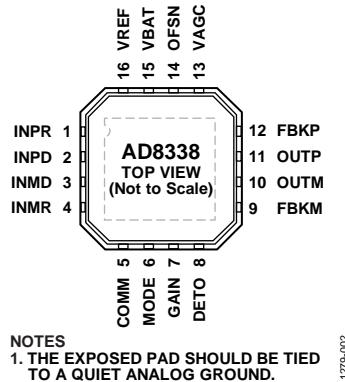

図 3. ピン配置

表 4. ピン機能の説明

| ピン番号 | 記号   | 説明                                                                                                                                             |

|------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | EPAD | エクスポート・パッド。エクスポート・パッドは、安定なアナログ・グラウンドへ接続する必要があります。                                                                                              |

| 1    | INPR | 電圧入力アプリケーション用の正の 500 Ω 抵抗入力。                                                                                                                   |

| 2    | INPD | 電流入力アプリケーション用の正の入力。                                                                                                                            |

| 3    | INMD | 電流入力アプリケーション用の負の入力。                                                                                                                            |

| 4    | INMR | 電圧入力アプリケーション用の負の 500 Ω 抵抗入力。                                                                                                                   |

| 5    | COMM | グラウンド。                                                                                                                                         |

| 6    | MODE | ゲイン・モード。このピンで、ゲイン制御用の正または負のゲイン・スロープを選択します。このピンを VBAT に接続した場合、AD8338 のゲインは GAIN ピンの電圧増加に比例して増加します。このピンを COMM へ接続した場合、GAIN ピンの電圧が増加するとゲインは減少します。 |

| 7    | GAIN | ゲイン制御入力、12.5 mV/dB または 80 dB/V。                                                                                                                |

| 8    | DETO | 検出器出力端子、±10 μA。AGC 機能を使わない場合、DETO は COMM に接続します。                                                                                               |

| 9    | FBKM | 負帰還ノード。詳細については、FBKP、FBKM、OUTP、OUTM の各ピンのセクションを参照してください。                                                                                        |

| 10   | OUTM | 負側出力。                                                                                                                                          |

| 11   | OUTP | 正側出力。                                                                                                                                          |

| 12   | FBKP | 正帰還ノード。詳細については、FBKP、FBKM、OUTP、OUTM の各ピンのセクションを参照してください。                                                                                        |

| 13   | VAGC | 自動ゲイン制御回路に対する電圧。このピンは、AGC 回路のターゲット rms 出力電圧を制御します。詳細については、AGC 回路、VAGC ピンのセクションを参照してください。AGC 機能を使わない場合、VAGC は VREF に接続します。                      |

| 14   | OFSN | オフセット・ヌル端子。詳細については、オフセット補正回路、OFSN ピンのセクションを参照してください。オフセット・ヌル機能を使わない場合は、OFSN をグラウンドへ接続します。その他の場合、コンデンサを VREF へ接続して、オフセット・ヌル・ハイパス・コーナーの設定に使います。  |

| 15   | VBAT | 正電源電圧                                                                                                                                          |

| 16   | VREF | 内部 1.5 V リファレンス電圧。                                                                                                                             |

## 代表的な性能特性

特に指定がない限り、 $V_{BAT} = 3.0\text{ V}$ 、 $T_A = 25^\circ\text{C}$ 、 $\text{OUTP}$ と $\text{OUTM}$ で $C_L = 2\text{ pF}$ 、 $R_L = \infty$ 、MODE ピン=ハイ・レベル、 $R_{IN} = 2 \times 500\text{ }\Omega$ 、 $V_{GAIN} = 0.6\text{ V}$ 、差動動作。

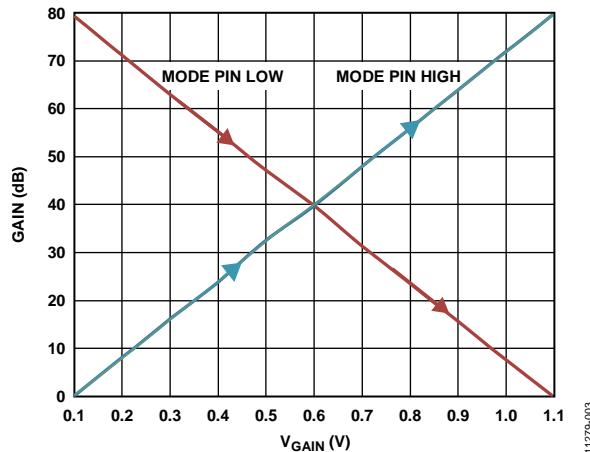

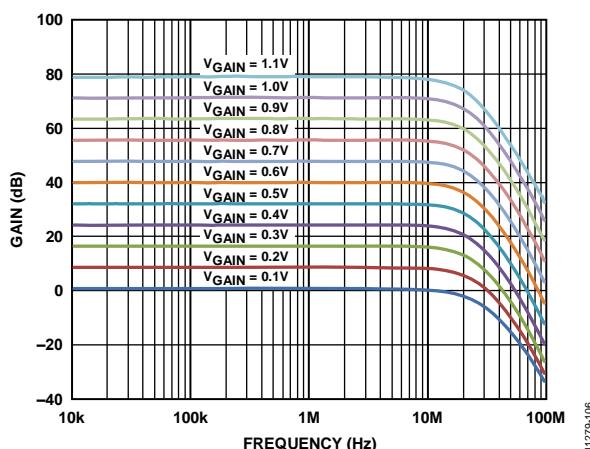

図 4.  $V_{GAIN}$  対ゲイン図 7. ゲインの周波数特性、 $R_{IN} = 50\text{ }\Omega$ 、20 dB ステップ

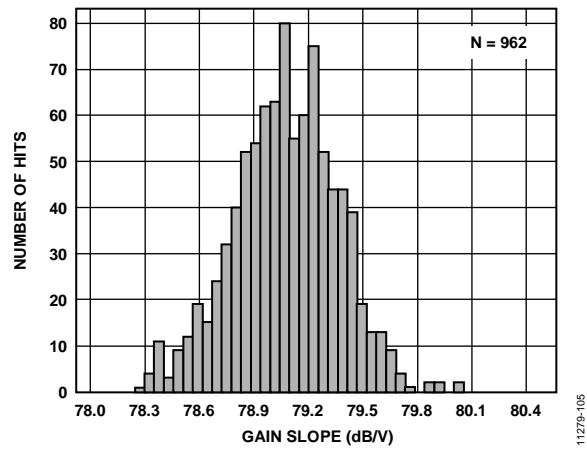

図 5. ゲインスロープのヒストグラム

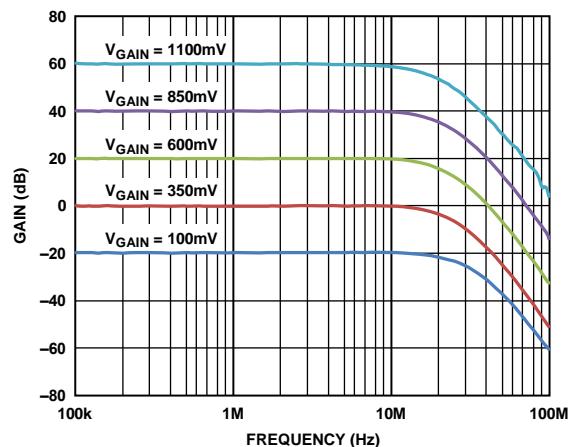

図 8. ゲインの周波数特性、 $R_{IN} = 5\text{ k}\Omega$ 、20 dB ステップ

図 6. ゲインの周波数特性、8 dB ステップ

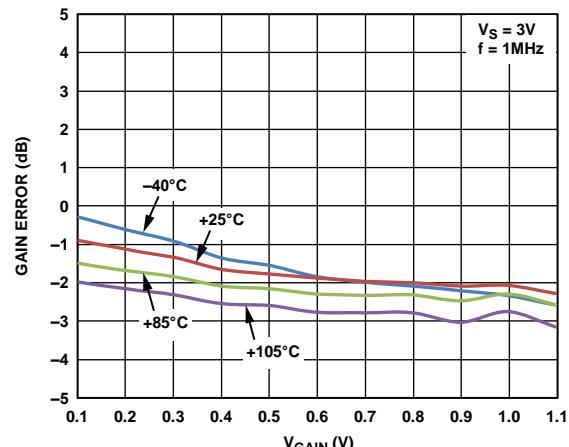

図 9. 様々な温度での  $V_{GAIN}$  対ゲイン誤差

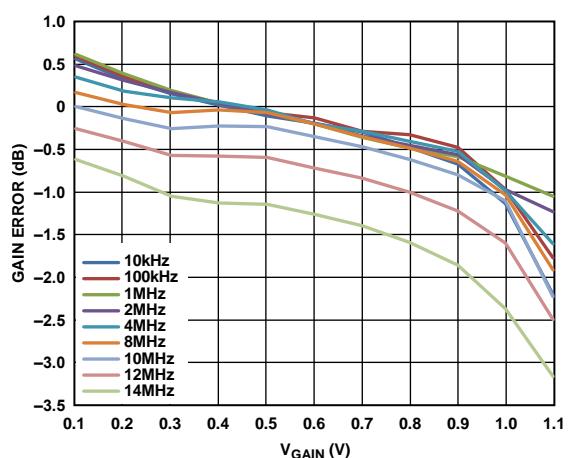

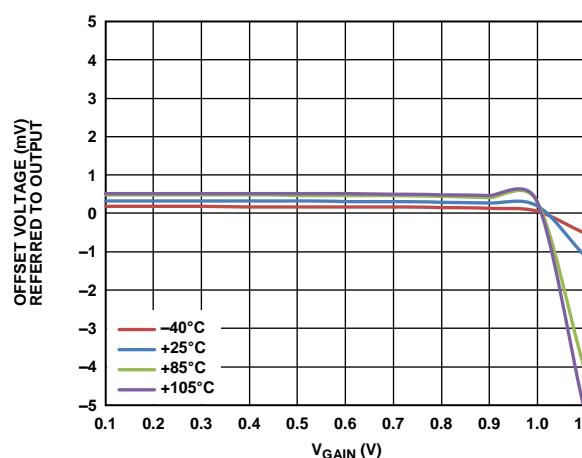

図 10. 様々な周波数での  $V_{GAIN}$  対ゲイン誤差図 13.  $V_{GAIN}$  対差動オフセット電圧、オフセット・ヌル・オン

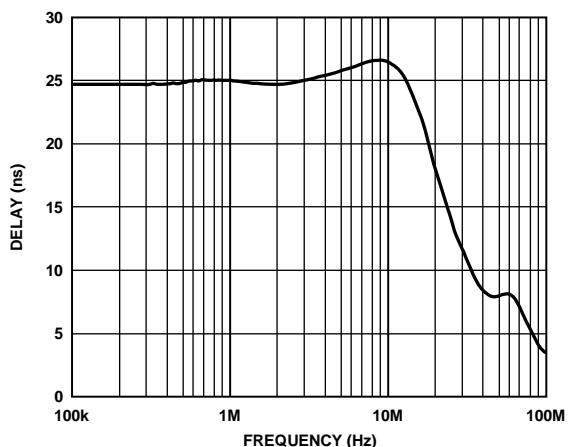

図 11. 群遅延の周波数特性

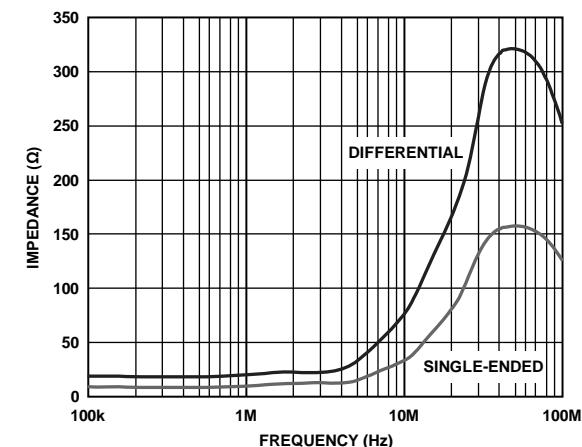

図 14. 出力インピーダンスの周波数特性

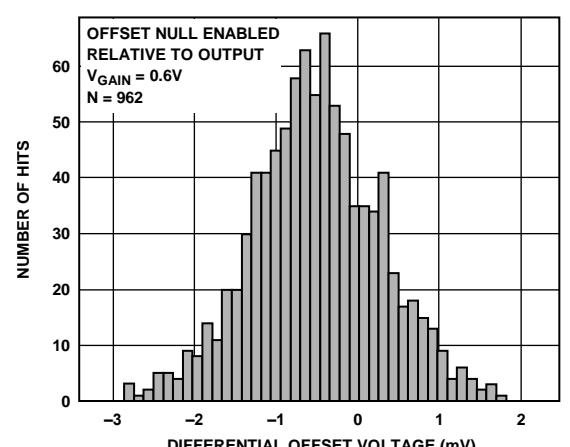

図 12. 差動オフセット電圧のヒストグラム

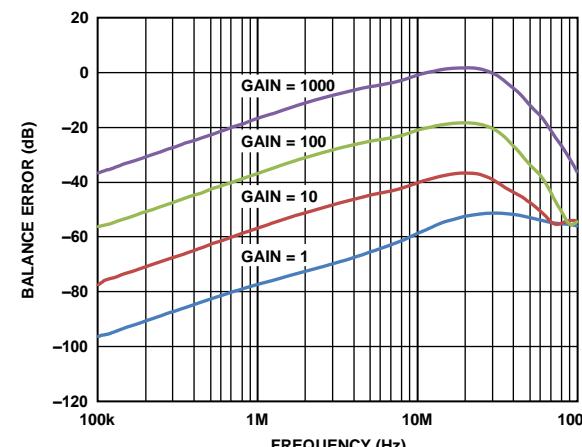

図 15. 出力バランス誤差の周波数特性

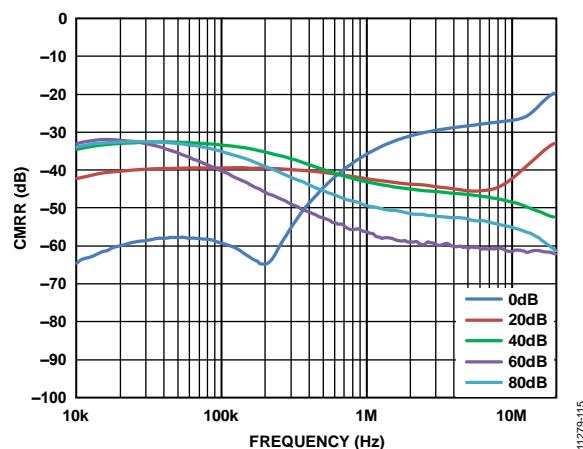

図 16. 様々なゲインでの CMRR の周波数特性、オフセット・ヌル・オン、入力換算

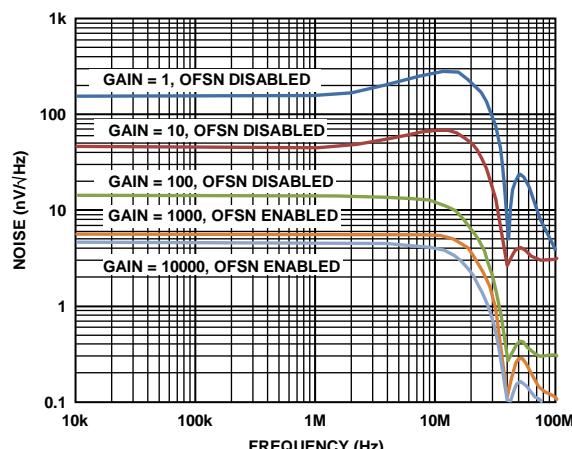

図 19. 入力換算ノイズの周波数特性

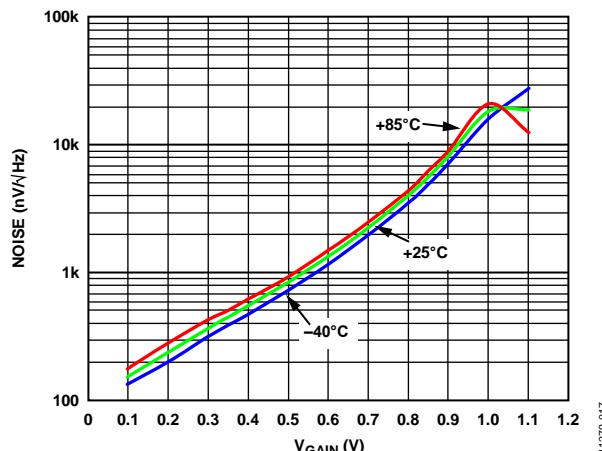

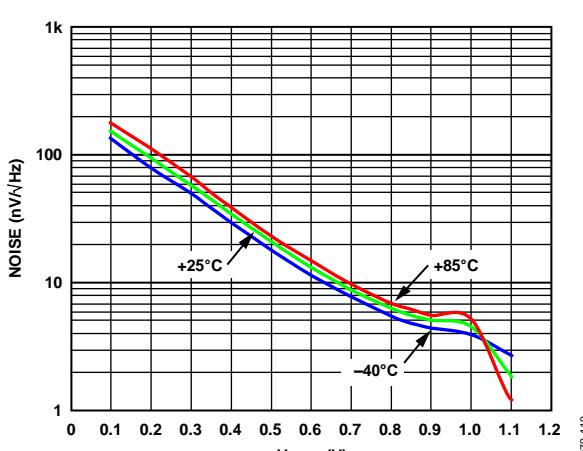

図 17.  $V_{GAIN}$  対出力換算ノイズ

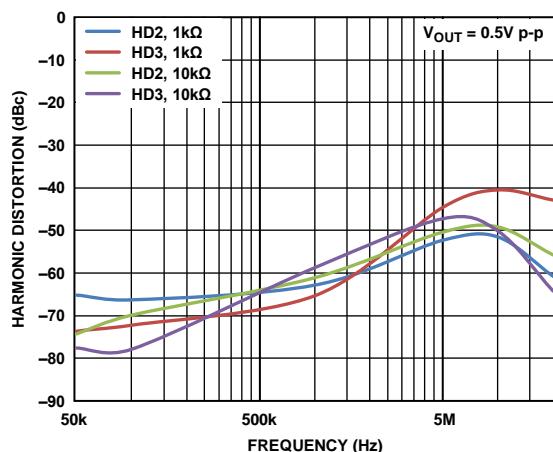

図 20. 高調波歪みの周波数特性

図 18.  $V_{GAIN}$  対入力換算ノイズ

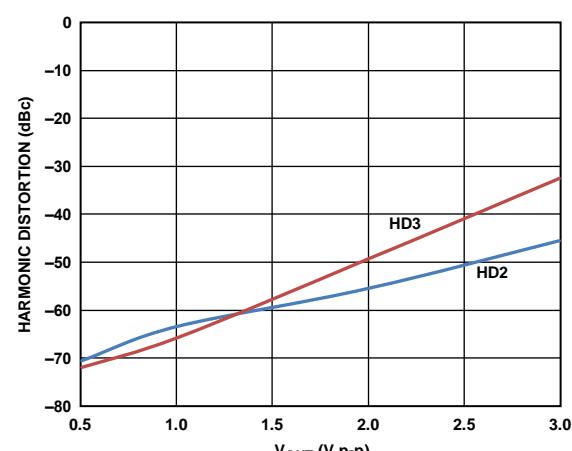

図 21. 出力振幅対高調波歪み

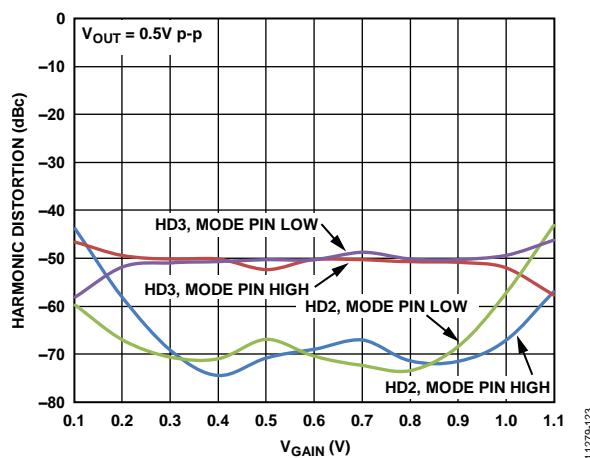

図 22.  $V_{GAIN}$  対高調波歪み

11279-123

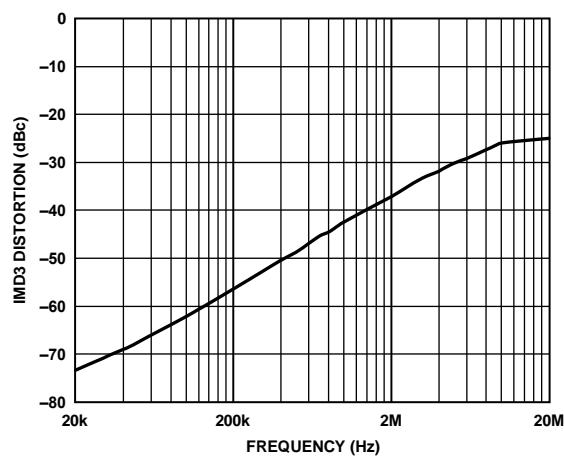

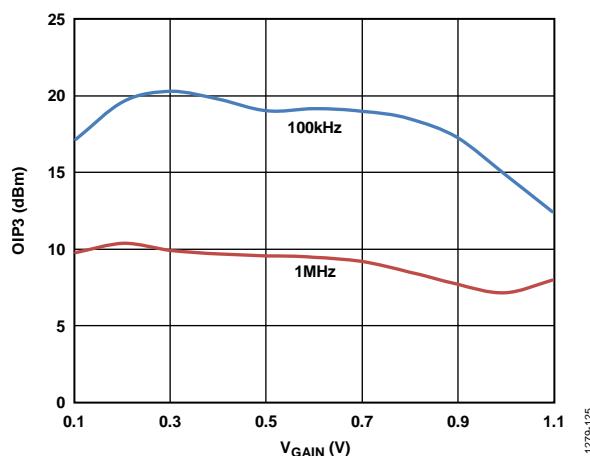

図 25. IMD3 歪みの周波数特性

11279-124

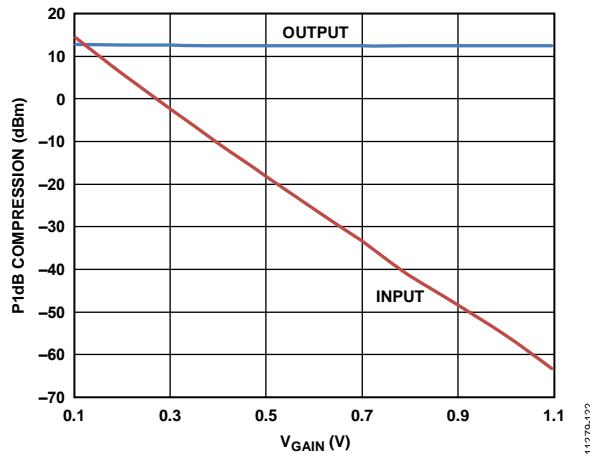

図 23.  $V_{GAIN}$  対入力と出力の 1 dB 圧縮

11279-122

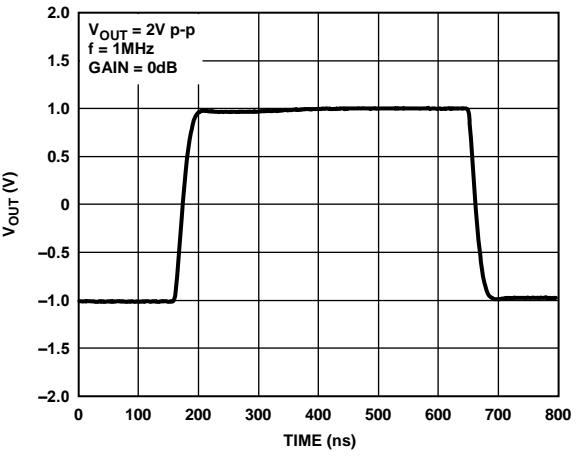

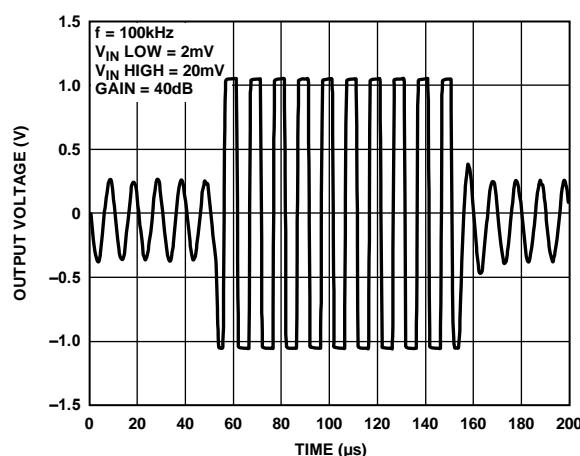

図 26. 大信号パルス応答、 $V_{GAIN} = 0$  V

11279-027

図 24.  $V_{GAIN}$  対 OIP3

11279-125

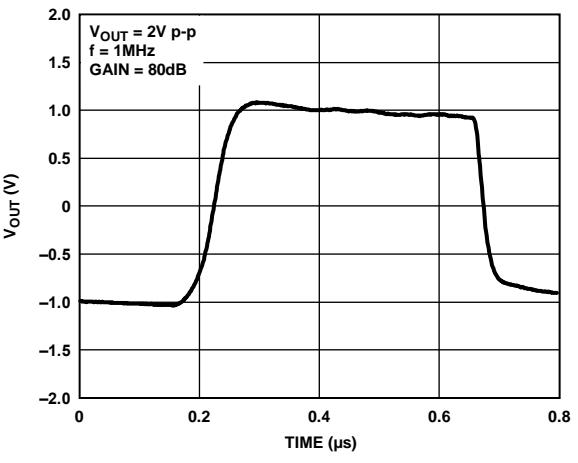

図 27. 大信号パルス応答、 $V_{GAIN} = 1.0$  V

11279-028

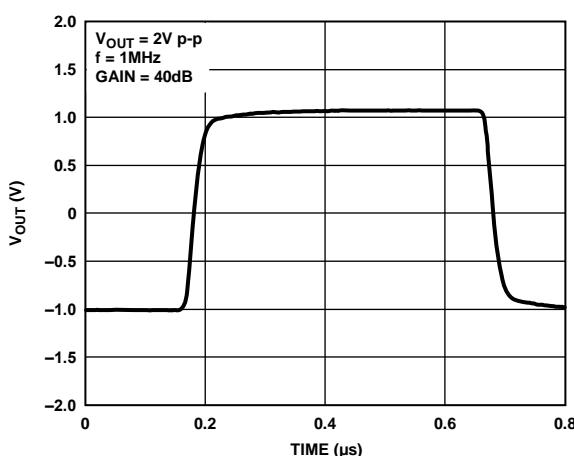

図 28.大信号パルス応答、 $V_{GAIN} = 0.6$  V

図 31.オーバードライブ回復

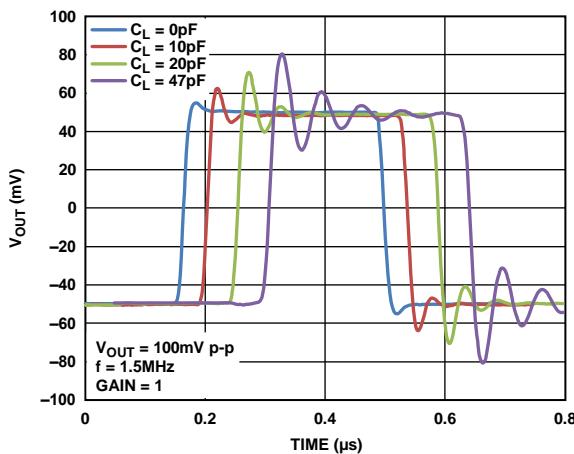

図 29.小信号パルス応答(容量負荷変化)

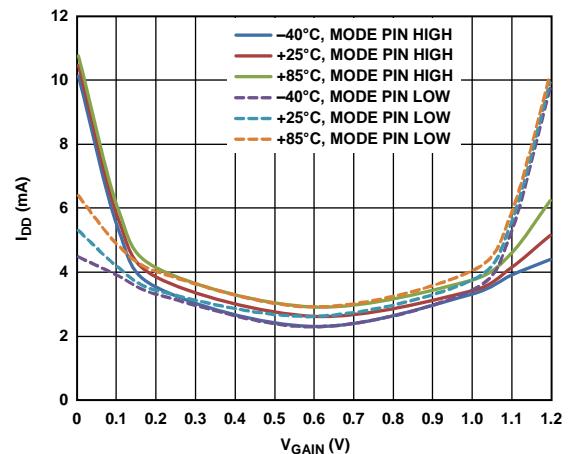

図 32. $V_{GAIN}$  対電源電流

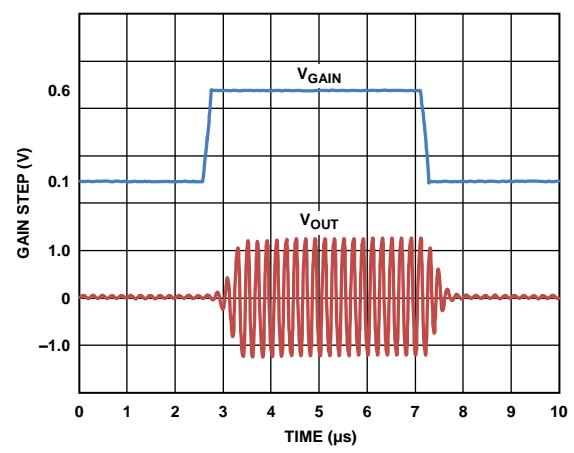

図 30.ゲイン・ステップ応答

図 33.オフセット・ヌル・コンデンサ対

オフセット・ヌル帯域幅

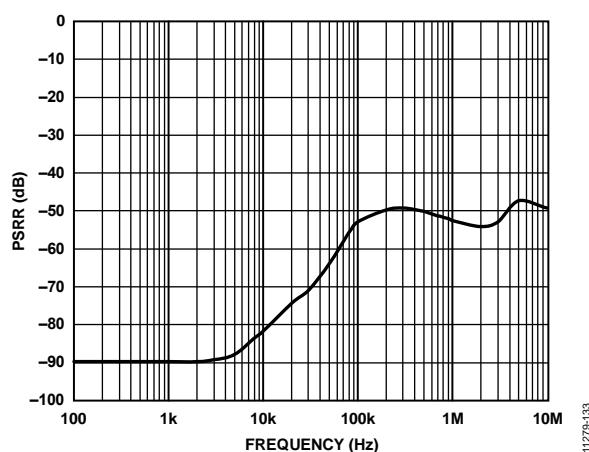

図 34.PSRR の周波数特性

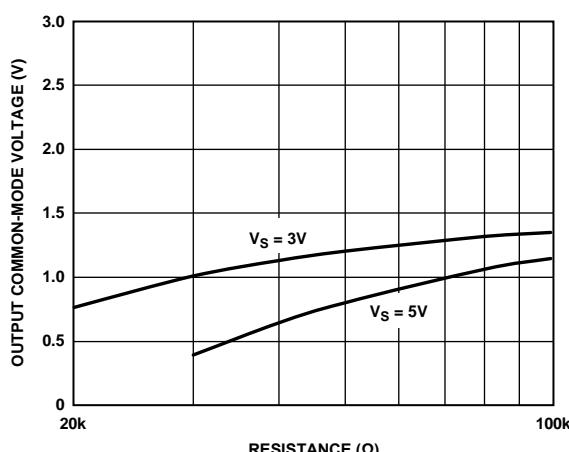

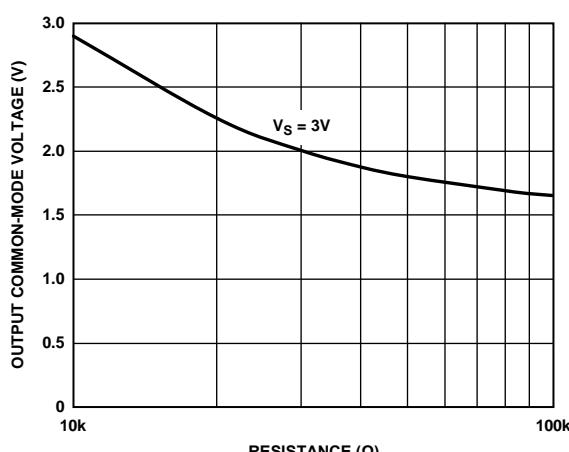

図 37.VBAT の  $R_{CM}$  対出力同相モード電圧

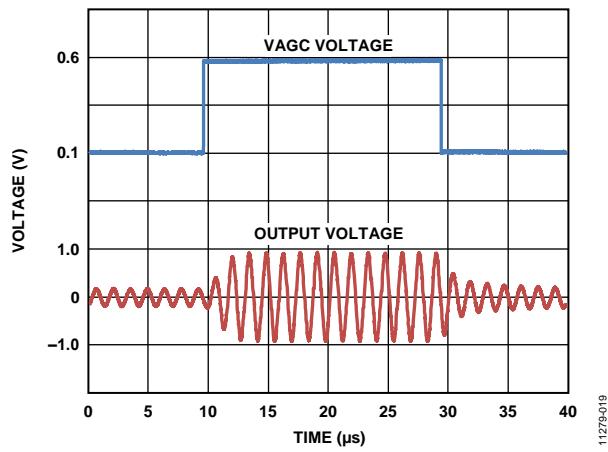

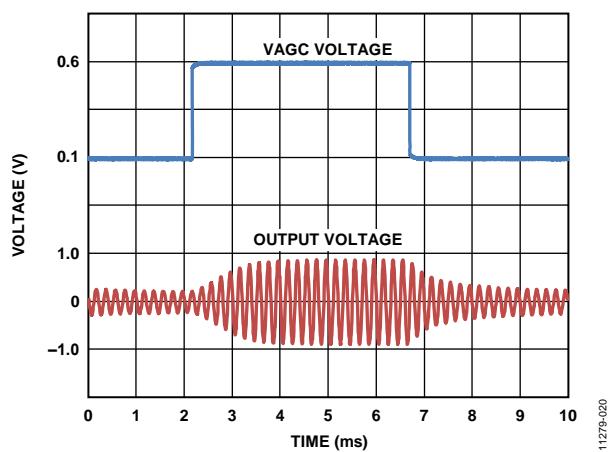

図 35.AGC 応答、無負荷、入力 100 mV 差動

図 38.COMM の  $R_{CM}$  対出力同相モード電圧図 36.AGC 応答、 $C_L = 0.01 \mu F$ 、入力 100 mV 差動

## 動作原理

### はじめに

AD8338 は、80 dB の調整可能なゲイン範囲を持つ单電源可変ゲイン・アンプ(VGA)です。正確には、AD8338 は、広い範囲の入力振幅を受け付け、可変ゲインを使って、狭い範囲の出力振幅または一定の出力振幅へ圧縮するようにデザインされた入力可変ゲイン・アンプ(IVGA)ということができます(例えば、自動ゲイン制御アプリケーション)。AD8338 はアナログ・デバイセズの他の VGA と同様に、全ゲイン範囲で一定の帯域幅を処理します。このため、AD8338 は帯域幅 18 MHz かつ最大ゲイン設定(ゲイン= 80 dB)で 180 GHz のゲイン帯域幅を実現します。さらに、AD8338 の差動出力を使って、VGA からシングルエンド／差動変換なしで差動入力 ADC を直接駆動することができます。

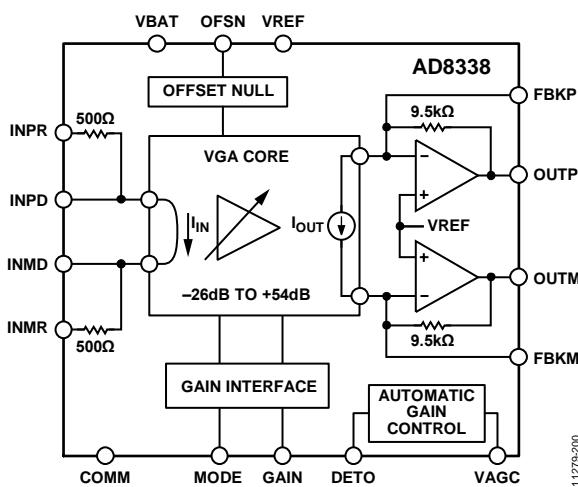

### AD8338 の全体構造

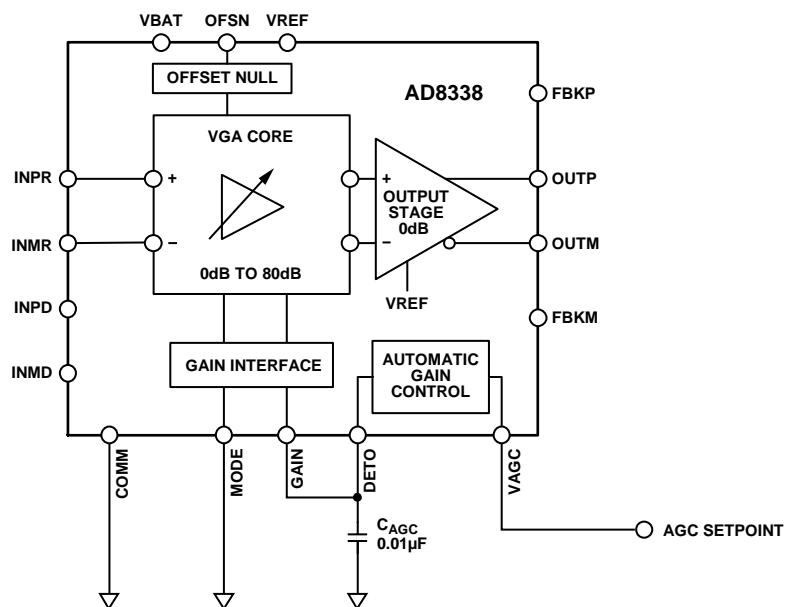

図 39 に、VGA の主要部分と機能概要を説明する AD8338 のブロック回路図を示します。AD8338 の信号パスは、500 Ω の入力抵抗、VGA コア、トランジスタインピーダンス出力アンプから構成されています。信号パスのゲインは、デシベル・リニアなゲイン・インターフェースと COMM ピンのローカル・グラウンドを基準とする GAIN ピン電圧を使って調節されます。自動ゲイン制御(AGC)回路ブロックは、電流出力 RMS 検出器です。この RMS 検出器は、GAIN ピンの駆動と、AD8338 を一定 RMS 出力振幅を持つ AGC アンプとして設定するときに使うことができます。この出力振幅は、VREF ピン電圧を基準とする VAGC ピン電圧によって調整されます。オフセット・ヌル回路ブロックを使うと、AD8338 の DC オフセット電圧を自動的にゼロにすることができます。オフセット・ヌル機能をイネーブルするときは、OFSN ピンと VREF ピンの間にコンデンサを接続します。オフセット・ヌル機能をディスエーブルするときは、OFSN ピンをグラウンドに接続します。INPD、INMD、FBKP、FBKM の各ピンは、AD8338 の VGA コアと出力アンプの内部ノードへのアクセスを提供するため、ゲイン範囲、出力同相モード電圧、デバイスの帯域幅を調整することができます。

図 39. ブロック図

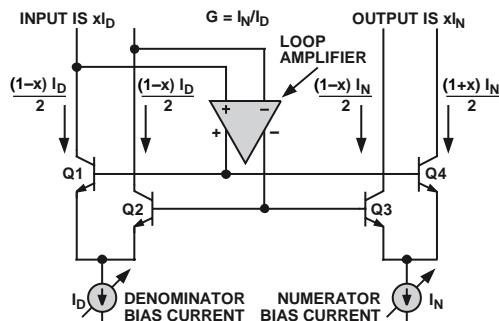

### VGA コア

図 40 に、AD8338 の中心となる VGA コアの簡略化した図を示します。この VGA コア動作に関する重要概念は、第一に、2 つの差動対が同じベース駆動を共用する場合、2 つの差動対(Q1、Q2 と Q3、Q4)のコレクタ電流比が等しいことです。この比は変調係数  $x$  で表されます。ここで、 $x$  の値の範囲は-1～+1 です。第二に、入力電流信号はループ・アンプを使って強制的に入力差動対(Q1、Q2)のコレクタに流され、固定テール電流  $I_D$  が変調されて、変調係数  $x$  が設定されます。入力差動対の  $x$  の値は出力差動対(Q3、Q4)内で複製され固定テール電流  $I_N$  が変調され、差動出力電流が発生されます。第三に、多くのディケードで変化できるバイアス電流に対して、このセルの電流ゲインは正確に  $G = I_N/I_D$  となります。

$I_N$  を変化させることにより、セルの全体機能は 2 象限アナログ乗算器の機能と同じで、信号変調係数  $x$  とこの分子電流に比例します。これに対して、 $I_D$  を変化させることにより、全体機能は 2 象限アナログ除算器の機能になり、分母電流から制御される変調係数  $x$  に対する双曲線ゲイン関数になります。AD8338 は入力 VGA であるため、 $I_D$  を制御してアンプ・ゲインを調整しますが、双曲線ゲイン関数は一様に 1 より小さい値を持ち、デシベル・ゲインが制御入力のリニア関数となっているため、AD8338 は  $I_D$  の指数制御を増加または減少させるための特別なインターフェースを内蔵しています。

図 40. VGA コアの簡略化した回路図

### 通常動作の条件

AD8338の通常動作条件は次のように定義されます。

- 入力ピン(INPR と INMR)は電圧駆動されます(ソース・インピーダンスはゼロと見なします)。

- 出力ピン(OUTP と OUTM)はオープンとします(負荷インピーダンスは無限大とします)。

- COMM ピンはグラウンドに接続されます。

- MODE ピンは、ロジック・ハイに接続するかオープンのままにして、非反転ゲイン・スロープ・ゲイン・モードを設定します。

### INPR、INMR、INPD、INMD の各ピン

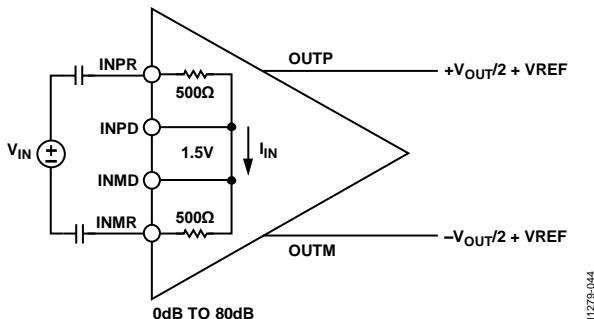

AD8338 の入力信号は、INPR/INMR と INPD/INMD の差動入力ポートに入力されます。これらのピンは、内部で約 1.5 V (= VREF ピン電圧) にバイアスされます。INPR ピンと INMR ピンは、電圧入力ピン(図 41 参照) であり、これらのピンで差動入力電圧と内部入力抵抗により電流  $I_{IN}$  が発生され、この電流が VGA コアの入力電流になります。電圧入力はシングルエンドまたは差動で駆動できますが、差動駆動が推奨されるため、他に注記がない限り、仕様ではこれを想定しています。電圧入力のピン間入力抵抗は  $1000 \Omega \pm 20\%$  と規定されています。大部分の場合、電圧入力ピンは十分な低周波伝送を可能にする 2 個のコンデンサで AC 結合されます。これにより、1.5 V 以外の同相モード電圧がこれらの入力ピンに加わったとき大きくなる入力ノイズが最小になります。最大ゲインでの短絡(INPR と INMR を接続) 入力換算ノイズは約  $4.5 \text{ nV}/\sqrt{\text{Hz}}$  です。

図 41. INPR ピンと INMR ピンに加える入力電圧

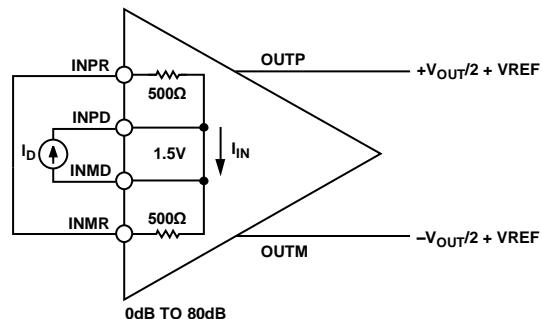

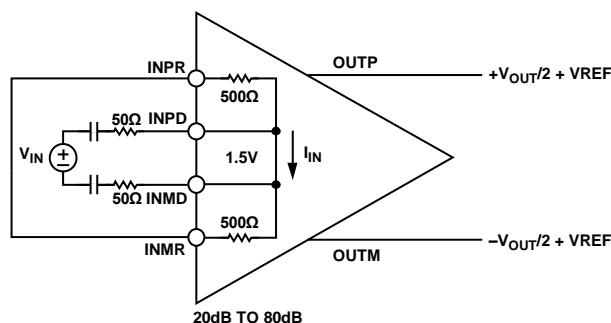

INPD ピンと INMD ピンは電流入力ピン(図 42)であり、これらのピンで差動入力電流が VGA コア入力へ直接加えられます。この入力電流はバイアスのないフォトダイオードのように外付け電流源から直接発生させるか、または電圧源と外付け結合抵抗から発生させることができます(図 43 参照)。後者の方法を使うと、ゲイン関数の説明のセクションで説明するように AD8338 のゲイン範囲をシフトさせることができます。INPD 入力と INMD 入力を使う場合、INPR ピンと INMR ピンを互いに接続して安定性の問題を回避する必要があります。

図 42. INPD ピンと INMD ピンに加える入力電流

図 43. INPD ピンと INMD ピンに外付け抵抗を使用

### FBKP、FBKM、OUTP、OUTM の各ピン

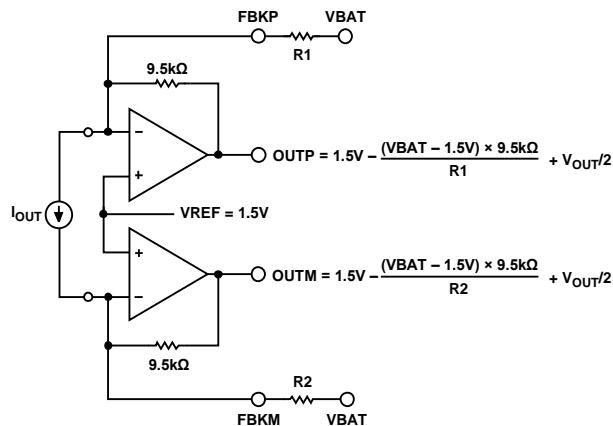

出力電圧ピン(OUTP と OUTM)には、デフォルト同相モード電圧 1.5 V (= VREF ピン電圧)があります。この出力同相モード電圧は、同相モード電流を FBKP ピンと FBKM ピン(1.5 V にバイアスされた出力アンプの加算ノード)に流して調整することができます。AD8338 の出力アンプはレール to レール出力ステージを採用しており、このステージを使うと、このような極端な値の使用により差動出力信号振幅に小さい範囲しか残しませんが、VGA の出力同相モードをグラウンドから正電源へシフトすることができます。

各ノード(OUTP、FBKP、OUTM、FBKM)の間に帰還コンデンサ  $C_{FBK}$  を接続すると、AD8338 出力アンプと VGA 信号バスの帯域幅が狭くなります。これらのコンデンサと出力アンプの帰還抵抗が、カットオフ周波数が次式で近似されるローパス・フィルタを構成します。

$$f_C = \frac{1}{2\pi \times R_{\text{EPK}} \times C_{\text{EPK}}} \quad (1)$$

一九二〇

$R_{FBK}$ は出力アンプの内部帰還抵抗。

$R_{FBK}$  は  $9800\ \Omega \pm 20\%$

AD8338 の帯域幅を狭くすると、出力ノイズが小さくなり、VGA を使って ADC を駆動する際、折り返し防止フィルタのデザインが簡素化されます。

### デシベル・リニア・ゲイン制御、GAIN ピン

80 dB のゲイン範囲の使用を可能にするために、AD8338 はデシベル・リニア・ゲイン制御機能を内蔵しています。ゲインは、ローカル・グラウンド COMM を基準とする GAIN ピン電圧により制御されます。通常の動作状態では、GAIN ピン電圧を 0.1 V ~ 1.1 V の範囲で調整すると、最小値 0 dB ~ 最大値 80 dB の範囲でゲインを調整することができます。基本ゲイン式は、

$$G(dB) = \frac{V_{GAIN}}{12.5 \text{ mV}} - 8 \text{ dB} \quad (2)$$

ここで、 $V_{GAIN}$  の単位はボルトです。

あるいは、ゲイン振幅量として次のように表すことができます。

$$G_N = 0.398 \times 10^{\frac{V_{GAIN}}{250 \text{ mV}}} \quad (3)$$

ここで、 $V_{GAIN}$  の単位はボルトです。

### ゲインスロープの反転、MODE ピン

MODE ピンは、ゲイン調整の極性を制御します。MODE ピンを使うと、ゲイン関数のスロープを反転することができます。MODE ピンを VBAT に接続した場合、GAIN ピン電圧が増加すると、AD8338 のゲインは指数的(すなわちデシベル・リニア)に増加します。MODE ピンを COMM に接続した場合、GAIN ピン電圧が増加すると、AD8338 のゲインは指数的(すなわちデシベル・リニア)に減少します。図 44 に、AD8338 を通常動作モードに設定した場合の 2 つのゲイン制御モードを示します。

図 44. AD8338 の 2 つのゲイン制御モード

### オフセット補正回路、OFSN ピン

AD8338 は、VGA に発生する DC オフセットを除去するオフセット補正回路を内蔵しています。OFSN ピンと VREF ピンの間にコンデンサ  $C_{OFSN}$  を接続すると、オフセット補正回路がイネーブルされます。

オフセット補正回路は、信号パスへ小信号ハイパス・フィルタ特性を導入する内部自動ゼロ帰還ループを使用しています。 $-3$  dB コーナー周波数は、

$$f_{OFSN} = \frac{1}{2\pi \times 400\Omega \times C_{OFSN}} \quad (4)$$

オフセット補正回路をイネーブルすると、AD8338 の伝達関数はハイパス・フィルタ特性を示しますが、回路が除去できる DC 入力電圧の範囲が狭いため、後者はハイパス・フィルタとして使用できません。注目帯域より低い周波数の信号を除去する必要がある場合、最適性能を得るためには、AD8338 の前にハイパス・フィルタを使用してください。これは、入力を AC 結合することにより実現できます(図 41 参照)。

DC 結合信号バスを設けるときは、OFSN ピンを COMM ピンへ接続してオフセット補正回路をディスエーブルすることができます。オフセット補正回路をディスエーブルして AD8338 を動作させるときは、ゲインが大きいとき、DC オフセットにより VGA 出力で大きな DC 誤差が発生するため、注意が必要です。

## AGC 回路、VAGC ピン

AD8338 は、AD8338 を AGC アンプとして構成する際に使える電流出力 RMS 検出器を内蔵しています(図 46)。

この構成では、AGC 回路が VGA の RMS 出力振幅を所望の RMS 出力振幅( VREF ピン電圧を基準とする VAGC ピン電圧)と比較し、差を小さくするように GAIN ピンを駆動します。このため、静止状態では、回路は AD8338 の RMS 出力振幅を VAGC ピン電圧(VREF ピン電圧を基準とします)に強制的に一致させます。AGC 回路は負帰還を使用するため、MODE ピンをグラウンドへ接続して AD8338 のゲイン・スロープを反転させる必要があります。

AGC 回路の帯域幅は、コンデンサ  $C_{DETO}$  により支配されます。このコンデンサを注意深く選択して、入力信号振幅の高速変化に対応できように AGC 回路の帯域幅が十分広くなるようにし、かつ AGC 回路で注目する信号に歪が生じないよう十分狭くする必要があります。例えば、キャリア周波数 6.8 MHz でビット・レート 10 kb/s のオン／オフ・キーイング(OOK)アプリケーションでは、0.01  $\mu$ F コンデンサの使用が推奨されます。このコンデンサ値は、ゲインがビット・エネルギーに応答しますが、キャリア信号には応答しません。

前述のように、AGC 回路は AD8338 の RMS 出力振幅を VAGC ピン電圧(VREF ピン電圧が基準)に強制的に一致させます。さらに、AGC 回路の入力(VAGC ピン)は、VREF ピンに対して対称です。言い換えれば、AGC 回路は VAGC ピンと VREF ピンとの間の電位差の絶対値に応答します(図 45 参照)。

すべてのアプリケーションで AGC 回路が必要なわけではありません。このため、DETO ピンをグラウンドへ接続し、さらに VAGC ピンと VREF ピンを接続して AGC 回路をディスエーブルすることができます。

## 内蔵リファレンス、ピン VREF

AD8338 は、VGA の多くの主要ノードに静止バイアス電圧を設定するときに使用される 1.5 V のリファレンス電圧を内蔵しています。これらのノードとしては、入力ピン(INPR、INMR、INPD、INMD)、出力ピン(OUTP と OUTM)、帰還ピン(FBKP と FBKM)などがあります。内蔵リファレンスの出力電圧(VREF ピン)は、0.1  $\mu$ F のコンデンサで COMM ピンへバイパスできますが、外部に出力しないでください。

11279-148

## ゲイン関数の説明

AD8338 のシグナル・チェーンは 3 つのステージに分割することができます。最初のステージは、VGA の入力抵抗  $R_P$  と  $R_N$  で構成される差動電圧／電流コンバータです。これらの入力抵抗は、INPR ピンと INMR ピンに接続される内蔵  $500\Omega$  抵抗か、または INPD ピンと INMD ピンに接続される外付け抵抗です。電圧／電流コンバータのトランスレジスタンスは、 $R_P + R_N$  です。次式で与えられる電流がこの抵抗に流れます。

$$I_{IN} = \frac{V_{INPx} - V_{INMx}}{R_P + R_N} \quad (5)$$

入力抵抗の電流  $I_{IN}$  は、AD8338 の 2 段目ステージである VGA コアに入力されます。VGA コアは、80 dB のゲイン範囲を持つフル差動の可変ゲイン電流アンプです。非反転ゲイン・スロープ設定(MODE ピンを VBAT ピンに接続)では、VGA コアの電流ゲイン範囲は-26 dB ( $V_{GAIN} = 0.1\text{ V}$ )～+54 dB ( $V_{GAIN} = 1.1\text{ V}$ )になります。ゲイン量で表す場合、VGA コアのゲインは次式で与えられます。

$$I_{OUT,VGA} = I_{IN} \times 10^{\frac{V_{GAIN}-34}{20}} \approx I_{IN} \times 0.02 \times 10^{\frac{V_{GAIN}}{250\text{ mV}}} \quad (6)$$

VGA コアの差動出力電流は、AD8338 の 3 段目ステージのフル差動電流／電圧コンバータ(出力アンプと対応する帰還抵抗  $R_{FBK}$  で構成)へ入力されます。電流／電圧コンバータの全体トランスインピーダンスは  $2R_{FBK}$  となり、このステージの差動出力電圧は次式で与えられます。

$$V_{OUT,DIFF} = I_{OUT,VGA} \times 2 \times R_{FBK} \quad (7)$$

したがって、AD8338 の全体の電圧ゲインは次式で表されます。

$$G(\text{dB}) = 80 \times V_{GAIN} \times 20 \times \log\left(\frac{2 \times R_{FBK}}{R_P + R_N}\right) - 34 \quad (8)$$

あるいは、ゲイン量として次のように表すことができます。

$$G_N = 0.02 \times \frac{2 \times R_{FBK}}{R_P + R_N} \times 10^{\frac{V_{GAIN}}{250\text{ mV}}} \quad (9)$$

式 8 と式 9 は、AD8338 のゲイン範囲が外付け入力抵抗  $R_P$  と  $R_N$  を使ってシフトできることを表しています。例えば、INPD ピンと INMD ピンを  $50\Omega$  の  $R_P$  と  $R_N$  で駆動すると、AD8338 のゲイン範囲は 20 dB 上にシフトし、20 dB～100 dB になります(図 43 参照)。同様に、INPD ピンと INMD ピンを  $5\text{k}\Omega$  の  $R_P$  と  $R_N$  で駆動すると、ゲイン範囲は下に 20 dB シフトして、-20 dB～+60 dB になります。

図 43 に示すように、外付け抵抗を使って INPD ピンと INMD ピンを駆動するときは、INPR ピンと INMR ピンを接続して安定性の問題を回避してください。

## 外付け抵抗使用の影響

外付け抵抗を使ってゲイン範囲をシフトさせると、幾つかのトレードオフを考慮する必要があります。INPD ピンと INMD ピンに接続した外付け抵抗は、VGA コアの電流入力の負荷になるため、このロックのダイナミック動作と AD8338 の-3 dB 帯域幅が変わります。外付け抵抗を使った場合の AD8338 の-3 dB 帯域幅は、

$$f_{CL} = 18\text{MHz} \times \left( \frac{500\Omega \times R_{EXT}}{500\Omega + R_{EXT}} \right) \times \frac{1}{500\Omega} \quad (10)$$

例えば、 $50\Omega$  外付け抵抗の場合、最大ゲインでの入力換算ノイズは約  $1\text{nV}/\sqrt{\text{Hz}}$  に減少し、ゲイン範囲は上に 20 dB シフトします。ただし、-3 dB 帯域幅は 18 MHz から約 1.8 MHz へ減少します。

## 出力同相モード電圧の調整

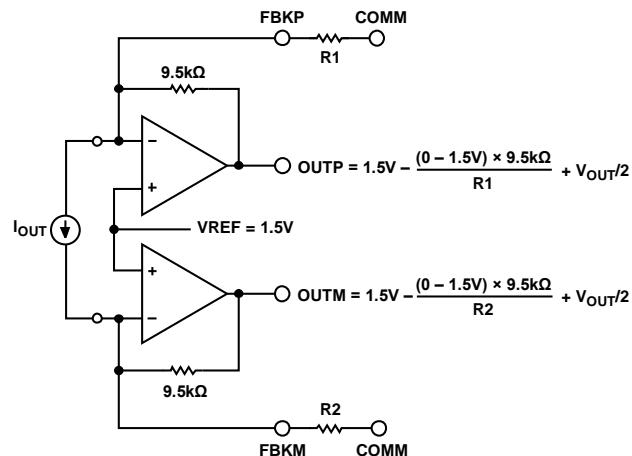

AD8338 差動出力の出力同相モード電圧は、公称 1.5 V (= VREF ピン電圧)に設定されています。この出力同相モード電圧は、各出力アンプの加算ノード(FBKp ピンと FBKm ピン)と COMM ピンまたは VBAT ピンとの間に抵抗を接続して、調整することができます。FBKP ピンおよび FBKM ピンと VBAT ピンとの間に抵抗を接続すると、出力同相モード電圧が小さくなりますが、FBKP ピンおよび FBKM ピンと COMM ピンとの間に抵抗を接続すると、出力同相モード電圧が大きくなります(図 47 と図 48 参照)。

図 47. 出力同相モード電圧の減少

11279-150

図 48. 出力同相モード電圧の増加

11279-151

表 5 と表 6 に、図 47 と図 48 に示す外付け抵抗に対する推奨値を示します。

表 5. 出力同相モード電圧を減少させる抵抗値

| VBAT (V) | Target V <sub>OCM</sub> (V) | Resistor Value (Ω) | Tied to |

|----------|-----------------------------|--------------------|---------|

| 5.0      | 0.9                         | 55,417             | VBAT    |

| 3.3      | 0.9                         | 28,500             | VBAT    |

| 3.0      | 0.9                         | 23,750             | VBAT    |

表 6. 出力同相モード電圧を増加させる抵抗値

| VBAT (V) | Target V <sub>OCM</sub> (V) | Resistor Value (Ω) | Tied to |

|----------|-----------------------------|--------------------|---------|

| Any      | 1.8                         | 47,500             | COMM    |

| Any      | 2.0                         | 28,500             | COMM    |

| Any      | 2.5                         | 14,250             | COMM    |

## アプリケーション情報

AD8338 の優れた性能により、様々なゲインで平坦な応答、レール to レール出力信号振幅、高い駆動能力、わずか 12 mW で非常に広いダイナミックレンジが得られます。AD8338 はこれらの機能を持つため、バッテリ駆動の装置、低周波およびベースバンド・アプリケーション、その他多くのアプリケーションに対する優れた選択肢になっています。

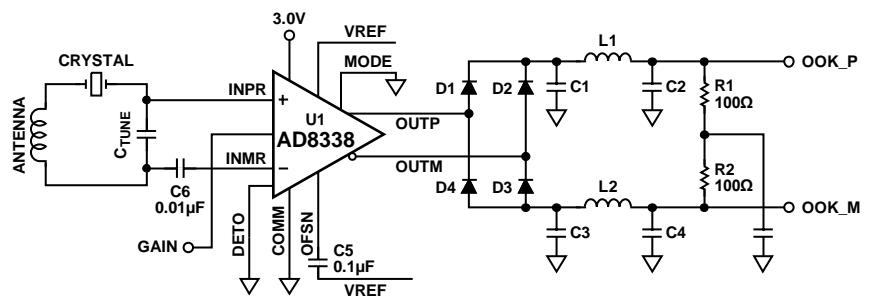

### シンプルなオン・オフ・キーイング(OOK)レシーバ

簡素で低消費電力データ通信向けに、オン／オフ状態に変調キャリア・トーンを使って構成したシンプルな回線が、高速で経済的なソリューションを提供します。このようなデザインは、干渉のないメカニカル・システム、低データ・レート・センサー、RFID タグなど近端通信を含む多様なアプリケーションで使用されています。

図 49 に、誘導性テレメタリのオン・オフ・キーイング(OOK)プロント・エンド全体の回路図を示します。水晶はターゲット受信周波数用にカットされ、非常に狭い帯域フィルタを構成しています(約 6.78 MHz の ISM 帯域)。

AD8338 は信号を増幅して(ゲインは外部コントローラから設定)全波整流ブリッジを駆動します。このブリッジ出力はローパス・フィルタされ  $100\Omega$  で終端されます。このデザインは、後段の判定ステージに対して優れた RF 除去比と優れたベースバンド情報再生を提供します。

リアクティブ・フィルタ部品(コンデンサ C1～C4 とインダクタ L1 と L2)で、ベースバンド再生性能が設定されます。ベースバンド応答と RF 減衰量の間でデザイン・トレードオフが行われます。

表 7 に、2 つのデータ・レートに対してこれらの部品の typ 値を示します。コンデンサ C1～C4 はすべて等しい値で、インダクタ L2 と L1 は同じ値であることに注意してください。

表 7.リアクティブ・フィルタの部品値(typ)

| Data Rate  | C1 to C4 | L1 and L2   | Carrier Attenuation (f = 6.78 MHz) |

|------------|----------|-------------|------------------------------------|

| 19,200 bps | 12 nF    | 240 $\mu$ H | -101 dB                            |

| 57,600 bps | 3.9 nF   | 82 $\mu$ H  | -73 dB                             |

11279-046

図 49.低消費電力 OOK レシーバの全体回路図

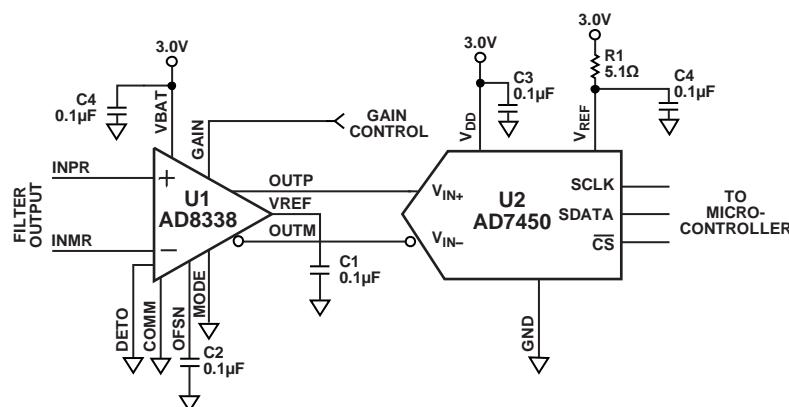

## AD8338 と ADC とのインターフェース

AD8338 は高速 A/D コンバータ(ADC)の駆動に適し、アナログ・デバイセズの多くの ADC と互換性を持っています。AD8338 と AD7450 とのインターフェース例を示します。AD7450 は低消費電力の 3.0 V ADC で、低価格トータル・ソリューション向けに競争力があります。

図 50 に、AD8338 と AD7450 との間の基本接続を示します。同相モード電圧は、AD7450 の仕様を満たして AD8338 から供給されます。

AD8338 を直接 AD7450 に接続して、低消費電力(160 mW typ)かつ最高レベルの性能で、DC~18 MHz の動作が可能です。外付け部品不要のインターフェースにより小型で高性能なデータ・アクイジション・システムが可能になり、多くの領域での計装機器として最適です。VGA の前のフィルタは、折り返し防止機能とノイズ制限機能を提供します。

変調された情報が信号振幅にエンコードされないアプリケーションでは、AD8338 の AGC 機能を使ってサンプルされた信号のビット誤りを小さくすることができます。

図 50. AD7450 ADC との基本接続

11279-149

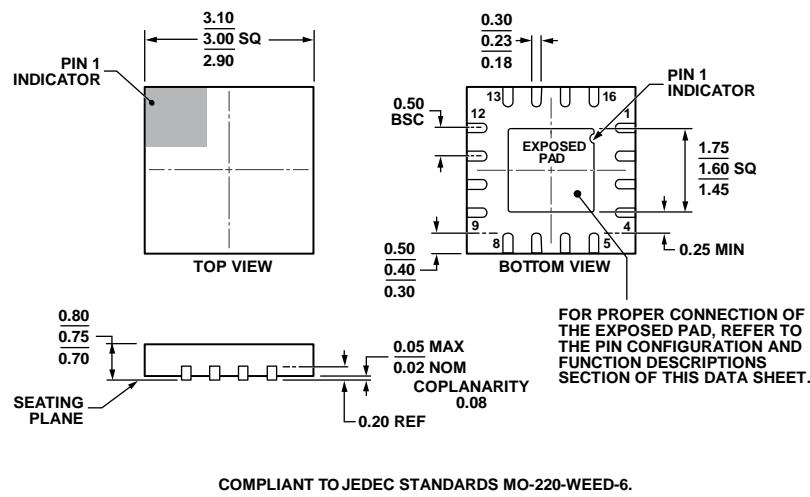

## 外形寸法

図 51.16 ピン・リードフレーム・チップ・スケール・パッケージ[LFCSP\_WQ]

3 mm x 3 mm ボディ、極薄クワッド

(CP-16-22)

寸法: mm

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                              | Package Option | Branding |

|--------------------|-------------------|--------------------------------------------------|----------------|----------|

| AD8338ACPZ-R7      | -40°C to +85°C    | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-16-22       | Y4K      |

| AD8338ACPZ-RL      | -40°C to +85°C    | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-16-22       | Y4K      |

| AD8338-EVALZ       |                   | AD8338 Evaluation Board                          |                |          |

<sup>1</sup> Z = RoHS 準拠製品