# AD7888

## 特長

$V_{DD}$ 仕様: +2.7 ~ +5.25V

フレキシブルなパワー/スループット・レート管理

シャットダウン・モード: 1 $\mu$ A Max

シングル・エンド入力×8

シリアル・インターフェース:

SPI™/QSPI™/MICROWIRE™/DSP互換

16ピン小型SOICパッケージおよびTSSOPパッケージを採用

## アプリケーション

バッテリ駆動のシステム (PDA、医療機器、移動通信)

計装システムおよび制御システム

高速モデム

## 概要

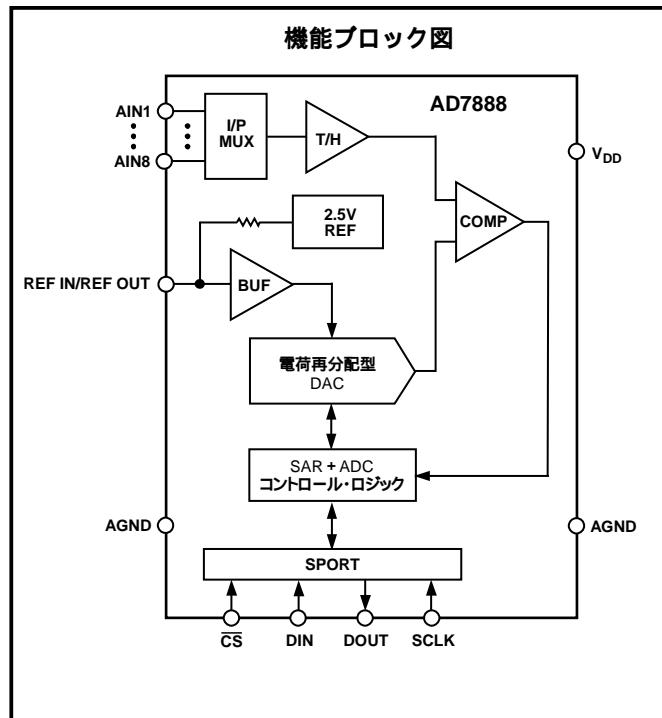

AD7888は、+2.7 ~ +5.25V 単電源で動作し、125kSPSのスループット・レートを低消費電力で実現する、高速12ビットADCです。入力トラック / ホールド回路は500nsで信号を取り込み、シングル・エンド・サンプリング方式を採用しています。AD7888にはAIN1 ~ AIN8の8つの入力ピンがあり、これらの各チャンネルには0 ~  $V_{REF}$ の信号を入力することができ、最大2.5MHzまでのフル・パワー信号を変換できます。

AD7888は、A/Dコンバータのリファレンスとして使用できる+2.5Vのリファレンスを内蔵しています。REF IN/REF OUTピンを使用して、この内蔵リファレンスにアクセスできます。あるいは、VREFピンを外部リファレンスでオーバーライドすることにより、外部からリファレンスが得られます。この外部リファレンスの範囲は、1.2V ~  $V_{DD}$ です。

AD7888はCMOS構造を採用し、通常動作で2mW (typ) パワーダウン・モードで3 $\mu$ W (typ) の低消費電力を保証しています。パッケージは小型の16ピンSOICと、16ピンTSSOPを採用しています。

## 製品のハイライト

- 最小の12ビット8チャンネルADC; 16ピンTSSOPパッケージは、16ピンSOICパッケージ面積は同じですが、高さは半分以下です。

- 消費電力最小の12ビット8チャンネルADC。

- 変換後の自動パワーダウンなど、フレキシブルなパワー・マネジメント・オプション。

- 0V ~  $V_{REF}$  ( $V_{DD}$ ) のアナログ入力範囲。

- SPI/QSPI/MICROWIRE/DSP互換のシリアルI/Oポート。

SPIとQSPIは、Motorola, Inc.の商標です。

MICROWIREは、National Semiconductor Corporationの商標です。

REV.0

アナログ・デバイセズ社が提供する情報は正確で信頼できるものを期していますが、その情報の利用または利用したことにより引き起こされる第3者の特許または権利の侵害に関して、当社はいっさいの責任を負いません。さらに、アナログ・デバイセズ社の特許または特許の権利の使用を許諾するものではありません。

# AD7888 - 仕様

(特に指定のない限り、 $V_{DD} = +2.7 \sim +5.25V$ 、REFIN/REFOUT = +2.5V外部 / 内蔵リファレンス、

$f_{SCLK} = 2MHz$  ( $V_{DD} = +2.7 \sim +5.25V$ )  $T_A = T_{MIN} \sim T_{MAX}$ )

| パラメータ                             | Aバージョン <sup>1</sup> | Bバージョン <sup>1</sup> | 単位          | テスト条件 / 備考                                                   |

|-----------------------------------|---------------------|---------------------|-------------|--------------------------------------------------------------|

| ダイナミック特性                          |                     |                     |             |                                                              |

| S/N+歪み比 <sup>2,3</sup> SNR )      | 71                  | 71                  | dB typ      | $f_{IN} = 10kHz$ サイン波、 $f_{SAMPLE} = 125kSPS$                |

| 全高調波歪み <sup>2</sup> ( THD )       | - 80                | - 80                | dB typ      | $f_{IN} = 10kHz$ サイン波、 $f_{SAMPLE} = 125kSPS$                |

| ピーク高調波またはスプリアス・ノイズ <sup>2</sup>   | - 80                | - 80                | dB typ      | $f_{IN} = 10kHz$ サイン波、 $f_{SAMPLE} = 125kSPS$                |

| 相互変調歪み <sup>2</sup> ( IMD )       |                     |                     |             |                                                              |

| 2次項                               | - 78                | - 78                | dB typ      | $f_a = 9.983kHz$ , $f_b = 10.05kHz$ , $f_{SAMPLE} = 125kSPS$ |

| 3次項                               | - 78                | - 78                | dB typ      | $f_a = 9.983kHz$ , $f_b = 10.05kHz$ , $f_{SAMPLE} = 125kSPS$ |

| チャンネル間アイソレーション <sup>2</sup>       | - 80                | - 80                | dB typ      | $f_{IN} = 25kHz$                                             |

| フレパワー・帯域幅                         | 2.5                 | 2.5                 | MHz typ     | @3dB                                                         |

| DC精度                              |                     |                     |             |                                                              |

| 分解能                               | 12                  | 12                  | ビット         | 任意のチャンネル                                                     |

| 積分非直線性 <sup>2</sup>               | $\pm 2$             | $\pm 1$             | LSB max     |                                                              |

| 微分非直線性 <sup>2</sup>               | $\pm 2$             | $\pm 1$             | LSB max     | 11ビットのノーミス・コードを保証( Aグレード )<br>12ビットのノーミス・コードを保証( Bグレード )     |

| オフセット誤差 <sup>2</sup>              | $\pm 6$             | $\pm 6$             | LSB max     | $V_{DD} = 4.75 \sim 5.25V$ ( $\pm 3LSB$ ( typ ) )            |

|                                   | $\pm 4.5$           | $\pm 4.5$           | LSB max     | $V_{DD} = 2.7 \sim 3.6V$ ( $\pm 2LSB$ ( typ ) )              |

| オフセット誤差マッチ <sup>2</sup>           | 2                   | 2                   | LSB typ     |                                                              |

| ゲイン誤差 <sup>2</sup>                | $\pm 2$             | $\pm 2$             | LSB max     | 内蔵リファレンス使用時30LSB( typ )                                      |

| ゲイン誤差マッチ <sup>2</sup>             | 2                   | 2                   | LSB max     |                                                              |

| アナログ入力                            |                     |                     |             |                                                              |

| 入力電圧範囲                            | $0 \sim V_{REF}$    | $0 \sim V_{REF}$    | V           |                                                              |

| リーケ電流                             | $\pm 1$             | $\pm 1$             | $\mu A$ max |                                                              |

| 入力容量                              | 38                  | 38                  | pF typ      | トラック時                                                        |

|                                   | 4                   | 4                   | pF typ      | ホールド時                                                        |

| リファレンス入 / 出力                      |                     |                     |             |                                                              |

| REFIN入力電圧範囲                       | $2.5/V_{DD}$        | $2.5/V_{DD}$        | V min/max   | 1.2Vで動作                                                      |

| 入力インピーダンス                         | 5                   | 5                   | k typ       | 内蔵リファレンスのディスエーブル時は高インピーダンス                                   |

| REFOUT出力電圧                        | $2.45/2.55$         | $2.45/2.55$         | V min/max   |                                                              |

| REFOUT温度係数                        | $\pm 50$            | $\pm 50$            | ppm/ typ    |                                                              |

| ロジック入力                            |                     |                     |             |                                                              |

| 入力電圧ハイ、 $V_{INH}$                 | 2.4                 | 2.4                 | V min       | $V_{DD} = +4.75 \sim +5.25V$                                 |

|                                   | 2.1                 | 2.1                 | V min       | $V_{DD} = +2.7 \sim +3.6V$                                   |

| 入力電圧ロー、 $V_{INL}$                 | 0.8                 | 0.8                 | V max       | $V_{DD} = +2.7 \sim +5.25V$                                  |

| 入力電流、 $I_{IN}$                    | $\pm 10$            | $\pm 10$            | $\mu A$ max | $10nA$ ( typ ) $\lambda V_{IN} = 0V$ または $V_{DD}$            |

| 入力容量、 $C_{IN}$                    | 10                  | 10                  | pF max      |                                                              |

| ロジック出力                            |                     |                     |             |                                                              |

| 出力電圧ハイ、 $V_{OH}$                  | $V_{DD} - 0.5$      | $V_{DD} - 0.5$      | Vmin        | $I_{SOURCE} = 200\mu A$                                      |

| 出力電圧ロー、 $V_{OL}$                  | 0.4                 | 0.4                 | V max       | $V_{DD} = +2.7 \sim +5.25V$                                  |

| フローテイキング状態リーケ電流                   | $\pm 10$            | $\pm 10$            | $\mu A$ max | $I_{SINK} = 200\mu A$                                        |

| フローテイキング状態出力容量 <sup>5</sup>       | 10                  | 10                  | pF max      |                                                              |

| 出力コーディング                          |                     | 自然2進数               |             |                                                              |

| 変換レート                             |                     |                     |             |                                                              |

| スループット・タイム                        | 16                  | 16                  | SCLK周期      | 変換時間 + 2MHzクロックでのアクイジョン時間125kSPS                             |

| トラック / ホールド・アクイジョン時間 <sup>2</sup> | 1.5                 | 1.5                 | SCLK周期      |                                                              |

| 変換時間                              | 14.5                | 14.5                | SCLK周期      | $7.25\mu s$ ( 2MHzクロック )                                     |

| パラメータ                      | Aバージョン <sup>1</sup> | Bバージョン <sup>1</sup> | 単位          | テスト条件 / 備考                                              |

|----------------------------|---------------------|---------------------|-------------|---------------------------------------------------------|

| 電源条件                       |                     |                     |             |                                                         |

| $V_{DD}$                   | +2.7/+5.25          | +2.7/+5.25          | V min/max   |                                                         |

| $I_{DD}$                   |                     |                     |             |                                                         |

| 通常モード <sup>5</sup> ( 静止時 ) | 700                 | 700                 | $\mu A$ max |                                                         |

| 通常モード <sup>5</sup> ( 動作時 ) | 700                 | 700                 | $\mu A$ typ | $f_{SAMPLE} = 125\text{kSPS}$                           |

| スタンバイ・モード使用時               | 450                 | 450                 | $\mu A$ typ | $f_{SAMPLE} = 50\text{kSPS}$                            |

| シャットダウン・モード使用時             | 80                  | 80                  | $\mu A$ typ | $f_{SAMPLE} = 10\text{kSPS}$                            |

|                            | 12                  | 12                  | $\mu A$ typ | $f_{SAMPLE} = 1\text{kSPS}$                             |

| スタンバイ・モード <sup>6</sup>     | 200                 | 200                 | $\mu A$ max | $V_{DD} = +2.7 \sim +5.25\text{V}$                      |

| シャットダウン・モード <sup>6</sup>   | 2                   | 2                   | $\mu A$ max | $V_{DD} = +4.75 \sim +5.25\text{V}$ ( 0.5 $\mu A$ typ ) |

|                            | 1                   | 1                   | $\mu A$ max | $V_{DD} = +2.7 \sim +3.6\text{V}$                       |

| 通常モード消費電力                  | 3.5                 | 3.4                 | mW max      | $V_{DD} = +5\text{V}$                                   |

|                            | 2.1                 | 2.1                 | mW max      | $V_{DD} = +3\text{V}$                                   |

| シャットダウン消費電力                | 10                  | 10                  | $\mu W$ max | $V_{DD} = +5\text{V}$                                   |

|                            | 3                   | 3                   | $\mu W$ max | $V_{DD} = +3\text{V}$                                   |

| スタンバイ消費電力                  | 1                   | 1                   | mW max      | $V_{DD} = +5\text{V}$                                   |

|                            | 600                 | 600                 | $\mu W$ max | $V_{DD} = +3\text{V}$                                   |

## 注

1 温度範囲 : Aバージョン : -40 ~ +105 °C 、 Bバージョン : 0 ~ +105 °C 。

2 用語集を参照してください。

3 S/N比の計算には、歪み成分とノイズ成分が含まれます。

4 +25 °C でサンプル・テストを行い適合性を保証します。

5 全デジタル入力をGNDに接続。ただし、CSは $V_{DD}$ に接続。デジタル出力は無負荷。アナログ入力はGNDに接続。

6 SCLKのOFF時はSCLKをGNDに接続。全デジタル入力をGNDに接続。ただし、CSは $V_{DD}$ に接続。デジタル出力は無負荷。アナログ入力はGNDに接続。

仕様は予告なく変更されることがあります。

絶対最大定格<sup>1</sup>

( 特に指定のない限り、 $T_A = +25\text{ }^{\circ}\text{C}$  )

$V_{DD}$  ~ AGND ..... -0.3 ~ +7V

アナログ入力電圧 ~ AGND ..... -0.3V ~  $V_{DD}$  +0.3V

デジタル入力電圧 ~ AGND ..... -0.3V ~  $V_{DD}$  +0.3V

デジタル出力電圧 ~ AGND ..... -0.3V ~  $V_{DD}$  +0.3V

REFIN/REFOUT ~ AGND ..... -0.3V ~  $V_{DD}$  +0.3V

電源以外の任意のピンの入力電流<sup>2</sup> ..... ±10mA

## 動作温度範囲

## 商業用

( Aバージョン ) ..... -40 ~ +105 °C

( Bバージョン ) ..... 0 ~ +105 °C

## 保管温度範囲

接合温度 ..... +150 °C

SOIC、TSSOPパッケージ、ワット損 ..... 450mW

$J_A$ 熱インピーダンス ..... 124.9 /W ( SOIC )

..... 150.4 /W ( TSSOP )

$J_C$ 熱インピーダンス ..... 42.9 /W ( SOIC )

..... 27.6 /W ( TSSOP )

## ピン温度、ハンダ処理

蒸着 ( 60sec ) ..... +215 °C

赤外線 ( 15sec ) ..... +220 °C

ESD ..... 1.5 kV

## 注

1 上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

2 100mAまでの過渡電流ではSCRラッチアップは発生しません。

## オーダー・ガイド

| モデル                             | 直線性誤差<br>( LSB ) <sup>1</sup> | パッケージ | パッケージ・<br>オプション |

|---------------------------------|-------------------------------|-------|-----------------|

| AD7888AR                        | ±2                            | SOIC  | R-16A           |

| AD7888BR <sup>2</sup>           | ±1                            | SOIC  | R-16A           |

| AD7888ARU                       | ±2                            | TSSOP | RU-16           |

| AD7888BRU <sup>2</sup>          | ±1                            | TSSOP | RU-16           |

| EVAL-AD7888CB <sup>3</sup>      |                               |       |                 |

| EVAL-CONTROL BOARD <sup>4</sup> |                               |       |                 |

## 注

1 ここでの直線性エラーは積分直線性誤差を意味します。

2 供給状況はお問い合わせください。

3 独立の評価ボードとして、またはEVAL-CONTROL BOARDと組み合わせて、評価 / デモストレーション用に使用できます。

4 このボードは完成ユニットで、このユニットを使うと、PC側から全アナログ・デバイス評価ボード ( CBサフィックス付き ) に対して制御または通信を行えます。

# AD7888

## タイミング特性<sup>1</sup> (特に指定のない限り、 $T_A = T_{MIN} \sim T_{MAX}$ )

| パラメータ         | $T_{MIN}, T_{MAX}$ での規格値<br>(A、Bバージョン) |                | 単位          | 説明                                    |

|---------------|----------------------------------------|----------------|-------------|---------------------------------------|

|               | +4.75 ~ +5.25V                         | +2.7 ~ +3.6V   |             |                                       |

| $f_{SCLK}^2$  | 2                                      | 2              | MHz max     |                                       |

| $t_{CONVERT}$ | $14.5t_{SCLK}$                         | $14.5t_{SCLK}$ |             |                                       |

| $t_{ACQ}$     | $1.5t_{SCLK}$                          | $1.5t_{SCLK}$  |             |                                       |

| $t_1$         | 10                                     | 10             | ns min      | $\bar{CS}$ からのSCLKまでのセットアップ時間         |

| $t_2^3$       | 30                                     | 60             | ns max      | $\bar{CS}$ からDOUTスリーステート・ディスエーブルまでの遅延 |

| $t_3^3$       | 75                                     | 100            | ns max      | SCLK立ち下がりエッジからのデータ・アクセス時間             |

| $t_4$         | 20                                     | 20             | ns min      | SCLK立ち上がりエッジまでのデータ・セットアップ時間           |

| $t_5$         | 20                                     | 20             | ns min      | データ有効からSCLKホールド時間まで                   |

| $t_6$         | $0.4t_{SCLK}$                          | $0.4t_{SCLK}$  | ns min      | SCLKのハイパリス幅                           |

| $t_7$         | $0.4t_{SCLK}$                          | $0.4t_{SCLK}$  | ns min      | SCLKのローパリス幅                           |

| $t_8^4$       | 80                                     | 80             | ns max      | $\bar{CS}$ 立ち上がりエッジからDOUT高インピーダンスまで   |

| $t_9$         | 5                                      | 5              | $\mu s$ typ | シャットダウンからのパワーアップ時間                    |

### 注

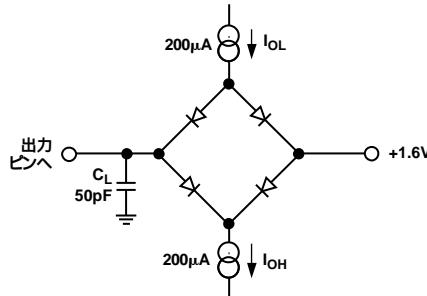

1 +25 °Cでサンプル・テストを行い適合性を保証します。全入力信号は $t_r = t_f = 5\text{ns}$  ( $V_{DD}$ の10 ~ 90%) で、電圧レベル1.6Vで時間を測定。

2 SCLK入力のマーク / スペース比は40/60 ~ 60/40。

3 図1の負荷回路で測定し、 $V = 5V \pm 10\%$ では出力が0.8Vまたは2.4Vを通過するために要する時間として、 $V = 3V \pm 10\%$ では出力が0.4Vまたは2.0Vを通過するために要する時間として、それぞれ定義。

4  $t_8$ は、図1の負荷回路使用時にデータ出力が0.5Vまで変化するときに要する時間の測定値から導出しています。測定値は、50pFのコンデンサの充電または放電の効果を除去するため測定後外挿されています。したがって、タイミング特性で示している時間 $t_8$ はバス負荷と無関係であり、このデバイスの真のバス解放時間を表しています。

仕様は予告なしで変更されることがあります。

図1 デジタル出力タイミング仕様の負荷回路

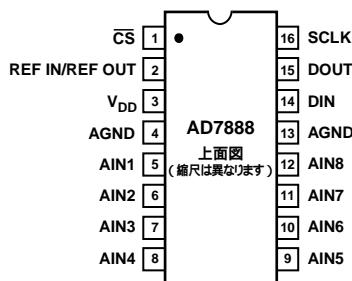

**ピン配置**

SOIC、TSSOP

**ピン機能説明**

| ピン番号   | 記号              | 機能                                                                                                                                                                              |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | CS              | チップ・セレクト。アクティブ・ローのロジック入力。この入力は、AD7888の変換開始とシリアル・データ転送フレーム化の2つの機能を持っています。                                                                                                        |

| 2      | REF IN/REF OUT  | リファレンス入／出力。AD7888の外部で使用するため内蔵リファレンスをこのピンから取り出せます。あるいは内蔵リファレンスをディスエーブルにして、このピンに外部リファレンスを接続できます。外部から入力するリファレンス範囲は +1.2V ~ V <sub>DD</sub> です。                                     |

| 3      | V <sub>DD</sub> | 電源入力。AD7888のV <sub>DD</sub> 範囲は +2.7 ~ +5.25V です。                                                                                                                               |

| 4、13   | AGND            | アナログ・グラウンド・ピン。このピンは、AD7888の全回路に対するグラウンド・リファレンス・ポイントになります。すべての入力信号とすべての外部リファレンス信号はこのピンの電位を基準とします。両ピンともシステムのAGNDパターンに接続してください。                                                    |

| 5 ~ 12 | AIN1 ~ AIN8     | アナログ入力1~8。この8本のシングルエンド・アナログ入力は、マルチプレクスされて、内蔵のトラック／ホールド回路に入力されます。変換対象チャンネルは、コントロール・レジスタのADD0 ~ ADD2ビットで指定します。各ピンの入力電圧範囲は0 ~ V <sub>REF</sub> です。未使用チャンネルはノイズの混入を避けるためAGNDに接続します。 |

| 14     | DIN             | データ入力。ロジック入力。AD7888のコントロール・レジスタに書き込むデータをこのピンに接続し、SCLKの立ち上がりエッジでレジスタに入力します（コントロール・レジスタの節を参照してください）。                                                                              |

| 15     | DOUT            | データ出力。ロジック出力。AD7888の変換結果がこのピンにシリアル・データ・ストリームとして出力され、SCLK入力の立ち下がりエッジで駆動されます。データ・ストリームは、先頭の4ビットのゼロと、それに続く12ビットの変換データ（MSB先頭）により構成されます。                                             |

| 16     | SCLK            | シリアル・クロック。ロジック入力。SCLKは、デバイスからのデータの読み出し、およびコントロール・レジスタへのシリアル・データの書き込みで、シリアル・クロックとして機能します。このクロック入力は、AD7888の変換プロセスに対するクロック・ソースとしても使用されます。                                          |

# AD7888

## 用語集

### 積分非直線性

ADC伝達関数の両端を結ぶ直線からの最大偏差をいいます。伝達関数の両端とは、最初のコード変化より1/2LSB下のゼロ・スケールと最後のコード変化より1/2LSB上のフル・スケールをいいます。

### 微分非直線性

ADCの2つの隣接コード間における1LSB変化の測定値と理論値の差をいいます。

### オフセット誤差

最初のコード変化( 0000 . . . 000から0000 . . . 001への変化 )と理論変化( AGND + 0.5LSB )の差をいいます。

### オフセット誤差マッチ

任意の2チャンネル間のオフセット誤差の差をいいます。

### ゲイン誤差

オフセット誤差を調整した後の、最後のコード変化( 1111 . . . 110から1111 . . . 111への変化 )と理論変化(  $V_{REF} - 1.5\text{LSB}$  )の差をいいます。

### ゲイン誤差マッチ

任意の2チャンネル間のゲイン誤差の差をいいます。

### トラック / ホールド・アクイジション時間

変換の終わりにトラック / ホールド・アンプはトラック・モードに戻ります。トラック / ホールド・アクイジション時間は、変換終了後にトラック / ホールド・アンプ出力が最終値  $\pm 1/2\text{LSB}$  に到達するまでに要する時間をいいます。

### 信号対ノイズ+歪み比

A/Dコンバータの出力で測定される信号と( ノイズ+歪み )の比をいいます。信号は基本波のrms振幅で、ノイズはサンプリング周波数の1/2(  $f_S/2$  )までの、DCと基本波を除く全信号のrms値の総和です。この比は、量子化プロセスの量子化レベル数に依存します。レベル数が大きいほど、量子化ノイズは小さくなります。サイン波入力に対する理想Nビット・コンバータの理論的な信号対( ノイズ+歪み )比は、次式で得られます。

$$\text{信号対( ノイズ+歪み )比} = ( 6.02 N + 1.76 ) \text{dB}$$

12ビット・コンバータの場合、この値は74dBになります。

### 全高調波歪み

全高調波歪み( THD )は、高調波のrms値総和と基本波の比です。AD7888の場合、次式で得られます。

$$THD(\text{dB}) = \log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}$$

ここで、 $V_1$ は基本波のrms振幅で、 $V_2, V_3, V_4, V_5, V_6$ は2次～6次高調波のrms振幅です。

### ピーク高調波またはスプリアス・ノイズ

ピーク高調波またはスプリアス・ノイズは、ADC出力スペクトル( DCを除き、 $f_S/2$ まで )内で2番目に大きい成分のrms値と基本波のrms値の比として定義されます。通常、この仕様の値はスペクトル内の最大高調波により決定されますが、高調波がノイズプロアに埋もれているデバイスの場合は、ノイズ・ピークにより決定されます。

### 相互変調歪み

2つの周波数 $f_a$ と $f_b$ を持つサイン波で構成される入力に対して、非直線性を持つすべてのアクティブ・デバイスは、和と差の周波数 $m f_a \pm n f_b$  (  $m, n = 0, 1, 2, 3, \dots$  )の歪み項を発生します。相互変調項は、 $m$ と $n$ が非ゼロの項です。例えば、2次項には、 $( f_a + f_b )$ と $( f_a - f_b )$ が含まれ、3次項には $( 2f_a + f_b )$ 、 $( 2f_a - f_b )$ 、 $( f_a + 2f_b )$ 、 $( f_a - 2f_b )$ が含まれます。

AD7888はCCIF規格に従い入力帯域上限に近い2つの入力周波数を使ってテストされています。この場合、一般に、2次項は元のサイン波から離れた周波数になりますが、3次項は、入力周波数に近い周波数になります。そのため、2次項と3次項は別々に規定されます。相互変調歪みの計算は、個々の歪み成分のrms総和と基本波rms振幅の比( 単位dB )と定めているTHD仕様に従って行います。

### チャンネル間アイソレーション

チャンネル間アイソレーションは、チャンネル間のクロストーク・レベルの測定値をいいます。フル・スケールの25kHzサイン波信号を非選択入力チャンネルに入力して、選択チャンネルでのその信号の減衰量を測定します。この数値は、AD7888の全4チャンネルまたは全8チャンネル間での最悪時にあたります。

### PSR ( 電源除去比 )

電源変動はフルスケール変化に影響を与えますが、コンバータの直線性には影響しません。電源除去比は、公称値からの電源電圧変化に起因するフルスケール変化ポイントでの最大変化になります。

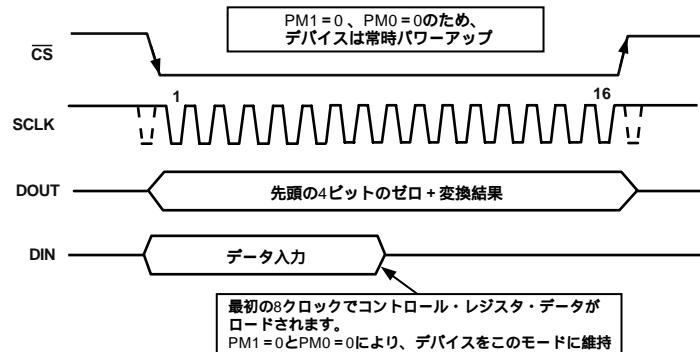

## コントロール・レジスタ

AD7888のコントロール・レジスタは8ビットの書き込み専用レジスタです。データはAD7888のDINピンからSCLKの立ち上がりエッジでロードされます。データは、デバイスからの変換結果の読み出しと同時にDINライン上に転送されます。この動作では、各データ転送に対して16個のシリアルクロックを必要とします。CSの立ち下がりエッジ後の最初の8個のクロック立ち上がりエッジで入力された情報のみが、コントロール・レジスタにロードされます。MSBはデータ・ストリームの先頭ビットです。ビットの機能を表Iに示します。コントロール・レジスタはパワーアップ時にゼロクリアされます。

表I コントロール・レジスタ

## MSB

| DONTC | ZERO | ADD2 | ADD1 | ADD0 | REF | PM1 | PM0 |

|-------|------|------|------|------|-----|-----|-----|

|-------|------|------|------|------|-----|-----|-----|

| ビット | 記号       | 備考                                                                                                                                                                      |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DONTC    | 無視。コントロール・レジスタのこのビットに書き込まれた値は無視、すなわち、このビットは“0”または“1”的いずれでもかまいません。                                                                                                       |

| 6   | ZERO     | AD7888の正常動作のためにこのビットにはゼロを書き込む必要があります。                                                                                                                                   |

| 5   | ADD2     | これらの3ビットは現在の変換シーケンスの終わりにロードされ、次に変換するアナログ入力チャンネルを選択します。選択された入力チャンネルは表IIのようにデコードされます。                                                                                     |

| 4   | ADD1     |                                                                                                                                                                         |

| 3   | ADD0     |                                                                                                                                                                         |

| 2   | REF      | リファレンスピット。このビットが“0”的場合は、オンチップリファレンスがイネーブルにされます。このビットが“1”的場合は、内蔵フーレンスがディスエーブルにされます。外部からリファレンスを与えるときは、AD7888の最適性能を得るために内蔵リファレンスをディスエーブルにしておく必要があります(内蔵リファレンスの節を参照してください)。 |

| 1,0 | PM1, PM0 | パワー・マネジメントビット。この2ビットは、次の表IIIに従いAD7888の動作モードを指定します。                                                                                                                      |

## 性能曲線

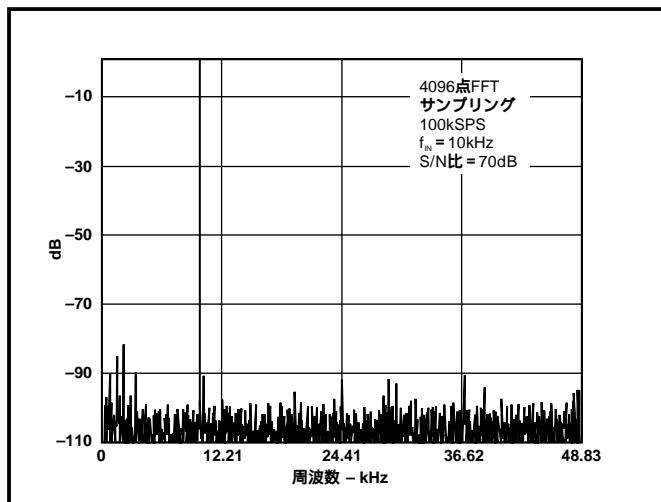

図2に、100kHzサンプル・レートと10kHz入力周波数におけるAD7888の代表的なFFTプロットを示します。

図2 ダイナミック性能

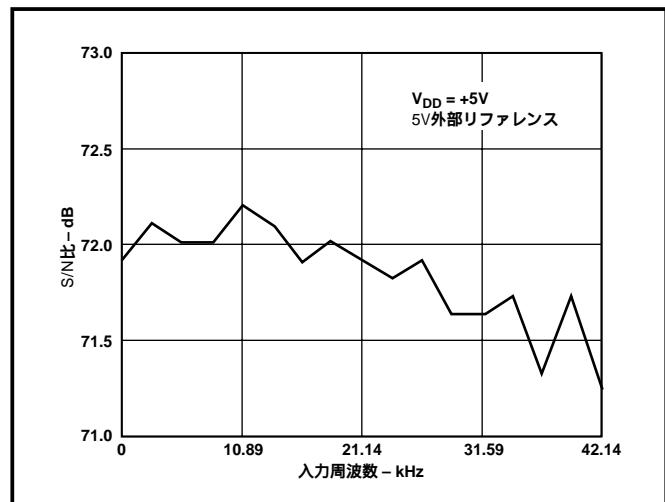

図3に、5V電源と5V外部リファレンスを使用した場合のS/N比と周波数の関係を示します。

図3 S/N比対入力周波数

# AD7888

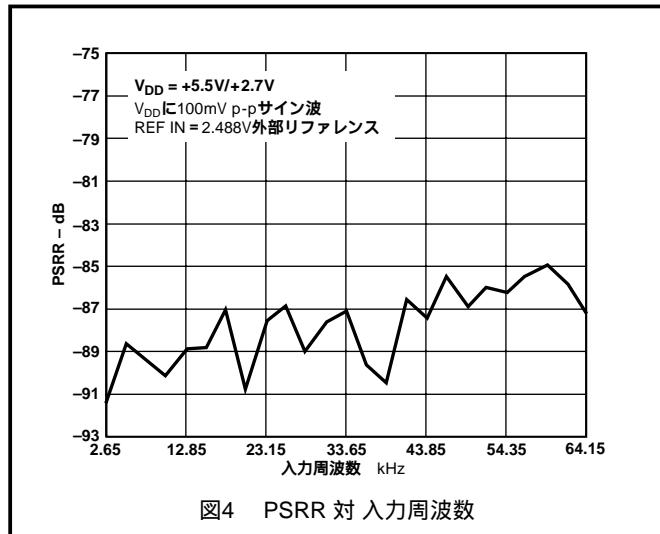

図4に、デバイスの電源除去比と周波数の関係を示します。電源除去比は、ADC出力での周波数fの電力とADCに入力された周波数f<sub>s</sub>のフルスケール・サイン波電力の比として次のように定義されます。

$$PSRR(\text{dB}) = 10 \log(P_f/P_{fs})$$

ここで、P<sub>f</sub> = ADC出力での周波数fの電力、P<sub>fs</sub> = 周波数f<sub>s</sub>のADCフルスケール入力の電力。ここで、100mVのピークtoピークサイン波をV<sub>DD</sub>電源に結合しています。+2.7V電源と+5.5V電源の性能が示してあります。

## 回路情報

AD7888は、単電源動作、低消費電力の高速12ビット・シングル / デュアルレ・チャンネルA/Dコンバータです。+3V( +2.7 ~ +3.6V )電源または+5V( +4.75 ~ +5.25V )電源で動作します。+5Vまたは+3Vの電源で動作する場合、AD7888は2MHzクロックで125kSPSのスループット・レートを実現します。

AD7888は、トラック / ホールド、A/Dコンバータ、リファレンス、シリアル・インターフェースを内蔵し、際立った省スペース効果を持つ小型16ピン・パッケージを採用しています。シリアル・クロック入力は、デバイスからのデータ読み出しと、逐次近似型A/Dコンバータに対するクロック・ソースとして使います。アナログ入力範囲は0 ~ V<sub>REF</sub>( 外部から入力するV<sub>REF</sub>は+1.2V ~ V<sub>DD</sub> )になります。

8チャンネル・マルチプレクサは、デバイスのコントロール・レジスタにより制御されます。また、このコントロール・レジスタは、内蔵リファレンスのパワーオフと動作モードの指定にも使用されます。

## 変換動作

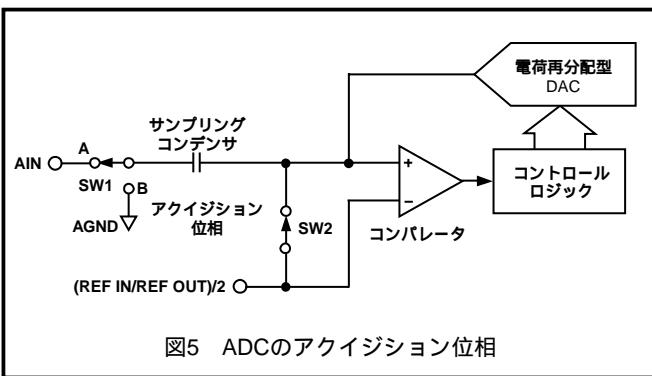

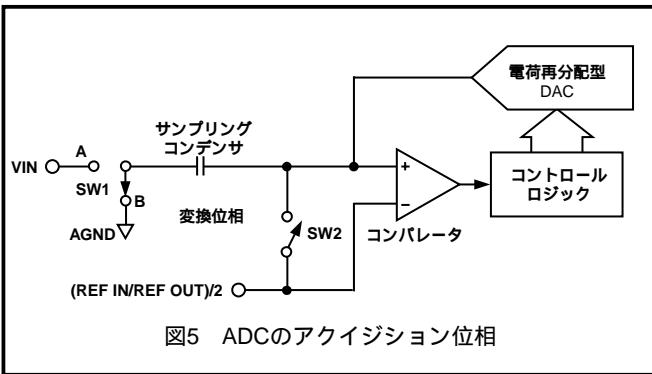

AD7888は、電荷再分配型DACを採用した逐次近似型A/Dコンバータです。図5と図6に、ADCの簡略化した回路図を示します。図5に、アクイジション位相のADCを示します。SW2が閉じて、SW1はポジションAにあり、コンパレータは平衡状態にあります。サンプリング・コンデンサは、AIN上の信号を取り込みます。

図5 ADCのアクイジション位相

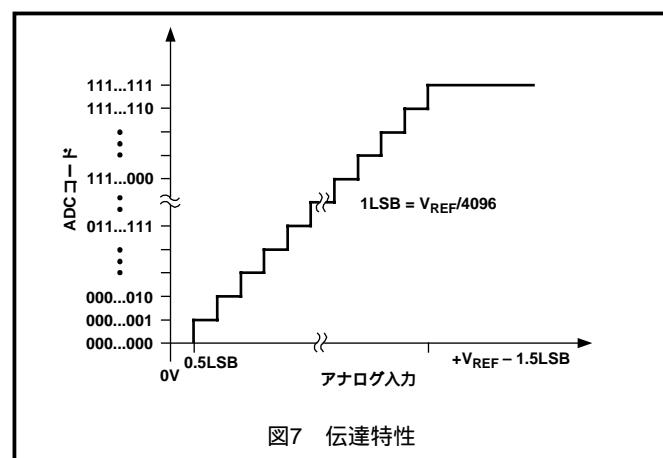

ADCが変換を開始すると(図6参照)、SW2が開いて、SW1がポジションBに移動してコンパレータの平衡を失わせます。次に、コントロール・ロジックと電荷再分配型DACを使って、サンプリング・コンデンサに対して一定量の電荷を加算または減算してコンパレータを平衡状態に戻します。コンパレータが平衡状態に戻ると、変換が完了します。コントロール・ロジックはADC出力コードを発生します。図7に、ADCの伝達関数を示します。

図5 ADCのアクイジション位相

## ADCの伝達関数

AD7888の出力コード化は自然2進数です。符号付きコードの変化は、LSBの連続する整数倍値( すなわち、1×LSB、2×LSB... )で発生します。LSBサイズ=V<sub>REF</sub>/4096です。AD7888の理論伝達関数を図7に示します。

図7 伝達特性

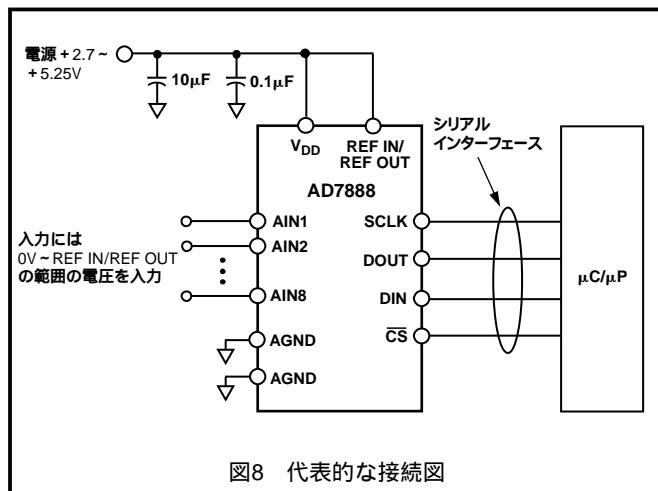

## 代表的な接続図

図8に、AD7888の代表的な接続図を示します。両AGNDピンはシステムのアナログ・グラウンド・プレーンに接続されています。 $V_{REF}$ は良好にデカップリングされた $V_{DD}$ ピンに内部で接続されており、アナログ範囲は0V ~  $V_{DD}$ になります。変換結果は16ビット・ワードで出力され、先頭の4ビットのゼロの後ろに12ビット変換結果のMSBが続きます。消費電力が問題になるアプリケーションに対しては、変換の終了時に自動パワーダウンを使って消費電力性能を改善できます。データシートの動作モードの節を参照してください。

図8 代表的な接続図

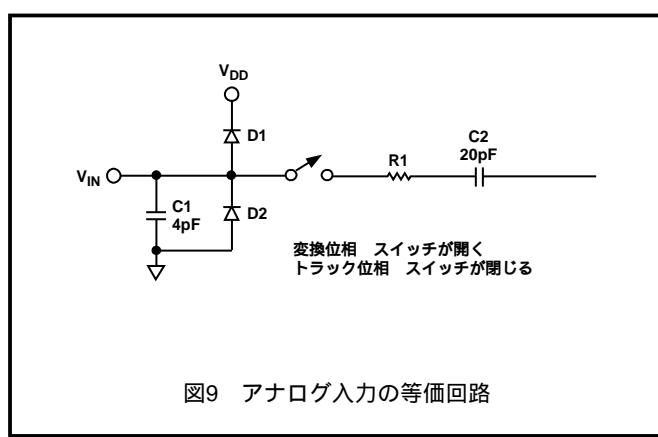

## アナログ入力

図9に、AD7888のアナログ入力構造の等価回路を示します。2個のダイオードD1とD2は、アナログ入力にESD保護機能を提供します。アナログ入力信号は、絶対に電源電圧より200mV以上高くしないように注意してください。電源電圧より高くなると、これらのダイオードが順方向バイアスされて、電流はサブストレートに流入します。デバイスに回復不可能な損傷を与えないでこれらのダイオードに流すことができる最大電流は20mAですが、非選択チャンネル上の過電圧に起因して小さい電流(1mA)がサブストレートに流入すると、選択されたチャンネル上の変換に悪影響を与えることがあります。図9に示すコンデンサC1は通常約4pFであり、主にピン容量に寄与します。抵抗R1は、マルチプレクサとスイッチのON抵抗から構成されており、約100Ωです。コンデンサC2はADCサンプリング・コンデンサであり、20pF(typ)です。

注: トラック・モードでのアナログ入力容量は38pF(typ)で、ホールド・モードでは4pF(typ)です。

図9 アナログ入力の等価回路

ACアプリケーションに対しては、該当するアナログ入力ピンにRCオーパス・フィルタを使用して、アナログ入力信号から高周波成分を除去することを推奨します。高調波歪みとS/N比が重要なアプリケーションでは、アナログ入力を低インピーダンス・ソースから駆動する必要があります。高いソース・インピーダンスは、ADCのAC性能に大きな影響を与えます。このために、入力バッファ・アンプの使用が必要になります。オペアンプの選択は、アプリケーションに依存します。

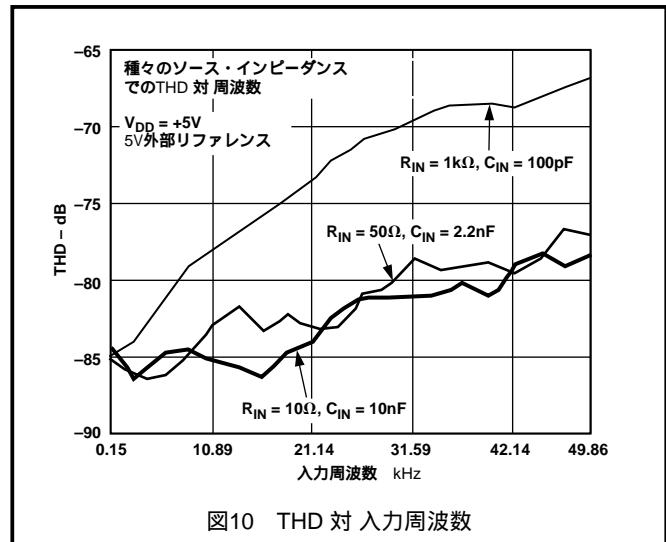

アンプを使用しないでアナログ入力を駆動するときは、ソース・インピーダンスを小さい値に制限する必要があります。最大ソース・インピーダンスは、許容全高調波歪み(THD)に依存します。ソース・インピーダンスが大きくなるほどTHDが大きくなり、性能が低下します。図10に、全高調波歪みとアナログ入力信号周波数の関係を、種々のソース・インピーダンスに対して示します。

図10 THD 対 入力周波数

## アナログ入力の選択

パワー・アップ時に、デフォルトとしてAIN1が選択されます。パワーダウン状態から通常動作に戻るときは、パワーダウンに入る前に選択されていたAINが選択されます。表IIに、AD7888のアナログ入力AIN1 ~ AIN8に対応するマルチプレクサのアドレスを示します。

表 II チャンネルの選択

| ADD2 | ADD1 | ADD0 | アナログ入力チャンネル |

|------|------|------|-------------|

| 0    | 0    | 0    | AIN1        |

| 0    | 0    | 1    | AIN2        |

| 0    | 1    | 0    | AIN3        |

| 0    | 1    | 1    | AIN4        |

| 1    | 0    | 0    | AIN5        |

| 1    | 0    | 1    | AIN6        |

| 1    | 1    | 0    | AIN7        |

| 1    | 1    | 1    | AIN8        |

## 内蔵リファレンス

AD7888は2.5Vリファレンスを内蔵しています。このリファレンスは、コントロール・レジスタ内内のREFビットをクリア / セットして、イネーブル / ディスエーブルを選択できます。システム内で内蔵リファレンスを外部から使用する場合は、バッファを通す必要があります。外部リファレンスをデバイスに接続すると、内蔵リファレンスは自動的に切り離されますが、デバイスの最適性能を得るために、外部リファレンスを接続する場合には、コントロール・レジスタ内内のREFビットをセットして、内蔵リファレンスをディスエーブルにしておくことを推奨します。

# AD7888

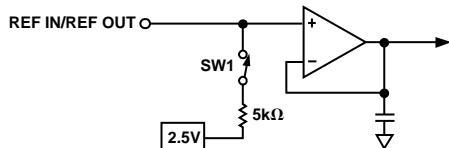

内蔵リファレンスをディスエーブルにすると、図11のSW1が開いて、REF IN/REF OUTピンの入力インピーダンスとしては、リファレンスバッファの入力インピーダンス(ギガ 値)がみられます。内蔵リファレンスがイネーブルにされると、ピンの入力インピーダンスは5k (typ)になります。

図11 内蔵リファレンスの回路

表 III パワー・マネジメントのオプション

| PM1 | PM0 | モード                                                                                                                                                              |

|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | 通常モード。このモードでは、AD7888はすべてのロジック入力ピンの状態に無関係に、フルパワーに留まります。このモードでは、AD7888の最高のスループットが得られます。                                                                            |

| 0   | 1   | フル・シャットダウン・モード。このモードでは、内蔵リファレンスを含むAD7888上の全回路がパワーダウン・モードになります。AD7888はフル・シャットダウン・モードになります。                                                                        |

| 1   | 0   | 自動シャットダウン。このモードでは、各変換の終わりにAD7888は自動的にシャットダウン・モードになります。フル・シャットダウン・モードからのウェイクアップ時間は5μsであるため、このモードで変換を有効に行なうためには、5μs経過後に変換を開始する必要があります。                             |

| 1   | 1   | 自動スタンバイ・モード。このスタンバイモードでは、AD7888の一部がパワーダウンされますが、内蔵リファレンスは動作します。内蔵リファレンスを確実にイネーブルにするため、REFビットは“0”に設定する必要があります。このモードは自動シャットダウン・モードに似ていますが、デバイスのパワーアップが高速である点が異なります。 |

## パワーダウン・オプション

AD7888はフレキシブルなパワー・マネジメントを持っており、与えられたスループット・レートに対して最適性能を得ることができます。パワー・マネジメント・オプションは、コントロール・レジスタ内のパワー・マネジメント・ビット( PM1とPM0 )を使って選択できます。表IIIに、使用可能なオプションを示します。パワー・マネジメント・ビットがいずれかの自動パワーダウン・モードに設定されると、デバイスは、CSの立ち下がリエッジの後の、SCLKの16個目の立ち上がりエッジでパワーダウン・モードに入ります。CS立ち下がリエッジの後の、SCLKの最初の立ち下がリエッジで、デバイスは再度パワーアップします。AD7888がフル・シャットダウン・モードの場合、デバイスを再度パワーアップさせる唯一の方法は、パワー・マネジメント・ビットをPM1 = PM0 = 0(通常モード)に再設定することです。この場合、デバイスはCSの立ち下がリエッジの後の、SCLKの16個目の立ち上がりエッジでパワーアップします。これはパワー・マネジメント・ビットがこのタイミングで有効になるためです。

## パワーアップ時間

スタンバイ・モードからのパワーアップの場合、または外部リファレンスを使用する場合には、AD7888には約1μsのパワーアップ時間がかかります。V<sub>DD</sub>が最初に接続されると、AD7888は通常モードでパワーアップします。デバイスがシャットダウンされた場合、その後のパワーアップには、約5μs必要です。自動スタンバイ・モードでのAD7888のウェイクアップ時間は非常に短いため、同一の読み出し / 書き込み動作内でウェイクアップと有効な変換を実行できます。

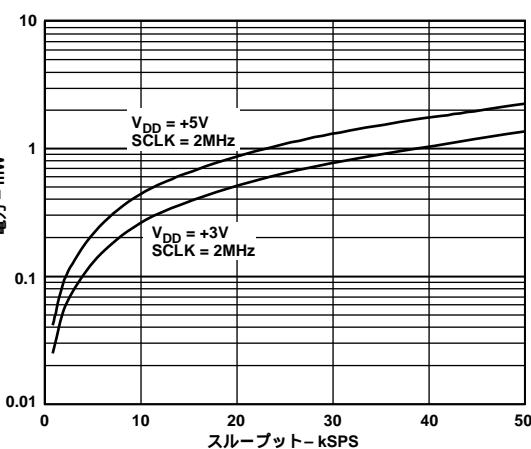

## 消費電力 対 スループット

AD7888を自動シャットダウン・モードまたは自動スタンバイ・モードで動作させることにより、AD7888の平均消費電力を低速スループット・レートで削減できます。図12に、スループット・レートを減少させていくと、デバイスはパワーダウン状態に長く留まるようになるため、平均消費電力が減少していく様子を示します。

例えば、AD7888が連続サンプリング・モードで動作し、スループット・レートが10kSPS、SCLK = 2MHz( V<sub>DD</sub> = 5V ) PM1 = 1かつPM0 = 0の場合、すなわちデバイスが自動シャットダウン・モードで内部リファレンスを使用する場合、消費電力は次のように計算されます。通常動作時の消費電力は3.5mW( V<sub>DD</sub> = 5V )です。パワーアップ時間が5μsで、残りの変換時間とアクイジョン時間の和が15.5tSCLK( 約7.75μs )の場合( 図14a )、AD7888は各変換サイクルの12.75μs間で3.5mWを消費するといえます。スループット・レートが10kSPSの場合、サイクル時間は100μsで、各サイクルでの平均消費電力は、( 12.75/100 ) × ( 3.5mW ) = 446.25μWになります。V<sub>DD</sub> = 3V、SCLK = 2MHz、かつデバイスが内蔵リファレンスを使って自動シャットダウン・モードで動作する場合、通常動作の消費電力は2.1mWです。AD7888は各変換サイクル12.75μsで2.1mW消費するといえます。スループット・レートが10kSPSの場合、各サイクルでの平均消費電力は、( 12.75/100 ) × ( 2.1mW ) = 267.75μWになります。図12に、自動シャットダウンにおける5Vと3Vの電源に対する消費電力とスループット・レートの関係を示します。

図12 消費電力 対 スループット

図13 通常モードの動作

### 動作モード

AD7888には多くの動作モードがあります。これらは、フレキシブルなパワー・マネジメント・オプションを提供するために設計されています。これらのオプションを選択して、様々なアプリケーションの条件に対して消費電力 / スループット・レート比を最適化できます。動作モードは先述のように、コントロール・レジスタ内のPM1ビットとPM0ビットにより制御されます。

#### 通常モード (PM1 = 0, PM0 = 0)

このモードでは、AD7888を常時動作させるためパワーアップ時間を感じる必要がなく、最高のスループット・レートで動作させることができます。図13に、このモードでのAD7888の動作の全体図を示します。

AD7888のDINラインに入力されたデータは、データ転送の最初の8クロック・サイクルでコントロール・レジスタにロードされます。変換までの書き込みでPM0とPM1が“0”に設定される限り、デバイスはその変換の終わりにもパワーオン状態を維持します。このモードでの動作を維持するためには、各データ転送でPM0=PM1=0をロードする必要があります。

CSの立ち下がりエッジにより、シーケンスが起動され、SCLK入力の2つの立ち上がりエッジで、入力信号がサンプルされます。変換を完了して変換結果を得るために、シリアル・クロックで16周期を要します。データ転送が完了したら( CSがハイに戻ったら ) CSをローに戻すことにより、直ちに次の変換を開始できます。

#### フル・シャットダウン (PM1 = 0, PM0 = 1)

このモードでは、内蔵リファレンスを含むAD7888の全回路がパワー

ダウンします。フル・シャットダウン中でもコントロール・レジスタの情報は維持されます。パワー・マネジメント・ビットが変更されるまで、デバイスはフル・シャットダウン状態を維持します。パワー・マネジメント・ビットがPM1=1かつPM0=0( 自動シャットダウン・モード )に変更されると、デバイスはシャットダウン状態を維持しますが( ただし今度は自動シャットダウン )その後で変換が開始されると、デバイスはパワーアップします( パワーアップ時間の節を参照 )。コントロール・レジスタが変更されると直ちにデバイスのモードが変わるため、デバイスのフル・シャットダウン中にパワー・マネジメント・ビットがPM1=0かつPM0=0( 通常モード )に変更されると、SCLKの16個目の立ち上がりエッジでデバイスはパワーアップします。

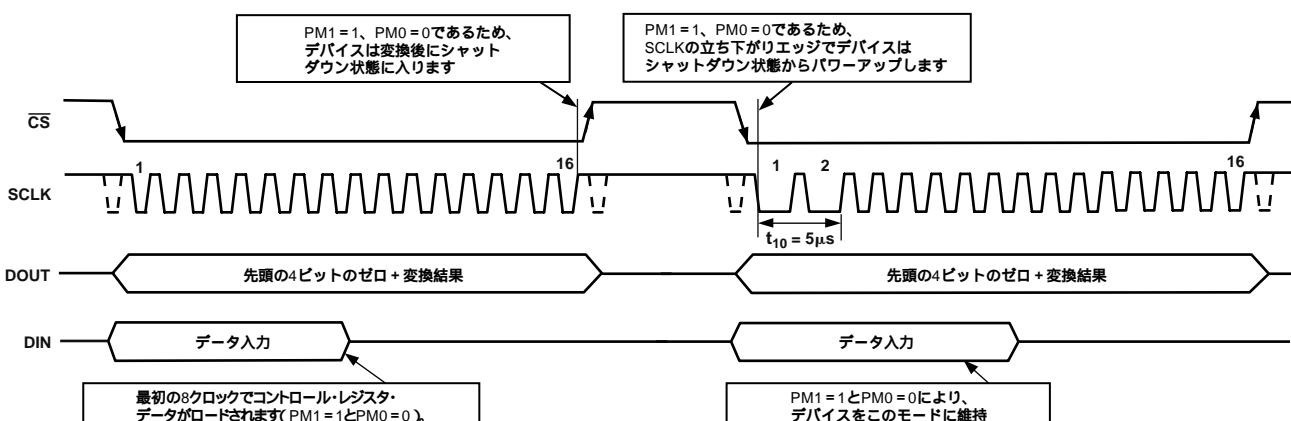

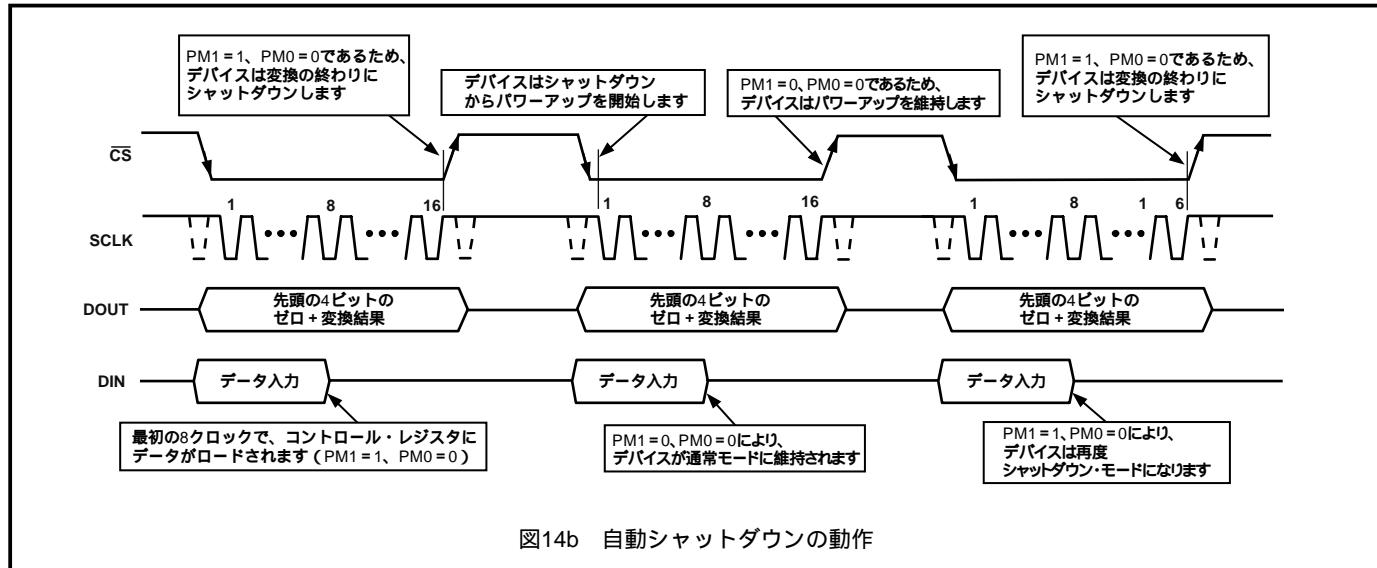

#### 自動シャットダウン (PM1 = 1, PM0 = 0)

このモードでは、AD7888は各変換終了後に自動的にパワーダウン・モードに入ります。通常モードに似ていますが、AD7888のパワーダウン状態がCSの状態に影響されない点が異なります。図14aに、このモードでのAD7888の動作の全体図を示します。

CSがハイからローに変化すると、SCLKの次の立ち下がりエッジで、全内部回路がパワーアップを開始します。SCLKの16個目の立ち上がりエッジでデバイスは再度パワーダウンします。AD7888の内部回路が完全にパワーアップするためには、約5μsを要します。そのため、この5μsの間は、変換( すなわち、サンプル / ホールド・アクイジョン )を開始できません。CS立ち下がりエッジの後の、SCLKの2つの立ち上がりエッジで入力信号がサンプルされます。CSの立ち下がりエッジの後の、SCLKの最初の立ち下がりエッジとSCLKの2つの立ち上がりエッジの間で5μsを保証する必要があります( 図14a )。

図14a 自動シャットダウン動作

# AD7888

図14b 自動シャットダウンの動作

マイクロコントローラ・アプリケーションでは、これは、 $\overline{CS}$ 入力をポート・ラインの1本で駆動し、マイクロコントローラのシリアル・ポートからのシリアル・データの読み出しを5 $\mu$ s間隔らせることにより実現できますが、一般にシリアル・フレーム同期ラインから $\overline{CS}$ を導出するDSPアプリケーションの場合は、 $\overline{CS}$ の立ち下がり後の、SCLKの最初の立ち上がりエッジと2個目の立ち上がりエッジの間に最大5 $\mu$ sの遅延を挿入することはできません。したがって、コントロール・レジスタに書き込みを行ってこのモードを抜け出した後に、PM1=0とPM0=0を書き込んでデバイスを通常モードにして、デバイスがパワーアップした後に2番目の変換を開始して変換結果を得るようにします(図14b)。

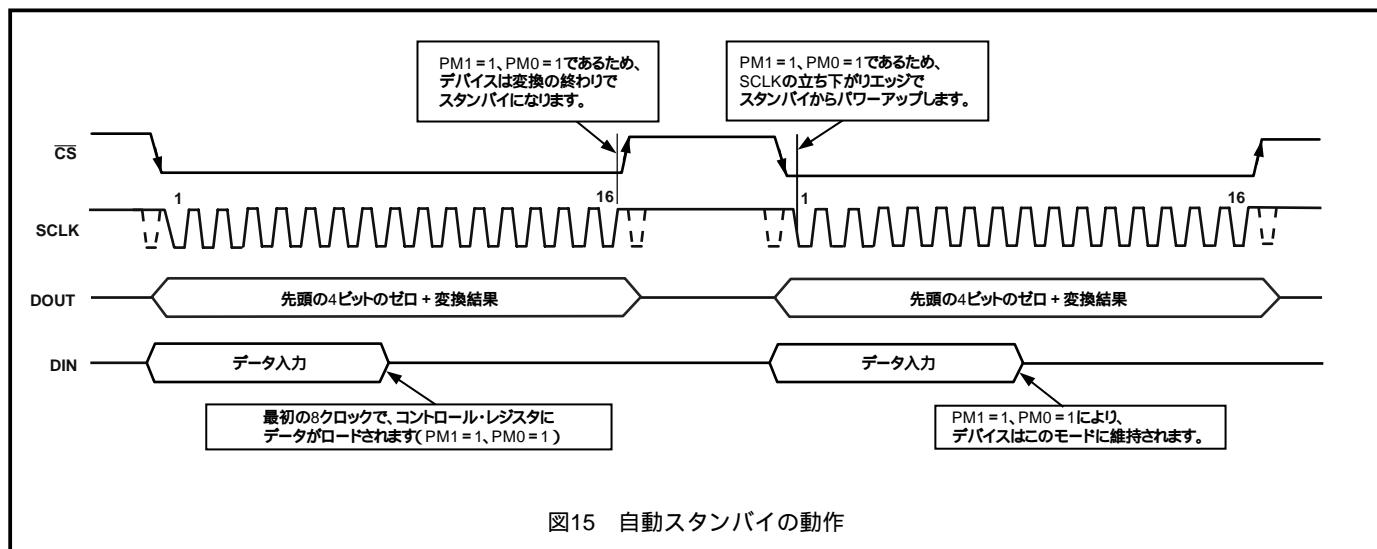

## 自動スタンバイ (PM1 = 1, PM0 = 1)

このモードでは、AD7888は各変換終了後に自動的にスタンバイ(またはスリープ)モードに入ります。このモードでは、内蔵リファレンスに接続されていない全内蔵回路がパワーダウン状態になります。このスタンバイ・モードはシャットダウン・モードに似ていますが、内蔵リファレンスが常時動作しているためパワーアップ時間が短くなります。図16に、このモードでのAD7888の動作の全体図を示します。 $\overline{CS}$ がローに変化した後の最初のSCLKの立ち下がりエッジで、AD7888はスタンバイを抜け出します。このモードでは、AD7888ウェイクアップ時間が非常に短いため、同一の読み出し / 書き込み動作内でデバイスのウェイクアップと有効な変換を行えます。 $\overline{CS}$ 立ち下がりエッジの後のSCLKの2つ目の立ち上がりエッジで、入力信号がサンプルされます。変換の終わりに( SCLKの最後の立ち上がりエッジ )で、デバイスは自動的にスタンバイ・モードに入ります。

図15 自動スタンバイの動作

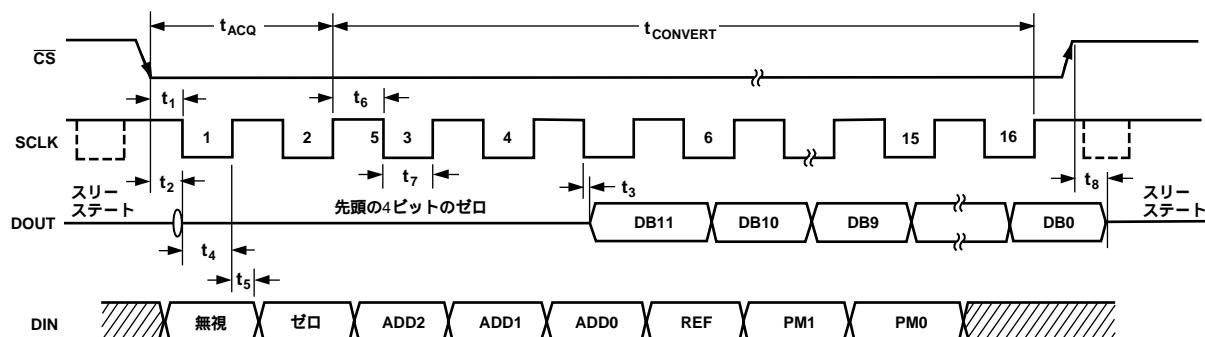

## シリアル・インターフェース

図16に、AD7888のシリアル・インターフェースの詳細タイミング図を示します。シリアル・クロックは変換クロックを提供し、さらに変換中のAD7888に対する情報転送も制御します。

$\overline{CS}$ はデータ転送と変換プロセスを開始させます。シャットダウン・モードでは、 $\overline{CS}$ の立ち下がりエッジの後の、SCLKの最初の立ち下がりエッジがデバイスをウェイクアップさせます。どの場合でも、 $\overline{CS}$ はAD7888に対するシリアル・クロックをゲーティングし、内蔵トラック／ホールド回路をトラック・モードに設定します。 $\overline{CS}$ の立ち下がりエッジの後の、SCLK入力の2つ目の立ち上がりエッジで入力信号がサンプルされます。このため、 $\overline{CS}$ の立ち下がりエッジの後の、最初の1.5クロック・サイクルで、入力信号のアクイジションが実行されます。この時間はアクイジション時間( $t_{ACQ}$ )と呼ばれています。自動シャットダウン・モードでは、アクイジション時間内に5 $\mu$ sのウェイクアップ時間を確保する必要があります。オンチップ・トラック／ホールド回路はSCLKの2番目の立ち上がりエッジでトラック・モードからホールド・モードに変わり、このエッジで変換も開始されます。変換プロセスが完了するまでにさらに14.5個のSCLKサイクルを必要とします。 $\overline{CS}$ の立ち上がりエッジにより、バスはスリーステートに戻されます。 $\overline{CS}$ をローのままに維持すると、新しい変換が開始されます。

コントロール・レジスタに対する前の書き込みで選択されたチャンネルが、サンプルされる入力チャンネルになります。したがって、チャン

ネルの変換に先だって、書き込みを行つ必要があります。言い換えれば、次の変換のチャンネル・アドレスを現在の変換の進行中に書き込む必要があります。

コントロール・レジスタに対する情報の書き込みは、データ転送内の、SCLKの最初の8個の立ち上がりエッジで行われます。データ転送を行うときは、常にコントロール・レジスタに書き込みを行つ必要があります。データをデバイスから読み出す際、常に、DINラインに正しい情報を設定するように注意する必要があります。

変換プロセスを実行してAD7888からデータを読み出すためには、16サイクルのシリアル・クロックが必要です。 $\overline{CS}$ がローに変化した後の、最初のシリアル・クロック・エッジが立ち下がりエッジであるアプリケーションでは、このエッジが先頭のゼロを出力します。したがって、SCLKクロックの最初の立ち上がりクロック・エッジにより、先頭のゼロを出力します。最初のシリアル・クロック・エッジが立ち上がりエッジであるアプリケーションでは、最初のゼロをプロセッサが正しく読み取るまでに間に合わない可能性があります。ただし、後続のビットをSCLKの立ち下がりエッジで出力して、次の立ち上がりエッジでプロセッサに間に合うように出力します。このため、2つ目のゼロは最初の立ち上がりエッジの次の立ち下がりエッジで出力されます。データ転送内の最終ビットは、16番目の立ち上がりエッジで有効で、前の立ち下がりエッジで出力されています。

図16 シリアル・インターフェースのタイミング図

# AD7888

## マイクロプロセッサとのインターフェース

AD7888は、シリアル・インターフェースを使ってさまざまなマイクロプロセッサに直接接続できます。この節では、AD7888と一般的なマイクロコントローラとのインターフェース方法とDSPシリアル・インターフェース・プロトコルについて説明します。

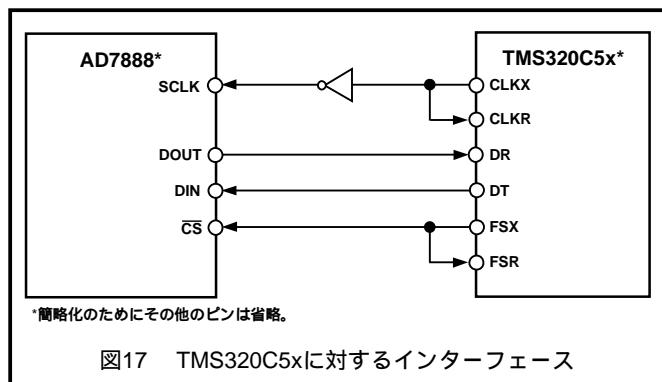

### AD7888とTMS320C5xのインターフェース

TMS320C5xのシリアル・インターフェースでは、連続シリアル・クロック信号とフレーム同期信号を使って、データ転送動作をAD7888のような周辺デバイスと同期化しています。CS入力を使うと、TMS320C5xのシリアル・クロックとAD7888の間にインバータを接続するだけで容易にインターフェースできます。TMS320C5xのシリアル・ポートは、内部CLKX(TXシリアル・クロック)とFSX(TXフレーム同期)により、バースト・モード動作に設定されます。シリアル・ポート・コントロール・レジスタ(SPC)は、FO=0, FSM=1, MCM=1, TXM=1に設定してください。図17に、接続図を示します。

図17 TMS320C5xに対するインターフェース

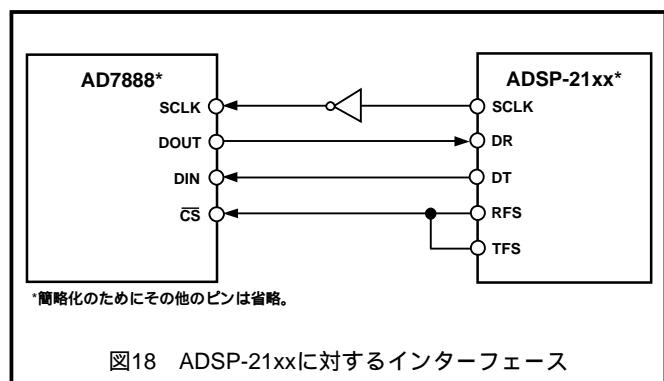

### AD7888とADSP-21xxとのインターフェース

DSPのADSP-21xxファミリーは、ADSP-21xxのシリアル・クロックとAD7888との間にインバータを接続するだけで容易にインターフェースできます。SPORTコントロール・レジスタは、次のように設定する必要があります。

TFSW=RFSW=1、交代フレーミング

INVRFS=INVTFS=1、アクティブ・ローのフレーム信号

DTYPE=00、データ右詰め

SLEN=1111、16ビット・データ・ワード

ISCLK=1、内部シリアル・クロック

TFSR=RFSR=1、ワード毎のフレーム

IRFS=0

ITFS=1

接続図を図18に示します。ADSP-21xxでは、TFSとSPORTのRFSを接続し、さらにTFSを出力に、RFSを入力にそれぞれ設定します。DSPは交代フレーミング・モードで動作し、SPORTコントロール・レジスタを上述のように設定します。TFS上で発生されるフレーム同期化信号はCSに接続され、すべての信号処理アプリケーションと同様に等間隔サンプリングが必要ですが、この例では、タイマー割り込みを使って、一定の条件下でADCのサンプリング・レートを制御するため、等間隔サンプリングは不可能です。

タイマー・レジスタなどには、必要なサンプル間隔で割り込みを発生するような値を設定します。割り込みを受信すると、TFS/DT(ADCコントロール・ワード)と一緒に値が送信されます。TFSを使ってRFSを制御するため、データの読み出しあれこれにより制御されます。シリアル・クロックの周波数はSCLKDIVレジスタに設定されます。TFSと一緒に送信する命令が与えられる(すなわち、AX0=TX0)SCLKの状態がチェックされます。DSPは、SCLKがハイからロー、次にまたローの順に変化するのを待った後に、送信を開始します。送信命令がSCLKの立ち上がりエッジまたはその近傍で発生するようにタイマー値とSCLK値が選択されている場合は、データが送信されるか、あるいは次のクロック・エッジまで待ちます。

例えば、ADSP-2111のマスター・クロック周波数が16MHzの場合、SCLKDIVレジスタに値3がロードされると、2MHzのSCLKが得られて、SCLKの1周期はマスター・クロックの8周期に相当します。タイマー・レジスタに値803がロードされると、割り込みの間隔、およびその後の送信命令の間隔はSCLK周期で100.5個分になります。この場合は、送信命令がSCLKエッジで発生するため、不等間隔のサンプリングになります。割り込みと割り込みの間のSCLK数がN.5の数値でない場合は、DSPでは等間隔サンプリングが実行されます。

図18 ADSP-21xxに対するインターフェース

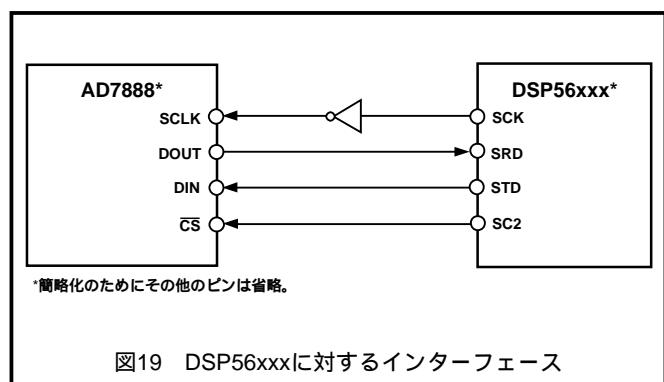

### AD7888とDSP56xxxとのインターフェース

AD7888とモトローラ社のDSP56xxxファミリーのSSI(同期シリアル・インターフェース)との接続方法を図19に示します。SSIは、TXとRXに対して内部で発生した1ビット・クロック幅のフレーム同期信号を使い(CRB内のFSL1ビット=1, FSL0ビット=0)同期モード(CRB内のSYNビット=1)で動作します。CRA内でWL1ビット=1とWL0ビット=0の設定を行い、ワード長を16に設定します。DSP56xxxのSCLKとAD7888のSCLKピンの間にインバータも必要です(図19)。

図19 DSP56xxxに対するインターフェース

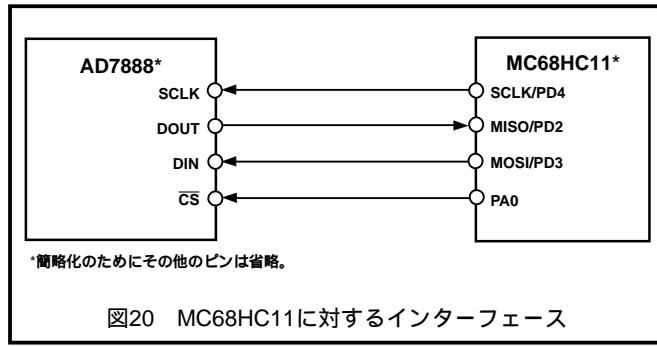

## AD7888とMC68HC11とのインターフェース

MC68HC11のシリアル・ペリフェラル・インターフェース(SPI)をマスター・モード(MSTR=1)に、クロック極性ビット(CPOL)=1に、クロック位相ビット(CPHA)=1に、それぞれ設定します。SPIはSPIコントローラ・レジスタ(SPCR)に対する書き込みにより設定されます(68HC11ユーザー・マニュアルを参照してください)。シリアル転送は2回の8ビット動作として実行されます。接続図を図20に示します。

図20 MC68HC11に対するインターフェース

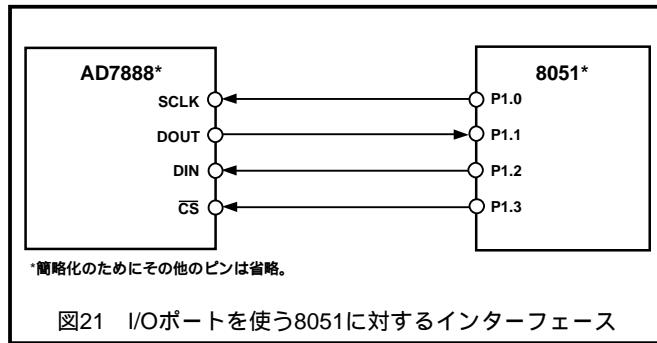

## AD7888と8051とのインターフェース

8051のデータ・ポートを使ってシリアル・インターフェースを構成できます。この方法では、全二重シリアル転送が可能です。I/Oポート(例えば、P1.0)でのビット操作によりシリアル・クロックを発生し、他の2本のI/Oポート(例えば、P1.1とP1.2)を使って、データの入出力を行います(図21)。

図21 I/Oポートを使う8051に対するインターフェース

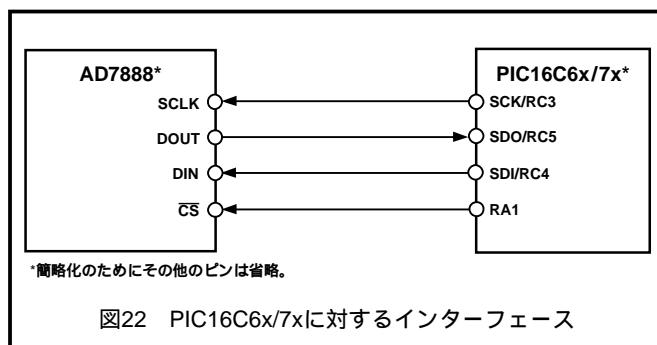

## AD7888とPIC16C6x/7xとのインターフェース

クロック極性ビット=1に設定して、PIC16C6x同期シリアル・ポート(SSP)をSPIマスターに設定します。この設定は、同期シリアル・ポート・コントローラ・レジスタ(SSPCON)に対する書き込みにより行います。PIC16/17マイクロコントローラ・ユーザー・マニュアルを参照してください。図22に、PIC16C6x/7xに対するインターフェースで必要なハードウェア接続を示します。この例では、I/OポートRA1を使ってCSパルスを発生しています。このマイクロコントローラは、各シリアル転送動作で8ビットのデータだけを転送します。したがって、連続した2回の読み出し/書き込み動作が必要です。

図22 PIC16C6x/7xに対するインターフェース

## アプリケーション・ヒント

### グラウンドとレイアウト

PSRRと周波数の関係のグラフに示すように、AD7888は電源ノイズに対して優れたノイズ耐性を持っていますが、グラウンドとレイアウトに関して注意が必要です。

AD7888を実装するプリント回路板は、アナログ部分とデジタル部分を分離して、ボードの一定の領域にまとめるように設計してください。そうすることにより、グラウンド・プレーンの分離が容易になります。グラウンド・プレーンは最善のシールド効果を与えるため、グラウンド・プレーンに対するエッチングは最小に抑えることを原則とします。デジタル・グラウンド・プレーンとアナログ・グラウンド・プレーンは、1点でのみ接続します。AD7888の両AGNDピンは、AGNDプレーンに接続します。AGNDプレーンとDGNDプレーンの接続は1点(AD7888のAGNDピンにできるだけ近い星形グラウンド・ポイント)で行う必要があります。

デバイスの裏面にデジタル・ラインを配線するとノイズがチップに混入するので、このような配線は避けてください。AD7888の裏面にアナログ・グラウンド・プレーンを配置してノイズの混入を避けてください。AD7888に入力する電源ラインはできるだけ太くしてバスのインピーダンスを小さくし、電源ライン上のグリッチの影響を削減してください。クロックのような高速スイッチング信号はデジタル・グラウンドによりシールドして、ボードの他の部分に対するノイズ放射を防止し、クロック信号をアナログ入力の近くに配線しないでください。デジタル信号とアナログ信号の交叉は回避してください。ボードの反対面のパターンは互いに右角度になるように配線してください。これにより、ボードを垂直に通過する結合効果を小さくできます。マイクロ・ストリップ技術は最適ですが、両面ボードで常に可能とは限りません。この技術では、ボードの部品面をグラウンド・プレーン専用に使用し、信号はハンダ面に配線されます。

優れたデカップリングも重要です。すべてのアナログ電源を10 $\mu$ Fタンタル・コンデンサと0.1 $\mu$ Fコンデンサの並列接続でAGNDからデカップリングする必要があります。これらのデカップリング部品を使って最善の効果を得るためにには、これらをデバイスのできるだけ近くに配置し、理想的にはデバイスの直ぐ隣りに配置することが望されます。

### AD7888の性能評価

AD7888に対する推奨レイアウトの概要をAD7888の評価ボードに示してあります。評価ボード・パッケージには、組み立ておよびテスト済みの評価ボード、ドキュメント、EVAL-CONTROL BOARDを経由してPCからボードを制御するためのソフトウェアが含まれています。EVAL-CONTROL BOARDをAD7888評価ボードや末尾番号CBの他の多くのアナログ・デバイセズの評価ボードと組み合わせて使うと、AD7888のAC/DC両方の特性のデモストレーション/評価を行うことができます。

このソフトウェアを使うと、AD7888のACテスト(高速フーリエ変換)とDCテスト(コードのヒストグラム)を行えます。

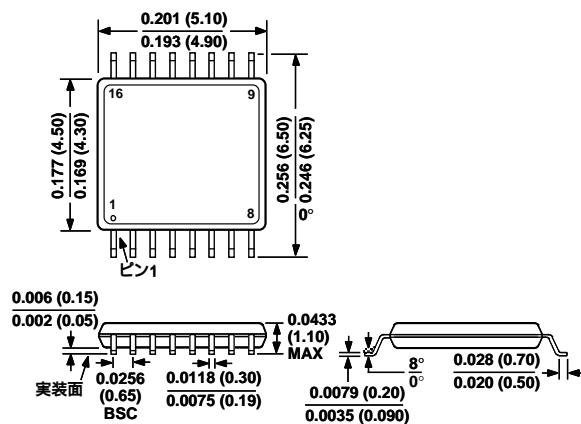

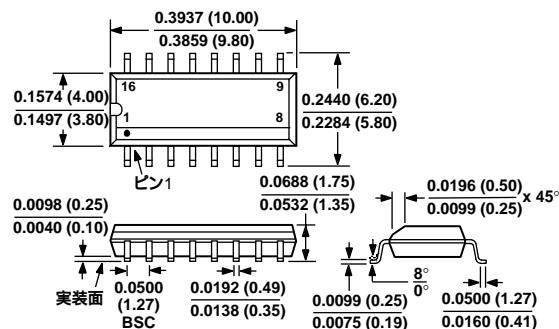

## 外形寸法

サイズはインチと (mm) で示します。

### 16 ピン・スマート・アウトライン (SOIC) (R-16 A)

### 16 ピン薄型シールド・スマート・アウトライン (TSSOP) (RU-16)