# 真のレール to レール・バッファ 内蔵 24 ビット、8/16 チャンネル 250 kSPS、Σ-Δ ADC

## データシート

**AD7175-8**

### 特長

高速かつ柔軟な出力レート: 5 SPS ~ 250 kSPS

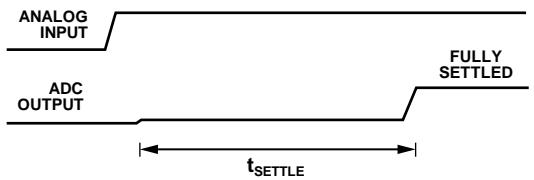

チャンネル・スキヤン・データ・レート: 50 kSPS / チャンネル (セトリング時間 20 $\mu$ s)

性能仕様

ノイズ・フリー・ビット数: 250 kSPS で 17.2 ビット

ノイズ・フリー・ビット数: 2.5 kSPS で 20.2 ビット

ノイズ・フリー・ビット数: 20 SPS で 24 ビット

INL: FSR の ±1 ppm

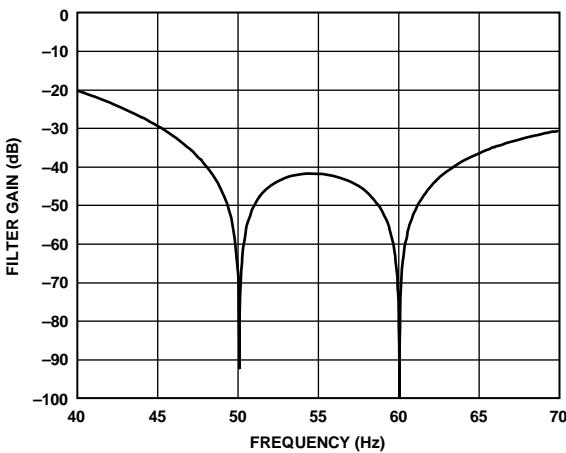

50 Hz と 60 Hz のフィルタ除去比: 50 ms セトリングで 85 dB

入力チャンネルをユーザーが設定可能

完全差動の 8 チャンネルまたはシングルエンドの 16 チャンネル

クロスポイント・マルチプレクサ

2.5 V のリファレンスを内蔵 (ドリフト ±2 ppm/°C)

真のレール to レールのアナログ入力バッファとリファレンス入力バッファ

内部または外部クロック

電源電圧: AVDD1 - AVSS = 5 V, AVDD2 = IOVDD = 2V ~ 5V (公称値)

AVDD1/AVSS を ±2.5 V とする両電源も可能

ADC 消費電流: 8.4 mA

温度範囲: -40°C ~ +105°C

3 線式または 4 線式のシリアル・デジタル・インターフェース (シユミット・トリガ付き SCLK)

シリアル・ポート・インターフェース (SPI)、QSPI、MICROWIRE、DSP 互換

### アプリケーション

プロセス・コントロール: PLC/DCS モジュール

温度計測および圧力計測

医療や科学分野向けマルチチャネル計測機器

クロマトグラフィー

### 概要

AD7175-8 は、低ノイズ、高速セトリングのマルチプレクス型 8/16 チャンネル (完全差動/擬似差動) Σ-Δ A/D コンバータ (ADC) で、低い帯域の入力信号を対象としています。データが完全に安定する最大チャンネル・スキヤン・レートは 50 kSPS (20  $\mu$ s) です。出力データ・レートは 5 SPS ~ 250 kSPS の範囲です。

AD7175-8 はアナログおよびデジタルの主要な信号処理ブロックを内蔵しており、使用する各アナログ入力チャンネルの構成をユーザーが個別に設定することができます。各機能はユーザーがチャンネルごとに選択できます。アナログ入力と外部リファレンス入力に内蔵されている真のレール to レール・バッファにより、容易に駆動できる高インピーダンス入力が与えられています。高精度、低ドリフト (2 ppm/°C) の 2.5 V 内部バンドギャップ・リファレンス (出力リファレンス・バッファ付き) によって組み込み機能が強化されているため、外付け部品数を減らすことができます。

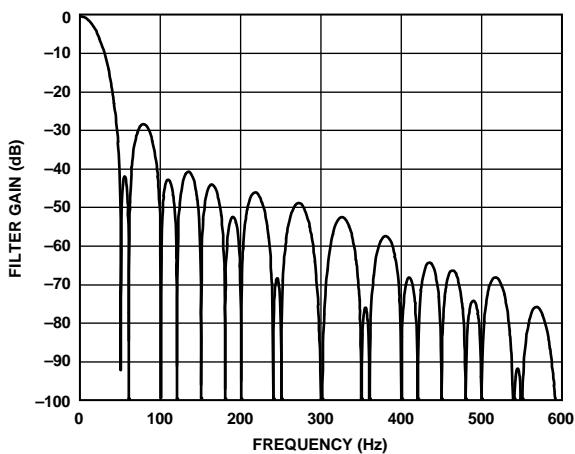

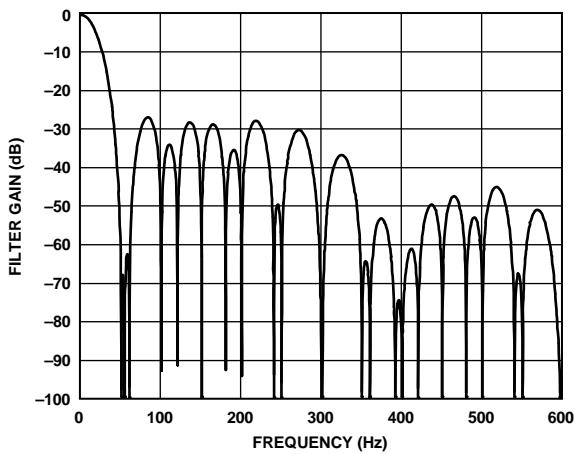

デジタル・フィルタにより、27.27 SPS の出力データ・レートで 50 Hz と 60 Hz の同時除去が可能です。アプリケーションの各チャンネルの要求に合わせて、フィルタ・オプションを切り替えることができます。ADC は選択された各チャンネルを自動的に順に切り替えていきます。さらに、デジタル処理機能にはチャンネルごとに設定可能なオフセット調整レジスタとゲイン調整レジスタがあります。

このデバイスは AVDD1 - AVSS = 5 V の単電源あるいは AVDD1/AVSS = ±2.5 V の両電源で動作します。また、AVDD2 と IOVDD の公称電源電圧範囲は 2 V ~ 5 V です。規定動作温度範囲は -40°C ~ +105°C です。AD7175-8 は 40 ピン LFCSP パッケージを採用しています。

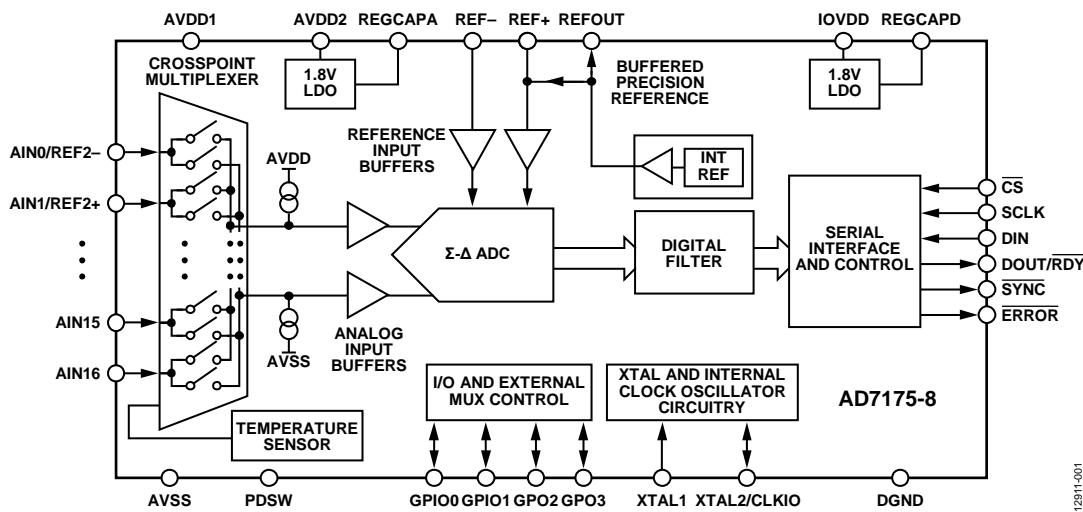

### 機能ブロック図

図 1

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                                |    |

|--------------------------------|----|

| 特長                             | 1  |

| アプリケーション                       | 1  |

| 概要                             | 1  |

| 機能ブロック図                        | 1  |

| 改訂履歴                           | 2  |

| 仕様                             | 3  |

| タイミング特性                        | 6  |

| 絶対最大定格                         | 8  |

| 熱抵抗                            | 8  |

| ESD に関する注意                     | 8  |

| ピン配置およびピン機能説明                  | 9  |

| 代表的な性能特性                       | 11 |

| ノイズ性能と分解能                      | 17 |

| 評価開始にあたって                      | 18 |

| 電源                             | 19 |

| デジタル・コミュニケーション                 | 19 |

| AD7175-8 のリセット                 | 20 |

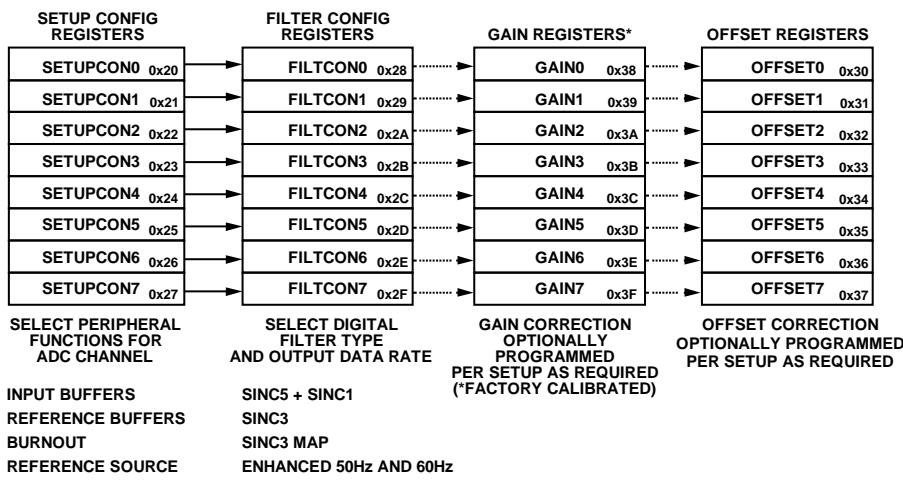

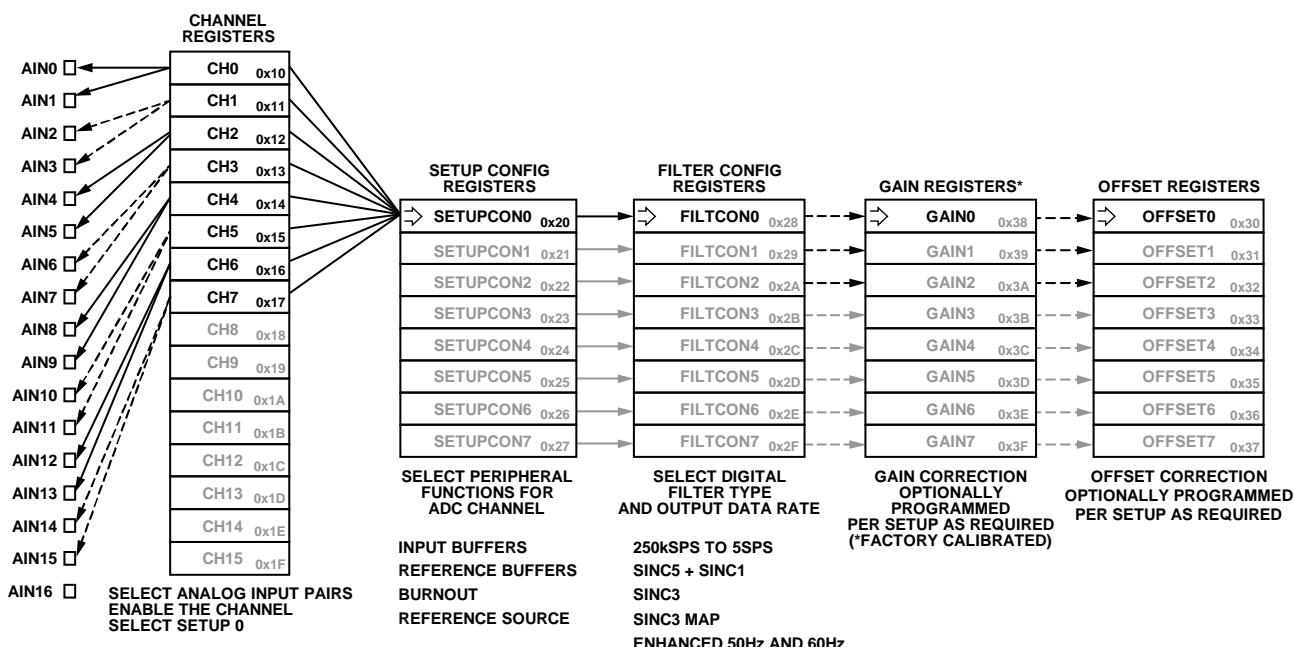

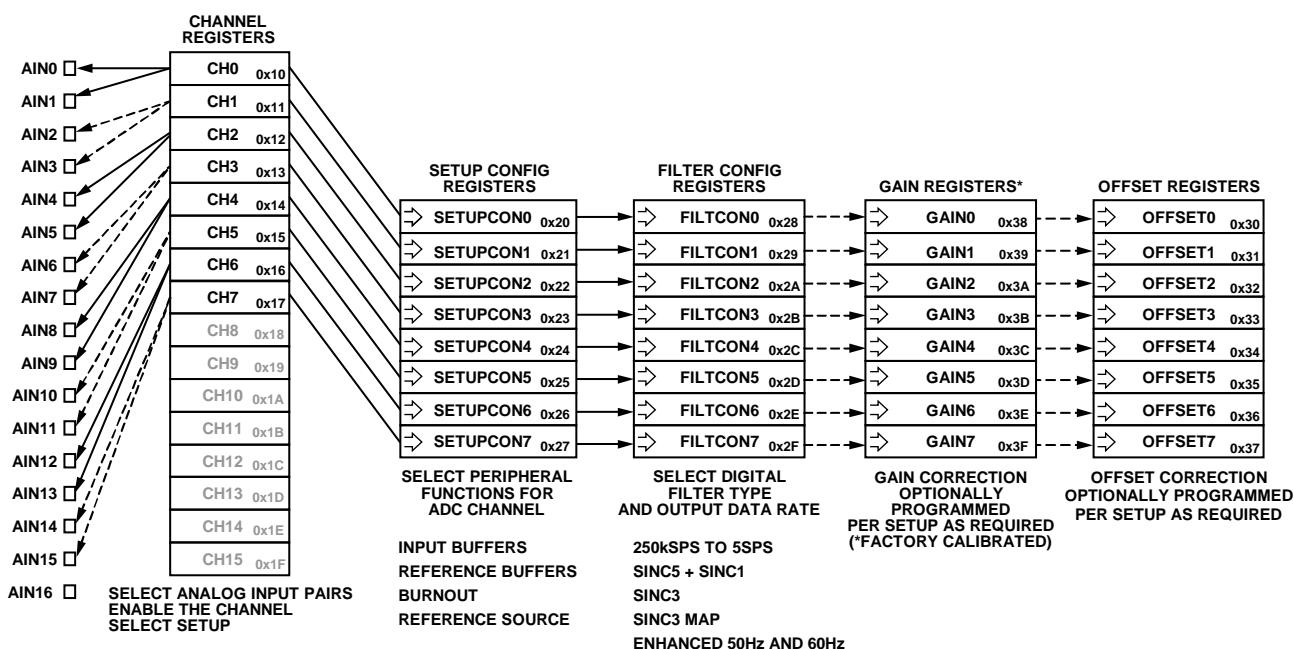

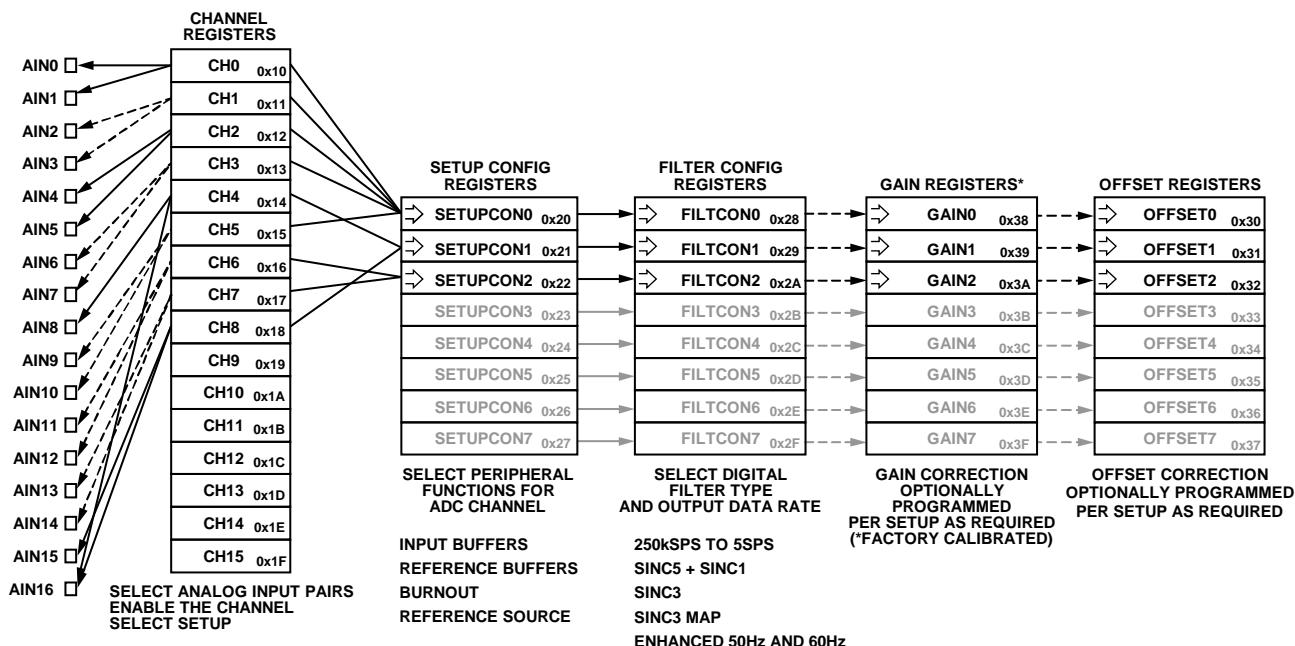

| 設定の概要                          | 20 |

| 回路説明                           | 25 |

| バッファ付きアナログ入力                   | 25 |

| クロスポイント・マルチプレクサ                | 25 |

| AD7175-8 のリファレンス               | 26 |

| バッファ付きリファレンス入力                 | 27 |

| クロック源                          | 27 |

| デジタル・フィルタ                      | 28 |

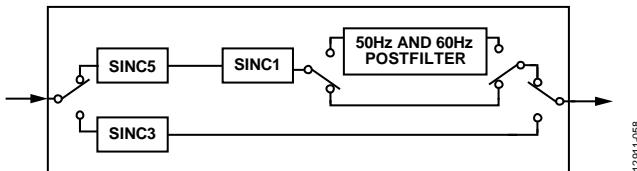

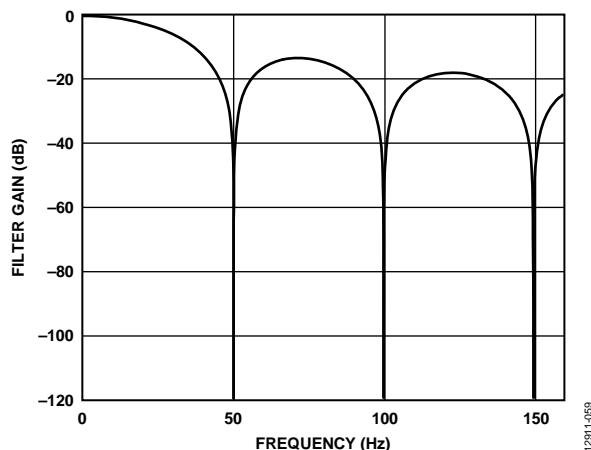

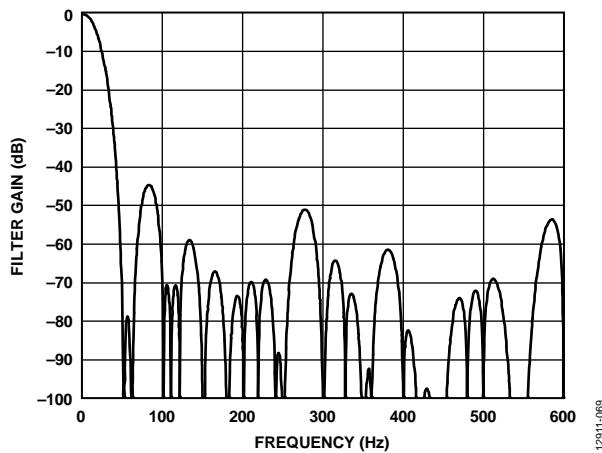

| sinc5 + sinc1 フィルタ             | 28 |

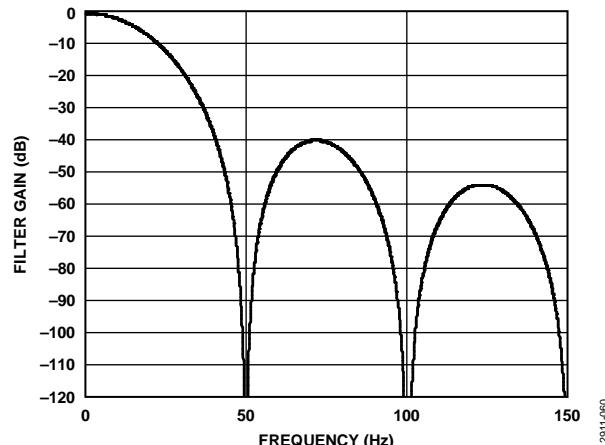

| sinc3 フィルタ                     | 28 |

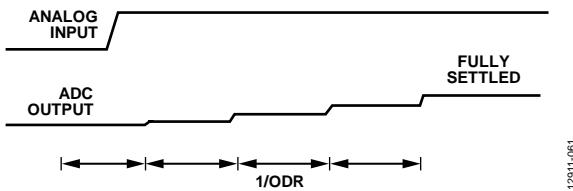

| シングル・サイクル・セトリング                | 29 |

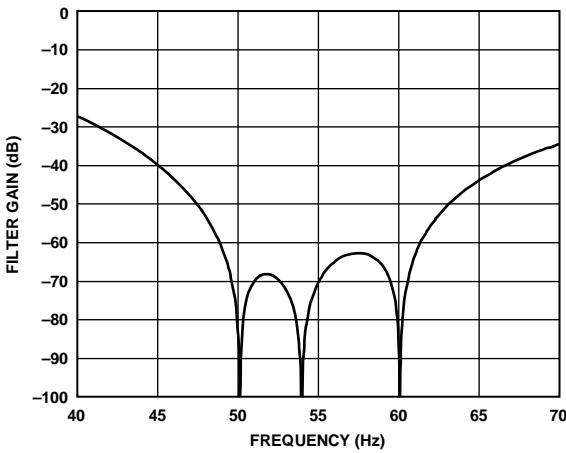

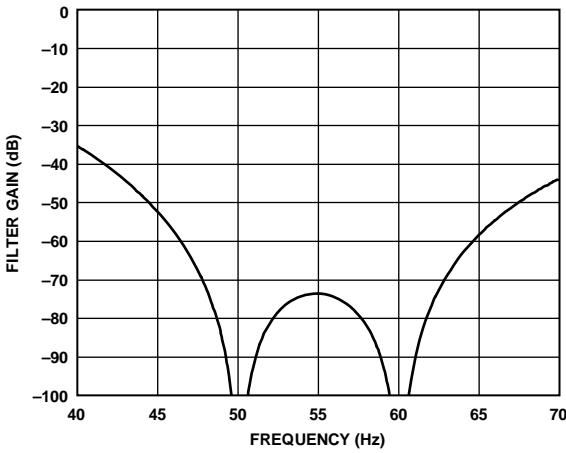

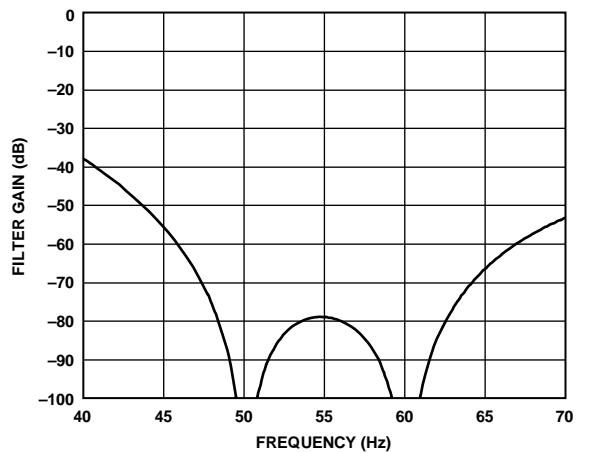

| 50 Hz と 60 Hz を除去するエンハンスド・フィルタ | 33 |

| 動作モード                          | 36 |

| 連続変換モード                        | 36 |

| 連続読み出しモード                      | 37 |

| シングル変換モード                      | 38 |

| スタンバイ・モードとパワーダウン・モード           | 39 |

| キャリブレーション                      | 39 |

| デジタル・インターフェース                  | 40 |

| チェックサム保護                       | 40 |

|                                 |    |

|---------------------------------|----|

| CRC の計算                         | 41 |

| 内蔵機能                            | 43 |

| 汎用 I/O                          | 43 |

| 外部マルチプレクサの制御                    | 43 |

| 遅延                              | 43 |

| 16 ビット / 24 ビット変換               | 43 |

| DOUT_RESET                      | 43 |

| 同期                              | 43 |

| エラー・フラグ                         | 44 |

| DATA_STAT                       | 44 |

| IOSTRENGTH                      | 44 |

| パワーダウン・スイッチ                     | 45 |

| 内部温度センサー                        | 45 |

| グラウンドィングとレイアウト                  | 46 |

| レジスタの一覧                         | 47 |

| レジスタの詳細                         | 49 |

| コミュニケーション・レジスタ                  | 49 |

| ステータス・レジスタ                      | 51 |

| ADC モード・レジスタ                    | 52 |

| インターフェース・モード・レジスタ               | 53 |

| レジスタ・チェック                       | 54 |

| データ・レジスタ                        | 54 |

| GPIO 設定レジスタ                     | 55 |

| ID レジスタ                         | 56 |

| チャンネル・レジスタ 0                    | 56 |

| チャンネル・レジスタ 1 ~ チャンネル・レジスタ 15    | 58 |

| セットアップ設定レジスタ 0                  | 59 |

| セットアップ設定レジスタ 1 ~ セットアップ設定レジスタ 7 | 60 |

| フィルタ設定レジスタ 0                    | 61 |

| フィルタ設定レジスタ 1 ~ フィルタ設定レジスタ 7     | 62 |

| オフセット・レジスタ 0                    | 62 |

| オフセット・レジスタ 1 ~ オフセット・レジスタ 7     | 62 |

| ゲイン・レジスタ 0                      | 62 |

| ゲイン・レジスタ 1 ~ ゲイン・レジスタ 7         | 63 |

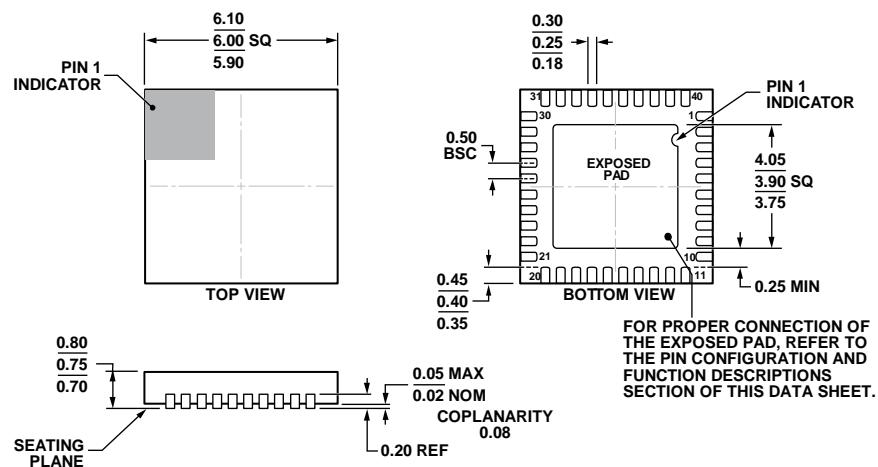

| 外形寸法                            | 64 |

| オーダー・ガイド                        | 64 |

## 改訂履歴

10/15—Revision 0: Initial Version

## 仕様

特に指定のない限り、AVDD1 = 4.5 V ~ 5.5 V、AVDD2 = 2 V ~ 5.5 V、IOVDD = 2 V ~ 5.5 V、AVSS = DGND = 0 V、REF+ = 2.5 V、REF- = AVSS、内部マスター・クロック (MCLK) = 16 MHz、TA = TMIN ~ TMAX (-40°C ~ +105°C)。

表 1.

| Parameter                                 | Test Conditions/Comments                                                                                                    | Min         | Typ                  | Max             | Unit                                |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|-----------------|-------------------------------------|

| ADC SPEED AND PERFORMANCE                 |                                                                                                                             |             |                      |                 |                                     |

| Output Data Rate (ODR)                    |                                                                                                                             | 5           |                      | 250,000         | SPS                                 |

| No Missing Codes <sup>1</sup>             | Excluding sinc3 filter $\geq$ 125 kSPS                                                                                      | 24          |                      |                 | Bits                                |

| Resolution                                | See Table 19 to Table 23                                                                                                    |             |                      |                 |                                     |

| Noise                                     | See Table 19 to Table 23                                                                                                    |             |                      |                 |                                     |

| ACCURACY                                  |                                                                                                                             |             |                      |                 |                                     |

| Integral Nonlinearity (INL)               | All input buffers enabled<br>All input buffers disabled                                                                     |             | $\pm 4.5$<br>$\pm 1$ | 10<br>$\pm 4.5$ | ppm of FSR<br>ppm of FSR            |

| Offset Error <sup>2</sup>                 | Internal short                                                                                                              |             | $\pm 60$             |                 | $\mu\text{V}$                       |

| Offset Drift                              | Internal short                                                                                                              |             | $\pm 150$            |                 | $\text{nV}/^\circ\text{C}$          |

| Gain Error <sup>2</sup>                   |                                                                                                                             |             | $\pm 80$             | $\pm 110$       | ppm of FSR                          |

| Gain Drift <sup>1</sup>                   |                                                                                                                             |             | $\pm 0.5$            | $\pm 0.75$      | $\text{ppm}/^\circ\text{C}$         |

| REJECTION                                 |                                                                                                                             |             |                      |                 |                                     |

| Power Supply Rejection                    | AVDD1, AVDD2, for V <sub>IN</sub> = 1 V                                                                                     |             | 90                   |                 | dB                                  |

| Common-Mode Rejection                     | V <sub>IN</sub> = 0.1 V                                                                                                     |             |                      |                 |                                     |

| At DC                                     |                                                                                                                             | 95          |                      |                 | dB                                  |

| At 50 Hz, 60 Hz <sup>1</sup>              | 20 Hz output data rate (post filter), 50 Hz $\pm$ 1 Hz and 60 Hz $\pm$ 1 Hz                                                 | 120         |                      |                 | dB                                  |

| Normal Mode Rejection <sup>1</sup>        | 50 Hz $\pm$ 1 Hz and 60 Hz $\pm$ 1 Hz<br>Internal clock, 20 SPS ODR (postfilter)<br>External clock, 20 SPS ODR (postfilter) | 71<br>85    | 90<br>90             |                 | dB<br>dB                            |

| ANALOG INPUTS                             |                                                                                                                             |             |                      |                 |                                     |

| Differential Input Range                  | V <sub>REF</sub> = (REF+) - (REF-)                                                                                          |             | $\pm V_{\text{REF}}$ |                 | V                                   |

| Absolute Voltage Limits <sup>1</sup>      |                                                                                                                             |             |                      |                 |                                     |

| Input Buffers Disabled                    |                                                                                                                             | AVSS - 0.05 |                      | AVDD1 + 0.05    | V                                   |

| Input Buffers Enabled                     |                                                                                                                             | AVSS        |                      | AVDD1           | V                                   |

| Analog Input Current                      |                                                                                                                             |             |                      |                 |                                     |

| Input Buffers Disabled                    |                                                                                                                             |             | $\pm 48$             |                 | $\mu\text{A}/\text{V}$              |

| Input Current                             |                                                                                                                             |             | $\pm 0.75$           |                 | $\text{nA}/\text{V}/^\circ\text{C}$ |

| Input Current Drift                       | External clock<br>Internal clock                                                                                            |             | $\pm 4$              |                 | $\text{nA}/\text{V}/^\circ\text{C}$ |

| Input Buffers Enabled                     |                                                                                                                             |             | $\pm 30$             |                 | nA                                  |

| Input Current                             | AVDD1 - 0.2 V to AVSS + 0.2 V                                                                                               |             | $\pm 75$             |                 | pA/ $^\circ\text{C}$                |

| Input Current Drift                       | AVDD1 to AVSS                                                                                                               |             | $\pm 1$              |                 | nA/ $^\circ\text{C}$                |

| Crosstalk                                 | 1 kHz input                                                                                                                 |             | -120                 |                 | dB                                  |

| INTERNAL REFERENCE                        | 100 nF external capacitor to AVSS                                                                                           |             |                      |                 |                                     |

| Output Voltage                            | REFOUT, with respect to AVSS                                                                                                |             | 2.5                  |                 | V                                   |

| Initial Accuracy <sup>3</sup>             | REFOUT, TA = 25°C                                                                                                           | -0.12       |                      | +0.12           | % of V                              |

| Temperature Coefficient <sup>1</sup>      |                                                                                                                             |             |                      |                 |                                     |

| 0°C to 105°C                              |                                                                                                                             |             | $\pm 2$              | $\pm 5$         | ppm/ $^\circ\text{C}$               |

| -40°C to +105°C                           |                                                                                                                             |             | $\pm 3$              | $\pm 10$        | ppm/ $^\circ\text{C}$               |

| Reference Load Current, I <sub>LOAD</sub> | AVDD1, AVDD2 (line regulation)                                                                                              | -10         |                      | +10             | mA                                  |

| Power Supply Rejection                    | $\Delta V_{\text{OUT}}/\Delta I_{\text{LOAD}}$                                                                              |             | 95                   |                 | dB                                  |

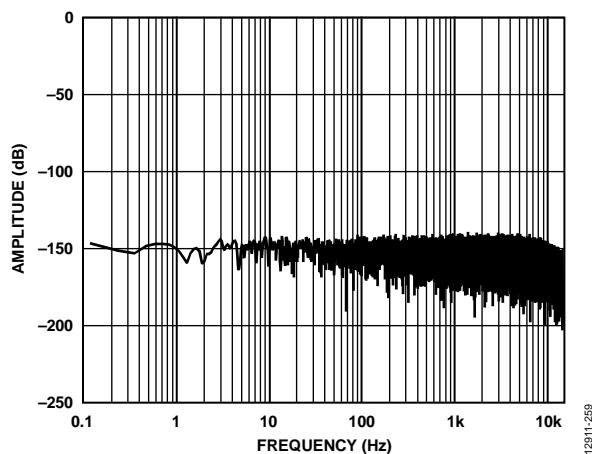

| Load Regulation                           | e <sub>N</sub> , 0.1 Hz to 10 Hz, 2.5 V reference                                                                           |             | 32                   |                 | ppm/mA                              |

| Voltage Noise                             | e <sub>N</sub> , 1 kHz, 2.5 V reference                                                                                     |             | 4.5                  |                 | $\mu\text{V rms}$                   |

| Voltage Noise Density                     |                                                                                                                             |             | 215                  |                 | nV/ $\sqrt{\text{Hz}}$              |

| Parameter                                                 | Test Conditions/Comments             | Min         | Typ  | Max          | Unit    |

|-----------------------------------------------------------|--------------------------------------|-------------|------|--------------|---------|

| Turn-On Settling Time                                     | 100 nF REFOUT capacitor              |             | 200  |              | μs      |

| Short-Circuit Current, $I_{SC}$                           |                                      |             | 25   |              | mA      |

| EXTERNAL REFERENCE INPUTS                                 |                                      |             |      |              |         |

| Differential Input Range                                  | $V_{REF} = (REF+) - (REF-)$          | 1           | 2.5  | AVDD1        | V       |

| Absolute Voltage Limits <sup>1</sup>                      |                                      | AVSS - 0.05 |      | AVDD1 + 0.05 | V       |

| Input Buffers Disabled                                    |                                      | AVSS        |      | AVDD1        | V       |

| Input Buffers Enabled                                     |                                      |             |      |              | V       |

| REF+/REF- Input Current                                   |                                      |             |      |              |         |

| Input Buffers Disabled                                    |                                      |             |      |              |         |

| Input Current                                             |                                      |             | ±72  |              | μA/V    |

| Input Current Drift                                       | External clock<br>Internal clock     |             | ±1.2 |              | nA/V/°C |

|                                                           |                                      |             | ±6   |              | nA/V/°C |

| Input Buffers Enabled                                     |                                      |             | ±800 |              | nA      |

| Input Current                                             |                                      |             | 1.2  |              | nA      |

| Input Current Drift                                       |                                      |             |      |              | nA/°C   |

| Normal Mode Rejection <sup>1</sup>                        | See the Rejection parameter          |             | 95   |              | dB      |

| Common-Mode Rejection                                     |                                      |             |      |              |         |

| TEMPERATURE SENSOR                                        |                                      |             |      |              |         |

| Accuracy                                                  | After user calibration at 25°C       |             | ±2   |              | °C      |

| Sensitivity                                               |                                      |             | 470  |              | μV/K    |

| BURNOUT CURRENTS                                          |                                      |             |      |              |         |

| Source/Sink Current                                       | Analog input buffers must be enabled |             | ±10  |              | μA      |

| POWER-DOWN SWITCH                                         |                                      |             |      |              |         |

| $R_{ON}$                                                  |                                      | 24          |      |              | Ω       |

| Allowable Currents                                        |                                      |             | 16   |              | mA      |

| GENERAL-PURPOSE INPUTS/OUTPUTS (GPIO0, GPIO1, GPO2, GPO3) | With respect to AVSS                 |             |      |              |         |

| Input Mode Leakage Current <sup>1</sup>                   |                                      | -10         |      | +10          | μA      |

| Floating State Output Capacitance                         |                                      |             | 5    |              | pF      |

| Output High Voltage, $V_{OH}^1$                           | $I_{SOURCE} = 200 \mu A$             | AVSS + 4    |      |              | V       |

| Output Low Voltage, $V_{OL}^1$                            | $I_{SINK} = 800 \mu A$               |             |      | AVSS + 0.4   | V       |

| Input High Voltage, $V_{INH}^1$                           |                                      | AVSS + 3    |      |              | V       |

| Input Low Voltage, $V_{INL}^1$                            |                                      |             |      | AVSS + 0.7   | V       |

| CLOCK                                                     |                                      |             |      |              |         |

| Internal Clock                                            |                                      |             |      |              |         |

| Frequency                                                 |                                      | 16          |      |              | MHz     |

| Accuracy                                                  |                                      | -2.5%       |      | +2.5%        | %       |

| Duty Cycle                                                |                                      | 50          |      |              | %       |

| Output Low Voltage, $V_{OL}$                              |                                      |             |      | 0.4          | V       |

| Output High Voltage, $V_{OH}$                             |                                      | 0.8 × IOVDD |      |              | V       |

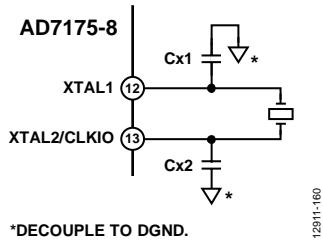

| Crystal                                                   |                                      |             |      |              |         |

| Frequency                                                 |                                      | 14          | 16   | 16.384       | MHz     |

| Start-Up Time                                             |                                      |             | 10   |              | μs      |

| External Clock (CLKIO)                                    |                                      |             | 16   | 16.384       | MHz     |

| Duty Cycle <sup>1</sup>                                   |                                      | 30          | 50   | 70           | %       |

| Parameter                                | Test Conditions/Comments                                                                                                                                                                   | Min                 | Typ      | Max                        | Unit          |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|----------------------------|---------------|

| <b>LOGIC INPUTS</b>                      |                                                                                                                                                                                            |                     |          |                            |               |

| Input High Voltage, $V_{INH}^1$          | $2 \text{ V} \leq IOVDD < 2.3 \text{ V}$                                                                                                                                                   | $0.65 \times IOVDD$ |          |                            | V             |

| Input Low Voltage, $V_{INL}^1$           | $2.3 \text{ V} \leq IOVDD \leq 5.5 \text{ V}$<br>$2 \text{ V} \leq IOVDD < 2.3 \text{ V}$<br>$2.3 \text{ V} \leq IOVDD \leq 5.5 \text{ V}$                                                 | $0.7 \times IOVDD$  |          | $0.35 \times IOVDD$<br>0.7 | V<br>V        |

| Hysteresis <sup>1</sup>                  | $IOVDD \geq 2.7 \text{ V}$<br>$IOVDD < 2.7 \text{ V}$                                                                                                                                      | 0.08                | 0.25     | 0.2                        | V             |

| Leakage Current                          |                                                                                                                                                                                            | 0.04                |          | +10                        | $\mu\text{A}$ |

| <b>LOGIC OUTPUT (DOUT/RDY)</b>           |                                                                                                                                                                                            |                     |          |                            |               |

| Output High Voltage, $V_{OH}^1$          | $IOVDD \geq 4.5 \text{ V}, I_{SOURCE} = 1 \text{ mA}$<br>$2.7 \text{ V} \leq IOVDD < 4.5 \text{ V}, I_{SOURCE} = 500 \mu\text{A}$<br>$IOVDD < 2.7 \text{ V}, I_{SOURCE} = 200 \mu\text{A}$ | $0.8 \times IOVDD$  |          |                            | V             |

| Output Low Voltage, $V_{OL}^1$           | $IOVDD \geq 4.5 \text{ V}, I_{SINK} = 2 \text{ mA}$<br>$2.7 \text{ V} \leq IOVDD < 4.5 \text{ V}, I_{SINK} = 1 \text{ mA}$<br>$IOVDD < 2.7 \text{ V}, I_{SINK} = 400 \mu\text{A}$          | $0.8 \times IOVDD$  | 0.4      | 0.4                        | V             |

| Leakage Current                          | Floating state                                                                                                                                                                             | -10                 |          | +10                        | $\mu\text{A}$ |

| Output Capacitance                       | Floating state                                                                                                                                                                             |                     | 10       |                            | pF            |

| <b>SYSTEM CALIBRATION<sup>1</sup></b>    |                                                                                                                                                                                            |                     |          |                            |               |

| Full-Scale (FS) Calibration Limit        |                                                                                                                                                                                            |                     |          | $1.05 \times FS$           | V             |

| Zero-Scale Calibration Limit             |                                                                                                                                                                                            |                     |          | $-1.05 \times FS$          | V             |

| Input Span                               |                                                                                                                                                                                            |                     |          | $0.8 \times FS$            | V             |

| <b>POWER REQUIREMENTS</b>                |                                                                                                                                                                                            |                     |          |                            |               |

| Power Supply Voltage                     |                                                                                                                                                                                            |                     |          |                            |               |

| AVDD1 to AVSS                            |                                                                                                                                                                                            | 4.5                 | 5        | 5.5                        | V             |

| AVDD2 to AVSS <sup>4</sup>               |                                                                                                                                                                                            | 2                   | 2.5 to 5 | 5.5                        | V             |

| AVSS to DGND                             |                                                                                                                                                                                            | -2.75               |          | 0                          | V             |

| IOVDD to DGND <sup>4</sup>               |                                                                                                                                                                                            | 2                   | 2.5 to 5 | 5.5                        | V             |

| IOVDD to AVSS                            | For $AVSS < DGND$                                                                                                                                                                          |                     |          | 6.35                       | V             |

| <b>POWER SUPPLY CURRENTS<sup>5</sup></b> | All outputs unloaded, digital inputs connected to IOVDD or DGND                                                                                                                            |                     |          |                            |               |

| Full Operating Mode                      |                                                                                                                                                                                            |                     |          |                            |               |

| AVDD1 Current                            | Analog input and reference input buffers ( $A_{IN\pm}$ , $REF\pm$ ) disabled, external reference                                                                                           |                     | 1.4      | 1.65                       | mA            |

|                                          | Analog input and reference input buffers disabled, internal reference                                                                                                                      |                     | 1.75     | 2                          | mA            |

|                                          | Analog input and reference input buffers enabled, external reference                                                                                                                       |                     | 13       | 16                         | mA            |

| AVDD2 Current                            | Each buffer: $A_{IN+}$ , $A_{IN-}$ , $REF+$ , $REF-$                                                                                                                                       |                     | 2.9      |                            | mA            |

|                                          | External reference                                                                                                                                                                         |                     | 4.5      | 5                          | mA            |

|                                          | Internal reference                                                                                                                                                                         |                     | 4.75     | 5.2                        | mA            |

| IOVDD Current                            | External clock                                                                                                                                                                             |                     | 2.5      | 2.8                        | mA            |

|                                          | Internal clock                                                                                                                                                                             |                     | 2.75     | 3.1                        | mA            |

|                                          | External crystal                                                                                                                                                                           |                     | 3        |                            | mA            |

| Standby Mode (LDO On)                    | Internal reference off, total current consumption                                                                                                                                          |                     | 30       |                            | $\mu\text{A}$ |

|                                          | Internal reference on, total current consumption                                                                                                                                           |                     | 425      |                            | $\mu\text{A}$ |

| Power-Down Mode                          | Full power-down (including LDO and internal reference)                                                                                                                                     |                     | 5        | 10                         | $\mu\text{A}$ |

| Parameter                      | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                              | Min                                | Typ | Max | Unit                             |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----|-----|----------------------------------|

| POWER DISSIPATION <sup>5</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                    |     |     |                                  |

| Full Operating Mode            | All buffers disabled, external clock and reference, AVDD2 = 2 V, IOVDD = 2 V<br>All buffers disabled, external clock and reference, all supplies = 5 V<br>All buffers disabled, external clock and reference, all supplies = 5.5 V<br>All buffers enabled, internal clock and reference, AVDD2 = 2 V, IOVDD = 2 V<br>All buffers enabled, internal clock and reference, all supplies = 5 V<br>All buffers enabled, internal clock and reference, all supplies = 5.5 V | 21<br>42<br>52<br>82<br>105<br>136 |     |     | mW<br>mW<br>mW<br>mW<br>mW<br>mW |

| Standby Mode                   | Internal reference off, all supplies = 5 V<br>Internal reference on, all supplies = 5 V                                                                                                                                                                                                                                                                                                                                                                               | 150<br>2.2                         |     |     | μW<br>mW                         |

| Power-Down Mode                | Full power-down, all supplies = 5 V                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25                                 | 50  |     | μW                               |

<sup>1</sup>これらの仕様については出荷テストを行っていませんが、量産開始時の特性評価データにより保証しています。

<sup>2</sup>システムもしくは内蔵ゼロスケールのキャリブレーション手順に従えば、オフセット誤差は、プログラムされた出力データ・レートのノイズ・レベルとほぼ同等になります。システム・フルスケール・キャリブレーションは、ゲイン誤差をプログラムされた出力データ・レートのノイズ・レベルと同等レベルにまで減少させることができます。

<sup>3</sup>この仕様には、MSL (Moisture Level) プリコンディショニングの影響が含まれています。

<sup>4</sup>公称範囲は 2 V ~ 5 V です。

<sup>5</sup>これらは、REFOUT ピンと、デジタル出力ピンに負荷が接続されていないときの仕様です。

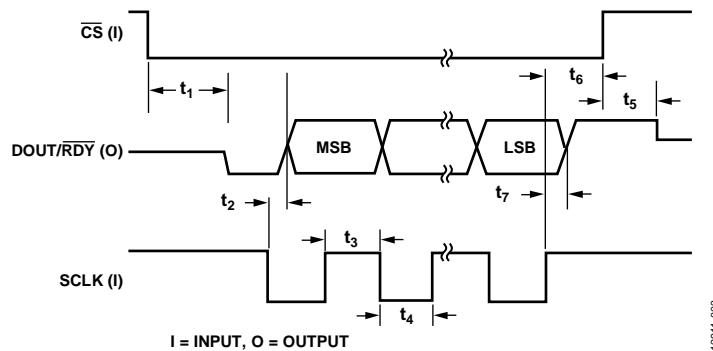

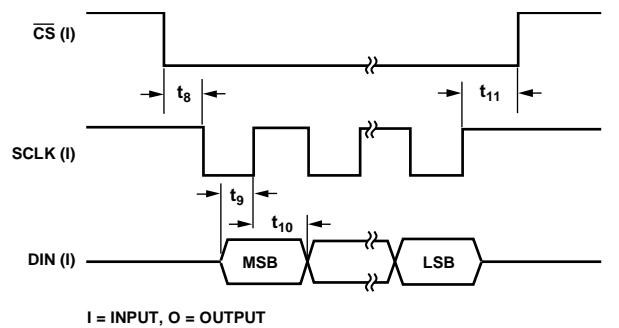

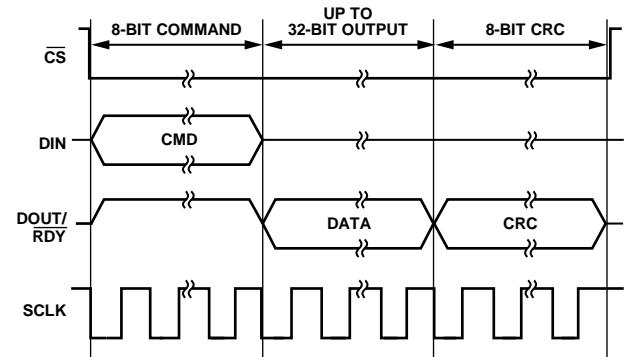

## タイミング特性

特に指定のない限り、IOVDD = 2 V ~ 5.5 V、DGND = 0 V、入力ロジック 0 = 0 V、入力ロジック 1 = IOVDD、C<sub>LOAD</sub> = 20 pF。

表 2.

| Parameter                   | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit                       | Description <sup>1, 2</sup>                                                                          |

|-----------------------------|----------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------|

| SCLK                        |                                              |                            |                                                                                                      |

| t <sub>3</sub>              | 25                                           | ns min                     | SCLK high pulse width                                                                                |

| t <sub>4</sub>              | 25                                           | ns min                     | SCLK low pulse width                                                                                 |

| READ OPERATION              |                                              |                            |                                                                                                      |

| t <sub>1</sub>              | 0<br>15<br>40                                | ns min<br>ns max<br>ns max | CS falling edge to DOUT/RDY active time<br>IOVDD = 4.75 V to 5.5 V<br>IOVDD = 2 V to 3.6 V           |

| t <sub>2</sub> <sup>3</sup> | 0<br>12.5<br>25                              | ns min<br>ns max<br>ns max | SCLK active edge to data valid delay <sup>4</sup><br>IOVDD = 4.75 V to 5.5 V<br>IOVDD = 2 V to 3.6 V |

| t <sub>5</sub> <sup>5</sup> | 2.5<br>20                                    | ns min<br>ns max           | Bus relinquish time after CS inactive edge                                                           |

| t <sub>6</sub>              | 0                                            | ns min                     | SCLK inactive edge to CS inactive edge                                                               |

| t <sub>7</sub>              | 10                                           | ns min                     | SCLK inactive edge to DOUT/RDY high/low                                                              |

| WRITE OPERATION             |                                              |                            |                                                                                                      |

| t <sub>8</sub>              | 0                                            | ns min                     | CS falling edge to SCLK active edge setup time <sup>4</sup>                                          |

| t <sub>9</sub>              | 8                                            | ns min                     | Data valid to SCLK edge setup time                                                                   |

| t <sub>10</sub>             | 8                                            | ns min                     | Data valid to SCLK edge hold time                                                                    |

| t <sub>11</sub>             | 5                                            | ns min                     | CS rising edge to SCLK edge hold time                                                                |

<sup>1</sup>初期リリース時にサンプル・テストにより適合性を保証。

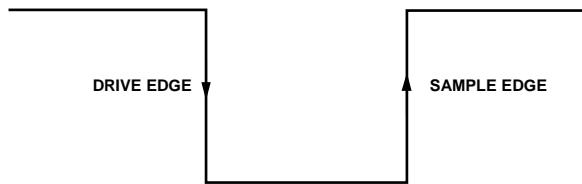

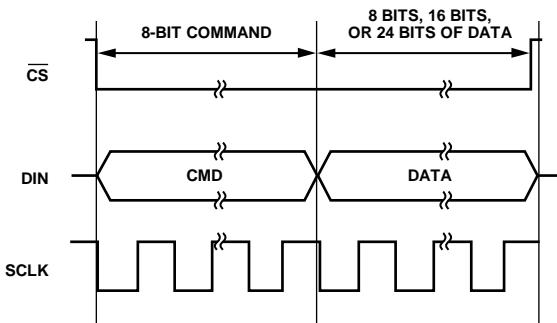

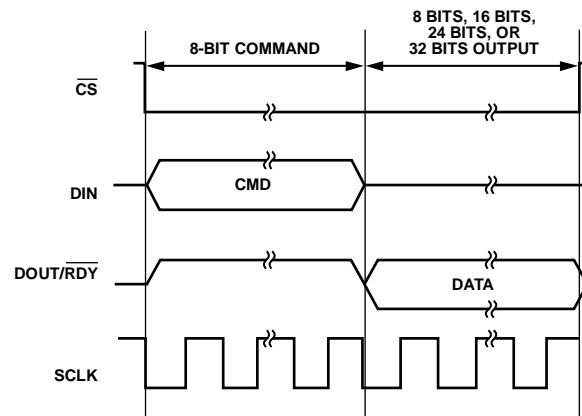

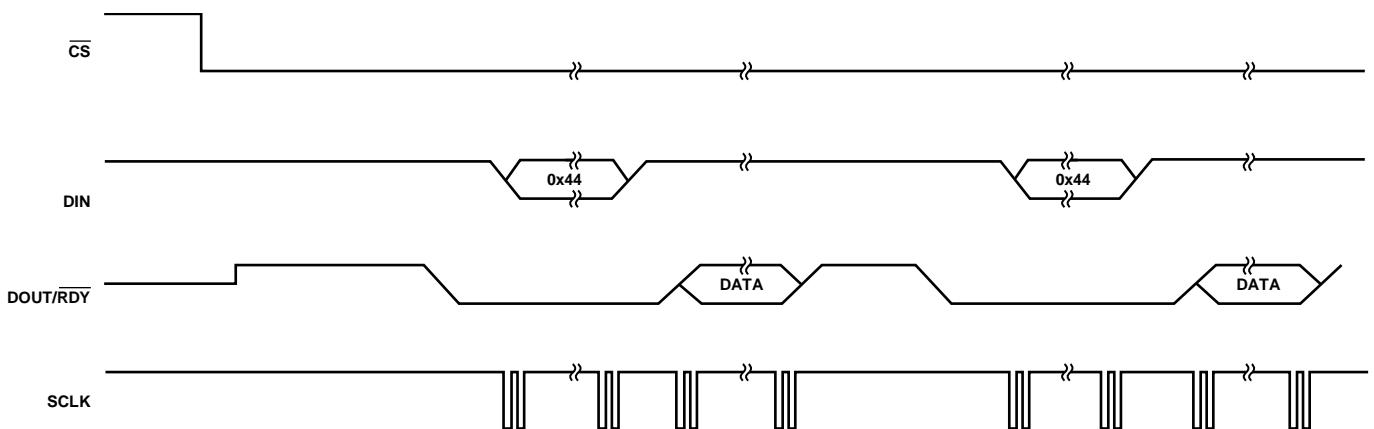

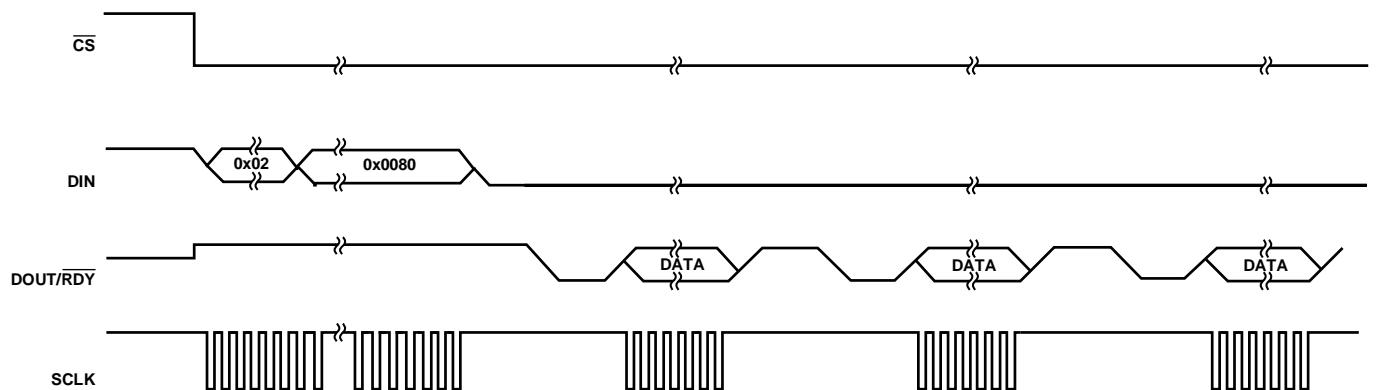

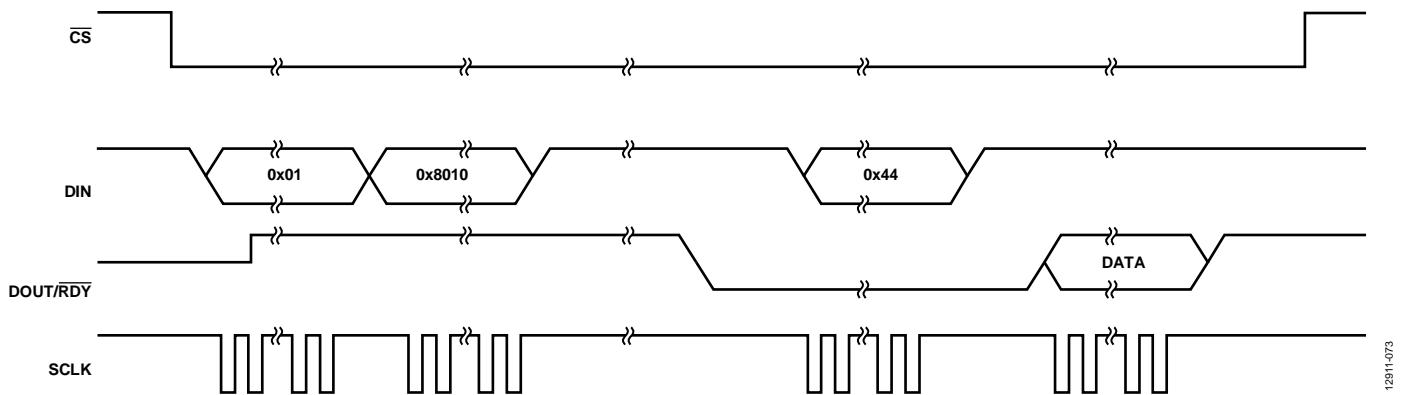

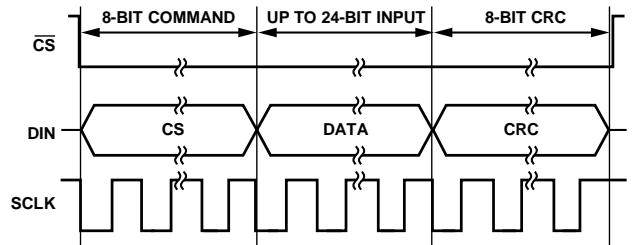

<sup>2</sup>図 2 と 図 3 を参照。

<sup>3</sup>このパラメータは、出力が V<sub>OL</sub> リミットもしくは V<sub>OH</sub> リミットを横切るために要する時間で定義されています。

<sup>4</sup>SCLK のアクティブ・エッジとは、SCLK の立下がりエッジを意味します。

<sup>5</sup>データ・レジスタを読み出した後、DOUT/RDY はハイ・レベルに戻ります。シングル変換モードおよび連続変換モードで、DOUT/RDY がハイ・レベルの間に、必要ならば、同一データを再度読み出すことができますが、2 回目以降の読み出しは次の出力更新が近いところで読み出さないように注意してください。連続読み出し機能がイネーブルされていると、デジタル・ワードは 1 回しか読み出すことができません。

## タイミング図

図 2. 読出しサイクルのタイミング図

12911-003

図 3. 書込みサイクルのタイミング図

12911-004

## 絶対最大定格

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

表 3.

| Parameter                          | Rating                  |

|------------------------------------|-------------------------|

| AVDD1, AVDD2 to AVSS               | -0.3 V to +6.5 V        |

| AVDD1 to DGND                      | -0.3 V to +6.5 V        |

| IOVDD to DGND                      | -0.3 V to +6.5 V        |

| IOVDD to AVSS                      | -0.3 V to +7.5 V        |

| AVSS to DGND                       | -3.25 V to +0.3 V       |

| Analog Input Voltage to AVSS       | -0.3 V to AVDD1 + 0.3 V |

| Reference Input Voltage to AVSS    | -0.3 V to AVDD1 + 0.3 V |

| Digital Input Voltage to DGND      | -0.3 V to IOVDD + 0.3 V |

| Digital Output Voltage to DGND     | -0.3 V to IOVDD + 0.3 V |

| Analog Input/Digital Input Current | 10 mA                   |

| Operating Temperature Range        | -40°C to +105°C         |

| Storage Temperature Range          | -65°C to +150°C         |

| Maximum Junction Temperature       | 150°C                   |

| Lead Soldering, Reflow Temperature | 260°C                   |

| ESD Rating (Human Body Model)      | 4 kV                    |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。製品を長時間絶対最大定格状態に置くと、製品の信頼性に影響を与えることがあります。

## 熱抵抗

$\theta_{JA}$  は、表面実装パッケージ用の JEDEC テスト・ボードにハンダ付けされたデバイスで仕様規定されています。

表 4. 热抵抗

| Package Type                             | $\theta_{JA}$ | Unit |

|------------------------------------------|---------------|------|

| 40-Lead, 6 mm × 6 mm LFCSP               | 114           | °C/W |

| 1-Layer JEDEC Board                      | 54            | °C/W |

| 4-Layer JEDEC Board                      | 34            | °C/W |

| 4-Layer JEDEC Board with 16 Thermal Vias |               |      |

## ESD に関する注意

### ESD (静電放電) の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

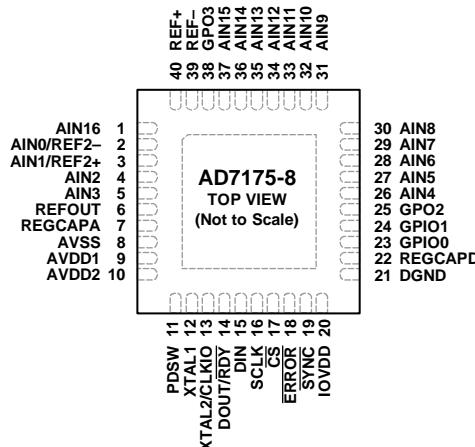

## ピン配置およびピン機能説明

12811-005

図 4. ピン配置

表 5. ピン機能の説明<sup>1</sup>

| Pin No. | Mnemonic    | Type <sup>2</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|-------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | AIN16       | AI                | アナログ入力 16。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2       | AIN0/REF2-  | AI                | アナログ入力 0 (AIN0) /リファレンス 2、負入力 (REF2-)。外部リファレンスは、REF2+ と REF2- の間に与えることができます。REF2- の範囲は AVSS ~ AVDD1 - 1 V です。アナログ入力 0 はクロスポイント・マルチプレクサを介して選択できます。リファレンス 2 は、セットアップ設定レジスタの REF_SELx ビットを介して選択できます。                                                                                                                                                                                                                                                                     |

| 3       | AIN1/REF2+  | AI                | アナログ入力 1 (AIN0) /リファレンス 2、正入力 (REF2+)。外部リファレンスは、REF2+ と REF2- の間に与えることができます。REF2+ の範囲は AVDD1 ~ AVSS + 1 V です。アナログ入力 1 はクロスポイント・マルチプレクサを介して選択できます。リファレンス 2 は、セットアップ設定レジスタの REF_SELx ビットを介して選択できます。                                                                                                                                                                                                                                                                     |

| 4       | AIN2        | AI                | アナログ入力 2。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5       | AIN3        | AI                | アナログ入力 3。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6       | REFOUT      | AO                | 内部リファレンスのバッファ付き出力。出力は AVSS を基準として 2.5 V です。                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7       | REGCAPA     | AO                | アナログ低ドロップアウト (LDO) レギュレータの出力。1 μF のコンデンサを使用して、このピンを AVSS へデカップリングします。                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8       | AVSS        | P                 | 負のアナログ電源。電源電圧範囲は 0 V ~ -2.75 V で、公称 0 V に設定されています。                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9       | AVDD1       | P                 | アナログ電源電圧 1。この電圧は、AVSS を基準として、5 V ± 10 % です。AVDD1 - AVSS は、5 V の単電源または ± 2.5 V の両電源にすることができます。                                                                                                                                                                                                                                                                                                                                                                         |

| 10      | AVDD2       | P                 | アナログ電源電圧 2。この電圧範囲は、AVSS を基準として、2 V ~ AVDD1 です。                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11      | PDSW        | AO                | AVSS に接続されたパワーダウン・スイッチ。このピンは、GPIOCON レジスタの PDSW ビットによって制御されます。                                                                                                                                                                                                                                                                                                                                                                                                        |

| 12      | XTAL1       | AI                | 水晶振動子用入力 1。                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 13      | XTAL2/CLKIO | AI/DI             | 水晶振動子用入力 2 (XTAL2) /クロック入力または出力 (CLKIO)。詳細については、ADCMODE レジスタの CLOCKSEL ビットの設定を参照してください。                                                                                                                                                                                                                                                                                                                                                                               |

| 14      | DOUT/RDY    | DO                | シリアル・データ出力 (DOUT) /データ・レディ出力 (RDY)。このピンには 2 つの機能があります。ADC の出力シフト・レジスタにアクセスするときは、シリアル・データ出力ピンとして機能します。出力シフト・レジスタには、内蔵のどのデータ・レジスタまたはコントロール・レジスタからのデータでも格納できます。データワード/コントロール・ワード情報は SCLK の立下がりエッジで DOUT/RDY ピンに与えられ、SCLK の立上がりエッジで有効です。CS がハイ・レベルのとき、DOUT/RDY 出力はスリーステートになります。CS がロー・レベルで、レジスタが読み出し中でない場合、DOUT/RDY は、データ・レディー・ピンとして機能し、ロー・レベルに下がると変換完了を示します。変換後にデータが読み出されない場合、次の更新が行われる前にこのピンはハイ・レベルになります。DOUT/RDY の立下がりエッジは、プロセッサに対する割込みとして使用可能で、有効なデータが準備できていることを示します。 |

| Pin No. | Mnemonic        | Type <sup>2</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|-----------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15      | DIN             | DI                | ADC の入力シフト・レジスタへのシリアル・データ入力。このシフト・レジスタのデータは、ADC 内のコントロール・レジスタに転送されます。該当するレジスタは、コミュニケーション・レジスタのレジスタ・アドレス (RA) ビットにより指定されます。データは、SCLK の立上がりエッジでクロックインされます。                                                                                                                                                                                                                                                                        |

| 16      | SCLK            | DI                | シリアル・クロック入力。このシリアル・クロック入力は、ADC とのデータ転送に使用します。SCLK はシェミット・トリガ入力を備えているため、光絶縁アブリケーションのインターフェースに適しています。                                                                                                                                                                                                                                                                                                                             |

| 17      | $\overline{CS}$ | DI                | チップ・セレクト入力。このピンはアクティブ・ローのロジック入力で、ADC の選択に使用します。 $\overline{CS}$ は、シリアル・バスに複数のデバイスが接続されているシステムで ADC を選択するときに使います。 $\overline{CS}$ をロー・レベルにハードワイヤ接続することにより、デバイスとのインターフェースに SCLK、DIN、DOUT/RDY を使った 3 線式モードで ADC を動作させることができます。 $\overline{CS}$ がハイ・レベルのとき、DOUT/RDY 出力はスリーステートになります。                                                                                                                                                |

| 18      | ERROR           | DI/O              | エラー入力／出力または汎用出力。このピンは、以下の 3 つのモードのいずれかで使うことができます。<br>アクティブ・ローのエラー入力モード。このモードは、STATUS レジスタの ADC_ERROR ビットをセットします。<br>アクティブ・ローのオープンドレイン・エラー出力モード。ステータス・レジスタのエラー・ビットは ERROR ピンにマップされます。複数のデバイスの ERROR ピンを共通のプルアップ抵抗へ接続することができるため、どのデバイスのエラーも検知できます。<br>汎用出力モード。このピンのステータスは、GPIOCON レジスタの ERR_DAT ビットによって制御されます。このピンは、GPIO1 ピンと GPIO2 ピンで使われている AVDD1 と AVSS ではなく、IOVDD と DGND 間の電圧を基準としています。このモードでは、ERROR ピンはアクティブ・プルアップ回路を備えています。 |

| 19      | SYNC            | DI                | 同期入力。複数の AD7175-8 を使うときに、デジタル・フィルタとアナログ変調器の同期を可能にします。                                                                                                                                                                                                                                                                                                                                                                           |

| 20      | IOVDD           | P                 | デジタル I/O 電源電圧。IOVDD の電圧範囲は、2 V ~ 5 V (公称値) です。IOVDD は、AVDD1 と AVDD2 から独立しています。例えば、AVDD1 または AVDD2 が 5 V の場合に、IOVDD は 3.3 V で動作でき、その逆も可能です。AVSS を -2.5 V に設定した場合、IOVDD の電圧は 3.6 V を超えてはなりません。                                                                                                                                                                                                                                    |

| 21      | DGND            | P                 | デジタル・グラウンド。                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22      | REGCAPD         | AO                | デジタル LDO レギュレータ出力。このピンはデカッピング専用です。1 $\mu$ F のコンデンサを使用して、このピンを DGND へデカッピングします。                                                                                                                                                                                                                                                                                                                                                  |

| 23      | GPIO0           | DI/O              | 汎用入出力 0。このピンのロジック入出力は、AVDD1 電源と AVSS 電源を基準としています。                                                                                                                                                                                                                                                                                                                                                                               |

| 24      | GPIO1           | DI/O              | 汎用入出力 2。このピンのロジック入出力は、AVDD1 電源と AVSS 電源を基準としています。                                                                                                                                                                                                                                                                                                                                                                               |

| 25      | GPO2            | DO                | 汎用出力 2。このピンのロジック出力は、AVDD1 電源と AVSS 電源を基準としています。                                                                                                                                                                                                                                                                                                                                                                                 |

| 26      | AIN4            | AI                | アナログ入力 4。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                        |

| 27      | AIN5            | AI                | アナログ入力 5。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                        |

| 28      | AIN6            | AI                | アナログ入力 6。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                        |

| 29      | AIN7            | AI                | アナログ入力 7。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                        |

| 30      | AIN8            | AI                | アナログ入力 8。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                        |

| 31      | AIN9            | AI                | アナログ入力 9。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                        |

| 32      | AIN10           | AI                | アナログ入力 10。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                       |

| 33      | AIN11           | AI                | アナログ入力 11。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                       |

| 34      | AIN12           | AI                | アナログ入力 12。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                       |

| 35      | AIN13           | AI                | アナログ入力 13。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                       |

| 36      | AIN14           | AI                | アナログ入力 14。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                       |

| 37      | AIN15           | AI                | アナログ入力 15。このピンはクロスポイント・マルチプレクサを介して選択できます。                                                                                                                                                                                                                                                                                                                                                                                       |

| 38      | GPO3            | DO                | 汎用出力 3。このピンのロジック出力は、AVDD1 電源と AVSS 電源を基準としています。                                                                                                                                                                                                                                                                                                                                                                                 |

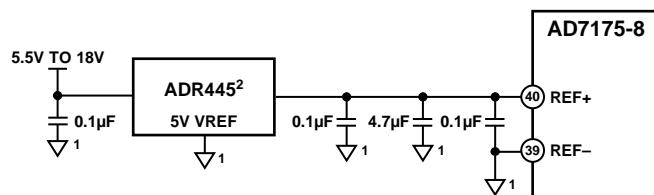

| 39      | REF-            | AI                | リファレンス 1 入力の負端子。REF- の範囲は、AVSS ~ AVDD1 - 1 V です。リファレンス 1 は、セットアップ設定レジスタの REF_SELx ビットを介して選択できます。                                                                                                                                                                                                                                                                                                                                |

| 40      | REF+            | AI                | リファレンス 1 入力の正端子。外部リファレンスを REF+ と REF- の間に与えることができます。REF+ の範囲は、AVDD1 ~ AVSS + 1 V です。リファレンス 1 は、セットアップ設定レジスタの REF_SELx ビットを介して選択できます。                                                                                                                                                                                                                                                                                            |

|         | EP              | P                 | 露出パッド。露出パッドは、パッケージの機械的強度と放熱効果を高めるため、露出パッドの下の PCB 上の同様のパッドにハンダ付けします。露出パッドは、PCB 上のこのパッドを介して AVSS に接続する必要があります。                                                                                                                                                                                                                                                                                                                    |

<sup>1</sup> このデータシートでは、2 つの機能名を持つピンは、そのいずれかのみを用いて該当する機能を説明していることにご注意下さい。<sup>2</sup> AI = アナログ入力、AO = アナログ出力、P = 電源、DI = デジタル入力、DO = デジタル出力、DI/O = 双方向デジタル入出力。

## 代表的な性能特性

特に指定のない限り、AVDD1 = 5 V、IOVDD = 3.3 V、TA = 25°C。

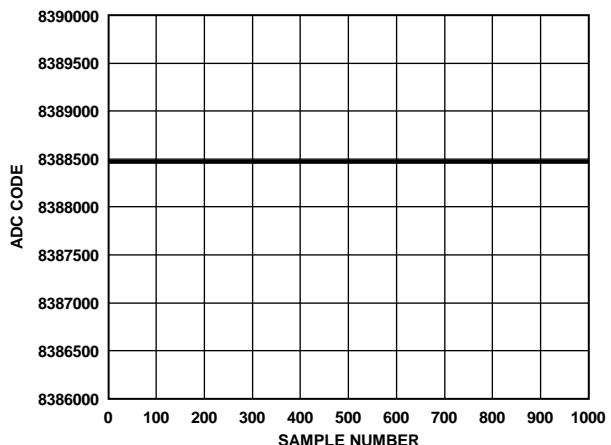

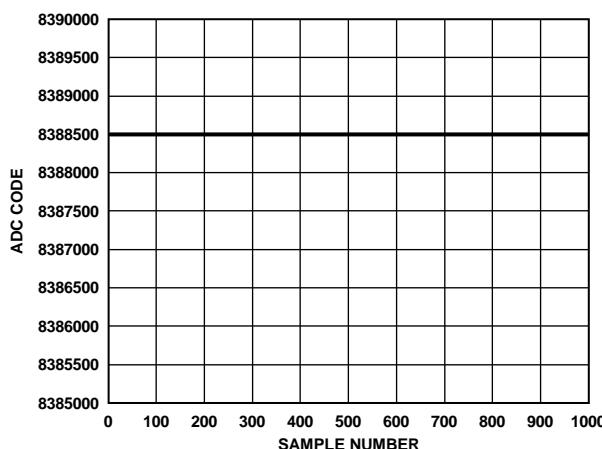

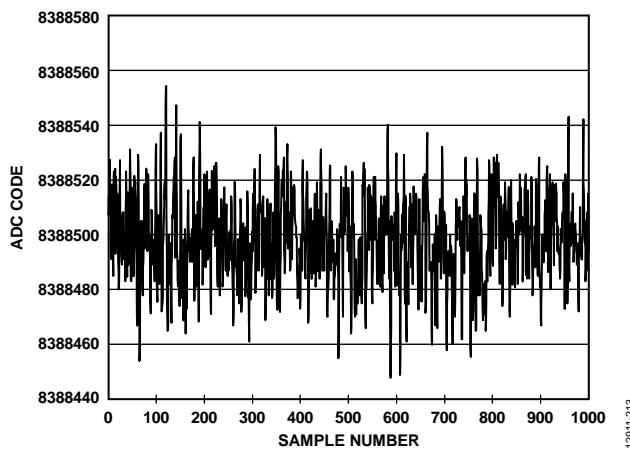

図 5. ノイズ（アナログ入力バッファはディスエーブル、

VREF = 5 V、出力データ・レート = 5 SPS）

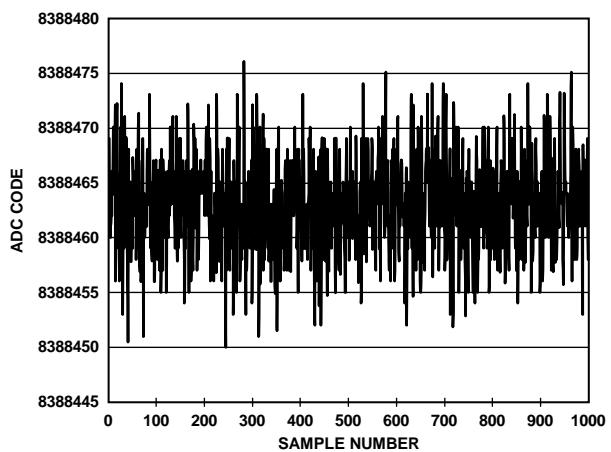

図 6. ノイズ（アナログ入力バッファはディスエーブル、

VREF = 5 V、出力データ・レート = 10 kSPS）

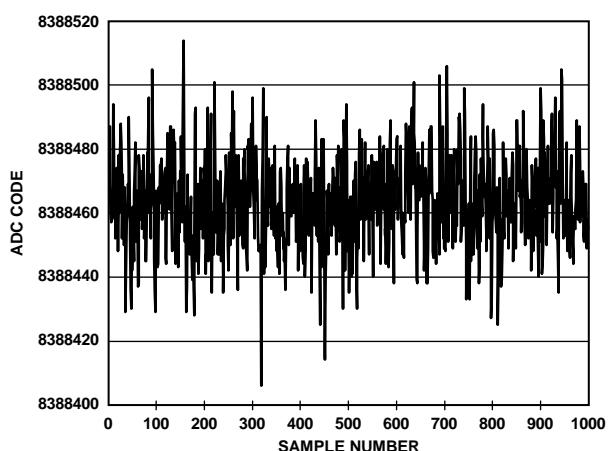

図 7. ノイズ（アナログ入力バッファはディスエーブル、

VREF = 5 V、出力データ・レート = 250 kSPS）

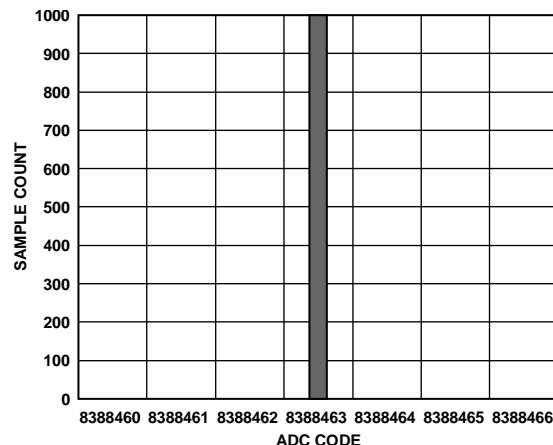

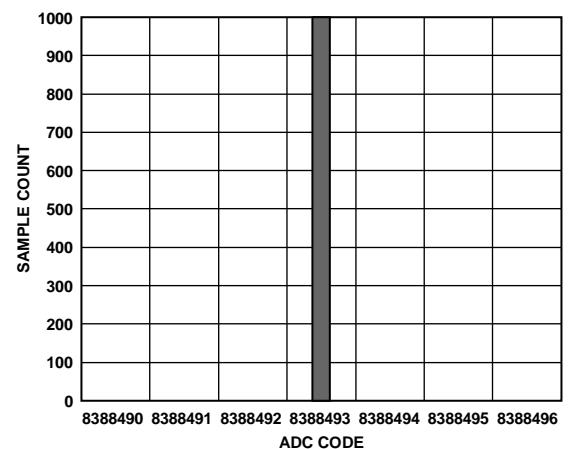

図 8. ヒストグラム（アナログ入力バッファはディスエーブル、

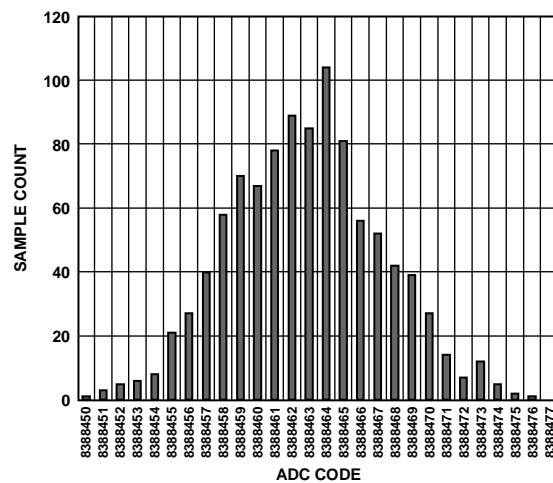

VREF = 5 V、出力データ・レート = 5 SPS）

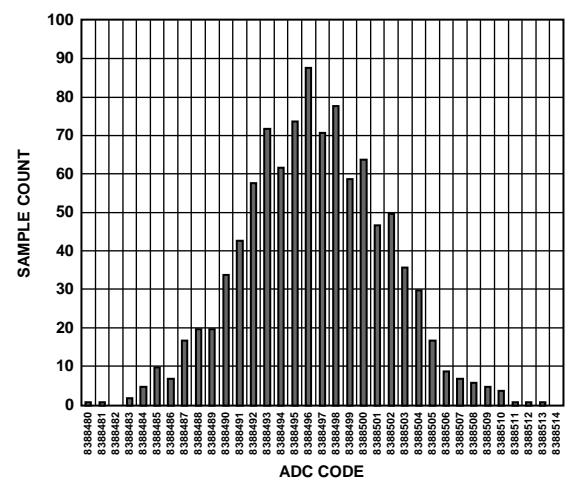

図 9. ヒストグラム（アナログ入力バッファはディスエーブル、

VREF = 5 V、出力データ・レート = 10 kSPS）

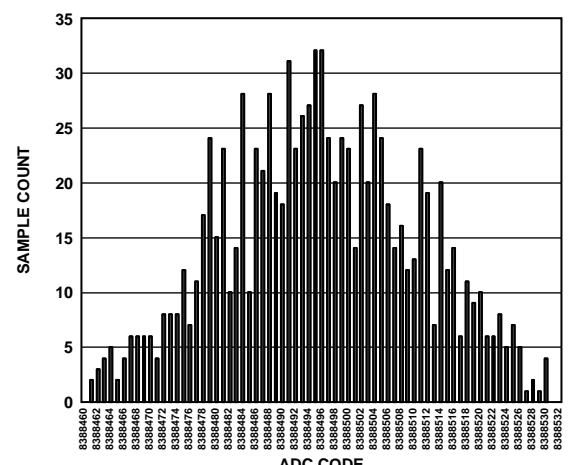

図 10. ヒストグラム（アナログ入力バッファはディスエーブル、

VREF = 5 V、出力データ・レート = 250 kSPS）

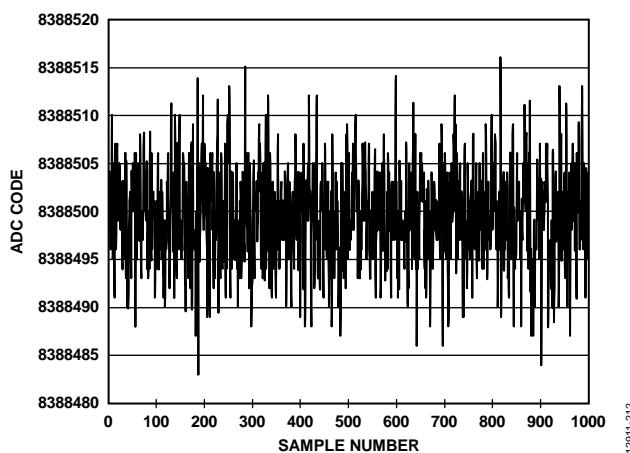

図 11. ノイズ（アナログ入力バッファはイネーブル、 $V_{REF} = 5\text{ V}$ 、出力データ・レート = 5 SPS）

図 12. ノイズ（アナログ入力バッファはイネーブル、 $V_{REF} = 5\text{ V}$ 、出力データ・レート = 10 kSPS）

図 13. ノイズ（アナログ入力バッファはイネーブル、 $V_{REF} = 5\text{ V}$ 、出力データ・レート = 250 kSPS）

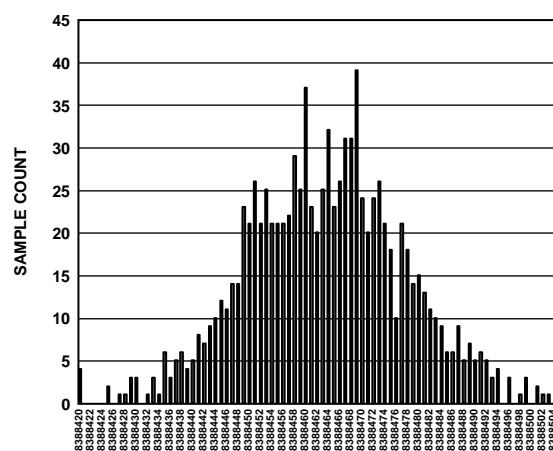

図 14. ヒストグラム（アナログ入力バッファはイネーブル、 $V_{REF} = 5\text{ V}$ 、出力データ・レート = 5 SPS）

図 15. ヒストグラム（アナログ入力バッファはイネーブル、 $V_{REF} = 5\text{ V}$ 、出力データ・レート = 10 kSPS）

図 16. ヒストグラム（アナログ入力バッファはイネーブル、 $V_{REF} = 5\text{ V}$ 、出力データ・レート = 250 kSPS）

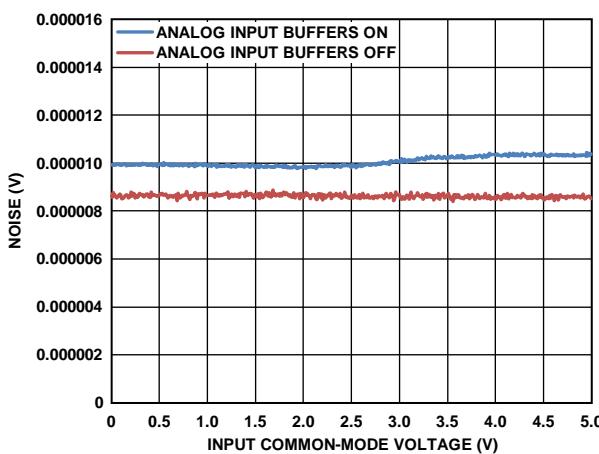

図 17. アナログ入力バッファのオン／オフ時における、

入力コモンモード電圧対ノイズ

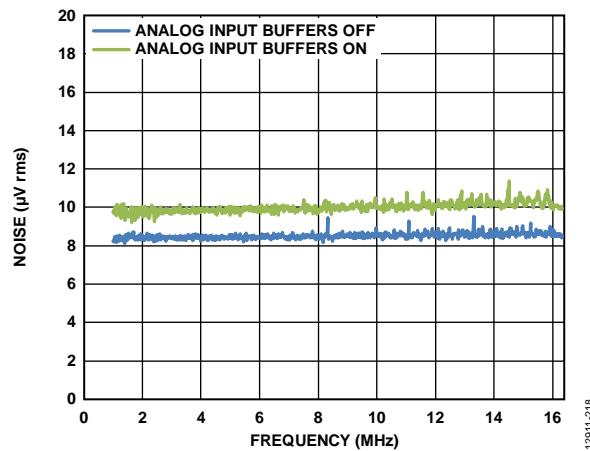

図 18. アナログ入力バッファのオン／オフ時における、

外部マスター・クロック周波数対ノイズ

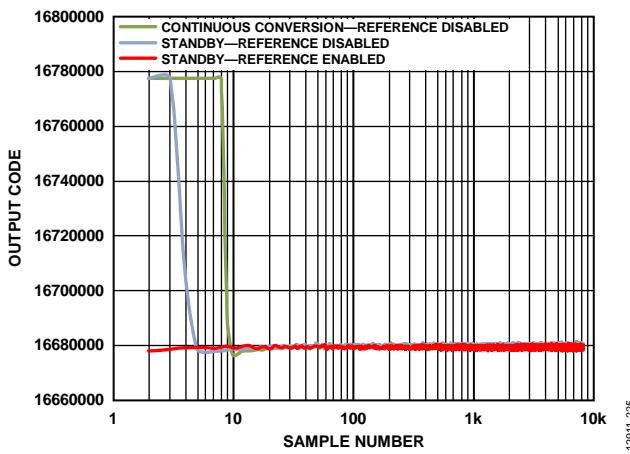

図 19. 内部リファレンスのセトリング時間

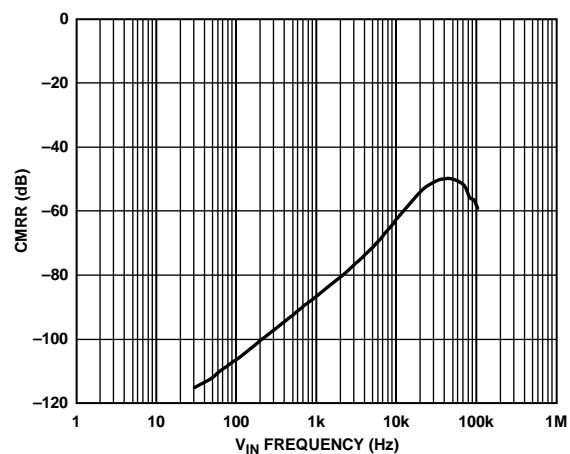

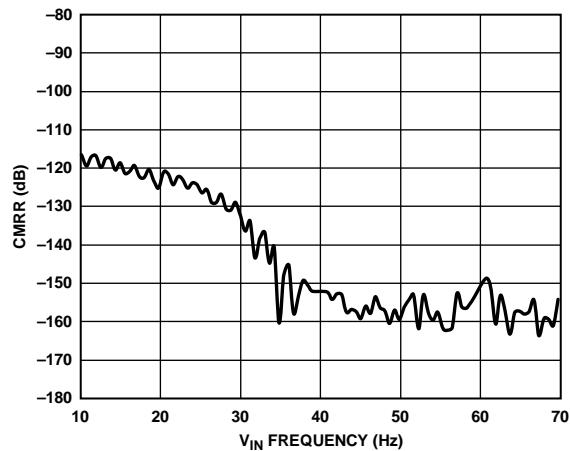

図 20. V<sub>IN</sub> の周波数対同相ノイズ除去比 (CMRR)

(V<sub>IN</sub> = 0.1 V、出力データ・レート = 250 kSPS)

図 21. V<sub>IN</sub> の周波数対同相ノイズ除去比 (CMRR)

(V<sub>IN</sub> = 0.1 V、10 Hz ~70 Hz、出力データ・レート = 20 SPS、

エンハンスド・フィルタ)

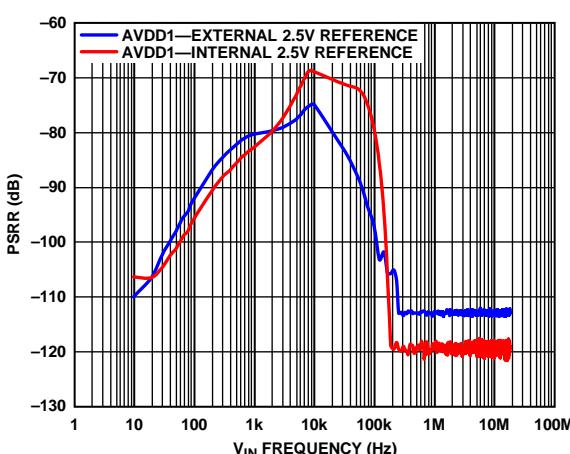

図 22. V<sub>IN</sub> の周波数対電源電圧変動除去比 (PSRR)

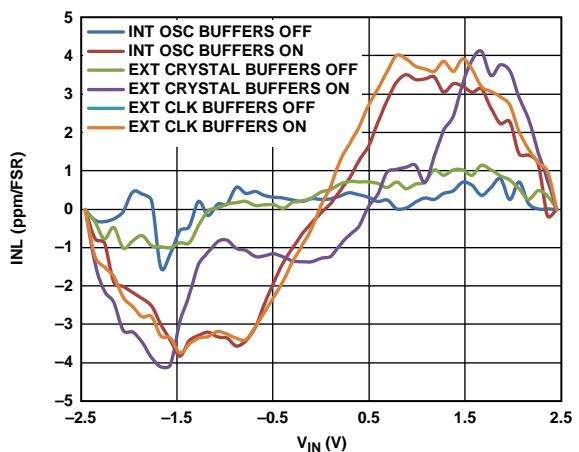

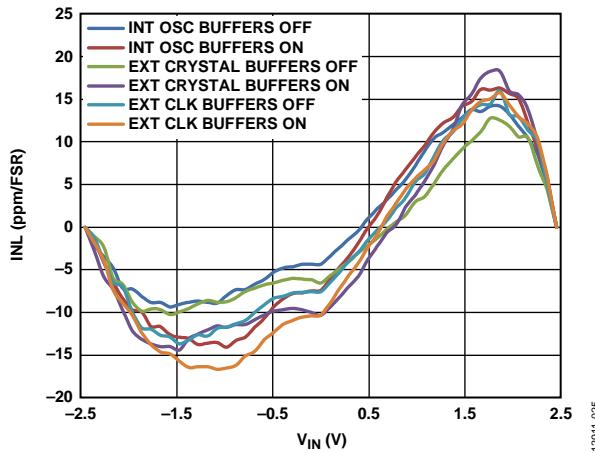

図 23.  $V_{IN}$  対積分非直線性 (INL)

(差動入力、2.5 V 外部リファレンス)

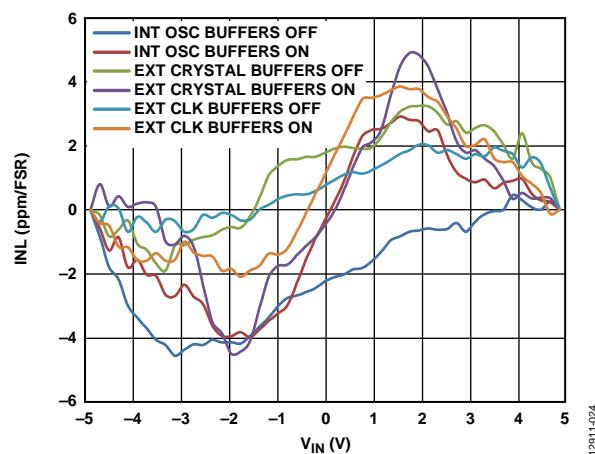

図 24.  $V_{IN}$  対積分非直線性 (INL)

(差動入力、5 V 外部リファレンス)

図 25.  $V_{IN}$  対積分非直線性 (INL)

(差動入力、2.5 V 内部リファレンス)

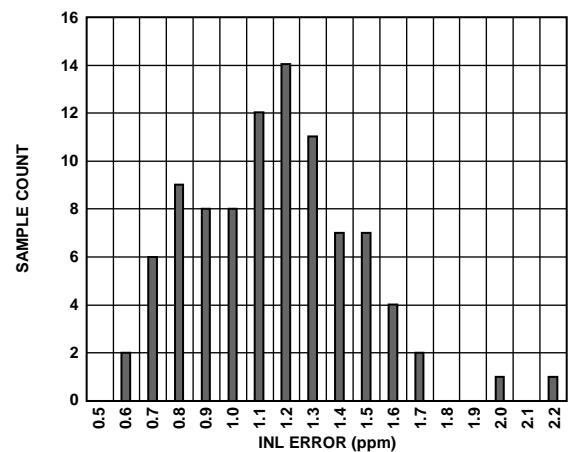

図 26. 積分非直線性 (INL) 分布ヒストグラム

(全てのアナログ入力バッファがディスエーブル、差動入力、 $V_{REF} = 5$  V 外部リファレンス、92 ユニット)

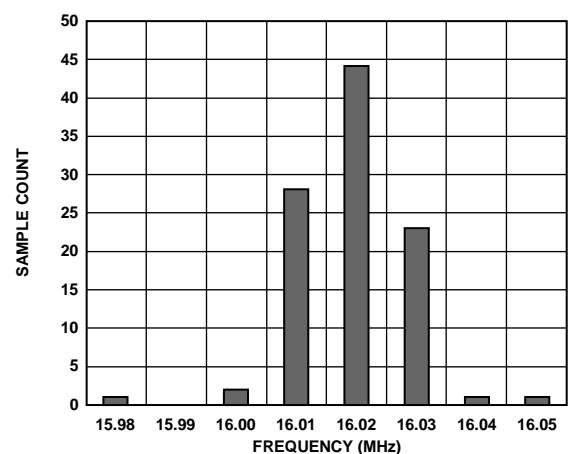

図 27. 内部発振器の周波数／精度分布ヒストグラム

(100 ユニット)

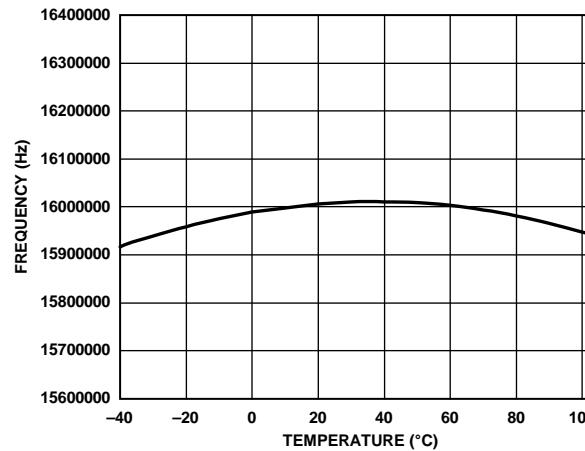

図 28. 内部発振器の周波数の温度特性

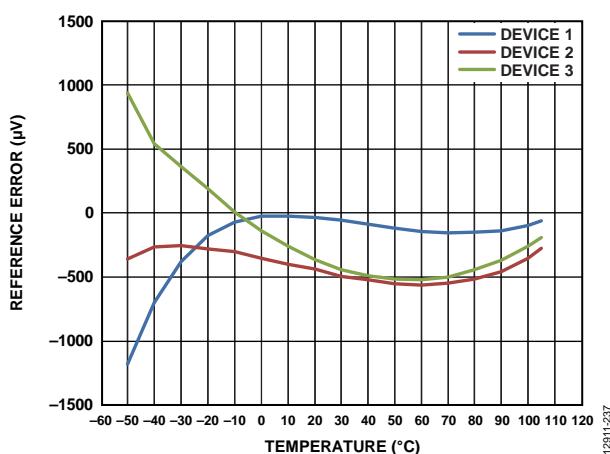

図 29. 絶対リファレンス誤差の温度特性

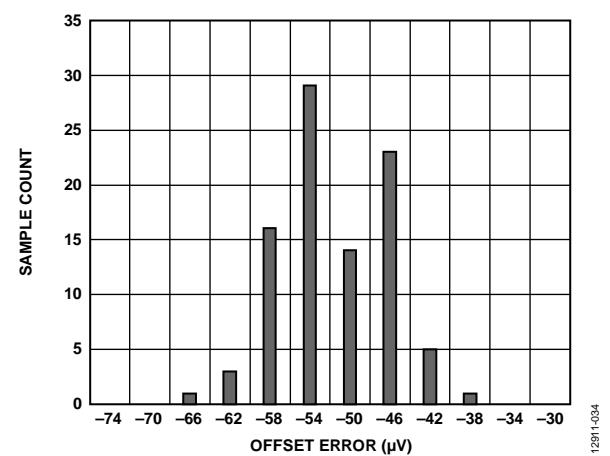

図 30. オフセット誤差分布ヒストグラム

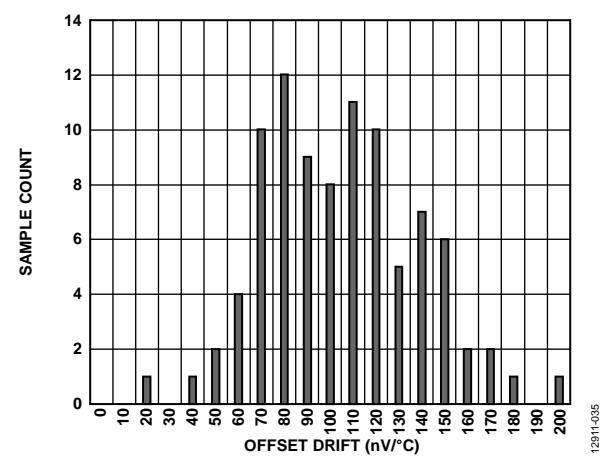

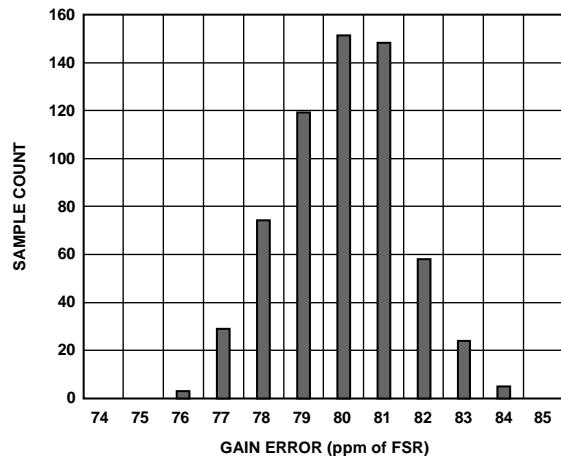

(内部短絡、92 ユニット)図 31. オフセット誤差ドリフト分布ヒストグラム

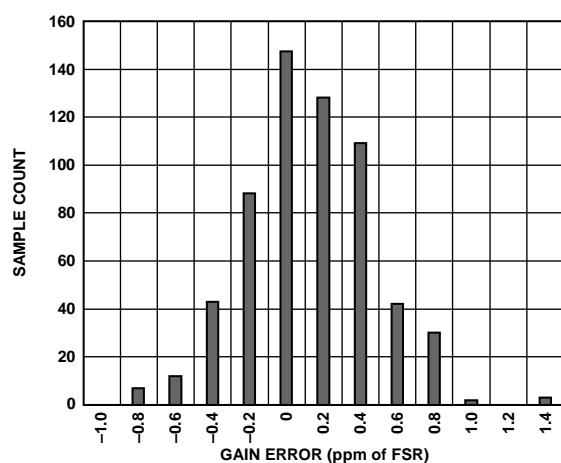

(内部短絡、92 ユニット)図 32. ゲイン誤差分布ヒストグラム

(全ての入力バッファがイネーブル、611 ユニット)図 33. ゲイン誤差分布ヒストグラム

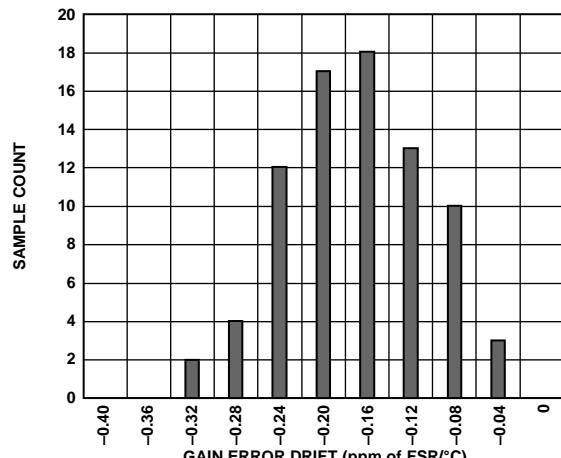

(全ての入力バッファがディスエーブル、647 ユニット)図 34. ゲイン誤差ドリフト分布ヒストグラム

(全ての入力バッファがイネーブル、79 ユニット)

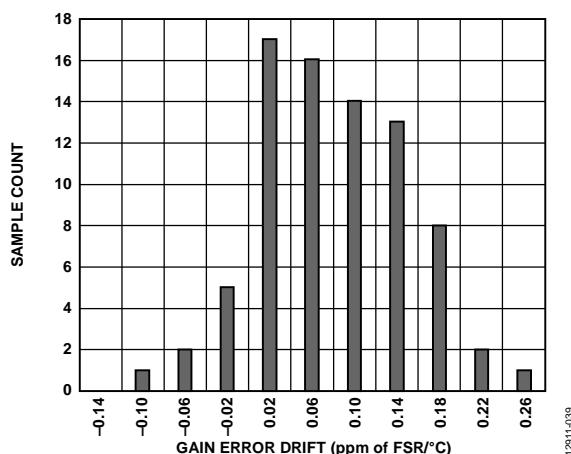

図 35. 全温度範囲のゲイン誤差ドリフト分布ヒストグラム

(全ての入力バッファがディスエーブル、79 ユニット)

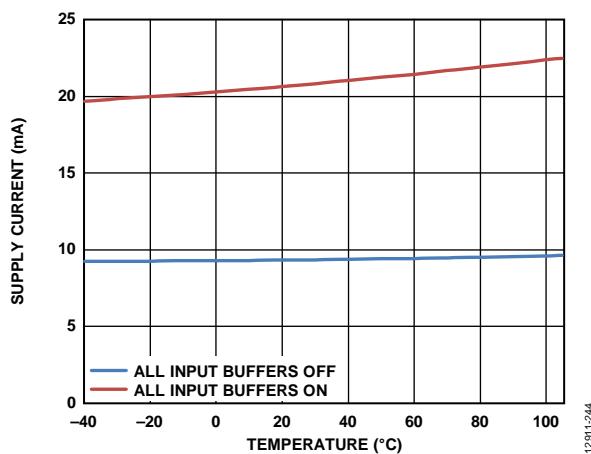

図 36. 電源電流の温度特性（連続変換モード）

図 37. 電源電流の温度特性（スタンバイ・モード、リファレンスはイネーブル）

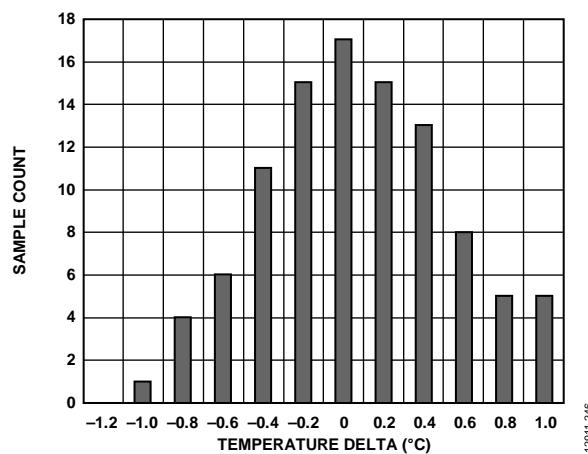

図 38. 温度センサー分布ヒストグラム（未校正、100 ユニット）

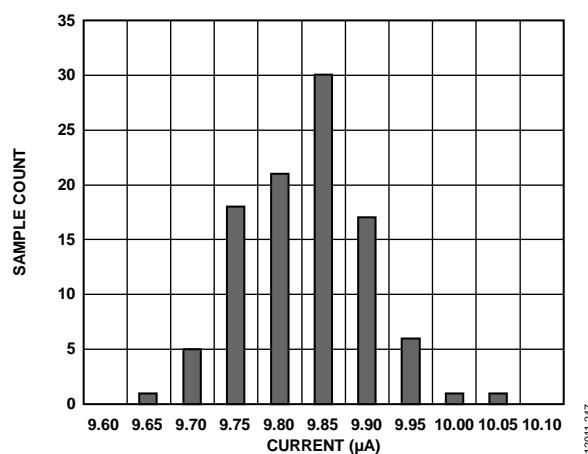

図 39. パーンアウト電流分布ヒストグラム（100 ユニット）

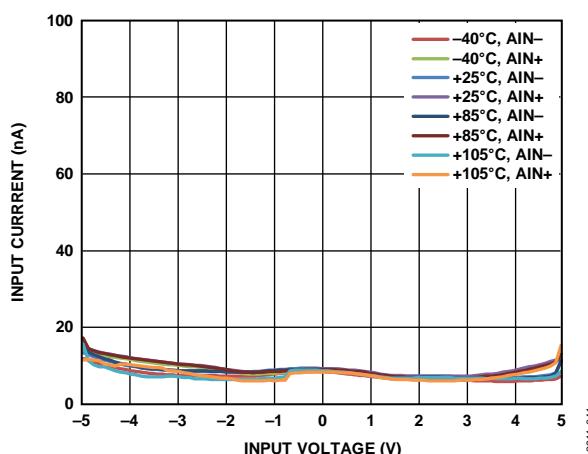

図 40. 入力電圧対アナログ入力電流 ( $V_{CM} = 2.5 \text{ V}$ )

## ノイズ性能と分解能

各種出力データ・レートとフィルタに対する、AD7175-8 の rms ノイズ、ピーク to ピーク・ノイズ、実効分解能、およびノイズ・フリー（ピーク to ピーク）分解能を表 6 と表 7 に示します。ここに示した値は、5 V の外部リファレンスを使用したバイポーラ入力範囲の場合です。これらの値は代表値であり、

ADC が 1 チャンネルを連続変換するとき、0 V の差動入力電圧で生成される値です。ピーク to ピーク分解能は、ピーク to ピーク・ノイズを基に計算された値であることに注意して下さい。このピーク to ピーク分解能は、コード・フリッカが生じない分解能を表します。

表 6. 出力データ・レートに対する RMS ノイズとピーク to ピーク分解能（デフォルトは sinc5 + sinc1 フィルタ使用）<sup>1</sup>

| Output Data Rate (SPS) | RMS Noise ( $\mu\text{V}$ rms) | Effective Resolution (Bits) | Peak-to-Peak Noise ( $\mu\text{V}$ p-p) | Peak-to-Peak Resolution (Bits) |

|------------------------|--------------------------------|-----------------------------|-----------------------------------------|--------------------------------|

| Input Buffers Disabled |                                |                             |                                         |                                |

| 250,000                | 8.7                            | 20.1                        | 65                                      | 17.2                           |

| 62,500                 | 5.5                            | 20.8                        | 43                                      | 17.8                           |

| 10,000                 | 2.5                            | 21.9                        | 18.3                                    | 19.1                           |

| 1000                   | 0.77                           | 23.6                        | 5.2                                     | 20.9                           |

| 59.92                  | 0.19                           | 24                          | 1.1                                     | 23.1                           |

| 49.96                  | 0.18                           | 24                          | 0.95                                    | 23.3                           |

| 16.66                  | 0.1                            | 24                          | 0.45                                    | 24                             |

| 5                      | 0.07                           | 24                          | 0.34                                    | 24                             |

| Input Buffers Enabled  |                                |                             |                                         |                                |

| 250,000                | 9.8                            | 20                          | 85                                      | 16.8                           |

| 62,500                 | 6.4                            | 20.6                        | 55                                      | 17.5                           |

| 10,000                 | 3                              | 21.7                        | 23                                      | 18.7                           |

| 1000                   | 0.92                           | 23.4                        | 5.7                                     | 20.7                           |

| 59.98                  | 0.23                           | 24                          | 1.2                                     | 23.0                           |

| 49.96                  | 0.2                            | 24                          | 1                                       | 23.3                           |

| 16.66                  | 0.13                           | 24                          | 0.66                                    | 23.9                           |

| 5                      | 0.07                           | 24                          | 0.32                                    | 24                             |

<sup>1</sup>選択されたレートのみ、1000 サンプル。

表 7. 出力データ・レートに対する RMS ノイズとピーク to ピーク分解能（sinc3 フィルタ使用）<sup>1</sup>

| Output Data Rate (SPS) | RMS Noise ( $\mu\text{V}$ rms) | Effective Resolution (Bits) | Peak-to-Peak Noise ( $\mu\text{V}$ p-p) | Peak-to-Peak Resolution (Bits) |

|------------------------|--------------------------------|-----------------------------|-----------------------------------------|--------------------------------|

| Input Buffers Disabled |                                |                             |                                         |                                |

| 250,000                | 210                            | 15.5                        | 1600                                    | 12.6                           |

| 62,500                 | 5.2                            | 20.9                        | 40                                      | 17.9                           |

| 10,000                 | 1.8                            | 22.4                        | 14                                      | 19.4                           |

| 1000                   | 0.56                           | 24                          | 3.9                                     | 21.3                           |

| 60                     | 0.13                           | 24                          | 0.8                                     | 23.6                           |

| 50                     | 0.13                           | 24                          | 0.7                                     | 23.8                           |

| 16.66                  | 0.07                           | 24                          | 0.37                                    | 24                             |

| 5                      | 0.05                           | 24                          | 0.21                                    | 24                             |

| Input Buffers Enabled  |                                |                             |                                         |                                |

| 250,000                | 210                            | 15.5                        | 1600                                    | 12.6                           |

| 62,500                 | 5.8                            | 20.7                        | 48                                      | 17.7                           |

| 10,000                 | 2.1                            | 22.2                        | 16                                      | 19.3                           |

| 1000                   | 0.71                           | 23.7                        | 4.5                                     | 21.1                           |

| 60                     | 0.17                           | 24                          | 1.1                                     | 23.1                           |

| 50                     | 0.15                           | 24                          | 0.83                                    | 23.5                           |

| 16.66                  | 0.12                           | 24                          | 0.6                                     | 24                             |

| 5                      | 0.08                           | 24                          | 0.35                                    | 24                             |

<sup>1</sup>選択されたレートのみ、1000 サンプル。

## 評価開始にあたって

AD7175-8 は、高速セトリング、高分解能のマルチプレクス型 ADC であり、高いレベルで設定が可能です。AD7175-8 は以下のようない機能を備えています。

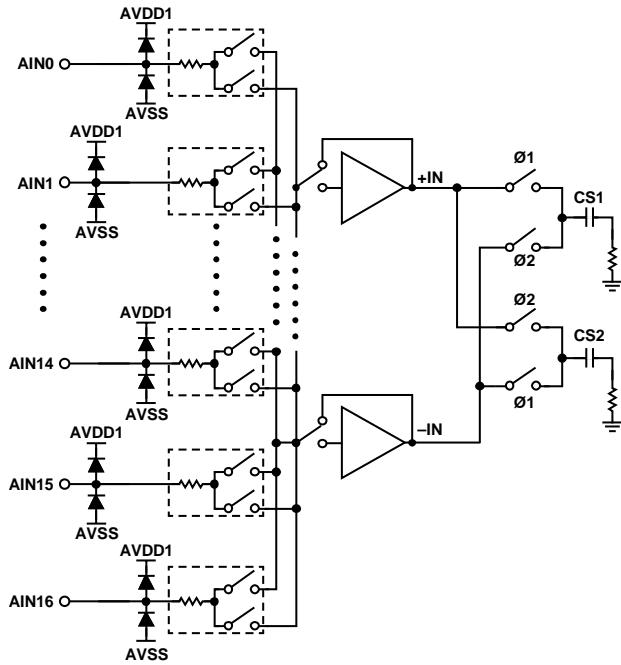

- 8 チャンネルの完全差動または 16 チャンネルのシングルエンド・アナログ入力。

- クロスポイント・マルチプレクサにより、変換対象の入力信号として任意のアナログ入力の組み合わせを選択し、変調器の正入力または負入力へ接続します。

- 真のレール to レール・パッファ付きのアナログ入力とリファレンス入力。

- いずれのアナログ入力を基準にしても完全差動入力またはシングルエンド入力が可能。

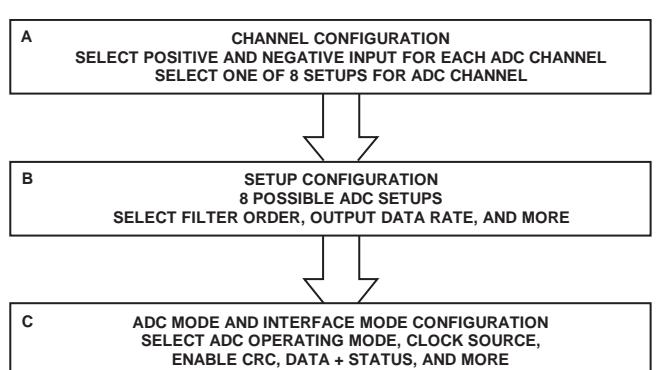

- チャンネルごとに柔軟な設定が可能。最多 8 つの異なるセットアップを定義でき、個別のセットアップをチャンネルごとにマップすることができます。それぞれのセットアップにより、パッファのイネーブル/ディスエーブル、ゲイン補正およびオフセット補正の有無、フィルタのタイプ、出力データ・レート、リファレンス・ソースの選択（内部/外部）を設定することができます。

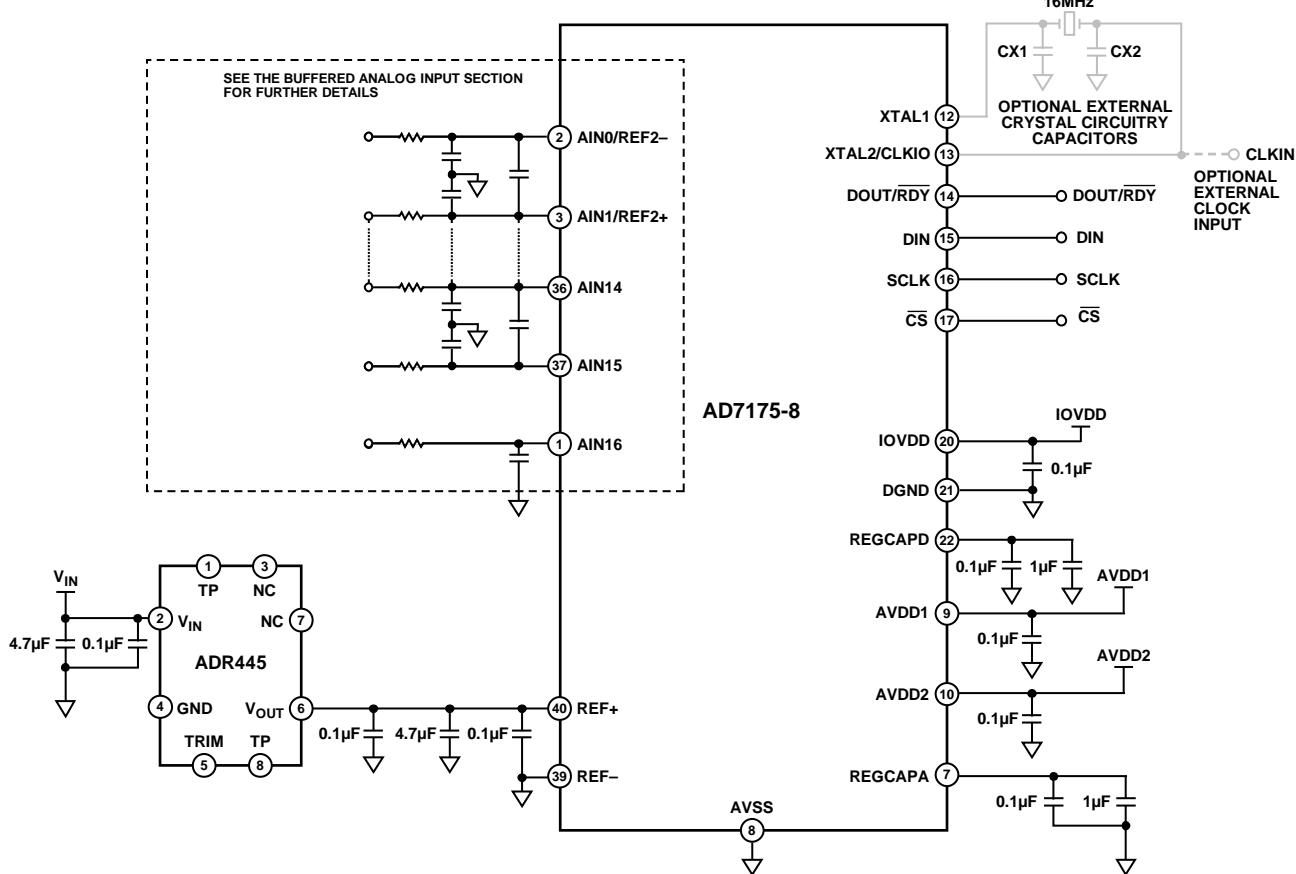

AD7175-8 は高精度で低ドリフト ( $\pm 2 \text{ ppm}/^\circ\text{C}$ ) の 2.5 V バンドギヤップ・リファレンスを内蔵しています。このリファレンスを ADC 変換に使用できるので、外部部品数を減らせます。また、REFOUT ピンヘリファレンスを出力し、外部回路への低ノイズ・バイアス電圧として用いることもできます。この例としては、REFOUT 信号を使った外部アンプの入力コモンモードの設定があります。

AD7175-8 は、アナログ回路とデジタル回路の両方に個別のリニア・レギュレータ・ブロックを内蔵しています。アナログ LDO は AVDD2 電源を 1.8 V に安定化し、ADC コアに給電します。接続を簡単にするため、AVDD1 電源と AVDD2 電源を一緒に接続することもできます。システム内に 2 V (最小値) ~ 5.5 V (最大値) のクリーンなアナログ電源がすでに存在する場合は、この電源を AVDD2 入力に接続して消費電力を抑えることもできます。

図 41. 代表的な接続図

デジタル IOVDD 電源用のリニア・レギュレータも同様の機能を実行し、IOVDD ピンに印加された入力電圧を 1.8 V に安定化して内部のデジタル・フィルタに供給します。シリアル・インターフェース信号は、常にこのピンの IOVDD 電源で動作します。つまり、IOVDD ピンに 3.3 V が印加されている場合、インターフェース・ロジックの入出力は、この電圧レベルで動作します。

AD7175-8 は幅広いアプリケーションで使用でき、高分解能と高精度を提供します。これらの例を以下に示します。

- 内部マルチプレクサを使ったアナログ入力チャンネルの高速スキャニング。

- GPIO で自動制御する外部マルチプレクサを使ったアナログ入力チャンネルの高速スキャニング。

- チャンネル・スキャニングまたはチャンネルごとに ADC が必要なアプリケーションにおける低速での高分解能。

- プリント回路基板 (PCB) の面積を節減するため、高集積ソリューションを必要とする高分解能アプリケーション。