## データシート

AD7175-2

### 特長

高速かつ柔軟な出力レート 5 SPS から 250k SPS

チャンネル・スキャン・データレート : 50kSPS/チャンネル

(セトリング時間 20μs)

#### 性能仕様

ノイズ・フリー・ビット数: 250 kSPS で 17.2 ビット

ノイズ・フリー・ビット数: 2.5k SPS で 20 ビット

ノイズ・フリー・ビット数: 20 SPS で 24 ビット

INL: FSR の±1ppm

50 Hz と 60 Hz の除去比: 50 ms セトリングで 85 dB

入力チャンネルがユーザ設定可能

2 チャンネル完全差動または 4 チャンネルシングルエンド

クロスポイント・マルチプレクサ

2.5 V のリファレンスを内蔵 (ドリフト 2ppm/°C)

真のレール to レールのアナログ入力バッファとリファレンス

入力バッファ

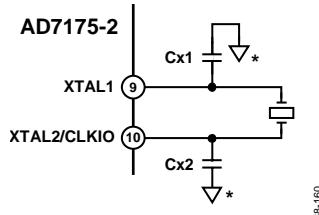

内部または外部クロック

電源電圧 :

AVDD1 = 5 V, AVDD2 = IOVDD = 2 V to 5 V

AVDD1/AVSS を±2.5 V とする両電源も可能

ADC 消費電流 : 8.4 mA

温度範囲 : -40°C ~ +105°C

3 線式または 4 線式のシリアル・デジタル・インターフェー

ス (シムミット・トリガ付き SCLK)

シリアル・インターフェース :

SPI/QSPI/MICROWIRE/DSP 互換

### アプリケーション

プロセス・コントロール : PLC/DCS モジュール

温度計測および圧力計測

医療や科学分野向けのマルチ・チャンネル計測機器

クロマトグラフィ

### 概要

AD7175-2 は低ノイズ、高速セトリング時間のマルチプレクサ型 2/4 (完全差動 / 擬似差動) チャンネル Σ-Δ A/D コンバータ (ADC) で、低い帯域の入力信号を対象としています。データが完全に安定する最大チャンネル・スキャン・データレートは 50k SPS (20μs) です。出力データレートは 5 SPS ~ 250k SPS の範囲です。

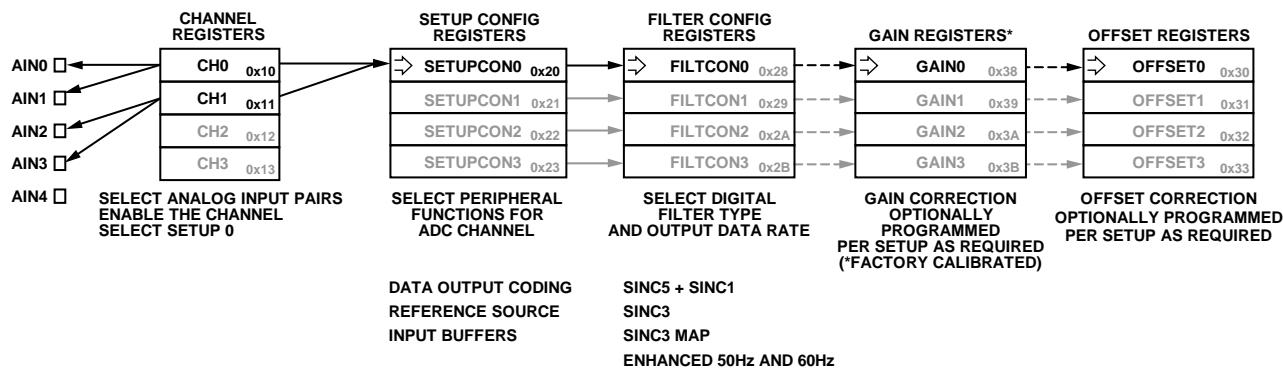

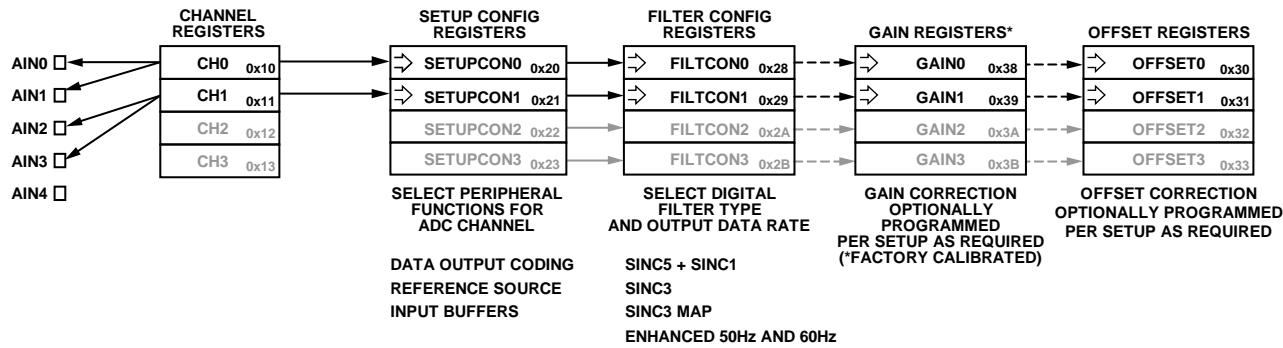

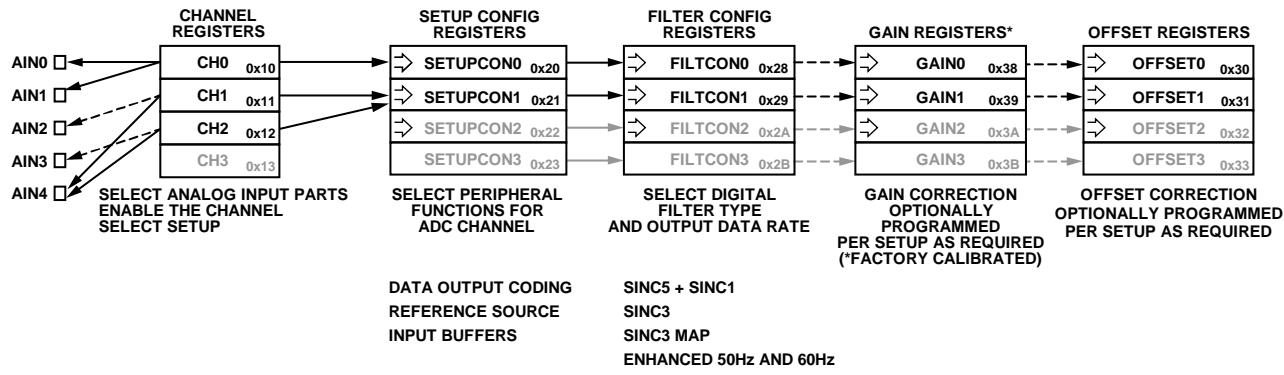

AD7175-2 は、主要なアナログ / デジタル信号処理ブロックを内蔵しており、ユーザは使用する各アナログ入力チャンネルの個別の構成を設定することができます。各機能はチャンネルごとにユーザ選択可能になっています。アナログ入力と外部リファレンス入力に内蔵されている真のレール to レール・バッファにより高インピーダンス入力の駆動が容易になっています。高精度、2.5V、低ドリフト (2ppm/°C) の内部バンドギャップ・リファレンスには、出力リファレンス・バッファが追加されているため、外部バッファを必要とせず、外付け部品数を削減できます。

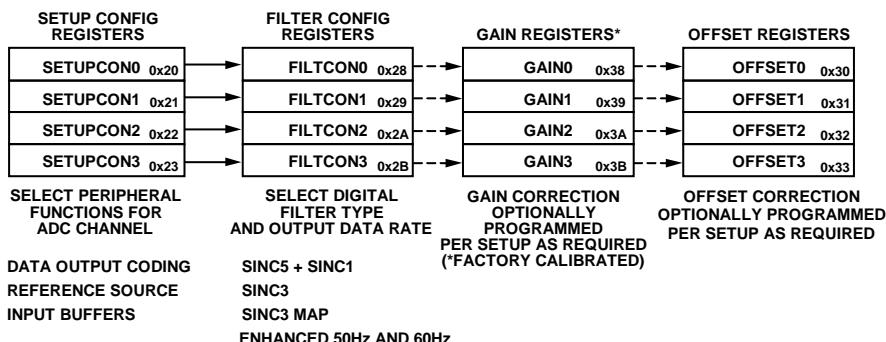

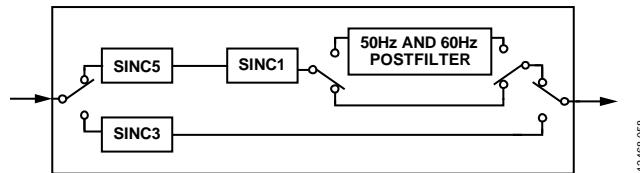

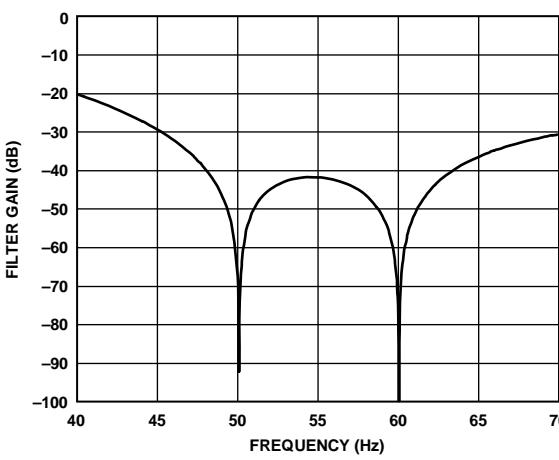

デジタル・フィルタにより、27.27 SPS の出力データレートにおいては、50Hz および 60Hz の同時除去が可能です。ユーザは、アプリケーション毎に異なる各チャンネルの要求に合わせて、異なったフィルタ・オプションを選択できます。ADC は選択した各チャンネルを通して自動的に切り替えます。さらにデジタル処理機能にはチャンネルごとに調整可能なオフセット調整レジスタ、ゲイン調整用レジスタがあります。

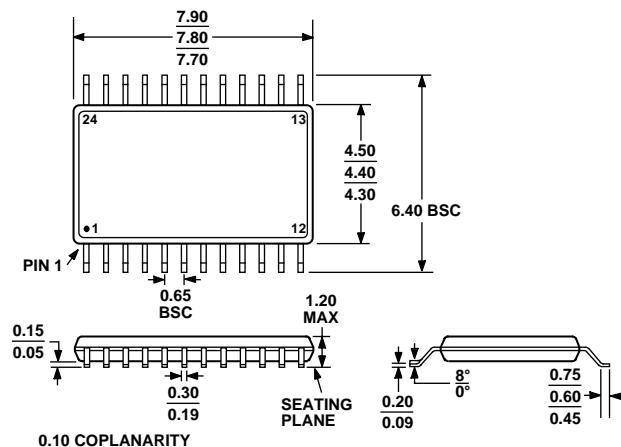

デバイスは AVDD1=5V の単電源、あるいは、AVDD1/AVSS =±2.5V の両電源で動作します。また、AVDD2 と IOVDD の電圧範囲は 2V ~ 5V です。規定の動作温度範囲は -40°C ~ +105°C です。AD7175-2 は 24 ピン TSSOP パッケージを採用しています。

なお、このデータシートでは、複数の機能名を持つピンは、そのいずれかのみを用いて、該当する機能を説明していることにご注意下さい。

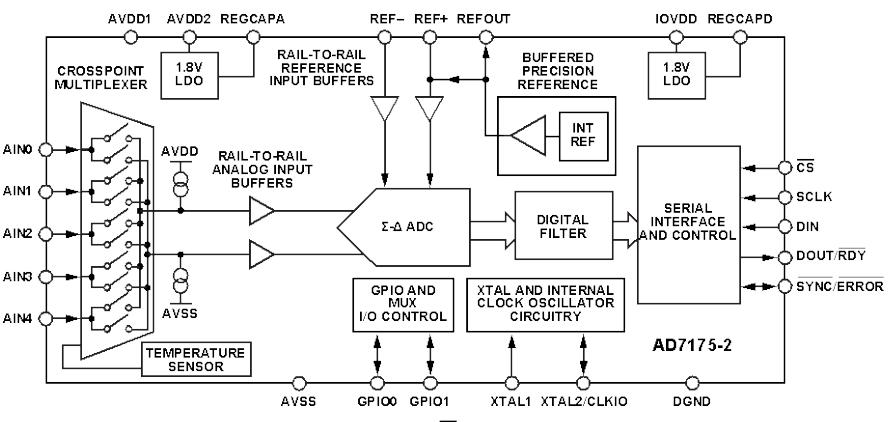

### 機能ブロック図

図 1.

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。

\*日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2015 Analog Devices, Inc. All rights reserved.

Rev.A

## 目次

|                        |    |

|------------------------|----|

| 特長                     | 1  |

| アプリケーション               | 1  |

| 概要                     | 1  |

| 機能ブロック図                | 1  |

| 仕様                     | 3  |

| タイミング特性                | 6  |

| タイミング図                 | 7  |

| 絶対最大定格                 | 8  |

| 熱抵抗                    | 8  |

| ESD の注意                | 8  |

| ピン配置およびピン機能説明          | 9  |

| 代表的な性能特性               | 11 |

| ノイズ特性と分解能              | 18 |

| 評価開始にあたって              | 19 |

| 電源                     | 20 |

| デジタル通信                 | 20 |

| AD7175-2 のリセット         | 21 |

| 構成概要                   | 21 |

| 回路説明                   | 26 |

| バッファ付きアナログ入力           | 26 |

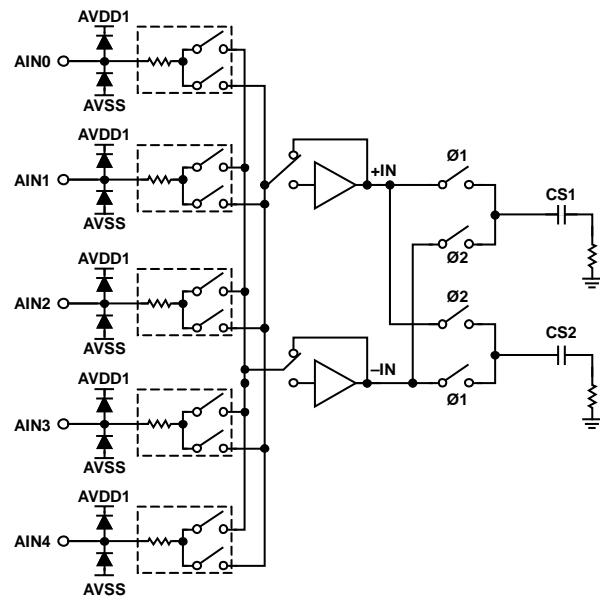

| クロスポイント・マルチブレクサ        | 26 |

| AD7175-2 リファレンス        | 26 |

| バッファされたリファレンス入力        | 28 |

| クロック・ソース               | 28 |

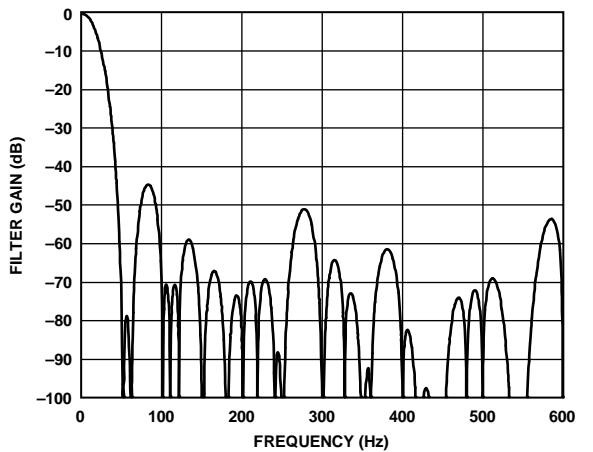

| デジタル・フィルタ              | 29 |

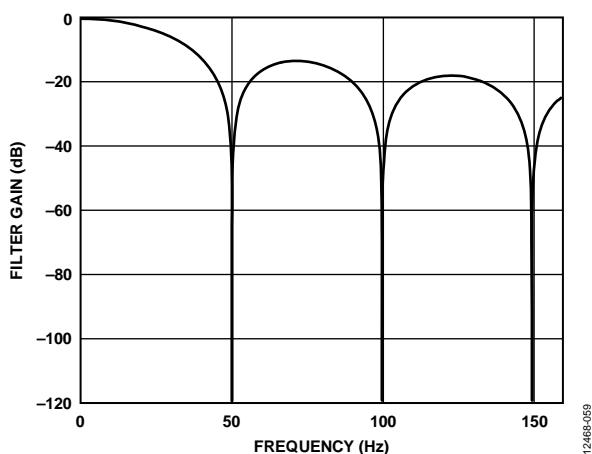

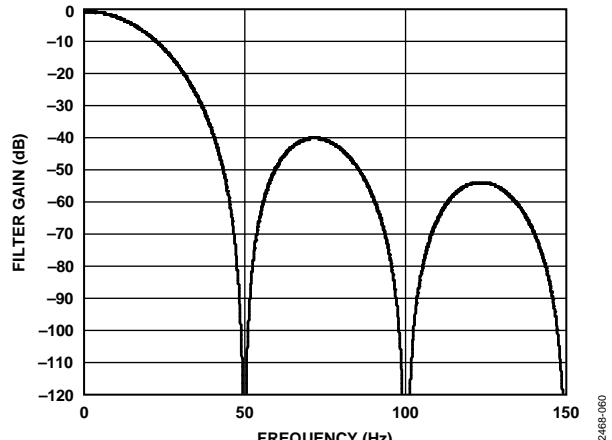

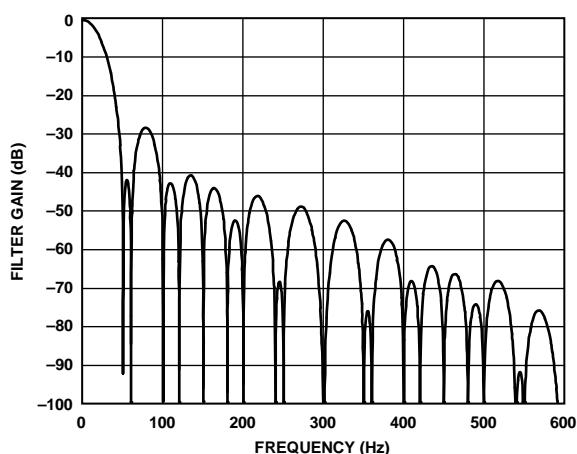

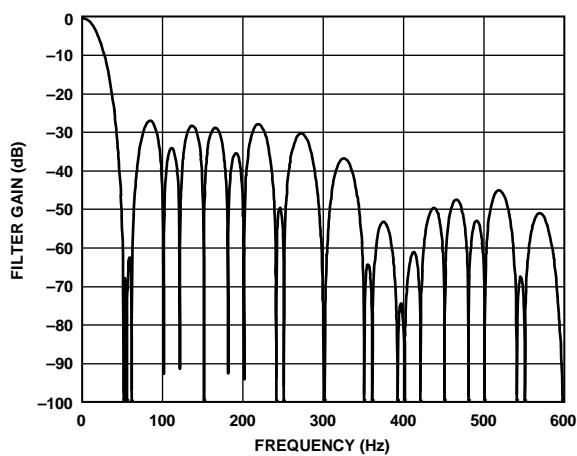

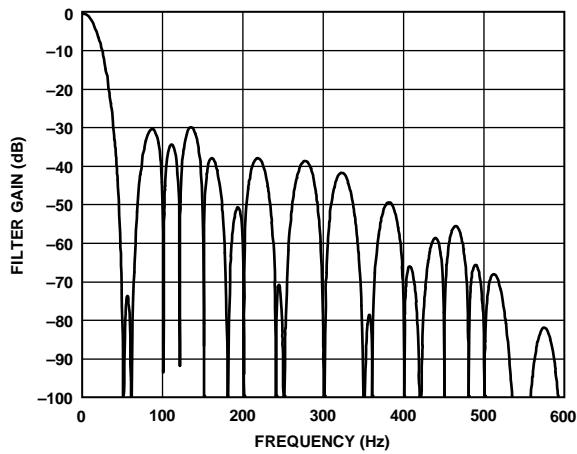

| Sinc5 + Sinc1 フィルタ     | 29 |

| Sinc3 フィルタ             | 29 |

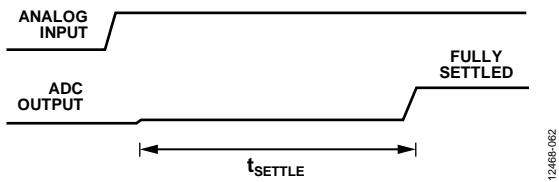

| シングル・サイクル・セトリング        | 30 |

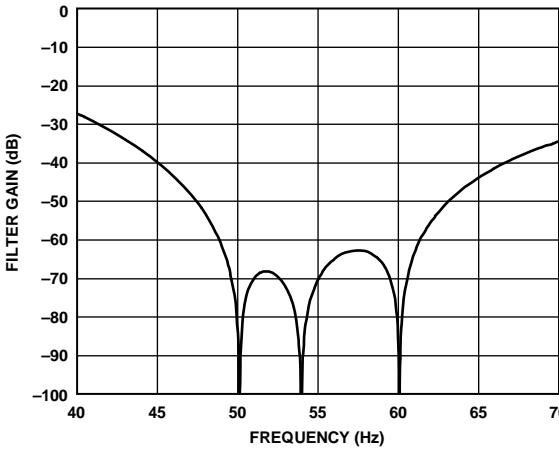

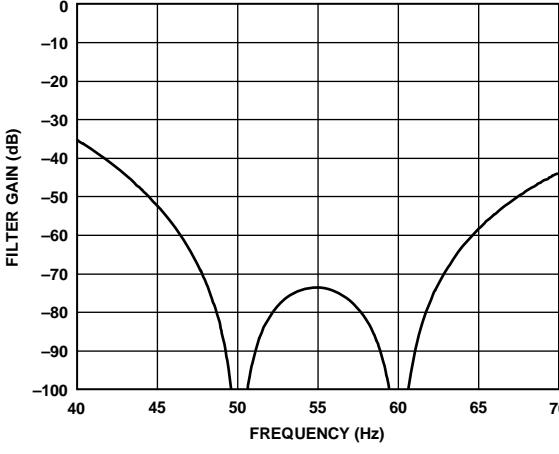

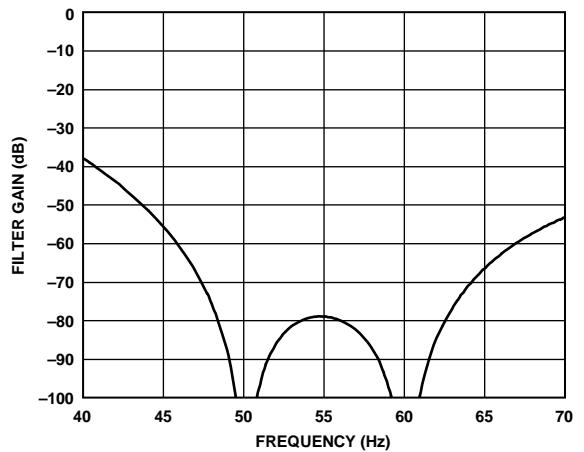

| 強化された 50Hz/60Hz 除去フィルタ | 34 |

| 動作モード                  | 37 |

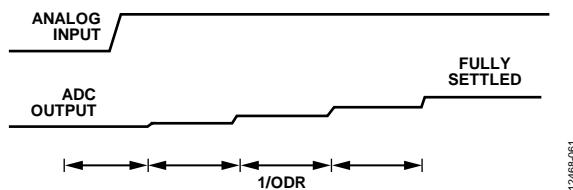

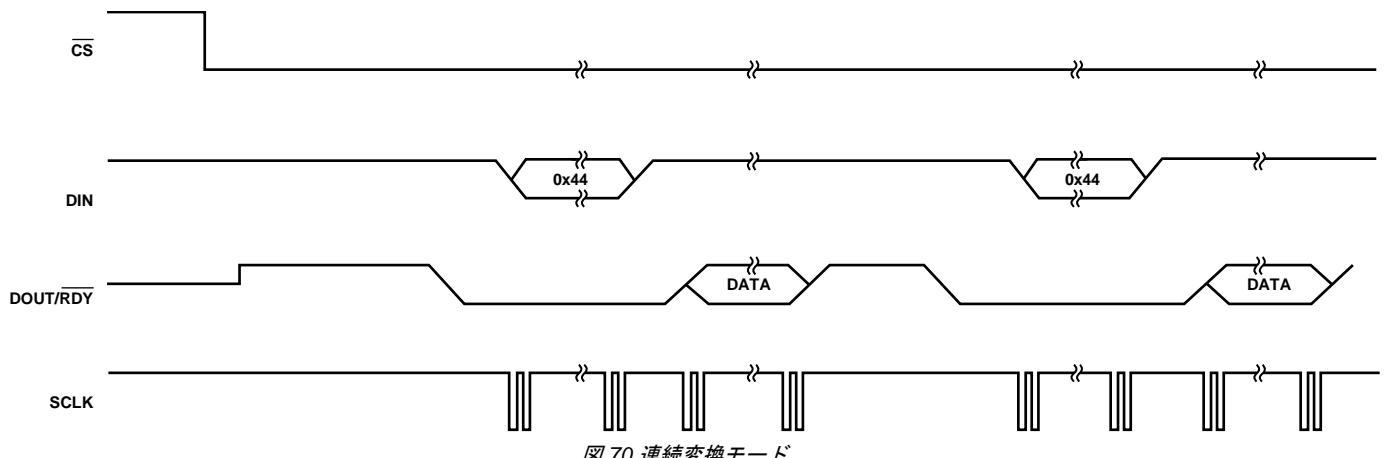

| 連続変換モード                | 37 |

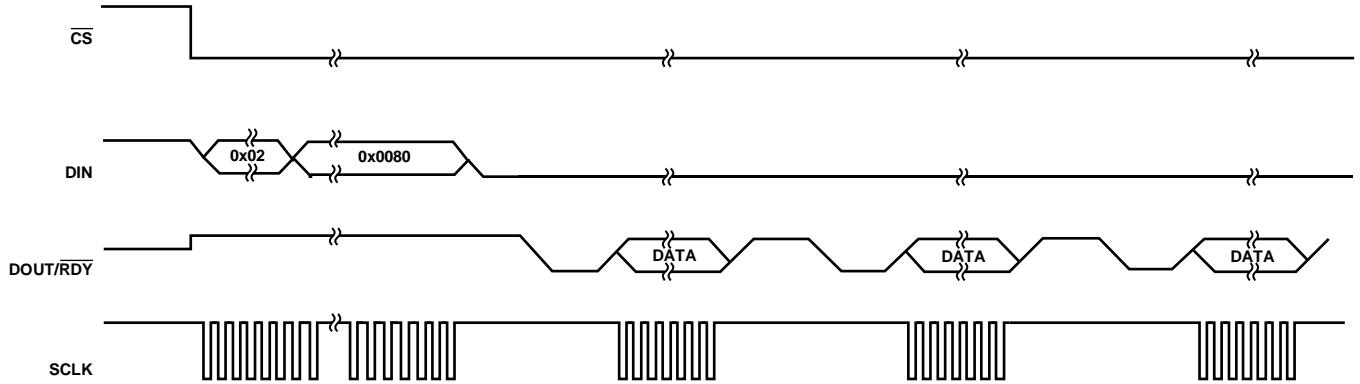

| 連続読み出しモード              | 38 |

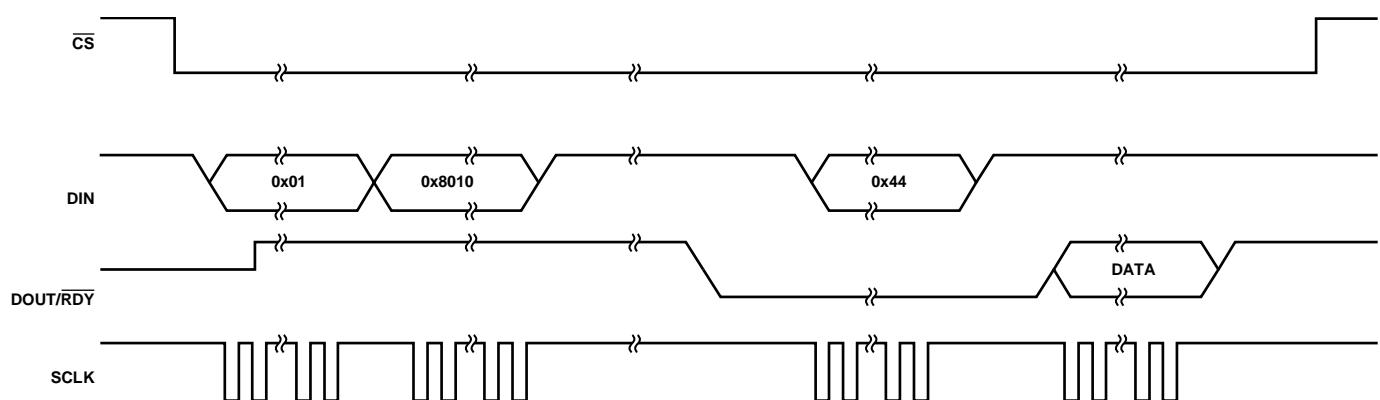

| シングル変換モード              | 39 |

| スタンバイおよびパワーダウン・モード     | 40 |

| キャリブレーション              | 40 |

| デジタル・インターフェース          | 41 |

| チェックサム保護               | 41 |

|                                |    |

|--------------------------------|----|

| CRC の計算                        | 42 |

| 内蔵機能                           | 44 |

| 汎用 I/O                         | 44 |

| 外部マルチブレクサの制御                   | 44 |

| 遅延                             | 44 |

| 16 ビット/24 ビット変換                | 44 |

| DOUT_RESET                     | 44 |

| 同期                             | 44 |

| エラー・フラグ                        | 45 |

| DATA_STAT                      | 45 |

| IOSTRENGTH                     | 46 |

| 内部温度センサー                       | 46 |

| グラウンド接続とレイアウト                  | 47 |

| レジスタの一覧                        | 48 |

| レジスタの詳細                        | 49 |

| コミュニケーション・レジスタ                 | 49 |

| ステータス・レジスタ                     | 50 |

| ADC モード・レジスタ                   | 51 |

| インターフェース・モード・レジスタ              | 52 |

| レジスタ・チェック                      | 53 |

| データ・レジスタ                       | 53 |

| GPIO 設定レジスタ                    | 54 |

| ID レジスタ                        | 55 |

| チャンネル・レジスタ 0                   | 55 |

| チャンネル・レジスタ 1 から チャンネル・レジスタ 3   | 56 |

| アットアップ・レジスタ 0                  | 57 |

| セットアップ・レジスタ 1 から セットアップ・レジスタ 3 | 57 |

| フィルタ設定レジスタ 0                   | 58 |

| フィルタ設定レジスタ 1 から フィルタ設定レジスタ 3   | 59 |

| オフセット設定レジスタ 0                  | 59 |

| オフセット設定レジスタ 1 から オフセット設定レジスタ 3 | 59 |

| ゲイン設定レジスタ 0                    | 59 |

| ゲイン設定レジスタ 1 から ゲイン設定レジスタ 3     | 59 |

| 外形寸法                           | 60 |

| オーダー・ガイド                       | 60 |

## 改訂履歴

9/14—Rev. 0 to Rev. A

Changes to Ordering Guide 60

7/14—Revision 0: Initial Version

## 仕様

特に指定のない限り、AVDD1 = 4.5 V～5.5 V, AVDD2 = 2 V～5.5 V, IOVDD = 2 V～5.5 V, AVSS = DGND = 0V, REF+ = 2.5 V, REF- = AVSS, MCLK = 内部マスター・クロック = 16 MHz、TA = T<sub>MIN</sub> から T<sub>MAX</sub> (-40°C～+105°C)

表 1.

| Parameter                                               | Test Conditions/Comments                                                                                              | Min                 | Typ               | Max                   | Unit                     |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|-----------------------|--------------------------|

| ADC SPEED AND PERFORMANCE                               |                                                                                                                       |                     |                   |                       |                          |

| Output Data Rate (ODR)<br>No Missing Codes <sup>1</sup> | Excluding sinc3 filter at 125 kSPS                                                                                    | 5<br>24             |                   | 250,000               | SPS<br>Bits              |

| Resolution                                              | 表 6 と表 7 参照                                                                                                           |                     |                   |                       |                          |

| Noise                                                   | 表 6 と表 7 参照                                                                                                           |                     |                   |                       |                          |

| ACCURACY                                                |                                                                                                                       |                     |                   |                       |                          |

| Integral Nonlinearity (INL)                             | Analog input buffers enabled<br>Analog input buffers disabled                                                         |                     | ±3.5<br>±1        | ±7.8<br>±3.5          | ppm of FSR<br>ppm of FSR |

| Offset Error <sup>2</sup>                               | Internal short                                                                                                        |                     | ±40               |                       | μV                       |

| Offset Drift                                            | Internal short                                                                                                        |                     | ±80               |                       | nV/°C                    |

| Gain Error <sup>2</sup>                                 |                                                                                                                       |                     | ±35               | ±85                   | ppm of FSR               |

| Gain Drift                                              |                                                                                                                       |                     | ±0.4              | ±0.75                 | ppm/°C                   |

| REJECTION                                               |                                                                                                                       |                     |                   |                       |                          |

| Power Supply Rejection                                  | AVDD1, AVDD2, V <sub>IN</sub> = 1 V                                                                                   |                     | 95                |                       | dB                       |

| Common-Mode Rejection<br>At DC                          | V <sub>IN</sub> = 0.1 V                                                                                               | 95                  |                   |                       | dB                       |

| At 50 Hz, 60 Hz <sup>1</sup>                            | 20 Hz output data rate (post filter),<br>50 Hz ± 1 Hz and 60 Hz ± 1 Hz                                                | 120                 |                   |                       | dB                       |

| Normal Mode Rejection <sup>1</sup>                      | 50 Hz ± 1 Hz and 60 Hz ± 1 Hz<br>Internal clock, 20 SPS ODR (post filter)<br>External clock, 20 SPS ODR (post filter) | 71<br>85            | 90<br>90          |                       | dB                       |

| ANALOG INPUTS                                           |                                                                                                                       |                     |                   |                       |                          |

| Differential Input Range                                | V <sub>REF</sub> = (REF+) - (REF-)                                                                                    |                     | ±V <sub>REF</sub> |                       | V                        |

| Absolute AIN Voltage Limits <sup>1</sup>                |                                                                                                                       | AVSS - 0.05<br>AVSS |                   | AVDD1 + 0.05<br>AVDD1 | V<br>V                   |

| Input Buffers Disabled                                  |                                                                                                                       |                     |                   |                       |                          |

| Input Buffers Enabled                                   |                                                                                                                       |                     |                   |                       |                          |

| Analog Input Current                                    |                                                                                                                       |                     |                   |                       |                          |

| Input Buffers Disabled                                  |                                                                                                                       |                     | ±48               |                       | μA/V                     |

| Input Current                                           |                                                                                                                       |                     | ±0.75             |                       | nA/V/°C                  |

| Input Current Drift                                     | External clock<br>Internal clock (±2.5% clock)                                                                        |                     | ±4                |                       | nA/V/°C                  |

| Input Buffers Enabled                                   |                                                                                                                       |                     |                   |                       |                          |

| Input Current                                           |                                                                                                                       |                     | ±30               |                       | nA                       |

| Input Current Drift                                     | AVDD1 - 0.2 V to AVSS + 0.2 V<br>AVDD1 - AVSS                                                                         |                     | ±75<br>±1         |                       | pA/°C<br>nV/°C           |

| Crosstalk                                               | 1 kHz input                                                                                                           |                     | -120              |                       | dB                       |

| INTERNAL REFERENCE                                      |                                                                                                                       |                     |                   |                       |                          |

| Output Voltage                                          | 100 nF external capacitor to AVSS                                                                                     |                     |                   |                       | V                        |

| Initial Accuracy <sup>3</sup>                           | REFOUT with respect to AVSS                                                                                           |                     |                   |                       | % of V                   |

| Temperature Coefficient<br>0°C～105°C                    | REFOUT, TA = 25°C                                                                                                     | -0.12               | 2.5               | +0.12                 |                          |

| -40°C～+105°C                                            |                                                                                                                       |                     | ±2                | ±5                    | ppm/°C                   |

| Reference Load Current,<br>I <sub>LOAD</sub>            |                                                                                                                       |                     | ±3                | ±10                   | ppm/°C                   |

| Power Supply Rejection                                  | AVDD1, AVDD2, (line regulation)                                                                                       |                     | 90                |                       | mA                       |

| Load Regulation                                         | ΔV <sub>OUT</sub> /ΔI <sub>LOAD</sub>                                                                                 |                     | 32                |                       | ppm/mA                   |

| Voltage Noise                                           | e <sub>N</sub> , 0.1 Hz to 10 Hz, 2.5 V reference                                                                     |                     | 4.5               |                       | μV rms                   |

| Parameter                                | Test Conditions/Comments                  | Min                | Typ       | Max          | Unit                                |

|------------------------------------------|-------------------------------------------|--------------------|-----------|--------------|-------------------------------------|

| Voltage Noise Density                    | $e_N$ , 1 kHz, 2.5 V reference            |                    | 215       |              | nV/ $\sqrt{\text{Hz}}$              |

| Turn-On Settling Time                    | 100 nF REFOUT capacitor                   |                    | 200       |              | $\mu\text{s}$                       |

| Short-Circuit Current, $I_{SC}$          |                                           |                    | 25        |              | mA                                  |

| EXTERNAL REFERENCE INPUTS                |                                           |                    |           |              |                                     |

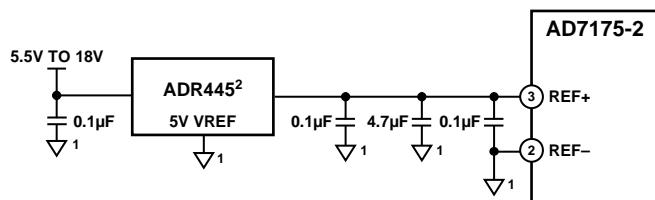

| Differential Input Range                 | $V_{REF} = (\text{REF+}) - (\text{REF-})$ | 1                  | 2.5       | AVDD1        | V                                   |

| Absolute AIN Voltage Limits <sup>1</sup> |                                           | AVSS - 0.05        |           | AVDD1 + 0.05 | V                                   |

| Input Buffers Disabled                   |                                           | AVSS               |           | AVDD1        | V                                   |

| Input Buffers Enabled                    |                                           |                    |           |              |                                     |

| REFIN Input Current                      |                                           |                    |           |              |                                     |

| Input Buffers Disabled                   |                                           |                    | $\pm 72$  |              | $\mu\text{A}/\text{V}$              |

| Input Current                            |                                           |                    | $\pm 1.2$ |              | $\text{nA}/\text{V}/^\circ\text{C}$ |

| Input Current Drift                      |                                           |                    | $\pm 6$   |              | $\text{nA}/\text{V}/^\circ\text{C}$ |

| Input Buffers Enabled                    |                                           |                    | $\pm 800$ |              | nA                                  |

| Input Current                            |                                           |                    | 1.25      |              | $\text{nA}/\text{V}/^\circ\text{C}$ |

| Input Current Drift                      |                                           |                    |           |              |                                     |

| Normal Mode Rejection <sup>1</sup>       | See the Rejection parameter               |                    | 95        |              | dB                                  |

| Common-Mode Rejection                    |                                           |                    |           |              |                                     |

| TEMPERATURE SENSOR                       |                                           |                    |           |              |                                     |

| Accuracy                                 | After user calibration at 25°C            |                    | $\pm 2$   |              | °C                                  |

| Sensitivity                              |                                           |                    | 477       |              | $\mu\text{V}/\text{K}$              |

| BURNOUT CURRENTS                         |                                           |                    |           |              |                                     |

| Source/Sink Current                      | Analog input buffers must be enabled      |                    | $\pm 10$  |              | $\mu\text{A}$                       |

| GENERAL-PURPOSE I/O (GPIO0, GPIO1)       | With respect to AVSS                      |                    |           |              |                                     |

| Input Mode Leakage Current <sup>1</sup>  |                                           | -10                |           | +10          | $\mu\text{A}$                       |

| Floating State Output Capacitance        |                                           |                    | 5         |              | pF                                  |

| Output High Voltage, $V_{OH}^1$          | $I_{SOURCE} = 200 \mu\text{A}$            | AVSS + 4           |           |              | V                                   |

| Output Low Voltage, $V_{OL}^1$           | $I_{SINK} = 800 \mu\text{A}$              |                    |           | AVSS + 0.4   | V                                   |

| Input High Voltage, $V_{IH}^1$           |                                           | AVSS + 3           |           |              | V                                   |

| Input Low Voltage, $V_{IL}^1$            |                                           |                    |           | AVSS + 0.7   | V                                   |

| CLOCK                                    |                                           |                    |           |              |                                     |

| Internal Clock                           |                                           |                    |           |              |                                     |

| Frequency                                |                                           |                    | 16        |              | MHz                                 |

| Accuracy                                 |                                           | -2.5%              |           | +2.5%        | %                                   |

| Duty Cycle                               |                                           | 50                 |           |              | %                                   |

| Output Low Voltage, $V_{OL}$             |                                           |                    |           | 0.4          | V                                   |

| Output High Voltage, $V_{OH}$            |                                           | 0.8 $\times$ IOVDD |           |              | V                                   |

| Crystal                                  |                                           |                    |           |              |                                     |

| Frequency                                |                                           | 14                 | 16        | 16.384       | MHz                                 |

| Startup Time                             |                                           |                    | 10        |              | $\mu\text{s}$                       |

| External Clock (CLKIO)                   |                                           |                    | 16        | 16.384       | MHz                                 |

| Duty Cycle <sup>1</sup>                  |                                           | 30                 | 50        | 70           | %                                   |

# データシート

AD7175-2

| Parameter                          | Test Conditions/Comments                                                                                                                                                                                                             | Min                                                                                 | Typ               | Max                               | Unit          |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------|-----------------------------------|---------------|

| LOGIC INPUTS                       |                                                                                                                                                                                                                                      |                                                                                     |                   |                                   |               |

| Input High Voltage, $V_{INH}^1$    | $2 \text{ V} \leq \text{IOVDD} < 2.3 \text{ V}$                                                                                                                                                                                      | $0.65 \times \text{IOVDD}$                                                          |                   |                                   | V             |

| Input Low Voltage, $V_{INL}^1$     | $2.3 \text{ V} \leq \text{IOVDD} \leq 5.5 \text{ V}$<br>$2 \text{ V} \leq \text{IOVDD} < 2.3 \text{ V}$<br>$2.3 \text{ V} \leq \text{IOVDD} \leq 5.5 \text{ V}$                                                                      | $0.7 \times \text{IOVDD}$                                                           |                   | $0.35 \times \text{IOVDD}$<br>0.7 | V<br>V        |

| Hysteresis <sup>1</sup>            | $\text{IOVDD} \geq 2.7 \text{ V}$<br>$\text{IOVDD} < 2.7 \text{ V}$                                                                                                                                                                  | 0.08<br>0.04                                                                        | 0.25<br>0.2       |                                   | V<br>V        |

| Leakage Currents                   |                                                                                                                                                                                                                                      | -10                                                                                 |                   | +10                               | $\mu\text{A}$ |

| LOGIC OUTPUT (DOUT/RDY)            |                                                                                                                                                                                                                                      |                                                                                     |                   |                                   |               |

| Output High Voltage, $V_{OH}^1$    | $\text{IOVDD} \geq 4.5 \text{ V}, I_{\text{SOURCE}} = 1 \text{ mA}$<br>$2.7 \text{ V} \leq \text{IOVDD} < 4.5 \text{ V}, I_{\text{SOURCE}} = 500 \mu\text{A}$<br>$\text{IOVDD} < 2.7 \text{ V}, I_{\text{SOURCE}} = 200 \mu\text{A}$ | $0.8 \times \text{IOVDD}$<br>$0.8 \times \text{IOVDD}$<br>$0.8 \times \text{IOVDD}$ |                   |                                   | V<br>V<br>V   |

| Output Low Voltage, $V_{OL}^1$     | $\text{IOVDD} \geq 4.5 \text{ V}, I_{\text{SINK}} = 2 \text{ mA}$<br>$2.7 \text{ V} \leq \text{IOVDD} < 4.5 \text{ V}, I_{\text{SINK}} = 1 \text{ mA}$<br>$\text{IOVDD} < 2.7 \text{ V}, I_{\text{SINK}} = 400 \mu\text{A}$          |                                                                                     | 0.4<br>0.4<br>0.4 |                                   | V<br>V<br>V   |

| Leakage Current                    | Floating state                                                                                                                                                                                                                       | -10                                                                                 |                   | +10                               | $\mu\text{A}$ |

| Output Capacitance                 | Floating state                                                                                                                                                                                                                       |                                                                                     | 10                |                                   | pF            |

| SYSTEM CALIBRATION <sup>1</sup>    |                                                                                                                                                                                                                                      |                                                                                     |                   |                                   |               |

| Full-Scale (FS) Calibration Limit  |                                                                                                                                                                                                                                      |                                                                                     |                   | 1.05 × FS                         | V             |

| Zero-Scale Calibration Limit       |                                                                                                                                                                                                                                      | -1.05 × FS                                                                          |                   |                                   | V             |

| Input Span                         |                                                                                                                                                                                                                                      | 0.8 × FS                                                                            |                   | 2.1 × FS                          | V             |

| POWER REQUIREMENTS                 |                                                                                                                                                                                                                                      |                                                                                     |                   |                                   |               |

| Power Supply Voltage               |                                                                                                                                                                                                                                      |                                                                                     |                   |                                   |               |

| AVDD1 to AVSS                      |                                                                                                                                                                                                                                      | 4.5                                                                                 |                   | 5.5                               | V             |

| AVDD2 to AVSS                      |                                                                                                                                                                                                                                      | 2                                                                                   |                   | 5.5                               | V             |

| AVSS to DGND                       |                                                                                                                                                                                                                                      | -2.75                                                                               |                   | 0                                 | V             |

| IOVDD to DGND                      |                                                                                                                                                                                                                                      | 2                                                                                   |                   | 5.5                               | V             |

| IOVDD to AVSS                      | For $\text{AVSS} < \text{DGND}$                                                                                                                                                                                                      |                                                                                     |                   | 6.35                              | V             |

| POWER SUPPLY CURRENTS <sup>4</sup> | All outputs unloaded, digital inputs connected to IOVDD or DGND                                                                                                                                                                      |                                                                                     |                   |                                   |               |

| Full Operating Mode                |                                                                                                                                                                                                                                      |                                                                                     |                   |                                   |               |

| AVDD1 Current                      | Analog input and reference input buffers disabled, external reference                                                                                                                                                                |                                                                                     | 1.4               | 1.65                              | mA            |

|                                    | Analog input and reference input buffers disabled, internal reference                                                                                                                                                                |                                                                                     | 1.75              | 2                                 | mA            |

|                                    | Analog input and reference input buffers enabled, external reference                                                                                                                                                                 |                                                                                     | 13                | 16                                | mA            |

|                                    | Each buffer: AIN+, AIN-, REF+, REF-                                                                                                                                                                                                  |                                                                                     | 2.9               |                                   | mA            |

| AVDD2 Current                      | External reference                                                                                                                                                                                                                   |                                                                                     | 4.5               | 5                                 | mA            |

|                                    | Internal reference                                                                                                                                                                                                                   |                                                                                     | 4.75              | 5.2                               | mA            |

| IOVDD Current                      | External clock                                                                                                                                                                                                                       |                                                                                     | 2.5               | 2.8                               | mA            |

|                                    | Internal Clock                                                                                                                                                                                                                       |                                                                                     | 2.75              | 3.1                               | mA            |

|                                    | External crystal                                                                                                                                                                                                                     |                                                                                     | 3                 |                                   | mA            |

| Standby (LDO on)                   | Internal reference off, total current consumption                                                                                                                                                                                    |                                                                                     | 25                |                                   | $\mu\text{A}$ |

|                                    | Internal reference on, total current consumption                                                                                                                                                                                     |                                                                                     | 425               |                                   | $\mu\text{A}$ |

| Power-Down Mode                    | Full power-down (including LDO and internal reference)                                                                                                                                                                               |                                                                                     | 5                 | 10                                | $\mu\text{A}$ |

| Parameter                      | Test Conditions/Comments                                                     | Min | Typ | Max | Unit |

|--------------------------------|------------------------------------------------------------------------------|-----|-----|-----|------|

| POWER DISSIPATION <sup>4</sup> |                                                                              |     |     |     |      |

| Full Operating Mode            | All buffers disabled, external clock and reference, AVDD2 = 2 V, IOVDD = 2 V |     | 21  |     | mW   |

|                                | All buffers disabled, external clock and reference, all supplies = 5 V       |     | 42  |     | mW   |

|                                | All buffers disabled, external clock and reference, all supplies = 5.5 V     |     | 52  |     | mW   |

|                                | All buffers enabled, internal clock and reference, AVDD2 = 2 V, IOVDD = 2 V  |     | 82  |     | mW   |

|                                | All buffers enabled, internal clock and reference, all supplies = 5 V        |     | 105 |     | mW   |

|                                | All buffers enabled, internal clock and reference, all supplies = 5.5 V      |     | 136 |     | mW   |

| Standby Mode                   | Reference off, all supplies = 5 V                                            |     | 125 |     | μW   |

|                                | Internal reference on, all supplies = 5 V                                    |     | 2.2 |     | mW   |

| Power-Down Mode                | Full power-down, all supplies = 5 V                                          | 25  | 50  |     | μW   |

<sup>1</sup> これらの値は、出荷テストを行いませんが、設計および／または量産開始時のキャラクタライゼーション・データにより保証します。

<sup>2</sup> システムもしくは内蔵ゼロスケールのキャリブレーション手順に従えば、オフセット誤差は、プログラムされた出力データレートにおけるノイズ・レベルとほぼ同等になります。システム・フルスケール・キャリブレーションは、ゲイン誤差をプログラムされた出力データレートのノイズ・レベルと同等レベルにまで減少させることができます。

<sup>3</sup> この仕様は、MSL (Moisture Level) プリコンディショニングの影響を含んでいます。

<sup>4</sup> これらは、REFOUT ピンと、デジタル出力ピンに負荷が接続されていない時の仕様です。

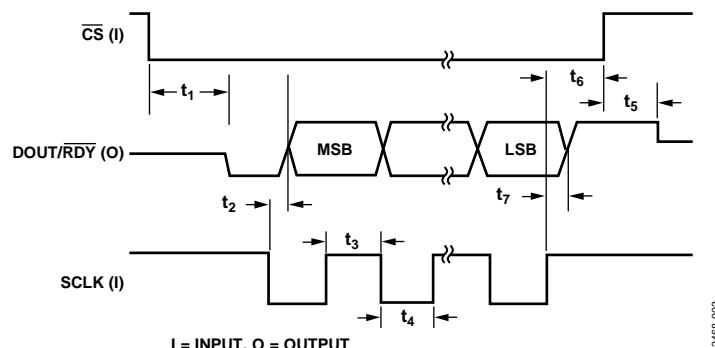

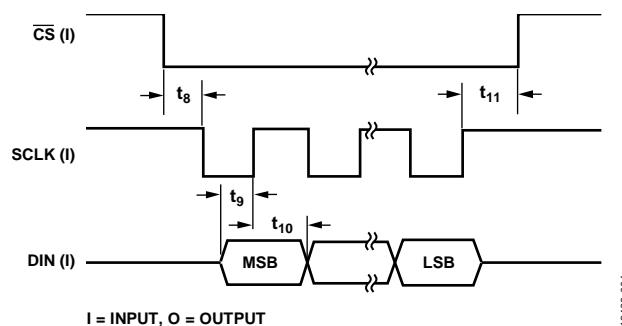

## タイミング特性

特に指定のない限り、IOVDD = 2 V～5.5 V、DGND = 0 V、Input Logic 0 = 0 V、Input Logic 1 = IOVDD、C<sub>LOAD</sub> = 20 pF

表 2

| Parameter                   | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Test Conditions/Comments <sup>1, 2</sup>                    |

|-----------------------------|----------------------------------------------|--------|-------------------------------------------------------------|

| SCLK                        |                                              |        |                                                             |

| t <sub>3</sub>              | 25                                           | ns min | SCLK high pulse width                                       |

| t <sub>4</sub>              | 25                                           | ns min | SCLK low pulse width                                        |

| READ OPERATION              |                                              |        |                                                             |

| t <sub>1</sub>              | 0                                            | ns min | CS falling edge to DOUT/RDY active time                     |

|                             | 15                                           | ns max | IOVDD = 4.75 V to 5.5 V                                     |

|                             | 40                                           | ns max | IOVDD = 2 V to 3.6 V                                        |

| t <sub>2</sub> <sup>3</sup> | 0                                            | ns min | SCLK active edge to data valid delay <sup>4</sup>           |

|                             | 12.5                                         | ns max | IOVDD = 4.75 V to 5.5 V                                     |

|                             | 25                                           | ns max | IOVDD = 2 V to 3.6 V                                        |

| t <sub>5</sub> <sup>5</sup> | 2.5                                          | ns min | Bus relinquish time after CS inactive edge                  |

|                             | 20                                           | ns max |                                                             |

| t <sub>6</sub>              | 0                                            | ns min | SCLK inactive edge to CS inactive edge                      |

| t <sub>7</sub>              | 10                                           | ns min | SCLK inactive edge to DOUT/RDY high/low                     |

| WRITE OPERATION             |                                              |        |                                                             |

| t <sub>8</sub>              | 0                                            | ns min | CS falling edge to SCLK active edge setup time <sup>4</sup> |

| t <sub>9</sub>              | 8                                            | ns min | Data valid to SCLK edge setup time                          |

| t <sub>10</sub>             | 8                                            | ns min | Data valid to SCLK edge hold time                           |

| t <sub>11</sub>             | 5                                            | ns min | CS rising edge to SCLK edge hold time                       |

<sup>1</sup> 初期リリース時にサンプル・テストにより適合性を保証。

<sup>2</sup> 図 2 及び図 3 参照。

<sup>3</sup> このパラメータは、出力が V<sub>OL</sub> もしくは V<sub>OH</sub> を横切るために要する時間で定義されています。

<sup>4</sup> SCLK のアクティブ・エッジとは、SCLK の立ち下がりエッジを意味します。

<sup>5</sup> データ・レジスタを読み出した後、DOUT/RDY はハイ・レベルに戻ります。シングル変換モードおよび連続変換モードで、DOUT/RDY がハイ・レベルの間に、必要ならば、同一データを再度読み出すことができますが、2 回目以降の読み出しは次の出力更新が近いところで読み出さないように注意してください。連続読み出しモードでは、デジタル・ワードは 1 回しか読み出すことができません。

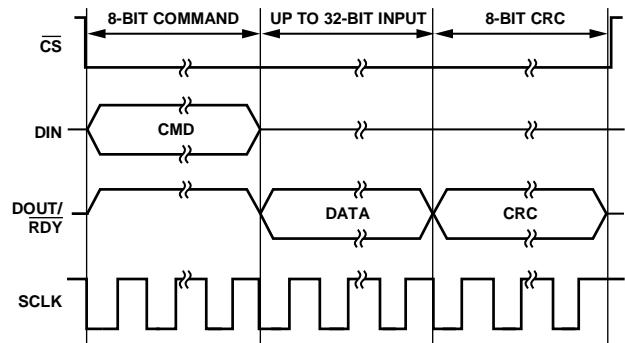

## タイミング図

図2.読み出しサイクルのタイミング図

図3.書き込みサイクルのタイミング図

## 絶対最大定格

特に指定のない限り、 $T_A = 25^\circ\text{C}$

表 3.

| Parameter                          | Rating                  |

|------------------------------------|-------------------------|

| AVDD1, AVDD2 to AVSS               | -0.3 V ~ +6.5 V         |

| AVDD1 to DGND                      | -0.3 V ~ +6.5 V         |

| IOVDD to DGND                      | -0.3 V ~ +6.5 V         |

| IOVDD to AVSS                      | -0.3 V ~ +7.5 V         |

| AVSS to DGND                       | -3.25 V ~ +0.3 V        |

| Analog Input Voltage to AVSS       | -0.3 V to AVDD1 + 0.3 V |

| Reference Input Voltage to AVSS    | -0.3 V to AVDD1 + 0.3 V |

| Digital Input Voltage to DGND      | -0.3 V to IOVDD + 0.3 V |

| Digital Output Voltage to DGND     | -0.3 V to IOVDD + 0.3 V |

| Analog Input/Digital Input Current | 10A                     |

| Operating Temperature Range        | -40°C ~ +105°C          |

| Storage Temperature Range          | -65°C ~ +150°C          |

| Maximum Junction Temperature       | 150°C                   |

| Lead Soldering, Reflow Temperature | 260°C                   |

| ESD Rating (HBM)                   | 4 kV                    |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作の節に記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

## 熱抵抗

$\theta_{JA}$  は、表面実装用 JEDEC テスト・ボードにハンダ付けされたデバイスで規定されています。

表 4. 热抵抗

| Package Type     | $\theta_{JA}$ | Unit |

|------------------|---------------|------|

| 24 ピン TSSOP      |               |      |

| 1 層 JEDEC ボードの場合 | 149           | °C/W |

| 2 層 JEDEC ボードの場合 | 81            | °C/W |

## ESD の注意

### ESD (electrostatic discharge) sensitive device.

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

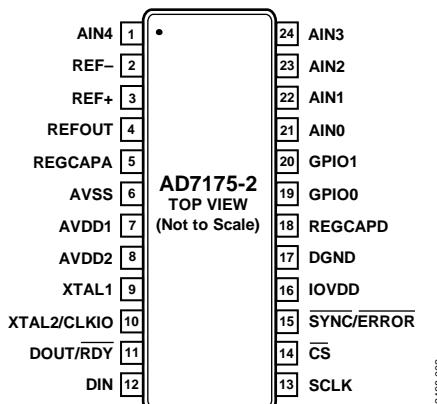

## ピン配置およびピン機能説明

図 4. ピン配置

表 5. ピン機能の説明

| Pin No. | Mnemonic    | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | AIN4        | AI                | アナログ入力 4 : クロスポイント・マルチプレクサから選択可能。                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2       | REF -       | AI                | リファレンス入力、負側入力ピン。REF - の範囲は AVSS~AVDD1 - 1V です。                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3       | REF +       | AI                | リファレンス入力、正側入力ピン。外部リファレンス電圧は、REF+ と REF-との間に入力することができます。REF + の範囲は、AVSS+1V~AVDD1 です。このデバイスは、1V~AVDD1 のリファレンス電圧で動作します。                                                                                                                                                                                                                                                                                                                                                 |

| 4       | REFOUT      | AO                | バッファ付き内部リファレンス電圧出力 : 出力は 2.5V で、AVSS を基準としています。                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5       | REGCAPA     | AO                | アナログ LDO レギュレータ出力 : このピンを 1μF と 0.1μF のコンデンサを使って AVSS ヘデカップリングして下さい。                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6       | AVSS        | P                 | 負のアナログ電源 : 電源電圧範囲は 0 から -2.75V で、通常は 0V に設定してください。                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7       | AVDD1       | P                 | アナログ電源 1 : この電圧は、AVSS を基準として、5V±10%にして下さい。                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8       | AVDD2       | P                 | アナログ電源 2 : この電圧は、AVSS を基準として、2V から 5V の範囲に設定してください。                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9       | XTAL1       | AI                | 水晶発振子用入力 1                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10      | XTAL2/CLKIO | AI/DI             | 水晶発振子用入力 2/クロック入力、またはクロック出力。どちらの機能として動作させるかは、ADCMODE レジスタ内の CLOCKSEL ビットで設定します。MCLK 源の選択には、以下の 4 つのオプションがあります：<br>内部発振器 : 外部への出力無し<br>内部発振器出力 : XTAL2/CLKIO へ出力。これは、IOVDD のロジック・レベルで動作します。<br>外部クロック : XTAL2/CLKIO へ入力は、IOVDD ロジック・レベルの信号を与えて下さい。<br>外付け水晶発振子 : XTAL1 と XTAL2/CLKIO ピンとの間に接続します。                                                                                                                                                                     |

| 11      | DOUT/RDY    | DO                | シリアル・データ出力/データ・レディ出力。DOUT/RDY は 2 つの機能を有します。ADC の出力シフト・レジスタにアクセスするときは、シリアル・データ出力ピンとして機能します。出力シフト・レジスタには、内蔵のデータ・レジスタまたはコントロール・レジスタからのデータが格納されます。データ・ワード/コントロール・ワード情報が SCLK の立ち下がりエッジで、DOUT/RDY ピンに送られ、SCLK の立ち上がりエッジで有効になります。CS がハイ・レベルのとき、DOUT/RDY 出力はスリーステートになります。CS がロー・レベルの時、DOUT/RDY は、データ・レディー・ピンとして機能し、変換完了をロー・レベルで示します。変換後、もしデータが読み出されなかった場合、このピンは次のデータ更新の直前にハイ・レベルになり、次の更新が完了するまでハイ・レベルを維持します。DOUT/RDY の立ち下がりエッジは、プロセッサに対する割り込みとして使われ、有効なデータが準備できていることを示します。 |

| 12      | DIN         | DI                | デバイスの入力シフト・レジスタに対するシリアル・データ入力 : このシフト・レジスタ内のデータは、デバイス内のコントロール・レジスタに転送されます。該当するレジスタは、コミュニケーション・レジスタのレジスタ・アドレス (RA) ビットにより指定されます。データは、SCLK の立ち上がりエッジに同期して入力されます。                                                                                                                                                                                                                                                                                                       |

| 13      | SCLK        | DI                | シリアル・クロック入力 : このシリアル・クロック入力は、デバイスとの双方向データ転送の同期用です。SCLK にはシュミット・トリガ入力が内蔵されているため、光アイソレーション・アプリケーションのインターフェースにも適応しています。                                                                                                                                                                                                                                                                                                                                                 |

| 14      | CS          | DI                | チップ・セレクト入力 : アクティブ・ローのロジック入力。このチップへのアクセスを指定するときに使います。CS は、シリアル・バス上に複数のデバイスが存在し、システムが特定のデバイスを選択するときに使います。CS がロー・レベルになると、デバイスとの通信を CLK、DIN、DOUT を使った 3 線で行えるようになります。CS がハイ・レベルのとき、DOUT/RDY 出力はスリーステートになります。                                                                                                                                                                                                                                                            |

| Pin No. | Mnemonic       | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15      | SYNC<br>/ERROR | DI/O              | <p>同期入力または、エラー入出力。このピンの機能は、GPIOCON レジスタで、ロジック入力とロジック出力との切り替えができます。同期入力 (SYNC) がイネーブルの時、このピンを使って、複数の AD7175-2 間のデジタル・フィルタとアナログ変調器との同期を可能にします。詳細は、同期 を参照して下さい。同期入力がディスエーブルの時、このピンは、以下に示す 3 つのモードの内、どれか 1 つの機能を持ちます。</p> <p>アクティブ・ローのエラー入力モード：このモードは、ステータス・レジスタの ADC_ERROR ビットで設定できます。</p> <p>アクティブ・ローのオープン・ドレイン・エラー出力モード：ステータス・レジスタのエラー・ビットのデータが、ERROR 出力に反映されます。複数のデバイスにおける SYNC/ERROR ピンは、共通のプルアップ抵抗で接続することができます。したがって、どのデバイスでエラーが起きても、そのエラーを検知できます。</p> <p>汎用出力モード：このピンの状態は、GPIOCON レジスタの ERR_DAT ビットによって制御されます。このピンは、GPIOx ピンで使われている AVDD1 と AVSS とは違って、IOVDD と DGND 間の電圧を基準としています。この場合、ピンは、アクティブ・プルアップです。</p> |

| 16      | IOVDD          | P                 | デジタル I/O 電源電圧：IOVDD の電圧範囲は、2 V~5 V です。IOVDD は AVDD2 とは独立しています。例えば、AVDD2 に 5V を与えた状態で、IOVDD に 3V を与えて動作させることができます。その逆も可能です。もし AVSS に -2.5 V を与えた場合、IOVDD に与える電圧は 3.6V を超えてはいけません。                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17      | DGND           | P                 | デジタル・グラウンド                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18      | REGCAPD        | AO                | デジタル LDO レギュレータ出力：このピンはデカッピング専用です。このピンは、1 nF と 0.1 μF のコンデンサで DGND へデカッピングしてください。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 19      | GPIO0          | DI/O              | 汎用入出力 0：このピンにおけるロジック入力/出力レベルは、AVDD1 と AVSS を基準としています。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 20      | GPIO1          | DI/O              | 汎用入出力 1：このピンにおけるロジック入力/出力レベルは、AVDD1 と AVSS を基準としています。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 21      | AIN0           | AI                | アナログ入力 0：クロスポイント・マルチプレクサから選択可能。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22      | AIN1           | AI                | アナログ入力 1：クロスポイント・マルチプレクサから選択可能。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 23      | AIN2           | AI                | アナログ入力 2：クロスポイント・マルチプレクサから選択可能。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 24      | AIN3           | AI                | アナログ入力 3：クロスポイント・マルチプレクサから選択可能。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

<sup>1</sup> AI = アナログ入力、AO = アナログ出力、DI = デジタル入力、DO = デジタル出力、DIO = デジタル入力/出力、P = 電源。

## 代表的な性能特性

特に指定のない限り、AVDD1 = 5 V, AVDD2 = 5 V, IOVDD = 3.3 V, TA = 25°C

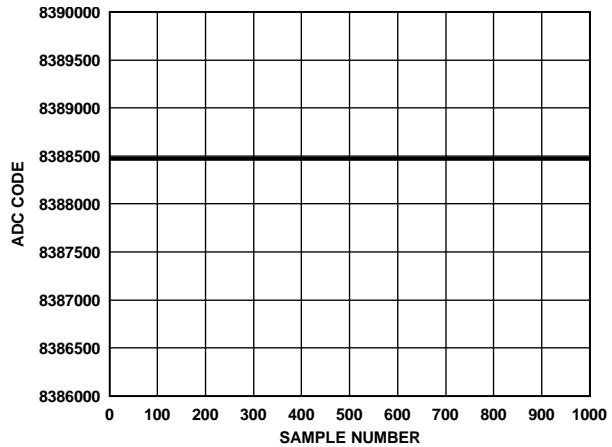

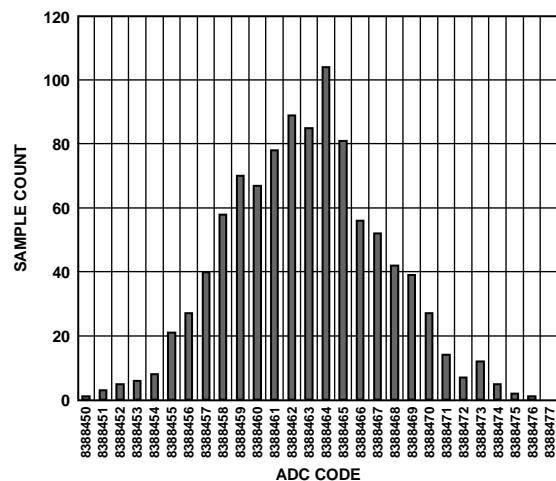

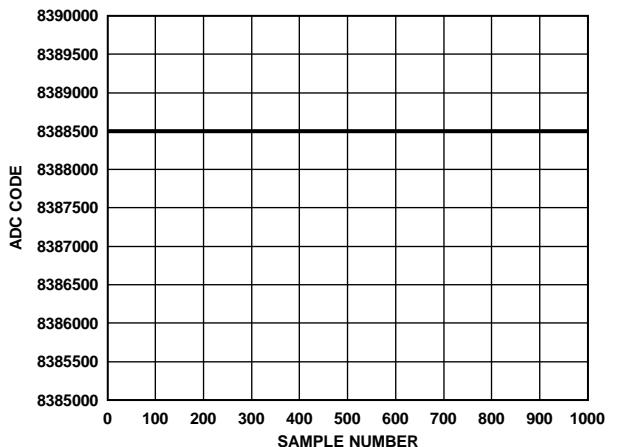

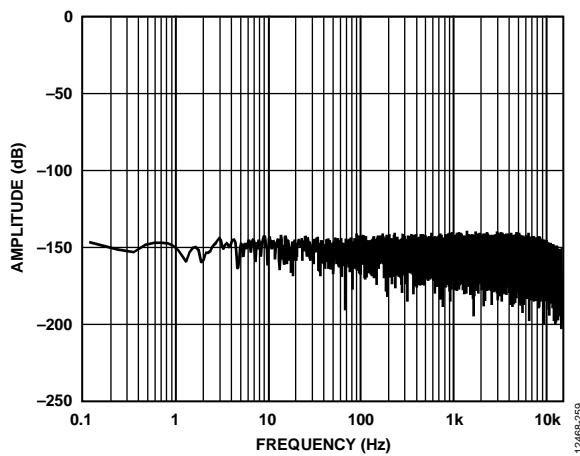

図5.ノイズ

(アナログ入力バッファ・ディスエーブル、 $V_{REF} = 5\text{ V}$ ,

出力データレート = 5 SPS)

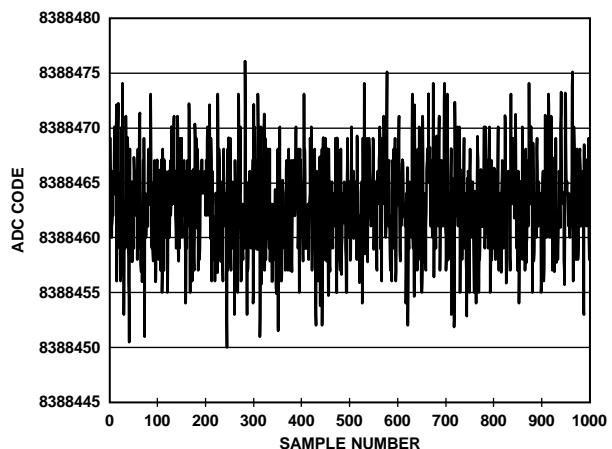

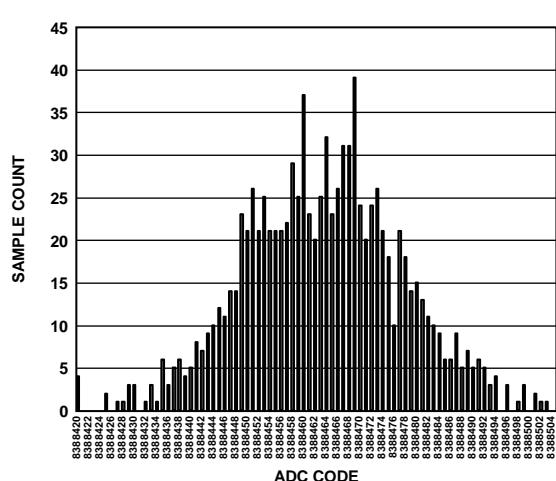

図6.ノイズ

(アナログ入力バッファ・ディスエーブル、 $V_{REF} = 5\text{ V}$ ,

出力データレート = 10 kSPS)

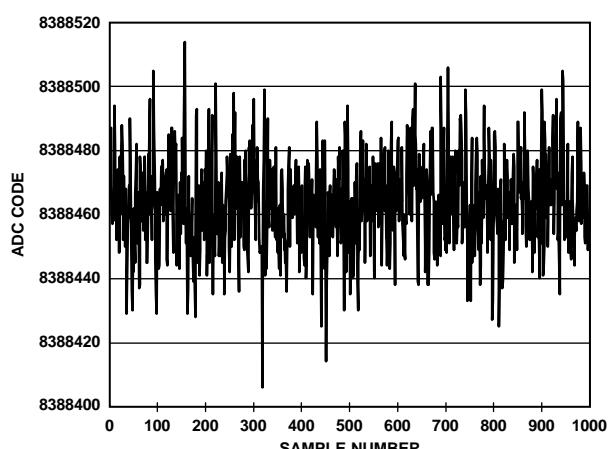

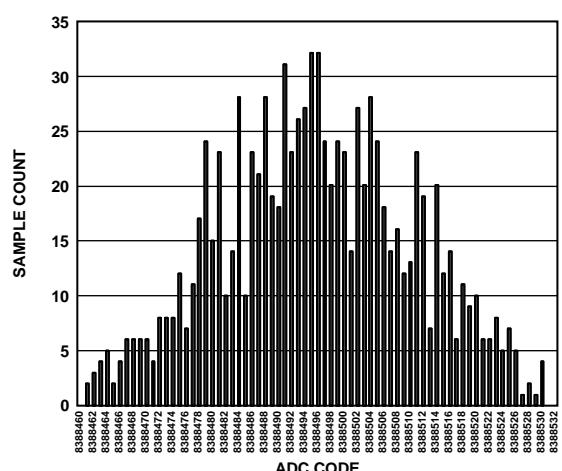

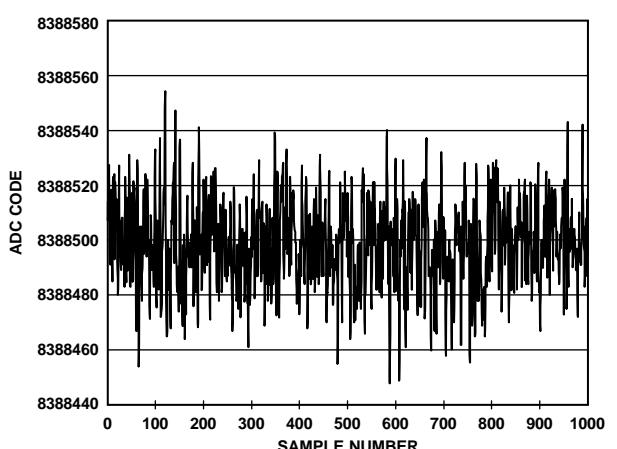

図7.ノイズ

(アナログ入力バッファ・ディスエーブル、 $V_{REF} = 5\text{ V}$ ,

出力データレート = 250 kSPS)

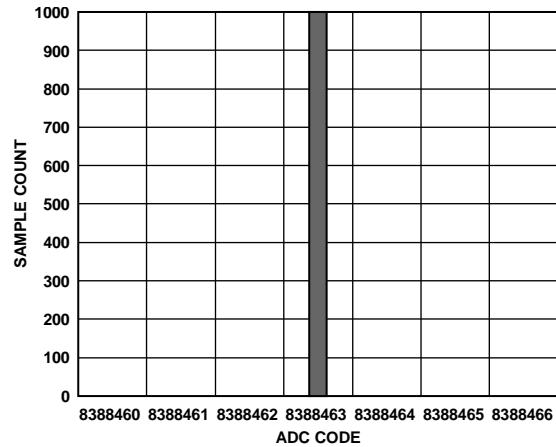

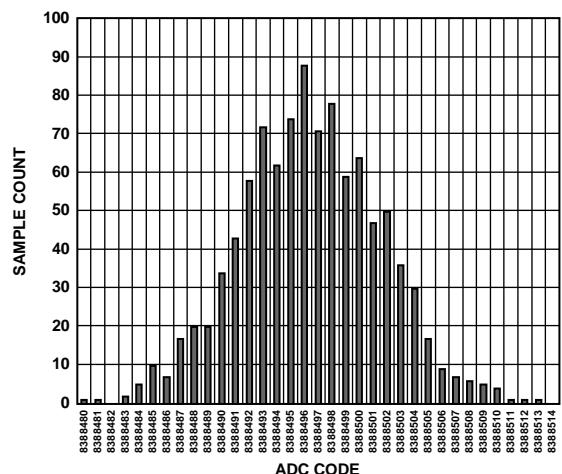

図8.ノイズ分布ヒストグラム

(アナログ入力バッファ・ディスエーブル、 $V_{REF} = 5\text{ V}$ ,

出力データレート = 5 SPS)

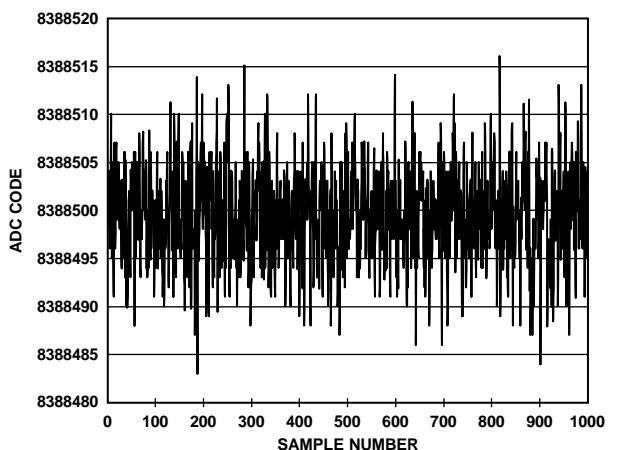

図9.ノイズ分布ヒストグラム

(アナログ入力バッファ・ディスエーブル、 $V_{REF} = 5\text{ V}$ ,

出力データレート = 10 kSPS)

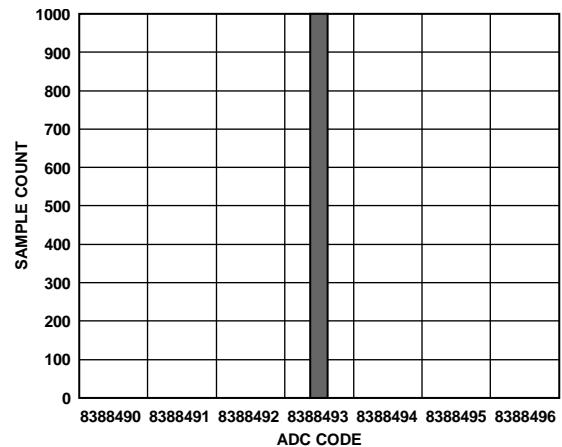

図10.ノイズ分布ヒストグラム

(アナログ入力バッファ・ディスエーブル、 $V_{REF} = 5\text{ V}$ ,

出力データレート = 250 kSPS)

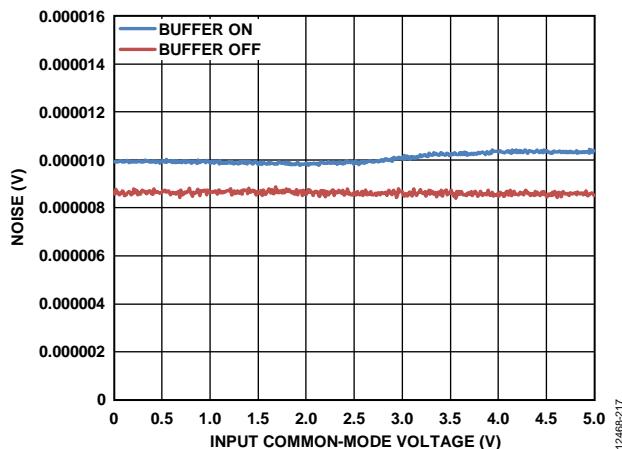

図17.アナログ入力バッファのオン・オフ時における、

入力コモン・モード入力電圧に対するノイズの変化

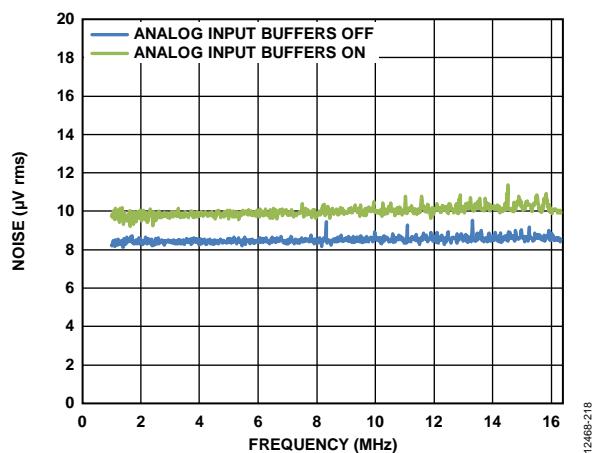

図18.アナログ入力バッファのオン・オフ時における、

外部マスター・クロック周波数に対するノイズ電圧の変化

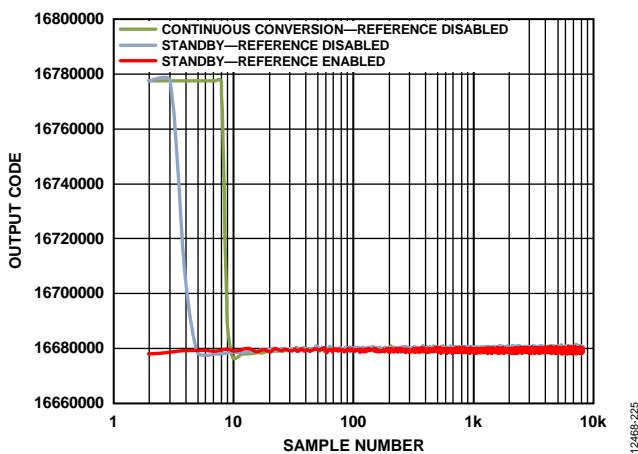

図19.内蔵リファレンス電圧のセトリング時間

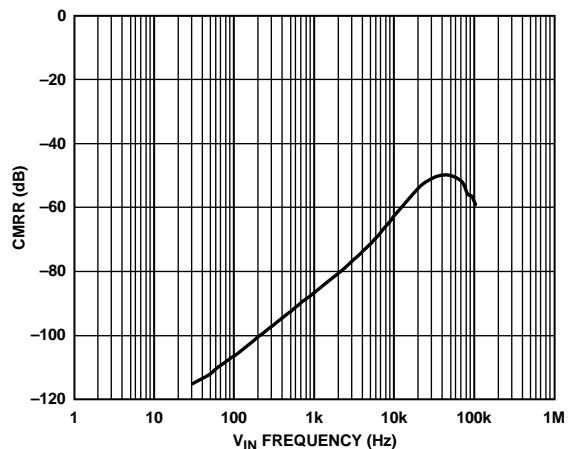

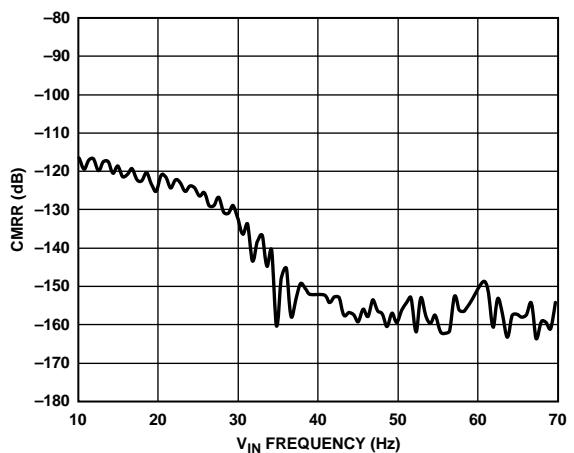

図20. $V_{IN}$ の周波数変化に対するコモン・モード除去比(CMRR)

( $V_{IN} = 0.1$  V, 出力データレート=250 kSPS)

図21. $V_{IN}$ の周波数変化に対するコモン・モード除去比(CMRR)

( $V_{IN} = 0.1$  V, 10 Hz to 70 Hz, 出力データレート=20 SPS 強化フィルタ)

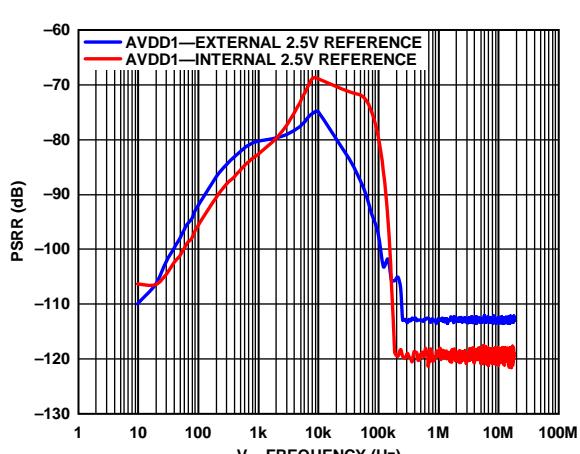

図22. $V_{IN}$ の周波数変化に対する電源変動除去比(PSRR)

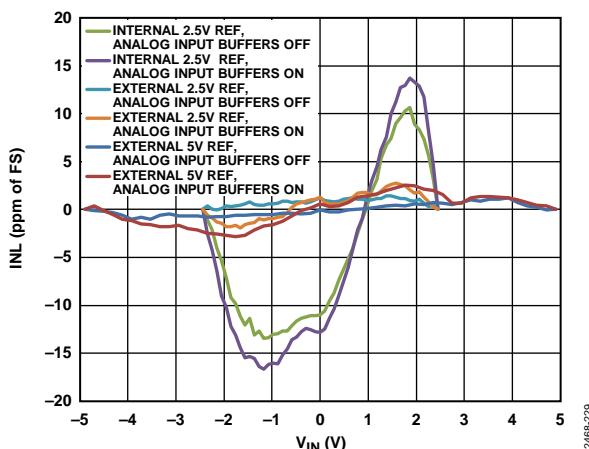

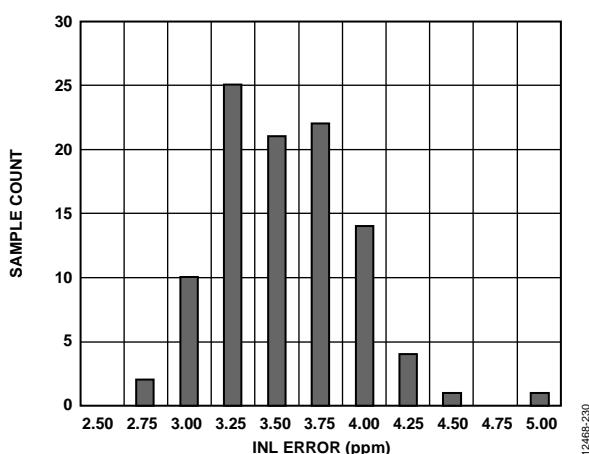

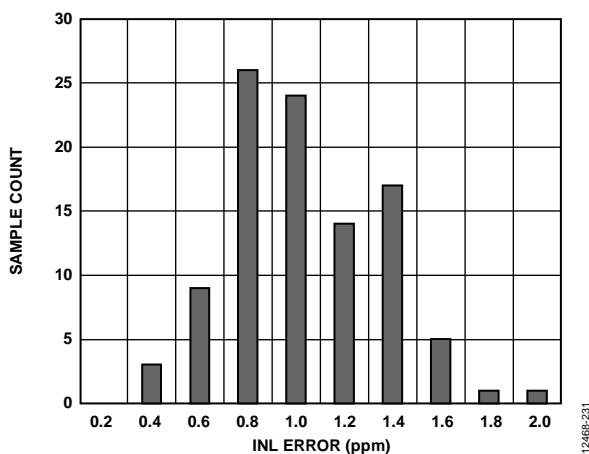

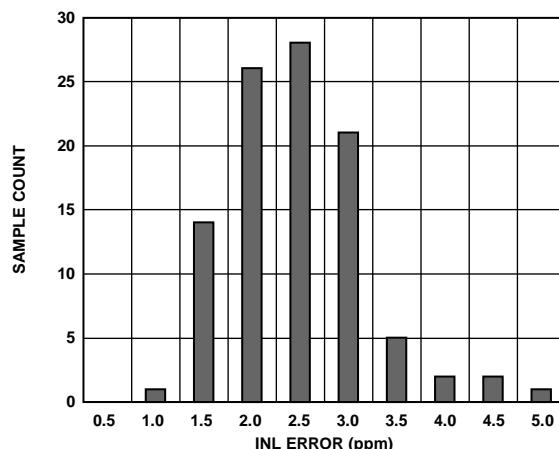

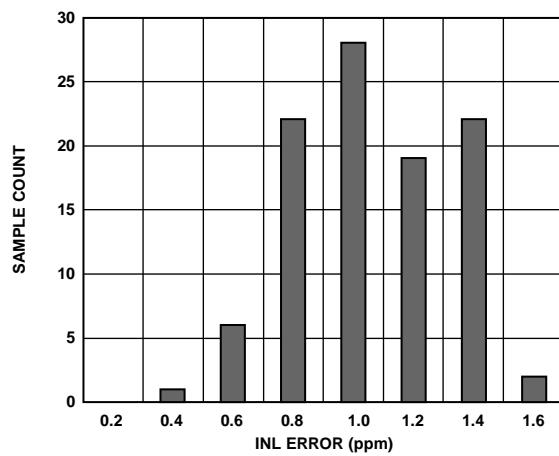

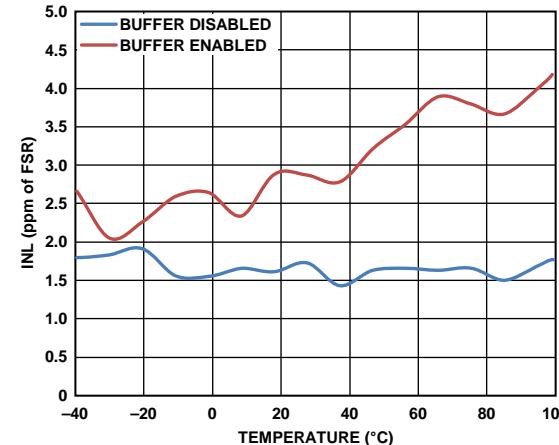

図23. $V_{IN}$  (差動入力) 対 積分非直線性 (INL)図24. 積分非直線性 (INL) 分布ヒストグラム

(差動入力、アナログ入力バッファ・イネーブル、 $V_{REF} = 2.5V$  外部リファレンス電圧、100 ユニット)図25. 積分非直線性 (INL) 分布ヒストグラム

(差動入力、アナログ入力バッファ・ディスエーブル、 $V_{REF} = 2.5V$  外部リファレンス電圧、100 ユニット)図26. 積分非直線性 (INL) 分布ヒストグラム

(差動入力、アナログ入力バッファ・イネーブル、 $V_{REF} = 5V$  外部リファレンス電圧、100 ユニット)図27. 積分非直線性 (INL) 分布ヒストグラム

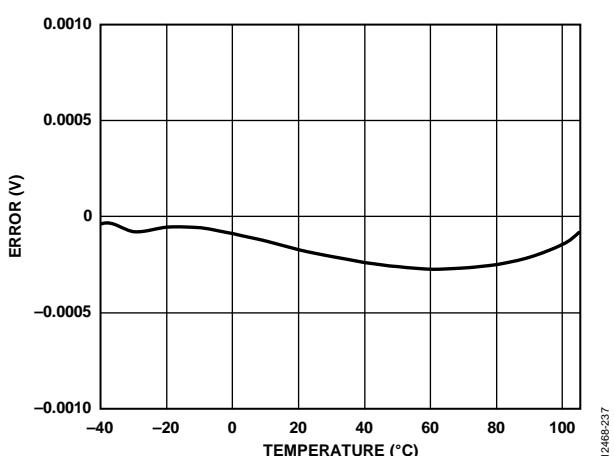

(差動入力、アナログ入力バッファ・ディスエーブル、 $V_{REF} = 5V$  外部リファレンス電圧、100 ユニット)図28. 積分非直線性 (INL) の温度特性

(差動入力  $V_{REF} = 2.5V$  外部リファレンス電圧)

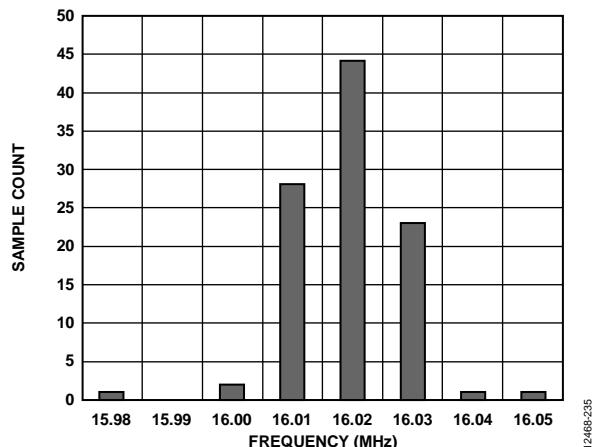

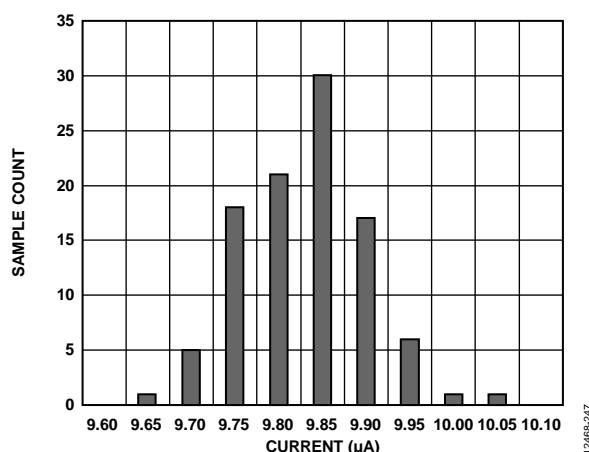

図 29. 内部発振器の周波数精度分布ヒストグラム

(100 ユニット)

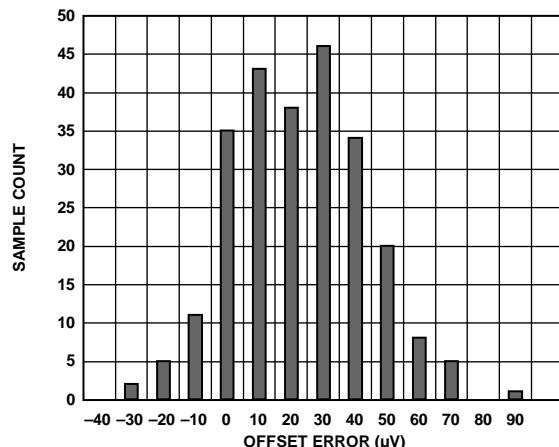

図 32. オフセット・エラー分布ヒストグラム

(内部ショート) (248 ユニット)

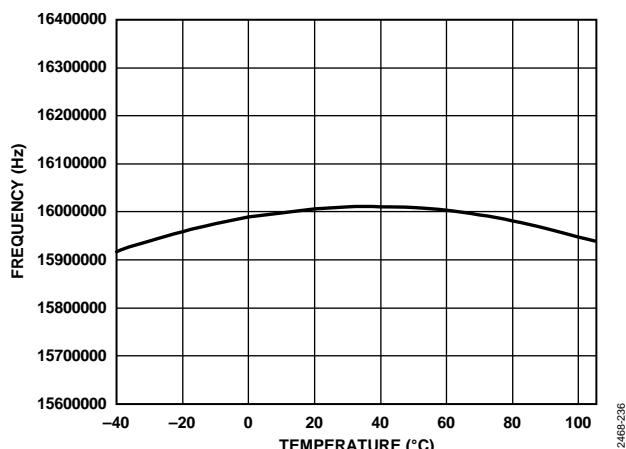

図 30. 内部発振器周波数の温度特性

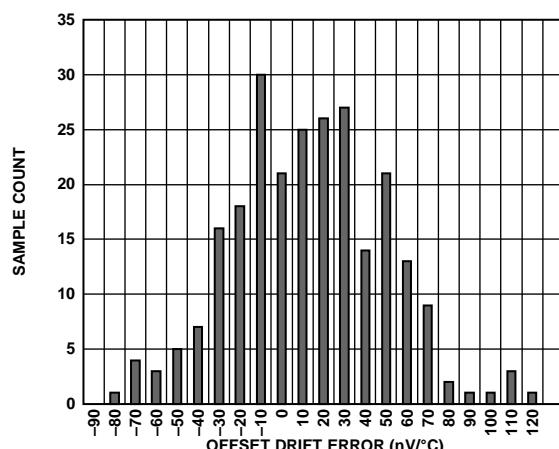

図 33. オフセット・エラー変動分布ヒストグラム

(内部ショート) (248 ユニット)

図 31. リファレンス電圧絶対値誤差の温度特性

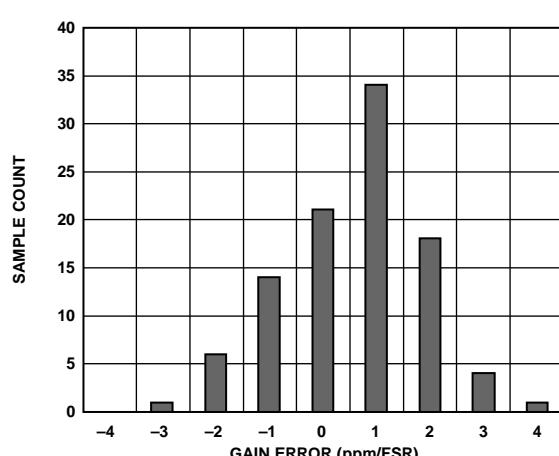

図 34. ゲイン誤差分布ヒストグラム

(アナログ入力バッファ + イネーブル)

(100 ユニット)

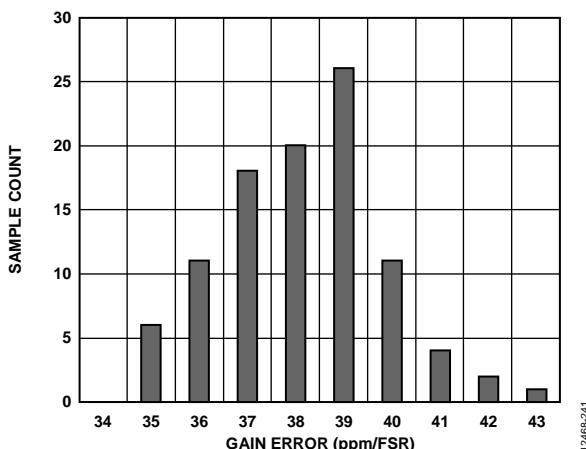

図 35. ゲイン誤差分布ヒストグラム

(アナログ入力バッファ・ディスエーブル、100 ユニット)

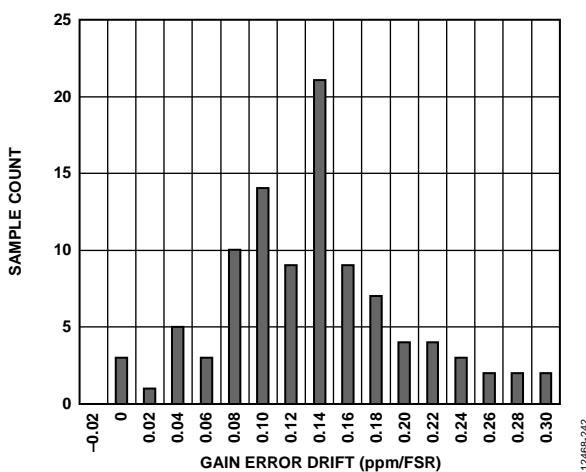

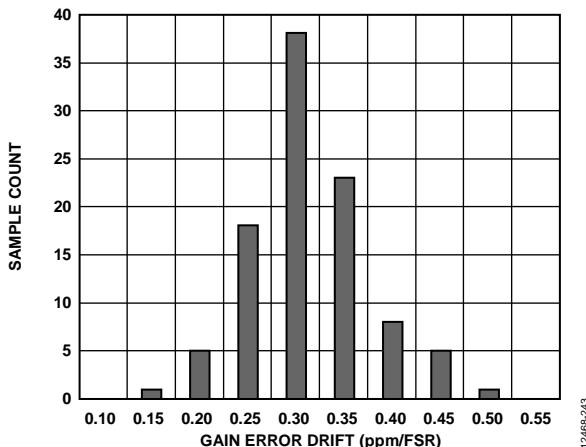

図 36. ゲイン誤差変動分布ヒストグラム

アナログ入力バッファ・イネーブル、100 ユニット)

図 37. ゲイン誤差変動分布ヒストグラム

(アナログ入力バッファ・ディスエーブル、100 ユニット)

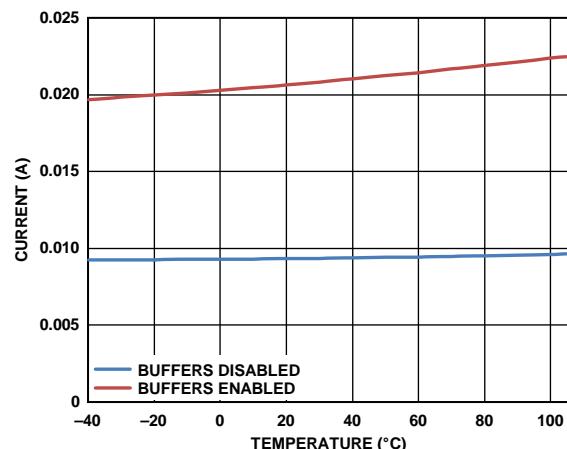

図 38. 周囲温度に対する消費電流変化

(連続変換モード時)

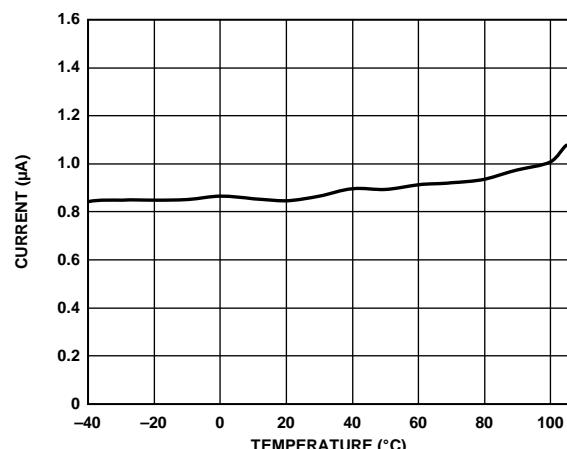

図 39. 周囲温度に対する消費電流変化

(パワーダウン・モード)

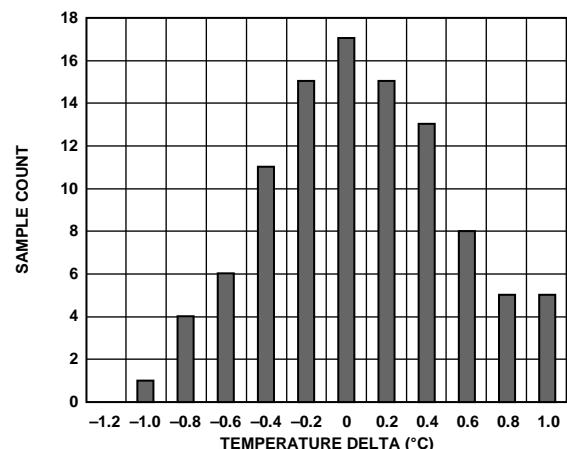

図 40. 温度センサー分布ヒストグラム

(未校正 100 ユニット)

図41.バーンアウト電流分布ヒストグラム (100 ユニット)

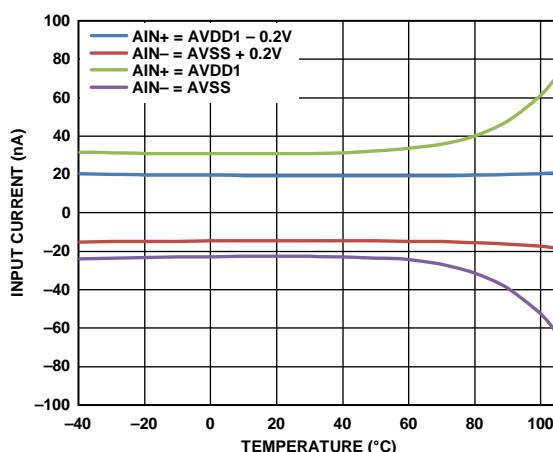

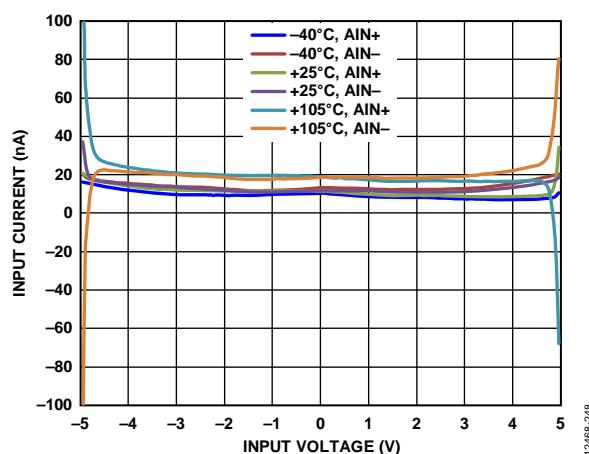

図43.入力バイアス電流の温度特性

図42.入力電圧に対するアナログ入力電流変化

( $V_{CM} = 2.5\text{ V}$ )

## ノイズ特性と分解能

表6と表7に、AD7175-2の各種出力レートやフィルタの組み合わせによる、rmsノイズ、ピークtoピーク・ノイズ、実効分解能、そして、ノイズ・フリー（ピークtoピーク）分解能を示します。ここに示した値は、バイポーラ入力とした時の値で、5Vの外部リファレンス電圧源を用いました。これらの

値は代表値であり、ADCの単一チャンネルの差動入力端子に0Vを入力して、連続変換しているときに得られた値です。ピークtoピーク分解能は、ピークtoピーク・ノイズを基に計算された値であることに注意をして下さい。このピークtoピーク分解能は、コード・フリッカが生じない分解能を示します。

表6.RMSノイズとピークtoピーク分解能 対 出力データレート（デフォルトはsinc5 + sinc1フィルタ使用）<sup>1</sup>

| Output Data Rate (SPS)        | RMS Noise ( $\mu\text{V rms}$ ) | Effective Resolution (Bits) | Peak-to-Peak Noise ( $\mu\text{V rms}$ ) | Peak-to-Peak Resolution (Bits) |

|-------------------------------|---------------------------------|-----------------------------|------------------------------------------|--------------------------------|

| <b>Input Buffers Disabled</b> |                                 |                             |                                          |                                |

| 250,000                       | 8.7                             | 20.1                        | 65                                       | 17.2                           |

| 62,500                        | 5.5                             | 20.8                        | 43                                       | 17.8                           |

| 10,000                        | 2.5                             | 21.9                        | 18.3                                     | 19.1                           |

| 1000                          | 0.77                            | 23.6                        | 5.2                                      | 20.9                           |

| 59.92                         | 0.19                            | 24                          | 1.1                                      | 23.1                           |

| 49.96                         | 0.18                            | 24                          | 0.95                                     | 23.3                           |

| 16.66                         | 0.1                             | 24                          | 0.45                                     | 24                             |

| 5                             | 0.07                            | 24                          | 0.34                                     | 24                             |

| <b>Input Buffers Enabled</b>  |                                 |                             |                                          |                                |

| 250,000                       | 9.8                             | 20                          | 85                                       | 16.8                           |

| 62,500                        | 6.4                             | 20.6                        | 55                                       | 17.5                           |

| 10,000                        | 3                               | 21.7                        | 23                                       | 18.7                           |

| 1000                          | 0.92                            | 23.4                        | 5.7                                      | 20.7                           |

| 59.98                         | 0.23                            | 24                          | 1.2                                      | 23.0                           |

| 49.96                         | 0.2                             | 24                          | 1                                        | 23.3                           |

| 16.66                         | 0.13                            | 24                          | 0.66                                     | 23.9                           |

| 5                             | 0.07                            | 24                          | 0.32                                     | 24                             |

<sup>1</sup> 選択されたレートのみ：1000サンプル

表7.RMSノイズとピークtoピーク分解能 対 出力データレート（sinc3フィルタ使用）<sup>1</sup>

| Output Data Rate (SPS)        | RMS Noise ( $\mu\text{V rms}$ ) | Effective Resolution (Bits) | Peak-to-Peak Noise ( $\mu\text{V rms}$ ) | Peak-to-Peak Resolution (Bits) |

|-------------------------------|---------------------------------|-----------------------------|------------------------------------------|--------------------------------|

| <b>Input Buffers Disabled</b> |                                 |                             |                                          |                                |

| 250,000                       | 210                             | 15.5                        | 1600                                     | 12.6                           |

| 62,500                        | 5.2                             | 20.9                        | 40                                       | 17.9                           |

| 10,000                        | 1.8                             | 22.4                        | 14                                       | 19.4                           |

| 1000                          | 0.56                            | 24                          | 3.9                                      | 21.3                           |

| 60                            | 0.13                            | 24                          | 0.8                                      | 23.6                           |

| 50                            | 0.13                            | 24                          | 0.7                                      | 23.8                           |

| 16.66                         | 0.07                            | 24                          | 0.37                                     | 24                             |

| 5                             | 0.05                            | 24                          | 0.21                                     | 24                             |

| <b>Input Buffers Enabled</b>  |                                 |                             |                                          |                                |

| 250,000                       | 210                             | 15.5                        | 1600                                     | 12.6                           |

| 62,500                        | 5.8                             | 20.7                        | 48                                       | 17.7                           |

| 10,000                        | 2.1                             | 22.2                        | 16                                       | 19.3                           |

| 1000                          | 0.71                            | 23.7                        | 4.5                                      | 21.1                           |

| 60                            | 0.17                            | 24                          | 1.1                                      | 23.1                           |

| 50                            | 0.15                            | 24                          | 0.83                                     | 23.5                           |

| 16.66                         | 0.12                            | 24                          | 0.6                                      | 24                             |

| 5                             | 0.08                            | 24                          | 0.35                                     | 24                             |

<sup>1</sup> 選択されたレートのみ：1000サンプル

## 評価開始にあたって

AD7175-2 は、高速セトリング、高分解能、さらにマルチプレクス機能を持った ADC で、それらの機能を高次元で組み合わせて構成することができます。

- 2つのフル差動または4つのシングルエンド入力。

- クロスポイント・マルチプレクサを搭載しているので、A/D 変換したい入力信号として、いずれのアナログ入力の組み合わせであっても選択することができます。これらの信号は入力バッファを経由したうえで、AD 変調器の正（非反転）もしくは負（反転）入力へと接続されます。

- アナログ及びリファレンス入力は、真のレール to レール・バッファ装備。

- どのアナログ入力に対しても、フル差動入力もしくはシングルエンド入力が可能。

- チャンネル毎に柔軟な構成が可能。最大4つの異なるセットアップを定義できます。個別のセットアップをチャンネルごとに割り当てることもできます。それぞれのセットアップは、以下の項目を構成できます。バッファのイネーブル/ディスエーブル、ゲインとオフセット補正の

有無、フィルタ・タイプ、出力データレート、リファレンス源の選択（内部/外部）です。

AD7175-2 は、高精度・低ドリフト (2 ppm/°C) の 2.5 V バンドギャップ・リファレンス電源を内蔵しています。このリファレンス電源を ADC の変換の基準として、用いることができるでの、外部部品の削減ができます。内蔵リファレンス電源をイネーブルにすると、REFOUT ピンからその電圧が outputされ、外部回路に対する低ノイズ・バイアス電圧源として用いることができます。REFOUT を使う一例として、シングルエンド入力で差動出力を持つアンプの入力コモン・モード信号として使うことが挙げられます。

AD7175-2 は、アナログおよびデジタル回路用に、それぞれ個別のリニア・レギュレータを内蔵しています。アナログ LDO は、AVDD2 から安定な 1.8V を作り、その電圧を ADC コアに供給します。電源接続を簡易化するため、AVDD1 と AVDD2 を接続することもできます。システム内に 2V (最少) から 5.5V (最大) のクリーンな電圧レールがあれば、電力消費を抑えるため、この電源レールを AVDD2 入力に接続するという選択も考えられます

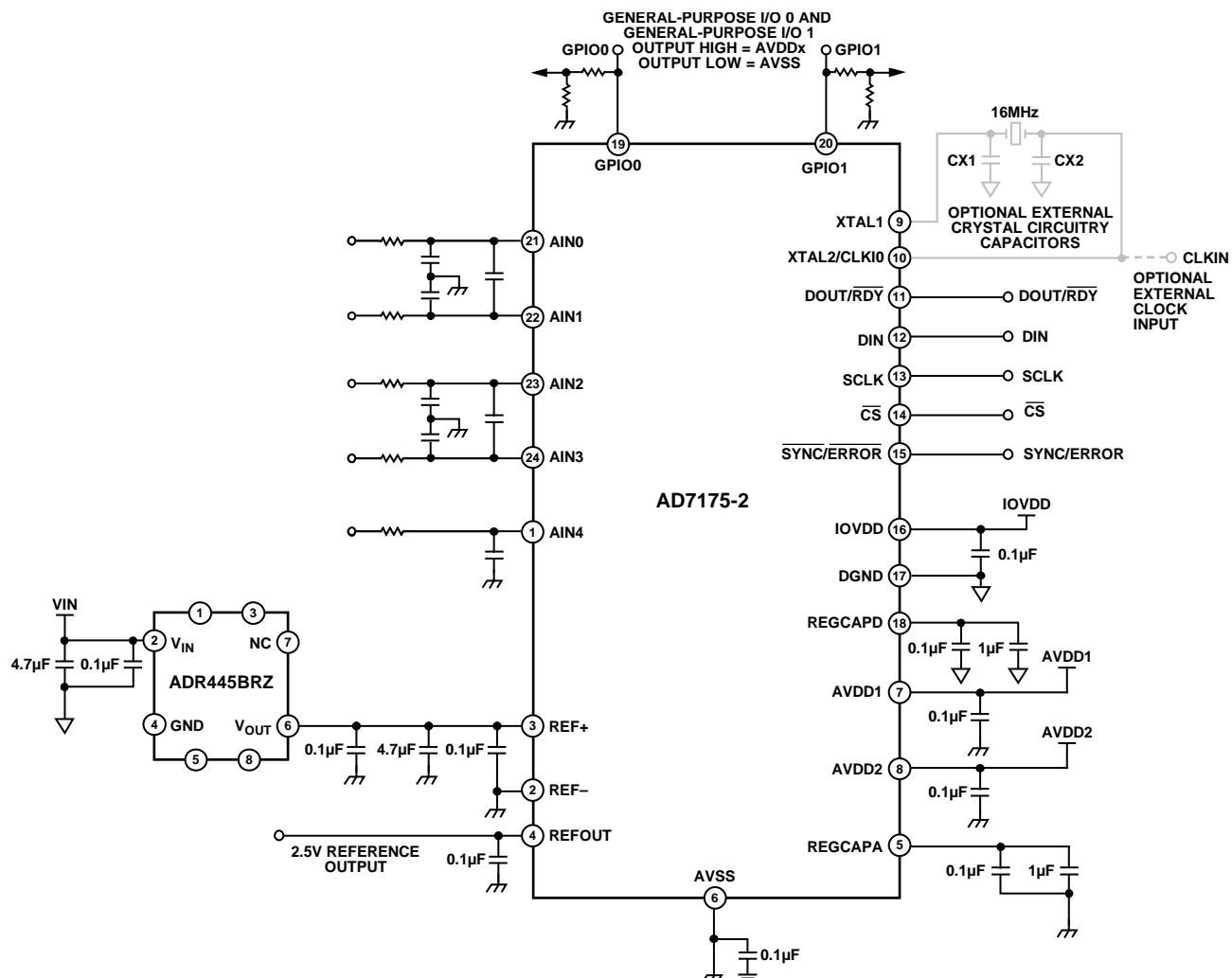

図 44. 代表的な接続図

デジタル IOVDD 用のリニア・レギュレータも、同様の機能を持ちます。つまり、IOVDD ピンに接続された入力電圧を 1.8V にレギュレーションし、AD7175-2 内部のデジタル・フィルタに供給します。シリアル・インターフェース信号は、常に IOVDD ピンに供給されている電圧で動作します。つまり IOVDD ピンに 3.3V が供給されている場合、インターフェース・ロジック入出力は、この電圧レベルで動作します。

AD7175-2 は、高分解能・高精度が要求される、幅広いアプリケーションで使うことができます。いくつかのシナリオを以下に示します。

- 内部マルチプレクサを使ったアナログ入力の高速スキャニング。

- GPIO で自動制御できる外部マルチプレクサを使った、アナログ入力の高速スキャニング。

- 低速で高分解能なデータが必要なマルチ・チャンネル、もしくはチャンネル毎に ADC が必要なアプリケーション。

- チャンネル毎にシングル ADC を必要とする場合：高速・低レイテンシ出力特性を実現しているので、外部のマイクロコントローラや、DSP、FPGA で設計された特定アプリケーション用のフィルタを使うことも可能。

## 電源

AD7175-2 は 3 つの独立した電源ピンを持っています。

AVDD1、AVDD2、そして IOVDD です。

AVDD1 は、クロスポイント・マルチプレクサ、内蔵のアナログ及びリファレンス・バッファに電源供給を行っています。AVDD1 の値は AVSS を基準とし、AVDD1 – AVSS = 5V として下さい。つまり、5V の単電源動作や ±2.5V の正負両電源動作が可能です。正負両電源動作によって、このデバイスは、真のバイポーラ入力が可能になります。正負両電源で動作させるときは、絶対最大定格に注意して下さい（詳細は、絶対最大定格セクション参照）。

AVDD2 は、内部の 1.8V のアナログ LDO レギュレータに電源供給を行っています。このレギュレータは、ADC コアに電源供給しています。AVDD2 は、AVSS を基準とし、AVDD2 – AVSS の範囲は、5.5V（最大）～2V（最小）です。

IOVDD は、内部の 1.8V デジタル LDO レギュレータに電源供給を行っています。このレギュレータは、ADC のデジタル・ロジック回路への電源供給を行っています。IOVDD は、ADC の SPI インターフェース電圧レベルを決めています。IOVDD は、DGND を基準とし、IOVDD – DGND の範囲は、5.5V（最大）～2V（最小）です。

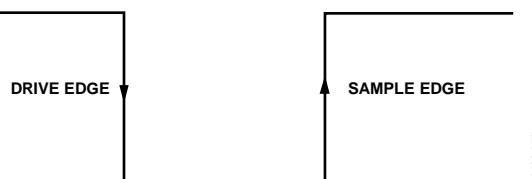

## デジタル通信

AD7175-2 は、3 線もしくは 4 線の SPI インターフェースを持ち、それらは、QSPI™、MICROWIRE®、DSP と互換性があります。このインターフェースは、SPI モード 3 で動作し、CS はロー・レベルに固定したままでも動作します。SPI モード 3 では、SCLK はアイドル・ハイで、SCLK の立下りエッジが起動エッジ、立ち上がりエッジがサンプル・エッジです。すなわち、データは立下りの起動エッジに同期して出力され、立ち上がりのサンプル・エッジに同期して入力されます。

図 45. SPI モード 3 の SCLK エッジ

12468-052

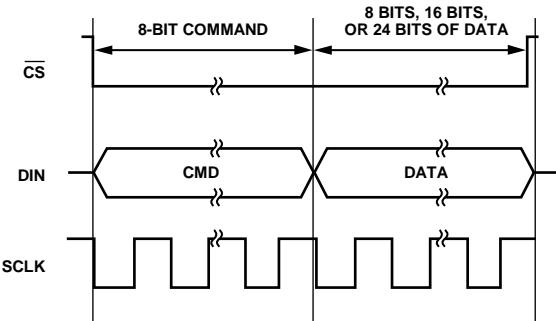

## ADC のレジスタ・マップへのアクセス

コミュニケーション・レジスタは、ADC 内全てのレジスタ・マップへのアクセスを制御しています。このレジスタは、8 ビットの書き込み専用レジスタです。パワーアップ時もしくはリセットの直後、デジタル・インターフェースはデフォルト状態になります。これはコミュニケーション・レジスタに対して書き込み待ちの状態です。従って全ての通信は、コミュニケーション・レジスタへのデータ書き込みによって開始されます。

コミュニケーション・レジスタへのデータ書き込みによって、どのレジスタへのアクセスが行われるかが決まり、さらに次の動作が指定したレジスタへの書き込みなのか、読み出しなのかも決まります。このレジスタのアドレス・ビット (RA[5:0]) の値で、どのレジスタに対して、データの読み書きを行うかを指定します。

選択されたレジスタへの読み出し動作または書き込み動作が完了すると、インターフェースはデフォルト状態、すなわち、コミュニケーション・レジスタに対する書き込み動作待ちの状態に戻ります。

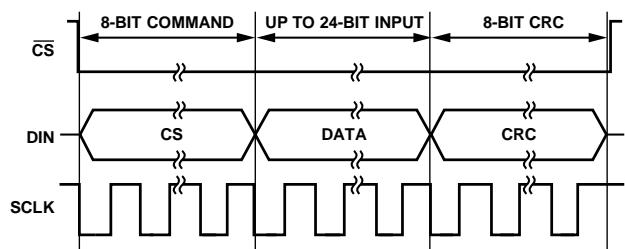

図 46 と 図 47 はそれぞれ、書き込み動作と読み出し動作の例を示していますが、最初に 8 ビット・コマンドをコミュニケーション・レジスタに書き込み、それに続いて指定したレジスタのデータの読み書きを行っている様子を示しています。

図 46. レジスタへの書き込み

（レジスタ・アドレスへ 8 ビットコマンドを送ると、それに続いて 8、16 もしくは 24 ビットのデータを書き込む。

データ長は選択されたレジスタによって変化する）

図 47. レジスタからの読み出し

（レジスタ・アドレスへ 8 ビットコマンドを送ると、それに続いて 8、16 もしくは 24 ビットのデータを読みだす。

データ長は選択されたレジスタによって変化する）

ID レジスタの読み出しは、このデバイスが正しい通信を行っているかを確認するための推奨される方法です。ID レジスタは読み出し専用のレジスタで、AD7175-2 は、0x0CDX という固有の値を持っています。コミュニケーション・レジスタと ID レジスタの詳細は、表 8 と表 9 を参照してください。

**AD7175-2 のリセット**

インターフェースの同期が失われた場合は、DIN をハイ・レベルにして、少なくともシリアル・クロックの 64 サイクルの間書き込み動作を行うことで、ADC はレジスタの内容を含むすべての設定をリセットしてデフォルト状態に戻ります。あるいは、CS をデジタル・インターフェースと共に使用し、CS をハイ・レベルにする事で、デジタル・インターフェースがリセットされ、その時の全ての動作を中止します。

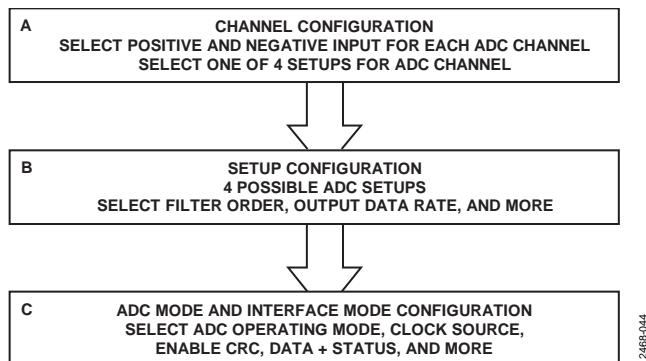

**コンフィギュレーションの概要**

パワーオン、もしくはリセット後の AD7175-2 のデフォルト状態を以下に示します：

- チャンネル・コンフィギュレーション：CH0 がイネーブル。AIN0 は正側入力、AIN1 は負側入力が選択状態。Setup0 が選択された状態。

- セットアップ・コンフィギュレーション：内蔵リファレンスとアナログ入力バッファがイネーブル。リファレンス入力バッファはディスエーブル。

- フィルタ・コンフィギュレーション：Sinc5 + Sinc 1 フィルタが選択、最大出力レートとして 250 kSPS が選択される。

- ADC モード：連続変換モードと内部発振器をイネーブル。

- インターフェース・モード：CRC、データとステータス出力がディスエーブル。

いくつかの重要なレジスタ・オプションのみを示しました。このリストは一例であることに留意してください。全てのレジスタ情報に関しては、「レジスタの詳細」セクションを参照してください。

図 48 に、ADC 動作の設定変更をするときの推奨フローの概要を示します。このフローは 3 つのブロックに分けられます：

12489-044

図 48. 推奨する ADC 構成時のフロー

表 8. コミュニケーション・レジスタ

| Reg. | Name  | Bits  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset | RW |

|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----|

| 0x00 | COMMS | [7:0] | WEN   | R/W   |       |       |       | RA    |       |       | 0x00  | W  |

表 9.ID レジスタ

| Reg. | Name | Bits   | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset   | RW |

|------|------|--------|-------|-------|-------|----------|-------|-------|-------|-------|---------|----|

| 0x07 | ID   | [15:8] |       |       |       | ID[15:8] |       |       |       |       | 0x0CD X | R  |

|      |      | [7:0]  |       |       |       | ID[7:0]  |       |       |       |       |         |    |

表 10. Channel 0 レジスタ