# 真のレール to レール・バッファ内蔵、低消費電力、 24 ビット、31.25 kSPS、シグマ・デルタ ( $\Sigma$ - $\Delta$ ) ADC

## データシート

**AD7172-4**

### 特長

高速かつ柔軟な出カレート : 1.25 SPS ~ 31.25 kSPS

チャンネル・スキャン・データ・レート: 6.21 kSPS / チャンネル (セトリング時間 161 $\mu$ s)

性能仕様

ノイズ・フリー・ビット数 : 31.25 kSPS で 17.2 ビット

ノイズ・フリー・ビット数 : 5 SPS で 24 ビット

INL : FSR の ±2 ppm

50 Hz と 60 Hz の除去比 : 50 ms セトリングで 85 dB

入力チャンネルがユーザー設定可能

4 チャンネル完全差動または 8 チャンネル・シングルエンド

クロスポイント・マルチプレクサ

真のレール to レールのアナログ入力バッファとリファレンス

入力バッファ

内部または外部クロック

電源

AVDD1 = 3.0 V ~ 5.5 V、AVDD2 = IOVDD = 2 V ~ 5.5 V

AVDD1 および AVSS を ±2.5 V または ±1.65 V とする両電源も可能

ADC 消費電流 : 1.5 mA

動作温度範囲 : -40°C to +105°C

3 線式または 4 線式のシリアル・デジタル・インターフェース

(シミュット・トリガー付き SCLK)

シリアル・インターフェース : (SPI)/QSPI/MICROWIRE/DSP 互換

### アプリケーション

プロセス制御 : PLC/DCS モジュール

温度計測および圧力計測

医療や科学分野向けのマルチ・チャンネル計測器

クロマトグラフィ

### 概要

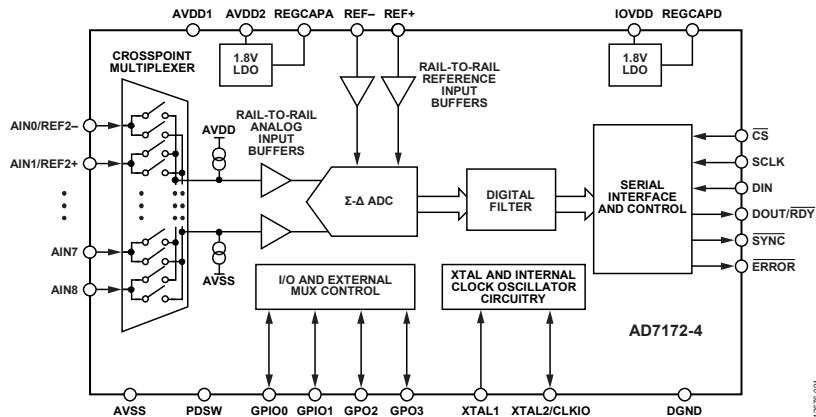

AD7172-4 は、低ノイズ、低消費電力、マルチプレクス型のシグマ・デルタ ( $\Sigma$ - $\Delta$ ) A/D コンバータ (ADC) で、低帯域幅信号用の 4 チャンネルまたは 8 チャンネル(完全差動/シングルエンド)入力を備えています。AD7172-4 の完全にセトリングされたデータの最大チャンネル・スキャン・データ・レートは 6.21 kSPS (161 $\mu$ s) です。出力データ・レートは 1.25 SPS ~ 31.25 kSPS の範囲です。

AD7172-4 は、主要なアナログ/デジタル信号処理ブロックを内蔵しており、ユーザーは SPI を介して使用する各アナログ入力チャンネルの構成を個別に設定することができます。アナログ入力とリファレンス入力に内蔵されている真のレール to レール・バッファにより、高インピーダンス入力の駆動が容易になっています。

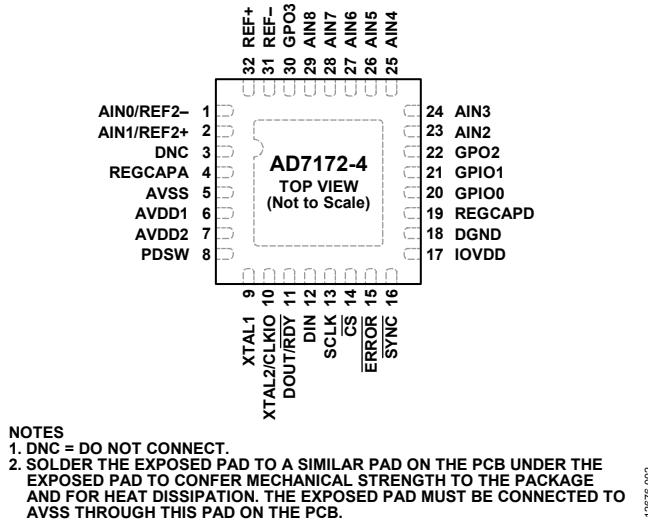

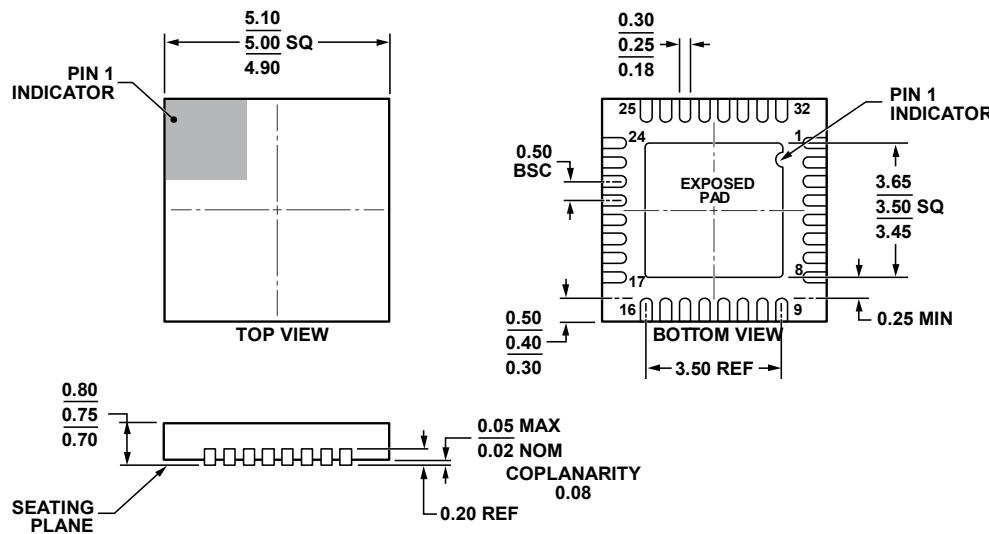

デジタル・フィルタにより、27.27 SPS の出力データ・レートで 50 Hz と 60 Hz の同時除去が可能です。ユーザーは、アプリケーションの各チャンネルの要求に応じてフィルタ・オプションを切り替えたり、チャンネルごとに設定可能なオフセット・キャリブレーション・レジスタやゲイン・キャリブレーション・レジスタなどの追加のデジタル処理機能を使用できます。汎用入出力 (GPIO) は、ADC 変換タイミングと同期した状態で外部マルチプレクサを制御します。規定温度範囲は、-40°C ~ +105°C です。AD7172-4 には 5 mm × 5 mm、32 ピン LFCSP パッケージが採用されています。

なお、このデータシートでは、複数の機能名を持つピンは、該当する名前のみを記載し、該当する機能のみを説明していることにご注意下さい。

### 機能ブロック図

12076-001

図 1.

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                                 |    |

|---------------------------------|----|

| 特長                              | 1  |

| アプリケーション                        | 1  |

| 概要                              | 1  |

| 機能ブロック図                         | 1  |

| 改訂履歴                            | 2  |

| 仕様                              | 3  |

| タイミング特性                         | 6  |

| タイミング図                          | 6  |

| 絶対最大定格                          | 7  |

| 熱抵抗                             | 7  |

| ESD に関する注意                      | 7  |

| ピン配置およびピン機能の説明                  | 8  |

| 代表的な性能特性                        | 10 |

| ノイズ特性と分解能                       | 16 |

| 評価開始にあたって                       | 17 |

| 電源                              | 18 |

| デジタル通信                          | 18 |

| AD7172-4 のリセット                  | 19 |

| 構成概要                            | 19 |

| 回路説明                            | 25 |

| バッファ付きアナログ入力                    | 25 |

| クロスポイント・マルチプレクサ                 | 25 |

| AD7172-4 リファレンス                 | 26 |

| バッファされたリファレンス入力                 | 27 |

| クロック源                           | 27 |

| デジタル・フィルタ                       | 28 |

| Sinc5 + Sinc1 フィルタ              | 28 |

| Sinc3 フィルタ                      | 28 |

| シングル・サイクル・セトリング                 | 29 |

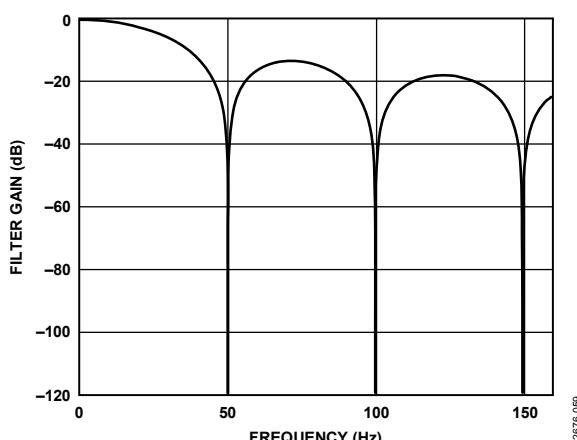

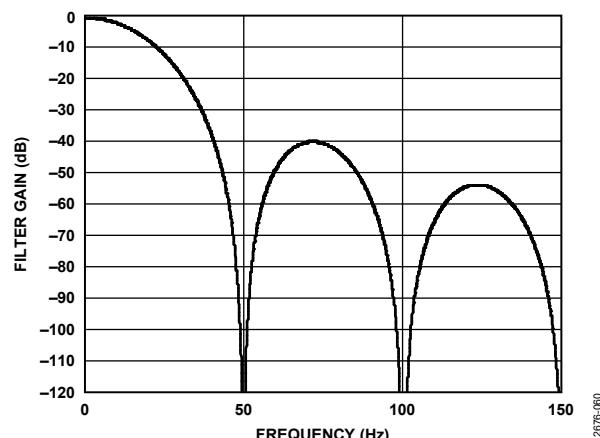

| 強化された 50 Hz / 60 Hz 除去フィルタ      | 32 |

| 動作モード                           | 34 |

| 連続変換モード                         | 34 |

| 連続読みしモード                        | 35 |

| シングル変換モード                       | 36 |

| スタンバイ・モードとパワーダウン・モード            | 37 |

| キャリブレーション                       | 37 |

| デジタル・インターフェース                   | 38 |

| チェックサム保護                        | 38 |

| CRC の計算                         | 39 |

| 内蔵機能                            | 41 |

| 汎用の入出力                          | 41 |

| 外部マルチプレクサの制御                    | 41 |

| 遅延                              | 41 |

| 16 ビット / 24 ビット変換               | 41 |

| DOUT_RESET                      | 41 |

| 同期                              | 41 |

| エラー・フラグ                         | 42 |

| DATA_STAT                       | 42 |

| IOSTRENGTH                      | 42 |

| グラウンドィングとレイアウト                  | 43 |

| レジスタの一覧                         | 44 |

| レジスタの詳細                         | 46 |

| コミュニケーション・レジスタ                  | 46 |

| ステータス・レジスタ                      | 47 |

| ADC モード・レジスタ                    | 48 |

| インターフェース・モード・レジスタ               | 49 |

| レジスタ・チェック                       | 50 |

| データ・レジスタ                        | 50 |

| GPIO 設定レジスタ                     | 51 |

| ID レジスタ                         | 52 |

| チャンネル・レジスタ 0                    | 53 |

| チャンネル・レジスタ 1 ~ チャンネル・レジスタ 7     | 54 |

| セットアップ構成レジスタ 0                  | 55 |

| セットアップ構成レジスタ 1 ~ セットアップ構成レジスタ 7 | 56 |

| フィルタ設定レジスタ 0                    | 57 |

| フィルタ設定レジスタ 1 ~ フィルタ設定レジスタ 7     | 58 |

| オフセット・レジスタ 0                    | 58 |

| オフセット・レジスタ 1 ~ オフセット・レジスタ 7     | 58 |

| ゲイン・レジスタ 0                      | 59 |

| ゲイン・レジスタ 1 ~ ゲイン・レジスタ 7         | 59 |

| 外形寸法                            | 60 |

| オーダー・ガイド                        | 60 |

## 改訂履歴

5/15—Revision 0: 初版

## 仕様

特に指定のない限り、AVDD1 = 3.0 V ~ 5.5 V、AVDD2 = IOVDD = 2 V ~ 5.5 V、AVSS = DGND = 0 V、REF+ = 2.5 V、REF- = AVSS、MCLK = 内部マスター・クロック = 2 MHz、TA = T<sub>MIN</sub> ~ T<sub>MAX</sub> (-40 °C ~ +105 °C)

表 1.

| Parameter                                               | Test Conditions/Comments                                                                                                    | Min                              | Typ                   | Max                   | Unit               |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|-----------------------|--------------------|

| ADC SPEED AND PERFORMANCE                               |                                                                                                                             |                                  |                       |                       |                    |

| Output Data Rate (ODR)<br>No Missing Codes <sup>1</sup> | Excluding sinc3 filter $\geq$ 15 kSPS                                                                                       | 1.25<br>24                       |                       | 31,250                | SPS<br>Bits        |

| Resolution                                              | See Table 6 and Table 7                                                                                                     |                                  |                       |                       |                    |

| Noise                                                   | See Table 6 and Table 7                                                                                                     |                                  |                       |                       |                    |

| ACCURACY                                                |                                                                                                                             |                                  |                       |                       |                    |

| Integral Nonlinearity (INL)                             | Internal short                                                                                                              |                                  | $\pm 2$               | $\pm 5.2$             | ppm of FSR         |

| Offset Error <sup>2</sup>                               | Internal short                                                                                                              |                                  | $\pm 75$              |                       | $\mu$ V            |

| Offset Drift                                            | Internal short                                                                                                              |                                  | $\pm 230$             |                       | nV/°C              |

| Gain Error <sup>2</sup>                                 | AVDD1 = 5 V                                                                                                                 |                                  | $\pm 5$               | $\pm 45$              | ppm of FSR         |

| Gain Drift                                              |                                                                                                                             |                                  | $\pm 0.2$             | $\pm 0.5$             | ppm/°C             |

| REJECTION                                               |                                                                                                                             |                                  |                       |                       |                    |

| Power Supply Rejection                                  | AVDD1, AVDD2, V <sub>IN</sub> = 1 V                                                                                         |                                  | 98                    |                       | dB                 |

| Common-Mode Rejection<br>At DC                          | V <sub>IN</sub> = 0.1 V                                                                                                     | 95                               |                       |                       | dB                 |

| At 50 Hz, 60 Hz <sup>1</sup>                            | 20 Hz output data rate (postfilter), 50 Hz $\pm$ 1 Hz and 60 Hz $\pm$ 1 Hz                                                  | 120                              |                       |                       | dB                 |

| Normal Mode Rejection <sup>1</sup>                      | 50 Hz $\pm$ 1 Hz and 60 Hz $\pm$ 1 Hz<br>Internal clock, 20 SPS ODR (postfilter)<br>External clock, 20 SPS ODR (postfilter) | 71<br>85                         | 90<br>90              |                       | dB<br>dB           |

| ANALOG INPUTS                                           |                                                                                                                             |                                  |                       |                       |                    |

| Differential Input Range                                | V <sub>REF</sub> = (REF+) - (REF-)                                                                                          |                                  | $\pm V_{REF}$         |                       | V                  |

| Absolute Voltage Limits <sup>1</sup>                    |                                                                                                                             | AVSS - 0.05<br>AVSS              |                       | AVDD1 + 0.05<br>AVDD1 | V<br>V             |

| Input Buffers Disabled                                  |                                                                                                                             |                                  | $\pm 6$               |                       | $\mu$ A/V          |

| Input Buffers Enabled                                   |                                                                                                                             |                                  | $\pm 0.45$            |                       | nA/V/°C            |

| Analog Input Current<br>Input Buffers Disabled          |                                                                                                                             |                                  | $\pm 5.5$             |                       | nA                 |

| Input Current                                           |                                                                                                                             |                                  | $\pm 0.1$             |                       | nA/°C              |

| Input Current Drift                                     |                                                                                                                             |                                  | -120                  |                       | dB                 |

| Input Buffers Enabled                                   | 1 kHz input                                                                                                                 |                                  |                       |                       |                    |

| Input Current                                           |                                                                                                                             |                                  | $\pm 9$               |                       | $\mu$ A/V          |

| Input Current Drift                                     |                                                                                                                             | External clock<br>Internal clock | $\pm 0.75$<br>$\pm 1$ |                       | nA/V/°C<br>nA/V/°C |

| Input Buffers Enabled                                   |                                                                                                                             |                                  | $\pm 100$             |                       | nA                 |

| Input Current                                           |                                                                                                                             |                                  | $\pm 2.5$             |                       | nA/°C              |

| Input Current Drift                                     |                                                                                                                             |                                  | 95                    |                       | dB                 |

| Normal Mode Rejection <sup>1</sup>                      | See the Rejection parameter                                                                                                 |                                  |                       |                       |                    |

| Common-Mode Rejection                                   |                                                                                                                             |                                  |                       |                       |                    |

| BURNOUT CURRENTS                                        |                                                                                                                             |                                  |                       |                       |                    |

| Source/Sink Current                                     | Analog input buffers must be enabled                                                                                        |                                  | $\pm 10$              |                       | $\mu$ A            |

| Parameter                               | Test Conditions/Comments                            | Min          | Typ          | Max        | Unit |

|-----------------------------------------|-----------------------------------------------------|--------------|--------------|------------|------|

| GPIO (GPIO0, GPIO1)                     | With respect to AVSS                                |              |              |            |      |

| Input Mode Leakage Current <sup>1</sup> |                                                     | -10          | 5            | +10        | µA   |

| Floating State Output Capacitance       |                                                     |              |              |            | pF   |

| Output Voltage <sup>1</sup>             |                                                     |              |              |            |      |

| High, V <sub>OH</sub>                   | I <sub>SOURCE</sub> = 200 µA                        | AVSS + 4     |              |            | V    |

| Low, V <sub>OL</sub>                    | I <sub>SINK</sub> = 800 µA                          |              |              | AVSS + 0.4 | V    |

| Input Voltage <sup>1</sup>              |                                                     |              |              |            |      |

| High, V <sub>IH</sub>                   |                                                     | AVSS + 3     |              |            | V    |

| Low, V <sub>IL</sub>                    |                                                     |              |              | AVSS + 0.7 | V    |

| CLOCK                                   |                                                     |              |              |            |      |

| Internal Clock                          |                                                     |              |              |            |      |

| Frequency                               |                                                     | 2            |              |            | MHz  |

| Accuracy                                |                                                     | -2.6%        |              | +2.5%      | %    |

| Duty Cycle                              |                                                     | 50           |              |            | %    |

| Output Voltage                          |                                                     |              |              |            |      |

| Low, V <sub>OL</sub>                    |                                                     |              | 0.4          |            | V    |

| High, V <sub>OH</sub>                   |                                                     | 0.8 × IOVDD  |              |            | V    |

| Crystal                                 |                                                     |              |              |            |      |

| Frequency                               |                                                     | 14           | 16           | 16.384     | MHz  |

| Startup Time                            |                                                     |              | 10           |            | µs   |

| External Clock (CLKIO)                  |                                                     |              | 2            | 2.048      | MHz  |

| Duty Cycle <sup>1</sup>                 |                                                     | 30           | 50           | 70         | %    |

| LOGIC INPUTS                            |                                                     |              |              |            |      |

| Input Voltage <sup>1</sup>              |                                                     |              |              |            |      |

| High, V <sub>INH</sub>                  | 2 V ≤ IOVDD < 2.3 V                                 | 0.65 × IOVDD |              |            | V    |

|                                         | 2.3 V ≤ IOVDD ≤ 5.5 V                               | 0.7 × IOVDD  |              |            | V    |

| Low, V <sub>INL</sub>                   | 2 V ≤ IOVDD < 2.3 V                                 |              | 0.35 × IOVDD |            | V    |

|                                         | 2.3 V ≤ IOVDD ≤ 5.5 V                               |              | 0.7          |            | V    |

| Hysteresis <sup>1</sup>                 | IOVDD ≥ 2.7 V                                       | 0.08         |              | 0.25       | V    |

|                                         | IOVDD < 2.7 V                                       | 0.04         |              | 0.2        | V    |

| Leakage Currents                        |                                                     | -10          |              | +10        | µA   |

| LOGIC OUTPUT (DOUT/RDY)                 |                                                     |              |              |            |      |

| Output Voltage <sup>1</sup>             |                                                     |              |              |            |      |

| High, V <sub>OH</sub>                   | IOVDD ≥ 4.5 V, I <sub>SOURCE</sub> = 1 mA           | 0.8 × IOVDD  |              |            | V    |

|                                         | 2.7 V ≤ IOVDD < 4.5 V, I <sub>SOURCE</sub> = 500 µA | 0.8 × IOVDD  |              |            | V    |

|                                         | IOVDD < 2.7 V, I <sub>SOURCE</sub> = 200 µA         | 0.8 × IOVDD  |              |            | V    |

| Low, V <sub>OL</sub>                    | IOVDD ≥ 4.5 V, I <sub>SINK</sub> = 2 mA             |              | 0.4          |            | V    |

|                                         | 2.7 V ≤ IOVDD < 4.5 V, I <sub>SINK</sub> = 1 mA     |              | 0.4          |            | V    |

|                                         | IOVDD < 2.7 V, I <sub>SINK</sub> = 400 µA           |              | 0.4          |            | V    |

| Leakage Current                         | Floating state                                      | -10          |              | +10        | µA   |

| Output Capacitance                      | Floating state                                      |              | 10           |            | pF   |

| SYSTEM CALIBRATION <sup>1</sup>         |                                                     |              |              |            |      |

| Full-Scale (FS) Calibration Limit       |                                                     |              |              | 1.05 × FS  | V    |

| Zero-Scale Calibration Limit            |                                                     | -1.05 × FS   |              |            | V    |

| Input Span                              |                                                     | 0.8 × FS     |              | 2.1 × FS   | V    |

| POWER REQUIREMENTS                      |                                                     |              |              |            |      |

| Power Supply Voltage                    |                                                     |              |              |            |      |

| AVDD1 to AVSS                           |                                                     | 3.0          |              | 5.5        | V    |

| AVDD2 to AVSS                           |                                                     | 2            |              | 5.5        | V    |

| AVSS to DGND                            |                                                     | -2.75        |              | 0          | V    |

| IOVDD to DGND                           |                                                     | 2            |              | 5.5        | V    |

| IOVDD to AVSS                           | For AVSS < DGND                                     |              |              | 6.35       | V    |

| Parameter                                            | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                       | Min                                      | Typ                | Max  | Unit    |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------|------|---------|

| POWER SUPPLY CURRENTS                                | All outputs unloaded, digital inputs connected to IOVDD or DGND                                                                                                                                                                                                                                                                                                                |                                          |                    |      |         |

| Full Operating Mode                                  |                                                                                                                                                                                                                                                                                                                                                                                |                                          |                    |      |         |

| AVDD1 Current                                        |                                                                                                                                                                                                                                                                                                                                                                                |                                          |                    |      |         |

| AVDD1 = 5 V Typical,<br>5.5 V Maximum                | AIN $\pm$ and REF $\pm$ buffers disabled                                                                                                                                                                                                                                                                                                                                       | 0.23                                     | 0.29               | 0.29 | mA      |

| AVDD1 = 3.3 V Typical,<br>3.6 V Maximum <sup>1</sup> | AIN $\pm$ and REF $\pm$ buffers enabled<br>Each buffer: AIN $\pm$ and REF $\pm$                                                                                                                                                                                                                                                                                                | 1.7<br>0.38                              | 2.15               | 2.15 | mA      |

| AVDD1 Current                                        | AIN $\pm$ and REF $\pm$ buffers disabled                                                                                                                                                                                                                                                                                                                                       | 0.15                                     | 0.2                | 0.2  | mA      |

| AVDD2 Current                                        | AIN $\pm$ and REF $\pm$ buffers enabled<br>Each buffer: AIN $\pm$ and REF $\pm$                                                                                                                                                                                                                                                                                                | 1.45<br>0.33                             | 1.9                | 1.9  | mA      |

| IOVDD Current                                        | External clock<br>Internal clock                                                                                                                                                                                                                                                                                                                                               | 1<br>0.33<br>0.61                        | 1.1<br>0.5<br>0.82 | 1.1  | mA      |

| Standby Mode                                         | External crystal                                                                                                                                                                                                                                                                                                                                                               | 0.98                                     |                    |      | mA      |

| Power-Down Mode                                      | LDO on<br>Full power-down including LDO                                                                                                                                                                                                                                                                                                                                        | 32<br>1                                  | 32<br>10           | 32   | $\mu$ A |

| POWER DISSIPATION                                    |                                                                                                                                                                                                                                                                                                                                                                                |                                          |                    |      |         |

| Full Operating Mode                                  | Unbuffered, external clock; AVDD1 = 3.3 V, AVDD2 = 2 V, IOVDD = 2 V<br>Unbuffered, external clock;<br>all supplies = 5 V<br>Unbuffered, external clock;<br>all supplies = 5.5 V<br>Fully buffered, internal clock; AVDD1 = 3.3 V, AVDD2 = 2 V, IOVDD = 2 V<br>Fully buffered, internal clock;<br>all supplies = 5 V<br>Fully buffered, internal clock;<br>all supplies = 5.5 V | 3.16<br>7.8<br>10.4<br>8<br>16.6<br>22.4 |                    |      | mW      |

| Standby Mode                                         | All supplies = 5 V                                                                                                                                                                                                                                                                                                                                                             | 160                                      |                    |      | $\mu$ W |

| Power-Down Mode                                      | Full power-down, all supplies = 5 V<br>Full power-down, all supplies = 5.5 V                                                                                                                                                                                                                                                                                                   | 5<br>55                                  |                    |      | $\mu$ W |

<sup>1</sup>これらの値に対する出荷テストは行われていませんが、設計および／または量産開始時の特性評価データで保証されています。

<sup>2</sup>システムまたは内蔵ゼロスケールのキャリブレーション手順に従えば、オフセット誤差は、プログラムされた出力データ・レートにおけるノイズ・レベルとほぼ同等になります。システム・フルスケール・キャリブレーションでは、プログラムされた出力データ・レートのノイズ・レベルと同等レベルにまでゲイン誤差を減少させることができます。

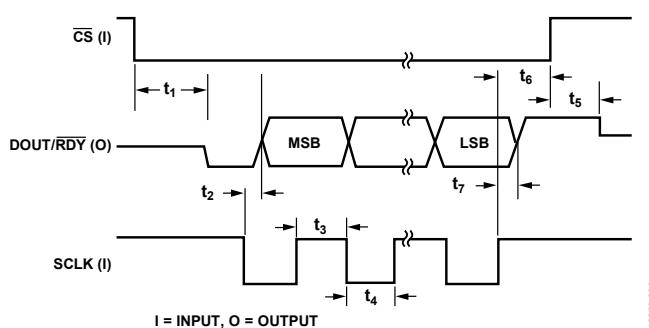

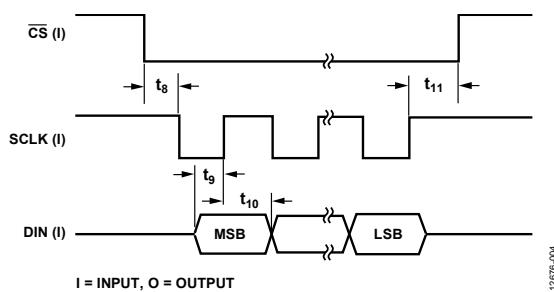

## タイミング特性

特に指定のない限り、 $\text{IOVDD} = 2 \text{ V} \sim 5.5 \text{ V}$ 、 $\text{DGND} = 0 \text{ V}$ 、Input Logic 0 = 0 V、Input Logic 1 =  $\text{IOVDD}$ 、 $C_{\text{LOAD}} = 20 \text{ pF}$

表 2.

| Parameter       | Limit at $T_{\text{MIN}}, T_{\text{MAX}}$ | Unit   | Test Conditions/Comments <sup>1, 2</sup>                                               |

|-----------------|-------------------------------------------|--------|----------------------------------------------------------------------------------------|

| SCLK            |                                           |        |                                                                                        |

| $t_3$           | 25                                        | ns min | SCLK high pulse width                                                                  |

| $t_4$           | 25                                        | ns min | SCLK low pulse width                                                                   |

| READ OPERATION  |                                           |        |                                                                                        |

| $t_1$           | 0                                         | ns min | $\overline{\text{CS}}$ falling edge to $\text{DOUT}/\overline{\text{RDY}}$ active time |

|                 | 15                                        | ns max | $\text{IOVDD} = 4.75 \text{ V}$ to $5.5 \text{ V}$                                     |

|                 | 40                                        | ns max | $\text{IOVDD} = 2 \text{ V}$ to $3.6 \text{ V}$                                        |

| $t_2^3$         | 0                                         | ns min | SCLK active edge to data valid delay <sup>4</sup>                                      |

|                 | 12.5                                      | ns max | $\text{IOVDD} = 4.75 \text{ V}$ to $5.5 \text{ V}$                                     |

|                 | 25                                        | ns max | $\text{IOVDD} = 2 \text{ V}$ to $3.6 \text{ V}$                                        |

| $t_5$           | 2.5                                       | ns min | Bus relinquish time after $\overline{\text{CS}}$ inactive edge                         |

|                 | 20                                        | ns max |                                                                                        |

| $t_6$           | 0                                         | ns min | SCLK inactive edge to $\overline{\text{CS}}$ inactive edge                             |

| $t_7^5$         | 10                                        | ns min | SCLK inactive edge to $\text{DOUT}/\overline{\text{RDY}}$ high/low                     |

| WRITE OPERATION |                                           |        |                                                                                        |

| $t_8$           | 0                                         | ns min | $\overline{\text{CS}}$ falling edge to SCLK active edge setup time <sup>4</sup>        |

| $t_9$           | 8                                         | ns min | Data valid to SCLK edge setup time                                                     |

| $t_{10}$        | 8                                         | ns min | Data valid to SCLK edge hold time                                                      |

| $t_{11}$        | 5                                         | ns min | CS rising edge to SCLK edge hold time                                                  |

<sup>1</sup> 初期リリース時にサンプル・テストによりコンプライアンスを保証。

<sup>2</sup> 図 2 および図 3 を参照。

<sup>3</sup> このパラメータは、出力が  $V_{\text{OL}}$  または  $V_{\text{OH}}$  を交差するのに要する時間で定義されています。

<sup>4</sup> SCLK のアクティブ・エッジとは、SCLK の立ち下がりエッジを意味します。

<sup>5</sup> データ・レジスタを読み出した後、 $\text{DOUT}/\overline{\text{RDY}}$  はハイ・レベルに戻ります。シングル変換モードおよび連続変換モードで、 $\text{DOUT}/\overline{\text{RDY}}$  がハイ・レベルの間に、必要ならば、同一データを再度読み出すことができますが、2 回目以降の読み出しは次の出力更新が近いところで読み出さないように注意してください。連続読み出し機能をイネーブルにすると、デジタル・ワードは 1 回しか読み出すことができません。

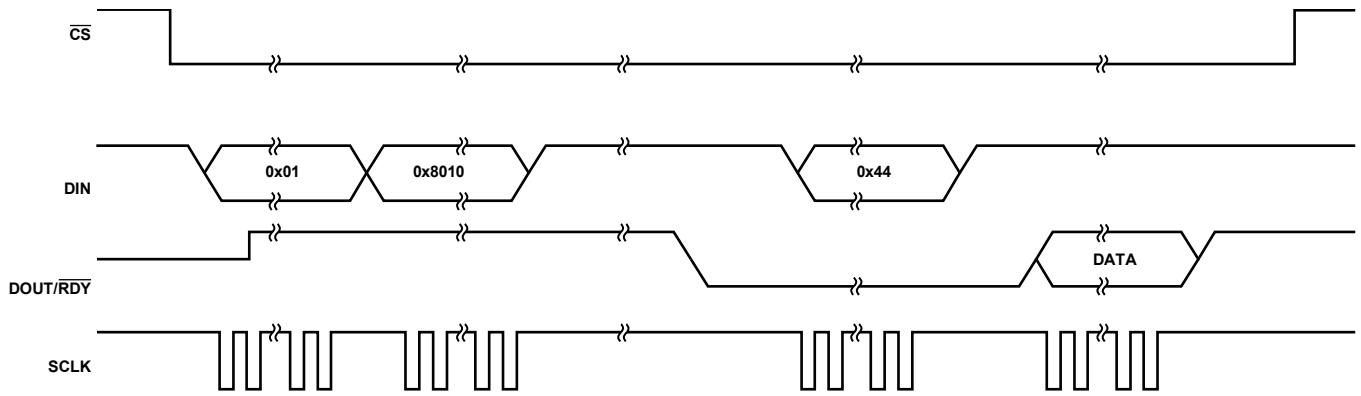

## タイミング図

図 2. 読出しサイクルのタイミング図

図 3. 書込みサイクルのタイミング図

## 絶対最大定格

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

表 3.

| Parameter                          | Rating                  |

|------------------------------------|-------------------------|

| AVDD1, AVDD2 to AVSS               | -0.3 V to +6.5 V        |

| AVDD1 to DGND                      | -0.3 V to +6.5 V        |

| IOVDD to DGND                      | -0.3 V to +6.5 V        |

| IOVDD to AVSS                      | -0.3 V to +7.5 V        |

| AVSS to DGND                       | -3.25 V to +0.3 V       |

| Analog Input Voltage to AVSS       | -0.3 V to AVDD1 + 0.3 V |

| Reference Input Voltage to AVSS    | -0.3 V to AVDD1 + 0.3 V |

| Digital Input Voltage to DGND      | -0.3 V to IOVDD + 0.3 V |

| Digital Output Voltage to DGND     | -0.3 V to IOVDD + 0.3 V |

| Analog Input/Digital Input Current | 10 mA                   |

| Operating Temperature Range        | -40°C to +105°C         |

| Storage Temperature Range          | -65°C to +150°C         |

| Maximum Junction Temperature       | 150 °C                  |

| Lead Soldering, Reflow Temperature | 260°C                   |

| ESD Rating (HBM)                   | 4 kV                    |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。長時間にわたり、デバイスを絶対最大定格を超える状態に置くと、デバイスの信頼性に影響を与えます。

## 熱抵抗

$\theta_{JA}$  は、表面実装パッケージ用の JEDEC テスト・ボードにハンダ付けされたデバイスで仕様規定されています。

表 4. 热抵抗

| Package Type                            | $\theta_{JA}$ | Unit |

|-----------------------------------------|---------------|------|

| 32-Lead, 5 mm × 5 mm LFCSP              |               |      |

| 1-Layer JEDEC Board                     | 138           | °C/W |

| 4-Layer JEDEC Board                     | 63            | °C/W |

| 4-Layer JEDEC Board with 9 Thermal Vias | 41            | °C/W |

## ESD に関する注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

## ピン配置およびピン機能の説明

図 4. ピン配置

表 5. ピン機能の説明

| ピン番号 | 記号          | タイプ <sup>1</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|-------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | AIN0/REF2-  | AI               | アナログ入力 0／リファレンス 2 負入力端子。REF2+ ピンと REF2- ピンの間にリファレンスを適用できます。REF2- の電圧範囲は AVSS ~ AVDD1 - 1 V です。アナログ入力 0 は、クロスポイント・マルチプレクサを通じて選択できます。リファレンス 2 は、セットアップ構成 (SETUPCONx) レジスタの REF_SELx ビットを通じて選択できます。                                                                                                                                                                                                                                                                                             |

| 2    | AIN1/REF2+  | AI               | アナログ入力 1／リファレンス 2 正入力端子。REF2+ ピンと REF2- ピンの間にリファレンスを適用できます。REF2+ の電圧範囲は AVDD1 ~ AVSS + 1 V です。アナログ入力 1 は、クロスポイント・マルチプレクサを通じて選択できます。リファレンス 2 は、セットアップ構成 (SETUPCONx) レジスタの REF_SELx ビットを通じて選択できます。                                                                                                                                                                                                                                                                                             |

| 3    | DNC         |                  | 接続なし。このピンは接続しないでください。                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4    | REGCAPA     | AO               | アナログ LDO レギュレータ出力です。1 μF のコンデンサを使用して、このピンを AVSS へデカップリングします。                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5    | AVSS        | P                | 負のアナログ電源。電源電圧範囲は 0 V ~ -2.75 V で、通常は 0 V に設定します。                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6    | AVDD1       | P                | アナログ電源電圧 1。この電圧範囲は、AVSS を基準にして 3.0 V (min) ~ 5.5 V (max) です。                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7    | AVDD2       | P                | アナログ電源電圧 2。この電圧範囲は、AVSS を基準にして、2 V ~ AVDD1 です。                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8    | PDSW        | AO               | AVSS に接続されたパワーダウン・スイッチ。このピンは、GPIOCON レジスタの PDSW ビットで制御されます。                                                                                                                                                                                                                                                                                                                                                                                                                                  |

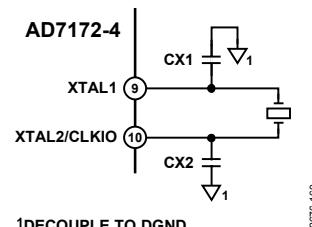

| 9    | XTAL1       | AI               | 水晶発振器用の入力 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10   | XTAL2/CLKIO | AI/DI            | 水晶発振器用の入力 2／クロック入出力。詳細については、表 28 の ADCMODE レジスタの CLOCKSEL ビットの設定を参照してください。                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11   | DOUT/RDY    | DO               | シリアル・データ出力／データ・レディ出力。DOUT/RDY は 2 つの機能を備えたピンです。このピンは、ADC の出力シフト・レジスタにアクセスするためのシリアル・データ出力ピンとして機能します。出力シフト・レジスタには、内蔵のデータ・レジスタまたはコントロール・レジスタからのデータを格納できます。データワード／コントロール・ワード情報が SCLK の立ち下がりエッジで、DOUT/RDY ピンに出力され、SCLK の立ち上がりエッジで有効になります。CS がハイ・レベルの場合、DOUT/RDY 出力はトライステートになります。CS がロー・レベルの場合、DOUT/RDY は、データ・レディー・ピンとして機能し、レジスタは読み出されず、ロー・レベルへ移行することで変換の完了を示します。変換後にデータが読み出されなかった場合、このピンは次のデータ更新の直前にハイ・レベルになり、次の更新が完了するまでハイ・レベルを維持します。DOUT/RDY の立ち下がりエッジは、プロセッサに対する割込みとして使用され、有効なデータが存在することを示します。 |

| 12   | DIN         | DI               | ADC の入力シフト・レジスタに対するシリアル・データ入力です。該当するレジスタは、コミュニケーション・レジスタのレジスタ・アドレス (RA) ビットにより指定され、ADC のコントロール・レジスタに転送されます。データは、SCLK の立ち上がりエッジに同期して入力されます。                                                                                                                                                                                                                                                                                                                                                   |

| 13   | SCLK        | DI               | シリアル・クロック入力です。このシリアル・クロック入力は、ADC との双方向データ転送に使用します。SCLK ピンにはシミュット・トリガー入力が内蔵されているため、光学絶縁されたアプリケーションのインターフェースに適しています。                                                                                                                                                                                                                                                                                                                                                                           |

| ピン番号 | 記号           | タイプ <sup>1</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|--------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14   | CS           | DI               | チップ・セレクト入力です。これは ADC を選択するのに使用するアクティブ・ローのロジック入力です。 <u>CS</u> を使用して、シリアル・バス上に複数のデバイスが存在するシステムで ADC を選択できます。 <u>CS</u> をロー・レベルに配線すれば、SCLK、DIN、DOUT ピンをデバイスとのインターフェースに使用して ADC を 3 線式モードで動作させることができます。 <u>CS</u> がハイ・レベルの場合、DOUT／RDY 出力はトライステートになります。                                                                                                                                                                          |

| 15   | <u>ERROR</u> | DI/O             | このピンは、次の 3 つのいずれかのモードで使用できます。<br>アクティブ・ローのエラー入力モード: このモードは、ステータス・レジスタの ADC_ERROR ビットで設定できます。<br>アクティブ・ローのオープンドレイン・エラー出力モード: ステータス・レジスタのエラー・ビットが <u>ERROR</u> ピンにマップされます。複数のデバイスの <u>ERROR</u> ピンを共通のプルアップ抵抗にまとめて接続して、あらゆるデバイスのエラーを監視できます。<br>汎用出力モード: このピンの状態は、GPIOCON レジスタの ERR_DAT ビットによって制御されます。ピンは、GPIO0 および GPIO1 ピンで使用される AVDD1 および AVSS レベルとは異なり、IOVDD と DGND 間の電圧を基準にしています。この場合、 <u>ERROR</u> ピンは、アクティブ・プルアップになります。 |

| 16   | <u>SYNC</u>  | DI               | 同期入力: 複数の AD7172-4 デバイスを使用している場合は、このピンによりデジタル・フィルタとアナログ変調器を同期できます。                                                                                                                                                                                                                                                                                                                                                          |

| 17   | IOVDD        | P                | デジタル入出力電源電圧。IOVDD 電圧範囲は 2 V ~ 5 V です。IOVDD は AVDD1 および AVDD2 から独立しています。例えば、AVDD1 または AVDD2 が 5 V の場合に、IOVDD は 3.3 V で動作でき、その逆も可能です。AVSS に -2.5 V をかけた場合、IOVDD にかける電圧は 3.6 V を超えてはいけません。                                                                                                                                                                                                                                     |

| 18   | DGND         | P                | デジタル・グラウンド。                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 19   | REGCAPD      | AO               | デジタル LDO レギュレータ出力: このピンはデカップリング専用です。1 μF のコンデンサを使用して、このピンを DGND へデカップリングします。                                                                                                                                                                                                                                                                                                                                                |

| 20   | GPIO0        | DI/O             | 汎用の入出力 0。このピンのロジック入出力は、AVDD1 および AVSS 電源を基準にしています。                                                                                                                                                                                                                                                                                                                                                                          |

| 21   | GPIO1        | DI/O             | 汎用の入出力 1。このピンのロジック入出力は、AVDD1 および AVSS 電源を基準にしています。                                                                                                                                                                                                                                                                                                                                                                          |

| 22   | GPO2         | DO               | 汎用出力。このピンのロジック出力は、AVDD1 および AVSS 電源を基準にしています。                                                                                                                                                                                                                                                                                                                                                                               |

| 23   | AIN2         | AI               | アナログ入力 2: アナログ入力 2 は、クロスポイント・マルチプレクサから選択可能。                                                                                                                                                                                                                                                                                                                                                                                 |

| 24   | AIN3         | AI               | アナログ入力 3: アナログ入力 3 は、クロスポイント・マルチプレクサから選択可能。                                                                                                                                                                                                                                                                                                                                                                                 |

| 25   | AIN4         | AI               | アナログ入力 4: アナログ入力 4 は、クロスポイント・マルチプレクサから選択可能。                                                                                                                                                                                                                                                                                                                                                                                 |

| 26   | AIN5         | AI               | アナログ入力 5: アナログ入力 5 は、クロスポイント・マルチプレクサから選択可能。                                                                                                                                                                                                                                                                                                                                                                                 |

| 27   | AIN6         | AI               | アナログ入力 6: アナログ入力 6 は、クロスポイント・マルチプレクサから選択可能。                                                                                                                                                                                                                                                                                                                                                                                 |

| 28   | AIN7         | AI               | アナログ入力 7: アナログ入力 7 は、クロスポイント・マルチプレクサから選択可能。                                                                                                                                                                                                                                                                                                                                                                                 |

| 29   | AIN8         | AI               | アナログ入力 8: アナログ入力 8 は、クロスポイント・マルチプレクサから選択可能。                                                                                                                                                                                                                                                                                                                                                                                 |

| 30   | GPO3         | DO               | 汎用出力。このピンのロジック出力は、AVDD1 および AVSS 電源を基準にしています。                                                                                                                                                                                                                                                                                                                                                                               |

| 31   | REF-         | AI               | リファレンス 1 入力負端子。REF- の入力電圧範囲は AVSS ~ AVDD1 - 1 V です。リファレンス 1 は、セットアップ構成 (SETUPCONx) レジスタの REF_SELx ビットを通じて選択できます。                                                                                                                                                                                                                                                                                                            |

| 32   | REF+         | AI               | リファレンス 1 入力正端子。REF+ と REF- の間にリファレンスを適用できます。REF+ の入力電圧範囲は AVDD1 ~ AVSS + 1 V です。リファレンス 1 は、セットアップ構成 (SETUPCONx) レジスタの REF_SELx ビットを通じて選択できます。                                                                                                                                                                                                                                                                               |

|      | EP           | P                | 露出パッドです。露出パッドは、パッケージの機械的強度と放熱効果を高めるため、プリント基板 (PCB) と同様のパッドにはんだ付けします(露出パッドの下)。露出パッドは、PCB のこのパッドを通じて AVSS に接続する必要があります。                                                                                                                                                                                                                                                                                                       |

<sup>1</sup> AI = アナログ入力、AO = アナログ出力、DI = デジタル入力、DO = デジタル出力、DIO = デジタル入力／出力、P = 電源。

## 代表的な性能特性

特に指定のない限り、AVDD1 = 5 V、AVDD2 = 5 V、IOVDD = 3.3 V、TA = 25 °C。

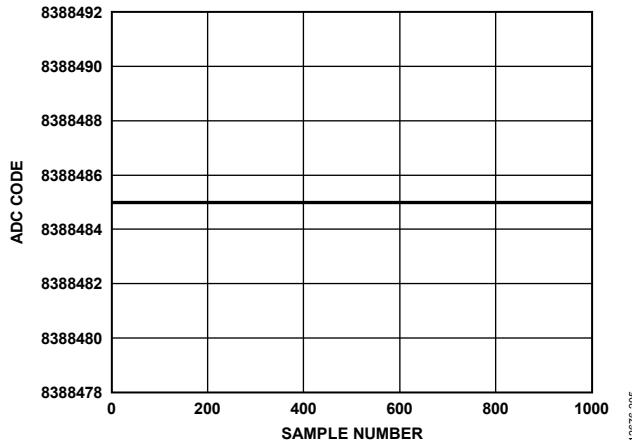

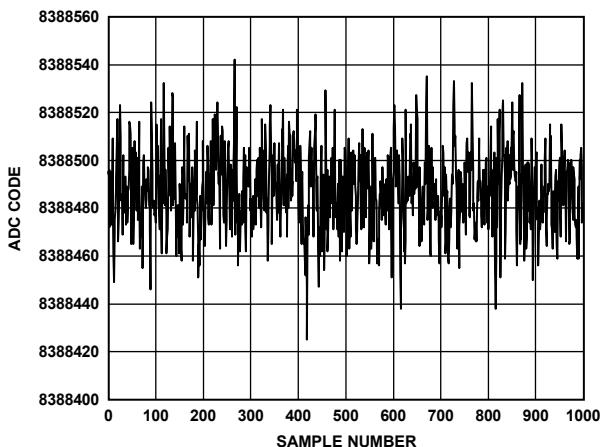

図 5. ノイズ (アナログ入力バッファはディスエーブル、 $V_{REF} = 5$  V、出力データ・レート = 1.25 SPS)

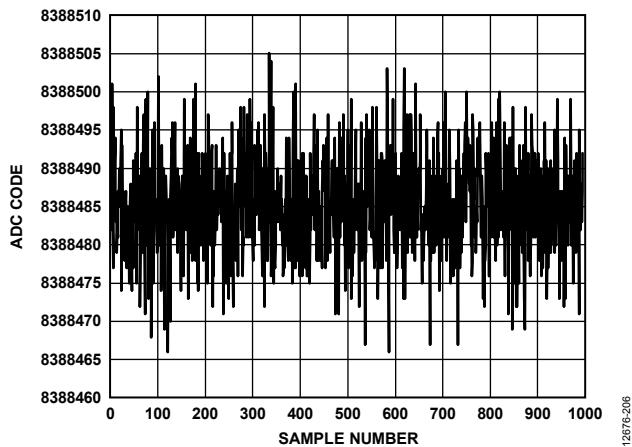

図 6. ノイズ (アナログ入力バッファはディスエーブル、 $V_{REF} = 5$  V、出力データ・レート = 2.6 kSPS)

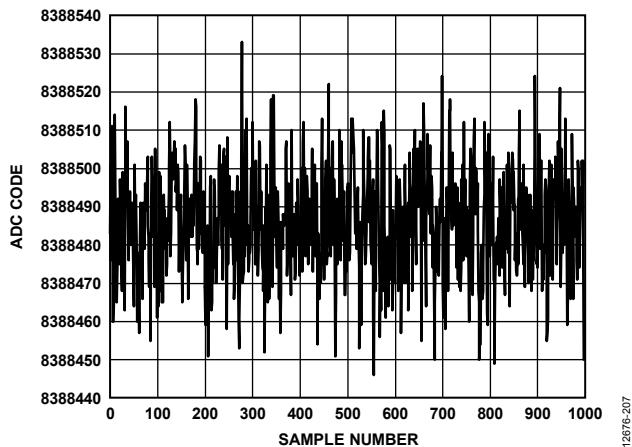

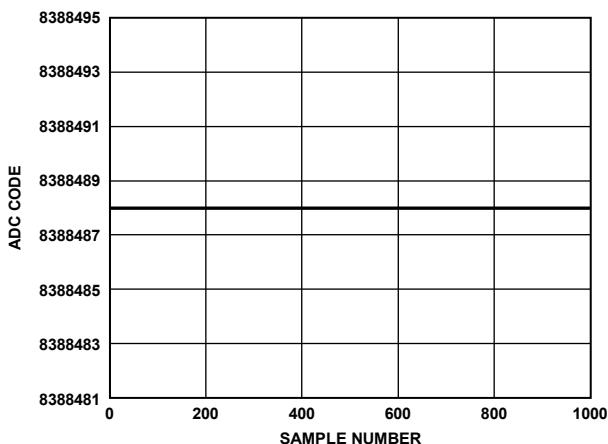

図 7. ノイズ (アナログ入力バッファはディスエーブル、 $V_{REF} = 5$  V、出力データ・レート = 31.25 kSPS)

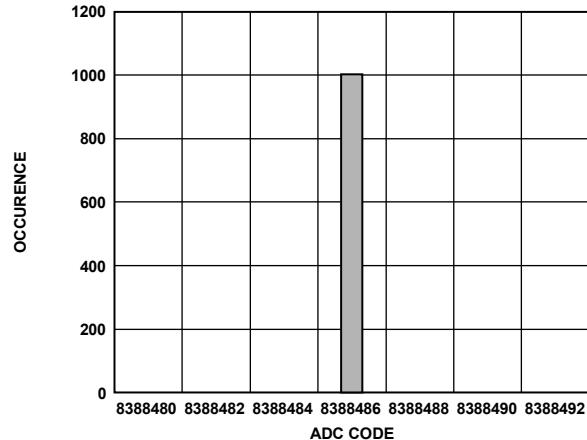

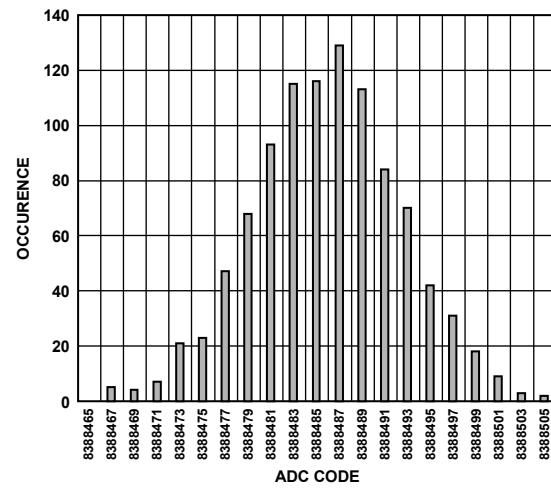

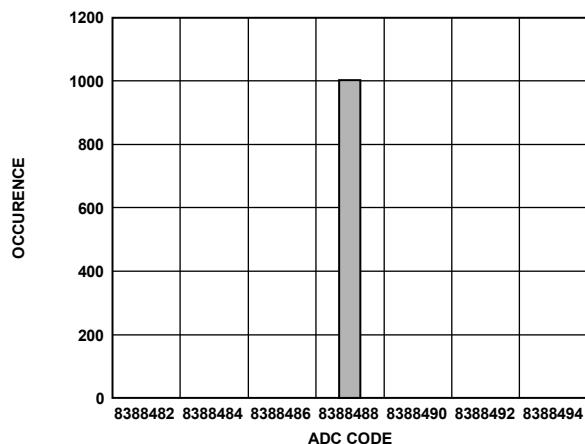

図 8. ヒストグラム (アナログ入力バッファはディスエーブル、 $V_{REF} = 5$  V、出力データ・レート = 1.25 SPS)

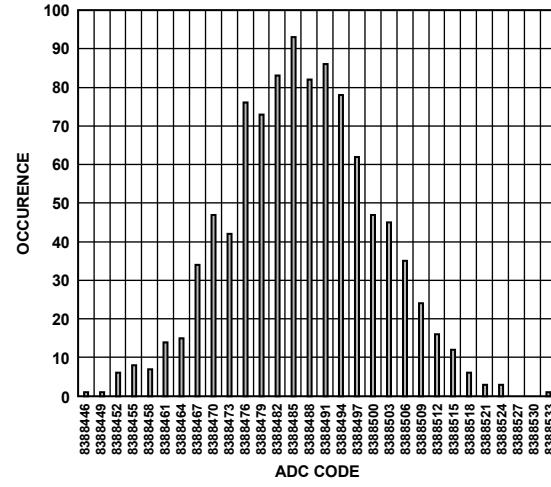

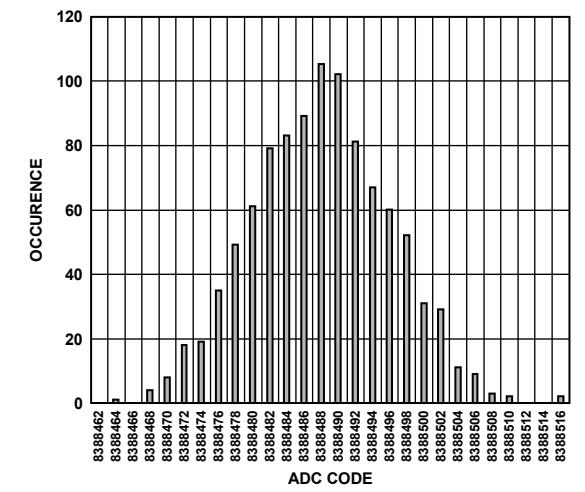

図 9. ヒストグラム (アナログ入力バッファはディスエーブル、 $V_{REF} = 5$  V、出力データ・レート = 2.6 kSPS)

図 10. ヒストグラム (アナログ入力バッファはディスエーブル、 $V_{REF} = 5$  V、出力データ・レート = 31.25 kSPS)

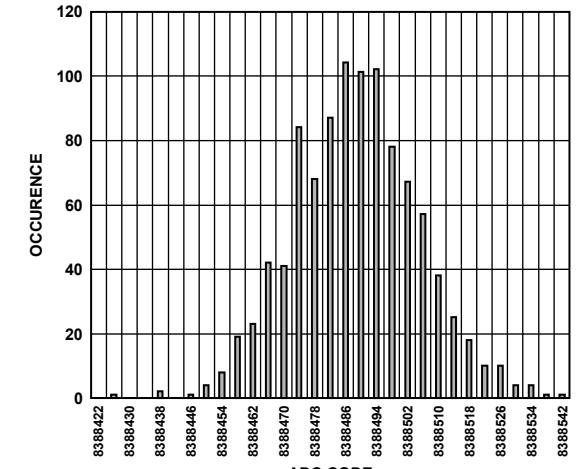

図 11. ノイズ(アナログ入力バッファはイネーブル、 $V_{REF} = 5\text{ V}$ 、出力データ・レート = 1.25 SPS)

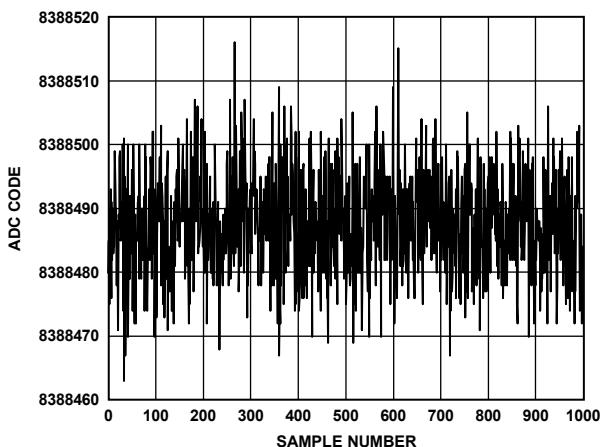

図 12. ノイズ(アナログ入力バッファはイネーブル、 $V_{REF} = 5\text{ V}$ 、出力データ・レート = 2.6 kSPS)

図 13. ノイズ(アナログ入力バッファはイネーブル、 $V_{REF} = 5\text{ V}$ 、出力データ・レート = 31.25 kSPS)

図 14. ヒストグラム(アナログ入力バッファはイネーブル、 $V_{REF} = 5\text{ V}$ 、出力データ・レート = 1.25 SPS)

図 15. ヒストグラム(アナログ入力バッファはイネーブル、 $V_{REF} = 5\text{ V}$ 、出力データ・レート = 2.6 kSPS)

図 16. ヒストグラム(アナログ入力バッファはイネーブル、 $V_{REF} = 5\text{ V}$ 、出力データ・レート = 31.25 kSPS)

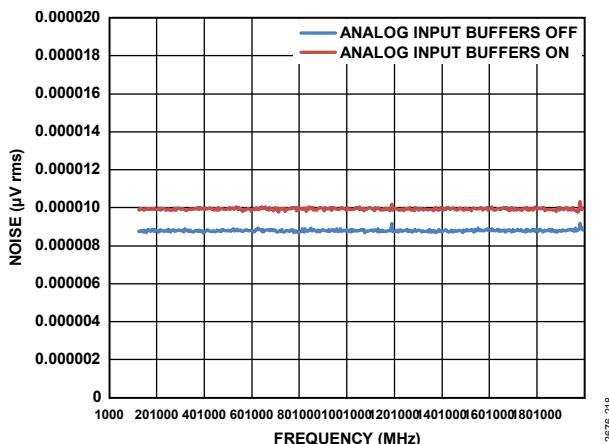

図 17. ノイズと外部マスター・クロック周波数の関係、

アナログ入力バッファはオン／オフ

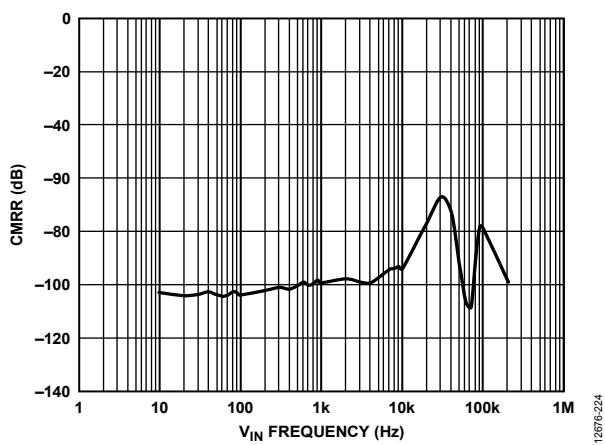

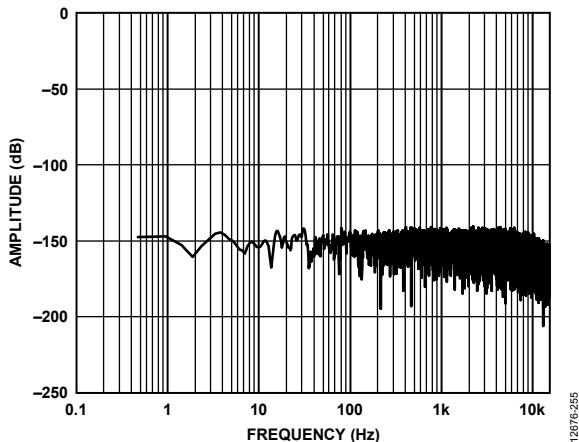

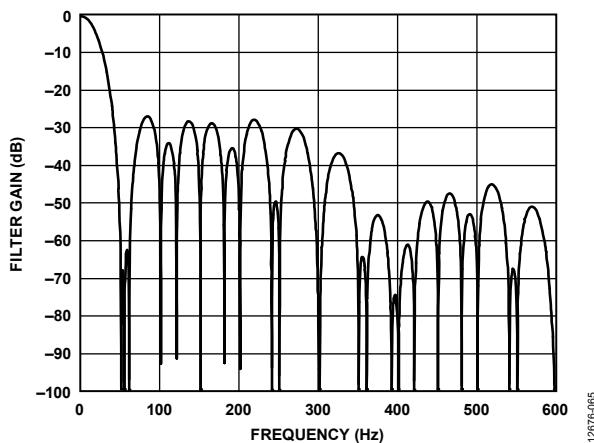

図 18. コモンモード除去比 (CMRR) と  $V_{IN}$  周波数の関係

( $V_{IN} = 0.1 \text{ V}$ 、出力データ・レート = 31.25 kSPS)

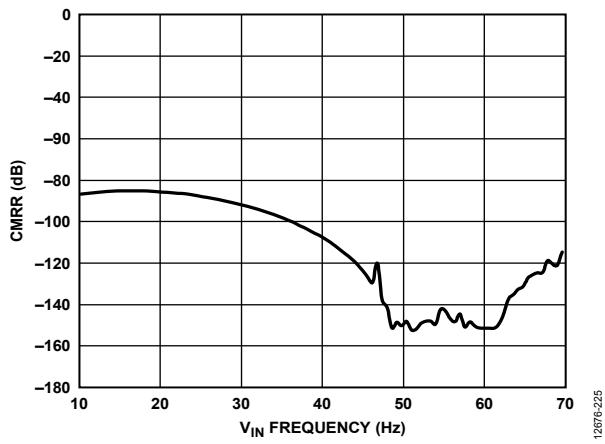

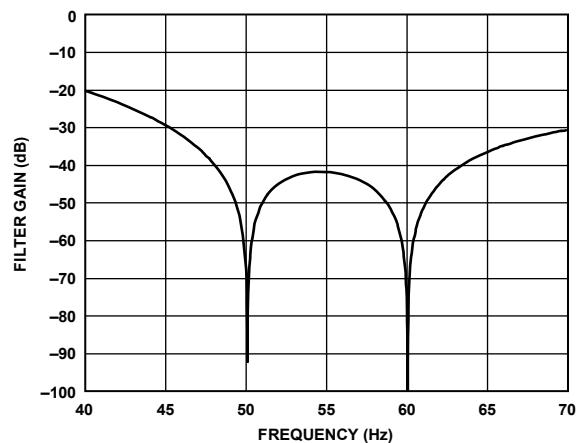

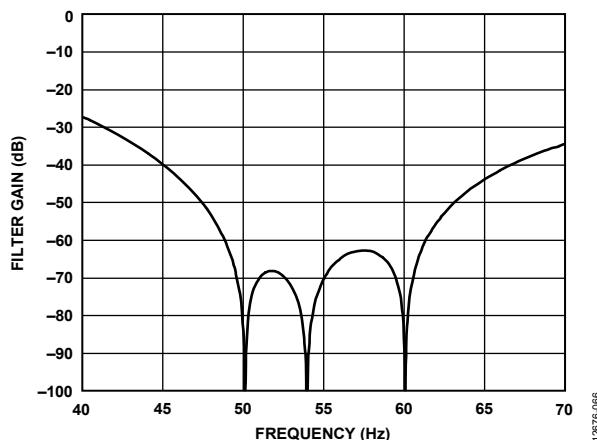

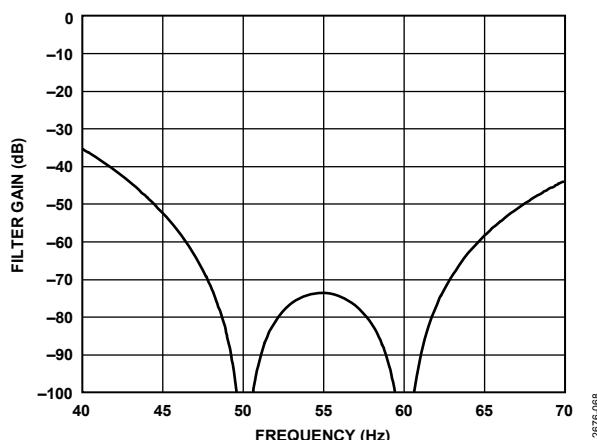

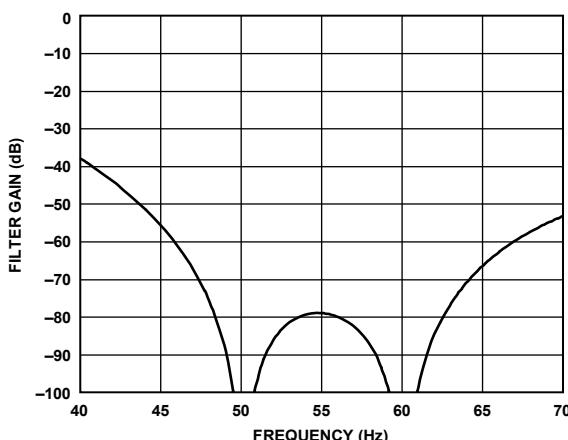

図 19. コモンモード除去比 (CMRR) と  $V_{IN}$  周波数の関係

( $V_{IN} = 0.1 \text{ V}$ 、10 Hz ~ 70 Hz、出力データ・

レート = 20 SPS 強化フィルタ)

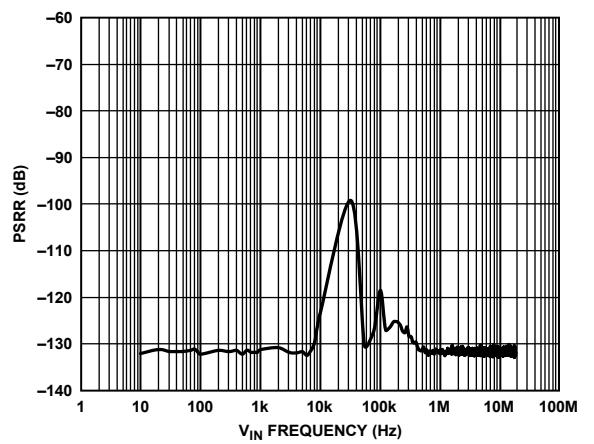

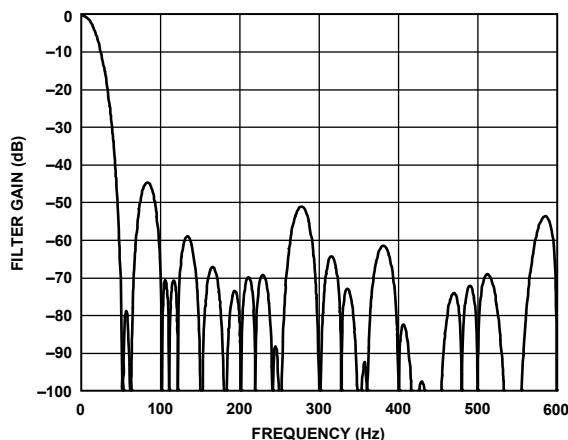

図 20. 電源電圧変動除去比 (PSRR) と  $V_{IN}$  周波数の関係

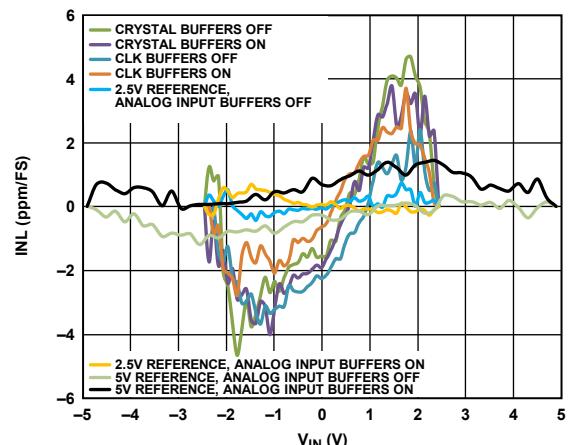

図 21. 積分非直線性 (INL) と  $V_{IN}$  (差動入力) の

関係

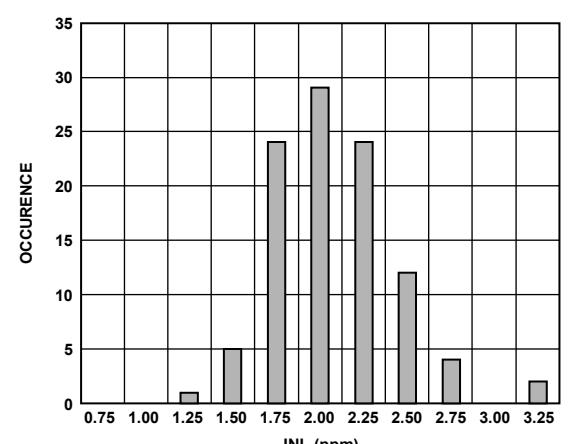

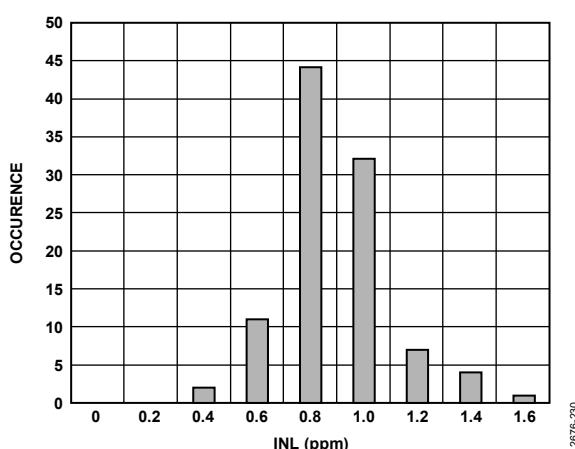

図 22. INL 分布ヒストグラム (差動入力、すべての入力バッ

ファはイネーブル、 $V_{REF} = 2.5 \text{ V}$  外部、100 ユニット)

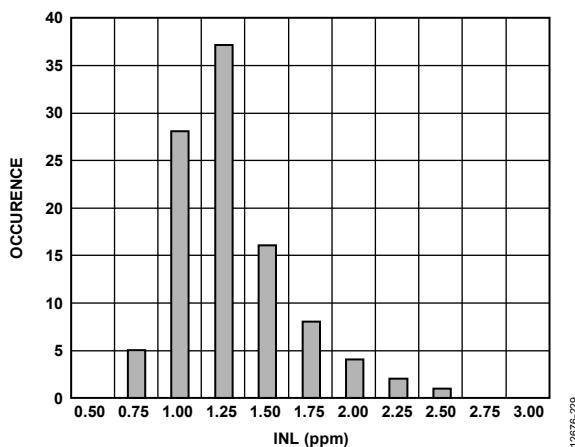

図 23. INL 分布ヒストグラム (差動入力、すべての入力バッファはディスエーブル、 $V_{REF} = 2.5$  V 外部、100 ユニット)

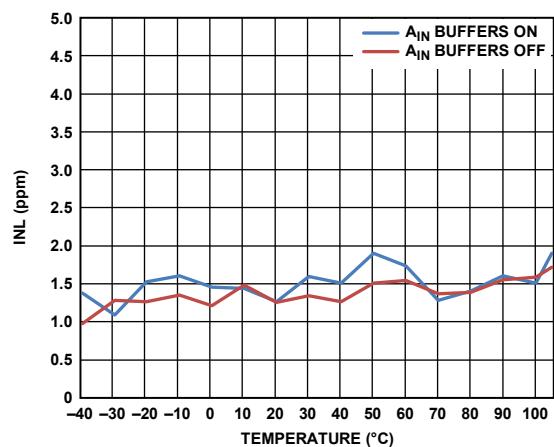

図 26. INL の温度特性 (差動入力、 $V_{REF} = 2.5$  V 外部)

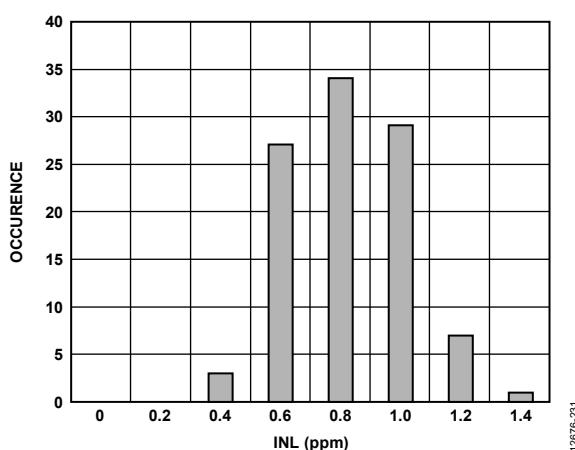

図 24. INL 分布ヒストグラム (すべての入力バッファはイネーブル、差動入力、 $V_{REF} = 5$  V 外部、100 ユニット)

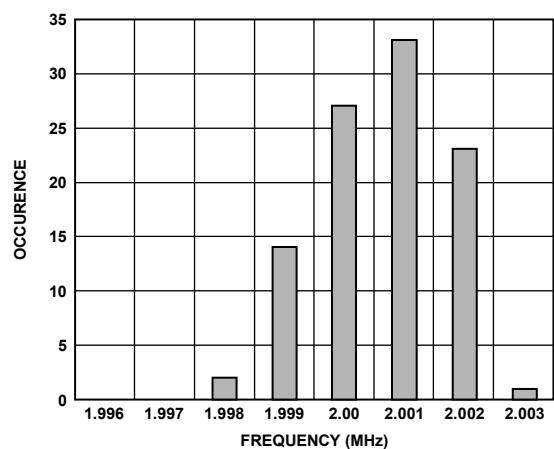

図 27. 内部発振器の周波数／精度分布ヒストグラム (100 ユニット)

図 25. INL 分布ヒストグラム (すべてのアナログ入力バッファはディスエーブル、差動入力、 $V_{REF} = 5$  V 外部、100 ユニット)

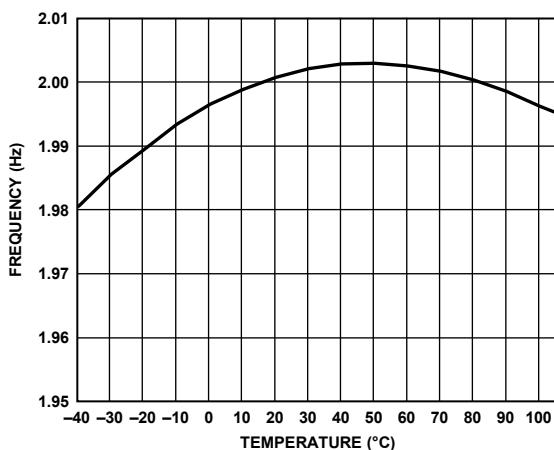

図 28. 内蔵発振器周波数と温度の関係

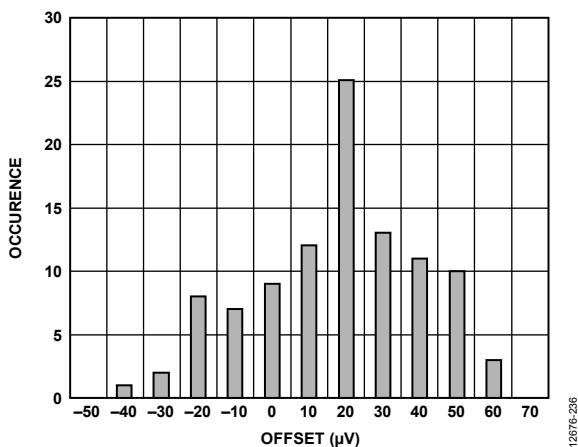

図 29. オフセット誤差分布ヒストグラム

(内部ショート、100 ユニット)

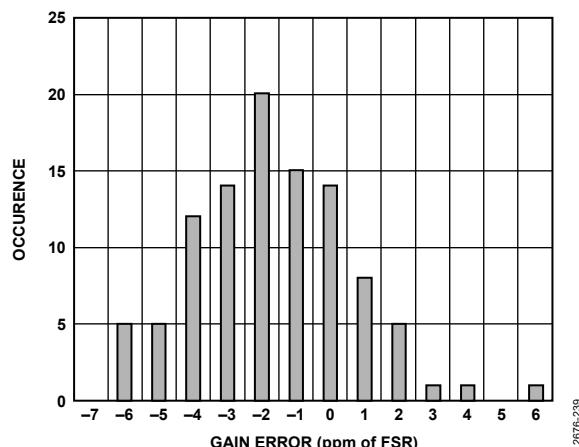

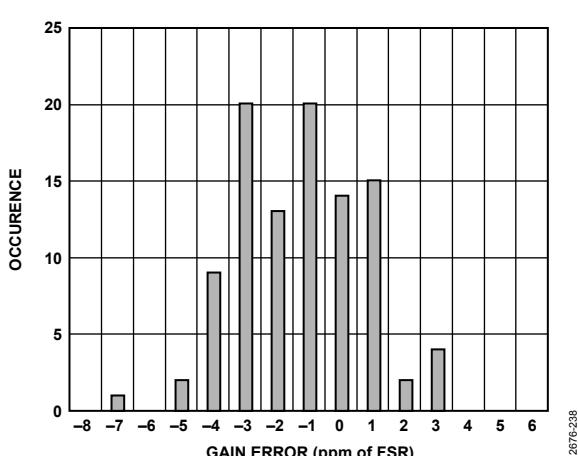

図 32. ゲイン誤差分布ヒストグラム

(すべての入力バッファはディスエーブル、100 ユニット)

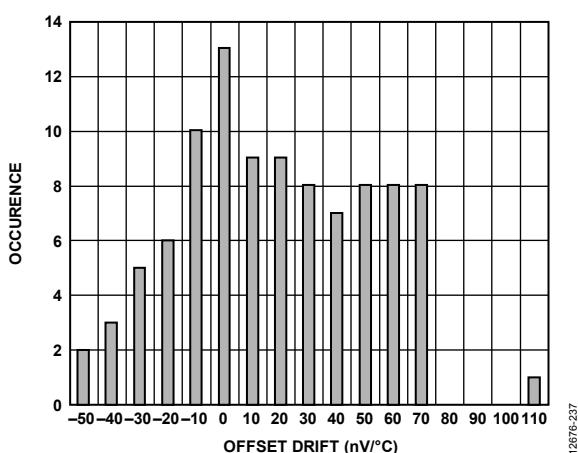

図 30. オフセット誤差ドリフト分布ヒストグラム

(内部ショート、100 ユニット)

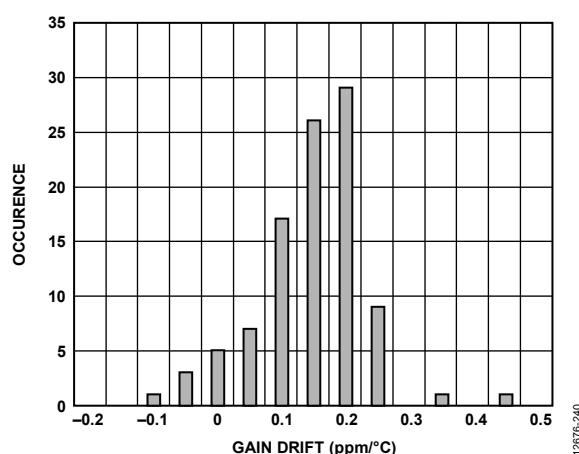

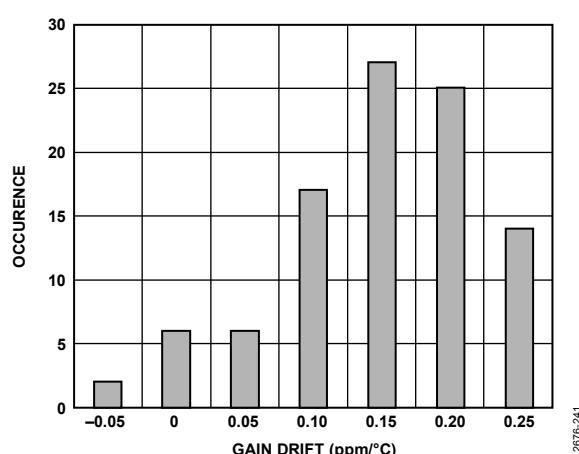

図 33. ゲイン・ドリフト分布ヒストグラム

(すべての入力バッファはイネーブル、100 ユニット)

図 31. ゲイン誤差分布ヒストグラム

(すべての入力バッファはイネーブル、100 ユニット)

図 34. ゲイン・ドリフト分布ヒストグラム

(すべての入力バッファはディスエーブル、100 ユニット)

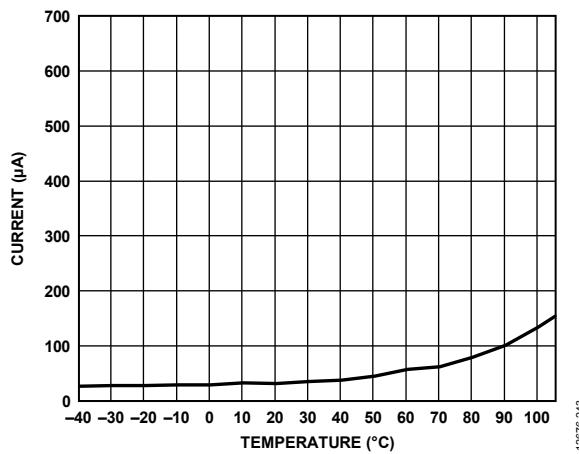

図 35. 消費電流と温度の関係 (スタンバイ・モード)

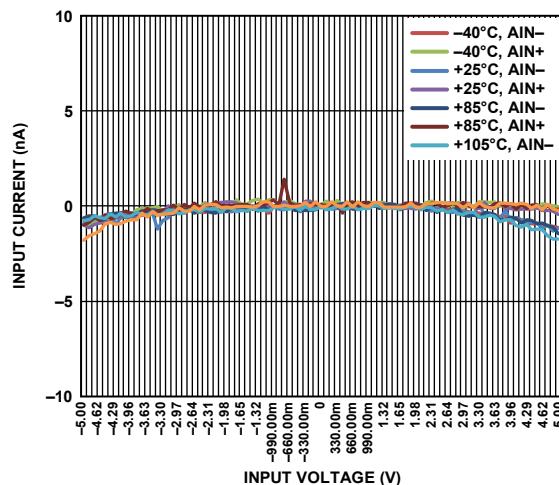

図 37. アナログ入力電流と入力電圧の関係

( $V_{CM} = 2.5$  V)

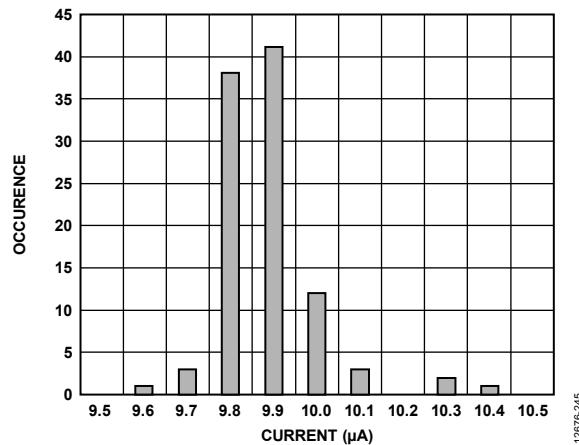

図 36. バーンアウト電流分布ヒストグラム (100 ユニット)

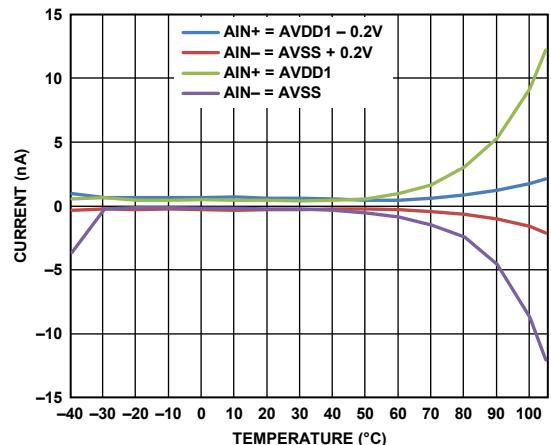

図 38. アナログ入力電流と温度の関係

## ノイズ特性と分解能

表 6 と表 7 に、AD7172-4 の各種出力データ・レートとフィルタの組み合わせによる AD7172-4 の rms ノイズ、ピーク to ピーク・ノイズ、実効分解能、およびノイズ・フリー(ピーク to ピーク) 分解能を示します。ここに示している値は、5 V のリファレンス電圧を使用した場合のバイポーラ入力範囲です。これらの値は代表値であり、ADC の单一チャンネルの差動入力端子

表 6. 出力データ・レートと RMS ノイズおよびピーク to ピーク分解能の関係 (Sinc5 + Sinc1 フィルタ (デフォルト) を使用)<sup>1</sup>

| Output Data Rate (SPS) | RMS Noise ( $\mu$ V rms) | Effective Resolution (Bits) | Peak-to-Peak Noise ( $\mu$ V p-p) | Peak-to-Peak Resolution (Bits) |

|------------------------|--------------------------|-----------------------------|-----------------------------------|--------------------------------|

| Input Buffers Disabled |                          |                             |                                   |                                |

| 31,250                 | 8.2                      | 20.2                        | 66                                | 17.2                           |

| 15,625                 | 7.0                      | 20.4                        | 52                                | 17.5                           |

| 10,417                 | 6.0                      | 20.7                        | 45                                | 17.8                           |

| 1007                   | 2.2                      | 22.2                        | 15                                | 19.3                           |

| 59.52                  | 0.48                     | 24                          | 3.2                               | 21.6                           |

| 49.68                  | 0.47                     | 24                          | 3.1                               | 21.6                           |

| 16.63                  | 0.25                     | 24                          | 1.6                               | 22.6                           |

| 1.25                   | 0.088                    | 24                          | 0.32                              | 24                             |

| Input Buffers Enabled  |                          |                             |                                   |                                |

| 31,250                 | 9.5                      | 20                          | 74                                | 17                             |

| 15,625                 | 8.2                      | 20.2                        | 63                                | 17.3                           |

| 10,417                 | 7.1                      | 20.4                        | 53                                | 17.5                           |

| 1007                   | 2.6                      | 21.9                        | 16                                | 19.3                           |

| 59.52                  | 0.62                     | 24                          | 3.6                               | 21.4                           |

| 49.68                  | 0.53                     | 24                          | 3.3                               | 21.5                           |

| 16.63                  | 0.32                     | 24                          | 1.7                               | 22.2                           |

| 1.25                   | 0.089                    | 24                          | 0.35                              | 24                             |

<sup>1</sup> 選択されたレートのみ: 1000 サンプル

表 7. 出力データ・レートに対する RMS ノイズおよびピーク to ピーク分解能の関係 (Sinc3 フィルタを使用)<sup>1</sup>

| Output Data Rate (SPS) | RMS Noise ( $\mu$ V rms) | Effective Resolution (Bits) | Peak-to-Peak Noise ( $\mu$ V p-p) | Peak-to-Peak Resolution (Bits) |

|------------------------|--------------------------|-----------------------------|-----------------------------------|--------------------------------|

| Input Buffers Disabled |                          |                             |                                   |                                |

| 31,250                 | 211                      | 15.5                        | 1600                              | 12.5                           |

| 15,625                 | 27.2                     | 18.5                        | 205                               | 15.6                           |

| 10,417                 | 7.9                      | 20.3                        | 57                                | 17.4                           |

| 1008                   | 1.6                      | 22.6                        | 11                                | 19.8                           |

| 59.98                  | 0.38                     | 24                          | 2.5                               | 21.9                           |

| 50                     | 0.35                     | 24                          | 2.3                               | 22                             |

| 16.67                  | 0.21                     | 24                          | 1.1                               | 23.1                           |

| 1.25                   | 0.054                    | 24                          | 0.27                              | 24                             |

| Input Buffers Enabled  |                          |                             |                                   |                                |

| 31,250                 | 212                      | 15.5                        | 1600                              | 12.5                           |

| 15,625                 | 27.7                     | 18.5                        | 210                               | 15.5                           |

| 10,417                 | 8.5                      | 20.2                        | 63                                | 17.3                           |

| 1008                   | 1.8                      | 22.4                        | 13                                | 19.6                           |

| 59.98                  | 0.45                     | 24                          | 2.8                               | 21.8                           |

| 50                     | 0.44                     | 24                          | 2.5                               | 22                             |

| 16.67                  | 0.24                     | 24                          | 1.2                               | 23                             |

| 1.25                   | 0.073                    | 24                          | 0.29                              | 24                             |

<sup>1</sup> 選択されたレートのみ: 1000 サンプル

に 0 V を入力して、連続変換しているときに生成される値です。ピーク to ピーク分解能は、ピーク to ピーク・ノイズを基に計算された値であることに注意してください。このピーク to ピーク分解能は、コード・フリッカが生じない分解能を示します。

## 評価開始にあたって

AD7172-4 は、設定機能の優れた、高速セトリングおよび高分解能のマルチプレクス型 ADC で、次の機能を備えています。

- 4 個の完全差動入力、または 8 個のシングルエンド入力。

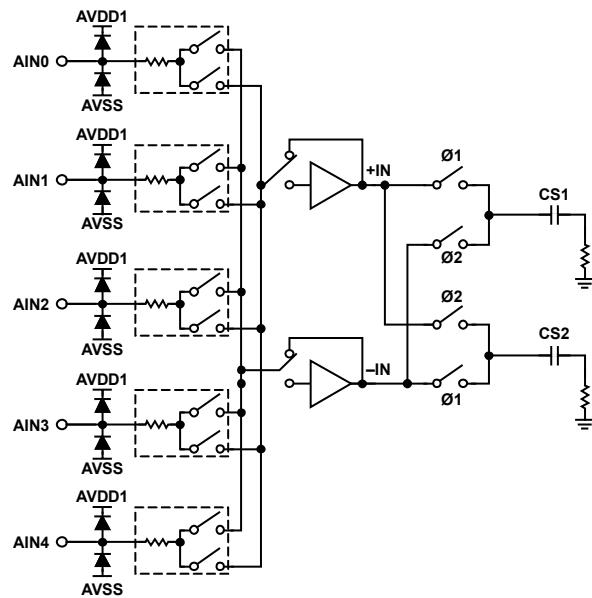

- 変換する入力信号としてあらゆるアナログ入力の組み合わせを選択し、それらを変調器の正入力または負入力にルーティングするクロスポイント・マルチプレクサ。

- 真のレール to レール・バッファ付きアナログ入力およびリファレンス入力。

- あらゆるアナログ入力を基準とした完全差動入力またはシングルエンド入力。

- チャンネルごとに構成可能。最大 8 個のセットアップを定義可能。各チャンネルに個別のセットアップをマップ可能。各セットアップでは、バッファのイネーブル/ディスエーブル、ゲインおよびオフセット補正、フィルタ・タイプ、出力データ・レートを設定したり、リファレンス源を選択したりできます。

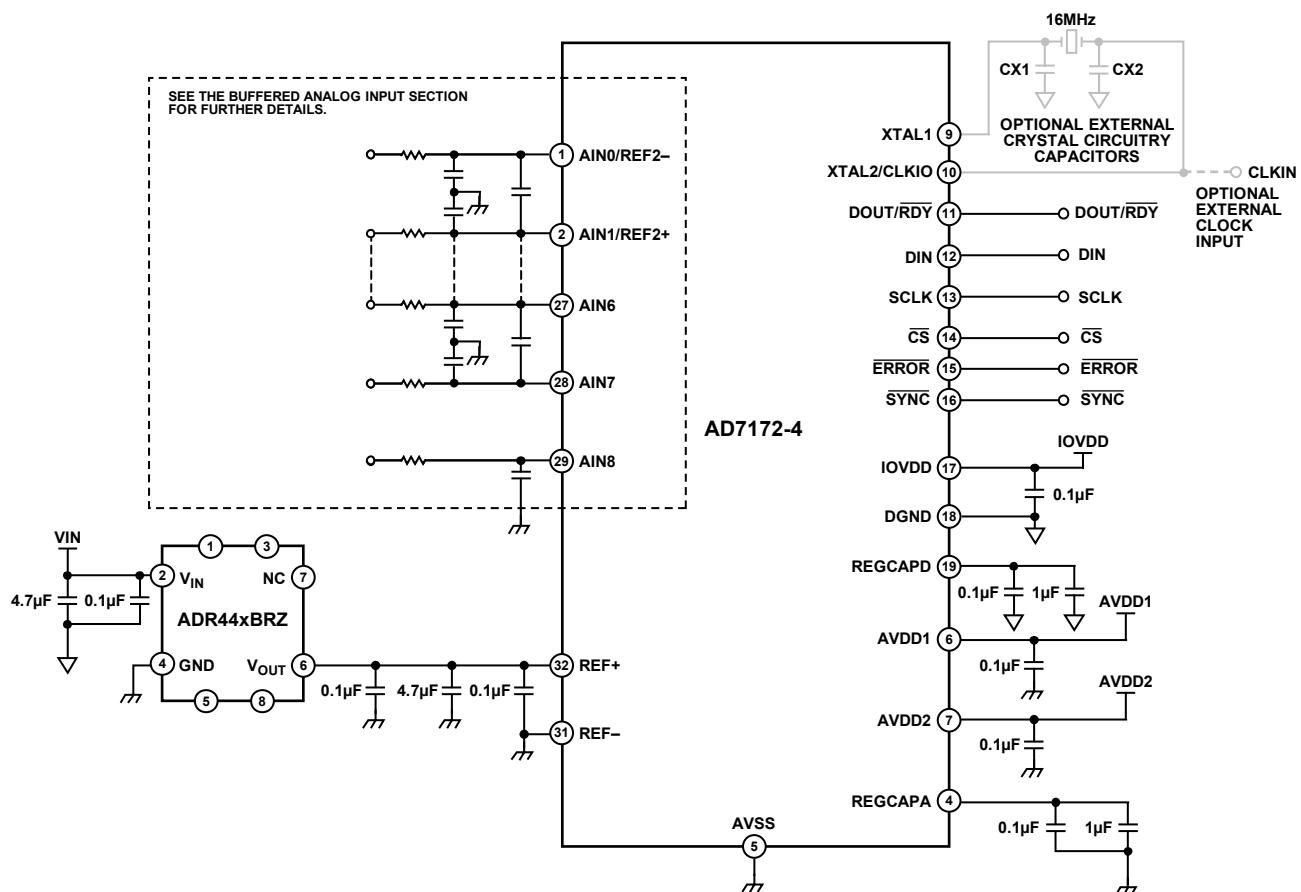

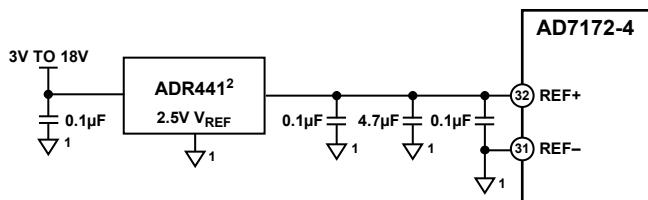

AD7172-4 は、アナログおよびデジタル回路用に 2 つの個別のリニア電圧レギュレータ・ブロックを内蔵しています。アナログ LDO レギュレータは、AVDD2 電源を 1.8 V に調整して ADC コアに供給します。接続を簡単にするには、AVDD1 と AVDD2 電源を接続します。システム内に 2 V (min) ~ 5.5 V (max) のクリーンなアナログ電源レールがすでに存在する場合は、この電源を AVDD2 入力に接続して消費電力を抑えることができます。

図 39. 代表的な接続図

デジタル IOVDD 電源のリニア電圧レギュレータは同様な機能を備えており、内蔵デジタル・フィルタリング用に IOVDD ピンに入力された電圧を 1.8 V に調整します。シリアル・インターフェース信号は、常にピンの IOVDD 電源で動作します。つまり、IOVDD ピンに 3.3 V が入力されている場合、インターフェース・ロジック入出力はこのレベルで動作します。

AD7172-4 は、さまざまなアプリケーションで使用でき、高い分解能と精度を提供できます。これらのアプリケーションの例を以下に示します。

- 内部マルチプレクサを使用したアナログ入力チャンネルの高速スキャニング

- GPIO からの自動制御と外部マルチプレクサを使用したアナログ入力チャンネルの高速スキャニング

- チャンネル・スキャニング・アプリケーションまたはチャンネルごとの ADC アプリケーションでの低速時の高分解能

- チャンネルごとに 1 個の ADC: 高速で低遅延の出力により、外部マイクロコントローラ、DSP、または FPGA でのアプリケーション固有のフィルタリングが可能

## 電源

AD7172-4 には、次の 3 つの独立した電源ピン AVDD1、AVDD2、IOVDD があります。AD7172-4 には、電源シーケンスに特定の要件はありません。すべての電源が安定したら、デバイスをリセットする必要があります。デバイスのリセット方法については、AD7172-4 のリセットのセクションを参照してください。

AVDD1 は、クロスポイント・マルチプレクサの他に、内蔵アナログ入力バッファとリファレンス入力バッファを駆動します。AVDD1 は AVSS を基準としており、AVDD1 – AVSS = 3.3 V または 5 V です。AVDD1 と AVSS には、3.3 V または 5 V の単電源、あるいは  $\pm 1.65$  V または  $\pm 2.5$  V の分離電源を使用できます。分離電源動作により、真のバイポーラ入力が可能になります。分離電源を使用する場合は、絶対最大定格を考慮してください（絶対最大定格のセクションを参照）。

AVDD2 は、内部 1.8 V アナログ LDO レギュレータを駆動します。このレギュレータは、ADC コアも駆動します。AVDD2 は AVSS を基準としており、AVDD2 から AVSS への電圧範囲は 5.5 V (max) ~ 2 V (min) です。

IOVDD は、内部 1.8 V デジタル LDO レギュレータを駆動します。このレギュレータは、ADC のデジタル・ロジックも駆動します。IOVDD は、ADC の SPI インターフェースの電圧レベルを設定します。IOVDD は DGND を基準としており、IOVDD から DGND への電圧範囲は 5.5 V (max) ~ 2 V (min) です。

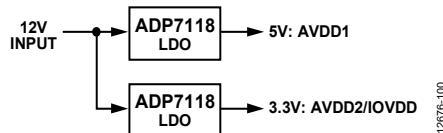

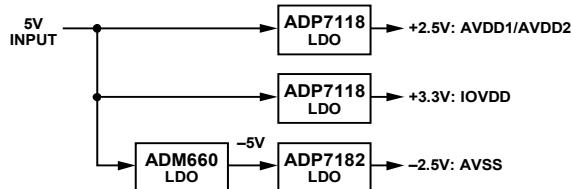

## 推奨リニア電圧レギュレータ

[ADP7118](#) は正電源レールを提供し、必要な電源構成に応じて AVDD1/IOVDD 用に 5 V または 3.3 V の単電源あるいは両電源を生成します。ADP7118 は、最大 20 V の入力電圧で動作できます。

図 40. 単電源リニア電圧レギュレータ

ADM660 と [ADP7182](#) は、バイポーラ構成での AVSS 用のクリーンな負側レールを生成し、最適なコンバータ性能を発揮します。

12876-101

図 41. バイポーラ AD7172-4 電源レール

表 8. 推奨パワー・マネジメント・デバイス

| 製品      | 説明                               |

|---------|----------------------------------|

| ADP7118 | 20 V、200 mA、低ノイズ、CMOS LDO レギュレータ |

| ADP7182 | -28 V、-200 mA、低ノイズ、リニア電圧レギュレータ   |

| ADM660  | CMOS スイッチド・キャパシタ電圧コンバータ          |

## デジタル通信

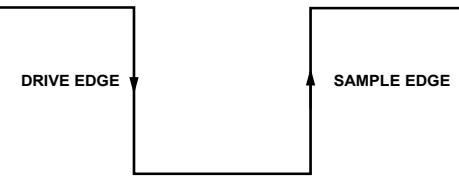

AD7172-4 は、QSPI™、MICROWIRE、および DSP と互換性のある 3 線式または 4 線式の SPI インターフェースを備えています。このインターフェースは、SPI モード 3 で動作し、CS がロー・レベルに接続したままでも動作します。SPI モード 3 の場合、SCLK ピンはアイドル・ハイになり、SCLK の立ち下りエッジは起動エッジ、立ち上がりエッジはサンプル・エッジになります。すなわち、データは立ち下りの起動エッジに同期して出力され、立ち上がりのサンプル・エッジに同期して入力されます。

12876-032

図 42. SPI モード 3 SCLK のエッジ

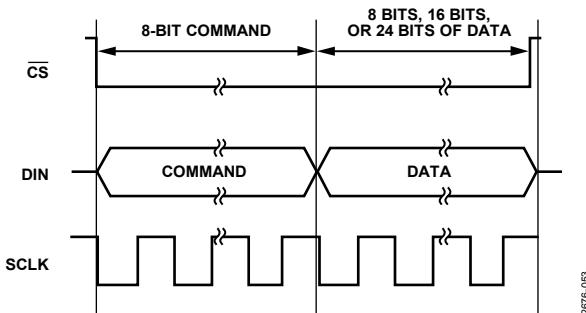

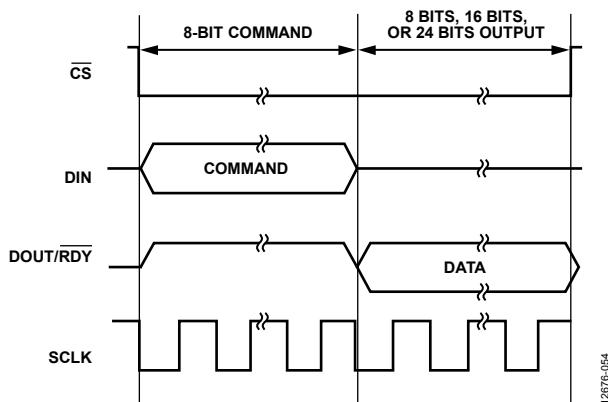

## ADC のレジスタ・マップへのアクセス

コミュニケーション・レジスタは、ADC 内のレジスタ・マップ全体へのアクセスを制御しています。このレジスタは 8 ビットの書き込み専用レジスタです。パワーアップ時またはリセット後に、デジタル・インターフェースは、デフォルトでコミュニケーション・レジスタへの書き込み待ちの状態になります。したがって、すべての通信はコミュニケーション・レジスタへの書き込みによって開始されます。

コミュニケーション・レジスタへのデータ書き込みによって、どのレジスタにアクセスするか決定され、次の動作が書き込みまたは読み出しのどちらであるかも決定されます。RA ビット (レジスタ 0x00 のビット[5:0]) により、どのレジスタに対して読み出しされたか書き込みが実行されるか決まります。

選択されたレジスタへの読み出し動作または書き込み動作が完了すると、インターフェースはデフォルト状態、すなわち、コミュニケーション・レジスタに対する書き込み動作待ちの状態に戻ります。

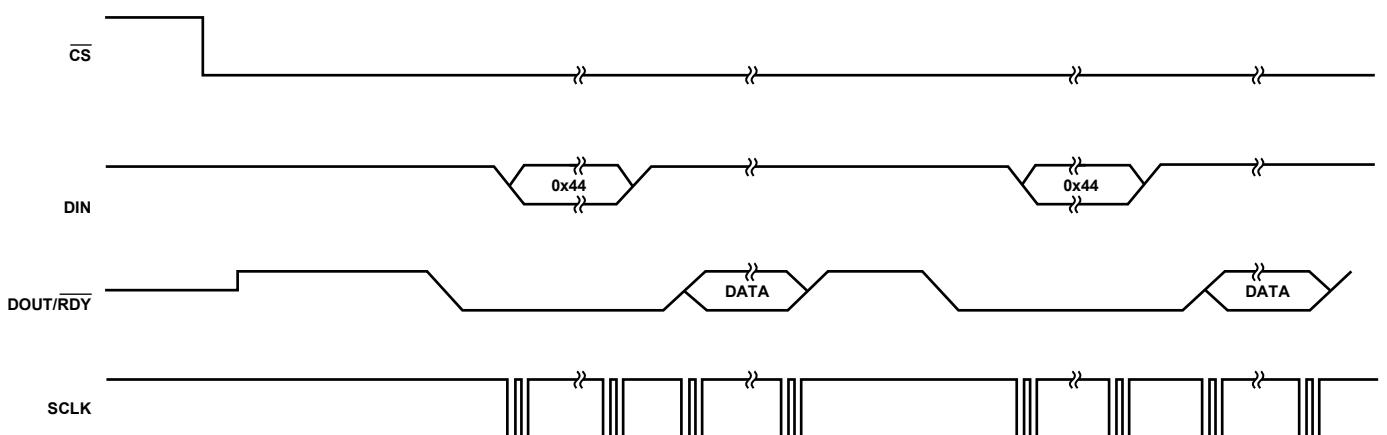

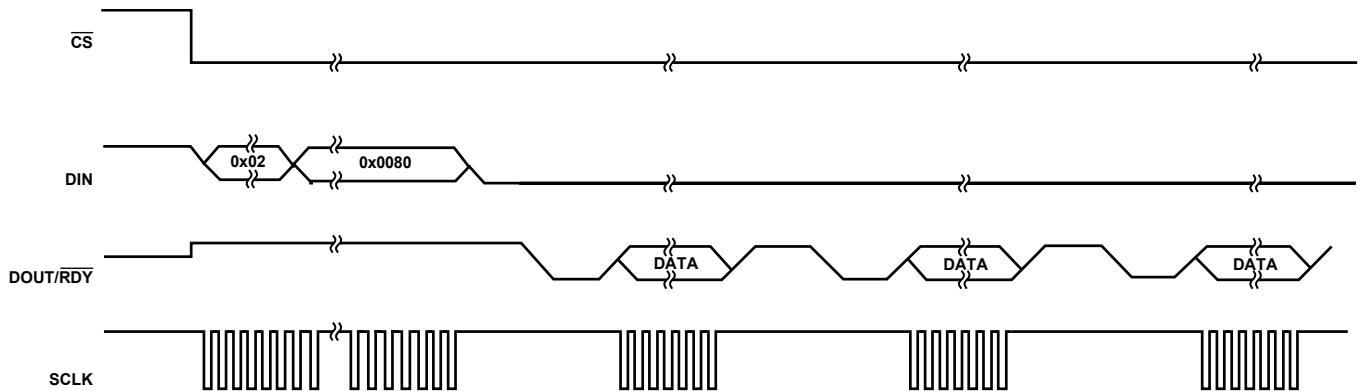

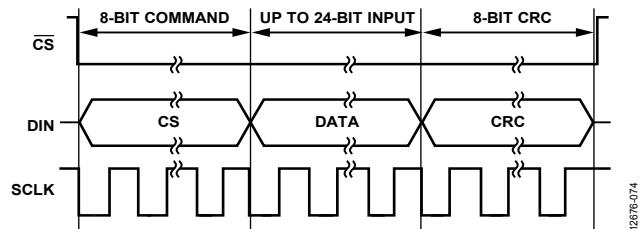

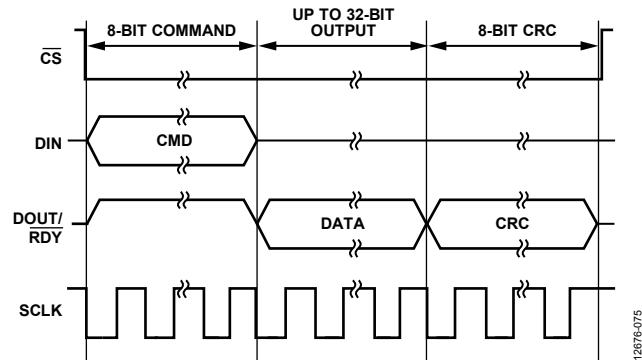

図 43 と 図 44 に、レジスタへの書き込み動作とレジスタからの読み出し動作を示します。8 ビット・コマンドをコミュニケーション・レジスタに書き込んだ後に、そのレジスタのデータの書き込み／読み出しを実行します。

図 43. レジスタへの書き込み(レジスタ・アドレスを含む 8 ビット・コマンドを送信して 8 ビット、16 ビット、または 24 ビットのデータを書き込む。DIN のデータ長は選択されたレジスタによって異なる)

図 44. レジスタからの読み出し(レジスタ・アドレスを含む 8 ビット・コマンドを送信して、8 ビット、16 ビット、または 24 ビットのデータを読み出す。DOUT/RDY のデータ長は選択されたレジスタによって異なる)

このデバイスが正常に通信しているか確認するには、ID レジスタの読み出しが推奨されます。ID レジスタは読み出し専用のレジスタで、AD7172-4 の値 0x205X が格納されています。コミュニケーション・レジスタと ID レジスタの詳細については、表 9 と表 10 を参照してください。

## AD7172-4 のリセット

パワーアップ・サイクル後に電源が安定したら、デバイスをリセットする必要があります。インターフェースの同期が失われた場合も、デバイスをリセットする必要があります。DIN がハイ・レベルで、少なくとも 64 シリアル・クロック・サイクルの書き込み動作が実行されると、レジスタの内容を含むデバイスのすべての設定がリセットされ、ADC がデフォルト状態に戻ります。代わりに、CS をデジタル・インターフェースと一緒に使用し、CS をハイ・レベルに戻すと、デジタル・インター

フェースがデフォルト状態に設定され、すべてのシリアル・インターフェースが停止します。

## 構成概要

パワーオンまたはリセット後の AD7172-4 のデフォルト設定は、次のとおりです。

- チャンネル構成。CH 0 はイネーブル、AIN0 は正入力として選択されており、AIN1 は負入力として選択されている。Setup0 が選択されている。

- セットアップ構成。アナログ入力バッファとリファレンス入力バッファはディスエーブル。REF $\pm$  ピンはリファレンス源として選択されている。

- フィルタ構成。sinc5 + sinc1 フィルタが選択されており、31.25 kSPS の最大出力データ・レートが選択されている。

- ADC モード。連続変換モードと内部発振器はイネーブル。

- インターフェース・モード。CRC、データ + ステータス出力はディスエーブル。

いくつかの重要なレジスタ設定オプションのみを示しました。このリストは一例であることに留意してください。レジスタの詳細については、レジスタの詳細のセクションを参照してください。

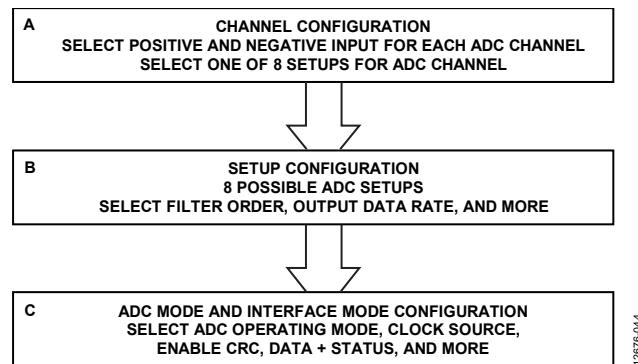

図 45 に、ADC 機動作の設定を変更するときの推奨フローの概要を示します。このフローは 3 つのブロックに分割されます。

- チャンネル構成(図 45 のボックス A を参照)

- セットアップ構成(図 45 のボックス B を参照)

- ADC モードとインターフェース・モードの構成(図 45 のボックス C を参照)

## チャンネル構成

AD7172-4 は 8 個の独立したチャンネルと 8 個の独立したセットアップを備えています。あらゆるチャンネルで任意のアナログ入力ペアを選択でき、あらゆるチャンネルで 8 個のセットアップのうち 1 つを自由に選択できるため、チャンネル構成に関する完全な柔軟性が実現されます。また、各チャンネルに独自の専用セットアップを適用できるため、差動入力およびシングルエンド入力を使用しているときにチャンネルごとの構成も可能です。

## チャンネル・レジスタ

チャンネル・レジスタでは、9 個のアナログ入力ピン(AIN0 ~ AIN8)のうち、どのピンをチャンネルの正のアナログ入力(AIN+)または負のアナログ入力(AIN-)として使用するか選択します。このレジスタには、チャンネルのイネーブル/ディスエーブル・ビットや、このセットアップ・チャンネルで使用するセットアップ(8 個のセットアップのいずれか)を選択するためのセットアップ選択ビットも含まれています。

複数のチャンネルがイネーブルになっている状態で AD7172-4 が動作している場合、チャンネル・シーケンサはチャンネル 0 からチャンネル 7 までイネーブル・チャンネルを順番にスキップします。チャンネルがディスエーブルの場合、この動作はシーケンサによってスキップされます。チャンネル 0 のチャンネル・レジスタの詳細を表 11 に示します。

図 45. 推奨する ADC 構成時のフロー

表 9. コミュニケーション・レジスタ

| Reg. | Name  | Bits  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset | RW |

|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----|

| 0x00 | COMMS | [7:0] | WEN   | R/W   |       |       |       |       |       |       | 0x00  | W  |

表 10. ID レジスタ

| Reg. | Name | Bits   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2 | Bit 1 | Bit 0 | Reset  | RW |

|------|------|--------|-------|-------|-------|-------|----------|-------|-------|-------|--------|----|

| 0x07 | ID   | [15:8] |       |       |       |       | ID[15:8] |       |       |       | 0x205X | R  |

|      |      | [7:0]  |       |       |       |       | ID[7:0]  |       |       |       |        |    |

表 11. チャンネル・レジスタ 0

| Reg. | Name | Bits   | Bit 7  | Bit 6        | Bit 5      | Bit 4 | Bit 3    | Bit 2   | Bit 1        | Bit 0  | Reset | RW |

|------|------|--------|--------|--------------|------------|-------|----------|---------|--------------|--------|-------|----|

| 0x10 | CH0  | [15:8] | CH_EN0 |              | SETUP_SEL0 |       | Reserved |         | AINPOS0[4:3] | 0x8001 | RW    |    |

|      |      | [7:0]  |        | AINPOS0[2:0] |            |       |          | AINNEG0 |              |        |       |    |

**ADC セットアップ**

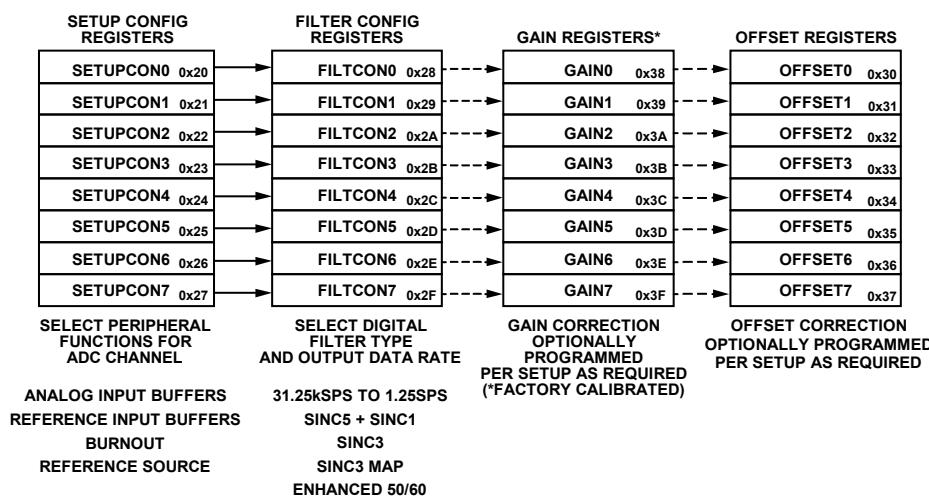

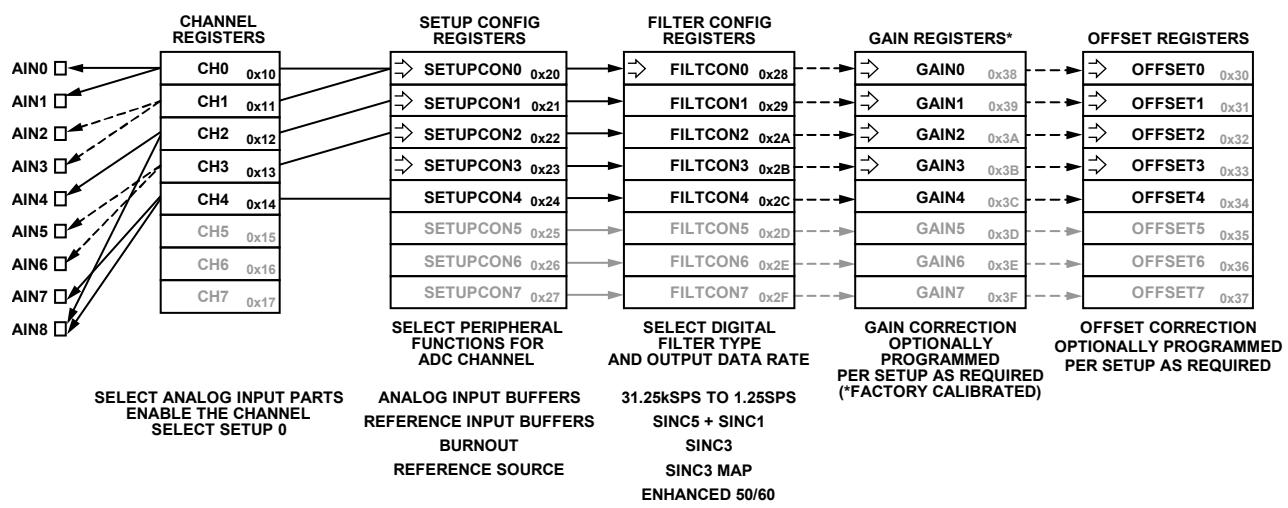

AD7172-4 には、8 個の独立したセットアップがあります。各セットアップは以下の 4 つのレジスタで構成されています。

- セットアップ構成レジスタ

- フィルタ設定レジスタ

- ゲイン・レジスタ

- オフセット・レジスタ

例えば、Setup 0 は、セットアップ構成レジスタ 0、フィルタ設定レジスタ 0、ゲイン・レジスタ 0、およびオフセット・レジスタ 0 で構成されています。図 46 に、これらのレジスタのグループを示します。セットアップは、チャンネル・レジスタから選択できます(チャンネル構成のセクションを参照)。これにより、各チャンネルを 8 個の個別のセットアップのいずれかに割り当てることができます。表 12 から

表 15 に、Setup 0 に関する 4 つのレジスタを示しています。Setup 1 から Setup 7 までは、Setup 0 と全く同じ構造です。

**セットアップ構成レジスタ**

セットアップ構成レジスタにより、バイポーラ・モードやユニポーラ・モードを選択して ADC の出力コーディングを選択できます。バイポーラ・モードの場合、ADC は負の差動入力電圧にも対応し、出力コーディングはオフセット・バイナリになります。ユニポーラ・モードの場合、ADC は正の差動電圧のみに対応し、コーディングはストレート・バイナリになります。どちらの場合も、入力電圧は AVDD1/AVSS 電源電圧以下にする必要があります。これらのレジスタを使用してリファレンス源を選択できます。REF+ ピンと REF- ピン間に接続されたリファレンス、REF2+ ピンと REF2- ピン間に接続されたリファレンス、または AVDD1-AVSS 電圧を使用できます。これらのレジスタを使用して、アナログ入力バッファとリファレンス電圧入力バッファをイネーブルまたはディスエーブルにすることもできます。

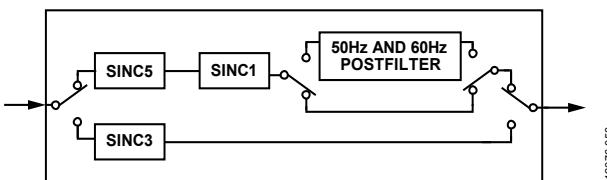

**フィルタ設定レジスタ**

フィルタ設定レジスタは、ADC 変調器の出力で使用するデジタル・フィルタを選択します。フィルタの次数と出力データ・レートは、これらのレジスタのビットをセットして選択します。詳細については、デジタル・フィルタのセクションを参照してください。

12876-045

図 46. ADC セットアップ・レジスタのグループ

表 12. セットアップ構成レジスタ 0

| Reg. | Name      | Bits   | Bit 7       | Bit 6    | Bit 5    | Bit 4            | Bit 3    | Bit 2    | Bit 1    | Bit 0    | Reset  | RW |

|------|-----------|--------|-------------|----------|----------|------------------|----------|----------|----------|----------|--------|----|

| 0x20 | SETUPCON0 | [15:8] | Reserved    |          |          | BI_UNIPOLAR<br>0 | REFBUFO+ | REFBUF0- | AINBUFO+ | AINBUF0- | 0x1000 | RW |

|      |           | [7:0]  | BURNOUT_EN0 | Reserved | REF_SEL0 | Reserved         |          |          |          |          |        |    |

表 13. フィルタ設定レジスタ 0

| Reg. | Name     | Bits   | Bit 7      | Bit 6    | Bit 5 | Bit 4 | Bit 3         | Bit 2    | Bit 1 | Bit 0 | Reset  | RW |

|------|----------|--------|------------|----------|-------|-------|---------------|----------|-------|-------|--------|----|

| 0x28 | FILTCON0 | [15:8] | SINC3_MAP0 | Reserved |       |       | ENHFILTN<br>0 | ENHFILT0 |       |       | 0x0500 | RW |

|      |          | [7:0]  | Reserved   | ORDER0   |       | ODR0  |               |          |       |       |        |    |

表 14. ゲイン・レジスタ 0

| Reg. | Name  | Bits   | Bits[23:0]  |  |  |  |  |  |  |  | Reset        | RW |

|------|-------|--------|-------------|--|--|--|--|--|--|--|--------------|----|

| 0x38 | GAIN0 | [23:0] | GAIN0[23:0] |  |  |  |  |  |  |  | 0x5XXXX<br>0 | RW |

表 15. オフセット・レジスタ 0

| Reg. | Name    | Bits   | Bits[23:0]    |  |  |  |  |  |  |  | Reset    | RW |

|------|---------|--------|---------------|--|--|--|--|--|--|--|----------|----|

| 0x30 | OFFSET0 | [23:0] | OFFSET0[23:0] |  |  |  |  |  |  |  | 0x800000 | RW |

## ゲイン・レジスタ

ゲイン・レジスタは、ADC のゲイン・キャリブレーション係数を保持する 24 ビット・レジスタです。ゲイン・レジスタはリード/ライト・レジスタです。パワーオン時、これらのレジスタには工場出荷時のキャリブレーション係数が格納されます。従って、各デバイスは個別のデフォルト係数を持っています。ユーザーがシステム・フルスケール・キャリブレーションを実行した場合、またはゲイン・レジスタに書き込みを行った場合、デフォルト値は自動的に上書きされます。詳細については、動作モードのセクションを参照してください。

## オフセット・レジスタ

オフセット・レジスタは、ADC のオフセット・キャリブレーション係数を保持します。オフセット・レジスタのパワーオン・リセット値は、0x800000 です。オフセット・レジスタは 24 ビットのリード/ライト・レジスタです。ユーザーが内部キャリブレーションまたはシステム・ゼロスケール・キャリブレーションを実行した場合、あるいはオフセット・レジスタに書き込みを行った場合、パワーオン・リセット値は自動的に上書きされます。

表 16. ADC モード・レジスタ

| Reg. | Name    | Bits   | Bit 7    | Bit 6      | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1 | Bit 0 | Reset  | RW |

|------|---------|--------|----------|------------|----------|----------|----------|----------|-------|-------|--------|----|

| 0x01 | ADCMODE | [15:8] | Reserved | HIDE_DELAY | SING_CYC | Reserved |          | Delay    |       |       | 0x2000 | RW |

|      |         | [7:0]  | Reserved | Mode       |          |          | CLOCKSEL | Reserved |       |       |        |    |

表 17. インターフェース・モード・レジスタ

| Reg. | Name   | Bits   | Bit 7    | Bit 6         | Bit 5         | Bit 4    | Bit 3      | Bit 2    | Bit 1    | Bit 0      | Reset  | RW |

|------|--------|--------|----------|---------------|---------------|----------|------------|----------|----------|------------|--------|----|

| 0x02 | IFMODE | [15:8] | Reserved |               |               | ALT_SYNC | IOSTRENGTH | Reserved |          | DOUT_RESET | 0x0000 | RW |

|      |        | [7:0]  | CONTREAD | DATA_STA<br>T | REG_CHEC<br>K | Reserved | CRC_EN     |          | Reserved | WL16       |        |    |

## ADC モードとインターフェース・モードの構成

ADC モード・レジスタとインターフェース・モード・レジスタは、AD7172-4 によって使用される ADC コア・ペリフェラルとデジタル・インターフェースのモードを設定します。

### ADC モード・レジスタ

ADC モード・レジスタでは、主に ADC の変換モードを連続変換モードまたはシングル変換モードに設定します。また、スタンバイ・モード、パワーダウン・モードの選択もできます。さらに、各種キャリブレーション・モードの選択も可能です。さらに、このレジスタにはクロック源の選択ビットも含まれています。リファレンスの選択ビットは、セットアップ構成レジスタに含まれています(詳細については、ADC セットアップのセクションを参照)。このレジスタの詳細を表 16 に示します。

### インターフェース・モード・レジスタ

インターフェース・モード・レジスタは、デジタル・インターフェースの動作を設定します。このレジスタにより、データワード長、CRC イネーブル、データとステータスの読み出し、および連続読み出しモードを制御できます。このレジスタの詳細を表 17 に示します。詳細については、デジタル・インターフェースのセクションを参照してください。

### 柔軟な構成

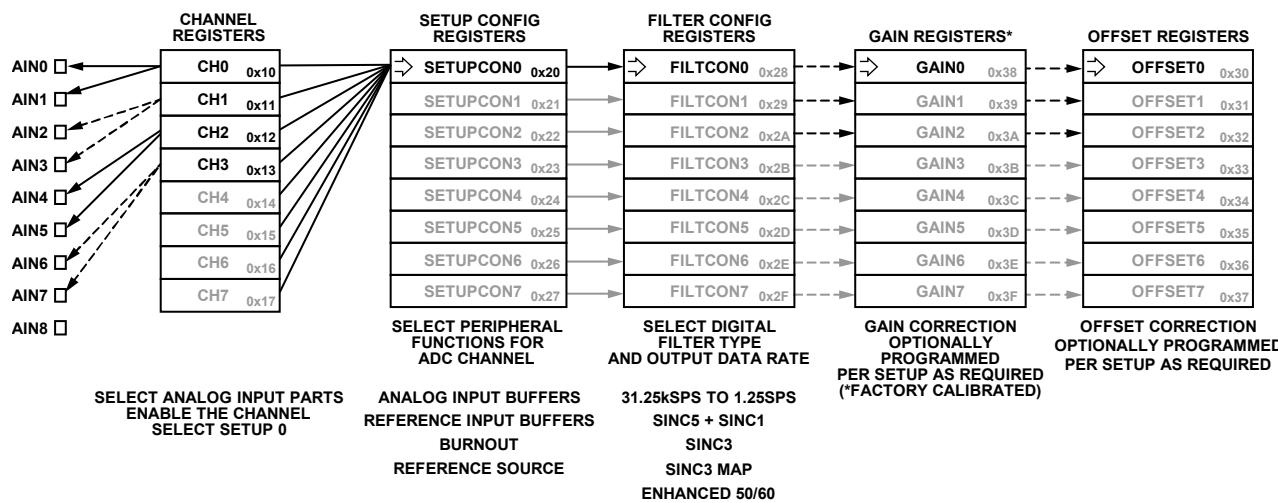

4個の差動入力と隣接するアナログ入力を使用して、それらすべてを同じセットアップ、ゲイン補正、およびオフセット補正レジスタで実行するには、AD7172-4 を実装するのが最も簡単な方法です。この場合、以下の組み合わせの差動入力を使用します。AIN0/AIN1、AIN2/AIN3、AIN4/AIN5、およびAIN6/AIN7。図47に黒色の文字で示しているレジスタは、このような構成でプログラムする必要があります。灰色の文字で示されているレジスタは、この構成では設定不要です。

レジスタ・ブロック間において点線で示すように、ゲインおよびオフセット・レジスタのプログラミングは、常にオプションです。

図 47. 4 個の完全差動入力すべてが 1 つのセットアップ (SETUPCON0、FILTCON0、GAIN0、OFFSET0) を使用

図 48. 4 個の完全差動入力がチャンネルごとに 1 つのセットアップを使用

12676-046

12676-047

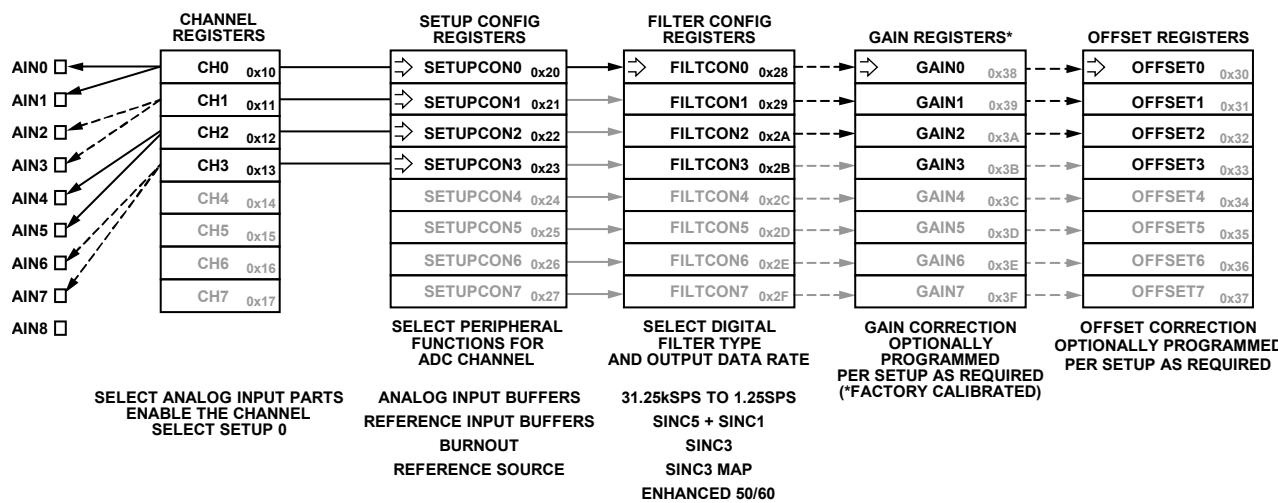

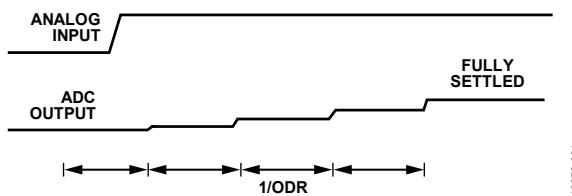

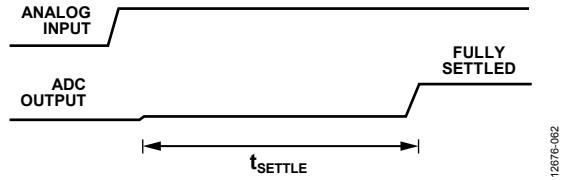

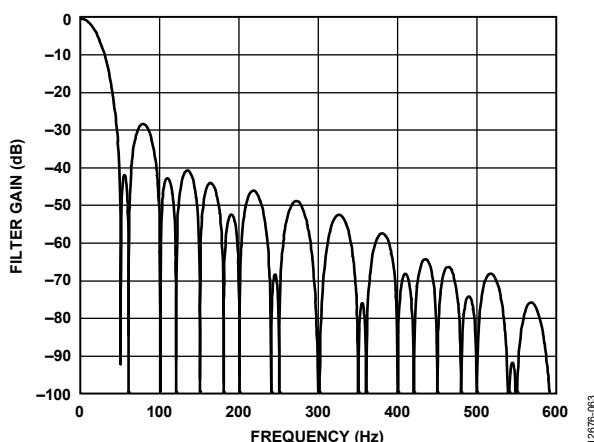

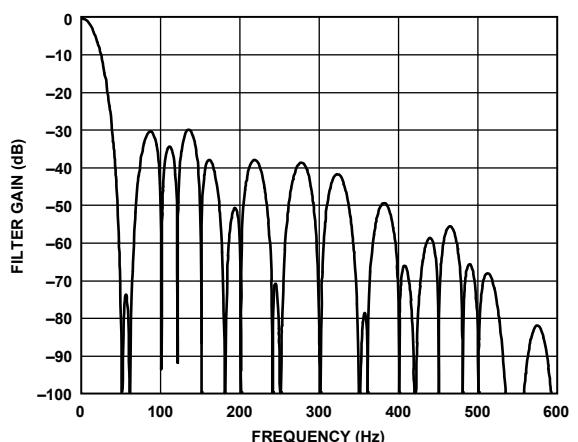

図 49 では、チャンネル・レジスタによってアナログ入力ピンとダウンストリーム側のセットアップ構成をどのように繋げていくか例を示しています。この例では、3つの差動入力と2つのシングルエンド入力が必要です。シングルエンド入力は、AIN4／AIN8 と AIN7／AIN8 の組み合わせです。差動入力ペアは、AIN0／AIN1 と AIN2／AIN3 (両方とも Setup 0 を使用)、および AIN5／AIN6 (Setup 2 を使用) です。2つのシングルエンド入力ペアは診断としてセットアップされ、この例では Setup 1 と Setup 4 という個別のセットアップを使用しています。5つのセットアップを使用するように選択しているため、SETUPCON0～SETUPCON4 レジスタを必要に応じてプログラムし、FILTCON0