# 16 チャンネル、12 ビット 電圧出力 denseDAC

## データシート

## AD5767

### 特長

フル機能 16 チャンネル、12 ビット D/A コンバータ (DAC)

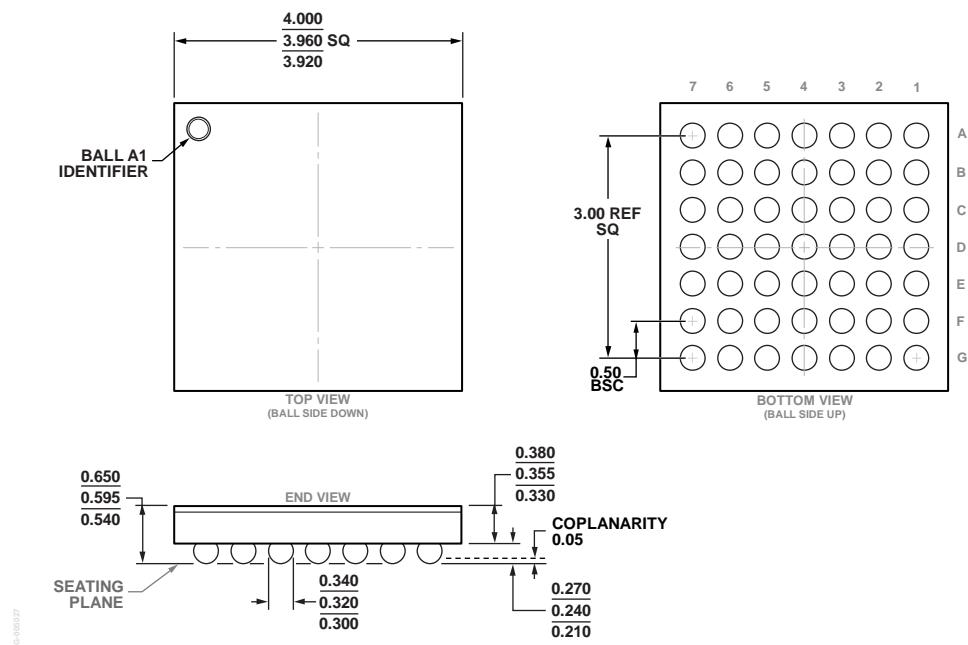

4 mm × 4 mm WLCSP パッケージ

1.8 V ロジックとの互換性

動作温度範囲:-40 °C ~ +105 °C

チャンネル監視マルチプレクサ

リファレンス・バッファを内蔵

内蔵 DAC 出力バッファ、±20 mA の出力電流能力

### アプリケーション

マッハ・ツェンダー変調器バイアス制御

光学モジュール

バイアス制御

アナログ出力モジュール

### 概要

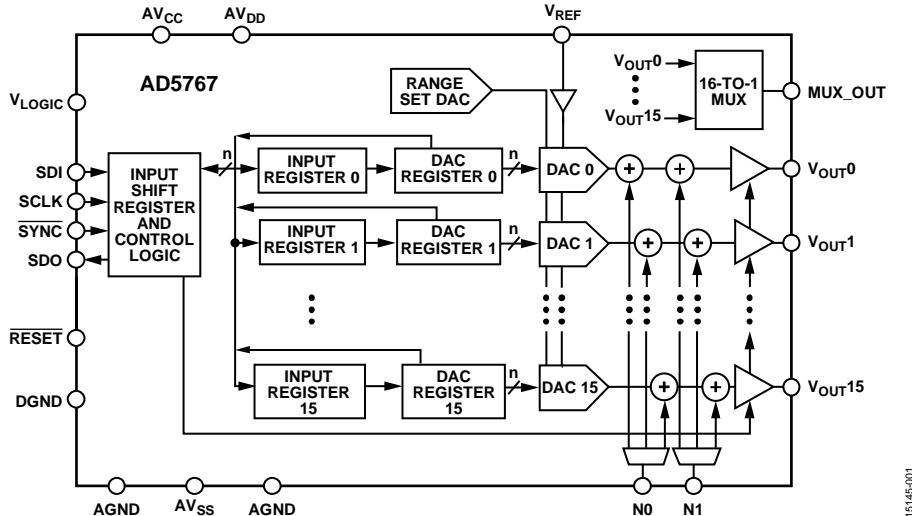

AD5767 は、16 チャンネル、12 ビット、電圧出力 denseDAC® D/A コンバータ (DAC) です。

DAC は、外部 2.5 V リファレンスから出力電圧範囲を生成します。選択した電圧範囲に応じて、出力スパンの中間点を調整して、最小-20 V の電圧から最大+14 V までの電圧を出力できます。各 16 チャンネルは、内蔵の出力マルチプレクサで監視できます。

AD5767 は、最大で 20 mA までシンクまたはソースできる内蔵出力バッファを備えています。これらのバッファを組み合わせることで、専用のディザ・ピンから各 DAC 出力に低周波信号を重畠できます。専用のディザ・ピンを使用すれば、オペアンプや抵抗などの外部実装に必要な外付け部品の数を減らすことで、システム設計を簡略化できます。AD5767 では、外付け部品の数を削減できるので、リン化インジウム・マッハ・ツェンダー変調器 (InP MZM) バイアス・アプリケーションに適しています。

このデバイスには、パワーオン・リセット (POR) 回路が組み込まれています。このため、パワーオン時に DAC 出力が GND にクランプされ、DAC の出力範囲が構成されるまでこのレベルを確実に維持できます。すべての DAC 出力は、レジスタ構成を通して更新されます。この際、ユーザー選択可能な DAC チャンネルの追加機能によって、すべての出力が同時に更新されます。

AD5767 は、書き込みモードにおいて最大 50 MHz のクロック・レートで動作する多機能の 4 線式シリアル・インターフェースを採用しています。また、シリアル・ペリフェラル・インターフェース (SPI)、QSPI™、MICROWIRE™、DSPインターフェース規格と互換性があります。AD5767 は、1.8 V / 3 V / 5 V ロジックを対象とした V<sub>LOGIC</sub> ピンも備えています。

AD5767 は 4 mm × 4 mm の 8 ピン WLCSP パッケージで供給され、-40 °C ~ +105 °C の範囲で動作します。

### 機能ブロック図

図 1.

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許や他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                  |    |                               |    |

|------------------|----|-------------------------------|----|

| 特長               | 1  | レジスタの詳細                       | 22 |

| アプリケーション         | 1  | 入力シフト・レジスタ                    | 22 |

| 概要               | 1  | 監視マルチプレクサ制御                   | 23 |

| 機能ブロック図          | 1  | 動作なし                          | 24 |

| 改訂履歴             | 2  | ディジーチェーン・モード                  | 24 |

| 仕様               | 3  | 書き込みコマンドと更新コマンド               | 24 |

| AC 性能特性          | 6  | スパン・レジスタ                      | 25 |

| タイミング特性          | 7  | パワー・コントロール・レジスタ               | 25 |

| 絶対最大定格           | 9  | すべての DAC レジスタへの入力データの書き込み     | 26 |

| 熱抵抗              | 9  | ソフトウェア・フル・リセット                | 26 |

| ESD に関する注意事項     | 9  | リードバックするレジスタの選択               | 26 |

| ピン配置およびピン機能の説明   | 10 | N0 または N1 のディザ信号を DAC レジスタに適用 | 27 |

| 代表的な性能特性         | 12 | ディザ・スケール                      | 28 |

| ディザ              | 16 | 反転ディザ・レジスタ                    | 28 |

| 用語の定義            | 18 | アプリケーション情報                    | 29 |

| 動作原理             | 19 | ディザ構成                         | 29 |

| D/A コンバータ        | 19 | 熱に関する考慮事項                     | 29 |

| DAC アーキテクチャ      | 19 | マイクロプロセッサ・インターフェース            | 29 |

| 抵抗ストリング          | 19 | AD5767 の SPI インターフェース         | 29 |

| パワーオン・リセット (POR) | 19 | レイアウトのガイドライン                  | 30 |

| ディザ              | 20 | 外形寸法                          | 31 |

| パワーダウン・モード       | 20 | オーダー・ガイド                      | 31 |

| 監視マルチプレクサ        | 20 |                               |    |

| シリアル・インターフェース    | 21 |                               |    |

## 改訂履歴

1/2017-Revision 0: Initial Version

**仕様**

特に指定がない限り、AV<sub>CC</sub> = 2.97 V ~ 5.5 V、V<sub>LOGIC</sub> = 1.7 V ~ 5.5 V、AV<sub>DD</sub> = 2.97 V ~ 16 V、AV<sub>SS</sub> = -22 V ~ -7 V、AGND = DGND = 0 V、V<sub>REF</sub> = 2.5 V、出力範囲 = ±5 V、V<sub>OUTX</sub> は無負荷、すべての仕様は -40 °C ~ +105 °C、代表的な仕様は 25 °C で規定されています。

表 1.

| Parameter                                                    | Min  | Typ   | Max  | Unit                                                                                        | Test Conditions/Comments       |

|--------------------------------------------------------------|------|-------|------|---------------------------------------------------------------------------------------------|--------------------------------|

| STATIC PERFORMANCE                                           |      |       |      |                                                                                             |                                |

| Resolution                                                   | 12   |       |      | Bits                                                                                        |                                |

| Relative Accuracy (INL)                                      | -1   | +1    | LSB  | -10 V to 0 V range and ±5 V range                                                           |                                |

|                                                              | -1.5 | +1.5  | LSB  | -20 V to 0 V, -16 V to 0 V, -10 V to +6 V, ±10 V, -12 V to +14 V, and -16 V to +10 V ranges |                                |

| Differential Nonlinearity                                    | -1   | +1    | LSB  | Guaranteed monotonic by design                                                              |                                |

| Bipolar Zero Error                                           | -85  | ±12   | +85  | mV                                                                                          | ±5 V range                     |

|                                                              | -110 | ±13   | +110 | mV                                                                                          | -10 V to +6 V range            |

|                                                              | -120 | ±15   | +120 | mV                                                                                          | ±10 V range                    |

|                                                              | -145 | ±16   | +145 | mV                                                                                          | -12 V to +14 V range           |

|                                                              | -145 | ±16   | +145 | mV                                                                                          | -16 V to +10 V range           |

| Bipolar Zero Error Temperature Coefficient (TC) <sup>1</sup> |      | ±2    |      | ppm FSR/°C                                                                                  |                                |

| Zero-Scale Error                                             | -80  | ±25   | +80  | mV                                                                                          | All 0s loaded to DAC register  |

|                                                              | -80  | ±25   | +80  | mV                                                                                          | -10 V to 0 V range             |

|                                                              | -110 | ±35   | +110 | mV                                                                                          | ±5 V range                     |

|                                                              | -110 | ±35   | +110 | mV                                                                                          | -16 V to 0 V range             |

|                                                              | -130 | ±35   | +130 | mV                                                                                          | -10 V to +6 V range            |

|                                                              | -130 | ±35   | +130 | mV                                                                                          | -20 V to 0 V range             |

|                                                              | -140 | ±45   | +140 | mV                                                                                          | ±10 V range                    |

|                                                              | -140 | ±45   | +140 | mV                                                                                          | -12 V to +14 V range           |

|                                                              |      | ±2    |      | ppm FSR/°C                                                                                  | -16 V to +10 V range           |

| Zero-Scale Error Temperature Coefficient (TC) <sup>1</sup>   |      | ±2    |      | ppm FSR/°C                                                                                  |                                |

| Full-Scale Error                                             | -0.9 | ±0.23 | +0.9 | % FSR                                                                                       | All 1s loaded to DAC register. |

|                                                              | -0.9 | ±0.23 | +0.9 | % FSR                                                                                       | -10 V to 0 V range             |

|                                                              | -0.8 | ±0.2  | +0.8 | % FSR                                                                                       | ±5 V range                     |

|                                                              | -0.8 | ±0.2  | +0.8 | % FSR                                                                                       | -16 V to 0 V range             |

|                                                              | -0.7 | ±0.18 | +0.7 | % FSR                                                                                       | -10 V to +6 V range            |

|                                                              | -0.7 | ±0.18 | +0.7 | % FSR                                                                                       | -20 V to 0 V range             |

|                                                              | -0.6 | ±0.15 | +0.6 | % FSR                                                                                       | ±10 V range                    |

|                                                              | -0.6 | ±0.15 | +0.6 | % FSR                                                                                       | -12 V to +14 V range           |

|                                                              |      | ±3    |      | ppm FSR/°C                                                                                  | -16 V to +10 V range           |

| Full-Scale Error Drift                                       |      | ±0.4  | +0.4 | % FSR                                                                                       |                                |

| Gain Error                                                   |      | ±0.07 | +0.4 | ppm FSR/°C                                                                                  |                                |

| Gain Error Temperature Coefficient (TC) <sup>1</sup>         |      | ±2    |      | ppm FSR/°C                                                                                  |                                |

| Offset Error                                                 | -80  | ±25   | +80  | mV                                                                                          | -10 V to 0 V range             |

|                                                              | -80  | ±25   | +80  | mV                                                                                          | ±5 V range                     |

|                                                              | -110 | ±35   | +110 | mV                                                                                          | -16 V to 0 V range             |

|                                                              | -110 | ±35   | +110 | mV                                                                                          | -10 V to +6 V range            |

|                                                              | -130 | ±35   | +130 | mV                                                                                          | -20 V to 0 V range             |

|                                                              | -130 | ±35   | +130 | mV                                                                                          | ±10 V range                    |

|                                                              | -140 | ±45   | +140 | mV                                                                                          | -12 V to +14 V range           |

|                                                              | -140 | ±45   | +140 | mV                                                                                          | -16 V to +10 V range           |

| Offset Error Drift <sup>1</sup>                              |      | ±2    |      | μV/°C                                                                                       |                                |

| Parameter                                           | Min                             | Typ        | Max                             | Unit       | Test Conditions/Comments                               |

|-----------------------------------------------------|---------------------------------|------------|---------------------------------|------------|--------------------------------------------------------|

| Total Unadjusted Error                              | -0.9                            | $\pm 0.18$ | +0.9                            | %FSR       | -10 V to 0 V range                                     |

|                                                     | -0.9                            | $\pm 0.18$ | +0.9                            | %FSR       | $\pm 5$ V range                                        |

|                                                     | -0.8                            | $\pm 0.15$ | +0.8                            | %FSR       | -16 V to 0 V range                                     |

|                                                     | -0.8                            | $\pm 0.15$ | +0.8                            | %FSR       | -10 V to +6 V range                                    |

|                                                     | -0.7                            | $\pm 0.13$ | +0.7                            | %FSR       | -20 V to 0 V range                                     |

|                                                     | -0.7                            | $\pm 0.13$ | +0.7                            | %FSR       | $\pm 10$ V range                                       |

|                                                     | -0.6                            | $\pm 0.12$ | +0.6                            | %FSR       | -12 V to +14 V range                                   |

|                                                     | -0.6                            | $\pm 0.12$ | +0.6                            | %FSR       | -16 V to +10 V range                                   |

|                                                     | 30                              |            |                                 | $\mu$ V    | Due to output voltage change                           |

|                                                     | 35                              |            |                                 | $\mu$ V/mA | Due to load current change (1 LSB)                     |

| <b>OUTPUT CHARACTERISTICS</b>                       |                                 |            |                                 |            |                                                        |

| Output Voltage Ranges <sup>2</sup>                  | -20                             | 0          |                                 | V          |                                                        |

|                                                     | -16                             | 0          |                                 | V          |                                                        |

|                                                     | -10                             | 0          |                                 | V          |                                                        |

|                                                     | -10                             | +6         |                                 | V          |                                                        |

|                                                     | -12                             | +14        |                                 | V          |                                                        |

|                                                     | -16                             | +10        |                                 | V          |                                                        |

|                                                     | -5                              | +5         |                                 | V          |                                                        |

|                                                     | -10                             | +10        |                                 | V          |                                                        |

|                                                     | -20                             | +20        |                                 | mA         | Refer to the Thermal Considerations section            |

|                                                     |                                 | 1          |                                 | nF         |                                                        |

| Output Current <sup>1</sup>                         |                                 | 0.2        |                                 | $\Omega$   |                                                        |

| Capacitive Load Stability <sup>1</sup>              |                                 | $\pm 60$   |                                 | mA         | Single channel only                                    |

| DC Output Impedance <sup>1</sup>                    |                                 | 108        |                                 | kHz        |                                                        |

| Short-Circuit Current <sup>1</sup>                  |                                 |            |                                 |            |                                                        |

| Output Amplifier Bandwidth <sup>1</sup>             |                                 |            |                                 |            |                                                        |

| <b>REFERENCE INPUT<sup>1</sup></b>                  |                                 |            |                                 |            |                                                        |

| Reference Input Voltage                             |                                 | 2.5        |                                 | V          | $\pm 1\%$ for specified performance                    |

| Reference Range                                     | 2.375                           |            | 2.625                           |            | Functional performance only                            |

| DC Input Impedance                                  | 2.5                             |            |                                 | M $\Omega$ |                                                        |

| Input Current                                       |                                 |            | 1                               | $\mu$ A    |                                                        |

| <b>DITHER INPUTS</b>                                |                                 |            |                                 |            |                                                        |

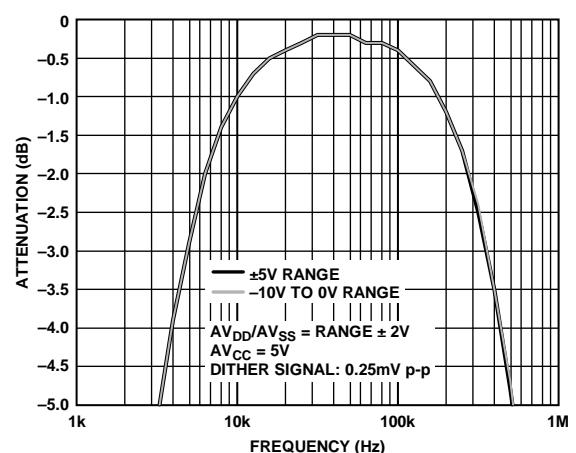

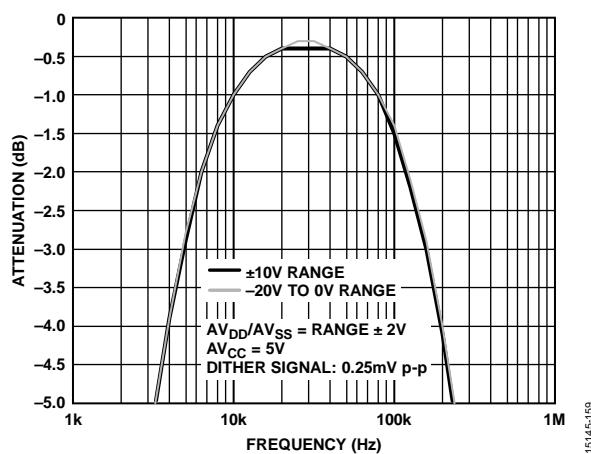

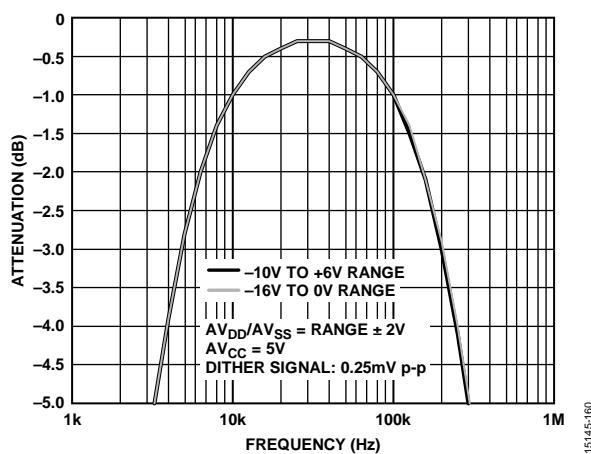

| Dither Frequency <sup>1</sup>                       |                                 | 10         |                                 | kHz        | Lower -3 dB point                                      |

|                                                     |                                 | 100        |                                 | kHz        | Upper -3 dB point                                      |

|                                                     |                                 |            | 0.25                            | V p-p      | Peak-to-peak ac voltage                                |

|                                                     | Amplitude <sup>1</sup>          | 0          | AV <sub>CC</sub>                | V          | Peak-to-peak ac and dc voltage                         |

|                                                     |                                 | -1         | $\pm 0.063$                     | LSB        | See the Terminology section                            |

| Dither Shift                                        |                                 |            |                                 |            | See Figure 34 to Figure 37 for typical performance     |

| Dither Input to DAC Output Attenuation <sup>1</sup> |                                 |            |                                 |            |                                                        |

| Dither Transient <sup>1</sup>                       |                                 | 5          |                                 | nV-sec     | Dither enabled/disabled, N0 and N1 floating            |

| Dither Selected Channel                             |                                 | 2          |                                 | nV-sec     | AV <sub>CC</sub> = 2.97 V and AV <sub>CC</sub> = 5.5 V |

| Dither Nonselected Channels                         |                                 | -70        |                                 | dB         | AV <sub>CC</sub> = 2.97 V and AV <sub>CC</sub> = 5.5 V |

| Dither Crosstalk <sup>1</sup>                       |                                 | -55        |                                 | dB         | 10 kHz dither frequency                                |

|                                                     |                                 |            |                                 |            | 100 kHz dither frequency                               |

| <b>LOGIC INPUTS<sup>1</sup></b>                     |                                 |            |                                 |            |                                                        |

| Input High Voltage, V <sub>IH</sub>                 | 0.7 $\times$ V <sub>LOGIC</sub> |            |                                 | V          |                                                        |

| Input Low Voltage, V <sub>IL</sub>                  |                                 |            | 0.3 $\times$ V <sub>LOGIC</sub> | V          |                                                        |

| Input Current                                       |                                 | -2         | +2                              | $\mu$ A    | Per pin                                                |

|                                                     |                                 | -6         | +6                              | $\mu$ A    | RESET pin pulled high                                  |

| Input Capacitance                                   |                                 | -57        | +57                             | $\mu$ A    | RESET pin pulled low                                   |

|                                                     |                                 | 2          |                                 | pF         | Per pin                                                |

| <b>LOGIC OUTPUT<sup>1</sup></b>                     |                                 |            |                                 |            |                                                        |

| Output Low Voltage                                  |                                 |            | 0.4                             | V          | Sinking 200 $\mu$ A                                    |

| Output High Voltage                                 | V <sub>LOGIC</sub> - 0.4        |            |                                 | V          | Sourcing 200 $\mu$ A                                   |

| Parameter                                              | Min  | Typ   | Max | Unit   | Test Conditions/Comments                                                                                                |

|--------------------------------------------------------|------|-------|-----|--------|-------------------------------------------------------------------------------------------------------------------------|

| High Impedance Leakage Current                         | -1   |       | +1  | µA     |                                                                                                                         |

| High Impedance Output Capacitance                      |      | 5     |     | pF     |                                                                                                                         |

| VOLTAGE MONITOR PIN<br>(MUX_OUT)                       |      |       |     |        |                                                                                                                         |

| Impedance <sup>1</sup>                                 |      | 1.3   |     | kΩ     |                                                                                                                         |

| Three-State Leakage Current                            | -1   | 0.006 | +1  | µA     |                                                                                                                         |

| Continuous Current <sup>1</sup>                        | -1   |       | +1  | mA     | Die temperature below 105°C                                                                                             |

| Glitch Impulse <sup>1</sup>                            |      | 0.2   |     | nV·sec | V <sub>OUTX</sub> glitch due to mux enable                                                                              |

| Voltage Settling Time <sup>1</sup>                     |      | 12    |     | µs     | ¼ to ¾ scale settling to ±0.5 LSB, ±5 V range and -10 V to 0 V range                                                    |

| POWER SUPPLIES                                         |      |       |     |        |                                                                                                                         |

| A <sub>V<sub>DD</sub></sub>                            | 2.97 |       | 16  | V      | A <sub>V<sub>DD</sub></sub> - A <sub>V<sub>SS</sub></sub> must be less than or equal to 30 V                            |

| A <sub>V<sub>SS</sub></sub>                            | -22  |       | -7  | V      | A <sub>V<sub>DD</sub></sub> - A <sub>V<sub>SS</sub></sub> must be less than or equal to 30 V                            |

| A <sub>V<sub>CC</sub></sub>                            | 2.97 |       | 5.5 | V      |                                                                                                                         |

| V <sub>LOGIC</sub>                                     | 1.7  |       | 5.5 | V      |                                                                                                                         |

| Headroom/Footroom <sup>1</sup>                         |      | 2     |     | V      | Applies to A <sub>V<sub>DD</sub></sub> and A <sub>V<sub>SS</sub></sub>                                                  |

| Normal Mode                                            |      |       |     |        |                                                                                                                         |

| A <sub>I<sub>DD</sub></sub>                            |      | 6     | 8   | mA     | All output ranges, -40°C to +105°C                                                                                      |

| A <sub>I<sub>SS</sub></sub>                            | -11  | -9    |     | mA     | All output ranges, -40°C to +105°C                                                                                      |

| A <sub>I<sub>CC</sub></sub>                            |      | 8.3   | 10  | mA     | All output ranges, -40°C to +105°C                                                                                      |

| I <sub>LOGIC</sub>                                     |      | 0.02  | 1   | µA     | All output ranges, -40°C to +105°C, V <sub>I<sub>H</sub></sub> = V <sub>LOGIC</sub> , V <sub>I<sub>L</sub></sub> = DGND |

| Power-Down Mode                                        |      |       |     |        | All channels powered down                                                                                               |

| A <sub>I<sub>DD</sub></sub>                            |      | 0.11  | 0.3 | mA     |                                                                                                                         |

| A <sub>I<sub>SS</sub></sub>                            | -0.5 | -0.16 |     | mA     |                                                                                                                         |

| A <sub>I<sub>CC</sub></sub>                            |      | 0.14  | 0.3 | mA     | A <sub>V<sub>CC</sub></sub> = 3.3V                                                                                      |

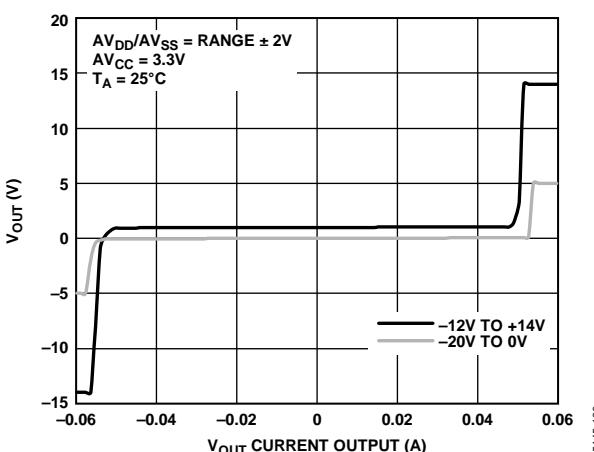

|                                                        |      | 0.55  | 0.8 | mA     | See Figure 28                                                                                                           |

| I <sub>LOGIC</sub>                                     |      | 0.02  | 1   | µA     |                                                                                                                         |

| DC Power Supply Rejection Ratio<br>(PSRR) <sup>1</sup> |      | 50    |     | µV/V   | A <sub>V<sub>DD</sub></sub> power supply                                                                                |

|                                                        |      | 50    |     | µV/V   | A <sub>V<sub>SS</sub></sub> power supply                                                                                |

|                                                        |      | 3     |     | mV/V   | A <sub>V<sub>CC</sub></sub> power supply                                                                                |

| AC Power Supply Rejection Ratio<br>(PSRR) <sup>1</sup> |      | -80   |     | dB     | A <sub>V<sub>DD</sub></sub> power supply, at 50 Hz                                                                      |

|                                                        |      | -80   |     | dB     | A <sub>V<sub>SS</sub></sub> power supply, at 50 Hz                                                                      |

|                                                        |      | -50   |     | dB     | A <sub>V<sub>CC</sub></sub> power supply, at 50 Hz                                                                      |

<sup>1</sup> 設計と特性評価による性能は確保していますが、出荷テストの対象外です。<sup>2</sup> 出力アンプのヘッドルーム条件は、最低 2 V です。

**AC 性能特性**

特に指定がない限り、 $AV_{CC} = 2.97 \text{ V} \sim 5.5 \text{ V}$ 、 $V_{LOGIC} = 1.7 \text{ V} \sim 5.5 \text{ V}$ 、 $AV_{DD} = 2.97 \text{ V} \sim 15 \text{ V}$ 、 $AV_{SS} = -22 \text{ V} \sim -7 \text{ V}$ 、 $AGND = DGND = 0 \text{ V}$ 、 $V_{REF} = 2.5 \text{ V}$ 、出力範囲 =  $-10 \text{ V} \sim 0 \text{ V}$ 、 $V_{OUTX}$  は無負荷、すべての仕様は  $-40^\circ\text{C} \sim +105^\circ\text{C}$ 、代表的な仕様は  $25^\circ\text{C}$  で規定されています。アナログ・ディザ信号は使用していません。

表 2.

| Parameter                                     | Min | Typ                          | Max | Unit | Test Conditions/Comments                                                                                                                    |

|-----------------------------------------------|-----|------------------------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------|

| <b>DYNAMIC PERFORMANCE<sup>1</sup></b>        |     |                              |     |      |                                                                                                                                             |

| Output Voltage Settling Time <sup>2</sup>     | 10  | $\mu\text{s}$                |     |      | $\frac{1}{4}$ to $\frac{3}{4}$ scale settling to $\pm 0.5 \text{ LSB}$ , $\pm 5 \text{ V}$ range and $-10 \text{ V}$ to $0 \text{ V}$ range |

|                                               | 4   | $\mu\text{s}$                |     |      | 32 LSB step to $\pm 0.5 \text{ LSB}$                                                                                                        |

| Slew Rate <sup>2</sup>                        | 1   | $\text{V}/\mu\text{s}$       |     |      |                                                                                                                                             |

| Digital-to-Analog Glitch Energy <sup>2</sup>  | 10  | $\text{nV}\cdot\text{sec}$   |     |      | 1 LSB change around major carry for 10 V span                                                                                               |

| Glitch Impulse Peak Amplitude <sup>2</sup>    | 8   | $\text{mV}$                  |     |      |                                                                                                                                             |

| Digital Feedthrough <sup>2</sup>              | 1   | $\text{nV}\cdot\text{sec}$   |     |      |                                                                                                                                             |

| Digital Crosstalk <sup>2</sup>                | 0.2 | $\text{nV}\cdot\text{sec}$   |     |      |                                                                                                                                             |

| Analog Crosstalk <sup>2</sup>                 | 15  | $\text{nV}\cdot\text{sec}$   |     |      |                                                                                                                                             |

| DAC-to-DAC Crosstalk <sup>2</sup>             | 15  | $\text{nV}\cdot\text{sec}$   |     |      |                                                                                                                                             |

| Total Harmonic Distortion <sup>2</sup>        | -80 | $\text{dB}$                  |     |      | $V_{REF} = 2.5 \text{ V} \pm 0.1 \text{ V p-p}$ , frequency = 10 kHz, $AV_{CC} = 2.97 \text{ V}$ and $3.3 \text{ V}$                        |

|                                               | -75 | $\text{dB}$                  |     |      | $V_{REF} = 2.5 \text{ V} \pm 0.1 \text{ V p-p}$ , frequency = 10 kHz, $AV_{CC} = 5.5 \text{ V}$                                             |

| Output Noise Spectral Density <sup>1, 2</sup> | 375 | $\text{nV}/\sqrt{\text{Hz}}$ |     |      | -10 V to 0 V and $\pm 5 \text{ V}$ ranges, frequency = 1 kHz                                                                                |

|                                               | 605 | $\text{nV}/\sqrt{\text{Hz}}$ |     |      | -16 V to 0 V and -10 V to +6 V ranges, frequency = 1 kHz                                                                                    |

|                                               | 750 | $\text{nV}/\sqrt{\text{Hz}}$ |     |      | -20 V to 0 V and $\pm 10 \text{ V}$ ranges, frequency = 1 kHz                                                                               |

|                                               | 835 | $\text{nV}/\sqrt{\text{Hz}}$ |     |      | -12 V to 14 V and -16 V to +10 V ranges, frequency = 1 kHz                                                                                  |

|                                               | 280 | $\text{nV}/\sqrt{\text{Hz}}$ |     |      | -10 V to 0 V and $\pm 5 \text{ V}$ ranges, frequency = 10 kHz                                                                               |

|                                               | 440 | $\text{nV}/\sqrt{\text{Hz}}$ |     |      | -16 V to 0 V and -10 V to +6 V ranges, frequency = 10 kHz                                                                                   |

|                                               | 470 | $\text{nV}/\sqrt{\text{Hz}}$ |     |      | -20 V to 0 V and $\pm 10 \text{ V}$ ranges, frequency = 10 kHz                                                                              |

|                                               | 610 | $\text{nV}/\sqrt{\text{Hz}}$ |     |      | -12 V to 14 V and -16 V to +10 V ranges, frequency = 10 kHz                                                                                 |

| Output Noise <sup>2, 3</sup>                  |     |                              |     |      | Dither disabled                                                                                                                             |

|                                               | 20  | $\mu\text{V rms}$            |     |      | $\pm 5 \text{ V}$ range                                                                                                                     |

|                                               | 23  | $\mu\text{V rms}$            |     |      | -10 V to 0 V range                                                                                                                          |

|                                               | 33  | $\mu\text{V rms}$            |     |      | -10 V to +6 V range                                                                                                                         |

|                                               | 38  | $\mu\text{V rms}$            |     |      | -16 V to 0 V range                                                                                                                          |

|                                               | 36  | $\mu\text{V rms}$            |     |      | $\pm 10 \text{ V}$ range                                                                                                                    |

|                                               | 45  | $\mu\text{V rms}$            |     |      | -20 V to 0 V range                                                                                                                          |

|                                               | 45  | $\mu\text{V rms}$            |     |      | -16 V to 10 V range                                                                                                                         |

|                                               | 45  | $\mu\text{V rms}$            |     |      | -12 V to 14 V range                                                                                                                         |

<sup>1</sup> DAC コード = ミッドスケール。 $AV_{DD} = V_{OUT\_MAX} + 2 \text{ V}$ 。 $AV_{SS} = V_{OUT\_MIN} - 2 \text{ V}$ 。

<sup>2</sup> 設計と特性評価による性能は確保していますが、出荷テストの対象外です。

<sup>3</sup> 0.1 Hz ~ 10 Hz。 $AV_{DD} = V_{OUT\_MAX} + 2 \text{ V}$ 。 $AV_{SS} = V_{OUT\_MIN} - 2 \text{ V}$ 。

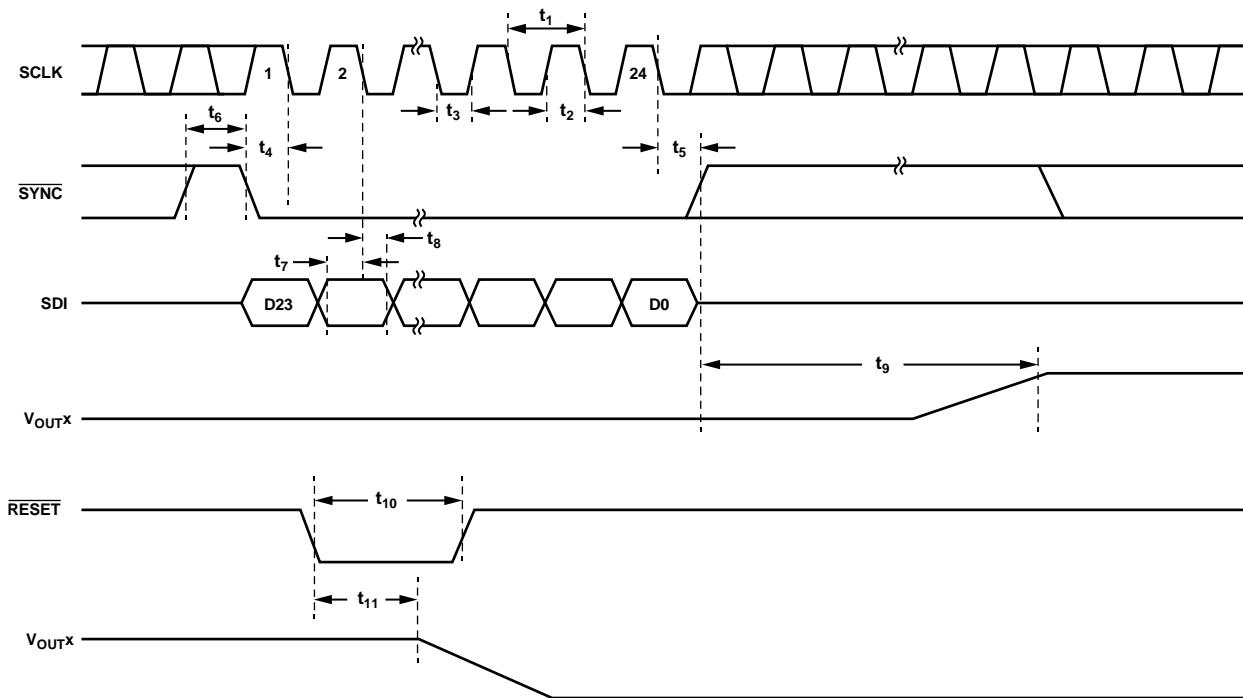

## タイミング特性

すべての入力信号は  $t_R = t_F = 1 \text{ ns/V}$  ( $\text{AV}_{\text{DD}}$  の 10 % ~ 90 %) で仕様規定し、 $(V_{\text{IL}} + V_{\text{IH}})/2$  の電圧レベルで時間を測定しています。図 2、図 3、および図 4 を参照してください。

特に指定がない限り、 $\text{AV}_{\text{CC}} = 2.97 \text{ V} \sim 5.5 \text{ V}$ 、 $V_{\text{LOGIC}} = 1.7 \text{ V} \sim 5.5 \text{ V}$ 、 $V_{\text{REF}} = 2.5 \text{ V}$ 。すべての仕様は  $-40^{\circ}\text{C} \sim +105^{\circ}\text{C}$  で規定されています。

表 3.

| Parameter                   | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Description                                                                                                      |

|-----------------------------|----------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------|

| t <sub>1</sub> <sup>1</sup> | 20                                           | ns min | SCLK cycle time                                                                                                  |

| t <sub>2</sub>              | 10                                           | ns min | SCLK high time                                                                                                   |

| t <sub>3</sub>              | 10                                           | ns min | SCLK low time                                                                                                    |

| t <sub>4</sub>              | 15                                           | ns min | SYNC falling edge to SCLK falling edge setup time                                                                |

| t <sub>5</sub>              | 15                                           | ns min | SCLK falling edge to <u>SYNC</u> rising edge time                                                                |

| t <sub>6</sub>              | 20                                           | ns min | Minimum <u>SYNC</u> high time (write mode)                                                                       |

| t <sub>7</sub>              | 5                                            | ns min | Data setup time                                                                                                  |

| t <sub>8</sub>              | 5                                            | ns min | Data hold time                                                                                                   |

| t <sub>9</sub>              | 4                                            | μs typ | DAC output settling time, 32 code step to $\pm 0.5$ LSB at 12-bit resolution (see Table 2)                       |

| t <sub>10</sub>             | 100                                          | ns typ | <u>RESET</u> <sup>2</sup> pulse width low                                                                        |

| t <sub>11</sub>             | 100                                          | ns typ | <u>RESET</u> <sup>2</sup> pulse activation time                                                                  |

| t <sub>12</sub>             | 10                                           | ns min | SYNC rising edge to SCLK falling edge                                                                            |

| t <sub>13</sub>             | 40                                           | ns max | SCLK rising edge to SDO valid ( $C_{L\_SDO}$ <sup>3</sup> = 15 pF)                                               |

| t <sub>14</sub>             | 50                                           | ns typ | Minimum <u>SYNC</u> high time (readback/daisy-chain mode)                                                        |

| t <sub>15</sub>             | 20                                           | μs typ | SYNC rising edge to <u>SYNC</u> rising edge (DAC register updates); not shown in Figure 2, Figure 3, or Figure 4 |

<sup>1</sup> 最大 SCLK 周波数は、書込みモードでは 50 MHz、リードバック・モードでは 10 MHz です。

<sup>2</sup> リセットと後続の正常な書き込みの間の最小時間は通常 25 ns です。

<sup>3</sup>  $C_{L\_SDO}$  は、SDO 出力の容量性負荷です。

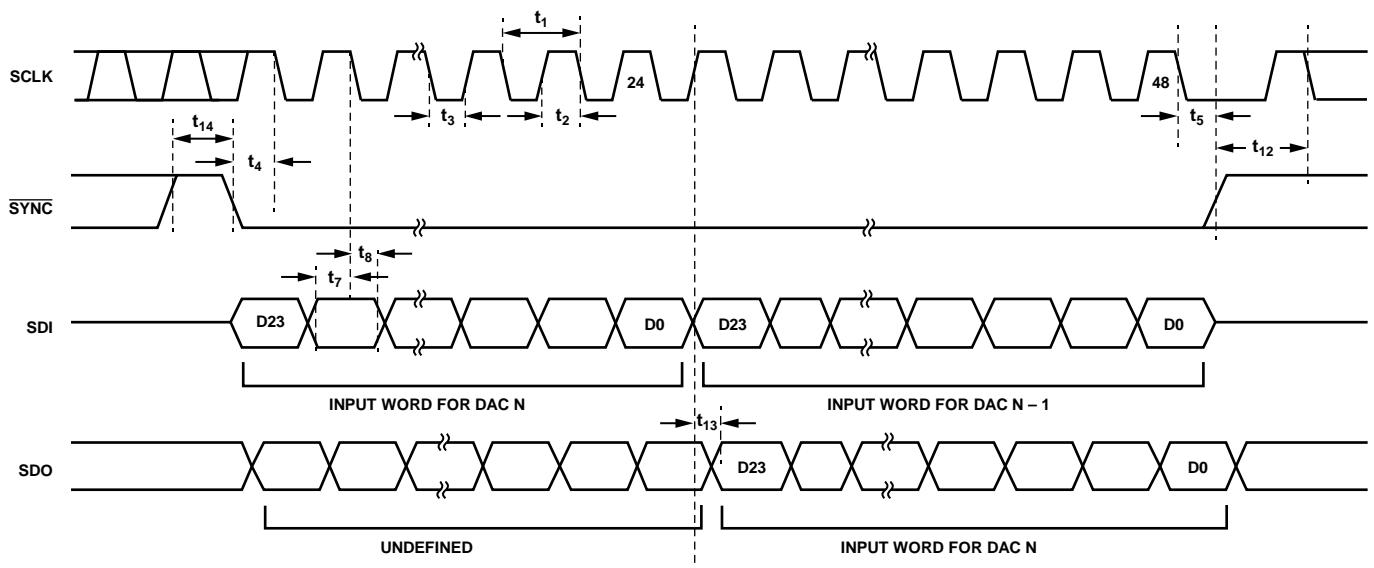

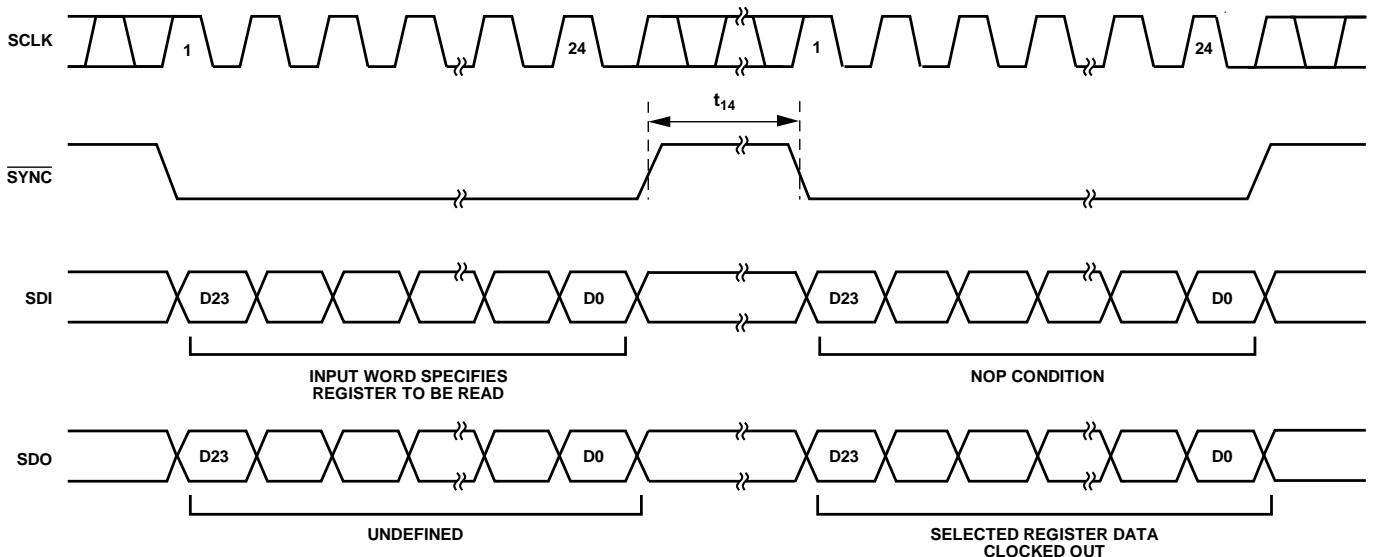

## タイミング図

図 2. シリアル・インターフェースのタイミング図

15145-002

図 3. デイジーチェーンのタイミング図

図 4. リードバックのタイミング図

## 絶対最大定格

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。最大 100 mA までの過渡電流では SCR ラッチアップは生じません。

表 4.

| Parameter                                          | Rating                                                             |

|----------------------------------------------------|--------------------------------------------------------------------|

| $\text{AV}_{\text{DD}}$ to AGND                    | -0.3 V to +34 V                                                    |

| $\text{AV}_{\text{SS}}$ to AGND                    | +0.3 V to -34 V                                                    |

| $\text{AV}_{\text{DD}}$ to $\text{AV}_{\text{SS}}$ | -0.3 V to +34 V                                                    |

| $\text{AV}_{\text{CC}}$ to AGND                    | -0.3 V to +7 V                                                     |

| $\text{AV}_{\text{CC}}$ to AGND                    | -0.3 V to $\text{AV}_{\text{DD}} + 0.3$ V                          |

| $\text{V}_{\text{LOGIC}}$ to DGND                  | -0.3 V to +7 V                                                     |

| Digital Inputs <sup>1</sup> to DGND                | -0.3 V to $\text{V}_{\text{LOGIC}} + 0.3$ V                        |

| Digital Output (SDO) to DGND                       | -0.3 V to $\text{V}_{\text{LOGIC}} + 0.3$ V                        |

| N0, N1 to AGND                                     | -0.3 V to $\text{AV}_{\text{CC}} + 0.3$ V                          |

| $\text{V}_{\text{REF}}$ to AGND                    | -0.3 V to $\text{AV}_{\text{CC}} + 0.3$ V                          |

| $\text{V}_{\text{OUTX}}$ to AGND                   | $\text{AV}_{\text{SS}} - 0.3$ V to $\text{AV}_{\text{DD}} + 0.3$ V |

| AGND to DGND                                       | -0.3 V to +0.3 V                                                   |

| Operating Temperature Range, $T_A$<br>Industrial   | -40°C to +105°C                                                    |

| Storage Temperature Range                          | -65°C to +150°C                                                    |

| Junction Temperature, $T_{\text{J MAX}}$           | 150°C                                                              |

| Power Dissipation                                  | $(T_{\text{J MAX}} - T_A)/\theta_{\text{JA}}$                      |

| Lead Temperature                                   |                                                                    |

| Soldering Reflow                                   | 260°C, as per JEDEC J-STD-020                                      |

<sup>1</sup> デジタル入力には、RESET、SCLK、SYNC、SDI が含まれます。

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を引き起こす場合があります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。製品を長時間にわたり絶対最大定格状態に置くと、製品の信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接関連しています。PCB の熱設計には、細心の注意を払う必要があります。

$\theta_{\text{JA}}$  は、1 立方フィートの密封容器内で測定される、自然対流下でのジャンクション温度と周囲温度間の熱抵抗です。

表 5. 热抵抗

| Package Type         | $\theta_{\text{JA}}$ | Unit |

|----------------------|----------------------|------|

| CB-49-4 <sup>1</sup> | 53                   | °C/W |

<sup>1</sup> 热抵抗のシミュレーション値は、16 個のサーマル・ビアを備えた JEDEC 2S2P サーマル・テスト・ボードに基づいています。JEDEC JESD51 を参照

## ESD に関する注意事項

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

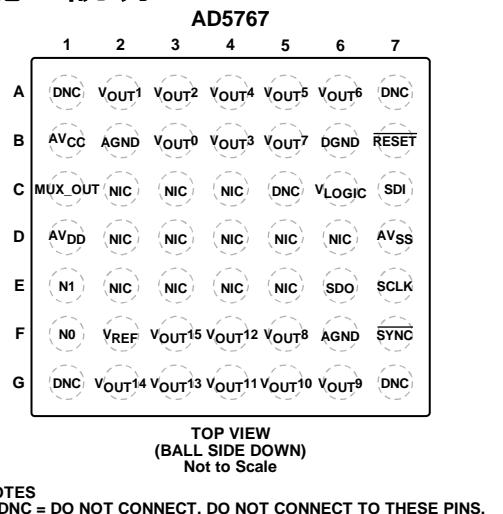

## ピン配置およびピン機能の説明

**NOTES**

1. DNC = DO NOT CONNECT. DO NOT CONNECT TO THESE PINS.

2. NIC = NO INTERNAL CONNECTION. THESE PINS SHOULD BE

ROUTED TO THERMAL VIAS ON THE PCB TO AID WITH HEAT

DISSIPATION. THESE SHOULD BE CONNECTED TO GROUND.

15145-005

図 5. ピン配置

表 6. ピン機能の説明

| ピン番号          | 記号    | 説明                                                                                                                                                                                                                                                |

|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ディザ<br>F1     | N0    | ディザ信号入力ピン0。このピンに接続される信号は、レジスタ・コマンド経由でDAC出力に追加できます。使用しない場合、このピンはグラウンドに接続します。詳細については、ディザのセクションを参照してください。                                                                                                                                            |

| E1            | N1    | ディザ信号入力ピン1。このピンに接続される信号は、レジスタ・コマンド経由でDAC出力に追加できます。使用しない場合、このピンはグラウンドに接続します。詳細については、ディザのセクションを参照してください。                                                                                                                                            |

| ロジック入出力<br>E7 | SCLK  | シリアル・クロック入力です。データは、シリアル・クロック入力の立下がりエッジで入力シフト・レジスタに入力されます。データは、書込みモードでは最大50MHz、リードバック・モードおよびデイジーチェーン・モードでは10MHzのレートで転送できます。                                                                                                                        |

| F7            | SYNC  | アクティブ・ローのコントロール入力。 <u>SYNC</u> は、入力データのフレーム同期信号です。 <u>SYNC</u> がロー・レベルになると、SCLKおよびSDIバッファの電源がオンになり、入力シフト・レジスタが有効になります。データは次の24回の立下がりエッジで転送されます。24番目の立下がりエッジの前に <u>SYNC</u> がハイ・レベルになった場合、 <u>SYNC</u> の立上がりエッジは割込みとして動作し、書込みシーケンスはデバイスによって無視されます。 |

| C7            | SDI   | シリアル・データ入力。このデバイスは、24ビットのシフト・レジスタを内蔵しています。データは、シリアル・クロック入力の立下がりエッジでレジスタに入力されます。                                                                                                                                                                   |

| E6            | SDO   | シリアル・データ出力。デイジーチェーン・モードまたはリードバック・モードで、シリアル・レジスタからこのピンにデータがクロック出力されます。データはSCLKの立上がりエッジでクロック出力され、SCLKの立下がりエッジで有効です。                                                                                                                                 |

| B7            | RESET | アクティブ・ローのリセット入力。このピン・ロジックをロー・レベルにアサートすると、AD5767はデフォルトのパワーオン状態に戻ります。このピンがロジック・ハイに戻った後、デバイスはリセット・モードを終了し、新しいSPIコマンドを受信できる状態になります。値の小さい内部プルアップ抵抗があるので、このピンは、フロート状態のままにすることができます。                                                                     |

| アナログ出力        |       |                                                                                                                                                                                                                                                   |

| B3            | VOUT0 | DAC 0からのアナログ出力電圧。                                                                                                                                                                                                                                 |

| A2            | VOUT1 | DAC 1からのアナログ出力電圧。                                                                                                                                                                                                                                 |

| A3            | VOUT2 | DAC 2からのアナログ出力電圧。                                                                                                                                                                                                                                 |

| B4            | VOUT3 | DAC 3からのアナログ出力電圧。                                                                                                                                                                                                                                 |

| A4            | VOUT4 | DAC 4からのアナログ出力電圧。                                                                                                                                                                                                                                 |

| A5            | VOUT5 | DAC 5からのアナログ出力電圧。                                                                                                                                                                                                                                 |

| A6            | VOUT6 | DAC 6からのアナログ出力電圧。                                                                                                                                                                                                                                 |

| B5            | VOUT7 | DAC 7からのアナログ出力電圧。                                                                                                                                                                                                                                 |

| F5            | VOUT8 | DAC 8からのアナログ出力電圧。                                                                                                                                                                                                                                 |

| ピン番号                        | 記号                 | 説明                                                                                                             |

|-----------------------------|--------------------|----------------------------------------------------------------------------------------------------------------|

| G6                          | V <sub>OUT9</sub>  | DAC 9 からのアナログ出力電圧。                                                                                             |

| G5                          | V <sub>OUT10</sub> | DAC 10 からのアナログ出力電圧。                                                                                            |

| G4                          | V <sub>OUT11</sub> | DAC 11 からのアナログ出力電圧。                                                                                            |

| F4                          | V <sub>OUT12</sub> | DAC 12 からのアナログ出力電圧。                                                                                            |

| G3                          | V <sub>OUT13</sub> | DAC 13 からのアナログ出力電圧。                                                                                            |

| G2                          | V <sub>OUT14</sub> | DAC 14 からのアナログ出力電圧。                                                                                            |

| F3                          | V <sub>OUT15</sub> | DAC 15 からのアナログ出力電圧。                                                                                            |

| 電源とリファレンス入力                 |                    |                                                                                                                |

| F2                          | V <sub>REF</sub>   | リファレンス入力電圧。仕様規定されている性能では、V <sub>REFIN</sub> = 2.5 V。                                                           |

| C6                          | V <sub>LOGIC</sub> | デジタル電源。                                                                                                        |

| B1                          | AV <sub>CC</sub>   | 電源入力。AD5767 は 2.97 V ~ 5.5 V で動作します。AV <sub>CC</sub> は、10 μF のコンデンサと 0.1 μF のコンデンサの並列接続でアナログ・グラウンドにデカッピングされます。 |

| D1                          | AV <sub>DD</sub>   | 出力アンプ正側（供給）アナログ電源                                                                                              |

| D7                          | AV <sub>SS</sub>   | 出力アンプ負側アナログ電源                                                                                                  |

| B2、F6                       | AGND               | アナログ・グラウンド。                                                                                                    |

| B6                          | DGND               | デジタル・グラウンド・ピン。                                                                                                 |

| チャンネル監視                     |                    |                                                                                                                |

| C1                          | MUX_OUT            | 監視出力。このピンは、16 個のチャンネル（チャンネル 0 ~ チャンネル 15）のいずれかを MUX_OUT ピンにマルチプレクサできる 16 チャンネル（入力）マルチプレクサの出力として動作します。          |

| 接続なし                        |                    |                                                                                                                |

| A1、A7、C5、G1、G7              | DNC                | 接続なし。これらのピンには接続しないでください。                                                                                       |

| 内部接続なし                      |                    |                                                                                                                |

| C2 ~ C4、D2 ~ D6、<br>E2 ~ E5 | NIC                | 内部接続なし。放熱を促進するため、これらのピンを PCB 上のサーマル・ビアにルーティングします。<br>これらピンはグラウンドに接続します。                                        |

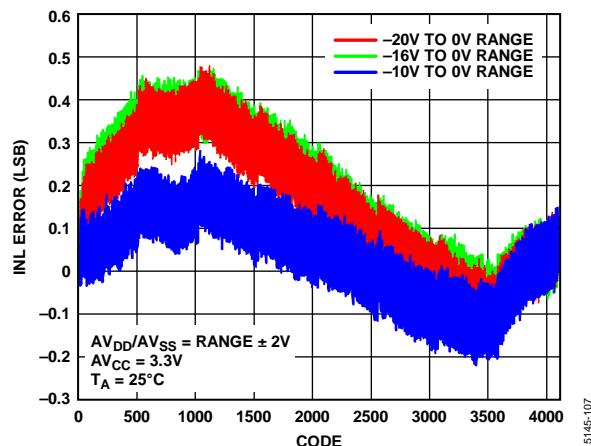

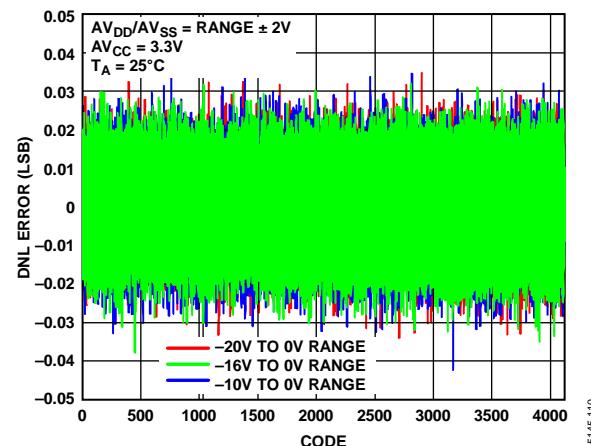

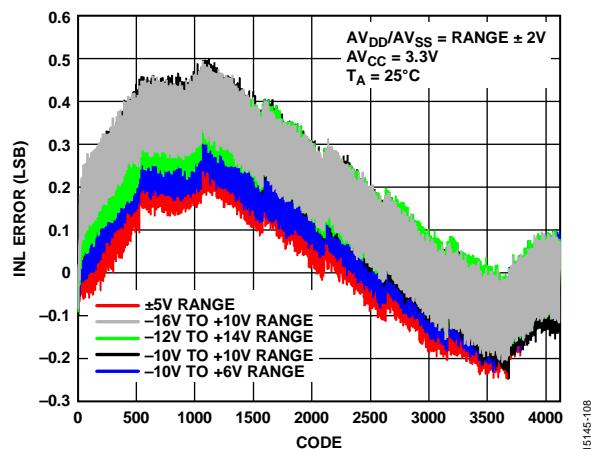

## 代表的な性能特性

図 6. INL 誤差と DAC コードの関係 (ユニポーラ出力)

図 9. DNL 誤差と DAC コードの関係 (ユニポーラ出力)

図 7. INL 誤差と DAC コードの関係 (バイポーラ出力)

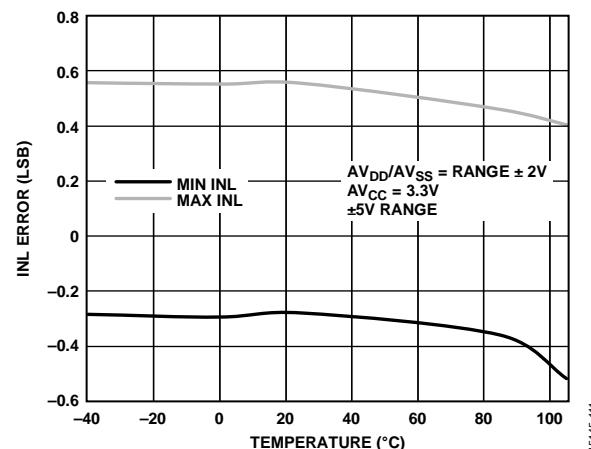

図 10. INL 誤差の温度特性

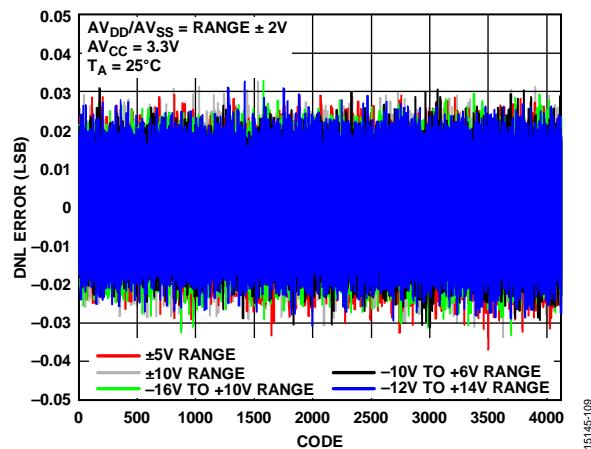

図 8. DNL 誤差と DAC コードの関係 (バイポーラ出力)

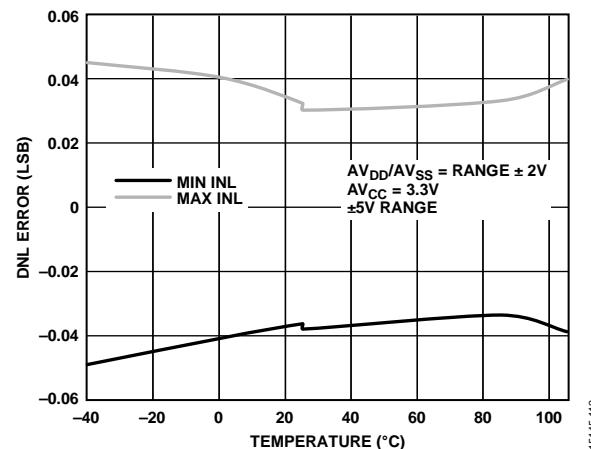

図 11. DNL 誤差の温度特性

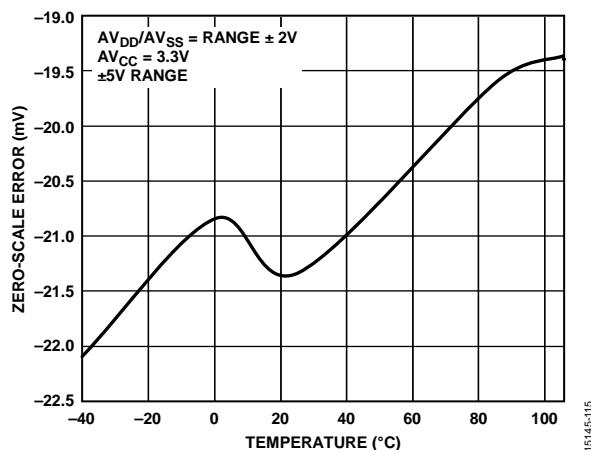

図 12. ゼロスケールの温度特性

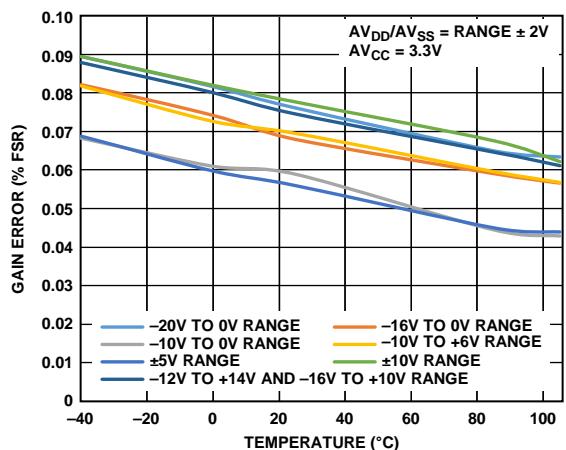

図 15. ゲイン誤差の温度特性

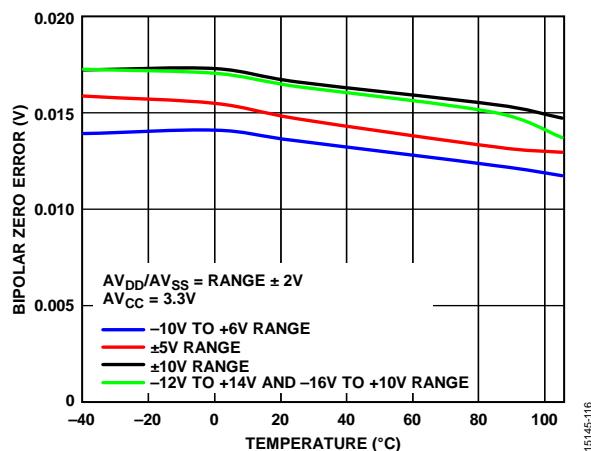

図 13. バイポーラ・ゼロ誤差の温度特性

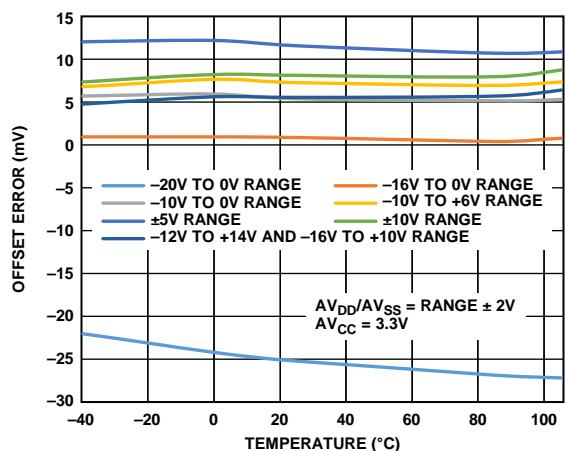

図 16. オフセット誤差の温度特性

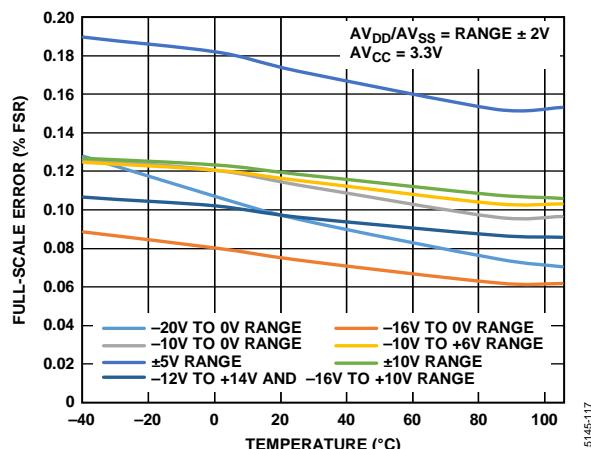

図 14. フルスケール誤差の温度特性

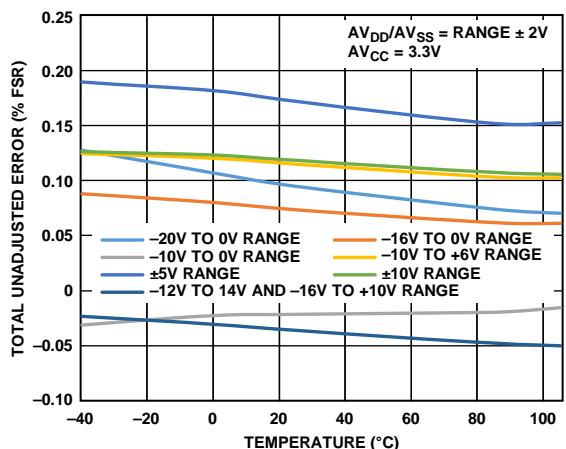

図 17. 総合未調整誤差の温度特性

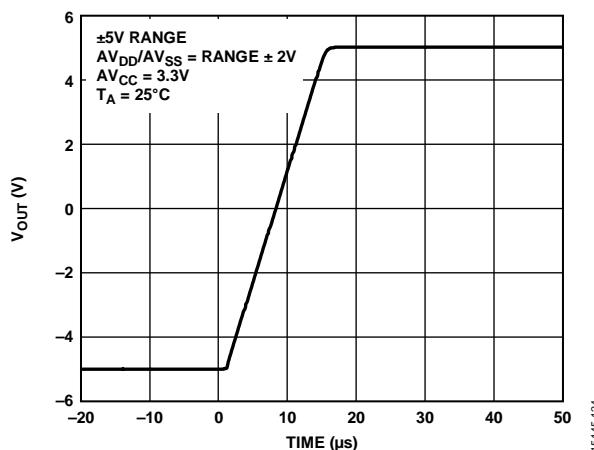

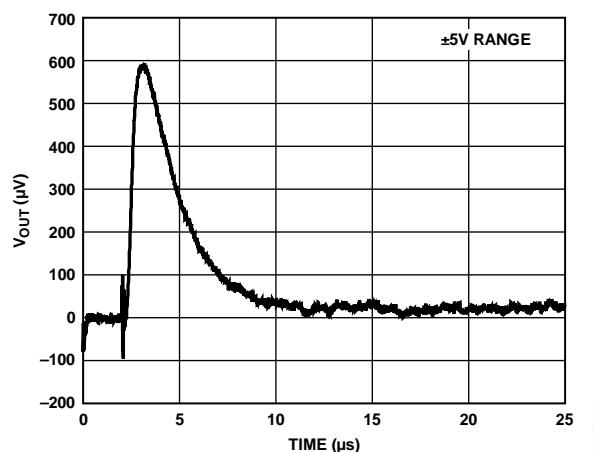

図 18. フルスケール・セトリング時間 (立上がり電圧ステップ)

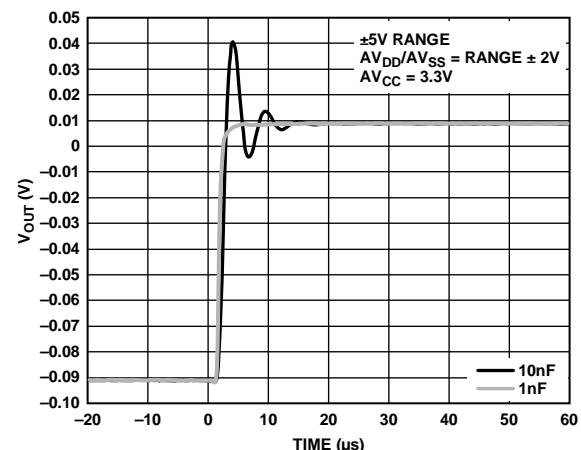

図 21. 多様な容量負荷での出力電圧とセトリング時間の関係

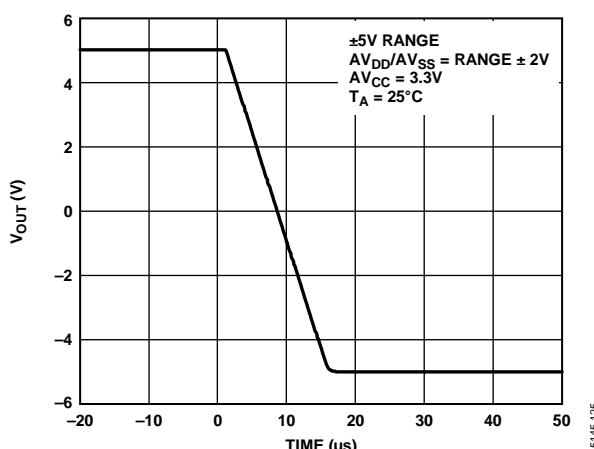

図 19. フルスケール・セトリング時間 (立下がり電圧ステップ)

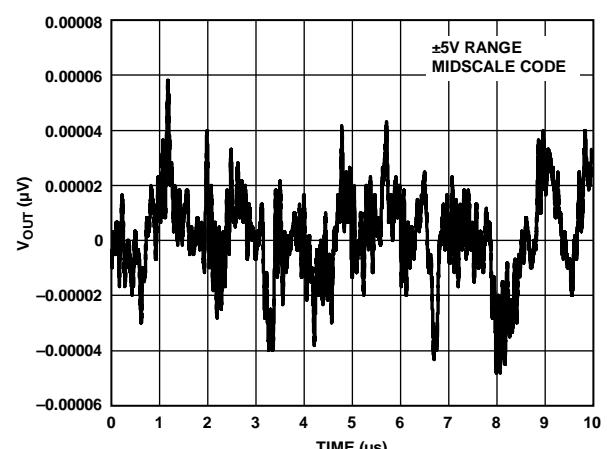

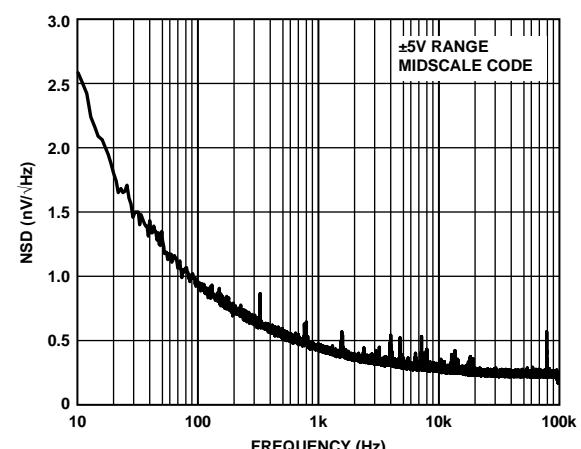

図 22. ピーク to ピーク・ノイズ (0.1 Hz ~ 10 Hz の帯域幅)、ディザは無効

図 20. 出力アンプのソース能力とシンク能力

図 23. ノイズ・スペクトル密度 (NSD) の周波数特性

図 24. デジタル・フィードスルー

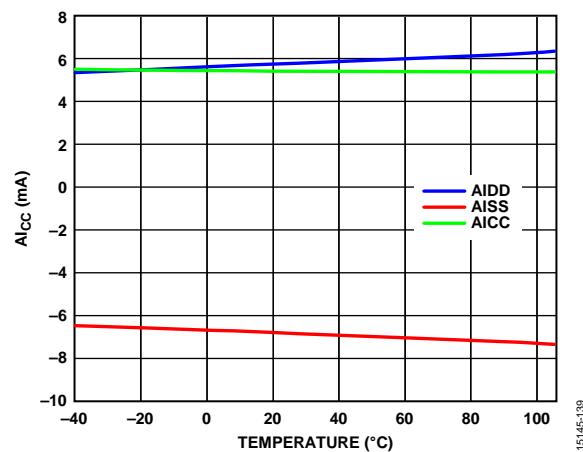

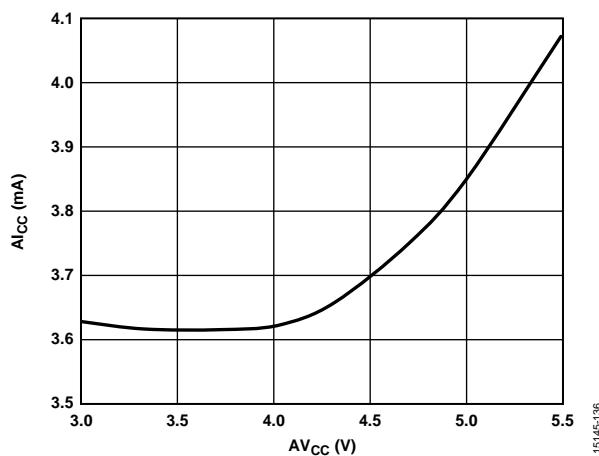

図 27. 通常動作モードでの電源電流 ( $AI_{CC}$ ) の温度特性図 25. 通常動作モードでの電源電流 ( $AI_{CC}$ )

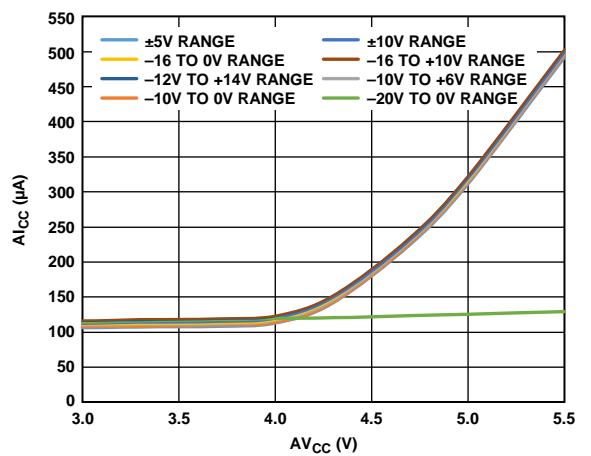

と電源電圧 ( $AV_{CC}$ ) の関係図 28. パワーダウン・モードでの電源電流 ( $AI_{CC}$ )

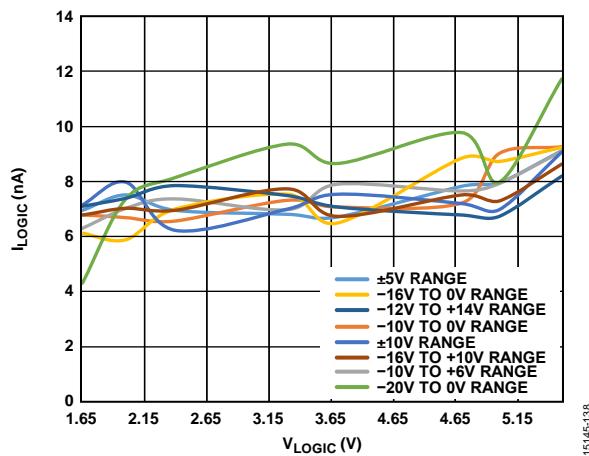

と電源電圧 ( $AV_{CC}$ ) の関係図 26. ロジック電流 ( $I_{LOGIC}$ ) とロジック入力電圧 ( $V_{LOGIC}$ )

の関係

## ディザ

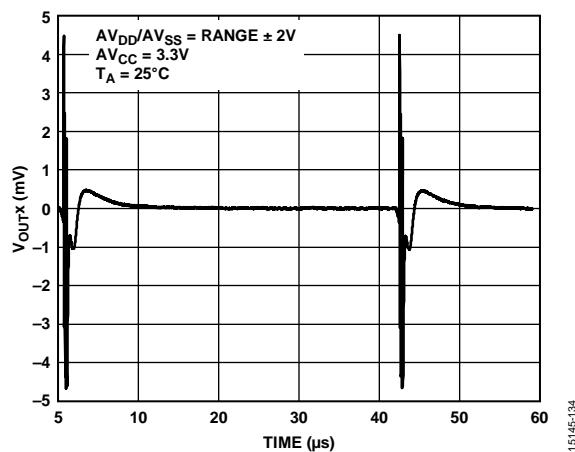

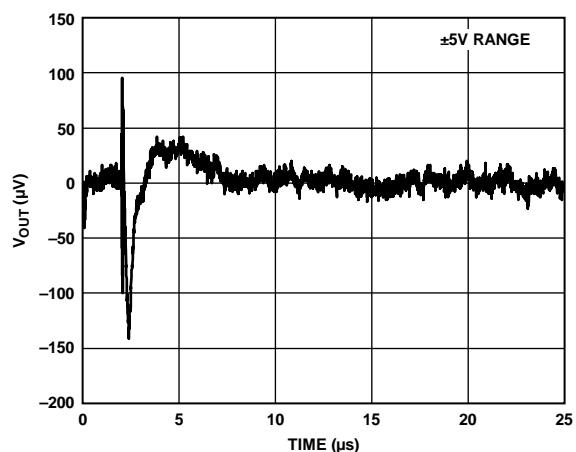

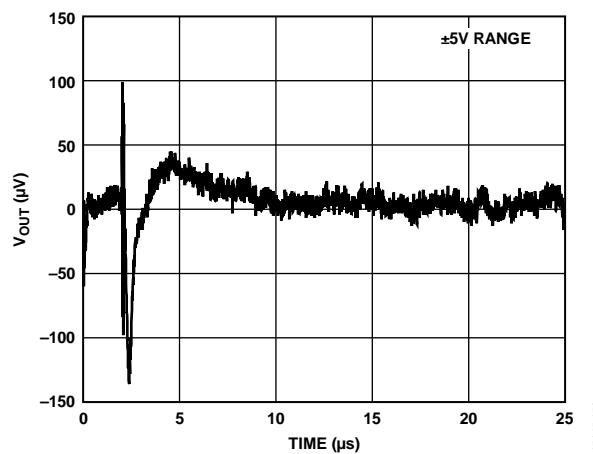

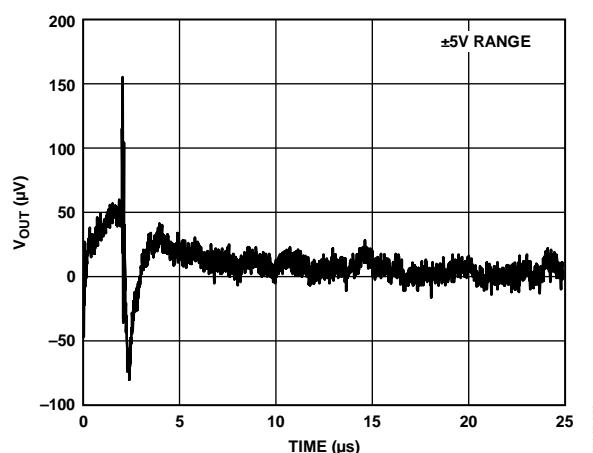

図 29. ディザ選択チャンネルでのトランジエント (ディザは有効)

図 32. ディザ未選択チャンネルでのトランジエント (ディザは無効)

図 30. ディザ未選択チャンネルでのトランジエント (ディザは有効)

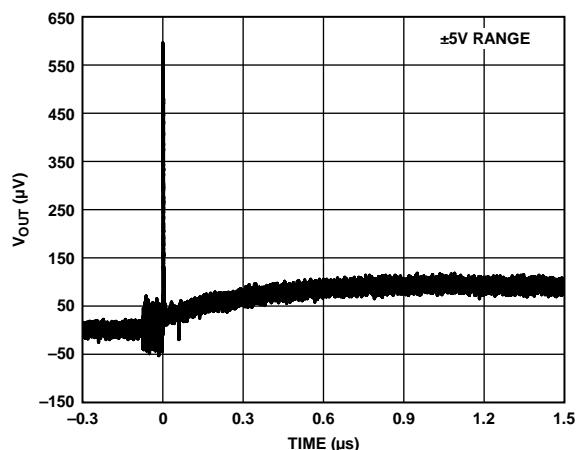

図 33. ディザの DC シフト

図 31. ディザ選択チャンネルでのトランジエント (ディザは無効)

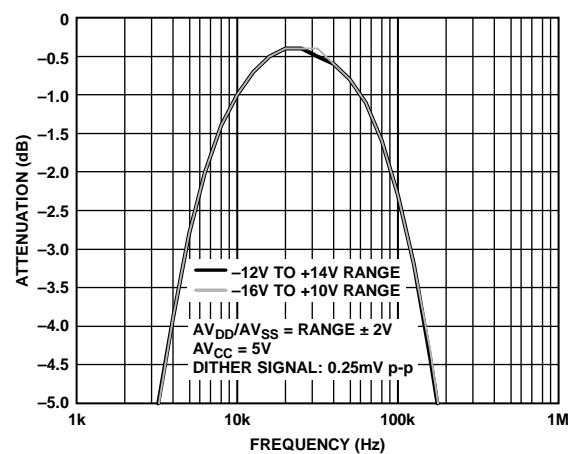

図 34. ディザ入力/DAC 出力の減衰量と周波数の関係 (範囲は ±5 V および -10 V ~ 0 V)

図 35. ディザ入力/DAC 出力の減衰量と周波数の関係

(範囲は ±10 V および -20 V ~ 0 V)

図 36. ディザ入力/DAC 出力の減衰量と周波数の関係

(範囲は -10 V ~ +6 V および -16 V ~ 0 V)

図 37. ディザ入力/DAC 出力の減衰量と周波数の関係

(範囲は -12 V ~ +14 V および -16 V ~ +10 V)

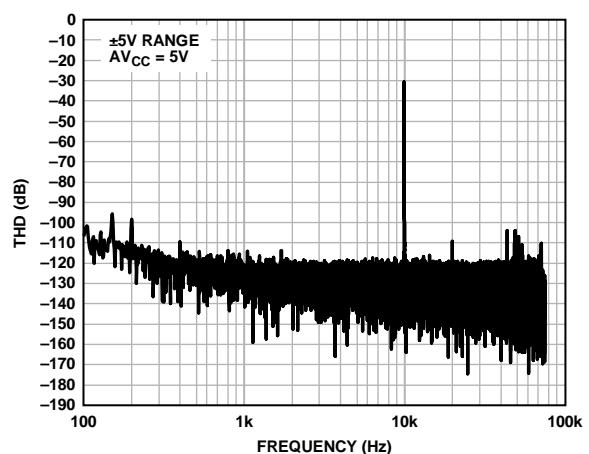

図 38. 全高調波歪み (THD) と周波数の関係

## 用語の定義

### 総合未調整誤差 (TUE)

総合未調整誤差とは、電源、温度、時間に関連するすべての誤差（つまり、INL 誤差、オフセット誤差、ゲイン誤差、出力ドリフト）を考慮する出力誤差の計測値です。TUE の単位は % FSR です。

### 相対精度または積分非直線性 (INL)

相対精度（積分非直線性）は、DAC の伝達関数の上下両端を結ぶ直線からの最大偏差（ LSB 単位）を表します。典型的な INL 誤差対 DAC コードのプロットを図 6 および図 7 に示します。

### 微分非直線性 (DNL)

微分非直線性 (DNL) は、隣接する 2 つのコードの間における測定された変化と理論的な 1 LSB 変化との差を表します。微分非直線性の仕様が ±1 LSB 以内の場合は、単調増加性が確保されます。この DAC は設計面で単調増加性を確保しています。典型的な DNL 誤差対 DAC コードのプロットを図 8 および図 9 に示します。

### ゼロスケール誤差

ゼロスケール誤差は、ゼロのコード（0x0000）を DAC レジスタに読み込んだときの出力誤差を測定したものです。ゼロコード誤差の単位は mV です。

### ゼロスケール誤差の温度係数

ゼロコード誤差ドリフトは、温度変化に伴うゼロコード誤差の変化を測定したもので、単位は  $\mu\text{V}/^\circ\text{C}$  です。

### バイポーラ・ゼロ誤差

バイポーラ・ゼロ誤差はすべての DAC レジスタに 0x2000 を読み込んだときの、0 V の理論ハーフスケール出力からのアナログ出力の偏差を表します。

### バイポーラ・ゼロ誤差の温度係数

バイポーラ・ゼロ・ドリフトは、温度変化に伴うバイポーラ・ゼロ誤差の変化を測定したもので、単位は  $\mu\text{V}/^\circ\text{C}$  です。

### ゲイン誤差

ゲイン誤差は DAC のスパン誤差を表します。DAC の伝達特性の傾き（理論値）からの偏差で、単位は % FSR です。

### ゲイン誤差の温度係数

ゲイン温度係数は、温度変化に伴うゲイン誤差の変化を測定したもので、単位は FSR/ $^\circ\text{C}$  です。

### オフセット誤差

オフセット誤差は、伝達関数の線形領域での  $V_{\text{OUTX}}$ （実測値）と  $V_{\text{OUTX}}$ （理想値）の差で、単位は mV です。オフセット誤差は、負または正の値となります。

### オフセット誤差ドリフト

オフセット誤差ドリフトは、温度変化に伴うオフセット誤差の変化を測定したもので、単位は  $\mu\text{V}/^\circ\text{C}$  です。

### DC シフト

DC シフトは、ディザ・トーンとアナログ出力の結合に起因する  $V_{\text{OUTX}}$ （実測値）と  $V_{\text{OUTX}}$ （理想値）間の DC 電圧の誤差の計測値です。単位は LSB です。

### ディザ・トランジェント

ディザ・トランジェントは、出力チャンネルのディザ機能を有効化または無効化することにより、アナログ出力に挿入されるインパルスの振幅です。このトランジェントは、選択された出力チャンネルとその他の選択されていないチャンネルで計測されます。単位は nV-sec です。

### DC 電源電圧変動除去比 (PSRR)

PSRR は、DAC 出力に対する電源電圧変化の影響を表します。PSRR は、DAC のフルスケール出力での  $\text{AV}_{\text{DD}}$  の変化に対する  $V_{\text{OUTX}}$  の変化の比で、単位は V/V です。

### 出力電圧セトリング・タイム

出力電圧セトリング・タイムは、フルスケールの 1/4 から 3/4 までの入力変化に対して、DAC 出力が規定のレベルで安定するのに要する時間で、SYNC の立上がりエッジから測定されます。

### デジタル／アナログ・グリッチ・インパルス

デジタル／アナログ・グリッチ・インパルスは、DAC レジスタの入力コードが変化したときに、アナログ出力に混入するインパルスを表します。通常、nV-sec で表すグリッチの面積として仕様規定され、メジャー・キャリー遷移時（AD5767 では 0x7FF から 0x800）に、デジタル入力コードが 1 LSB だけ変化したときに測定されます。

### デジタル・フィードスルー

デジタル・フィードスルーハーは、DAC 出力が更新されていないときに、DAC のデジタル入力から DAC のアナログ出力に注入されるインパルスを表します。nV-sec で仕様規定され、データ・バス上でのフルスケール・コードの変更時、すなわち全ビット 0 から全ビット 1 への変更時、または全ビット 1 から全ビット 0 への変更時に測定されます。

### DC クロストーク

DC クロストークとは、ある DAC 出力の変化によって生じる、別の DAC での出力レベルの DC 変化のことを指します。ある DAC をミッドスケールに維持してモニタリングしながら、別の DAC でのフルスケール出力の変化（または、パワーダウンおよびパワーアップ）を測定します。単位は  $\mu\text{V}$  です。

負荷電流変化に起因する DC クロストークでは、ある DAC の負荷電流の変化がミッドスケールに維持された別の DAC へ与える影響を測定します。単位は  $\mu\text{V}/\text{mA}$  です。

### デジタル・クロストーク

デジタル・クロストークとは、ある DAC の入力レジスタにおけるフルスケール・コードの変更（全ビット 0 から全ビット 1 への変更、および全ビット 1 から全ビット 0 への変更）に応じて、ミッドスケール・レベルにある別の DAC の出力に混入したグリッチ・インパルスのことを指します。スタンダードアロン・モードで測定し、単位は nV-sec です。

### アナログ・クロストーク

アナログ・クロストークとは、ある DAC の出力変化によって別の DAC の出力に混入したグリッチ・インパルスのことを指します。フルスケール・コードの変更時（全ビット 0 から全ビット 1 への変更、または全ビット 1 から全ビット 0 への変更）に入力レジスタのいずれかを読み込んで、ソフトウェア LDAC コマンドを実行し（表 17 を参照）、デジタル・コードが変更されなかった DAC の出力をモニタリングすることで計測されます。グリッチの面積は nV-sec で表されます。

### DAC 間クロストーク

DAC 間クロストークとは、デジタル・コードの変更に続く、ある DAC のアナログ出力の変化に起因して、別の DAC の出力に混入するグリッチ・インパルスのことを指します。書き込みコマンドと更新コマンドを使って、影響元のチャンネルにフルスケール・コードの変更（全ビット 0 から全ビット 1 への変更、および全ビット 1 から全ビット 0 への変更）を読み込み、ミッドスケールにある影響先のチャンネルの出力をモニタリングして測定します。グリッチのエネルギーの単位は nV-sec です。

### 出力ノイズ・スペクトル密度

出力ノイズ・スペクトル密度は、内部で発生するランダム・ノイズを測定したものです。ランダム・ノイズは、スペクトル密度 ( $\text{nV}/\sqrt{\text{Hz}}$ ) として特性評価されます。DAC にミッドスケールを読み込んで、その出力で発生するノイズを測定します。単位は  $\text{nV}/\sqrt{\text{Hz}}$  です。

## 動作原理

### D/A コンバータ

AD5767 は 16 チャンネル、12 ビット、シリアル入力、電圧出力 DAC 機能を備え、±20 mA の出力電流能力で複数の出力範囲を提供します。使用可能な範囲は次のとおりです。

- -20 V ~ 0 V

- -16 V ~ 0 V

- -10 V ~ 0 V

- -10 V ~ +6 V

- -12 V ~ +14 V

- -16 V ~ +10 V

- ±5 V

- ±10 V

デバイスは、次の 4 つの電源電圧で動作します。AV<sub>CC</sub>、AV<sub>DD</sub>、AV<sub>SS</sub>、V<sub>LOGIC</sub>。AV<sub>CC</sub> は DAC とその他の低電圧回路の電源入力電圧で、AV<sub>DD</sub> および AV<sub>SS</sub> は、出力アンプの正および負のアナログ電源です。出力アンプには、+2 V のヘッドルームと -2 V のフットルームが必要です。Table 7 に、選択した出力範囲の電源条件を示します。V<sub>LOGIC</sub> は、デジタル入出力信号のロジック・レベルを定義します。

表 7. 選択した出力範囲の電源条件

| Range (V)  | AV <sub>SS</sub> Maximum (V) | AV <sub>DD</sub> Minimum (V) |

|------------|------------------------------|------------------------------|

| -20 to 0   | -22                          | 2.97                         |

| -16 to 0   | -18                          | 2.97                         |

| -10 to 0   | -12                          | 2.97                         |

| -10 to +6  | -12                          | 8                            |

| -12 to +14 | -14                          | 16                           |

| -16 to +10 | -18                          | 12                           |

| -5 to +5   | -7                           | 7                            |

| -10 to +10 | -12                          | 12                           |

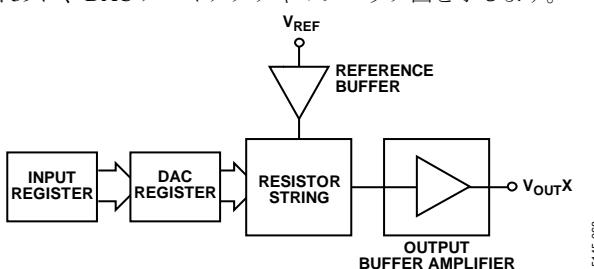

### DAC アーキテクチャ

DAC チャンネルのアーキテクチャは、抵抗ストリング DAC と一緒に続く出力バッファ・アンプで構成されます。V<sub>REF</sub> ピンの電圧は、すべての DAC チャンネルのリファレンス電圧を提供します。図 39 に、DAC アーキテクチャのブロック図を示します。

図 39. DAC アーキテクチャ

DAC の入力コーディングはストレート・バイナリで、理論上の電圧は次のように指定されます。

$$V_{OUT} = \left( \text{Span} \times \frac{D}{N} \right) + V_{MIN}$$

ここで

Span は、DAC 出力の最小値から最大値までの全範囲。

D は、DAC レジスタに読み込まれるバイナリ・コード（10 進数表示）。

N は、12 ビット・バージョンでは 4096。

V<sub>OUT</sub> は Span の最小電圧。

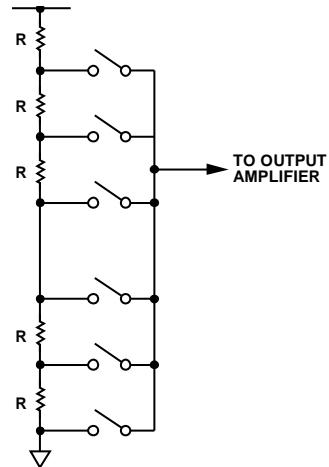

### 抵抗ストリング

図 40 に、抵抗ストリング・セクションを示します。これは簡略化された抵抗ストリング構造で、各抵抗値は R です。DAC レジスタに読み込まれるデジタル・コードによって、出力アンプに供給する電圧をストリング上のどのノードに接続するか決定されます。いずれかのスイッチを開じて、ストリングをアンプに接続することにより、電圧が取り出されます。抵抗ストリングが使用されるので、DAC の単調増加性が確保されます。

図 40. 抵抗ストリング

### パワーオン・リセット (POR)

AD5767 は、パワーアップ時に出力電圧を制御する POR 回路を内蔵しています。AD5767 出力は、パワーアップ時に GND にクランプされ、有効な書き込みシーケンスが Span・レジスタに対して実行されます。この際、DAC の出力範囲が設定されるまで、このレベルでパワーアップが維持されます。ソフトウェアで実行可能なリセット機能は、DAC をパワーアップ状態にリセットします。コマンド 0111 は、このリセット機能に割り当てられています（表 26 参照）。リセットと書き込みの間に必要な最小時間があります（表 3 の時間特性を参照）。

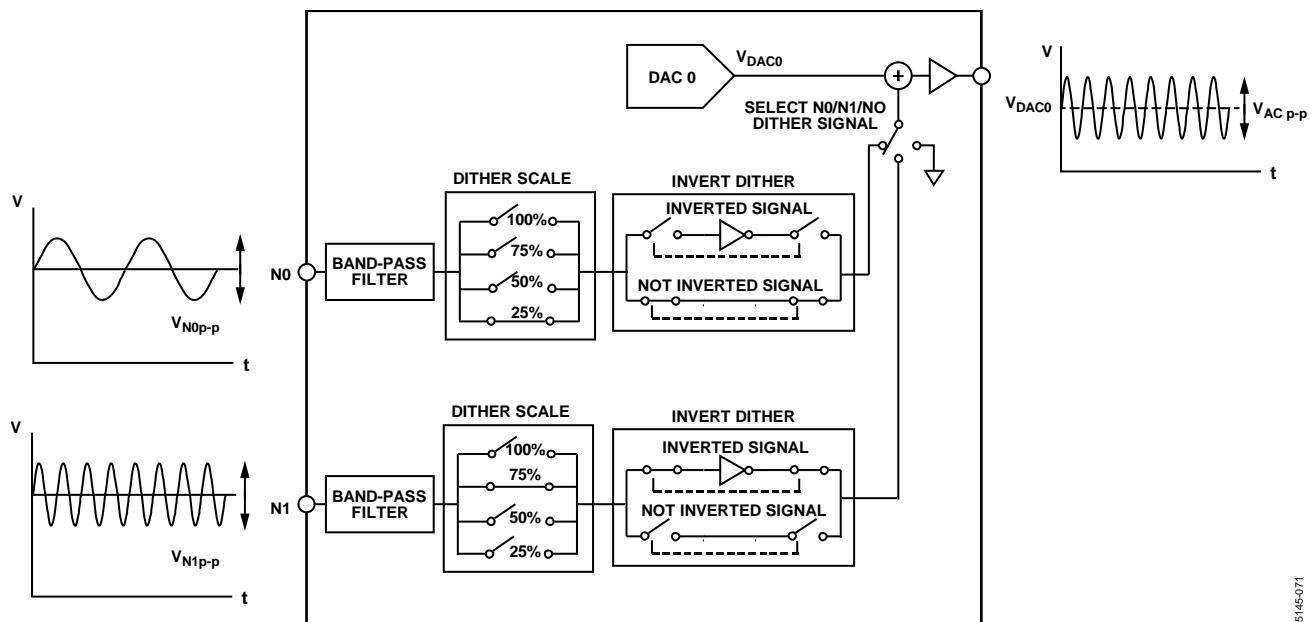

## ディザ

外部ディザ信号は、ディザ・レジスタに適切な値を書き込むことで、任意のDAC出力に結合できます。ディザ信号は、N0とN1の入力ピンに印加されます（図41を参照）。ディザが不要な場合は、これらのピンをAGNDに接続します。ディザ信号の振幅の最大ピークtoピーク電圧（AC電圧）は0.25V p-pです。絶対入力電圧（ACおよびDC電圧）は、0V～AV<sub>cc</sub>の範囲を超えてはいけません。必要に応じて、ディザ信号をチャンネルごとに内部で減衰または反転させることができます。10kHz～100kHzの範囲のディザ信号をディザ入力ピンに印加できます。内部ディザ回路の性質により、出力のDC値をシフトできます（表1を参照）。ディザ機能に推奨される構成については、アプリケーション情報のセクションを参照してください。

## パワーダウン・モード

AD5767には、2つの独立したパワーダウン・モード動作があります。チャンネル出力パワーダウン・モードとチャンネルごとのディザ・ロック・パワーダウン・モードです。コマンド0101がパワーダウン機能に予約されています（表8参照）。これら2つのパワーダウン・モードは、パワー・コントロール・レジスタの4ビット（ビットD19～ビットD16）を設定することで、ソフトウェアでプログラムできます。DACチャンネル出力のパワーダウン動作に対応するため、D19～D16を0000に設定する必要

があります。また、チャンネルごとのディザ・ロック・パワーダウンでは、D19～D16を0001に設定する必要があります（表22を参照）。ビットD16の状態と対応するデバイスの動作モードを表24に示します。対応する16ビット（D15～D0）を1に設定することで、すべてのDACを選択したモードにパワーダウンできます。

消費電力を節約するには、スパン・レジスタからすべてのチャンネルをイネーブルにしてから、未使用のDACチャンネルをすべてパワーダウン・モードにすることが推奨されます。

スパン・レジスタへの書き込みを実行してから、すべてのチャンネルをパワーダウンしてください。

## 監視マルチプレクサ

AD5767は、シリアル・インターフェース経由で指定されるアナログ・マルチプレクサによるチャンネル監視機能を備えています。これにより、外部監視用に任意のチャンネルを共通のMUX\_OUTピンにルーティングできます。

MUX\_OUTピンはバッファされないので、このピンから流れる電流の量により、スイッチ間の電圧が低下し、監視対象の電圧で誤差が発生します。そのため、MUX\_OUTピンは高インピーダンスの入力のみに接続するか、外部でバッファする必要があります。

図41. 典型的な外部ディザ信号の生成

15145-071

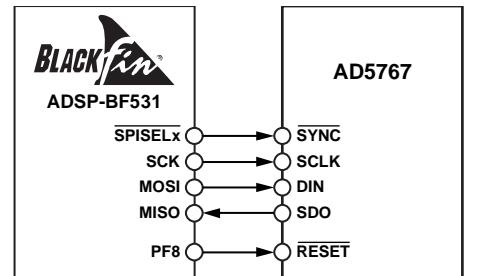

## シリアル・インターフェース

AD5767 4 線式 (SYNC、SCLK、SDI、SDO) インターフェースは、ほとんどのデジタル信号プロセッサ (DSP) と同様に、SPI、QSPI、および MICROWIRE インターフェース規格と互換性があります。SYNC ラインをロー・レベルにした後に書込みシーケンスが開始し、SDI ピンから完全なデータワードが読み込まれるまで、このラインはロー・レベルに維持されます。データは SCLK 立下がりエッジ遷移で AD5767 に読み込まれます (図 2 を参照)。SYNC で立上がりエッジが検出されると、シリアル・データワードが表 8 の指示に従ってデコードされます。コマンドは、24 の倍数にする必要があります。そうしないと、デバイスはコマンドを無視します。AD5767 は SDO ピンを備えているので、複数のデバイスをデイジーチェーン接続したり、ステータス・レジスタの内容をリードバックしたりできます。

## リードバック動作

ステータス・レジスタの内容は、SDO ピンからリードバックできます。図 4 に、レジスタをデコードする方法を示します。読み出し用レジスタが指定された後の 24 クロック・サイクルで、SDO ピンからデータをクロック出力します。クロックは、SYNC がロー・レベルの間に適用する必要があります。単一レジスタの読み出しでは、無操作 (NOP) 機能でデータをクロック出力します。代わりに、複数レジスタの読み出しでは、2 番目に読み出すレジスタが指定されると同時に、最初に指定されたレジスタのデータがクロック出力されます。

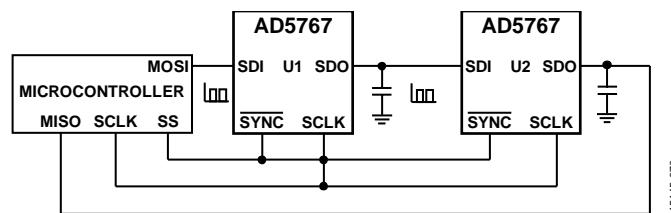

## デイジーチェーン動作

デイジーチェーンは、制御 IC で必要なポート・ピンの数を最低限に抑えます。図 42 に示すように、あるパッケージの SDO ピンを次のパッケージの SDI ピンに接続する必要があります。デイジーチェーン・モードを有効にするには、表 13 の DC\_EN ピットをハイにする必要があります。2 台の AD5767 デバイスをデイジーチェーン接続する場合は、48 ビットのデータが必要です。図 42 に示すように、最初の 24 ビットは U2 に割り当てられ、次の 24 ビットは U1 に割り当てられます。すべての 48 ビットが対応するシリアル・レジスタに入力されるまで、SYNC ピンをロー・レベルに維持します。

次に、SYNC ピンがハイ・レベルになり、動作が完了します。

データが (ノイズなどにより) 誤ってロックされないように、デバイスは内部カウンタを搭載しています。SCLK 立下がりエッジのカウントが 24 の倍数でない場合、デバイスはコマンドを無視します。有効なロック・カウントは、24、48、72 などです。SYNC がハイに戻ると、カウンタはリセットされます。

デイジーチェーン・モードはデフォルトで無効になっています。このモードは、デイジーチェーン制御レジスタを使用して有効にします (表 13 を参照)。

図 42. デイジーチェーンのブロック図

## レジスタの詳細

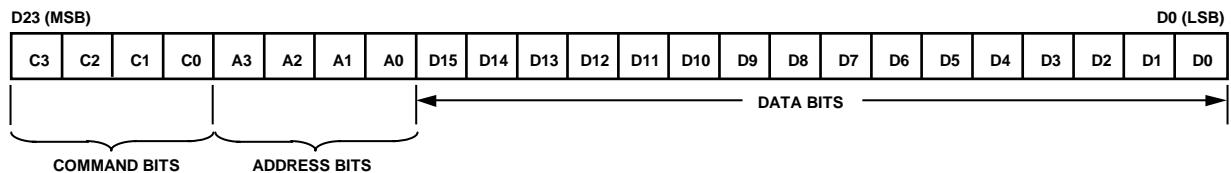

### 入力シフト・レジスタ

AD5767 の入力シフト・レジスタは 24 ビット幅です。データは MSB ファースト (DB23) で読み込まれます。最初の 4 ビットはコマンド・ビット C3 ~ C0 (図 43 参照)、次の 4 ビットは DAC アドレス・ビット (表 9 参照)、最後のビット列は DAC データワードです。データ・ビットは、SCLK の 24 個の立下がりエッジで入力レジスタに転送され、SYNC の立上がりエッジで更新されます。

1545-072

図 43. 入力シフト・レジスタ値

表 8. コマンドの定義<sup>1</sup>

| C3 | C2 | C1 | C0 | A3              | A2              | A1              | A0              | 名前                                                     | 説明                                                                                        |

|----|----|----|----|-----------------|-----------------|-----------------|-----------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 0  | 0  | 0  | 0  | 0               | 0               | 0               | 0               | NOP/monitor mux control                                | 動作なし (全ビット 0 のレジスタ)。監視マルチプレクサ制御レジスタ (D4=1) を使用して、MUX_OUT ピンで DAC 出力と出力なしのどちらに切り替えるか決定します。 |

| 0  | 0  | 0  | 0  | 0               | 0               | 0               | 1               | Daisy-chain mode                                       | デイジーチェーン・モードで SDO 出力バッファを有効／無効にします。                                                       |

| 0  | 0  | 0  | 1  | A3 <sup>2</sup> | A2 <sup>2</sup> | A1 <sup>2</sup> | A0 <sup>2</sup> | Write to DACx input register                           | 選択した DAC チャンネルに対して、入力レジスタにデータを書き込みます。                                                     |

| 0  | 0  | 1  | 0  | A3 <sup>2</sup> | A2 <sup>2</sup> | A1 <sup>2</sup> | A0 <sup>2</sup> | Write to input register and DAC register               | 選択した DAC チャンネルに対して、入力レジスタと DAC レジスタにデータを書き込みます。                                           |

| 0  | 0  | 1  | 1  | X               | X               | X               | X               | Software load DAC (LDAC)                               | 対応する入力レジスタのデータで、選択した DAC をアップロードします。                                                      |

| 0  | 1  | 0  | 0  | A3 <sup>2</sup> | A2 <sup>2</sup> | A1 <sup>2</sup> | A0 <sup>2</sup> | Span                                                   | AD5767 の出力スパンを選択します。                                                                      |

| 0  | 1  | 0  | 1  | 0               | 0               | 0               | 0               | Power control (DAC channel)                            | 個別の DAC チャンネルで選択した DAC 出力をパワーアップ／ダウントします。                                                 |

| 0  | 1  | 0  | 1  | 0               | 0               | 0               | 1               | Power control (dither)                                 | 個別の DAC チャンネルでディザ機能をパワー・アップ／ダウンします。                                                       |

| 0  | 1  | 1  | 0  | X               | X               | X               | X               | Write input data to all DAC registers                  | すべての DAC チャンネルに対して、入力レジスタと DAC レジスタにデータを書き込みます。                                           |

| 0  | 1  | 1  | 1  | 0               | 0               | 0               | 0               | Software full reset                                    | このレジスタに 0x1234 を書き込むと、AD5767 がリセットされます。                                                   |

| 1  | 0  | 0  | 0  | A3 <sup>2</sup> | A2 <sup>2</sup> | A1 <sup>2</sup> | A0 <sup>2</sup> | Select register for readback                           | 選択した DAC チャンネルに対して、リードバックするレジスタを選択します。                                                    |

| 1  | 0  | 0  | 1  | X               | X               | X               | X               | Apply N0 or N1 dither signal to DACs (DAC 7 to DAC 0)  | 各 DAC 出力に対して、N0 のディザを適用する、N1 のディザを適用する、またはディザを適用しないか選択します。                                |

| 1  | 0  | 1  | 0  | X               | X               | X               | X               | Apply N0 or N1 dither signal to DACs (DAC 15 to DAC 8) | 各 DAC 出力に対して、N0 のディザを適用する、N1 のディザを適用する、またはディザを適用しないか選択します。                                |

| 1  | 1  | 0  | 0  | X               | X               | X               | X               | Dither scale (DAC 7 to DAC 0)                          | 選択した DAC 出力に適用するディザ信号をスケーリングします。                                                          |

| 1  | 1  | 0  | 1  | X               | X               | X               | X               | Dither scale (DAC 15 to DAC 8)                         | 選択した DAC 出力に適用するディザ信号をスケーリングします。                                                          |

| 1  | 0  | 1  | 1  | X               | X               | X               | X               | Invert dither                                          | 選択した DAC 出力に適用するディザ信号を反転します。                                                              |

| 1  | 1  | 1  | 0  | X               | X               | X               | X               | Reserved                                               | 該当せず。                                                                                     |

| 1  | 1  | 1  | 1  | X               | X               | X               | X               | Reserved                                               | 該当せず。                                                                                     |

<sup>1</sup> X はドントケア。<sup>2</sup> アドレス・ビットの設定については、表 9 を参照してください。

表9に、DACxアドレス・コマンドを示します。16チャンネルすべてが必要でないアプリケーションでは、クロストークやデジタル・フィードスルーの影響を受けやすいので、チャンネル8を使用しないでください。

表9. DACxアドレス・コマンド

| Address |    |    |    | Selected DAC |

|---------|----|----|----|--------------|

| A3      | A2 | A1 | A0 |              |

| 0       | 0  | 0  | 0  | DAC 0        |

| 0       | 0  | 0  | 1  | DAC 1        |

| 0       | 0  | 1  | 0  | DAC 2        |

| 0       | 0  | 1  | 1  | DAC 3        |

| 0       | 1  | 0  | 0  | DAC 4        |

| 0       | 1  | 0  | 1  | DAC 5        |

| 0       | 1  | 1  | 0  | DAC 6        |

| 0       | 1  | 1  | 1  | DAC 7        |

| 1       | 0  | 0  | 0  | DAC 8        |

| 1       | 0  | 0  | 1  | DAC 9        |

| 1       | 0  | 1  | 0  | DAC 10       |

| 1       | 0  | 1  | 1  | DAC 11       |

| 1       | 1  | 0  | 0  | DAC 12       |

| 1       | 1  | 0  | 1  | DAC 13       |

| 1       | 1  | 1  | 0  | DAC 14       |

| 1       | 1  | 1  | 1  | DAC 15       |

### 監視マルチプレクサ制御

監視マルチプレクサ制御コマンドは、目的のD[4:0]値に従って、MUX\_OUTピンでDAC出力と出力なしのどちらに切り替えるか決定します。動作コマンドをアサートしない場合は、D15～D0ビットすべてに0を書き込みます。

表10. 監視マルチプレクサ制御レジスタ

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 to D5  | D4 to D0 |

|-----|-----|-----|-----|-----|-----|-----|-----|------------|----------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Don't care | VOUT_SEL |

表11. マルチプレクサからの出力電圧選択

| VOUT_SEL, Bits[4:0] <sup>1</sup> |   |   |   |   | Mux Output                |

|----------------------------------|---|---|---|---|---------------------------|

| 0                                | X | X | X | X | No output is switched out |

| 1                                | 0 | 0 | 0 | 0 | V <sub>OUT</sub> 0        |

| 1                                | 0 | 0 | 0 | 1 | V <sub>OUT</sub> 1        |

| 1                                | 0 | 0 | 1 | 0 | V <sub>OUT</sub> 2        |

| 1                                | 0 | 0 | 1 | 1 | V <sub>OUT</sub> 3        |

| 1                                | 0 | 1 | 0 | 0 | V <sub>OUT</sub> 4        |

| 1                                | 0 | 1 | 0 | 1 | V <sub>OUT</sub> 5        |

| 1                                | 0 | 1 | 1 | 0 | V <sub>OUT</sub> 6        |

| 1                                | 0 | 1 | 1 | 1 | V <sub>OUT</sub> 7        |

| 1                                | 1 | 0 | 0 | 0 | V <sub>OUT</sub> 8        |

| 1                                | 1 | 0 | 0 | 1 | V <sub>OUT</sub> 9        |

| 1                                | 1 | 0 | 1 | 0 | V <sub>OUT</sub> 10       |

| 1                                | 1 | 0 | 1 | 1 | V <sub>OUT</sub> 11       |

| 1                                | 1 | 1 | 0 | 0 | V <sub>OUT</sub> 12       |

| 1                                | 1 | 1 | 0 | 1 | V <sub>OUT</sub> 13       |

| 1                                | 1 | 1 | 1 | 0 | V <sub>OUT</sub> 14       |

| 1                                | 1 | 1 | 1 | 1 | V <sub>OUT</sub> 15       |

<sup>1</sup>Xはドントケア。

## 動作なし

全ビットに 0 を書き込んでも、デバイスの状態は変わりません。

表 12. 動作なしレジスタ

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 to D0           |

|-----|-----|-----|-----|-----|-----|-----|-----|---------------------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0000 0000 0000 0000 |

## デイジーチェーン・モード

デイジーチェーン・モードを使用するには、デイジーチェーン制御レジスタの DC\_EN ビットを有効にします。このビットは、内部 SDO バッファにリンクされます。この機能が不要の場合、DC\_EN ビットを 0 に設定すれば、SDO バッファで消費される電力を節約できます。

表 13. デイジーチェーン制御レジスタ

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 to D1  | D0    |

|-----|-----|-----|-----|-----|-----|-----|-----|------------|-------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | Don't care | DC_EN |

表 14. デイジーチェーン有効／無効ビットの説明

| DC_EN | 説明                |

|-------|-------------------|

| 0     | デイジーチェーン無効（デフォルト） |

| 1     | デイジーチェーン有効        |

## 書き込みコマンドと更新コマンド

### DAC x 入力レジスタへの書き込み

このコマンドを実行すると、各 DAC 専用の入力レジスタに個別に値を書き込みます。更新するように指定されたチャンネルが含まれるビットでソフトウェア LDAC レジスタへの書き込みが発生するまで、DAC の出力値は変わりません。

表 15. DAC x 入力レジスタへの書き込み

| D23 | D22 | D21 | D20 | D19 to D16                  | D15 to D4           | D3 to D0    |

|-----|-----|-----|-----|-----------------------------|---------------------|-------------|

| 0   | 0   | 0   | 1   | DAC x address (see Table 9) | Input register data | Do not care |

### 入力レジスタおよび DAC レジスタへの書き込み

このコマンドを実行すると、選択された DAC レジスタに値が書き込まれ、出力が更新されます。

表 16. DACx 入力および DAC レジスタへの書き込み

| D23 | D22 | D21 | D20 | D19 to D16                  | D15 to D4           | D3 to D0    |

|-----|-----|-----|-----|-----------------------------|---------------------|-------------|

| 0   | 0   | 1   | 0   | DAC x address (see Table 9) | Input register data | Do not care |

### ソフトウェア LDAC レジスタ

このコマンドを実行すると、選択した入力レジスタから対応する DAC レジスタにデータがコピーされ、出力が更新されます。

表 17. ソフトウェア LDAC レジスタ

| D23 | D22 | D21 | D20 | D19 to D16  | D15 to D4                   |

|-----|-----|-----|-----|-------------|-----------------------------|

| 0   | 0   | 1   | 1   | Do not care | LDAC (bit for each channel) |

表 18. LDAC ビットの説明

| LDAC | 説明          |

|------|-------------|

| 0    | チャンネルを更新しない |

| 1    | チャンネルの更新    |

## スパン・レジスタ

このレジスタは、AD5767の出力スパンを選択します。表20および表21を参照。スパン・レジスタへの書き込みを実行する前に、必ずソフトウェア・リセットを実行してください。

表 19. スパン・レジスタ

| D23 | D22 | D21 | D20 | D19 to D5   | D4 to D3                    | D2 to D0      |

|-----|-----|-----|-----|-------------|-----------------------------|---------------|

| 0   | 1   | 0   | 0   | Do not care | P[1:0] (power-up condition) | S[2:0] (span) |

表 20. スパン選択

| S2 | S1 | S0 | Output Voltage Range |

|----|----|----|----------------------|

| 0  | 0  | 0  | -20 V to 0 V         |

| 0  | 0  | 1  | -16 V to 0 V         |

| 0  | 1  | 0  | -10 V to 0 V         |