## 特長

シングル18ビットnanoDAC

18ビット単調増加性

12ビット精度を保証

小型の8ピンSOT-23パッケージ

ゼロスケール/ミッドスケールにパワーオン・リセット

電源電圧: 4.5~5.5V

シリアル・インターフェース

レールtoレール動作

SYNC割込み機能

温度範囲: -40~+105°C

## アプリケーション

クローズドループ・プロセス制御

低帯域幅データ・アクイジション・システム

バッテリ駆動の携帯型計測器

ゲインとオフセットの調整

高精度なセットポイント制御

## 概要

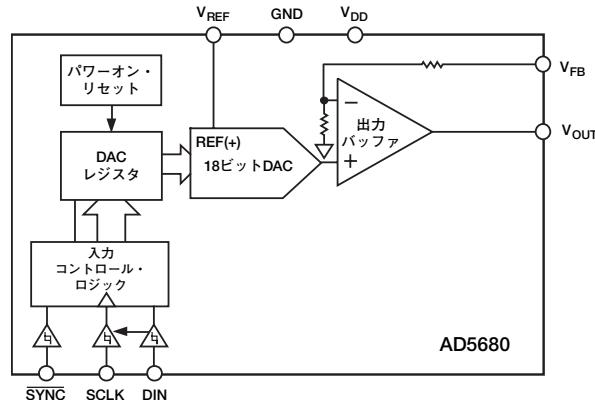

nanoDACファミリーのAD5680は、18ビット、バッファ付きの電圧出力シングルD/Aコンバータ(DAC)です。4.5~5.5Vの単電源で動作し、18ビットの単調増加性があります。

DACの出力電圧範囲を設定するには、外部リファレンス電圧が必要です。パワーオン・リセット回路を内蔵しているため、パワーアップ時にDACの出力が0V(AD5680-1)またはミッドスケール(AD5680-2)にリセットされ、有効な書き込みが行われるまで出力はこの電圧を維持します。

通常動作の消費電力が少ないため、バッテリ駆動の携帯型機器に最適です。消費電力は5V動作時に1.6mWです。

AD5680のオンチップ高精度出力アンプによって、レールtoレールの出力振幅が可能です。リモート・センシングのアプリケーションでは、出力アンプの反転入力を利用できます。

## 機能ブロック図

図1

05-001

AD5680は最高30MHzのクロック速度で動作する汎用3線式シリアル・インターフェースを使用し、業界標準のSPI®、QSPI™、MICROWIRE™、DSPインターフェース規格と互換性があります。

## 製品のハイライト

1. 18ビットの分解能

2. 18ビットDACで12ビット精度を保証

3. 8ピンSOT-23を採用

4. 低消費電力: 5V電源で1.6mW (typ)

5. ゼロスケールまたはミッドスケールにパワーオン・リセット

## 関連デバイス

AD5662: SOT-23パッケージの16ビットDAC

## 目次

|            |    |                                      |    |

|------------|----|--------------------------------------|----|

| 特長         | 1  | 出力アンプ                                | 11 |

| アプリケーション   | 1  | インターポレータのアーキテクチャ                     | 11 |

| 機能ブロック図    | 1  | シリアル・インターフェース                        | 12 |

| 概要         | 1  | 入力シフト・レジスタ                           | 12 |

| 製品のハイライト   | 1  | SYNC割込み                              | 12 |

| 関連デバイス     | 1  | パワー・リセット                             | 12 |

| 改訂履歴       | 2  | マイクロプロセッサとのインターフェース                  | 13 |

| 仕様         | 3  | アプリケーション                             | 14 |

| タイミング特性    | 4  | クローズドループ・アプリケーション                    | 14 |

| 絶対最大定格     | 5  | フィルタ                                 | 14 |

| ESDに関する注意  | 5  | AD5680のリファレンスの選択                     | 15 |

| ピン配置と機能の説明 | 6  | リファレンスをAD5680の電源として使用する方法            | 16 |

| 代表的な性能特性   | 7  | デジタル・アイソレータ ( <i>iCoupler</i> ) を用いた |    |

| 用語の説明      | 10 | 絶縁インターフェース                           | 16 |

| 動作原理       | 11 | 電源のバイパスとグラウンディング                     | 16 |

| DAC部       | 11 | 外形寸法                                 | 17 |

| 抵抗ストリング    | 11 | オーダー・ガイド                             | 17 |

## 改訂履歴

### 3/07—Rev. 0 to Rev. A

|                                         |    |

|-----------------------------------------|----|

| Changes to Input Shift Register Section | 12 |

| Changes to Figure 25                    | 12 |

### 6/06—Revision 0: Initial Version

## 仕様

$V_{DD}=4.5\sim5.5V$ 、 $R_L=2k\Omega$  (GNDに接続)、 $C_L=200pF$  (GNDに接続)、 $V_{REF}=V_{DD}$ 、特に指定のない限り、すべての仕様は $T_{MIN}\sim T_{MAX}$ で規定。

表1

| パラメータ                         | Min       | Typ       | Max | 単位               | テスト条件／備考                                                                     |

|-------------------------------|-----------|-----------|-----|------------------|------------------------------------------------------------------------------|

| 静的性能 <sup>2</sup>             |           |           |     |                  |                                                                              |

| 分解能                           | 18        |           |     | ビット              |                                                                              |

| 相対精度                          | $\pm 32$  | $\pm 64$  |     | LSB              |                                                                              |

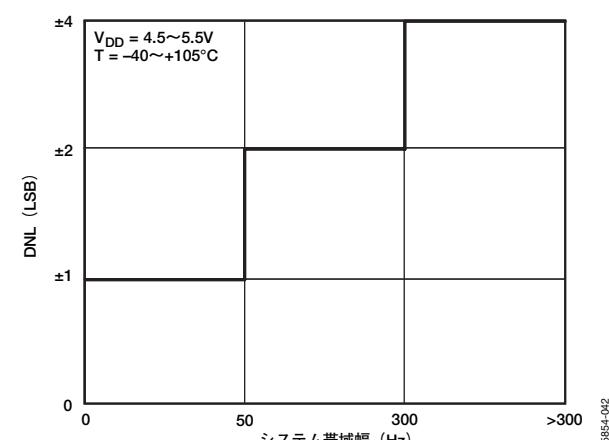

| 微分非直線性 <sup>3</sup>           | $\pm 1$   | LSB       |     | 50Hzのシステム帯域幅で測定  |                                                                              |

|                               | $\pm 2$   | LSB       |     | 300Hzのシステム帯域幅で測定 |                                                                              |

| ゼロコード誤差                       | 2         | 10        |     | mV               | DACレジスタに全ビット「0」をロード                                                          |

| フルスケール誤差                      | -0.2      | -1        |     | FSRの%            | DACレジスタに全ビット「1」ロード                                                           |

| オフセット誤差                       |           | $\pm 10$  |     | mV               |                                                                              |

| ゲイン誤差                         |           | $\pm 1.5$ |     | FSRの%            |                                                                              |

| ゼロコード誤差ドリフト                   | $\pm 2$   |           |     | $\mu V/^\circ C$ |                                                                              |

| ゲイン温度係数                       | $\pm 2.5$ |           |     | ppm              | FSR/°Cのppm                                                                   |

| DC電源電圧変動除去比                   | -100      |           |     | dB               | DACコード=ミッドスケール、 $V_{DD}=5V\pm 10\%$                                          |

| 出力特性 <sup>3</sup>             |           |           |     |                  |                                                                              |

| 出力電圧範囲                        | 0         | $V_{DD}$  |     | V                |                                                                              |

| 出力電圧セトリング時間                   | 80        | 85        |     | $\mu s$          | 1/4から3/4スケールへのコード遷移 ( $\pm 8$ LSBまで)<br>$R_L=2k\Omega$ 、 $0pF < C_L < 200pF$ |

| スルーレート                        | 1.5       |           |     | $V/\mu s$        | 1/4～3/4スケール                                                                  |

| 容量性負荷安定性                      | 2         |           |     | nF               | $R_L=\infty$                                                                 |

|                               | 10        |           |     | nF               | $R_L=2k\Omega$                                                               |

| 出力ノイズ・スペクトル密度 <sup>4</sup>    | 80        |           |     | $nV/\sqrt{Hz}$   | DACコード=ミッドスケール、10kHz                                                         |

| 出力ノイズ (0.1～10Hz) <sup>4</sup> | 25        |           |     | $\mu V_{p-p}$    | DACコード=ミッドスケール                                                               |

| 全高調波歪み (THD) <sup>4</sup>     | -80       |           |     | dB               | $V_{REF}=2V\pm 300mV_{p-p}$ 、 $f=200Hz$                                      |

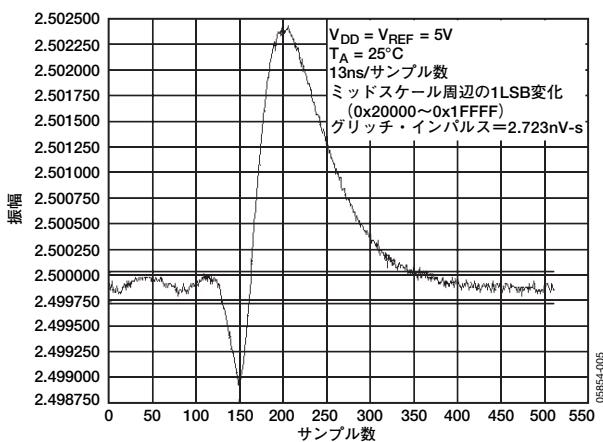

| デジタルからアナログへの<br>グリッチ・インパルス    | 5         |           |     | nV-s             | メジャー・キャリー周辺の1LSBの変化                                                          |

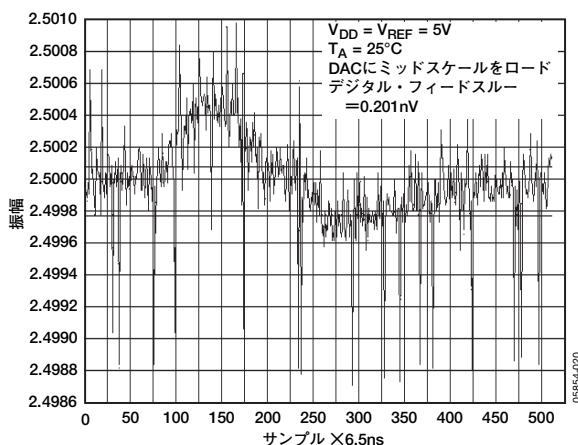

| デジタル・フィードスルー                  | 0.2       |           |     | nV-s             |                                                                              |

| DC出力インピーダンス                   | 0.5       |           |     | $\Omega$         |                                                                              |

| 短絡電流 <sup>4</sup>             | 30        |           |     | mA               | $V_{DD}=5V$                                                                  |

| リファレンス入力                      |           |           |     |                  |                                                                              |

| リファレンス電流                      | 40        | 75        |     | $\mu A$          | $V_{REF}=V_{DD}=5V$                                                          |

| リファレンス入力範囲 <sup>5</sup>       | 0.75      | $V_{DD}$  |     | V                |                                                                              |

| リファレンス入力インピーダンス               | 125       |           |     | $k\Omega$        |                                                                              |

| ロジック入力                        |           |           |     |                  |                                                                              |

| 入力電流                          |           | $\pm 2$   |     | $\mu A$          | すべてのデジタル入力                                                                   |

| ローレベル入力電圧 ( $V_{INL}$ )       |           | 0.8       |     | V                | $V_{DD}=5V$                                                                  |

| ハイレベル入力電圧 ( $V_{INH}$ )       | 2         |           |     | V                | $V_{DD}=5V$                                                                  |

| ピン容量                          | 3         |           |     | pF               |                                                                              |

| 電源条件                          |           |           |     |                  |                                                                              |

| $V_{DD}$                      | 4.5       | 5.5       |     | V                | すべてのデジタル入力=0Vまたは $V_{DD}$                                                    |

| $I_{DD}$ (ノーマル・モード)           |           |           |     |                  | DAC動作時 (負荷電流を除く)                                                             |

| $V_{DD}=4.5\sim 5.5V$         | 325       | 450       |     | $\mu A$          | $V_{INH}=V_{DD}$ および $V_{INL}=GND$                                           |

| 電力効率                          |           |           |     |                  |                                                                              |

| $I_{OUT}/I_{DD}$              |           | 85        |     | %                | $I_{LOAD}=2mA$ 、 $V_{DD}=5V$                                                 |

<sup>1</sup> Bバージョンの温度範囲： $-40\sim+105^\circ C$ 、 $25^\circ C$ で測定。

<sup>2</sup> 特に指定のない限り、DC仕様のテストは出力無負荷の条件で実施。直線性はコード範囲を2048～260096に縮小して計算。

<sup>3</sup> これらの仕様については出荷テストを行っていませんが、設計および特性評価により保証。

<sup>4</sup> 出力は無負荷。

<sup>5</sup> 最大DNL仕様が得られる周囲条件でのリファレンス入力電圧範囲。

# AD5680

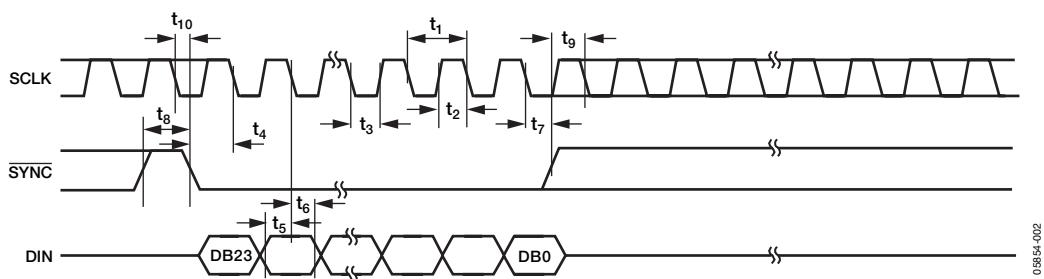

## タイミング特性

入力信号はすべて、 $t_R = t_F = 1\text{ns/V}$  ( $V_{DD}$ の10~90%) の条件で規定し、 $(V_{INL} + V_{INH})/2$ の電圧レベルからのタイミングを計測しています(図2を参照)。 $V_{DD} = 4.5\sim 5.5\text{V}$ 。特に指定のない限り、すべての仕様は $T_{MIN}\sim T_{MAX}$ で規定。

表2

| パラメータ    | $T_{MIN}, T_{MAX}$ での限界値<br>$V_{DD}=4.5\sim 5.5\text{V}$ | 単位       | テスト条件／備考                                              |

|----------|----------------------------------------------------------|----------|-------------------------------------------------------|

| $t_1^1$  | 33                                                       | ns (min) | SCLKサイクル時間                                            |

| $t_2$    | 13                                                       | ns (min) | SCLKハイレベル時間                                           |

| $t_3$    | 13                                                       | ns (min) | SCLKローレベル時間                                           |

| $t_4$    | 13                                                       | ns (min) | $\overline{\text{SYNC}}$ からSCLKの立下がりエッジまでのセットアップ時間    |

| $t_5$    | 5                                                        | ns (min) | データのセットアップ時間                                          |

| $t_6$    | 4.5                                                      | ns (min) | データのホールド時間                                            |

| $t_7$    | 0                                                        | ns (min) | SCLKの立下がりエッジから $\overline{\text{SYNC}}$ の立上がりエッジまでの時間 |

| $t_8$    | 33                                                       | ns (min) | 最小の $\overline{\text{SYNC}}$ ハイレベル時間                  |

| $t_9$    | 13                                                       | ns (min) | $\overline{\text{SYNC}}$ の立上がりエッジからSCLKの立下がりエッジまでの時間  |

| $t_{10}$ | 0                                                        | ns (min) | SCLKの立下がりエッジから $\overline{\text{SYNC}}$ の立上がりエッジまでの時間 |

<sup>1</sup> SCLKの最大周波数は30MHz ( $V_{DD}=4.5\sim 5.5\text{V}$ )。

図2. シリアル書込み動作

## 絶対最大定格

特に指定のない限り、 $T_A=25^\circ\text{C}$ 。

表3

| パラメータ                  | 定格値                                      |

|------------------------|------------------------------------------|

| GNDに対する $V_{DD}$       | $-0.3 \sim +7\text{V}$                   |

| GNDに対する $V_{OUT}$      | $-0.3\text{V} \sim V_{DD} + 0.3\text{V}$ |

| GNDに対する $V_{FB}$       | $-0.3\text{V} \sim V_{DD} + 0.3\text{V}$ |

| GNDに対する $V_{REF}$      | $-0.3\text{V} \sim V_{DD} + 0.3\text{V}$ |

| GNDに対するデジタル入力電圧        | $-0.3\text{V} \sim V_{DD} + 0.3\text{V}$ |

| 動作温度範囲                 |                                          |

| 工業用（Bバージョン）            | $-40 \sim +105^\circ\text{C}$            |

| 保存温度範囲                 | $-65 \sim +150^\circ\text{C}$            |

| ジャンクション温度 ( $T_J$ max) | $150^\circ\text{C}$                      |

| 消費電力                   | $(T_J\text{max} - T_A) / \theta_{JA}$    |

| $\theta_{JA}$ 熱抵抗      |                                          |

| SOT-23パッケージ (4層ボード)    | $119^\circ\text{C/W}$                    |

| リフロー・ハンダ付けのピーク温度       |                                          |

| 鉛フリー                   | $260^\circ\text{C}$                      |

左記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

### ESDに関する注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

## AD5680

### ピン配置と機能の説明

図3. ピン配置

表4. ピン機能の説明

| ピン番号 | 記号               | 説明                                                                                                                                                                                                               |

|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | V <sub>DD</sub>  | 電源入力。このデバイスは4.5~5.5Vで動作します。V <sub>DD</sub> はGNDにデカップリングしてください。                                                                                                                                                   |

| 2    | V <sub>REF</sub> | リファレンス電圧入力                                                                                                                                                                                                       |

| 3    | V <sub>FB</sub>  | 出力アンプの帰還接続ピン。通常の動作時はV <sub>FB</sub> をV <sub>OUT</sub> に接続してください。                                                                                                                                                 |

| 4    | V <sub>OUT</sub> | DACからのアナログ出力電圧。出力アンプはレールtoレールで動作します。                                                                                                                                                                             |

| 5    | SYNC             | レベル・トリガの制御入力（アクティブ・ロー）。これは入力データに対するフレーム同期信号です。SYNCがローレベルになると、入力シフト・レジスタがイネーブルになり、データは後続のクロックの立下がりエッジで転送されます。DACは、24番目のクロック・サイクルの後に更新されます。ただし、このエッジより前にSYNCがハイレベルになると、SYNCの立上がりエッジは割込みとして機能し、DACは書き込みシーケンスを無視します。 |

| 6    | SCLK             | シリアル・クロック入力。シリアル・クロック入力の立下がりエッジで、データが入力シフト・レジスタに入力されます。データは最大30MHzのレートで転送できます。                                                                                                                                   |

| 7    | DIN              | シリアル・データ入力。このデバイスには24ビットのシフト・レジスタがあります。データは、シリアル・クロック入力の立下がりエッジでレジスタに入力されます。                                                                                                                                     |

| 8    | GND              | グラウンド基準ポイント（デバイス上の全回路について）                                                                                                                                                                                       |

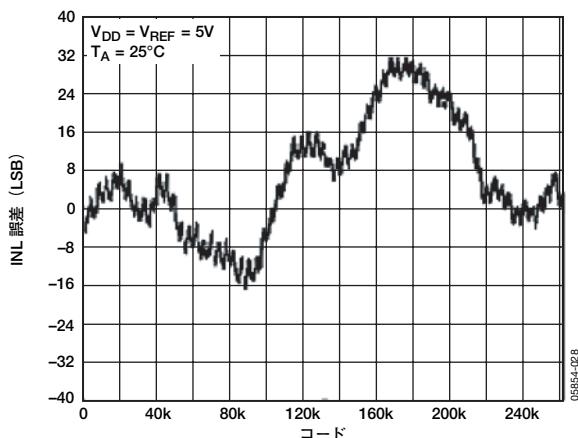

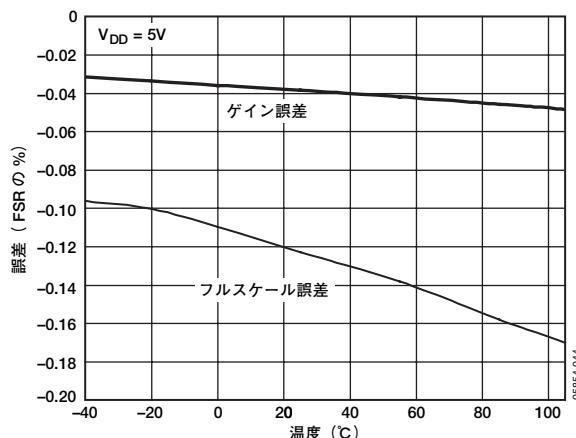

## 代表的な性能特性

図4. 代表的なINL

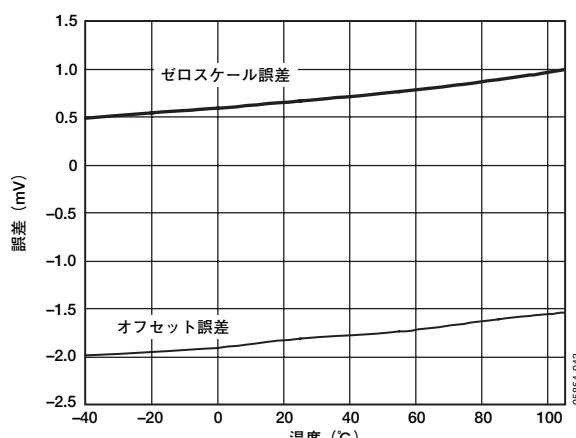

図7. ゲイン誤差とフルスケール誤差の温度特性

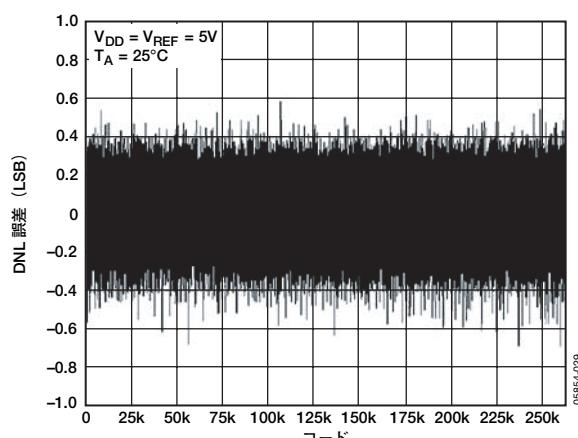

図5. 50Hzシステム帯域幅での代表的なDNL

図8. ゼロスケール誤差とオフセット誤差の温度特性

図6. システム帯域幅 対 DNL性能

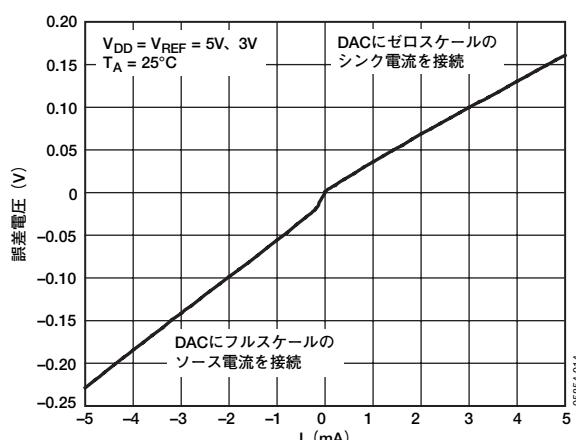

図9. ソースおよびシンク電流 対 電源レールのヘッドルーム

# AD5680

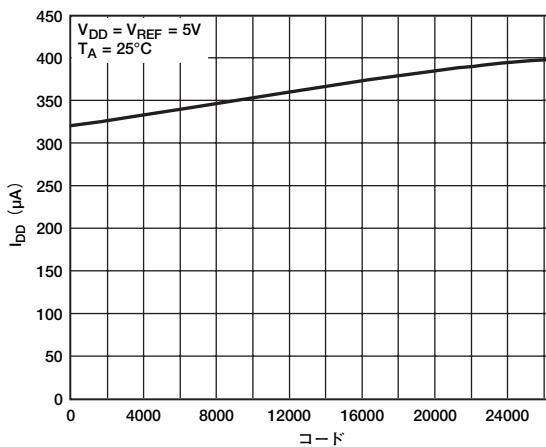

図10. コード対電源電流

05654-007

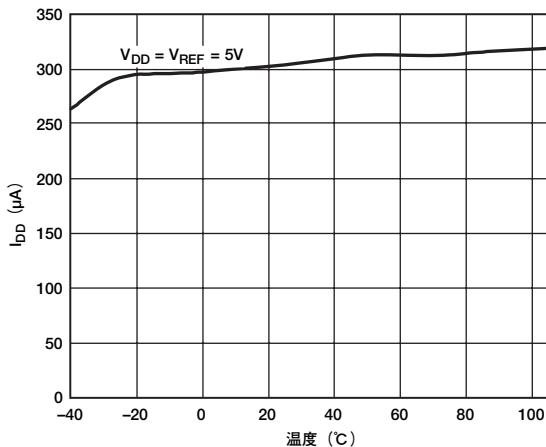

図11. 電源電流の温度特性

05654-006

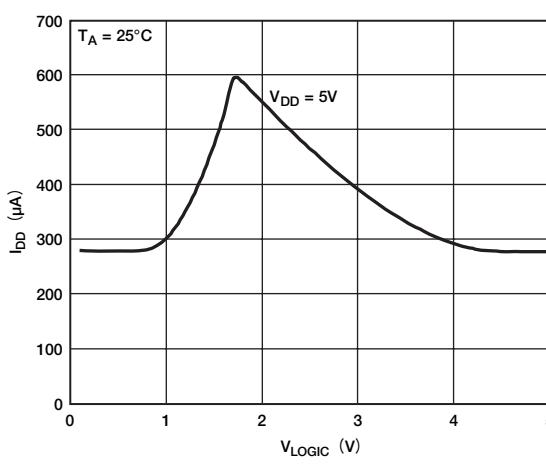

図12. ロジック入力電圧対電源電流

05654-004

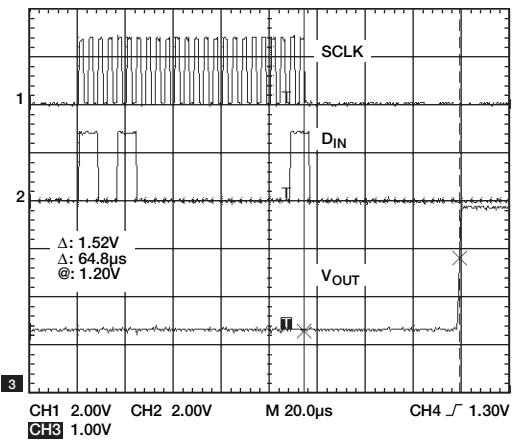

図13. フルスケールのセトリング時間 (5V)

05654-015

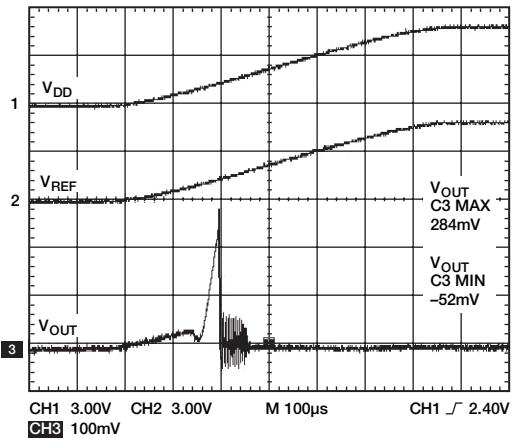

図14. パワーオン・リセット時の0V出力

05654-016

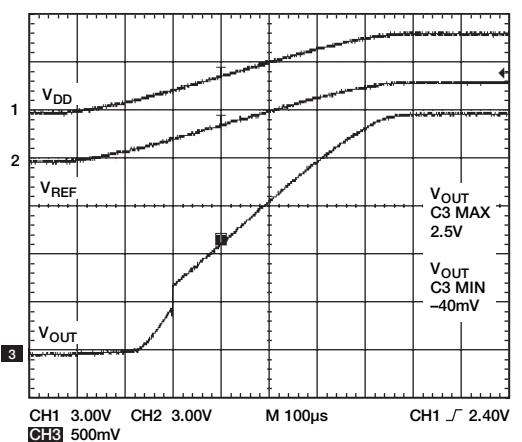

図15. パワーオン・リセット時のミッドスケール出力

05654-017

図16 デジタルからアナログへのグリッヂ・インパルス（負極性）

図17. デジタル・フィードスルー

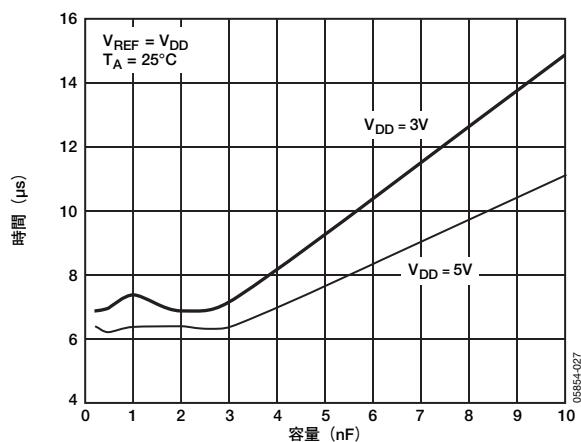

図19. 容量性負荷 対 セトリング時間

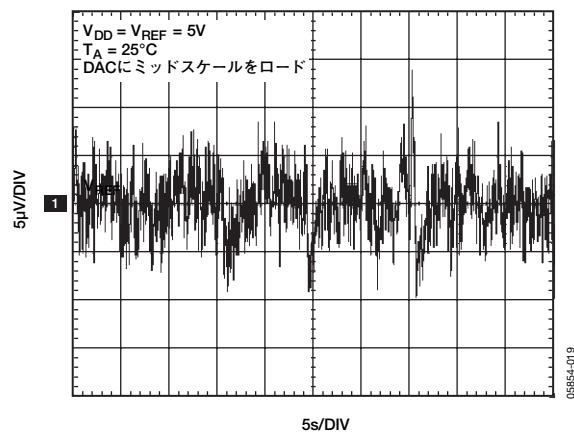

図20. 0.1~10Hzの出力ノイズ・プロット

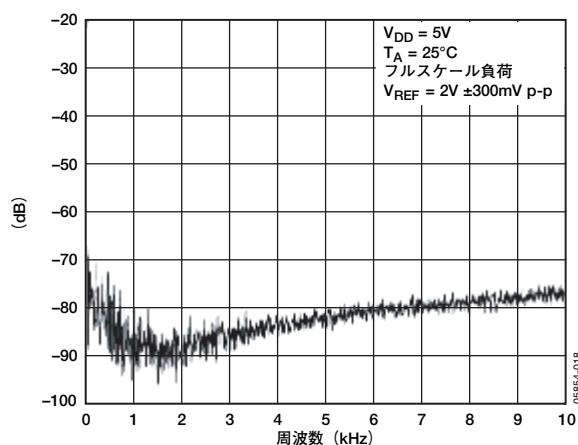

図18. 全高調波歪み

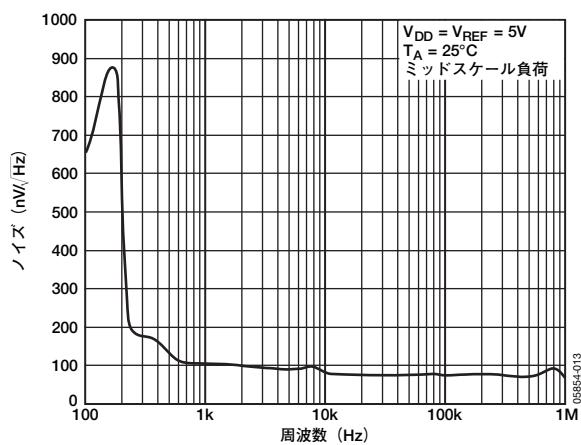

図21. ノイズ・スペクトル密度

## 用語の説明

### 相対精度または積分非直線性 (INL)

DACの場合、相対精度または積分非直線性とは、DAC伝達関数の2つのエンドポイントを結ぶ直線からの最大偏差（単位はLSB）を表します。代表的なコードとINLの関係を図4に示します。

### 微分非直線性 (DNL)

隣接する2つのコード間における1LSB変化の測定値と理論値の差です。微分非直線性の仕様が±1LSB以内の場合は、単調増加性が保証されています。代表的なコードとDNLの関係を図5に示します。

### ゼロコード誤差

ゼロコード（0x00000）をDACレジスタにロードしたときの出力誤差を表します。出力は理論上0Vになるはずです。AD5680ではDAC出力が0Vよりも低くなることはないため、ゼロコード誤差は常に正の値となります。この誤差は、DACのオフセット誤差と出力アンプのオフセット誤差が原因で発生します。ゼロコード誤差はmVの単位で表します。ゼロコード誤差の温度特性を図8に示します。

### フルスケール誤差

フルスケール・コード（0x3FFFF）をDACレジスタにロードしたときの出力誤差を表します。出力は理論上 $V_{DD}$ −1LSBになるはずです。フルスケール誤差は、フルスケール・レンジの%値で表します。

### ゲイン誤差

DACのスパン誤差を表します。これはDAC伝達特性の理論値からの実際の傾き偏差を示すもので、フルスケール・レンジの%値で表します。

### ゼロコード誤差ドリフト

温度変化にともなうゼロコード誤差の変化を表し、 $\mu\text{V}/^\circ\text{C}$ の単位で表します。

### ゲイン温度係数

温度変化にともなうゲイン誤差の変化を表し、（フルスケール・レンジのppm）/°Cの単位で表します。

### オフセット誤差

伝達関数の直線領域における $V_{OUT}$ （実際の出力電圧）と $V_{OUT}$ （理想的な出力電圧）との差をmVの単位で表します。AD5680のオフセット誤差は、コード2048をDACレジスタにロードして測定します。これは正または負の値となります。

### DC電源電圧除去比 (PSRR)

電源電圧の変動がDACの出力に与える影響を示します。PSRRは、DACのフルスケール出力に関する $V_{OUT}$ の変動と $V_{DD}$ の変動の比を表します。これはdBの単位で測定します。 $V_{REF}$ を2Vに保持し、 $V_{DD}$ を±10%のレンジで変動させます。

### 出力電圧セトリング時間

入力がフルスケールの1/4から3/4に変化するときに、DACの出力が規定のレベルにセトリングするまでの所要時間を表し、SCLKの24番目の立下がりエッジから測定します。

### デジタルからアナログへのグリッチ・インパルス

DACレジスタの入力コードが変化したときに、入力からアナログ出力に注入されるインパルスを表します。通常、グリッチの面積として規定され、nV·sで表します。メジャー・キャリーの遷移（0x1FFFFから0x20000）時に、デジタル入力コードが1LSB変化したときの測定値です。図16を参照。

### デジタル・フィードスルー

DAC出力の更新が行われていないときに、DACのデジタル入力からDACのアナログ出力に注入されるインパルスを表します。nV·sの単位で規定され、データ・バス上でのフルスケールのコード変化時、すなわち全ビット「0」から全ビット「1」に変化したとき、または全ビット「1」から全ビット「0」にコードが遷移するときに測定します。

### 全高調波歪み (THD)

DACを使用して減衰した正弦波と理論的な正弦波との偏差を表します。DACのリファレンスに正弦波を使用し、DACの出力上に存在する高調波成分を測定した値がTHDになります。dBの単位で測定します。

### ノイズ・スペクトル密度

内部で発生するランダム・ノイズの測定値です。ランダム・ノイズは、スペクトル密度（ $\sqrt{\text{Hz}}$ を基準とする電圧）として特性付けられます。この測定は、DACにミッドスケールをロードし、そのときに出力で発生するノイズを計測する方法によって行います。これはnV/ $\sqrt{\text{Hz}}$ の単位で測定します。ノイズ・スペクトル密度のプロットを図21に示します。

## 動作原理

### DAC部

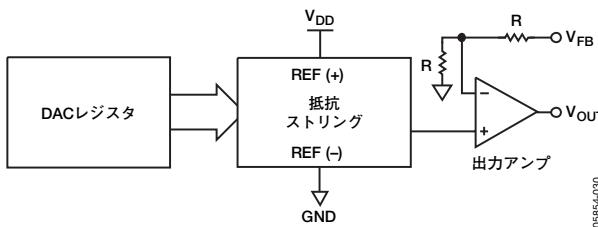

AD5680 DACは、CMOSプロセスを用いて製造されています。このアーキテクチャは、ストリングDACと後段の出力バッファ・アンプで構成されています。図22に、DACアーキテクチャのブロック図を示します。

図22. DACアーキテクチャ

DACの入力コーディングはストレート・バイナリであるため、理論的な出力電圧は次の式から求められます。

$$V_{OUT} = V_{REF} \times \left( \frac{D}{262,144} \right)$$

ここで、 $D$ はDACレジスタにロードされるバイナリ・コードの10進数値で、0~262,143の値になります。

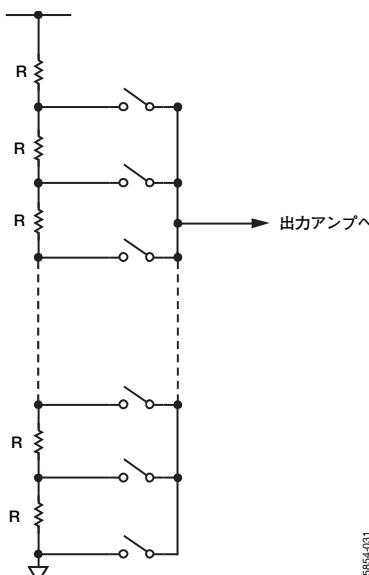

### 抵抗ストリング

図23に、抵抗ストリングの構造を示します。各値がRのシンプルな抵抗のストリングになっています。DACレジスタにロードされるコードにより、ストリング上のどのノードから出力アンプに電圧が供給されるかが決まります。ストリングとアンプを接続しているスイッチの1つを閉じることで、電圧が供給されます。抵抗のストリングであるため、単調増加性が保証されます。

図23. 抵抗ストリング

### 出力アンプ

出力バッファ・アンプによって、レールtoレールの電圧が出力で得られます。出力範囲は0V~V<sub>DD</sub>です。この出力バッファ・アンプには、帰還バスの50kΩ抵抗分圧ネットワークからゲイン2が設定されています。出力アンプの反転入力を利用できるため、リモート・センシングが可能です。通常の動作時は、このV<sub>FB</sub>ピンを必ずV<sub>OUT</sub>に接続してください。出力アンプは、GNDに接続された2kΩと、これに並列接続された1000pFの負荷を駆動できます。図9に、この出力アンプの電流ソースおよびシンク能力を示します。スルーレートは1.5V/μsで、セトリング時間は1/4フルスケールから3/4フルスケールへの変化に対して10μsです。

### インターポレータのアーキテクチャ

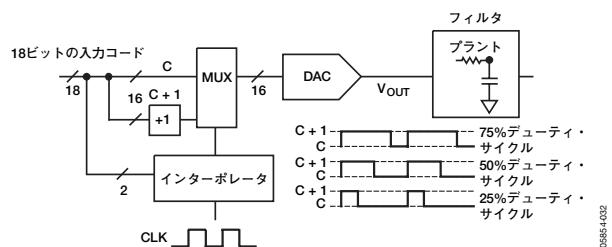

AD5680は、内部クロック発生器とインターポレータを備えた16ビットDACを内蔵しています。16ビット、1LSBステップで生成される電圧レベルは、インターポレータを用いて細分することで、分解能を18ビットまで増やすことができます。

18ビットの入力コードは、16ビットのDACコード (DB19~DB4) と2ビットのインターポレータ・コード (DB3とDB2) の2つに分けることができます。16ビット・コード (コード1023など) と16ビット・コード+1LSB (コード1024など) を切り替えて、DACに入力します。2ビットのインターポレータ・コードによって、スイッチングのデューティ・サイクル、したがって18ビットのコード・レベルが決まります。表5に例を示します。

表5

| 18ビット・コード | 16ビットのDACコード | 2ビットのインターポレータ・コード |     | デューティ・サイクル |

|-----------|--------------|-------------------|-----|------------|

|           |              | DB3               | DB2 |            |

| 4092      | 1023         | 0                 | 0   | 0          |

| 4093      | 1023         | 0                 | 1   | 25%        |

| 4094      | 1023         | 1                 | 0   | 50%        |

| 4095      | 1023         | 1                 | 1   | 75%        |

| 4096      | 1024         | 0                 | 0   | 0          |

DAC出力電圧は、16ビット・コード (C) と16ビット・コード+1 (C+1) の間の波形スイッチングの平均値から得られます。出力電圧は、スイッチングのデューティ・サイクルの関数です。

図24. インターポレーション・アーキテクチャ

## シリアル・インターフェース

AD5680は、SPI、QSPI、MICROWIREの各インターフェース規格、および大半のDSPと互換性をもつ3線式シリアル・インターフェース (SYNC、SCLK、DIN) を備えています。代表的な書込みシーケンスのタイミング図については、図2を参照してください。

SYNCラインをローレベルにすると、書込みシーケンスを開始します。DINラインからのデータは、SCLKの立下がりエッジで24ビットのシフト・レジスタに入力されます。シリアル・クロック周波数は最大30MHzまで対応しているため、デバイスは高速DSPと互換性があります。クロックの24番目の立下がりエッジで最後のデータビットが入力され、プログラミングされた機能を実行します (DACレジスタの内容の変更)。この時点で、SYNCラインをローレベルに保持するか、ハイレベルにすることができます。いずれの場合でも、次の書込みシーケンスの前に33ns以上SYNCラインをハイレベルに保持し、SYNCの立下がりエッジで次の書込みシーケンスが開始できるようになります。SYNCバッファを流れる電流は $V_{IN}=0.8V$ の場合より $V_{IN}=2V$ の場合の方が大きくなるため、さらにデバイスの消費電力を削減するには、書込みシーケンスが終了してから次の書込みシーケンスが始まるまでSYNCをアイドル・ローレベルに保持してください。ただし、前述のとおり次の書込みシーケンスの開始前にハイレベルに戻す必要があります。

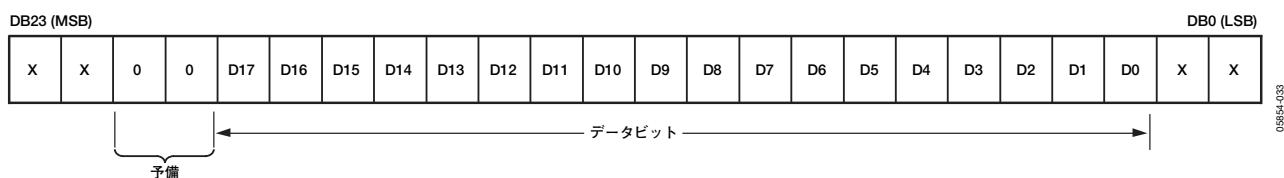

## 入力シフト・レジスタ

入力シフト・レジスタは24ビット幅です (図25を参照)。最初の2ビットは、ドント・ケア・ビットです。ビットDB21とDB20は予備で、0に設定します。次の18ビットはデータビットで、その後に2つのドント・ケア・ビットが続きます。これらはSCLKの24番目の立下がりエッジでDACレジスタに転送されます。

## SYNC割込み

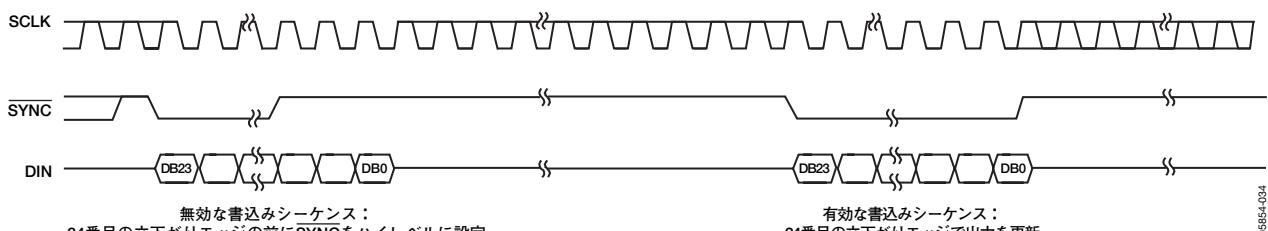

通常の書込みシーケンスでは、SCLKの少なくとも24個の立下がりエッジの間、SYNCラインがローレベルに保持され、24番目の立下がりエッジでDACが更新されます。ただし、24番目の立下がりエッジの前にSYNCをハイレベルに設定すると、SYNCは書込みシーケンスへの割込み信号として機能します。このときにシフト・レジスタがリセットされ、書込みシーケンスは無効と判断されます。DACレジスタのデータ内容は更新されず、また動作モードも変更されません (図26を参照)。

## パワーオン・リセット

AD5680ファミリーには、パワーアップ時の出力電圧を制御するパワーオン・リセット回路が内蔵されています。AD5680-1のDAC出力はパワーアップ時に0V、AD5680-2ではミッドスケール電圧にリセットされます。この出力状態は、DACに有効な書込みシーケンスが行われるまでそのまま保持されます。この機能は、デバイスのパワーアップ時にDACの出力状態を把握しておくことが重要なアプリケーションで特に便利です。

図25. 入力レジスタの内容

図26. SYNC割込み機能

## マイクロプロセッサとのインターフェース

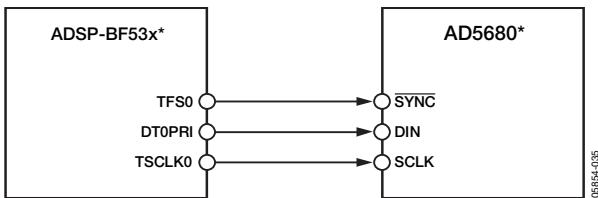

### AD5680とBlackfin® ADSP-BF53xとのインターフェース

図27に、AD5680とBlackfin ADSP-BF53xマイクロプロセッサとのシリアル・インターフェースを示します。ADSP-BF53Xファミリーのプロセッサには、シリアル通信とマルチプロセッサ通信用に2つのデュアル・チャンネル同期シリアル・ポート(SPORT1とSPORT0)が内蔵されています。SPORT0を用いたAD5680との接続では、次のようにインターフェースがセットアップされます。DT0PRIがAD5680のDINピンを駆動し、TSCLK0がAD5680のSCLKを駆動します。SYNCはTFS0から駆動されます。

\*わかりやすくするために、他のピンは省略しています。

図27. AD5680とBlackfin ADSP-BF53xとのインターフェース

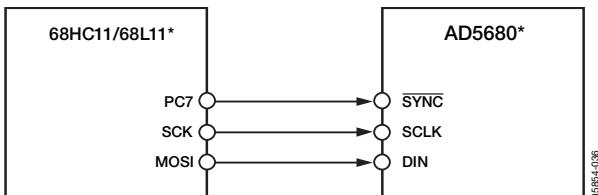

### AD5680と68HC11/68L11とのインターフェース

図28に、AD5680と68HC11/68L11マイクロコントローラとのシリアル・インターフェースを示します。68HC11/68L11のSCKではAD5680のSCLKピンを駆動しますが、MOSI出力ではDACのシリアル・データ・ラインを駆動します。

SYNC信号は、ポート・ライン(PC7)から生成されます。このインターフェースを正常に動作させるには、68HC11/68L11でCPOLビット=0、かつCPHAビット=1となるように設定してください。データがDACに転送されているときは、SYNCラインがローレベルになります(PC7)。68HC11/68L11が上記のように設定された場合は、MOSIに出力されるデータはSCKの立下がりエッジで有効になります。シリアル・データは68HC11/68L11から8ビットのバイトで転送され、送信サイクル内には立下がりクロック・エッジが8個しかありません。データはMSBファーストで転送されます。データをAD5680にロードするときは、最初の8ビットが転送された後もPC7をローレベルのままにして、DACに対して2番目のシリアル書込み動作を実行します。この手順の終わりに、PC7をハイレベルにします。

\*わかりやすくするために、他のピンは省略しています。

図28. AD5680と68HC11/68L11とのインターフェース

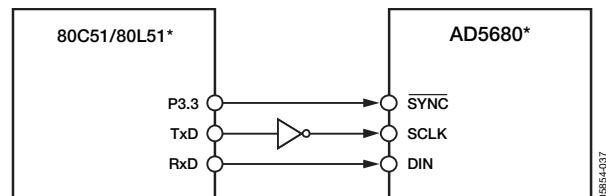

### AD5680と80C51/80L51とのインターフェース

図29に、AD5680と80C51/80L51マイクロコントローラとのシリアル・インターフェースを示します。このインターフェースのセットアップでは、80C51/80L51のTx DがAD5680のSCLKを駆動し、Rx DがAD5680のシリアル・データ・ラインを駆動します。SYNC信号はこの場合も、ポートのビット・プログラマブルなピンから生成されます。この場合はポート・ラインP3.3を使用します。データがAD5680に転送されるとき、P3.3はローレベルになります。データは80C51/80L51から8ビットのバイトで転送されるため、送信サイクル内には立下がりクロック・エッジが8個しかありません。データをDACにロードするときは、最初の8ビットが転送された後もP3.3をローレベルのままにして2番目の書込みサイクルを実行すると、データの2番目のバイトの転送が開始されます。このサイクルの完了後にP3.3をハイレベルにします。80C51/80L51はシリアル・データをLSBファーストで出力しますが、AD5680はMSBファーストでデータを受け取る必要があります。80C51/80L51の送信ルーチンは、これを考慮に入れてください。

\*わかりやすくするために、他のピンは省略しています。

図29. AD5680と80C51/80L51とのインターフェース

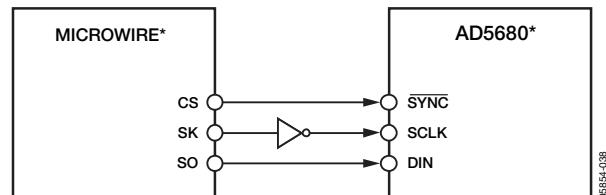

### AD5680とMICROWIREとのインターフェース

図30に、AD5680とMICROWIRE互換デバイスとのインターフェースを示します。シリアル・データは、シリアル・クロックの立下がりエッジでシフト・アウトされ、SKの立上がりエッジでAD5680に入力されます。

\*わかりやすくするために、他のピンは省略しています。

図30. AD5680とMICROWIREとのインターフェース

# AD5680

## アプリケーション

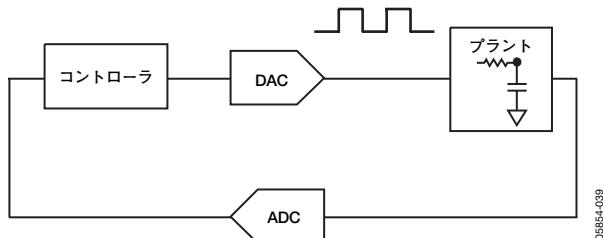

### クローズドループ・アプリケーション

AD5680は、クローズドループの低帯域幅アプリケーションに適しています。理論上、システム帯域幅がDAC出力に対するフィルタの機能を果たします。(DAC出力のプレフィルタリングとポストフィルタリングの詳細については、「フィルタ」を参照してください。) DACは、10kHzのインターポレーション周波数で更新します。

図31. 代表的なクローズドループ・アプリケーション

### フィルタ

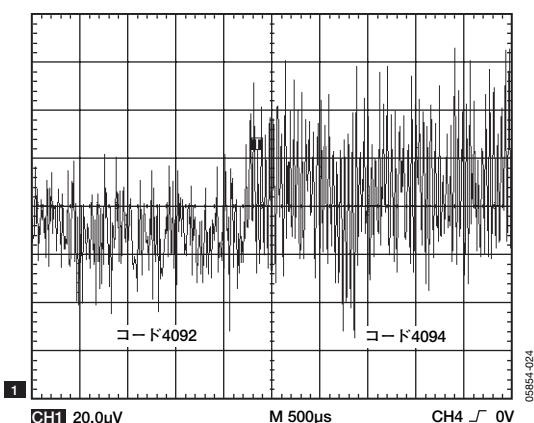

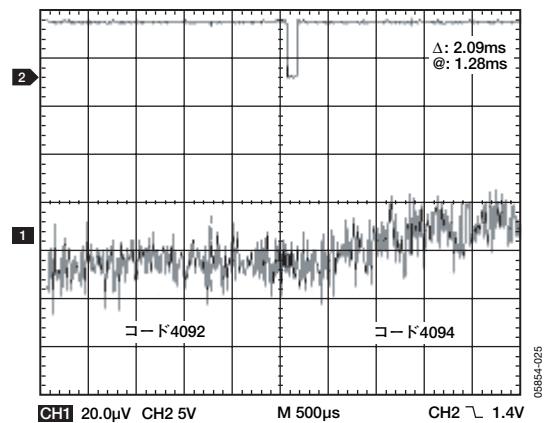

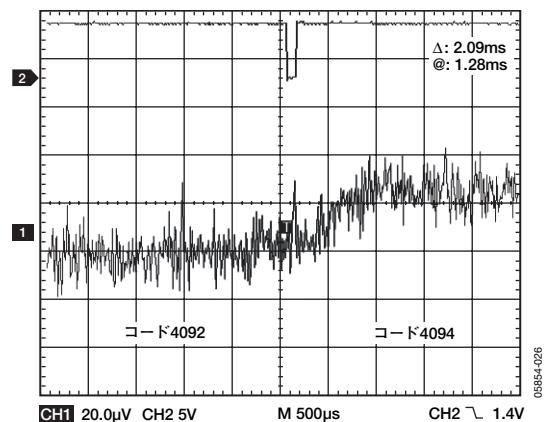

図32に、4092から4094へのコード遷移に対するDAC出力電圧を示します。これは、フィルタ処理をしていないDAC出力です。コード4092にはインターポレーションがありませんが、コード4094には50%デューティサイクルによるインターポレーションがあります(表5を参照)。図33に、50Hzの受動RCフィルタを備えたDAC出力を示します。図34は、300Hzの受動RCフィルタを備えた出力です。320kΩと10nFのRC結合を使用して50Hzのカットオフ周波数が得られ、81kΩと10nFのRC結合によって300Hzのカットオフ周波数が得られます。

図32. フィルタ処理なしのDAC出力

図33. 出力に50Hzのフィルタを使用したDAC出力

図34. 出力に300Hzのフィルタを使用したDAC出力

## AD5680のリファレンスの選択

AD5680から最適な性能を得るには、高精度な電圧リファレンスを注意して選ぶ必要があります。AD5680のリファレンス入力は $V_{REF}$ のみです。このリファレンス入力の電圧を、DACの供給電圧として使用します。したがって、リファレンスに少しでも誤差があると、DACにも影響が出ます。

高精度アプリケーション向けの電圧リファレンスの選択に際しては、誤差源となる初期精度、ppmドリフト、長期ドリフト、出力電圧ノイズを考慮します。DACの出力電圧の初期精度は、DACのフルスケール誤差を発生させる要因となるため、これらの誤差を最小限に抑えるには初期精度の高いリファレンスを選んでください。また、ADR425などの出力調整機能付きのリファレンスを選択すれば、リファレンス電圧をその公称値以外の電圧に設定してシステム誤差を抑えられます。この調整機能を動作温度環境で使用すれば、温度ドリフトなどの誤差も抑えられます。

表6. AD5680用高精度リファレンスのリスト（一部）

| 製品番号   | 初期精度 (mV max) | 温度ドリフト (ppm/°C max) | 0.1~10Hzノイズ (μV p-p typ) | $V_{OUT}$ (V) |

|--------|---------------|---------------------|--------------------------|---------------|

| ADR425 | ±2            | 3                   | 3.4                      | 5             |

| ADR395 | ±6            | 25                  | 5                        | 5             |

| REF195 | ±2            | 5                   | 50                       | 5             |

長期ドリフトは、リファレンスの経時変化を測定した値です。精度の高い長期ドリフト仕様を備えたリファレンスは、製品寿命を通じて比較的安定した状態に精度が維持されています。

リファレンスの出力電圧の温度係数は、INL、DNL、TUEに影響を及ぼします。周開条件に対するDAC出力電圧の温度依存性を低く抑えるために、精度の高い温度係数仕様を備えたリファレンスを選択してください。

比較的低いノイズが求められる高精度のアプリケーションでは、リファレンスの出力電圧ノイズを考慮に入れる必要があります。要求されるシステム・ノイズ分解能に対して、可能な限り出力ノイズ電圧が低いリファレンスを選択することが重要です。ADR425などの高精度電圧リファレンスは、0.1~10Hzの範囲で出力ノイズが低く抑えられています。表6に、AD5680の電源電圧に推奨する高精度リファレンスの例を示します。

# AD5680

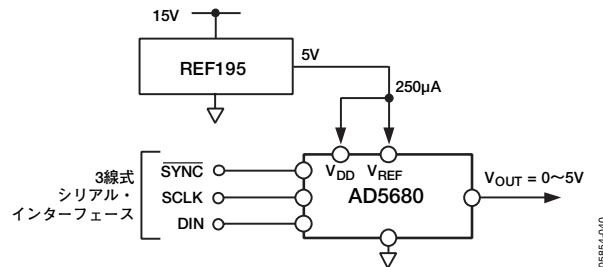

## リファレンスをAD5680の電源として使用する方法

AD5680は、必要とする電源電流が非常に小さいため、電圧リファレンスを使用してAD5680に必要な電圧を供給することもできます（図35を参照）。電源ノイズが非常に大きい場合や、システムの電源電圧が15Vなど、5V以外の電圧値の場合は、この方法が特に効果的です。電圧リファレンスは、AD5680に定常の電源電圧を出力します。適切な電圧リファレンスについては、表6を参照してください。低ドロップアウト電圧のREF195を使用する場合は、DACの出力に負荷を接続していない状態でAD5680に325 $\mu$ Aの電流を供給する必要があります。DAC出力に負荷を接続している場合も、REF195から負荷に電流を供給する必要があります。必要な電流の合計値（DAC出力に5k $\Omega$ の負荷を接続している場合）は、次のようになります。

$$325\mu\text{A} + (5\text{V}/5\text{k}\Omega) = 1.33\text{mA}$$

通常、REF195の負荷レギュレーションは2ppm/mAであるため、REF195から1.33mAの電流を供給すると2.7ppm（13.5 $\mu$ V）誤差が生じます。これは、0.177LSBの誤差に相当します。

図35. REF195をAD5680の電源として使用した場合

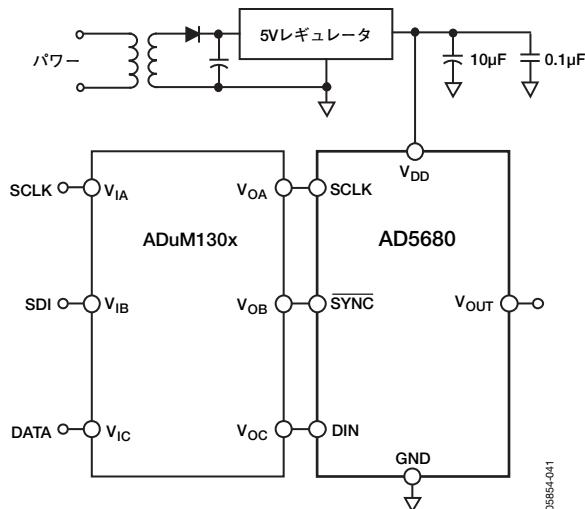

## デジタル・アイソレータ（iCoupler）を用いた絶縁インターフェース

工業環境のプロセス制御アプリケーションでは、絶縁インターフェースが必要になることがあります。それは、DACが動作している環境下で望ましくない同相電圧から制御回路を保護したり、絶縁したりする必要があるからです。iCoupler®は、3kVを超える絶縁が可能です。AD5680は3線式のシリアル・ロジック・インターフェースを使用しているため、3チャンネルのデジタル・アイソレータ「ADuM130x」で必要な絶縁を行うことができます（図36を参照）。デバイスの電源もトランクを使用して絶縁してください。トランクのDAC側では、5VのレギュレータがAD5680に必要な5V電源を供給します。

図36. デジタル・アイソレータを用いた絶縁インターフェース

## 電源のバイパスとグラウンド・リターン

精度が重視される回路では、ボード上の電源とグラウンド・リターンのレイアウトに注意してください。AD5680を実装するプリント回路ボードは、アナログ部とデジタル部を分離し、ボード内でそれぞれまとめて配置するように設計してください。複数のデバイスがAGNDとDGND間の接続を必要とするシステムでAD5680を使用する場合は、必ず1ヶ所のみでの接続を行ってください。グラウンド・ポイントはAD5680のできるかぎり近くに配置してください。

AD5680の電源は、10 $\mu$ Fと0.1 $\mu$ Fのコンデンサを使用してバイパスします。コンデンサはデバイスのできるだけ近くに配置し、0.1 $\mu$ Fのコンデンサは理想的にはデバイスの真上に配置してください。10 $\mu$ Fのコンデンサはタンタルのビード型を使います。0.1 $\mu$ Fのコンデンサは、セラミック型の等価直列抵抗（ESR）が小さく、かつ等価直列インダクタンス（ESL）が小さいものを使うことが重要です。この0.1 $\mu$ Fのコンデンサは、内部ロジックのスイッチングによる過渡電流によって発生する高周波に対して、グラウンドへの低インピーダンス・パスを提供します。

電源ラインはできるだけ太いパターンにしてインピーダンスを小さくし、電源ライン上のグリッチによる影響を低減させます。クロックとその他の高速スイッチング・デジタル信号は、デジタル・グラウンドを用いてボード上の他の部分からシールドします。デジタル信号とアナログ信号は、できるだけ交差しないようにしてください。ボードの反対側のパターンは、互いに直角になるように配置し、ボードを通過するフィードスルーの影響を削減します。最適なボード・レイアウト技術は、ボードの部品側をグラウンド・プレーン専用として使い、信号パターンをハンダ面に配置するマイクロストリップ技術ですが、2層ボードでは必ずしも使用できるとは限りません。

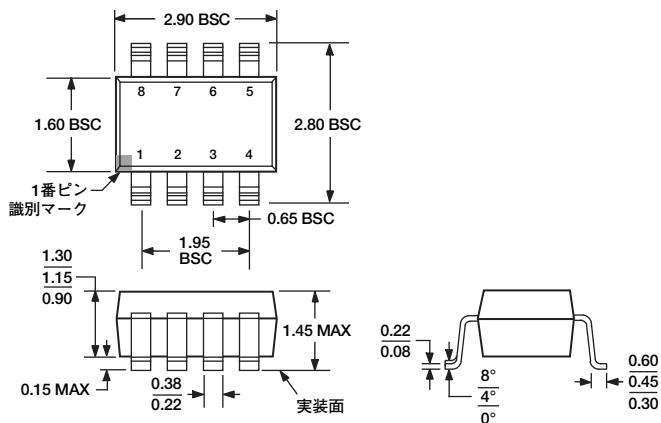

## 外形寸法

JEDEC規格MO-178-BAに準拠

図37. 8ピン・スモール・アウトライン・トランジスタ・パッケージ [SOT-23]

(RJ-8)

寸法単位: mm

## オーダー・ガイド

| モデル                             | 温度範囲       | パッケージ      | パッケージ・オプション | パワーオン・リセットのコード | 精度          | マーキング |

|---------------------------------|------------|------------|-------------|----------------|-------------|-------|

| AD5680BRJZ-1500RL7 <sup>1</sup> | -40~+105°C | 8ピン SOT-23 | RJ-8        | ゼロ             | ±64 LSB INL | D3C   |

| AD5680BRJZ-1REEL7 <sup>1</sup>  | -40~+105°C | 8ピン SOT-23 | RJ-8        | ゼロ             | ±64 LSB INL | D3C   |

| AD5680BRJZ-2500RL7 <sup>1</sup> | -40~+105°C | 8ピン SOT-23 | RJ-8        | ミッドスケール        | ±64 LSB INL | D3D   |

| AD5680BRJZ-2REEL7 <sup>1</sup>  | -40~+105°C | 8ピン SOT-23 | RJ-8        | ミッドスケール        | ±64 LSB INL | D3D   |

| EVAL-AD5680EB                   |            | 評価用ボード     |             |                |             |       |

<sup>1</sup> Z=RoHS準拠製品