## AD5346/AD5347/AD5348

### 特長

AD5346：オクタル8ビットDAC

AD5347：オクタル10ビットDAC

AD5348：オクタル12ビットDAC

低消費電力動作：3.6Vで1.4mA (max)

3Vで120nA、5Vで400nAまでパワーダウン

全コードについて設計により単調性を保証

レールtoレール出力レンジ：0V~ $V_{REF}$ または0V~ $2 \times V_{REF}$

0Vへのパワーオン・リセット

LDACピンによるDAC出力の同時更新

非同期CLR機能

リードバック

バッファ付き／バッファなしのリファレンス入力

WR時間：20ns

38ピンTSSOP/6mm×6mm 40ピンLFCSPパッケージ

温度範囲：-40~+105°C

### アプリケーション

バッテリ駆動の携帯型計測機器

ゲインとオフセットのデジタル調整

プログラマブルな電圧／電流源

光ネットワーキング

自動テスト機器

移動体通信

プログラマブル減衰器

工業用プロセス制御

### 概要

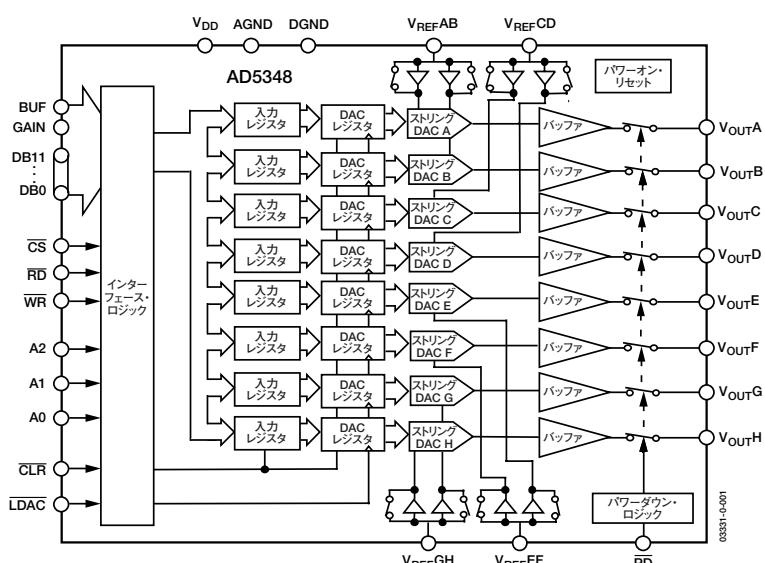

AD5346/AD5347/AD5348<sup>1</sup>は、2.5~5.5V電源で動作するオクタル8/10/12ビットDACです。2つの電源レールに出力を駆動できるオンチップ出力バッファを備え、バッファ付きまたはバッファなしのリファレンス入力を選択できます。

AD5346/AD5347/AD5348にはパラレル・インターフェースがあります。CSでデバイスを選択し、WRの立ち上がりエッジで入力レジスタにデータをロードします。リードバック機能によって、デジタル・ポートを通じて内部DACレジスタからの読み出しができます。

デバイスのGAINピンを使用すれば、出力レンジを0V~ $V_{REF}$ または0V~ $2 \times V_{REF}$ に設定できます。

DACへの入力データをダブル・バッファし、LDACピンを使用してシステム内の複数のDACを同時に更新することができます。

非同期CLR入力もあり、入力レジスタとDACレジスタの内容をオール0にリセットします。内蔵のパワーオン・リセット回路によって、DAC出力を0Vにパワーオンし、デバイスに有効なデータが書き込まれるまでそのままに保持します。

この3つのデバイスはすべてピン互換であり、ユーザーは回路ボードのデザインを変更することなく、アプリケーションに適した分解能を選択することができます。

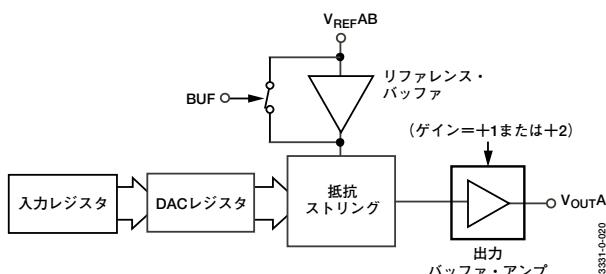

### 機能ブロック図

図1.

<sup>1</sup> 米国特許No. 5,969,657により保護されています。その他の特許は申請中です。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。本紙記載の商標および登録商標は、各社の所有に属します。

※日本語データシートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

© 2003 Analog Devices, Inc. All rights reserved.

# AD5346/AD5347/AD5348

## 目次

---

|                     |    |                                  |    |

|---------------------|----|----------------------------------|----|

| 仕様                  | 3  | パワーオン・リセット                       | 17 |

| AC特性                | 4  | パワーダウン・モード                       | 17 |

| タイミング特性             | 5  | 推奨データ・バス・フォーマット                  | 18 |

| 絶対最大定格              | 6  | アプリケーション情報                       | 19 |

| ESDに関する注意           | 6  | 代表的なアプリケーション回路                   | 19 |

| AD5346のピン配置および機能の説明 | 7  | リファレンス電圧からのV <sub>DD</sub> の駆動   | 19 |

| AD5347のピン配置および機能の説明 | 8  | AD5346/AD5347/AD5348を使用するバイポーラ動作 | 19 |

| AD5348のピン配置および機能の説明 | 9  | 複数のAD5346/AD5347/AD5348のデコーディング  | 20 |

| 用語集                 | 10 | デジタル設定可能なウインドウ検出器としての            |    |

| 代表的な性能特性            | 12 | AD5346/AD5347/AD5348             | 20 |

| 機能の説明               | 16 | プログラマブルな電流源                      | 20 |

| デジタル／アナログ変換部        | 16 | AD5346/AD5347/AD5348を使用する粗調整と微調整 | 21 |

| 抵抗ストリング             | 16 | 電源のバイパスとグラウンディング                 | 21 |

| DACリファレンス入力         | 16 | 外形寸法                             | 23 |

| 出力アンプ               | 16 | オーダー・ガイド                         | 24 |

| パラレル・インターフェース       | 17 |                                  |    |

## 改訂履歴

リビジョン0：初版

## 仕様

表1. 特に指定のない限り、 $V_{DD}=2.5\sim5.5V$ 、 $V_{REF}=2V$ 、 $R_L=2k\Omega\sim GND$ 、 $C_L=200pF\sim GND$ 、すべての仕様は $T_{MIN}\sim T_{MAX}$

| パラメータ <sup>2</sup>       | Min            | Typ        | Max     | 単位          | 条件／備考                                                                        |

|--------------------------|----------------|------------|---------|-------------|------------------------------------------------------------------------------|

| DC性能 <sup>3、4</sup>      |                |            |         |             |                                                                              |

| AD5346                   |                |            |         |             |                                                                              |

| 分解能                      | 8              |            |         | ビット         |                                                                              |

| 相対精度                     | $\pm 0.15$     | $\pm 1$    |         | LSB         |                                                                              |

| 微分非直線性                   | $\pm 0.02$     | $\pm 0.25$ |         | LSB         | 全コードについて設計によって単調性を保証                                                         |

| AD5347                   |                |            |         |             |                                                                              |

| 分解能                      | 10             |            |         | ビット         |                                                                              |

| 相対精度                     | $\pm 0.5$      | $\pm 4$    |         | LSB         |                                                                              |

| 微分非直線性                   | $\pm 0.05$     | $\pm 0.5$  |         | LSB         | 全コードについて設計によって単調性を保証                                                         |

| AD5348                   |                |            |         |             |                                                                              |

| 分解能                      | 12             |            |         | ビット         |                                                                              |

| 相対精度                     | $\pm 2$        | $\pm 16$   |         | LSB         |                                                                              |

| 微分非直線性                   | $\pm 0.2$      | $\pm 1$    |         | LSB         | 全コードについて設計によって単調性を保証                                                         |

| オフセット誤差                  | $\pm 0.4$      | $\pm 3$    |         | FSRの%       |                                                                              |

| ゲイン誤差                    | $\pm 0.1$      | $\pm 1$    |         | FSRの%       |                                                                              |

| 下側デッドバンド <sup>5</sup>    | 10             | 60         |         | mV          | オフセット誤差が負のときのみ、下側デッドバンドが存在                                                   |

| 上側デッドバンド <sup>5</sup>    | 10             | 60         |         | mV          | $V_{DD}=5V$ 。 $V_{REF}=V_{DD}$ のときのみ、上側デッドバンドが存在                             |

| オフセット誤差ドリフト <sup>6</sup> | -12            |            |         | FSRのppm /°C |                                                                              |

| ゲイン誤差ドリフト <sup>6</sup>   | -5             |            |         | FSRのppm /°C |                                                                              |

| DC電源除去比 <sup>6</sup>     | -60            |            |         | dB          | $\Delta V_{DD}=\pm 10\%$                                                     |

| DCクロストーク <sup>6</sup>    | 200            |            |         | μV          | $R_L=2k\Omega\sim GND$ 、 $2k\Omega\sim V_{DD}$ 、 $C_L=200pF\sim GND$ 、ゲイン=+1 |

| DACリファレンス入力 <sup>6</sup> |                |            |         |             |                                                                              |

| $V_{REF}$ 入力レンジ          | 1              |            |         | V           | バッファ・リファレンス・モード                                                              |

| $V_{REF}$ 入力レンジ          | 0.25           |            |         | V           | 非バッファ・リファレンス・モード                                                             |

| $V_{REF}$ 入力インピーダンス      |                | >10        |         | MΩ          | バッファ・リファレンス・モードとパワーダウン・モード                                                   |

|                          |                |            |         |             | ゲイン=+1、入力インピーダンス= $R_{DAC}$                                                  |

|                          |                |            |         |             | ゲイン=+2、入力インピーダンス= $R_{DAC}$                                                  |

| リファレンス・フィードスルー           |                |            |         |             | 周波数=10kHz                                                                    |

| チャンネル間絶縁                 |                |            |         |             | 周波数=10kHz                                                                    |

| 出力特性 <sup>6</sup>        |                |            |         |             |                                                                              |

| 最小出力電圧 <sup>4、7</sup>    | 0.001          |            |         | V (min)     | レールtoレール動作                                                                   |

| 最大出力電圧 <sup>4、7</sup>    | $V_{DD}-0.001$ |            |         | V (max)     |                                                                              |

| DC出力インピーダンス              | 0.5            |            |         | Ω           |                                                                              |

| 短絡電流                     | 25             |            |         | mA          | $V_{DD}=5V$                                                                  |

|                          | 16             |            |         | mA          | $V_{DD}=3V$                                                                  |

| パワーアップ時間                 | 2.5            |            |         | μs          | パワーダウン・モードからの復帰、 $V_{DD}=5V$                                                 |

|                          | 5              |            |         | μs          | パワーダウン・モードからの復帰、 $V_{DD}=3V$                                                 |

| ロジック入力                   |                |            |         |             |                                                                              |

| 入力電流                     |                |            | $\pm 1$ | μA          |                                                                              |

| $V_{IL}$ 、ローレベル入力電圧      |                |            | 0.8     | V           | $V_{DD}=5V\pm 10\%$                                                          |

|                          |                |            | 0.7     | V           | $V_{DD}=3V\pm 10\%$                                                          |

|                          |                |            | 0.6     | V           | $V_{DD}=2.5V$                                                                |

| $V_{IH}$ 、ハイレベル入力電圧      | 1.7            |            |         | V           | $V_{DD}=2.5\sim 5.5V$                                                        |

| ピン容量                     |                |            | 5       | pF          |                                                                              |

# AD5346/AD5347/AD5348

| パラメータ <sup>2</sup>                                                                         | Bバージョン <sup>1</sup> |             |                    | 単位                                                                                                                                 | 条件／備考 |

|--------------------------------------------------------------------------------------------|---------------------|-------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|

|                                                                                            | Min                 | Typ         | Max                |                                                                                                                                    |       |

| ロジック出力 <sup>6</sup><br>$V_{DD}=4.5\sim 5.5V$<br>ローレベル出力電圧、 $V_{OL}$<br>ハイレベル出力電圧、 $V_{OH}$ | $V_{DD}-1$          | 0.4         | V                  | $I_{SINK}=200\mu A$<br>$I_{SOURCE}=200\mu A$                                                                                       |       |

| $V_{DD}=2.5\sim 3.6V$<br>ローレベル出力電圧、 $V_{OL}$<br>ハイレベル出力電圧、 $V_{OH}$                        | $V_{DD}-0.5$        | 0.4         | V                  | $I_{SINK}=200\mu A$<br>$I_{SOURCE}=200\mu A$                                                                                       |       |

| 電源要求<br>$V_{DD}$<br>$I_{DD}$ (ノーマル・モード)<br>$V_{DD}=4.5\sim 5.5V$<br>$V_{DD}=2.5\sim 3.6V$  | 2.5                 | 5.5         | V                  | $V_{IH}=V_{DD}$ 、 $V_{IL}=GND$                                                                                                     |       |

| $I_{DD}$ (パワーダウン・モード)<br>$V_{DD}=4.5\sim 5.5V$<br>$V_{DD}=2.5\sim 3.6V$                    | 1<br>0.8            | 1.65<br>1.4 | mA<br>mA           | すべてのDACは非バッファ・モード。<br>バッファ・モードでは、増加する電流の代表値<br>はDACあたり $x\mu A$ ( $x=5\mu A + V_{REF}/R_{DAC}$ )<br>$V_{IH}=V_{DD}$ 、 $V_{IL}=GND$ |       |

|                                                                                            | 0.4<br>0.12         | 1<br>1      | $\mu A$<br>$\mu A$ |                                                                                                                                    |       |

AC特性の表の下に記載した脚注を参照してください。

## AC特性<sup>6</sup>

表2. 特に指定のない限り、 $V_{DD}=2.5\sim 5.5V$ 、 $R_L=2k\Omega\sim GND$ 、 $C_L=200pF\sim GND$ 、すべての仕様は $T_{MIN}\sim T_{MAX}$

| パラメータ <sup>2</sup>                          | Bバージョン <sup>1</sup> |              |             | 単位           | 条件／備考                                            |

|---------------------------------------------|---------------------|--------------|-------------|--------------|--------------------------------------------------|

|                                             | Min                 | Typ          | Max         |              |                                                  |

| 出力電圧セトリング・タイム<br>AD5346<br>AD5347<br>AD5348 | 6<br>7<br>8         | 8<br>9<br>10 | $\mu s$     | $V_{REF}=2V$ | 1/4スケールから3/4スケールへの変化 (40HからC0H)                  |

| スルーレート                                      | 0.7                 |              | $V/\mu s$   |              | 1/4スケールから3/4スケールへの変化 (100Hから300H)                |

| メジャー・コード遷移グリッチ・エネルギー                        | 8                   |              | $nV\cdot s$ |              | メジャー・キャリーを中心にして1LSBの変化                           |

| デジタル・フィードスルー                                | 0.5                 |              | $nV\cdot s$ |              |                                                  |

| デジタル・クロストーク                                 | 1                   |              | $nV\cdot s$ |              |                                                  |

| アナログ・クロストーク                                 | 1                   |              | $nV\cdot s$ |              |                                                  |

| DAC間クロストーク                                  | 3.5                 |              | $nV\cdot s$ |              |                                                  |

| 乗算帯域幅                                       | 200                 |              | $kHz$       |              | $V_{REF}=2V\pm 0.1V$ p-p、非バッファ・モード               |

| 全高調波歪み                                      | -70                 |              | $dB$        |              | $V_{REF}=2V\pm 0.1V$ p-p、周波数=10kHz、<br>非バッファ・モード |

<sup>1</sup> 温度範囲：Bバージョン：-40~+105°C。仕様のtyp値は25°C。

<sup>2</sup> 用語集を参照してください。

<sup>3</sup> 直線性はコード範囲を狭めてテスト：AD5346 (コード8~255)、AD5347 (コード28~1023)、AD5348 (コード115~4095)

<sup>4</sup> DC仕様は出力無負荷でテスト。

<sup>5</sup> これはxコードに対応します。x=デッドバンド電圧/LSBサイズ

<sup>6</sup> 設計と特性により保証しており、出荷テストは実施していません。

<sup>7</sup> アンプ出力を最小電圧にするには、負のオフセット誤差が必要です。アンプ出力を最大電圧にするには、 $V_{REF}=V_{DD}$ で、オフセットとゲイン誤差の合計が正になる必要があります。

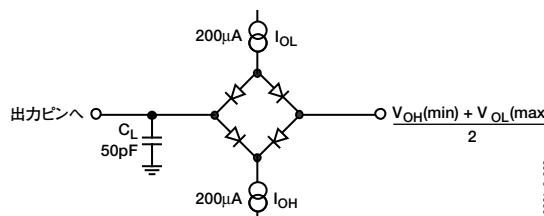

0335-0-002

図2. デジタル出力タイミング仕様のための負荷回路

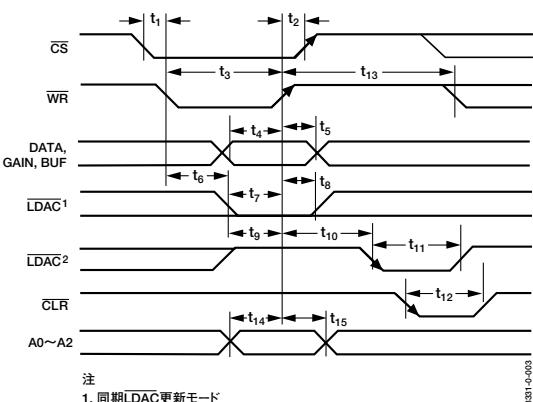

## タイミング特性<sup>1, 2, 3</sup>

表3. 特に指定のない限り、 $V_{DD}=2.5\sim5.5V$ 、すべての仕様は $T_{MIN}\sim T_{MAX}$

| パラメータ               | $T_{MIN}, T_{MAX}$ における限界 | 単位       | 条件／備考                                            |

|---------------------|---------------------------|----------|--------------------------------------------------|

| データ書き込みモード (図3)     |                           |          |                                                  |

| $t_1$               | 0                         | ns (min) | $\overline{CS}\sim\overline{WR}$ のセットアップ・タイム     |

| $t_2$               | 0                         | ns (min) | $\overline{CS}\sim\overline{WR}$ のホールド・タイム       |

| $t_3$               | 20                        | ns (min) | $WR$ パルス幅                                        |

| $t_4$               | 5                         | ns (min) | データ、GAIN、BUFのセットアップ・タイム                          |

| $t_5$               | 4.5                       | ns (min) | データ、GAIN、BUFのホールド・タイム                            |

| $t_6$               | 5                         | ns (min) | 同期モード。 $WR$ 立ち下がり～ $LDAC$ 立ち下がり                  |

| $t_7$               | 5                         | ns (min) | 同期モード。 $LDAC$ 立ち下がり～ $\overline{WR}$ 立ち上がり       |

| $t_8$               | 4.5                       | ns (min) | 同期モード。 $WR$ 立ち上がり～ $LDAC$ 立ち上がり                  |

| $t_9$               | 5                         | ns (min) | 非同期モード。 $LDAC$ 立ち上がり～ $\overline{WR}$ 立ち上がり      |

| $t_{10}$            | 4.5                       | ns (min) | 非同期モード。 $WR$ 立ち上がり～ $LDAC$ 立ち下がり                 |

| $t_{11}$            | 20                        | ns (min) | $LDAC$ パルス幅                                      |

| $t_{12}$            | 10                        | ns (min) | $CLR$ パルス幅                                       |

| $t_{13}$            | 20                        | ns (min) | $WR$ サイクル間の時間                                    |

| $t_{14}$            | 20                        | ns (min) | A0、A1、A2セットアップ・タイム                               |

| $t_{15}$            | 0                         | ns (min) | A0、A1、A2ホールド・タイム                                 |

| データ・リードバック・モード (図4) |                           |          |                                                  |

| $t_{16}$            | 0                         | ns (min) | A0、A1、A2～ $\overline{CS}$ のセットアップ・タイム            |

| $t_{17}$            | 0                         | ns (min) | A0、A1、A2～ $CS$ のホールド・タイム                         |

| $t_{18}$            | 0                         | ns (min) | $\overline{CS}\sim\overline{RD}$ の立ち下がりエッジ       |

| $t_{19}$            | 20                        | ns (min) | $RD$ パルス幅、 $V_{DD}=3.6\sim5.5V$                  |

|                     | 30                        | ns (min) | $RD$ パルス幅、 $V_{DD}=2.5\sim3.6V$                  |

| $t_{20}$            | 0                         | ns (min) | $CS\sim RD$ のホールド・タイム                            |

| $t_{21}$            | 22                        | ns (max) | $RD$ の立ち下がりエッジ後のデータ・アクセス時間、 $V_{DD}=3.6\sim5.5V$ |

|                     | 30                        | ns (max) | $RD$ の立ち下がりエッジ後のデータ・アクセス時間、 $V_{DD}=2.5\sim3.6V$ |

| $t_{22}$            | 4                         | ns (min) | $RD$ の立ち上がりエッジ後のバス開放時間                           |

|                     | 30                        | ns (max) |                                                  |

| $t_{23}$            | 22                        | ns (max) | $CS$ 立ち下がりエッジ～データ、 $V_{DD}=3.6\sim5.5V$          |

|                     | 30                        | ns (max) | $CS$ 立ち下がりエッジ～データ、 $V_{DD}=2.5\sim3.6V$          |

| $t_{24}$            | 30                        | ns (min) | $RD$ サイクル間の時間                                    |

| $t_{25}$            | 30                        | ns (min) | $RD$ から $WR$ までの時間                               |

| $t_{26}$            | 30                        | ns (min) | $WR$ から $RD$ までの時間、 $V_{DD}=3.6\sim5.5V$         |

|                     | 50                        | ns (min) | $WR$ から $RD$ までの時間、 $V_{DD}=2.5\sim3.6V$         |

<sup>1</sup> 設計と特性により保証しており、出荷テストは実施していません。

<sup>2</sup> すべての入力信号は $tr=tf=5ns$  ( $V_{DD}$ の10～90%) で仕様規定され、 $(V_{IL}+V_{IH})/2$ の電圧レベルからタイミングをとります。

<sup>3</sup> 図2を参照。

注

1. 同期 $LDAC$ 更新モード

2. 非同期 $LDAC$ 更新モード

図3. パラレル・インターフェースの書き込みタイミング図

図4. パラレル・インターフェースの読み出しタイミング図

# AD5346/AD5347/AD5348

## 絶対最大定格

表4. 特に指定のない限り、 $T_A=25^\circ\text{C}$

|                                 |                                              |

|---------------------------------|----------------------------------------------|

| GNDに対する $V_{DD}$ .....          | -0.3~+7V                                     |

| GNDに対するデジタル入力電圧.....            | -0.3~ $V_{DD}+0.3\text{V}$                   |

| GNDに対するデジタル出力電圧.....            | -0.3~ $V_{DD}+0.3\text{V}$                   |

| GNDに対するリファレンス入力電圧.....          | -0.3~ $V_{DD}+0.3\text{V}$                   |

| GNDに対する $V_{OUT}$ .....         | -0.3~ $V_{DD}+0.3\text{V}$                   |

| 動作温度範囲                          |                                              |

| 工業用 (Bバージョン) .....              | -40~+105°C                                   |

| 保存温度範囲.....                     | -65~+150°C                                   |

| ジャンクション温度.....                  | 150°C                                        |

| 38ピンTSSOPパッケージ                  |                                              |

| 消費電力 .....                      | $(T_{j\max} - T_A) / \theta_{JA} \text{ mW}$ |

| $\theta_{JA}$ 熱抵抗 .....         | 98.3°C/W                                     |

| $\theta_{JC}$ 熱抵抗 .....         | 8.9°C/W                                      |

| 40ピンLFCSPパッケージ                  |                                              |

| 消費電力 .....                      | $(T_{j\max} - T_A) / \theta_{JA} \text{ mW}$ |

| $\theta_{JA}$ 熱抵抗 (3層ボード) ..... | 29.6°C/W                                     |

| ピン温度、ハンダ処理 (10秒) .....          | 300°C                                        |

| IRリフロー、ピーク温度 .....              | 220°C                                        |

## 注意

ESD (静電放電) の影響を受けやすいデバイスです。人体や試験機器には4000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

左記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作に関するセクションに記載されている規定値以上でのデバイス動作を定めたものではありません。長時間デバイスを絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

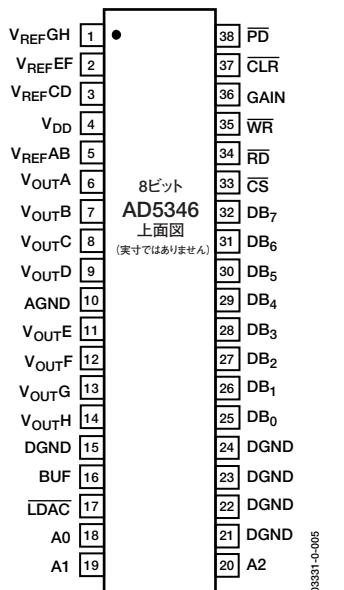

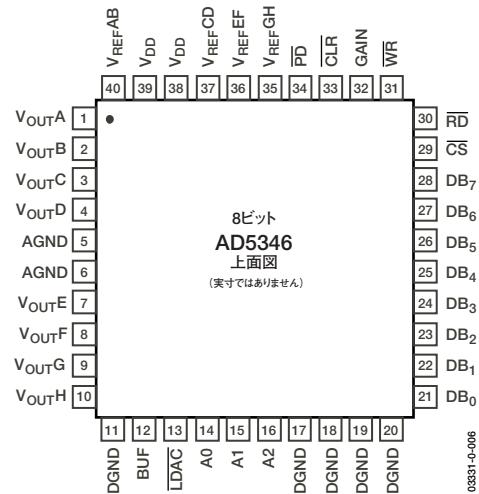

## AD5346のピン配置および機能の説明

図5. AD5346のピン配置—TSSOP

図6. AD5346のピン配置—LFCSP

表5. AD5346のピン機能の説明

| ピン番号      |          | 記号                               | 機能                                                                                                                         |

|-----------|----------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| TSSOP     | LFCSP    |                                  |                                                                                                                            |

| 1         | 35       | V <sub>REF</sub> GH              | DAC GとHのリファレンス入力                                                                                                           |

| 2         | 36       | V <sub>REF</sub> EF              | DAC EとFのリファレンス入力                                                                                                           |

| 3         | 37       | V <sub>REF</sub> CD              | DAC CとDのリファレンス入力                                                                                                           |

| 4         | 38、39    | V <sub>DD</sub>                  | 電源ピン。このデバイスは2.5~5.5Vで動作します。電源は、10μFと0.1μFのコンデンサを並列接続してGNDからデカッピングしてください。LFCSPパッケージでは、2本のV <sub>DD</sub> ピンを同じ電位にする必要があります。 |

| 5         | 40       | V <sub>REF</sub> AB              | DAC AとBのリファレンス入力                                                                                                           |

| 6~9、11~14 | 1~4、7~10 | V <sub>OUT</sub> X               | DAC Xの出力。レールtoレール動作によるバッファ出力                                                                                               |

| 10        | 5、6      | AGND                             | アナログ・グラウンド。アナログ回路のグラウンド・リファレンス                                                                                             |

| 15、21~24  | 11、17~20 | DGND                             | デジタル・グラウンド。デジタル回路のグラウンド・リファレンス                                                                                             |

| 16        | 12       | BUF                              | バッファ制御ピン。DACへのリファレンス入力をバッファするかどうかを制御します。                                                                                   |

| 17        | 13       | LDAC                             | アクティブ・ロー・コントロール入力。DACレジスタを入力レジスタの内容で更新します。これによって、すべてのDAC出力を同時に更新します。                                                       |

| 18        | 14       | A0                               | LSBアドレス・ピン。書き込み先のDACを選択します。                                                                                                |

| 19        | 15       | A1                               | アドレス・ピン。書き込み先のDACを選択します。                                                                                                   |

| 20        | 16       | A2                               | MSBアドレス・ピン。書き込み先のDACを選択します。                                                                                                |

| 25~32     | 21~28    | DB <sub>0</sub> ~DB <sub>7</sub> | 8個のパラレル・データ入力。DB <sub>7</sub> は、これら8ビットのMSBです。                                                                             |

| 33        | 29       | CS                               | アクティブ・ロー・チップ・セレクト入力。WRとともに使用し、パラレル・インターフェースにデータを書き込んだり、RDとともに使用し、DACからデータを読み出します。                                          |

| 34        | 30       | RD                               | アクティブ・ロー読み出し入力。CSとともに使用し、内部DACからデータを読み出します。                                                                                |

| 35        | 31       | WR                               | アクティブ・ロー書き込み入力。CSとともに使用し、パラレル・インターフェースにデータを書き込みます。                                                                         |

| 36        | 32       | GAIN                             | ゲイン制御ピン。DACからの出力レンジを0V~V <sub>REF</sub> または0V~2×V <sub>REF</sub> に制御します。                                                   |

| 37        | 33       | CLR                              | 非同期アクティブ・ロー・コントロール入力。すべての入力レジスタとDACレジスタをゼロにクリアします。                                                                         |

| 38        | 34       | PD                               | パワーダウン・ピン。このアクティブ・ロー制御ピンで、すべてのDACをパワーダウン・モードにします。                                                                          |

# AD5346/AD5347/AD5348

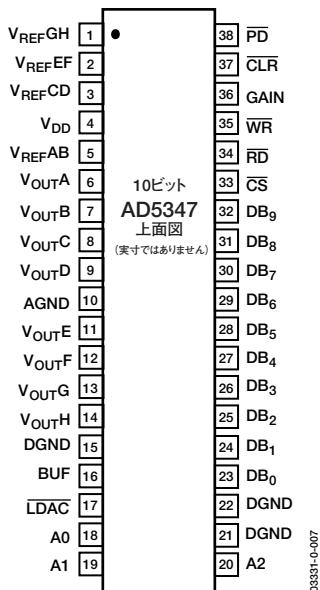

## AD5347のピン配置および機能の説明

図7. AD5347のピン配置—TSSOP

図8. AD5347のピン配置—LFCSP

表6. AD5347のピン機能の説明

| ピン番号      |          | 記号                               | 機能                                                                                                                         |

|-----------|----------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| TSSOP     | LFCSP    |                                  |                                                                                                                            |

| 1         | 35       | V <sub>REFGH</sub>               | DAC GとHのリファレンス入力                                                                                                           |

| 2         | 36       | V <sub>REFEF</sub>               | DAC EとFのリファレンス入力                                                                                                           |

| 3         | 37       | V <sub>REFCD</sub>               | DAC CとDのリファレンス入力                                                                                                           |

| 4         | 38、39    | V <sub>DD</sub>                  | 電源ピン。このデバイスは2.5~5.5Vで動作します。電源は、10μFと0.1μFのコンデンサを並列接続してGNDからデカッピングしてください。LFCSPパッケージでは、2本のV <sub>DD</sub> ピンを同じ電位にする必要があります。 |

| 5         | 40       | V <sub>REFAB</sub>               | DAC AとBのリファレンス入力                                                                                                           |

| 6~9、11~14 | 1~4、7~10 | V <sub>OUTX</sub>                | DAC Xの出力。レールtoレール動作によるバッファ出力                                                                                               |

| 10        | 5、6      | AGND                             | アナログ・グラウンド。アナログ回路のグラウンド・リファレンス                                                                                             |

| 15、21~22  | 11、17~18 | DGND                             | デジタル・グラウンド。デジタル回路のグラウンド・リファレンス                                                                                             |

| 16        | 12       | BUF                              | バッファ制御ピン。DACへのリファレンス入力をバッファするかどうかを制御します。                                                                                   |

| 17        | 13       | LDAC                             | アクティブ・ロー・コントロール入力。DACレジスタを入力レジスタの内容で更新します。これによって、すべてのDAC出力を同時に更新します。                                                       |

| 18        | 14       | A0                               | LSBアドレス・ピン。書き込み先のDACを選択します。                                                                                                |

| 19        | 15       | A1                               | アドレス・ピン。書き込み先のDACを選択します。                                                                                                   |

| 20        | 16       | A2                               | MSBアドレス・ピン。書き込み先のDACを選択します。                                                                                                |

| 23~32     | 19~28    | DB <sub>0</sub> ~DB <sub>9</sub> | 10個のパラレル・データ入力。DB <sub>9</sub> は、これら10ビットのMSBです。                                                                           |

| 33        | 29       | CS                               | アクティブ・ロー・チップ・セレクト入力。WRとともに使用し、パラレル・インターフェースにデータを書き込んだり、RDとともに使用し、DACからデータを読み出します。                                          |

| 34        | 30       | RD                               | アクティブ・ロー読み出し入力。CSとともに使用し、内部DACからデータを読み出します。                                                                                |

| 35        | 31       | WR                               | アクティブ・ロー書き込み入力。CSとともに使用し、パラレル・インターフェースにデータを書き込みます。                                                                         |

| 36        | 32       | GAIN                             | ゲイン制御ピン。DACからの出力レンジを0V~V <sub>REF</sub> または0V~2×V <sub>REF</sub> に制御します。                                                   |

| 37        | 33       | CLR                              | 非同期アクティブ・ロー・コントロール入力。すべての入力レジスタとDACレジスタをゼロにクリアします。                                                                         |

| 38        | 34       | PD                               | パワーダウン・ピン。このアクティブ・ロー制御ピンで、すべてのDACをパワーダウン・モードにします。                                                                          |

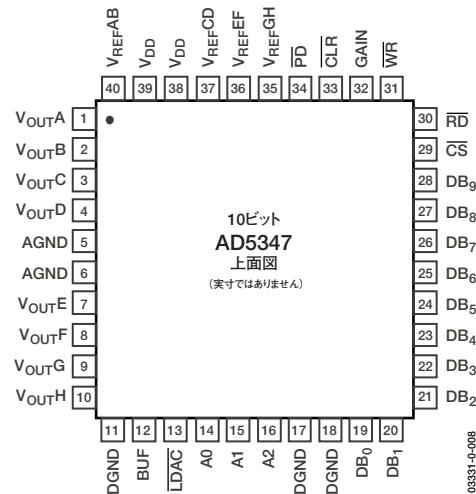

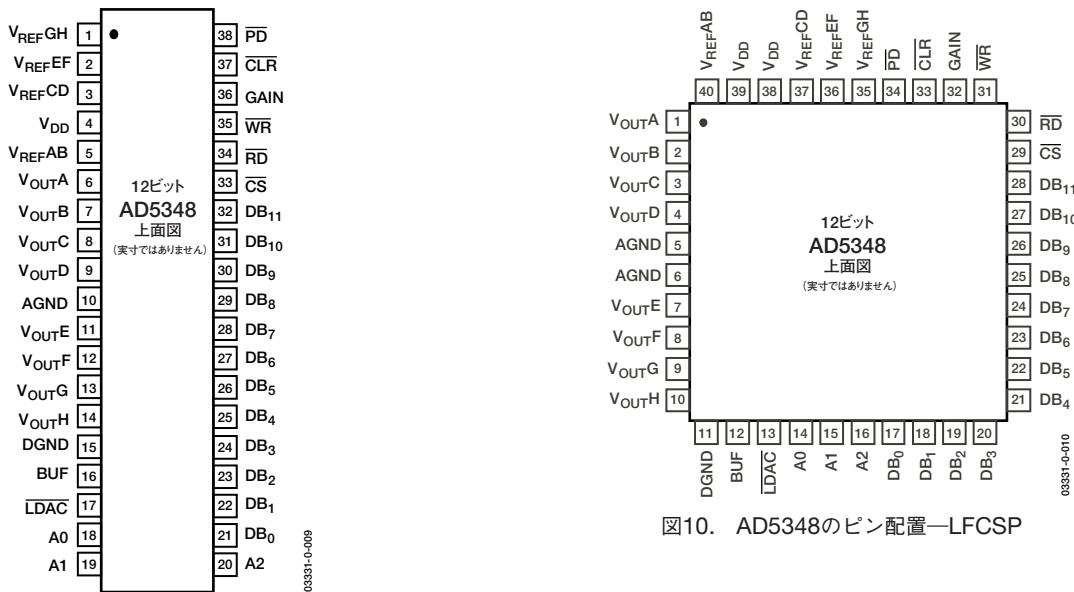

## AD5348のピン配置および機能の説明

図9. AD5348のピン配置—TSSOP

図10. AD5348のピン配置—LFCSP

表7. AD5348のピン機能の説明

| ピン番号      |          | 記号                                | 機能                                                                                                                         |

|-----------|----------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| TSSOP     | LFCSP    |                                   |                                                                                                                            |

| 1         | 35       | V <sub>REFGH</sub>                | DAC GとHのリファレンス入力                                                                                                           |

| 2         | 36       | V <sub>REFEF</sub>                | DAC EとFのリファレンス入力                                                                                                           |

| 3         | 37       | V <sub>REFCD</sub>                | DAC CとDのリファレンス入力                                                                                                           |

| 4         | 38、39    | V <sub>DD</sub>                   | 電源ピン。このデバイスは2.5~5.5Vで動作します。電源は、10μFと0.1μFのコンデンサを並列接続してGNDからデカッピングしてください。LFCSPパッケージでは、2本のV <sub>DD</sub> ピンを同じ電位にする必要があります。 |

| 5         | 40       | V <sub>REFAB</sub>                | DAC AとBのリファレンス入力                                                                                                           |

| 6~9、11~14 | 1~4、7~10 | V <sub>OUTX</sub>                 | DAC Xの出力。レールtoレール動作によるバッファ出力                                                                                               |

| 10        | 5、6      | AGND                              | アナログ・グラウンド。アナログ回路のグラウンド・リファレンス                                                                                             |

| 15        | 11       | DGND                              | デジタル・グラウンド。デジタル回路のグラウンド・リファレンス                                                                                             |

| 16        | 12       | BUF                               | バッファ制御ピン。DACへのリファレンス入力をバッファするかどうかを制御します。                                                                                   |

| 17        | 13       | LDAC                              | アクティブ・ロー・コントロール入力。DACレジスタを入力レジスタの内容で更新します。これによって、すべてのDAC出力を同時に更新します。                                                       |

| 18        | 14       | A0                                | LSBアドレス・ピン。書き込み先のDACを選択します。                                                                                                |

| 19        | 15       | A1                                | アドレス・ピン。書き込み先のDACを選択します。                                                                                                   |

| 20        | 16       | A2                                | MSBアドレス・ピン。書き込み先のDACを選択します。                                                                                                |

| 21~32     | 17~28    | DB <sub>0</sub> ~DB <sub>11</sub> | 12個のパラレル・データ入力。DB <sub>11</sub> は、これら12ビットのMSBです。                                                                          |

| 33        | 29       | CS                                | アクティブ・ロー・チップ・セレクト入力。WRとともに使用し、パラレル・インターフェースにデータを書き込んだり、RDとともに使用し、DACからデータを読み出します。                                          |

| 34        | 30       | RD                                | アクティブ・ロー読み出し入力。CSとともに使用し、内部DACからデータを読み出します。                                                                                |

| 35        | 31       | WR                                | アクティブ・ロー書き込み入力。CSとともに使用し、パラレル・インターフェースにデータを書き込みます。                                                                         |

| 36        | 32       | GAIN                              | ゲイン制御ピン。DACからの出力レンジを0V~V <sub>REF</sub> または0V~2×V <sub>REF</sub> に制御します。                                                   |

| 37        | 33       | CLR                               | 非同期アクティブ・ロー・コントロール入力。すべての入力レジスタとDACレジスタをゼロにクリアします。                                                                         |

| 38        | 34       | PD                                | パワーダウン・ピン。このアクティブ・ロー制御ピンで、すべてのDACをパワーダウン・モードにします。                                                                          |

# AD5346/AD5347/AD5348

## 用語集

### 相対精度

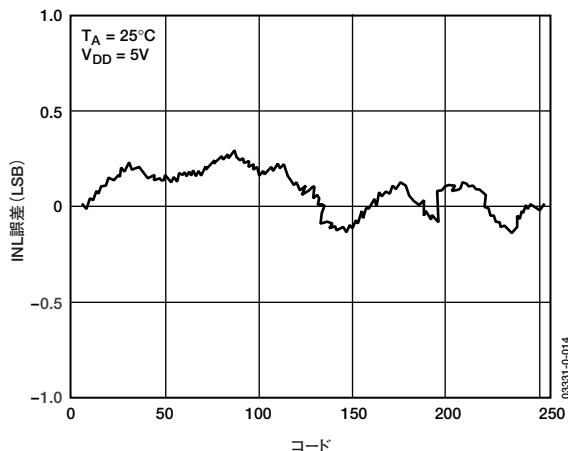

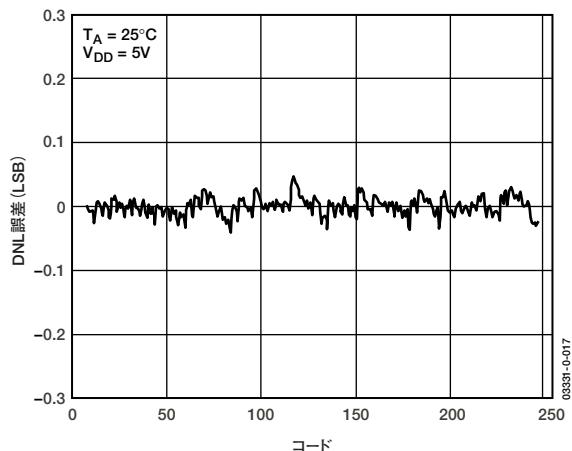

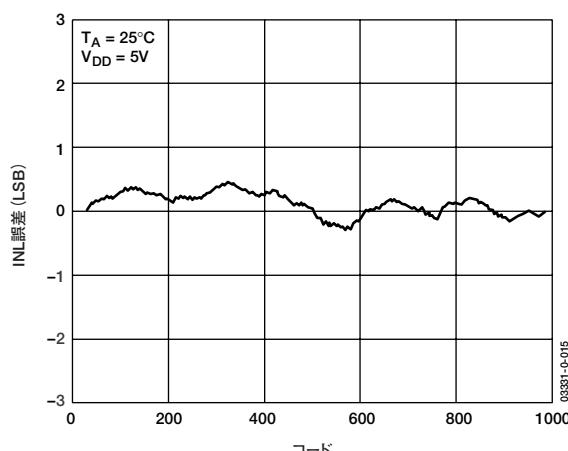

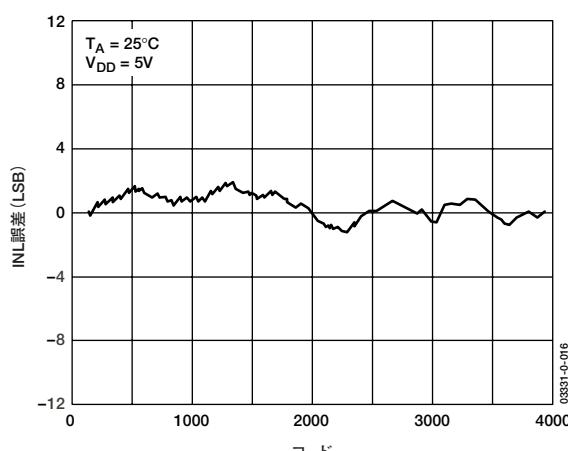

DACでは、相対精度または積分非直線性（INL）とは、DAC伝達関数の実際のエンドポイントを結ぶ直線からの最大偏差を示す値で、単位はLSBです。図14、図15、図16に、代表的なINLとコードの関係を示します。

### 微分非直線性

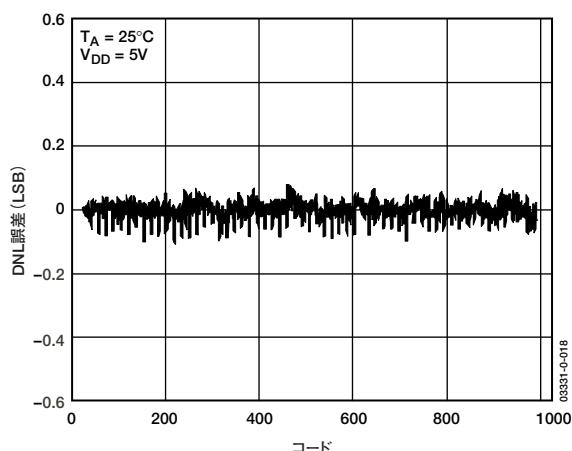

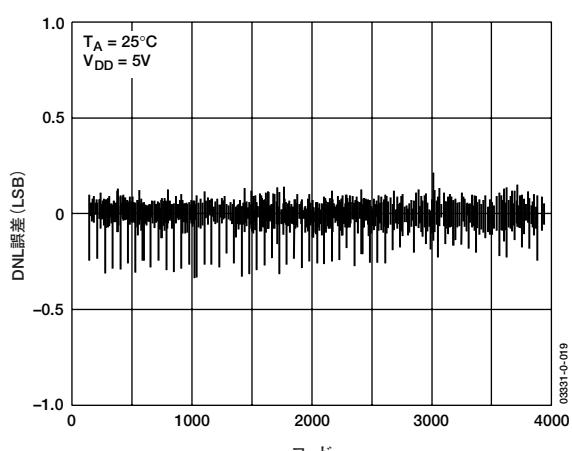

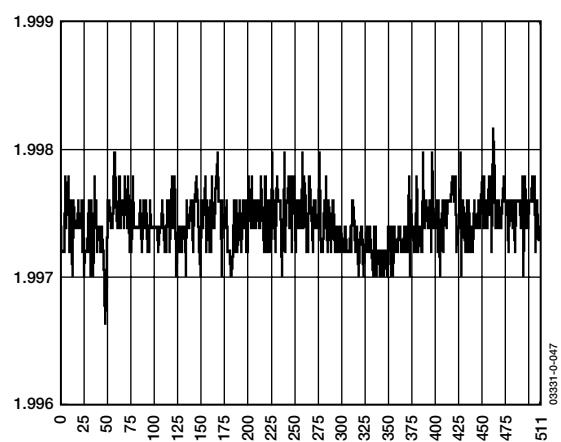

微分非直線性（DNL）とは、任意の2つの隣接するコード間で測定した変化と理想的な1LSB変化との差異です。最大±1LSBの仕様規定の微分非直線性によって、単調性を保証します。このDACは、設計によって単調性が保証されています。図17、図18、図19に、代表的なDNLとコードの関係を示します。

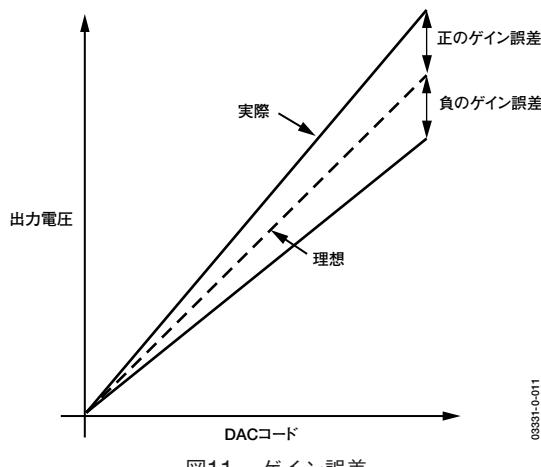

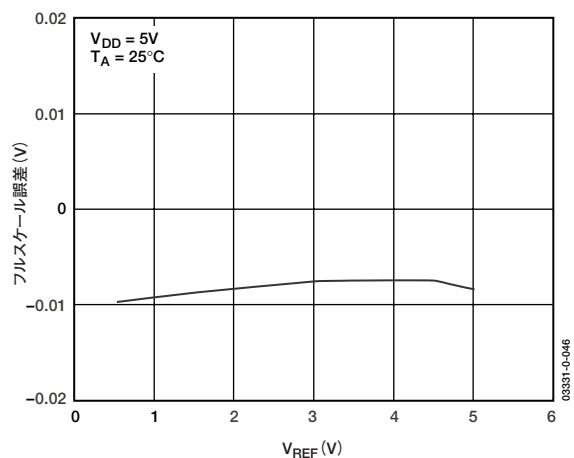

### ゲイン誤差

DACのスパン誤差を示す値で、バッファ・アンプのゲインの誤差も含まれます。ゲイン誤差はDAC伝達特性の理想値と実際値の傾きの偏差であり、フルスケール範囲のパーセンテージで表します。これを図11に示します。

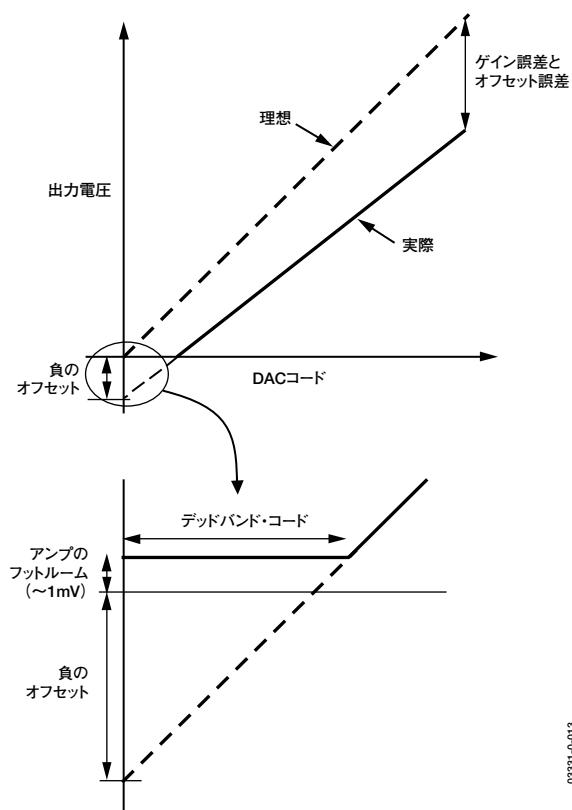

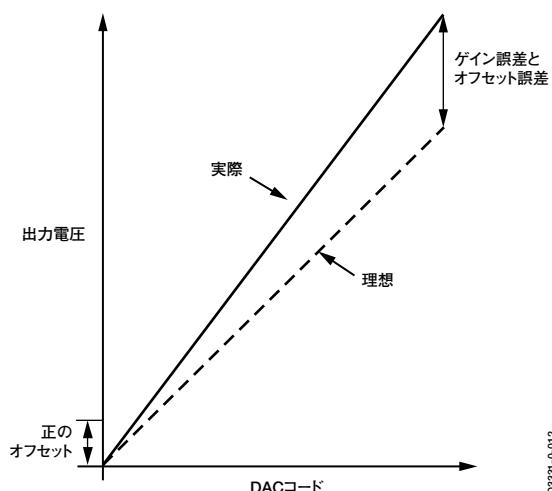

### オフセット誤差

DACと出力アンプのオフセット誤差を示す値で、フルスケール範囲のパーセンテージで表します。

オフセット電圧が正の場合、出力電圧はゼロ入力コードでもやはり正です。これを図12に示します。DACは単電源で動作するため、バッファ・アンプの出力に負のオフセットは生じません。その代わり、アンプ出力が飽和するゼロに近いコードがあります（アンプのフットルーム）。このコードより下には、出力電圧が変化しないデッドバンドがあります。これを図13に示します。

## オフセット誤差ドリフト

温度変化に伴うオフセット誤差の変化を示す値で、(フルスケール範囲に対するppm値) /°Cで表します。

## ゲイン誤差ドリフト

温度変化に伴うゲイン誤差の変化を示す値で、(フルスケール範囲に対するppm値) /°Cで表します。

## DC電源除去比 (PSRR)

電源電圧の変化がDACの出力に与える影響を示す値です。PSRRはDACのフルスケール出力に対する $V_{OUT}$ の変化と $V_{DD}$ の変化の比率であり、単位はdBです。 $V_{REF}$ は2Vに保持され、 $V_{DD}$ は±10%で変動します。

## DCクロストーク

ミッドスケールでの1つのDACの出力レベルにおいて、他のDACのフルスケール・コード変化（オール0からオール1、およびその逆）と出力変化に応じて発生するDC変動で、単位は $\mu$ Vです。

## リファレンス・フィードスルー

DAC出力が更新されていないとき（つまり、 $\overline{LDAC}$ がハイレベルの場合）の、DAC出力での信号の振幅とリファレンス入力との比率で、単位はdBです。

## チャンネル間絶縁

1つのDACの出力における信号の振幅と、他のDACのリファレンス入力上のサイン波との比率です。 $V_{REF}$ ピンの1つを接地し、他の $V_{REF}$ ピンに10kHzの4V p-pサイン波を印加して測定します。単位はdBです。

## メジャー・コード遷移グリッチ・エネルギー

DACが状態を変化させるときに、アナログ出力に注入されるインパルスのエネルギーです。通常、nV-s単位でのグリッチの領域として仕様規定され、メジャー・キャリー遷移（011...11から100...00または100...00から011...11）においてデジタル・コードが1LSBだけ変化するときに測定します。

## デジタル・フィードスルー

デバイスのデジタル入力ピンからDACのアナログ出力に注入されるインパルスを示す値ですが、DACに書き込みをしていないとき（ $\overline{CS}$ がハイレベル）に測定します。単位nV-sで仕様規定され、デジタル入力ピンでのフルスケール変化（つまりオール0からオール1、およびその逆）で測定します。

## デジタル・クロストーク

ミッドスケールでの1つのDACの出力に対して、他のDACの入力レジスタでのフルスケール・コード変化（オール0からオール1、およびその逆）に応じて転送されるグリッチ・インパルスであり、単位nV-sで表します。

## アナログ・クロストーク

1つのDACの出力に対して、他のDACの出力の変化によって転送されるグリッチ・インパルスです。アナログ・クロストークを測定するには、 $\overline{LDAC}$ をハイレベルに保持しながら、入力レジスタの1つにフルスケール・コード変化（オール0からオール1、およびその逆）をロードします。続いて、 $\overline{LDAC}$ にローのパルスを出し、デジタル・コードが変更されなかったDACの出力を監視します。グリッチの領域は単位nV-sで表します。

## DAC間クロストーク

1つのDACの出力に対して、他のDACのデジタル・コード変化とそれ以降の出力変化によって転送されるグリッチ・インパルスです。これには、デジタルとアナログの両方のクロストークが含まれます。DAC間クロストークを測定するには、 $\overline{LDAC}$ ピンをローレベルに設定して、DACの1つにフルスケール・コード変化（オール0からオール1、およびその逆）をロードして、他のDACの出力を監視します。グリッチのエネルギーは単位nV-sで表します。

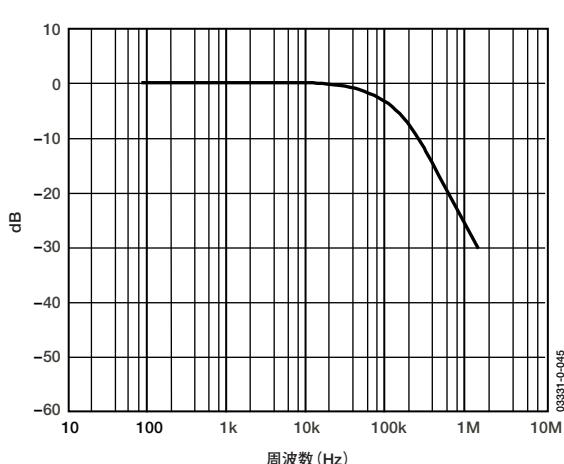

## 乗算帯域幅

DAC内のアンプには有限の帯域幅があります。乗算帯域幅はその値です。リファレンスのサイン波は、DACにフルスケール・コードをロードした状態で出力に現われます。乗算帯域幅は、出力振幅が入力より3dB低下する周波数です。

## 全高調波歪み (THD)

理想的なサイン波と、DACの使用で減衰したサイン波との差異です。サイン波はDACのリファレンスとして使用するもので、全高調波歪みはDAC出力に存在する高調波を示しています。単位はdBです。

# AD5346/AD5347/AD5348

## 代表的な性能特性

図14. AD5346の代表的なINLプロット

図17. AD5346の代表的なDNLプロット

図15. AD5347の代表的なINLプロット

図18. AD5347の代表的なDNLプロット

図16. AD5348の代表的なINLプロット

図19. AD5348の代表的なDNLプロット

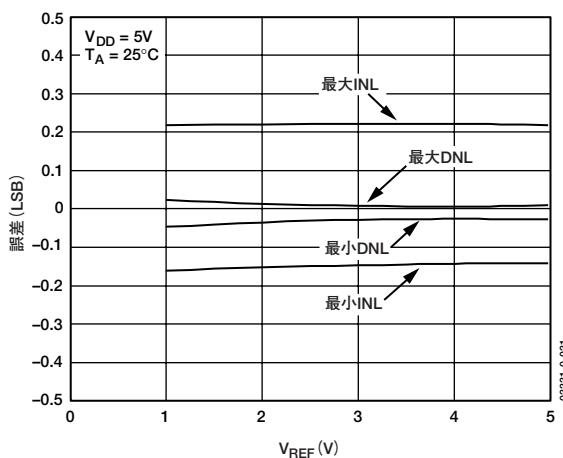

図20. AD5346のINLおよびDNL誤差対  $V_{REF}$

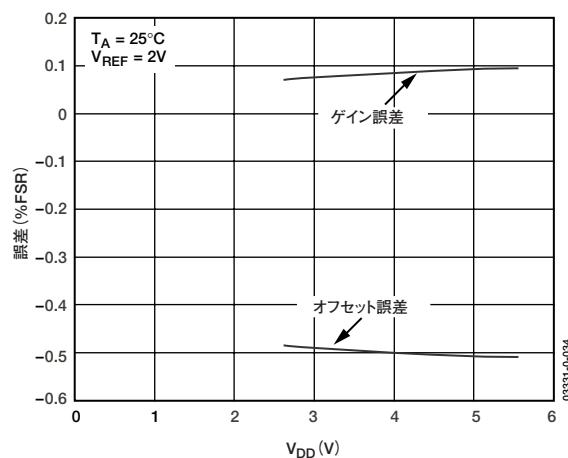

図23. オフセット誤差およびゲイン誤差対  $V_{DD}$

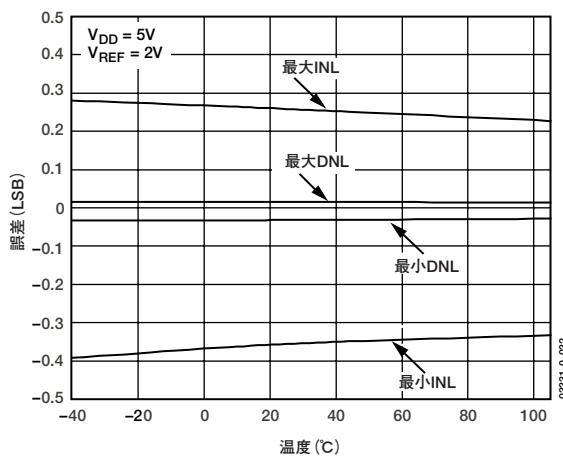

図21. AD5346のINLおよびDNL誤差対 温度

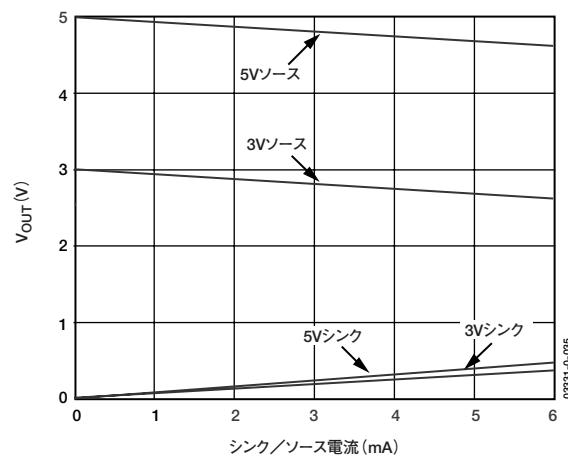

図24.  $V_{OUT}$ 対 ソース/シンク電流特性

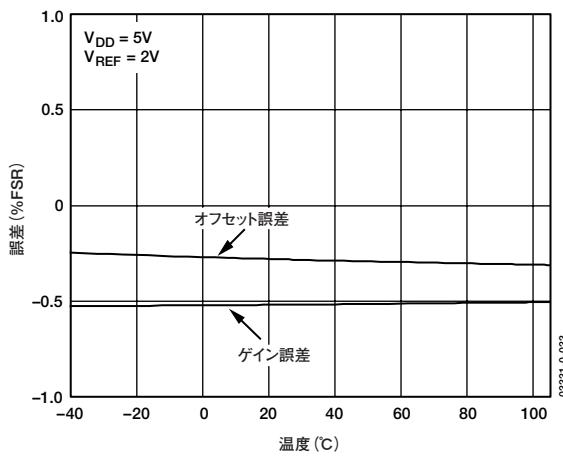

図22. AD5346のオフセット誤差および

ゲイン誤差対 温度

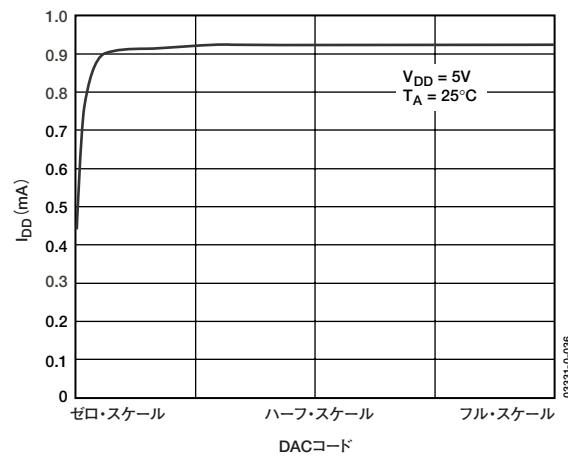

図25. 電源電流対 DACコード

# AD5346/AD5347/AD5348

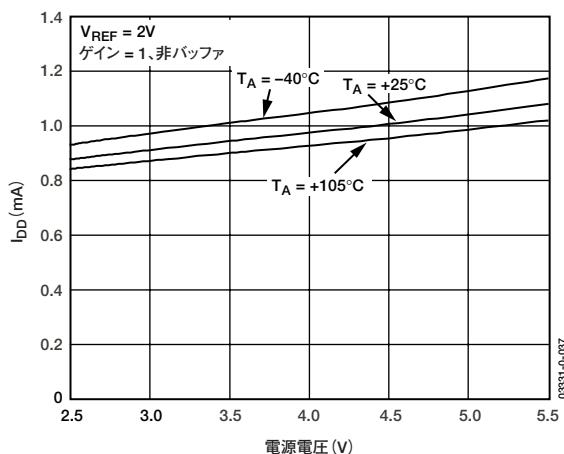

図26. 電源電流 対 電源電圧

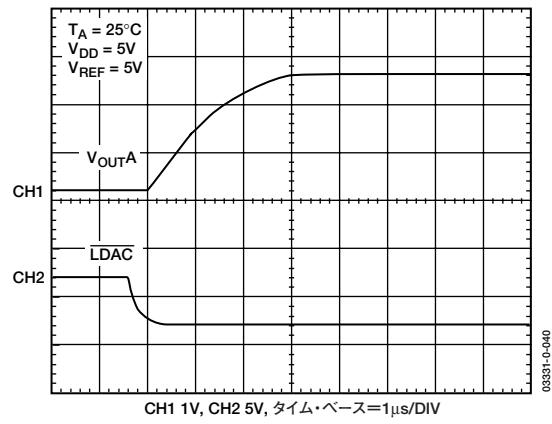

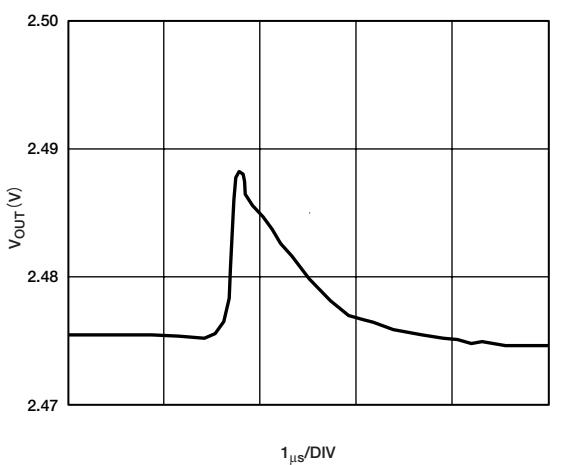

図29. ハーフスケール・セトリング

(1/4から3/4スケールへのコード変化)

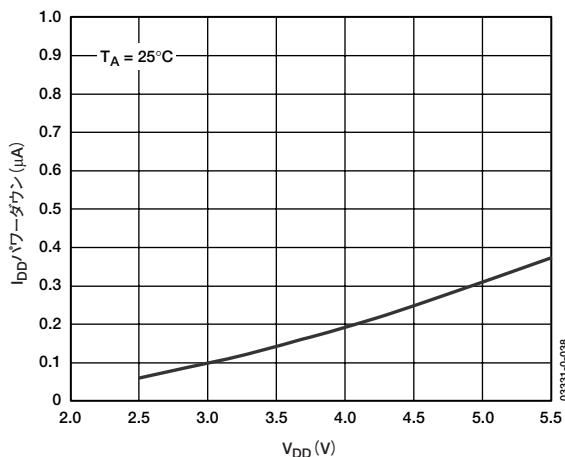

図27. パワーダウン電流 対 電源電圧

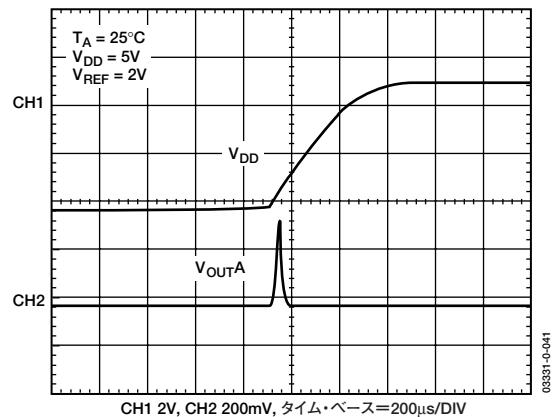

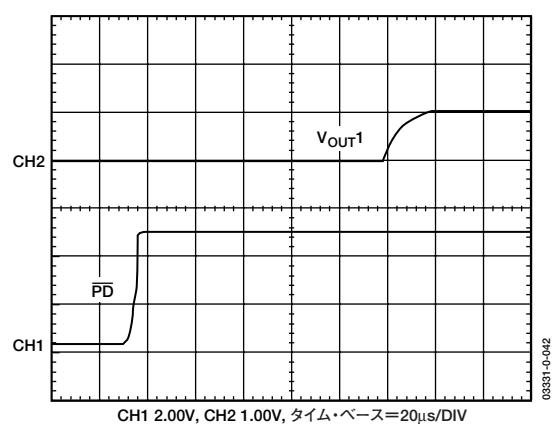

図30. 0Vへのパワーオン・リセット

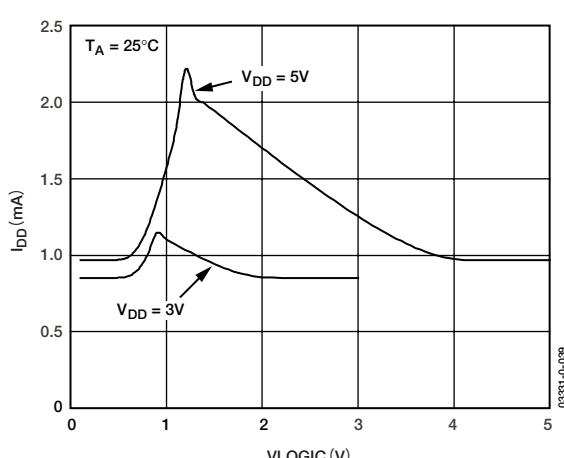

図28. 電源電流 対 ロジック入力電圧

図31. パワーダウンからミッドスケールへの復帰

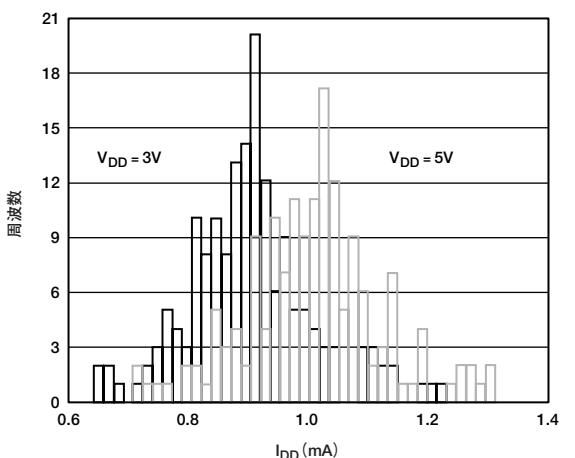

図32.  $V_{DD} = 3V$ と $V_{DD} = 5V$ での $I_{DD}$ のヒストグラム

図35. フルスケール誤差 対  $V_{REF}$

図33. AD5348のメジャー・コード遷移

グリッチ・エネルギー

図36. DAC間クロストーク

図34. 乗算帯域幅 (小信号周波数応答)

# AD5346/AD5347/AD5348

## 機能の説明

AD5346/AD5347/AD5348は、それぞれ8、10、12ビットの分解能の、CMOSプロセスで製造されたオクタル抵抗ストリングDACです。書き込みには、パラレル・インターフェースを使用します。DACは2.5~5.5Vの単電源で動作し、出力バッファ・アンプによってレールtoレールの出力振幅が得られます。バッファ・アンプのゲインを1または2に設定することで、出力電圧範囲は0V~V<sub>REF</sub>または0V~2×V<sub>REF</sub>になります。AD5346/AD5347/AD5348のリファレンス入力は、リファレンス源からほとんど電流を引き込まないようにバッファすることもできます。デバイスには、3Vでの消費電流をわずか100nAにまで低下できるパワーダウン機能があります。

### デジタル／アナログ変換部

1つのDACチャンネルのアーキテクチャは、リファレンス・バッファと抵抗ストリングDAC、これに続く出力バッファ・アンプで構成されています。V<sub>REF</sub>ピンの電圧がDACにリファレンス電圧を供給します。図37に、DACアーキテクチャのブロック図を示します。DACに対する入力コーディングはストレート・バイナリであるため、次の式で理想的な出力電圧を求めるることができます。

$$V_{OUT} = V_{REF} \times \frac{D}{2^N} \times \text{ゲイン}$$

ここで、

Dは2進コードと等価な10進値で、これをDACレジスタにロードします。

AD5346 (8ビット) では0~255

AD5347 (10ビット) では0~1023

AD5348 (12ビット) では0~4095

NはDACの分解能です。

「ゲイン」は出力アンプのゲインです (1または2)。

図37. 1つのDACチャンネルのアーキテクチャ

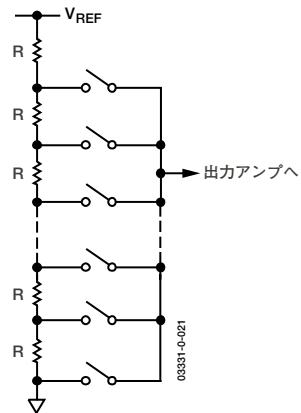

### 抵抗ストリング

抵抗ストリング部を図38に示します。これは、それぞれ値Rを持つ抵抗を並べただけの列 (ストリング) です。ストリング上のどのノードで電圧を取り出して出力アンプに供給するかは、DACレジスタにロードされるデジタル・コードによって決まります。ストリングをアンプに接続しているスイッチの1つを閉じて、電圧を取ります。抵抗で構成されたストリングであるため、単調性を保証します。

図38. 抵抗ストリング

### DACリファレンス入力

DACは外部リファレンスで動作します。AD5346/AD5347/AD5348には、DACの各ペア用のリファレンス入力があります。バッファ付きまたはバッファなしのリファレンス入力の設定が可能です。この設定は、BUFピンで制御します。

バッファ・モード (BUF=1) では、少なくとも10MΩのインピーダンスがあるため、外部リファレンス電圧からの電流はほぼゼロです。リファレンス入力レンジは1V~V<sub>DD</sub>です。

非バッファ・モード (BUF=0) では、リファレンス・アンプのヘッドルームとフットルームによる制約がないため、ユーザーはリファレンス電圧を0.25Vまで低くすることも、V<sub>DD</sub>まで上げることもできます。インピーダンスはまだかなり高く、0V~V<sub>REF</sub>モードで90kΩ、0V~2×V<sub>REF</sub>モードで45kΩになります (いずれもtyp値)。

外部バッファ・リファレンス (REF192など) を使用する場合は、オンチップ・バッファを使用する必要はありません。

### 出力アンプ

出力バッファ・アンプは、両側のレールから1mV以内の出力電圧を生成できます。実際の範囲は、V<sub>REF</sub>、GAIN、V<sub>OUT</sub>での負荷、オフセット誤差に依存します。

ゲインを+1にした場合 (GAIN=0)、出力レンジは0.001V~V<sub>REF</sub>になります。

ゲインを+2にした場合 (GAIN=+1)、出力レンジは0.001V~2×V<sub>REF</sub>になります。ただし、クランピングがあるため、最大出力はV<sub>DD</sub>-0.001Vになります。

出力アンプは、GNDまたはV<sub>DD</sub>に対する500pFに並列して、GNDまたはV<sub>DD</sub>に2kΩの負荷を駆動できます。出力アンプのソース／シンク特性を図24に示します。

スルーレートは0.7V/μsで、出力無負荷で±0.5LSB (8ビットで) までのハーフスケール・セトリング・タイムは6μsです。図29を参照してください。

## パラレル・インターフェース

AD5346/AD5347/AD5348は、データを8ビット、10ビット、または12ビットのシングル・ワードでロードします。

## ダブル・バッファ・インターフェース

AD5346/AD5347/AD5348のDACにはすべて、入力レジスタとDACレジスタからなるダブル・バッファ・インターフェースがあります。チップ・セレクト (CS) ピンと書き込み (WR) ピンの制御にしたがって、DACデータ、BUF、GAIN入力を入力レジスタに書き込みます。

DACレジスタへのアクセスは、LDAC機能で制御します。LDACがハイレベルのとき、DACレジスタはラッチされ、入力レジスタは、DACレジスタの内容を変えずに状態を変更できます。LDACがローレベルになると、DACレジスタは透過になり、入力レジスタの内容が転送されます。ゲインとバッファ制御信号もダブル・バッファされており、LDACがローレベルになったときだけ更新されます。

この機能が役に立つのは、ユーザーがすべてのDACとペリフェラルの同時更新を必要とする場合です。ユーザーはすべての入力レジスタに個別に書き込んでから、LDAC入力にローのパルスを出力することによって、すべての出力を同時に更新できます。

デバイスには、この他にもう1つの機能があります。これによって、LDACが最後にローであった時点以降入力レジスタが更新されていなければ、DACレジスタが更新されることはありません。通常、LDACがローのときには、DACレジスタには入力レジスタの内容が入っています。AD5346/AD5347/AD5348の場合、DACレジスタが更新されるのはDACレジスタが最後に更新された後に入力レジスタが変更されている場合のみです。このため、余計なクロストークがなくなります。

## クリア入力 (CLR)

CLRはアクティブ・ローの非同期クリアで、入力レジスタとDACレジスタをリセットします。

## チップ・セレクト入力 (CS)

CSは、デバイスを選択するアクティブ・ロー入力です。

## 書き込み入力 (WR)

WRは、デバイスへのデータの書き込みを制御するアクティブ・ロー入力です。データは、WRの立ち上がりエッジで入力レジスタにラッチされます。

## 読み出し入力 (RD)

RDはアクティブ・ロー入力で、内部DACレジスタからデータを読み出すタイミングを制御します。RDの立ち下がりエッジで、データがデータ・バスに移されます。高容量性負荷で高電源電圧という条件では、ユーザーが動的電流を許容できるレベルに抑えることで、チップ温度を仕様の範囲内にする必要があります。チップ温度は次式で計算できます。

$$T_{DIE} = T_{AMBIENT} + V_{DD} (I_{DD} + I_{DYNAMIC}) \theta_{JA}$$

ここで、  $I_{DYNAMIC} = cvf$

c=容量またはデータ・バス

v=V<sub>DD</sub>

f=リードバック周波数

## ロードDAC入力 (LDAC)

LDACはデータを入力レジスタからDACレジスタに転送することで、出力を更新します。LDAC機能によって、DACデータ、GAINデータ、BUFのダブル・バッファが可能となります。LDACには、2つのモードがあります。

- 同期モード このモードでは、WR入力の立ち上がりエッジで新しいデータを読み出した後、DACレジスタを更新します。LDACを常にローに固定しておくことも、または図3に示すようにパルスを与えることもできます。

- 非同期モード このモードでは、入力レジスタに書き込みが行われた時点で出力を同時に更新することはありません。LDACがローになると、入力レジスタの内容にしたがってDACレジスタを更新します。

## パワーオン・リセット

AD5346/AD5347/AD5348にはパワーオン・リセット機能があり、定義された状態でパワーアップします。パワーオン状態は次のとおりです。

- 通常動作

- バッファ付きのリファレンス入力

- 0V~V<sub>REF</sub>の出力レンジ

- 出力電圧を0Vに設定

入力レジスタとDACレジスタはいずれもゼロで埋められ、デバイスに対し有効な書き込みシーケンスが実行されるまでその状態にとどまります。デバイスがパワーアップするときのDAC出力の状態を把握していかなければならないアプリケーションでは、特にこの機能が役に立ちます。

## パワーダウン・モード

AD5346/AD5347/AD5348は低消費電力のデバイスで、3V電源で2.4mW、5V電源で5mWの電力を消費します（いずれもtyp値）。DACを使用していないときに消費電力をさらに低減するには、PDピンをローレベルにしてパワーダウン・モードにします。

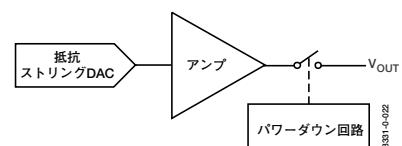

PDピンがハイレベルのとき、5Vで1mA (typ) の消費電流 (3Vで0.8mA) でDACは通常に動作します。パワーダウン・モードでは、DACをパワーダウンすると電源電流は5Vで400nA (3Vで120nA) に低下します。電源電流が低下するだけでなく、出力段も内部的にアンプの出力から切り替えられてオープン・サーキットになります。これにより、デバイスがパワーダウン・モードになっている間は出力がスリーステート状態になり、DACのアンプ出力に何が接続されていても入力条件が一定になるという利点が得られます。図39に出力段を示します。

図39. パワーダウン時の出力段

# AD5346/AD5347/AD5348

パワーダウン・モードがアクティブになると、バイアス・ジェネレータ、出力アンプ、抵抗ストリング、その他すべての関連するリニア回路がシャット・ダウンします。パワーダウン時には、レジスタの内容が影響を受けることはありません。パワーダウンから復帰するための時間は $V_{DD}=5V$ では $2.5\mu s$ 、 $V_{DD}=3V$ では $5\mu s$ です（いずれもtyp値）。これは、 $\overline{RD}$ ピンの立ち上がりエッジから、出力電圧がパワーダウン電圧から変化するまでの時間です。図31を参照してください。

## 推奨データ・バス・フォーマット

多くのアプリケーションでは、GAINピンとBUFピンを配線接続します。しかし、もっと柔軟性が要求される場合には、GAINとBUFをデータ・バスの中に入れることができます。この場合、ユーザーはGAINをソフトウェアで設定できるため、DACレンジの下半分で分解能を2倍にすることもできます。バス方式のシステムでは、GAINとBUFを書き込み動作時にデバイスに書き込み、LDACがローレベルになったときに有効にするため、これらをデータ入力として扱うことができます。つまり、複数のDACデバイスの出力アンプ・ゲインとリファレンス・バッファを共通のGAINラインとBUFラインを使用して制御できることになります。ただし、 $\overline{RD}$ 動作時にGAINとBUFが読み出されることはできません。

AD5347とAD5348のデータ・バスは、それぞれ少なくとも10ビットと12ビットの幅があり、16ビットのデータ・バス・システムに適しています。

図40に、GAINとBUFを16ビットのデータ・バス上に置くデータ・フォーマットの例を示します。実際のDACデータより上位の未使用ビットであれば、どれでもGAINとBUFに使用できます。

| AD5347 |   |     |      |      |      |     |     |     |     |     |     |     |     |     |     |

|--------|---|-----|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| X      | X | X   | X    | BUF  | GAIN | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

| AD5348 |   |     |      |      |      |     |     |     |     |     |     |     |     |     |     |

| X      | X | BUF | GAIN | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

X=未使用ビット

図40. GAINとBUFのデータを16ビット・バスに置いてワード・ロードするためのAD5347/AD5348のデータ・フォーマット

表8. AD5346/AD5347/AD5348の真理値表

| CLR | LDAC | CS | WR  | RD  | A2 | A1 | A0 | 機能              |

|-----|------|----|-----|-----|----|----|----|-----------------|

| 1   | 1    | 1  | X   | X   | X  | X  | X  | データ転送なし         |

| 1   | 1    | X  | 1   | 1   | X  | X  | X  | データ転送なし         |

| 0   | X    | X  | X   | X   | X  | X  | X  | 全レジスタをクリア       |

| 1   | 1    | 0  | 0→1 | 1   | 0  | 0  | 0  | DAC A入力レジスタにロード |

| 1   | 1    | 0  | 0→1 | 1   | 0  | 0  | 1  | DAC B入力レジスタにロード |

| 1   | 1    | 0  | 0→1 | 1   | 0  | 1  | 0  | DAC C入力レジスタにロード |

| 1   | 1    | 0  | 0→1 | 1   | 0  | 1  | 1  | DAC D入力レジスタにロード |

| 1   | 1    | 0  | 0→1 | 1   | 0  | 0  | 0  | DAC E入力レジスタにロード |

| 1   | 1    | 0  | 0→1 | 1   | 1  | 0  | 0  | DAC F入力レジスタにロード |

| 1   | 1    | 0  | 0→1 | 1   | 1  | 0  | 1  | DAC G入力レジスタにロード |

| 1   | 1    | 0  | 0→1 | 1   | 1  | 1  | 0  | DAC H入力レジスタにロード |

| 1   | X    | 0  | 1   | 1→0 | 0  | 0  | 0  | DACレジスタAを読み出す   |

| 1   | X    | 0  | 1   | 1→0 | 0  | 0  | 1  | DACレジスタBを読み出す   |

| 1   | X    | 0  | 1   | 1→0 | 0  | 1  | 0  | DACレジスタCを読み出す   |

| 1   | X    | 0  | 1   | 1→0 | 0  | 1  | 1  | DACレジスタDを読み出す   |

| 1   | X    | 0  | 1   | 1→0 | 1  | 0  | 0  | DACレジスタEを読み出す   |

| 1   | X    | 0  | 1   | 1→0 | 1  | 0  | 1  | DACレジスタFを読み出す   |

| 1   | X    | 0  | 1   | 1→0 | 1  | 1  | 0  | DACレジスタGを読み出す   |

| 1   | X    | 0  | 1   | 1→0 | 1  | 1  | 1  | DACレジスタHを読み出す   |

| 1   | 0    | X  | X   | 1   | X  | X  | X  | DACレジスタを更新      |

| X   | X    | 0  | 0   | 0   | X  | X  | X  | 無効操作            |

X=ドント・ケア

## アプリケーション情報

### 代表的なアプリケーション回路

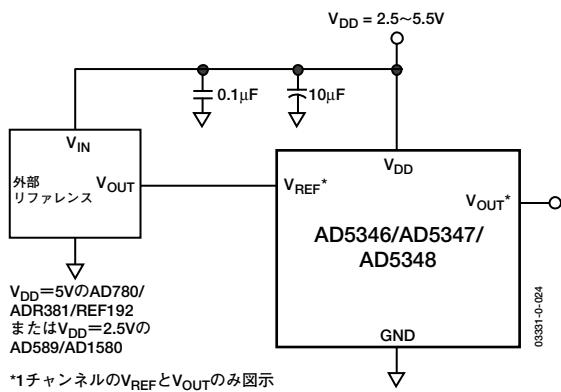

AD5346/AD5347/AD5348は、広範なリファレンス電圧で使用できます。特にリファレンス入力を非バッファに設定する場合、 $0.25V \sim V_{DD}$ のリファレンス範囲で完全な1象限の乗算機能が得られます。より一般的には、高精度の固定リファレンス電圧でこれらのデバイスを使用します。図41に、リファレンス入力に外部リファレンスを接続して使用する場合の代表的な構成を示します。5V動作に適したリファレンスは、AD780、ADR381、REF192 (2.5Vリファレンス) です。2.5V動作に適した外部リファレンスとしては、AD589とAD1580 (1.2Vバンドギャップ・リファレンス) があります。

図41. AD5346/AD5347/AD5348に外部リファレンスを使用する場合

### リファレンス電圧からのV<sub>DD</sub>の駆動

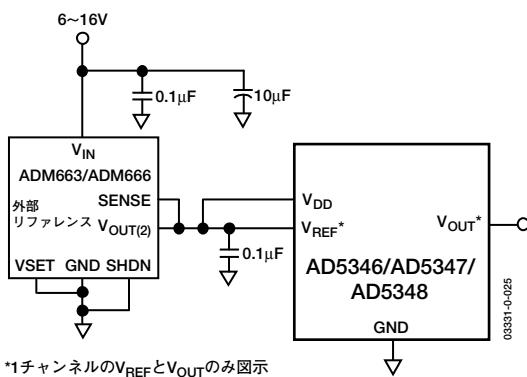

0V～V<sub>DD</sub>の出力レンジが必要な場合、最も簡単な方法はリファレンス入力をV<sub>DD</sub>に接続することです。この電源はあまり正確でなくノイズが多い場合もあるため、たとえば、図42に示すようにADM663やADM666などの5Vリファレンスを使用して、リファレンス電圧からデバイスに電力を供給することもできます。

図42. AD5346/AD5347/AD5348への電源およびリファレンスとしてADM663/ADM666を使用する場合

### AD5346/AD5347/AD5348を使用するバイポーラ動作

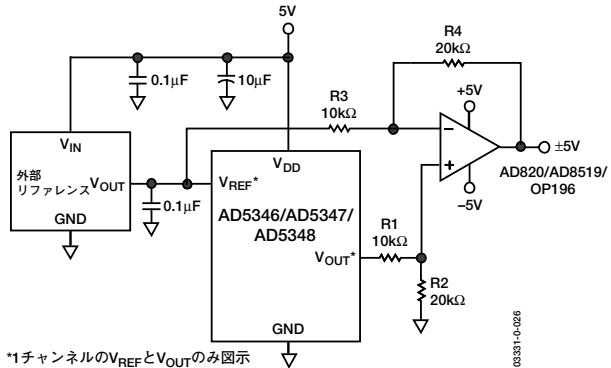

AD5346/AD5347/AD5348は単電源動作に設計されていますが、図43に示す回路を使用すれば、バイポーラ出力レンジ也可能になります。この回路の出力電圧レンジは±5Vです。出力アンプにAD820、AD8519、またはOP196を使用すれば、アンプ出力でのレールtoレール動作が得られます。

図43. AD5346/AD5347/AD5348によるバイポーラ動作

任意の入力コードに対する出力電圧は、次式で計算できます。

$$V_{OUT} = [(1 + R4/R3) \times (R2 / (R1 + R2) \times (2 \times V_{REF} \times D/2^N)) - R4 \times V_{REF}/R3]$$

ここで、

Dは、DACにロードされるコードと等価な10進値です。

NはDACの分解能です。

V<sub>REF</sub>はリファレンス電圧入力です。

値は以下のとおりです。

$$V_{REF} = 5V$$

$$R1 = R3 = 10k\Omega$$

$$R2 = R4 = 20k\Omega$$

$$V_{DD} = 5V$$

$$\text{ゲイン} = 2$$

$$V_{OUT} = (10 \times D/2^N) - 5$$

## AD5346/AD5347/AD5348

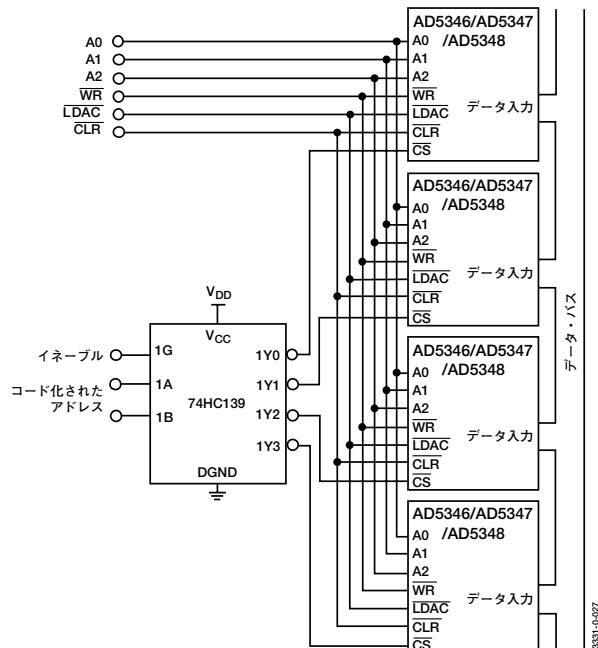

## 複数のAD5346/AD5347/AD5348の デコーディング

これらのデバイスのCSピンは、複数のDACをデコードするアプリケーションで使用できます。このようなアプリケーションでは、システム内のすべてのDACが同じデータとWRパルスを受信しますが、ある時点でアクティブになるのは1つのDACへのCSのみであり、データはCSがローレベルのDACにのみ書き込まれます。

システム内のどのDACでもアドレス指定できる2ラインから4ラインのデコーダとして、74HC139を使用します。タイミング誤差が生じないように、コード化されたアドレス入力が状態を変化させている間は、イネーブル入力を非アクティブ状態にしておく必要があります。図44に、システム内の複数のデバイスをデコードするための代表的な構成を示します。システム内の全DACに連続的にデータを書き込んだ後、共通のLDACラインを使用して、全DACを同時に更新できます。共通のCLRラインを使用すれば、全DAC出力を0Vにリセットすることもできます。

図44. 複数のDACデバイスのデコーディング

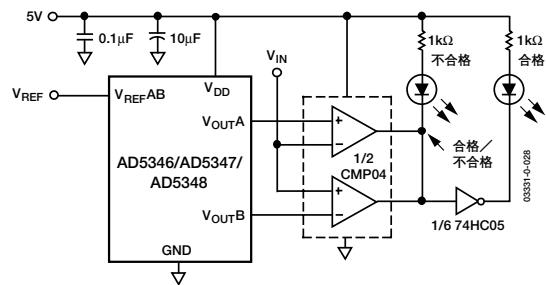

## デジタル設定可能なウィンドウ検出器としてのAD5346/AD5347/AD5348

図45に、AD5346/AD5347/AD5348内の2個のDACを使用したデジタル設定可能な上／下限検出器を示します。デバイス内の任意のペアのDACを使用できますが、この説明では便宜上、DAC AとDAC Bとします。

テストする上限値と下限値をDAC AとDAC Bにロードすると、CMP04の限界が設定されます。V<sub>IN</sub>入力での信号がプログラムされたウィンドウの外にある場合、LEDが点灯して不合格状態を示します。

図45. プログラマブルなウィンドウ検出器

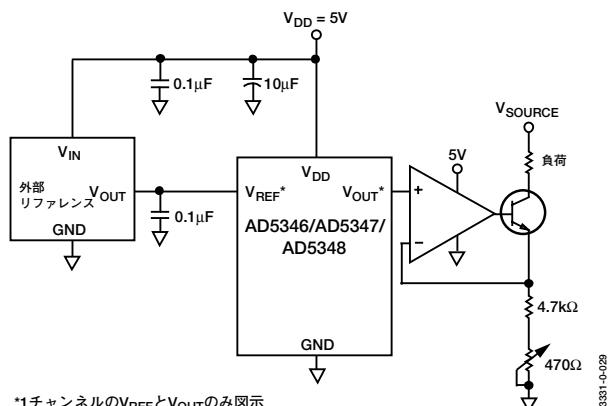

## プログラマブルな電流源

図46に、プログラマブルな電流源の制御エレメントとしてAD5346/AD5347/AD5348を使用する場合を示します。この例では、フルスケール電流を1mAに設定しています。DACからの出力電圧は、直列に接続された4.7kΩの電流設定抵抗と470Ωの調整用ポテンショメータを介して印加され、約±5%の調整が可能になります。このアンプの帰還ループに置く適切なトランジスタとしては、BC107や2N3904などがあります。これによって、最小6VのV<sub>SOURCE</sub>から電流源を動作させることができます。動作範囲は、トランジスタの動作特性によって決まります。適切なアンプとしてはAD820やOP295などがあり、いずれもその出力でレールtoレール動作が可能です。任意のデジタル入力コードと抵抗値に対する電流は、次式で計算できます。

$$I = G \times V_{\text{REF}} \frac{D}{(2^N \times R)} \text{mA}$$

ここで、

*G*はバッファ・アンプのゲインです (1または2)。

Dはデジタル入力コードです。

$N$ はDACの分解能です (8、10、または12ビット)。

$R$ は抵抗と調整用ポテンショメータの合計抵抗値です ( $\text{k}\Omega$ )。

図46. プログラマブルな電流源

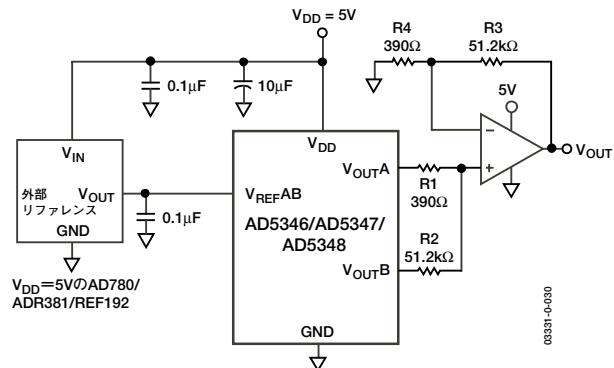

## AD5346/AD5347/AD5348を使用する 粗調整と微調整

図47に示すように、AD5346/AD5347/AD5348内の2個のDACをペアにして、粗調整と微調整の機能を実現できます。前述のウインドウ検出器の場合と同じく、ここでもDAC AとDAC Bについて説明します。

DAC Aは粗調整に使用し、DAC Bは微調整に使用します。R1とR2の比率を変更すると、粗調整と微調整の相対的効果が変わります。図に示す抵抗値を使用すると、出力アンプにDAC A出力に対するユニティ・ゲインがあるため、出力レンジは0V～(V<sub>REF</sub>−1LSB)になります。DAC Bではアンプのゲインが $7.6 \times 10^{-3}$ なので、DAC BのレンジはDAC Aの2LSBに等しくなります。

この回路は2.5Vリファレンスの場合ですが、最高V<sub>DD</sub>までのリファレンス電圧を使用できます。ここに示すオペアンプで、レールtoレール出力振幅が可能になります。

図47. 粗調整と微調整

## 電源のバイパスとグラウンディング

精度が大切な回路では、定格の性能を得るために電源とグラウンド・リターンのレイアウトを十分注意して行う必要があります。

AD5346/AD5347/AD5348を実装するプリント回路ボードでは、アナログ部とデジタル部を分離して、ボードの一定の場所にまとめて配置するように設計してください。これによって、簡単に分離できるグラウンド・プレーンを使用できるようになります。最適なシールド効果が得られるため、一般にエッチング部分を最小にする方法がグラウンド・プレーンには最適です。デジタル・グラウンド・プレーンとアナログ・グラウンド・プレーンは1点のみで接続してください。AGND～DGND接続を必要とするデバイスがAD5346/AD5347/AD5348のみである場合は、グラウンド・プレーンをAD5346/AD5347/AD5348のAGNDピンとDGNDピンで接続してください。複数のデバイスがAGND～DGND接続を必要とするシステム内では、AD5346/AD5347/AD5348のできるだけ近くで、星形グラウンド・ポイントの1個所のみで接続します。

AD5346/AD5347/AD5348では、10μFと0.1μFのコンデンサができるだけパッケージの近く、理想的にはデバイスのすぐ隣で並列接続し、電源に対して十分なバイパスをとる必要があります。10μFのコンデンサはタンタルのビード型を使います。0.1μFのコンデンサは、高周波でグラウンドに対する低インピーダンス・パスを提供する一般的なセラミック・タイプなど、低い有効直列抵抗 (ESR) と有効直列インダクタンス (ESI) を備えたものを使用し、内部ロジックの切り替えによる過渡電流を処理します。

デバイスの電源ラインには、できるだけ太いパターンを使って低インピーダンス・パスを実現し、電源ライン上でのグリッチの影響を抑えてください。クロックなどの高速スイッチング信号はデジタル・グラウンドでシールドし、ボード上の他の部品ヘノイズを拡散しないようにし、また絶対にリファレンス入力の近くを通さないようにしてください。デジタル信号とアナログ信号は、交差させないようにする必要があります。ボードの反対側のパターンは互いに直角になるように配置し、これによってボードを通過するフィードスルーの影響を低減します。マイクロストリップ技術は最善の方法ですが、両面ボードでは常に使用できるわけではありません。この技術では、ボードの部品面をグラウンド・プレーン専用にし、信号パターンをハンダ面に配置します。

# AD5346/AD5347/AD5348

表9. AD53xxパラレル・デバイスの概要

| 部品番号        | 分解能 | DNL   | V <sub>REF</sub> ピン | セトリング・タイム | 追加のピン機能 |      |      |     | パッケージ       | ピン    |

|-------------|-----|-------|---------------------|-----------|---------|------|------|-----|-------------|-------|

|             |     |       |                     |           | BUF     | GAIN | HBEN | CLR |             |       |

| <b>シングル</b> |     |       |                     |           |         |      |      |     |             |       |

| AD5330      | 8   | ±0.25 | 1                   | 6μs       | ✓       | ✓    |      | ✓   | TSSOP       | 20    |

| AD5331      | 10  | ±0.5  | 1                   | 7μs       |         | ✓    |      | ✓   | TSSOP       | 20    |

| AD5340      | 12  | ±1.0  | 1                   | 8μs       | ✓       | ✓    |      | ✓   | TSSOP       | 24    |

| AD5341      | 12  | ±1.0  | 1                   | 8μs       | ✓       | ✓    | ✓    | ✓   | TSSOP       | 20    |

| <b>デュアル</b> |     |       |                     |           |         |      |      |     |             |       |

| AD5332      | 8   | ±0.25 | 2                   | 6μs       |         |      |      | ✓   | TSSOP       | 20    |

| AD5333      | 10  | ±0.5  | 2                   | 7μs       | ✓       | ✓    |      | ✓   | TSSOP       | 24    |

| AD5342      | 12  | ±1.0  | 2                   | 8μs       | ✓       | ✓    |      | ✓   | TSSOP       | 28    |

| AD5343      | 12  | ±1.0  | 1                   | 8μs       |         |      | ✓    | ✓   | TSSOP       | 20    |

| <b>クワッド</b> |     |       |                     |           |         |      |      |     |             |       |

| AD5334      | 8   | ±0.25 | 2                   | 6μs       |         | ✓    |      | ✓   | TSSOP       | 24    |

| AD5335      | 10  | ±0.5  | 2                   | 7μs       |         |      | ✓    | ✓   | TSSOP       | 24    |

| AD5336      | 10  | ±0.5  | 4                   | 7μs       |         | ✓    |      | ✓   | TSSOP       | 28    |

| AD5344      | 12  | ±1.0  | 4                   | 8μs       |         |      |      | ✓   | TSSOP       | 28    |

| <b>オクタル</b> |     |       |                     |           |         |      |      |     |             |       |

| AD5346      | 8   | ±0.25 | 4                   | 6μs       | ✓       | ✓    |      | ✓   | TSSOP、LFCSP | 38、40 |

| AD5347      | 10  | ±0.5  | 4                   | 7μs       | ✓       | ✓    |      | ✓   | TSSOP、LFCSP | 38、40 |

| AD5348      | 12  | ±1.0  | 4                   | 8μs       | ✓       | ✓    |      | ✓   | TSSOP、LFCSP | 38、40 |

表10. AD53xxシリアル・デバイスの概要

| 部品番号        | 分解能 | DNL   | V <sub>REF</sub> ピン                    | セトリング・タイム | インターフェース         | パッケージ       | ピン   |

|-------------|-----|-------|----------------------------------------|-----------|------------------|-------------|------|

| <b>シングル</b> |     |       |                                        |           |                  |             |      |

| AD5300      | 8   | ±0.25 | 0 (V <sub>REF</sub> =V <sub>DD</sub> ) | 4μs       | SPI <sup>®</sup> | SOT-23、MSOP | 6, 8 |

| AD5310      | 10  | ±0.5  | 0 (V <sub>REF</sub> =V <sub>DD</sub> ) | 6μs       | SPI              | SOT-23、MSOP | 6, 8 |

| AD5320      | 12  | ±1.0  | 0 (V <sub>REF</sub> =V <sub>DD</sub> ) | 8μs       | SPI              | SOT-23、MSOP | 6, 8 |

| AD5301      | 8   | ±0.25 | 0 (V <sub>REF</sub> =V <sub>DD</sub> ) | 6μs       | 2線式              | SOT-23、MSOP | 6, 8 |

| AD5311      | 10  | ±0.5  | 0 (V <sub>REF</sub> =V <sub>DD</sub> ) | 7μs       | 2線式              | SOT-23、MSOP | 6, 8 |

| AD5321      | 12  | ±1.0  | 0 (V <sub>REF</sub> =V <sub>DD</sub> ) | 8μs       | 2線式              | SOT-23、MSOP | 6, 8 |

| <b>デュアル</b> |     |       |                                        |           |                  |             |      |

| AD5302      | 8   | ±0.25 | 2                                      | 6μs       | SPI              | MSOP        | 8    |

| AD5312      | 10  | ±0.5  | 2                                      | 7μs       | SPI              | MSOP        | 8    |

| AD5322      | 12  | ±1.0  | 2                                      | 8μs       | SPI              | MSOP        | 8    |

| AD5303      | 8   | ±0.25 | 2                                      | 6μs       | SPI              | TSSOP       | 16   |

| AD5313      | 10  | ±0.5  | 2                                      | 7μs       | SPI              | TSSOP       | 16   |

| AD5323      | 12  | ±1.0  | 2                                      | 8μs       | SPI              | TSSOP       | 16   |

| <b>クワッド</b> |     |       |                                        |           |                  |             |      |

| AD5304      | 8   | ±0.25 | 1                                      | 6μs       | SPI              | MSOP        | 10   |

| AD5314      | 10  | ±0.5  | 1                                      | 7μs       | SPI              | MSOP        | 10   |

| AD5324      | 12  | ±1.0  | 1                                      | 8μs       | SPI              | MSOP        | 10   |

| AD5305      | 8   | ±0.25 | 1                                      | 6μs       | 2線式              | MSOP        | 10   |

| AD5315      | 10  | ±0.5  | 1                                      | 7μs       | 2線式              | MSOP        | 10   |

| AD5325      | 12  | ±1.0  | 1                                      | 8μs       | 2線式              | MSOP        | 10   |

| AD5306      | 8   | ±0.25 | 4                                      | 6μs       | 2線式              | TSSOP       | 16   |

| AD5316      | 10  | ±0.5  | 4                                      | 7μs       | 2線式              | TSSOP       | 16   |

| AD5326      | 12  | ±1.0  | 4                                      | 8μs       | 2線式              | TSSOP       | 16   |

| AD5307      | 8   | ±0.25 | 2                                      | 6μs       | SPI              | TSSOP       | 16   |

| AD5317      | 10  | ±0.5  | 2                                      | 7μs       | SPI              | TSSOP       | 16   |

| AD5327      | 12  | ±1.0  | 2                                      | 8μs       | SPI              | TSSOP       | 16   |

| <b>オクタル</b> |     |       |                                        |           |                  |             |      |

| AD5308      | 8   | ±0.25 | 2                                      | 6μs       | SPI              | TSSOP       | 16   |

| AD5318      | 10  | ±0.5  | 2                                      | 7μs       | SPI              | TSSOP       | 16   |

| AD5328      | 12  | ±1.0  | 2                                      | 8μs       | SPI              | TSSOP       | 16   |

## 外形寸法

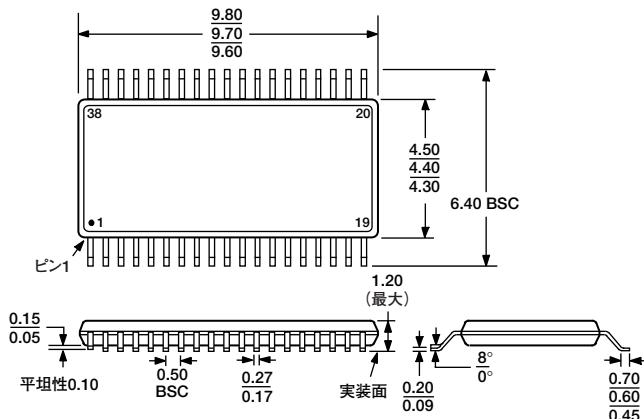

JEDEC規格MO-153BD-1に準拠

図48. 38ピン薄型シリンク・スマール・アウトライン・パッケージ [TSSOP]

(RU-38)

寸法単位 : mm

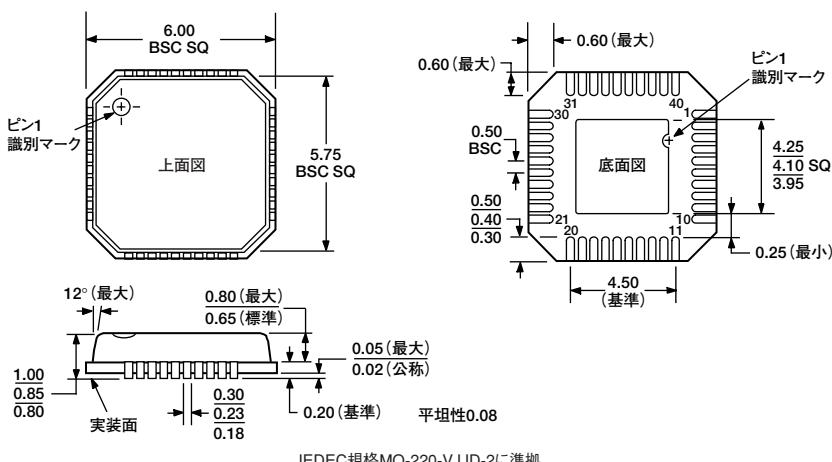

JEDEC規格MO-220-VJJD-2に準拠

図49. 40ピン・リード・フレーム・チップ・スケール・パッケージ [LFCSP]

(CP-40)

寸法単位 : mm

# AD5346/AD5347/AD5348

## オーダー・ガイド

表11. AD5346のオーダー・ガイド

| モデル             | 温度範囲       | パッケージ                           | パッケージ・オプション |

|-----------------|------------|---------------------------------|-------------|

| AD5346BRU       | -40~+105°C | TSSOP (薄型シユリンクSOP)              | RU-38       |

| AD5346BRU-REEL  | -40~+105°C | TSSOP (薄型シユリンクSOP)              | RU-38       |

| AD5346BRU-REEL7 | -40~+105°C | TSSOP (薄型シユリンクSOP)              | RU-38       |

| AD5346BCP       | -40~+105°C | LFCSP (リード・フレーム・チップ・スケール・パッケージ) | CP-40       |

| AD5346BCP-REEL  | -40~+105°C | LFCSP (リード・フレーム・チップ・スケール・パッケージ) | CP-40       |

| AD5346BCP-REEL7 | -40~+105°C | LFCSP (リード・フレーム・チップ・スケール・パッケージ) | CP-40       |

表12. AD5347のオーダー・ガイド

| モデル             | 温度範囲       | パッケージ                           | パッケージ・オプション |

|-----------------|------------|---------------------------------|-------------|

| AD5347BRU       | -40~+105°C | TSSOP (薄型シユリンクSOP)              | RU-38       |

| AD5347BRU-REEL  | -40~+105°C | TSSOP (薄型シユリンクSOP)              | RU-38       |

| AD5347BRU-REEL7 | -40~+105°C | TSSOP (薄型シユリンクSOP)              | RU-38       |

| AD5347BCP       | -40~+105°C | LFCSP (リード・フレーム・チップ・スケール・パッケージ) | CP-40       |

| AD5347BCP-REEL  | -40~+105°C | LFCSP (リード・フレーム・チップ・スケール・パッケージ) | CP-40       |

| AD5347BCP-REEL7 | -40~+105°C | LFCSP (リード・フレーム・チップ・スケール・パッケージ) | CP-40       |

表13. AD5348のオーダー・ガイド

| モデル             | 温度範囲       | パッケージ                           | パッケージ・オプション |

|-----------------|------------|---------------------------------|-------------|

| AD5348BRU       | -40~+105°C | TSSOP (薄型シユリンクSOP)              | RU-38       |

| AD5348BRU-REEL  | -40~+105°C | TSSOP (薄型シユリンクSOP)              | RU-38       |

| AD5348BRU-REEL7 | -40~+105°C | TSSOP (薄型シユリンクSOP)              | RU-38       |

| AD5348BCP       | -40~+105°C | LFCSP (リード・フレーム・チップ・スケール・パッケージ) | CP-40       |

| AD5348BCP-REEL  | -40~+105°C | LFCSP (リード・フレーム・チップ・スケール・パッケージ) | CP-40       |

| AD5348BCP-REEL7 | -40~+105°C | LFCSP (リード・フレーム・チップ・スケール・パッケージ) | CP-40       |

**AD5346/AD5347/AD5348**

# **AD5346/AD5347/AD5348**

C03331-0-11/03(0)-J