## 正誤表

この製品の和文データシートにおいて、英語版データシート (Rev. B) との差分がありましたのでお知らせ致します。

この正誤表は、2016年11月2日現在、アナログ・デバイセズ株式会社で確認した変更箇所を記したもので、なお、英語版データシートが最新となります。

正誤表作成年月日：2016年11月2日

製品名：AD1895

対象となる和文データシートのリビジョン(Rev)：Rev.0

訂正箇所：

### P.1

特長：

|    |                       |

|----|-----------------------|

| 旧) | 最大サンプル・レート：192kHz+12% |

| 新) | 最大サンプル・レート：～192kHz    |

### P.2

仕様：サンプル・レート比

|    |                        |           |

|----|------------------------|-----------|

| 旧) | ダウンサンプリング (短い GRPDLYS) |           |

| 新) | ダウンサンプリング              |           |

| 旧) | ダウンサンプリング (長い GRPDLYS) | 7:0:1 max |

| 新) | 削除                     |           |

### P.3

仕様：デジタル・タイミング

|    |                              |           |

|----|------------------------------|-----------|

| 旧) | $t_{MPWH}$                   | 8nS min   |

| 新) | $t_{MPWH}$                   | 9nS min   |

| 旧) | $t_{RSTL}$ RESET ロー・レベル・パルス幅 | 200nS max |

| 新) | $t_{RSTL}$ RESET ロー・レベル・パルス幅 | 200nS min |

### P.5

オーダーガイド

|    |                          |

|----|--------------------------|

| 旧) | AD1895YRS, AD1895YRSRL   |

| 新) | AD1895AYRS, AD1895AYRSRL |

### P.7~15

特性図 新) 英文のデータシート Rev B P.7~15 (TPC.1~TPC.52) までを利用して下さい。

アナログ・デバイセズ株式会社

本社／〒105-6891 東京都港区海岸1-16-1 ニュービア竹芝サウスタワー

ビル電話 03 (5402) 8200

大阪営業所／〒532-0003 大阪府大阪市淀川区富原3-5-36 新大阪

MTビル2号電話 06 (6350) 6868

## 正誤表

P.19

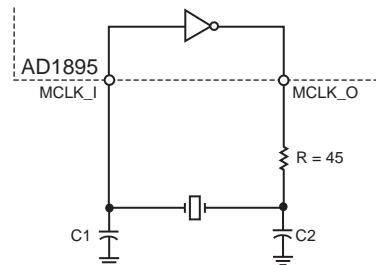

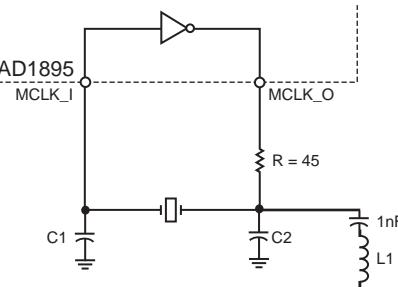

図 旧) Figure 9a, Figure 9b 共に  $R=45\Omega$

新) Figure 9a, Figure 9b 共に  $R$

P.23

パッケージ図

旧) mm 以外のパッケージサイズも記載

新) mm のサイズのみ記載 (英文 Rev B データシート P.23 参照)

アナログ・デバイセズ株式会社

本 社／〒105-6891 東京都港区海岸 1-16-1 ニューピア竹

芝サウスタワービル

電話 03 (5402) 8200

大阪営業所／〒532-0003 大阪府大阪市淀川区富原 3-5-36 新大

阪 MT ビル 2 号

電話 06 (6350) 6868

## 特長

サンプリング周波数自動検出

プログラミングが不要

サンプル・クロックのジッタを低減

入力電圧：3.3～5V、コア電源電圧：3.3V

16 / 18 / 20 / 24ビットのデータを入力可能

最大サンプル・レート：192kHz + 12%

入力 / 出力サンプル・レート比：7.75 : 1 ~ 1 : 8

バイパス・モード

複数のAD1895のTDMディジーチェーン接続モード

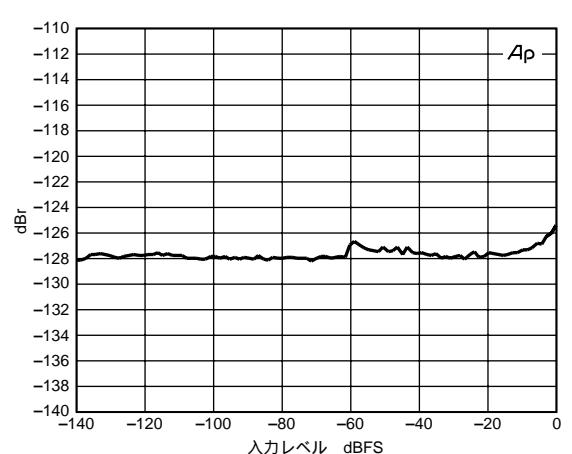

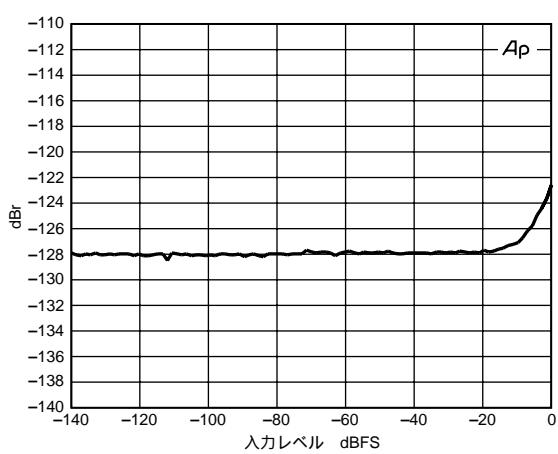

S/N比とダイナミックレンジ（Aウェイト、帯域20Hz ~ 20kHz）：128dB

THD + N：最大-122dB

線形位相FIRフィルタ

ハードウェア制御可能なソフト・ミュート

マスター・モード・クロック：256 ×  $f_s$ 、512 ×  $f_s$ 、768 ×  $f_s$  をサポート

フレキシブルな3線式シリアル・データ・ポート

左詰め、I<sup>2</sup>S、右詰め（16、18、20、24ビット）、TDMシリアル・ポートの各モードをサポート

マスター / スレーブ入出力モード

28ピンSSOPプラスチック・パッケージ

## アプリケーション

ホーム・シアターシステム、車載オーディオ・システム、DVD、DVD-R、CD-R、セット・トップ・ボックス、デジタル・オーディオ・エフェクト・プロセッサ

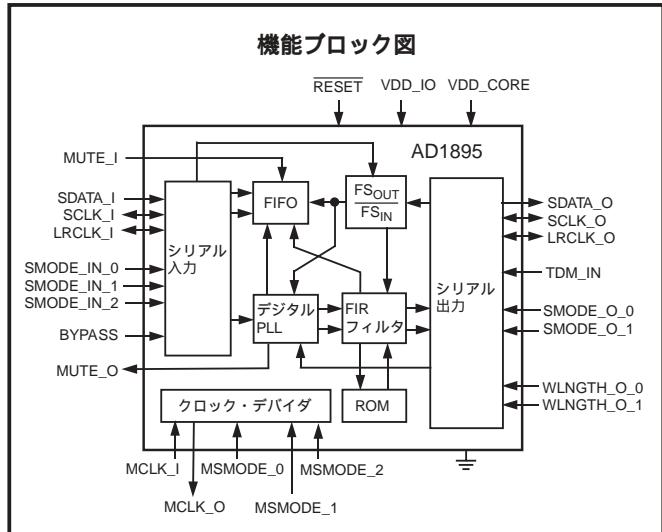

## 概要

AD1895は、第2世代の24ビット高性能ワンチップ非同期サンプル・レート・コンバータです。アナログ・デバイセズの最初の非同期サンプル・レート・コンバータAD1890での経験に基づき、AD1895はさらに性能を改善し、機能を追加しています。サンプル・レートと入力周波数によりTHD + Nは-115dB~-122dB、ダイナミックレンジは128dB（Aウェイト）、入力および出力のサンプル・レート周波数は192kHz、アップサンプリング比は1:8、ダウンサンプリング比は7.75:1に、それぞれ改善され、ジッタ除去特性も向上しています。より多くのシリアル・フォーマット、バイパス・モード、DSPに対するインターフェースなどが追加されています。

AD1895は、シリアル入力 / 出力ポートに3線式インターフェースを採用しており、左詰め、I<sup>2</sup>S、右詰め（16、18、20、24ビット）の各モードをサポートしています。さらに、シリアル出力ポートでは、DSPにディジーチェーン接続された複数のAD1895のためにTDMモードをサポートしています。シリアル出力データは20、18または16ビット出力データが選択

\*特許申請中。

REV.0

アナログ・デバイセズ株式会社

されたとき、ディザ処理された後、それぞれ20、18または16ビットに切りつめられます。

AD1895のサンプル・レートは、シリアル入力ポートからのデータをシリアル出力ポートのサンプル・レートに変換します。シリアル入力ポートのサンプル・レートは、出力シリアル・ポートの出力サンプル・レートに対して非同期にすることができます。AD1895に入力されるマスター・クロックMCLKは、シリアル入力 / 出力ポートの両方に対して非同期にできます。

MCLKは、チップ外部の発振器またはAD1895の内蔵マスター・クロック発振器で発生させることができます。MCLKは入力または出力シリアル・ポートに対して非同期にできるため、水晶を使ってMCLKを内部で生成させることでボード上のノイズとEMIの放出を低減することができます。MCLKが出力または入力シリアル・ポートに同期する場合は、AD1895をマスター・モードに設定することができます。このモードでは、MCLKを分周して、MCLKに同期するシリアル・ポートのL / Rクロックとビット・クロックを生成します。AD1895は、入力 / 出力の両方のシリアル・ポートに対してマスター・モードで256 ×  $f_s$ 、512 ×  $f_s$ 、768 ×  $f_s$ をサポートします。

AD1895の動作は概念的には、シリアル入力データを2<sup>20</sup>のレートで補間し、その補間したデータ・ストリームを出力サンプル・レートでサンプルしていると理解することができます。実際には、2<sup>20</sup>多相ステージの64タップFIRフィルタ、FIFO、入力サンプルと出力サンプル間の時間差を5ps以内で計測するデジタル・サーボ・ループと、サンプル・レート比を追跡するデジタル回路を使って、補間と出力サンプリングを行います。動作原理のセクションを参照してください。このデジタル・サーボ・ループとサンプル・レート回路は、入力と出力のサンプル・レートを自動的に追跡します。

（15ページに続く）

アナログ・デバイセズ社が提供する情報は正確で信頼できるものを期していますが、その情報の利用または利用したことにより引き起こされる第3者の特許または権利の侵害に関して、当社はいっさいの責任を負いません。さらに、アナログ・デバイセズ社の特許または特許の権利の使用を許諾するものではありません。

# AD1895 - 仕様

特に指示のない限り、以下のテスト条件によります。

電源電圧

|            |                         |

|------------|-------------------------|

| VDD_CORE   | 3.3V                    |

| VDD_IO     | 5.0Vまたは3.3V             |

| 周囲温度       | 25                      |

| 入力クロック     | 30.0MHz                 |

| 入力信号       | 1.000kHz、0dBFS          |

| 測定帯域幅      | 20 ~ $f_{s\_OUT}$ / 2Hz |

| ワード幅       | 24ビット                   |

| 負荷容量       | 50pF                    |

| ハイ・レベル入力電圧 | 2.4V                    |

| ロー・レベル入力電圧 | 0.8V                    |

仕様は予告なく変更されることがあります。

## デジタル性能 (VDD\_CORE = 3.3V ± 5%、VDD\_IO = 5.0V ± 10%)

| パラメータ                                           | Min   | Typ                                     | Max | 単位  |

|-------------------------------------------------|-------|-----------------------------------------|-----|-----|

| 分解能                                             | 24    |                                         |     | ビット |

| サンプル・レート (MCLK_I = 30MHzの時)                     | 6     | 215                                     |     | kHz |

| サンプル・レート (他のマスター・クロック使用時)                       |       | MCLK_I/5000 ≤ $f_{s\_OUT}$ ≤ MCLK_I/138 |     | kHz |

| サンプル・レート比                                       |       |                                         |     |     |

| アップサンプリング                                       |       | 1:8                                     |     |     |

| ダウンサンプリング (短いIGRPDLYS)                          |       | 7.75:1                                  |     |     |

| ダウンサンプリング (長いIGRPDLYS)                          |       | 7.0:1                                   |     |     |

| ダイナミックレンジ <sup>2</sup>                          |       |                                         |     |     |

| (20Hz ~ $f_{s\_OUT}$ / 2、1kHz、-60dBFS入力) Aウェイト  |       |                                         |     |     |

| 44.1kHz : 48kHz                                 | 128   |                                         |     | dB  |

| 48kHz : 44.1kHz                                 | 128   |                                         |     | dB  |

| 48kHz : 96kHz                                   | 128   |                                         |     | dB  |

| 44.1kHz : 192kHz                                | 128   |                                         |     | dB  |

| 96kHz : 48kHz                                   | 127   |                                         |     | dB  |

| 192kHz : 32kHz                                  | 127   |                                         |     | dB  |

| (20Hz ~ $f_{s\_OUT}$ / 2、1kHz、-60dBFS入力) フィルタなし |       |                                         |     |     |

| 44.1kHz : 48kHz                                 | 125   |                                         |     | dB  |

| 48kHz : 44.1kHz                                 | 125   |                                         |     | dB  |

| 48kHz : 96kHz                                   | 125   |                                         |     | dB  |

| 44.1kHz : 192kHz                                | 125   |                                         |     | dB  |

| 96kHz : 48kHz                                   | 124   |                                         |     | dB  |

| 192kHz : 32kHz                                  | 124   |                                         |     | dB  |

| 全高調波歪み + ノイズ <sup>2</sup>                       |       |                                         |     |     |

| (20Hz ~ $f_{s\_OUT}$ / 2、1kHz、0dBFS入力) フィルタなし   |       |                                         |     |     |

| ワースト・ケース (48kHz : 96kHz) <sup>3</sup>           | - 115 |                                         |     | dB  |

| 44.1kHz : 48kHz                                 | - 120 |                                         |     | dB  |

| 48kHz : 44.1kHz                                 | - 119 |                                         |     | dB  |

| 48kHz : 96kHz                                   | - 118 |                                         |     | dB  |

| 44.1kHz : 192kHz                                | - 120 |                                         |     | dB  |

| 96kHz : 48kHz                                   | - 122 |                                         |     | dB  |

| 192kHz : 32kHz                                  | - 122 |                                         |     | dB  |

| チャンネル間ゲイン・ミスマッチ                                 | 0.0   |                                         |     | dB  |

| チャンネル間位相偏差                                      | 0.0   |                                         |     | 度   |

| ミュート減衰量 (24ビット・ワード幅)                            | - 127 |                                         |     | dB  |

### 注

- この式で与えられるサンプリング・レートより低いレートも可能ですが、ジッタ除去性能が低下します。

- 広い範囲の入力 / 出力サンプル・レートでのDNRとTHD+Nの値については、代表的な性能特性を参照してください。

- 他の比では、最小THD+Nは-115dBより良くなります。詳細は性能曲線をご覧ください。

仕様は予告なく変更されることがあります。

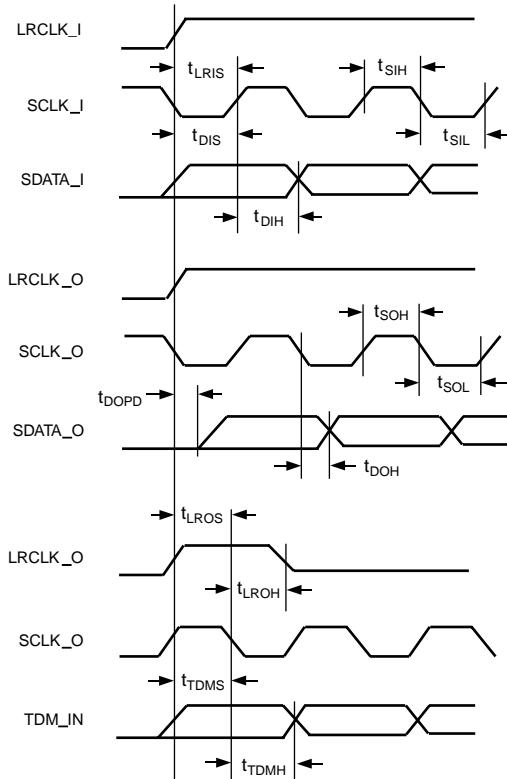

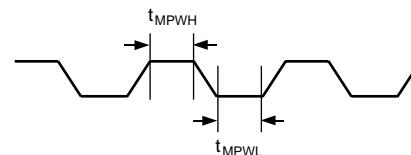

デジタル・タイミング (  $-40 < T_A < +105$  、  $VDD_{CORE} = 3.3V \pm 5\%$ 、  $VDD_{IO} = 5.0V \pm 10\%$  )

| パラメータ                   |                                      | Min  | Max                 | 単位  |

|-------------------------|--------------------------------------|------|---------------------|-----|

| $t_{MCLKI}$             | MCLK_I周期                             | 33.3 |                     | ns  |

| $f_{MCLK}$              | MCLK_I周波数                            |      | 30.0 <sup>2,3</sup> | MHz |

| $t_{MPWH}$              | MCLK_Iハイ・レベル・パルス幅                    | 8    |                     | ns  |

| $t_{MPWL}$              | MCLK_Iロー・レベル・パルス幅                    | 12   |                     | ns  |

| <b>入力シリアル・ポートのタイミング</b> |                                      |      |                     |     |

| $t_{LRIS}$              | SCLK_I前のLRCLK_Iセットアップ・タイム            | 8    |                     | ns  |

| $t_{SIH}$               | SCLK_Iハイ・レベル・パルス幅                    | 8    |                     | ns  |

| $t_{SIL}$               | SCLK_Iロー・レベル・パルス幅                    | 8    |                     | ns  |

| $t_{DIS}$               | SCLK_I立ち上がりエッジ前のSDATA_Iセットアップ・タイム    | 8    |                     | ns  |

| $t_{DIH}$               | SCLK_I立ち上がりエッジ後のSDATA_Iホールド・タイム      | 3    |                     | ns  |

| <b>出力シリアル・ポートのタイミング</b> |                                      |      |                     |     |

| $t_{TDMS}$              | SCLK_O立ち上がりエッジ前のTDM_INセットアップ・タイム     | 3    |                     | ns  |

| $t_{TDMH}$              | SCLK_O立ち上がりエッジ後のTDM_INホールド・タイム       | 3    |                     | ns  |

| $t_{DOPD}$              | SCLK_O、LRCLK_OからのSDATA_Oの伝搬遅延        |      | 20                  | ns  |

| $t_{DOH}$               | SCLK_O後のSDATA_Oホールド・タイム              | 3    |                     | ns  |

| $t_{LROS}$              | SCLK_O前のLRCLK_Oセットアップ・タイム (TDMモードのみ) | 5    |                     | ns  |

| $t_{LROH}$              | SCLK_O後のLRCLK_Oホールド・タイム (TDMモードのみ)   | 3    |                     | ns  |

| $t_{SOH}$               | SCLK_Oハイ・レベル・パルス幅                    | 10   |                     | ns  |

| $t_{SOL}$               | SCLK_Oロー・レベル・パルス幅                    | 5    |                     | ns  |

| $t_{RSTL}$              | RESETロー・レベル・パルス幅                     |      | 200                 | ns  |

## 注

1 タイミング図を参照してください。

2 許容最大サンプル・レート :  $f_{SAMPLERATE} = f_{MCLK} / 138$ 3 以下の条件で最大34MHzの $f_{MCLK}$ が可能 :  $0 < T_A < 70$  、45 / 55以上のMCLK\_Iデューティ・サイクル

仕様は予告なく変更されることがあります。

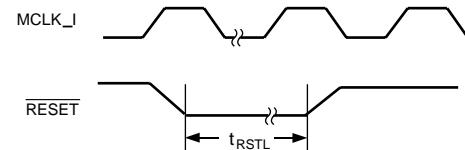

## タイミング図

図1. 入力 / 出力シリアル・ポートのタイミング

( SCLK\_I/O、LRCLK\_I/O、SDATA\_I/O、TDM\_IN )図2.  $\overline{RESET}$ のタイミング

図3. MCLK\_Iのタイミング

# AD1895 - 仕様

## デジタル・フィルタ (VDD\_CORE = 3.3V ± 5%、VDD\_IO = 5.0V ± 10%)

| パラメータ    | Min                 | Typ             | Max                 | 単位 |

|----------|---------------------|-----------------|---------------------|----|

| 通過帯域     |                     |                 | 0.4535 $f_{S\_OUT}$ | Hz |

| 通過帯域リップル |                     |                 | ± 0.016             | dB |

| 遷移帯域     | 0.4535 $f_{S\_OUT}$ |                 | 0.5465 $f_{S\_OUT}$ | Hz |

| 阻止帯域     | 0.5465 $f_{S\_OUT}$ |                 |                     | Hz |

| 阻止帯域減衰量  |                     | - 125           |                     | dB |

| 群遅延      |                     | 群遅延の式を参照してください。 |                     |    |

仕様は予告なく変更されることがあります。

## デジタルI/O特性 (VDD\_CORE = 3.3V ± 5%、VDD\_IO = 5.0V ± 10%)

| パラメータ                                                  | Min            | Typ            | Max | 単位 |

|--------------------------------------------------------|----------------|----------------|-----|----|

| ハイ・レベル入力電圧 (V <sub>IH</sub> )                          | 2.4            |                |     |    |

| ロー・レベル入力電圧 (V <sub>IL</sub> )                          |                |                | 0.8 | V  |

| 入力リーケ (I <sub>IH</sub> @ V <sub>IH</sub> = 5V)         |                |                | 2   | μA |

| 入力リーケ (I <sub>IL</sub> @ V <sub>IL</sub> = 0V)         |                |                | - 2 | μA |

| 入力容量                                                   |                | 5              | 10  | pF |

| ハイ・レベル出力電圧 (V <sub>OH</sub> @ I <sub>OH</sub> = - 4mA) | VDD_CORE - 0.5 | VDD_CORE - 0.4 |     | V  |

| ロー・レベル出力電圧 (V <sub>OL</sub> @ I <sub>OL</sub> = + 4mA) |                | 0.2            | 0.5 | V  |

| ハイ・レベル出力ソース電流 (I <sub>OH</sub> )                       |                |                | - 4 | mA |

| ロー・レベル出力シンク電流 (I <sub>OL</sub> )                       |                |                | + 4 | mA |

仕様は予告なく変更されることがあります。

## 電源

| パラメータ                  | Min      | Typ       | Max   | 単位 |

|------------------------|----------|-----------|-------|----|

| 電源電圧                   |          |           |       |    |

| VDD_CORE               | 3.135    | 3.3       | 3.465 | V  |

| VDD_IO*                | VDD_CORE | 3.3 / 5.0 | 5.5   | V  |

| アクティブ電源電流              |          |           |       |    |

| I_CORE_アクティブ           |          |           |       |    |

| 48kHz : 48kHz          |          | 20        |       | mA |

| 96kHz : 96kHz          |          | 26        |       | mA |

| 192kHz : 192kHz        |          | 43        |       | mA |

| I_IO_アクティブ             |          | 2         |       | mA |

| パワーダウン電源電流 : (全クロック停止) |          |           |       |    |

| I_CORE_PWRDN           |          | 0.5       |       | mA |

| I_IO_PWRDN             |          | 10        |       | μA |

\*3.3V入力の場合、VDD\_IO電源は3.3Vに設定する必要があります。ただし、VDD\_CORE電源電圧はVDD\_IOを超えることはできません。

仕様は予告なく変更されることがあります。

**電源** ( VDD\_CORE = 3.3V ± 5%、 VDD\_IO = 5.0V ± 10% )

| パラメータ                                                           | Min | Typ             | Max | 単位             |

|-----------------------------------------------------------------|-----|-----------------|-----|----------------|

| 全アクティブ消費電力<br>48kHz : 48kHz<br>96kHz : 96kHz<br>192kHz : 192kHz |     | 65<br>85<br>132 |     | mW<br>mW<br>mW |

| パワーダウン時の全消費電力 : ( RESET LO )                                    |     | 2               |     | mW             |

仕様は予告なく変更されることがあります。

**温度範囲**

| パラメータ                                        | Min | Typ                | Max            | 単位 |

|----------------------------------------------|-----|--------------------|----------------|----|

| 仕様保証<br>機能保証<br>保管<br>熱抵抗、 $J_A$ ( 接合部-周囲間 ) |     | 25<br>- 40<br>- 55 | + 105<br>+ 150 |    |

|                                              |     |                    | 109            | /W |

仕様は予告なく変更されることがあります。

**絶対最大定格\***

| パラメータ                    | Min            | Max                        | 単位           |

|--------------------------|----------------|----------------------------|--------------|

| 電源<br>VDD_CORE<br>VDD_IO | - 0.3<br>- 0.3 | + 3.6<br>+ 6.0             | V<br>V       |

| デジタル入力<br>入力電流<br>入力電圧   |                | + 10<br>DGND - 0.3<br>- 40 | mA<br>V<br>V |

| 周囲温度 ( 動作時 )             |                | + 105                      |              |

\*上記の絶対最大定格を超えるストレスを加えるとデバイスに永久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

**オーダー・ガイド**

| モデル         | 温度範囲         | パッケージ    | パッケージ・オプション         |

|-------------|--------------|----------|---------------------|

| AD1895YRS   | - 40 ~ + 105 | 28ピンSSOP | RS-28               |

| AD1895YRSRL | - 40 ~ + 105 | 28ピンSSOP | RS-28 ( 13インチ・リール ) |

**注意**

ESD ( 静電放電 ) の影響を受けやすいデバイスです。4000Vもの高圧の静電気が人体やテスト装置に容易に帯電し、検知されることなく放電されることがあります。本製品には当社独自のESD保護回路を備えていますが、高エネルギーの静電放電を受けたデバイスには回復不可能な損傷が発生することがあります。このため、性能低下や機能喪失を回避するために、適切なESD予防措置をとるようお奨めします。

# AD1895

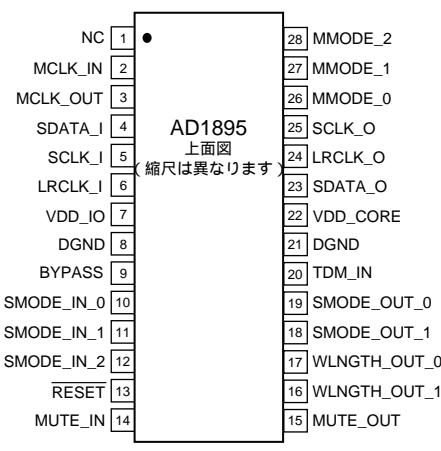

## ピン機能説明

| ピン番号 | 入/出力(IN/OUT) | 記号           | 説明                                           |

|------|--------------|--------------|----------------------------------------------|

| 1    | IN           | NC           | 未接続                                          |

| 2    | IN           | MCLK_IN      | マスタークロック入力または水晶入力                            |

| 3    | OUT          | MCLK_OUT     | マスター・クロック出力または水晶出力                           |

| 4    | IN           | SDATA_I      | (入力サンプル・レートでの)入力シリアル・データ                     |

| 5    | IN/OUT       | SCLK_I       | マスター/スレーブ入力のシリアル・ビット・クロック                    |

| 6    | IN/OUT       | LRCLK_I      | マスター/スレーブ入力のL/Rクロック                          |

| 7    | IN           | VDD_IO       | 3.3V/5Vの入力/出力デジタル電源ピン                        |

| 8    | IN           | DGND         | デジタル・グラウンド・ピン                                |

| 9    | IN           | BYPASS       | ASRC/バイパス・モード、アクティブ・ハイ                       |

| 10   | IN           | SMODE_IN_0   | 入力ポート・シリアル・インターフェース・モード・セレクト・ピン0             |

| 11   | IN           | SMODE_IN_1   | 入力ポート・シリアル・インターフェース・モード・セレクト・ピン1             |

| 12   | IN           | SMODE_IN_2   | 入力ポート・シリアル・インターフェース・モード・セレクト・ピン2             |

| 13   | IN           | RESET        | リセットピン、アクティブ・ロー                              |

| 14   | IN           | MUTE_IN      | ミュート入力ピン アクティブ・ハイ、通常MUTE_OUTに接続              |

| 15   | OUT          | MUTE_OUT     | 出力ミュート制御-アクティブ・ハイ                            |

| 16   | IN           | WLNGTH_OUT_1 | ハードウェア選択可能な出力ワード長 セレクト・ピン1                   |

| 17   | IN           | WLNGTH_OUT_0 | ハードウェア選択可能な出力ワード長 セレクト・ピン0                   |

| 18   | IN           | SMODE_OUT_1  | 出力ポート・シリアル・インターフェース・モード・セレクト・ピン1             |

| 19   | IN           | SMODE_OUT_0  | 出力ポート・シリアル・インターフェース・モード・セレクト・ピン0             |

| 20   | IN           | TDM_IN       | シリアル・データ入力* (デジーチェーン・モードの場合のみ) 未使用の場合はグラウンド。 |

| 21   | IN           | DGND         | デジタル・グラウンド・ピン                                |

| 22   | IN           | VDD_CORE     | 3.3Vデジタル電源ピン                                 |

| 23   | OUT          | SDATA_O      | (出力サンプル・レートでの)出力シリアル・データ                     |

| 24   | IN/OUT       | LRCLK_O      | マスター/スレーブ出力のL/Rクロック                          |

| 25   | IN/OUT       | SCLK_O       | マスター/スレーブ出力のシリアル・ビット・クロック                    |

| 26   | IN           | MMODE_0      | マスター/スレーブ・クロック比モード・セレクト・ピン0                  |

| 27   | IN           | MMODE_1      | マスター/スレーブ・クロック比モード・セレクト・ピン1                  |

| 28   | IN           | MMODE_2      | マスター/スレーブ・クロック比モード・セレクト・ピン2                  |

\*位相一致モード・データの入力にも使用。

## ピン配置

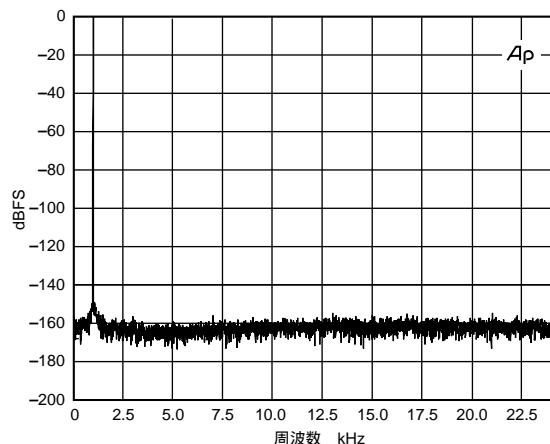

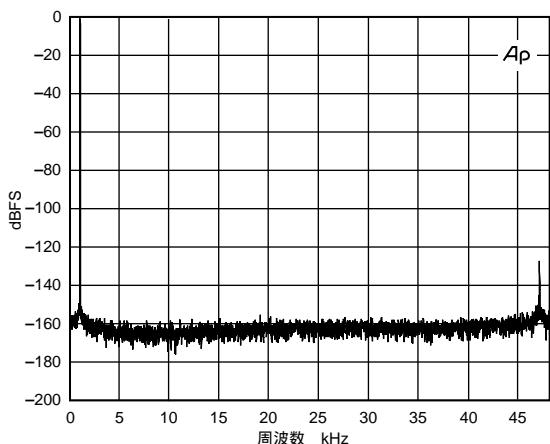

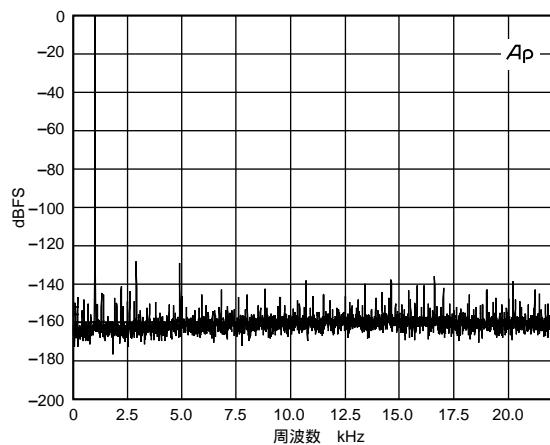

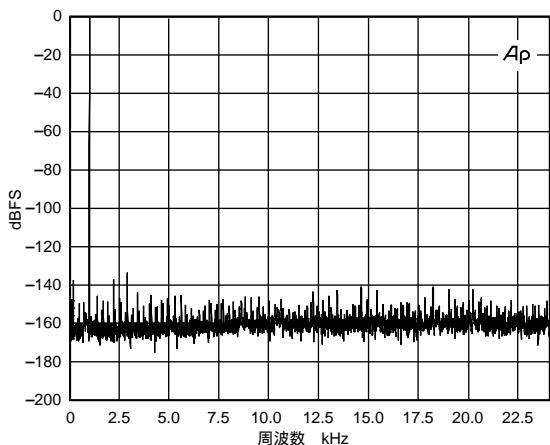

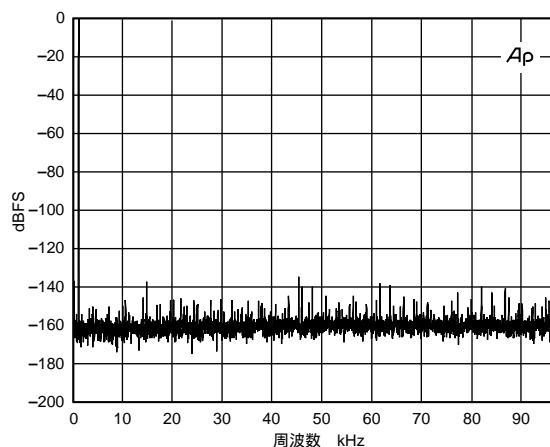

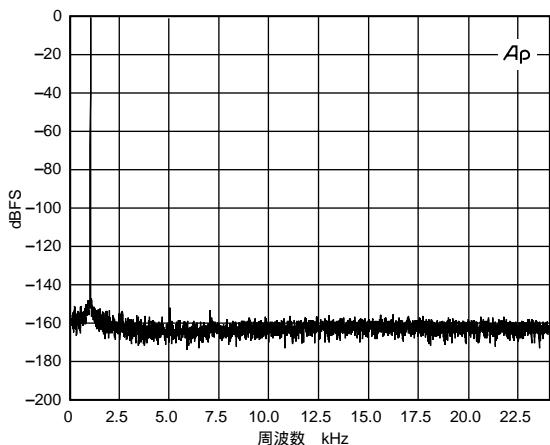

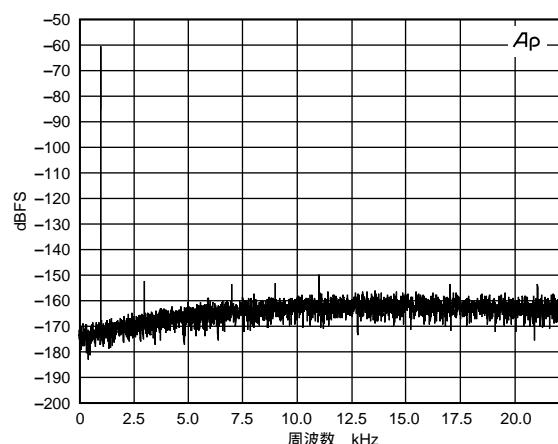

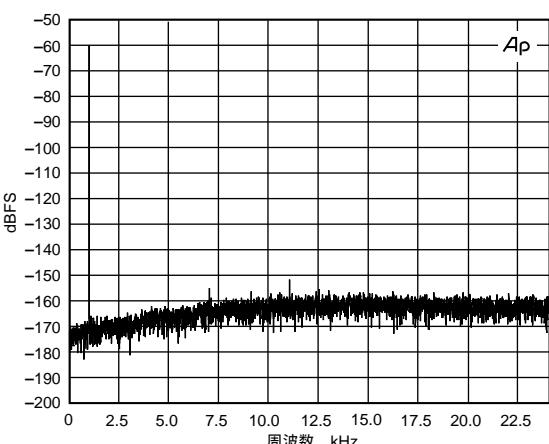

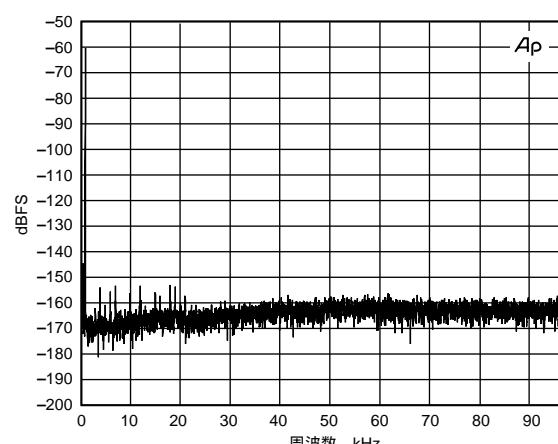

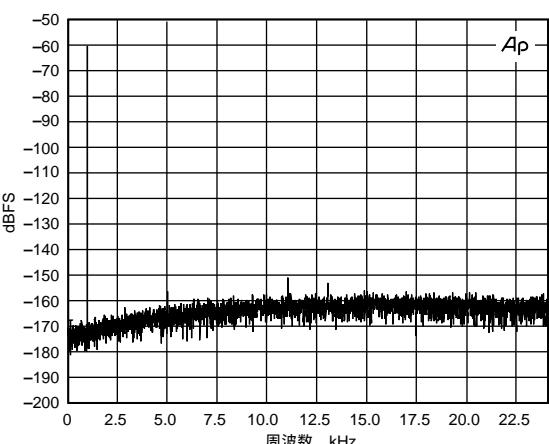

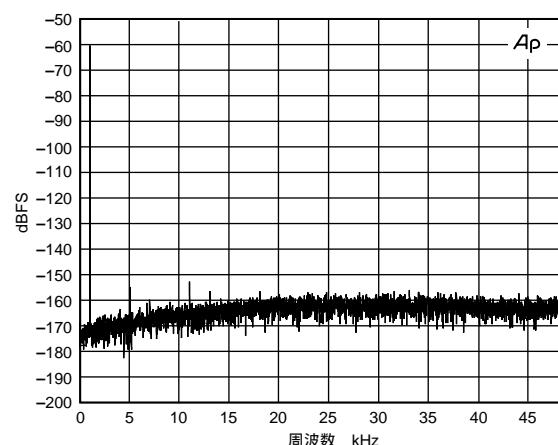

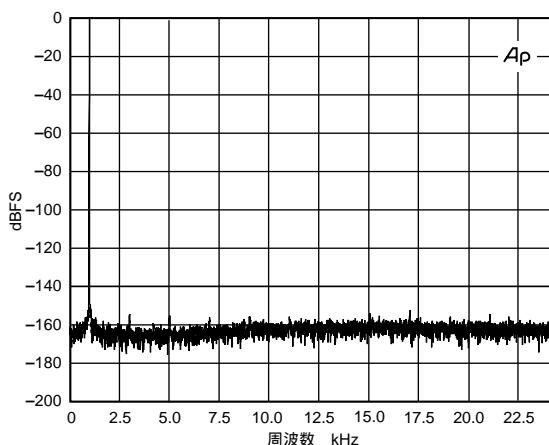

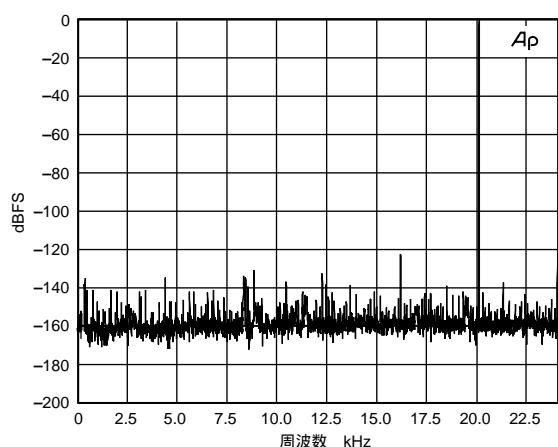

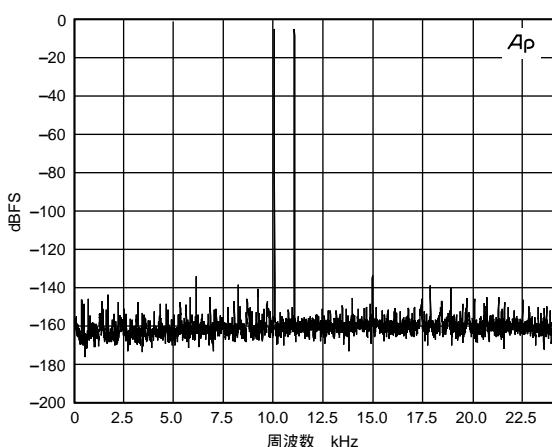

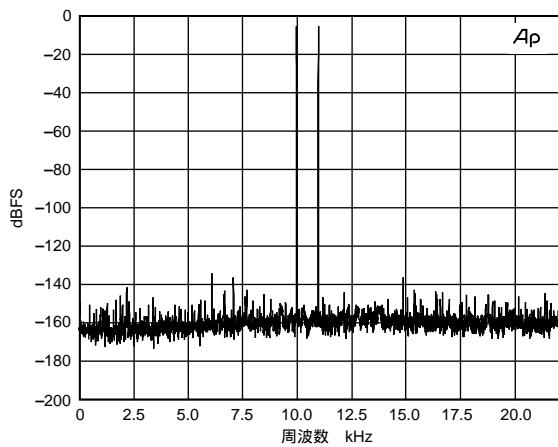

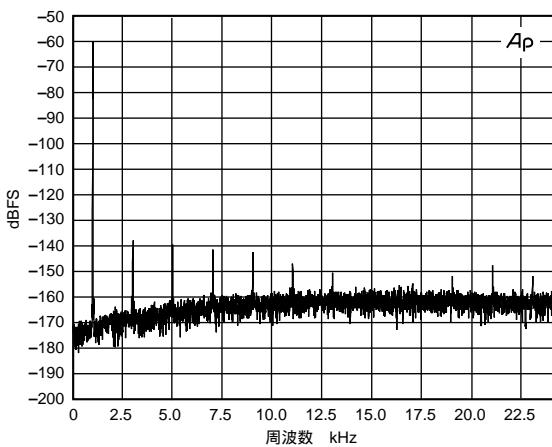

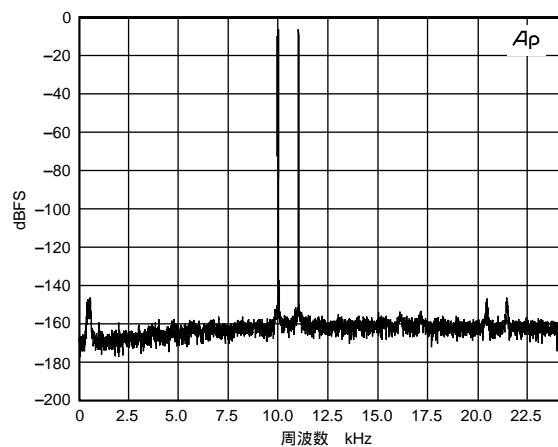

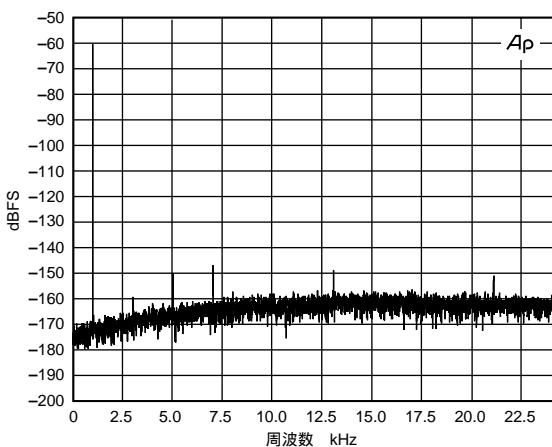

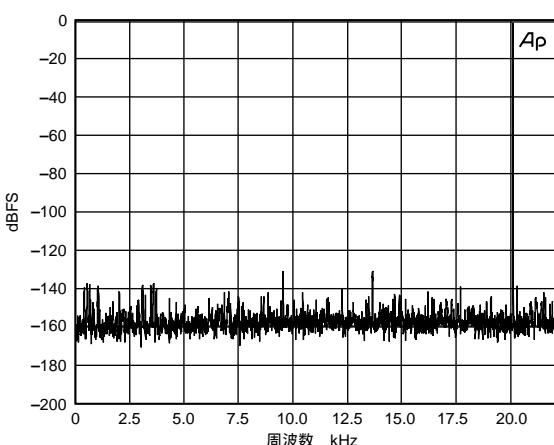

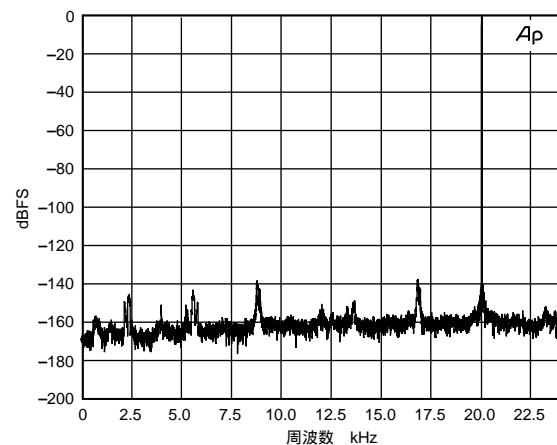

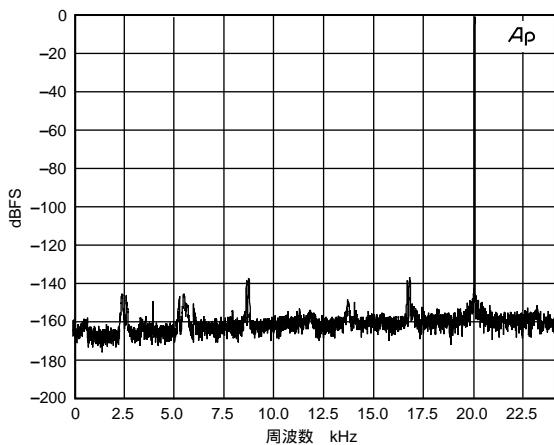

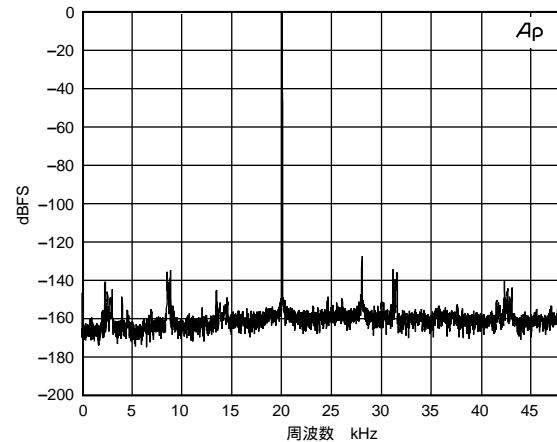

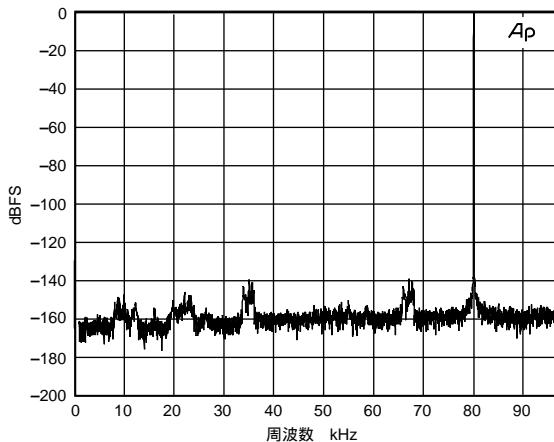

# 代表的な性能特性 - AD1895

# AD1895

# AD1895

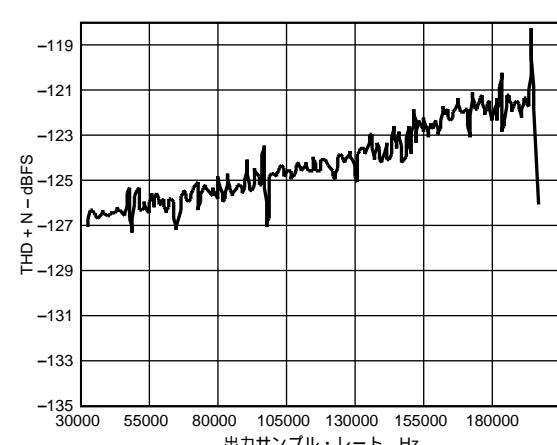

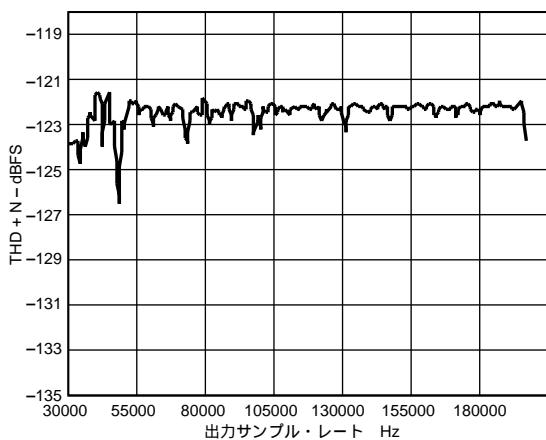

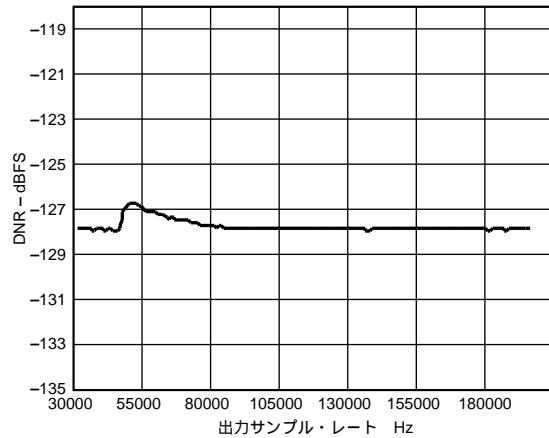

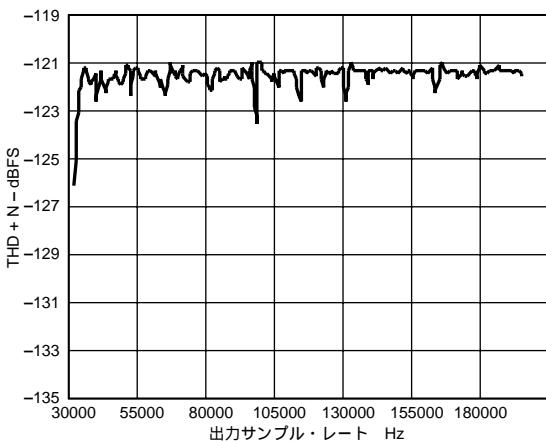

特性 25. THD + N対出力サンプル・レート、 $f_{S\_IN} = 48\text{kHz}$ 、

0dBFS 1kHzトーン

特性 28. THD + N対出力サンプル・レート、 $f_{S\_IN} = 96\text{kHz}$ 、0dBFS 1kHzトーン

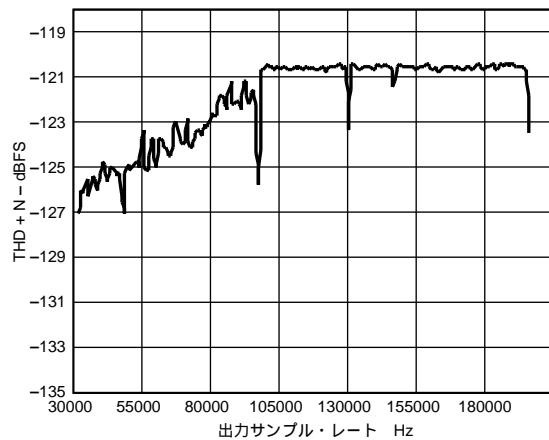

特性 26. THD + N対出力サンプル・レート、 $f_{S\_IN} = 44.1\text{kHz}$ 、0dBFS 1kHzトーン

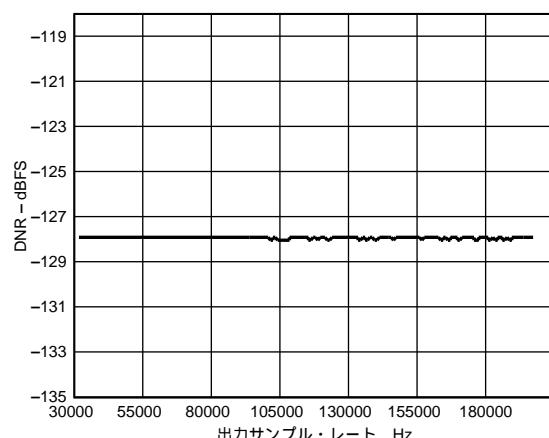

特性 29. DNR対出力サンプル・レート、 $f_{S\_IN} = 192\text{kHz}$ 、

-60dBFS 1kHzトーン

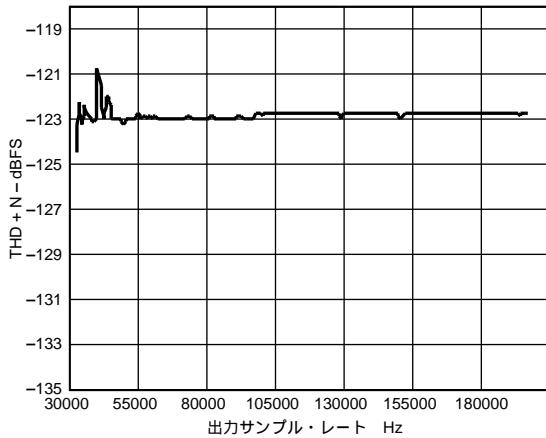

特性 27. THD + N対出力サンプル・レート、 $f_{S\_IN} = 32\text{kHz}$ 、

0dBFS 1kHzトーン

特性 30. DNR対出力サンプル・レート、 $f_{S\_IN} = 32\text{kHz}$ 、

-60dBFS 1kHzトーン

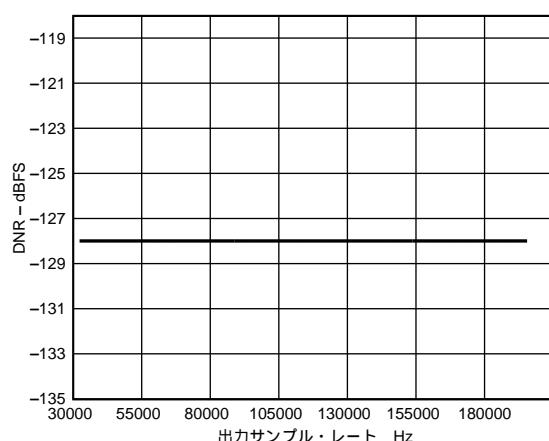

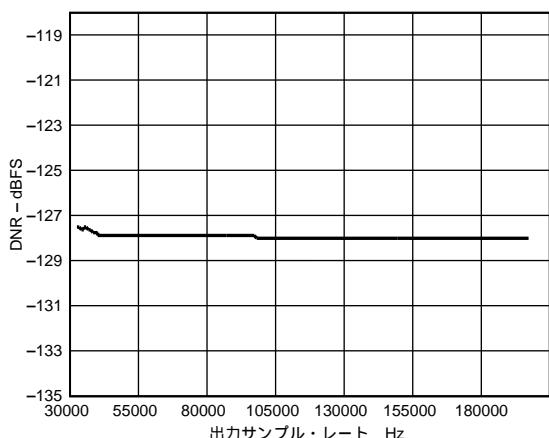

# AD1895

特性 31. DNR対出力サンプル・レート、 $f_{S\_IN} = 96\text{kHz}$ 、

- 60dBFS 1kHzトーン

特性 34. DNR対出力サンプル・レート、 $f_{S\_IN} = 44.1\text{kHz}$ 、- 60dBFS 1kHzトーン

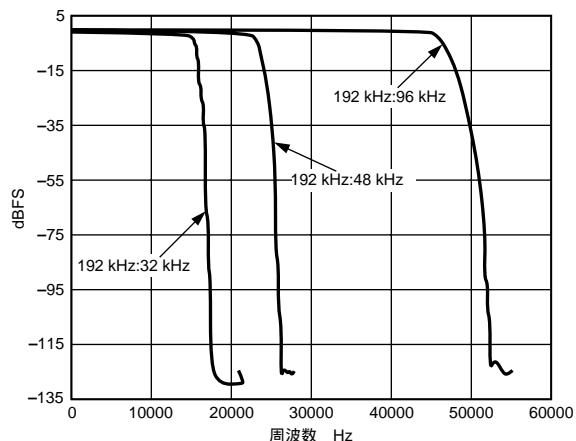

特性 32. デジタル・フィルタ周波数応答

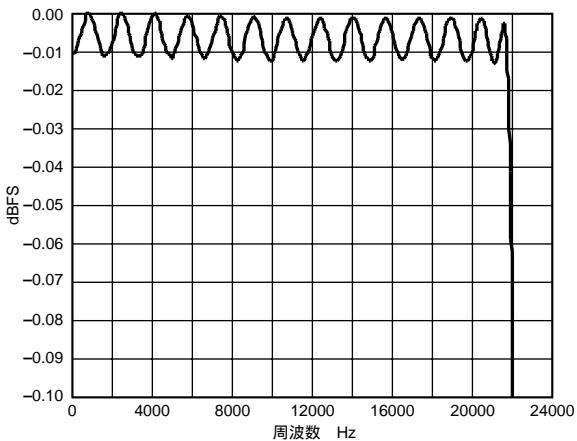

特性 35. 通過帯域リップル、192kHz : 48kHz

特性 33. DNR対出力サンプル・レート、 $f_{S\_IN} = 48\text{kHz}$ 、- 60dBFS 1kHzトーン

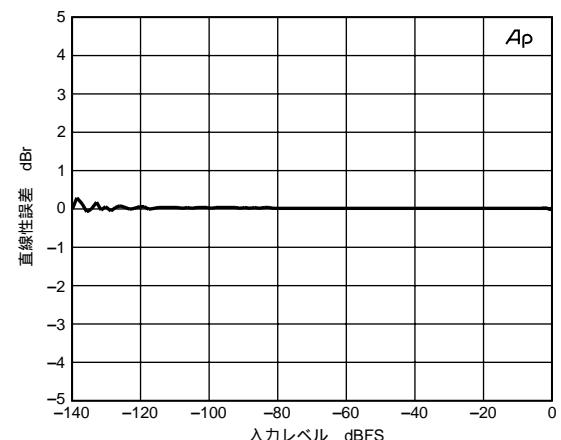

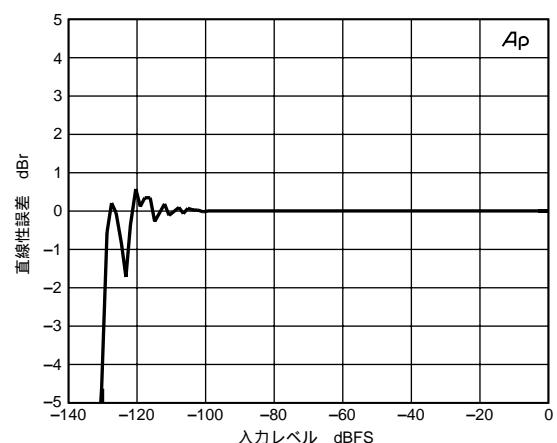

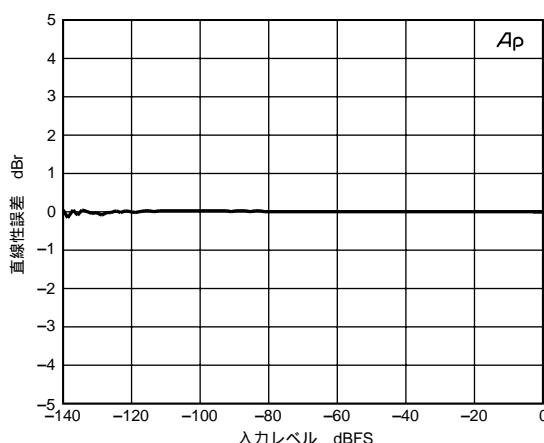

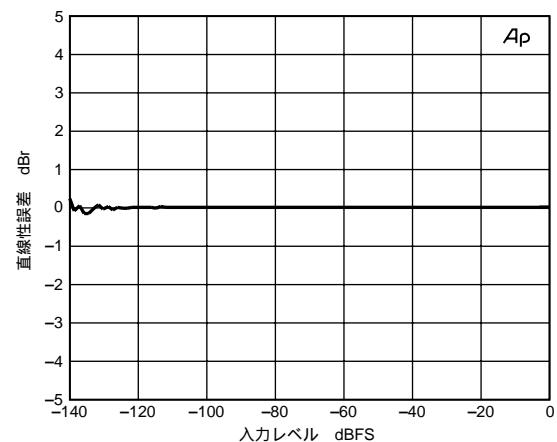

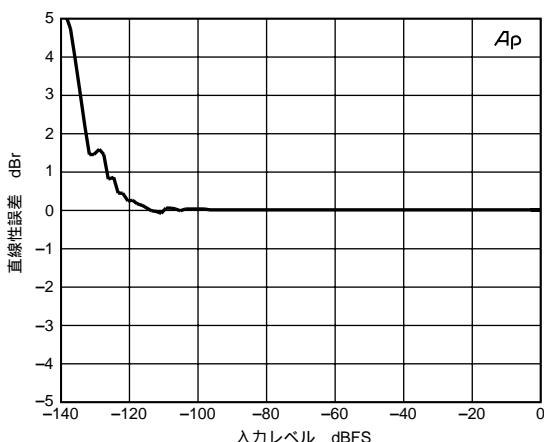

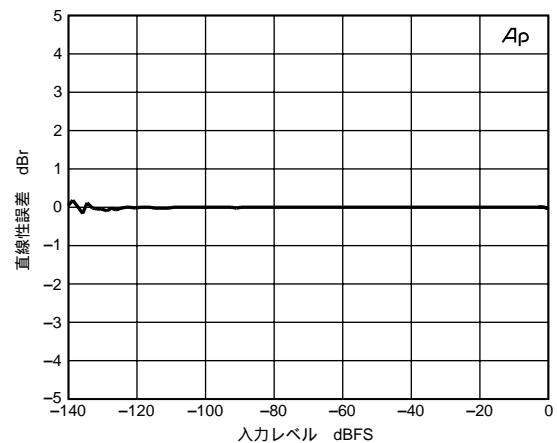

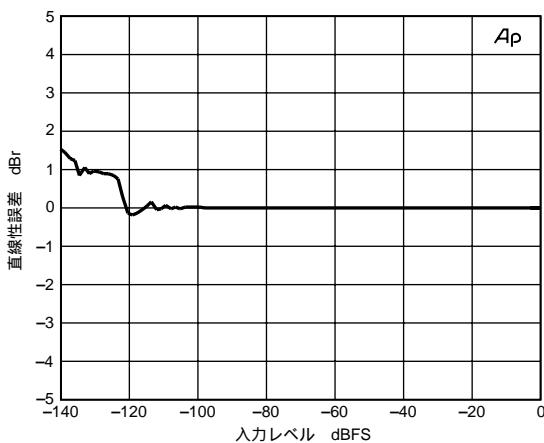

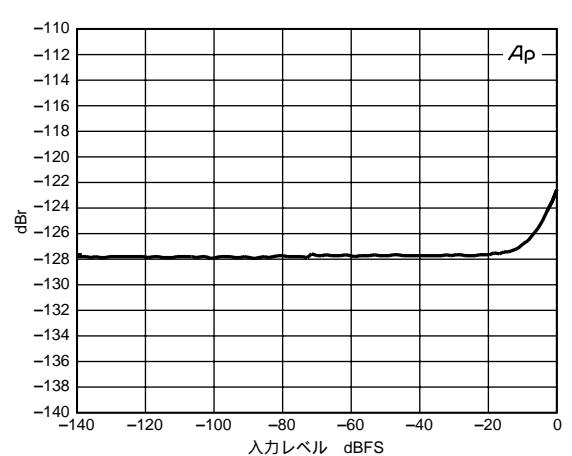

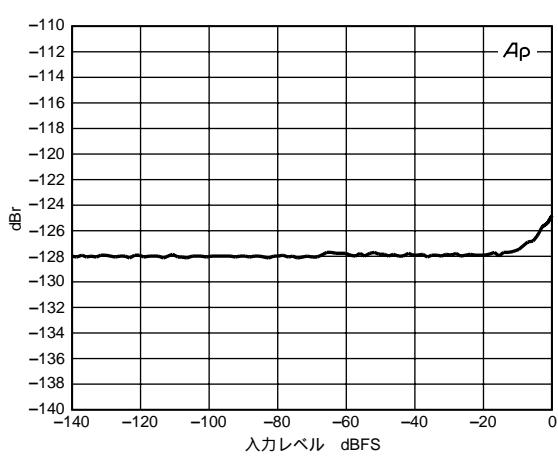

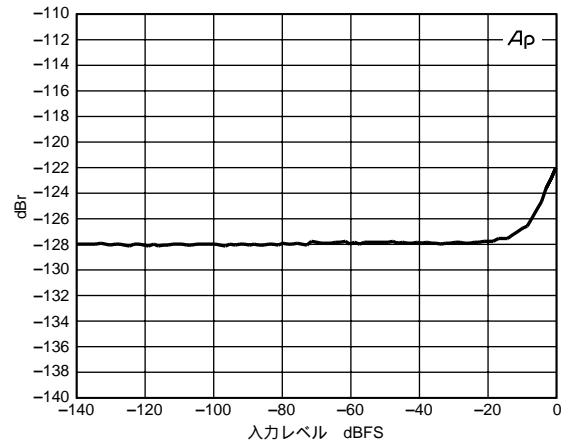

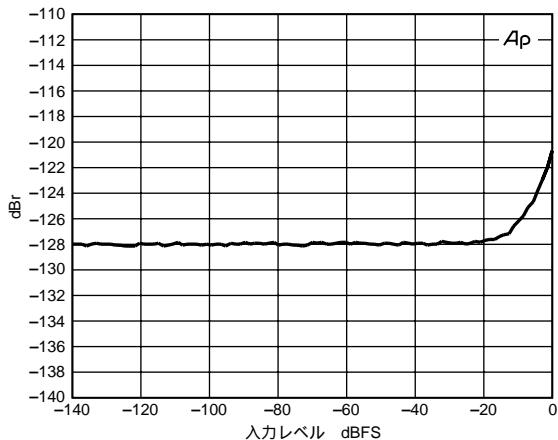

特性 36. 直線性誤差、48kHz : 48kHz、

0 ~ - 140dBFS入力、200Hzトーン

# AD1895

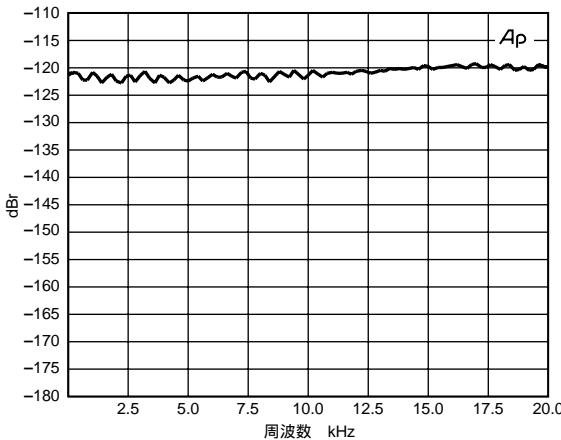

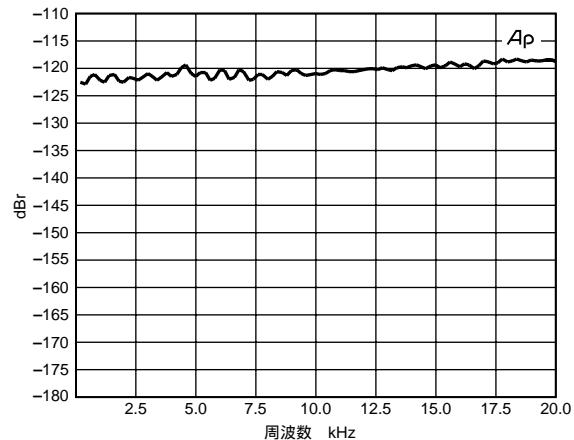

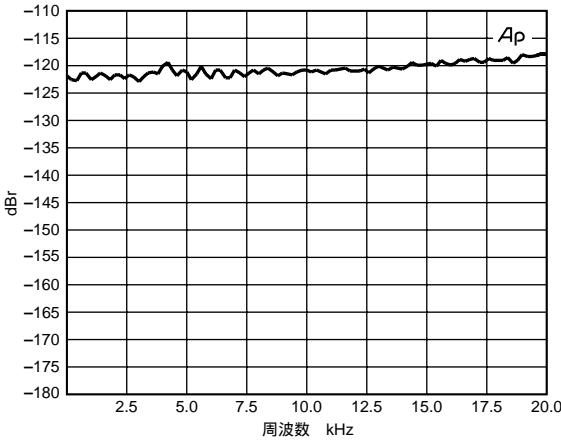

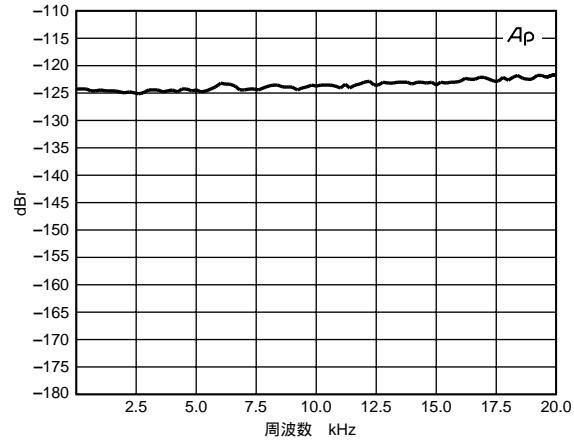

特性 49. THD + N対入力周波数、48kHz : 44.1kHz、0dBFS

特性 51. THD + N対入力周波数、48kHz : 96kHz、0dBFS

特性 50. THD + N対入力周波数、44.1kHz : 48kHz、00dBFS

特性 52. THD + N対入力周波数、96kHz : 48kHz、0dBFS

(1ページからの続き)

デジタル・サーボ・ループは、入力と出力のサンプル・レート間の時間差を5ps以内で計測します。これは、多相フィルタの正しい係数を選択するのに必要です。このデジタル・サーボ・ループは、入／出力サンプル・レートおよびマスター・クロックに対して、優れたジッタ除去能力を持っています。ジッタ除去は1Hz未満で開始されますが、このため、RESETが解除されたとき、あるいは入力または出力サンプル・レートが変更されたときに、長いセトリング・タイムを必要とします。セトリング・タイムを短くするため、RESETの解除時またはサンプル・レートの変化時に、デジタル・サーボ・ループは高速セトリング・モードに入ります。高速モードでデジタル・サーボ・ループが適正に整定すると、ノーマル・モードまたは低速セトリング・モードに切り替わり、入力と出力のサンプル・レート間の時間差計測値が5ps内に収まるまで整定動作を続けます。高速

モードでは、MUTE\_OUT信号がハイ・レベルにアサートされます。通常、MUTE\_OUTはMUTE\_INピンに接続されます。MUTE\_IN信号は、アサート時にAD1895をソフトにミュートさせ、アサート解除時にAD1895をミュートからソフトに回復させるときに使われます。

AD1895のサンプル・レート・コンバータは、バイパス・モードを使うとすべてバイパスさせることができます。バイパス・モードでは、AD1895のシリアル入力データは、ディザ処理されることなく直接シリアル出力ポートに接続されます。この機能は、非オーディオ・データを通過させとき、または入力と出力のサンプル・レートが互いに同期してサンプル・レート比がちょうど1:1のときに便利です。

AD1895は3.3Vと5Vの入力をサポートし、28ピンSSOP SMDパッケージを採用しています。AD1895は、VDD\_IO電源ピンに5Vを接続する場合のみ、5V入力をサポートします。

# AD1895

## 非同期サンプル・レート変換 (ASRC) の機能概要

### 動作原理

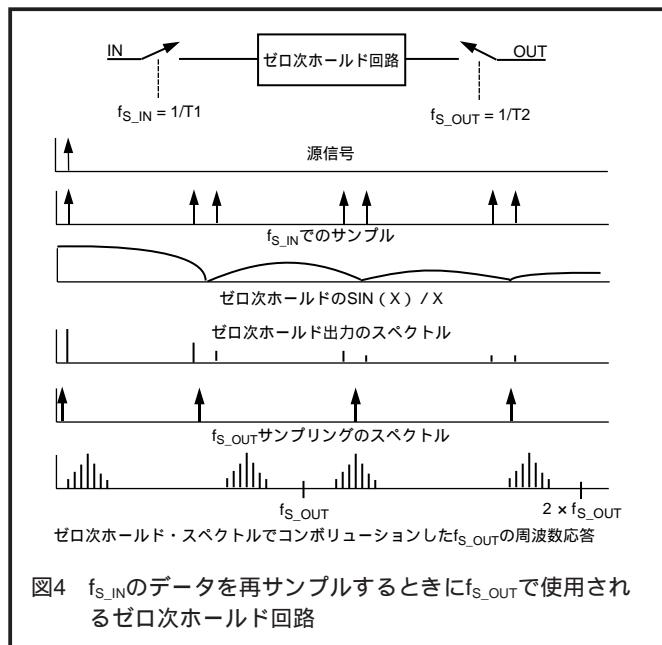

ASRCは、あるサンプル・レートのクロック・ソースを使うデータを、同一または異なるサンプル・レートで動作する別のクロック・ソースを使うデータに変換します。非同期サンプル・レート変換の最も単純な手法は、2個のサンプル回路の間にゼロ次ホールド回路を使う方法です（図4）。非同期システムでは、T2はT1に等しくなることはなく、T2とT1の比は有限小数にもなりません。そのため、 $f_{S\_OUT}$ でのサンプルは繰り返しや省略が行われて、再サンプリング過程で誤差が発生します。 $f_{S\_OUT}$ でのサンプリングが、ゼロ次ホールドの $\sin(x)/x$ の性質に起因する減衰したイメージとコンボリューションされたときに、この誤差により周波数領域ではサイド・ロープが広がります。ゼロ次ホールドの $f_{S\_IN}$ におけるイメージすなわちDC信号イメージは、無限に減衰されます。T2とT1の比が無限小数値であるため、 $f_{S\_OUT}$ での再サンプリングにより発生する誤差は除去することはできません。ただし、誤差は $f_{S\_IN}$ での入力データの補間により、大幅に小さくすることができます。AD1895は概念的には係数 $2^{20}$ で補間されています。

### 概念的な高比率補間モデル

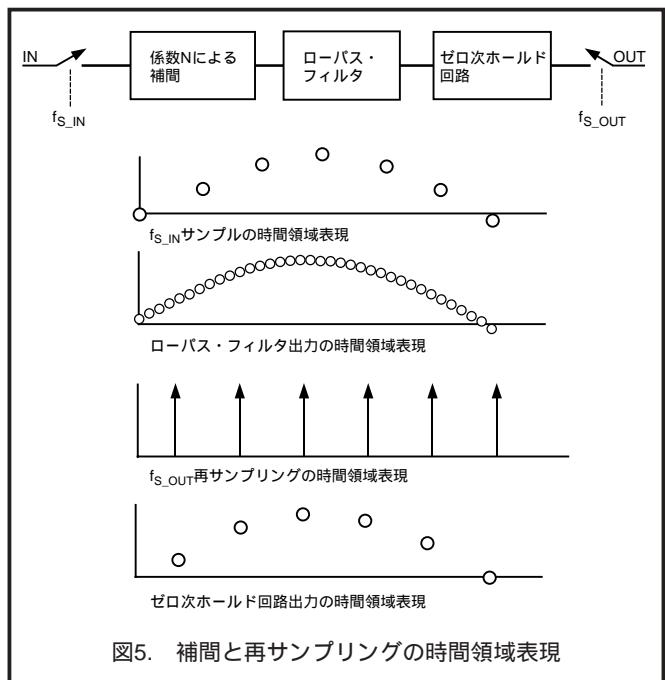

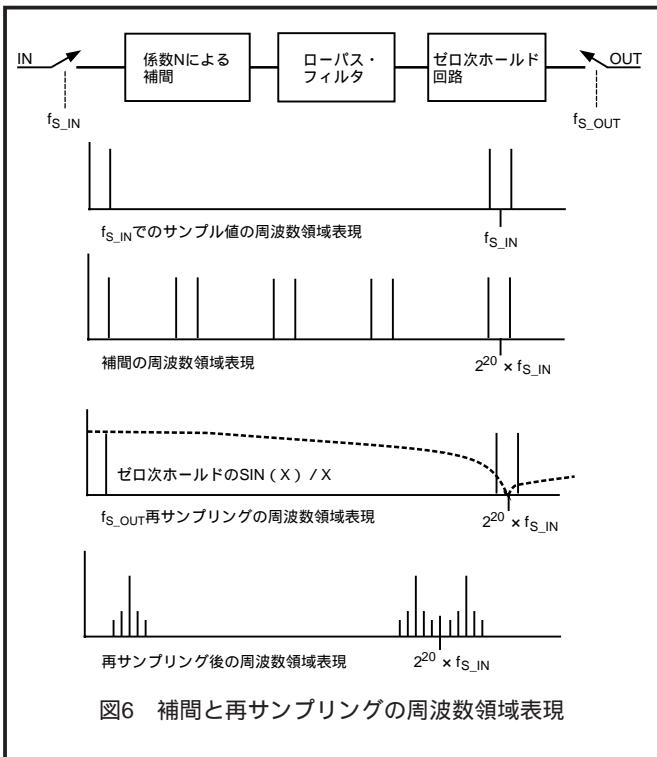

係数 $2^{20}$ によって行われる入力データの補間では、各 $f_{S\_IN}$ サンプルの間に $(2^{20} - 1)$ 個のサンプルを配置します。図5に、時間領域と周波数領域における係数 $2^{20}$ での補間を示します。係数 $2^{20}$ での補間は、概念的には、各 $f_{S\_IN}$ サンプル間に $(2^{20} - 1)$ 個のゼロ値サンプルを詰込み、この補間された信号をデジタル・ローパス・フィルタとコンボリューションしてイメージを減衰させるものと理解できます。時間領域では、ゼロ次ホールド回路から出力される $f_{S\_IN} \times 2^{20}$ サンプルの最も近い値を $f_{S\_OUT}$ で選択するものと見なせます。これは補間を行わない場合に $f_{S\_IN}$ サンプルから隣の値を選択するのと対照的です。これにより、再サンプリング誤差を大幅に削減できます。

周波数領域（図6）では、補間によりゼロ次ホールド回路の周波数軸が引き伸ばされます。補間後のイメージは適切なローパス・フィルタによって十分に減衰させることができます。ゼロ次ホールド回路からのイメージは、ゼロ次ホールド回路の無限減衰ポイントに向かって $2^{20}$ だけ（ $f_{S\_IN} \times 2^{20}$ ）移動されます。ゼロ次ホールド回路のイメージは、 $f_{S\_OUT}$ 出力の忠実度にとって決定的な要因です。ワーストケースのイメージは、ゼロ次ホールド回路の周波数応答から、最大イメージ =  $\sin(\pi F / f_{S\_INTERP}) / (\pi F / f_{S\_INTERP})$ として計算することができます。Fはワーストケース・イメージの周波数で $2^{20} \times f_{S\_IN} \pm f_{S\_IN} / 2$ に等しく、 $f_{S\_INTERP}$ は $f_{S\_IN} \times 2^{20}$ です。

$f_{S\_IN} = 192\text{kHz}$ の場合、次のワーストケース・イメージが発生します。

$$f_{S\_INTERP} - 96\text{kHz} \text{でのイメージ} = -125.1\text{dB}$$

$$f_{S\_INTERP} + 96\text{kHz} \text{でのイメージ} = -125.1\text{dB}$$

図6 補間と再サンプリングの周波数領域表現

## ハードウェア・モデル

図5のローパス・フィルタの出力レートは、補間レート $2^{20} \times 192000\text{kHz} = 201.3\text{GHz}$ になります。サンプリング・レート $201.3\text{GHz}$ は明らかに非現実的であり、補間された各サンプルを計算するのに必要なタップ数についても同様です。ただし、係数 $2^{20}$ の補間では $2^{20}-1$ 個のゼロ・サンプルを各 $f_{s\_IN}$ サンプルの間に詰め込むため、ローパスFIRフィルタ内の大部分の乗算はゼロになります。補間されたサンプルを $f_{s\_OUT}$ レートの出力で1個だけ取り出すだけで良いため、 $2^{20}$ 回のコンボリューションの代わりに、各 $f_{s\_OUT}$ 周期ごとに1回だけコンボリューションすればよいことを利用すると、さらに簡素化することができます。各 $f_{s\_OUT}$ サンプルに64タップFIRフィルタを使用すると、補間に起因するイメージを効果的に減衰することができます。

上の手法での難しい点は、 $f_{s\_OUT}$ のタイミングで正しい補間サンプルを選択する必要があります。 $f_{s\_OUT}$ 周期ごとに $2^{20}$ 回のコンボリューションが実行されることになるため、 $f_{s\_OUT}$ クロックの到来を $1/201.3\text{GHz} = 4.96\text{ps}$ の精度で計測する必要があります。 $f_{s\_OUT}$ 周期を周波数 $201.3\text{GHz}$ のクロックで計測することは明らかに不可能です。代わりに、 $f_{s\_OUT}$ クロック周期を粗い精度で何回か計測し、時間平均をとります。

上の手法でのもう1つの難しさは、必要とされる係数の数です。64タップFIRフィルタで $2^{20}$ 回のコンボリューションが実行されるため、各タップに対して $2^{20}$ 個の多位相係数が必要になり、合計 $2^{26}$ 個の係数が必要となります。ROM内の係数の数を減らすため、AD1895では少ないサブセットの係数を記憶しておき、記憶している係数間での高次補間を実行します。上の手法は、 $f_{s\_OUT} > f_{s\_IN}$ の場合に有効です。ただし、出力サンプル・レート $f_{s\_OUT}$ が入力サンプル・レート $f_{s\_IN}$ より低い場合は、ROM開始アドレス、入力データ、コンボリューションの長さを調整する必要があります。入力サンプル・レートが出力サンプル・レートより高くなるにつれて、アンチエリアス・フィルタのカットオフ周波数を下げる必要があります。これは出力サンプルのナイキスト周波数が

入力サンプルのナイキスト周波数より低くなるためです。アンチエリアス・フィルタのカットオフ周波数を移動するには、係数を動的に変更して、コンボリューションの長さを $(f_{s\_IN} / f_{s\_OUT})$ の係数で長くする必要があります。この技術は $f(t) \rightarrow F(\cdot)$ のとき、 $f(kxt) \rightarrow F(\cdot / k)$ になるというフーリエ変換の性質に基づいています。したがって、デシメーションの範囲は単純にRAMのサイズによって制限されます。

## サンプル・レート・コンバータのアーキテクチャ

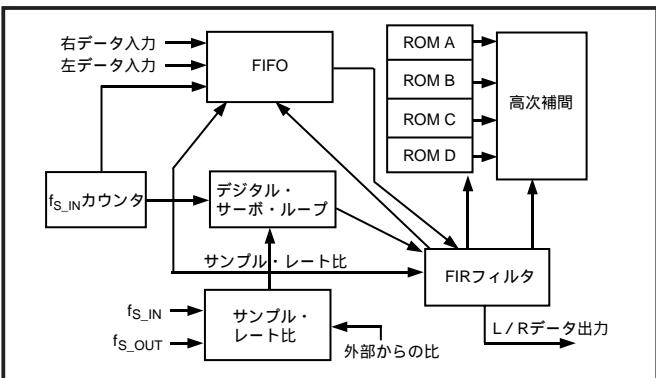

サンプル・レート・コンバータのアーキテクチャを図7に示します。サンプル・レート・コンバータのFIFOブロックでは、"L"と"R"の入力サンプルを調整してFIRフィルタのコンボリューション・サイクル用に記憶しておきます。 $f_{s\_IN}$ カウンタからは、FIFOブロックには書き込みアドレスを、デジタル・サーボ・ループにはランプ入力を出力します。ROMはFIRフィルタ・コンボリューションの係数を記憶し、記憶された係数間で高次補間を実行します。サンプル・レート比ブロックでは、ROM係数の動的な変更、入力データおよびFIRフィルタ長のスケーリングのためにサンプル・レートを計測します。デジタル・サーボ・ループでは、 $f_{s\_IN}$ と $f_{s\_OUT}$ のサンプル・レートを自動的に追いかけ、FIRフィルタ・コンボリューションの開始に必要なRAMとROMの開始アドレスを発生します。

図7. サンプル・レート・コンバータのアーキテクチャ

FIFOは"L"と"R"の入力データを受取り、サンプル・レート・コンバータのソフト・ミューティングおよびサンプル・レート比による入力データのスケーリングの両方のためにデータの振幅を調整してから、サンプル値をRAMに書き込みます。コンボリューションのFIRフィルタ長が長くなるにつれて、コンボリューション出力の振幅も大きくなるため、入力データはサンプル・レート比でスケーリングします。FIRフィルタ出力が飽和しないようにするために、 $f_{s\_OUT} < f_{s\_IN}$ の場合、入力データに $(f_{s\_OUT} / f_{s\_IN})$ を乗算してスケールダウンします。FIFOはAD1895のミューティングとミューティング解除の入力データもスケーリングします。

FIFO内のRAMは、"L"と"R"の両チャンネルに対して深さ512ワードです。小さなオフセット値16を $f_{s\_IN}$ カウンタからの書き込みアドレスに加算して、RAM読み出しポインタが書き込みアドレスと一致しないようにしています。最大デシメーション・レートは、RAMワードの深さ(512-16) / 64タップ = 7.75と、小さいオフセット値を使って計算することができます。

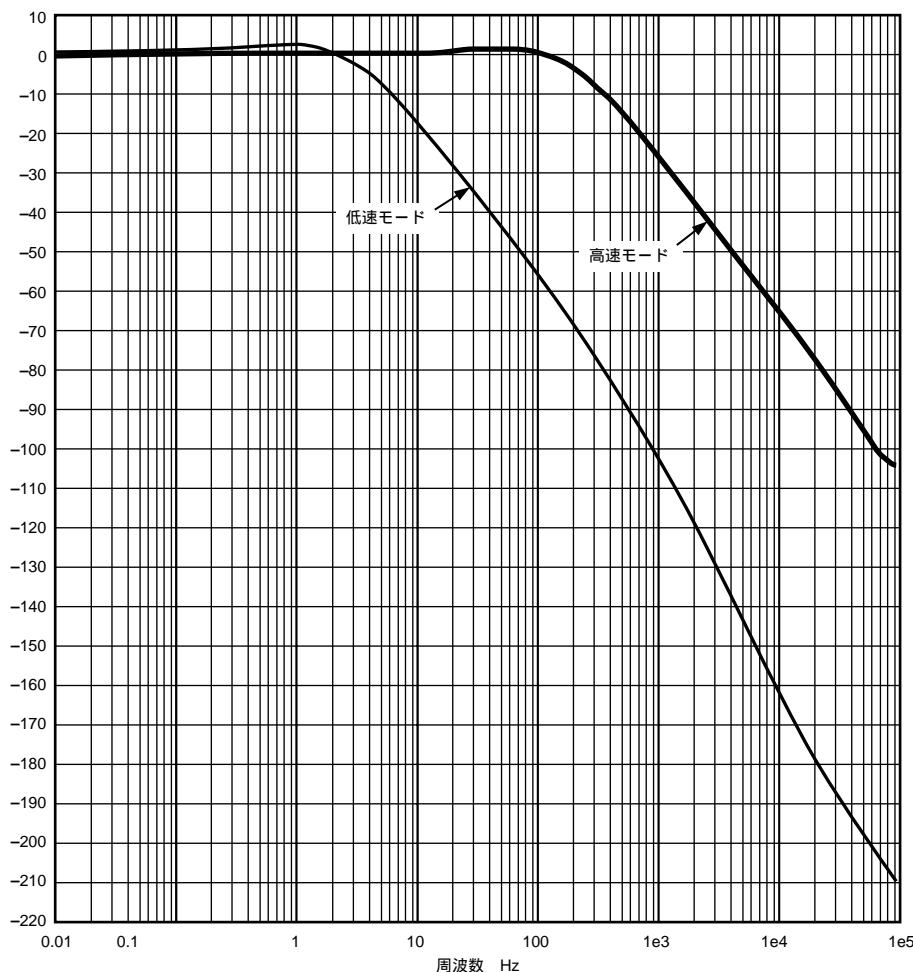

図8 デジタル・サーボ・ループの周波数応答。X軸は $f_{S\_IN}$ 、 $f_{S\_OUT} = 192\text{kHz}$ 、マスタークロック周波数は30MHz

デジタル・サーボ・ループは、FIRコンボリューションを開始させるRAMとROMのアドレスを指す初期ポインタを出力するランプ・フィルタです。RAMポインタはランプ・フィルタの整数値出力で、ROMの方は小数値です。デジタル・サーボ・ループは、 $f_{S\_IN}$ および $f_{S\_OUT}$ のクロックのジッタに對して優れた抑圧機能を持ち、かつ $f_{S\_OUT}$ クロックの到来を4.97 ps以内で計測できる必要があります。また、デジタル・サーボ・ループでは、 $f_{S\_IN} > f_{S\_OUT}$ の場合、ROM係数を動的に変更するため、ランプ出力の小数部を $f_{S\_IN} / f_{S\_OUT}$ 比で除算します。

デジタル・サーボ・ループは、マルチレート・フィルタで構成されます。起動時またはサンプル・レート変更時にデジタル・サーボ・ループ・フィルタを迅速に整定させるため、“高速モード”がフィルタに追加されています。デジタル・サーボ・ループの起動時またはサンプル・レートの変更時には、デジタル・サーボ・ループは新しいサンプル・レートに追従して整定するため“高速モード”に入ります。デジタル・サーボ・ループがある値にまで小さくなつたことが検出されると、デジタル・サーボ・ループは“ノーマル”すなわち“低速モード”に入ります。“高速モード”では、サンプル・レート・コンバータのMUTE\_OUT信号がアサートされて、クリック音などを発生させないようにサンプル・レート・コンバータをミュートさせなければいけないことが知らされます。“高速モード”と“低速モード”で

のデジタル・サーボ・ループの周波数応答を図8に示します。

FIRフィルタは $f_{S\_OUT} < f_{S\_IN}$ の場合は64タップ・フィルタに、 $f_{S\_IN} > f_{S\_OUT}$ の場合には $(f_{S\_IN} / f_{S\_OUT}) \times 64$ タップになります。FIRフィルタは、 $f_{S\_OUT}$ 周期の先頭で、デジタル・サーボ・ループからRAMアドレス・ポインタとROMアドレス・ポインタの開始アドレスを受け取って、コンボリューションを開始します。FIRフィルタは各タップについて、RAMポインタではアドレスを1ずつ減らしながら、ROMポインタでは、 $f_{S\_IN} > f_{S\_OUT}$ の場合には $(f_{S\_OUT} / f_{S\_IN}) \times 2^{20}$ 比だけ、 $f_{S\_OUT} < f_{S\_IN}$ の場合には $2^{20}$ だけ、アドレスを増やしながら処理を実行します。ROMアドレスがロールオーバーすると、コンボリューションが完了します。コンボリューションはL/R両チャンネルに対して実行され、コンボリューション用の積和回路は両チャンネル間で共用されます。

$f_{S\_IN} / f_{S\_OUT}$ サンプル・レート回路は、 $f_{S\_IN} > f_{S\_OUT}$ の場合にROM内の係数を動的に変更するのに使われます。この比率は、 $f_{S\_OUT}$ カウンタ出力と $f_{S\_IN}$ カウンタ出力を比較して計算されます。 $f_{S\_OUT} > f_{S\_IN}$ なら、この比の値は1に維持されます。 $f_{S\_IN} > f_{S\_OUT}$ なら、前回の $f_{S\_OUT}$ と $f_{S\_IN}$ の比較に比べて $f_{S\_OUT}$ 周期の2倍以上の差が発生したときに、サンプル・レート比が更新されます。この機能は、フィルタ長が発振や歪みを起こすのを防止するためのヒステリシスを与えるために実行されます。

## 動作機能

### リセットとパワーダウン

RESETがロー・レベルにアサートされると、AD1895はマスター・クロック入力MCLK\_Iをターンオフして、全内部レジスタをデフォルト値に初期化し、全I/Oピンをスリー・ステートにします。RESETがアクティブ・ローの間、AD1895の消費電力は最小になります。RESETがアクティブ・ローの間の消費電力を最小にするには、AD1895のすべての入力ピンは固定レベルでなければなりません。

RESETのアサートが解除されると、AD1895は初期化ルーチンを起動します。初期化ルーチンでは、FIFO内の全ロケーションがゼロに初期化され、MUTE\_OUTがハイ・レベルにアサートされて、出力に設定されたすべてのI/Oピンがイネーブルされます。入力サンプルのソフト・ミュート減衰量を制御するミュート・コントロール・カウンタは、最大減衰量-127dBに初期化されます（ミュート制御の節を参照）。RESETをアサートおよびアサート解除するときは、最小5MCLK\_Iサイクルの間、RESETをロー・レベルに維持する必要があります。パワーアップ時は、電源が安定するまでRESETをロー・レベルに維持する必要があります。

### 電源と電圧リファレンス

AD1895は、入力ピンでの5V入力を許容する3V動作向け設計です。VDD\_COREは3V電源で、AD1895のコア・ロジックへの電源および出力ピンの駆動に使用されます。VDD\_IOは、入力ピンの入力電圧偏差を設定するために使用します。入力ピンを5V入力に対応させるには、VDD\_IOを5V電源に接続しなければなりません。入力ピンが5V入力に対応の必要がない場合は、VDD\_IOをVDD\_COREに接続しておくことができます。VDD\_IOにVDD\_COREより低い電圧を加えることはできません。VDD\_COREとVDD\_IOには、ピンのできるだけ近くにバイパス用の100 nFのセラミック・チップ・コンデンサを接続して、パターンのインダクタンスに起因する電源とグラウンドのバウンスを最小にする必要があります。AD1895が実装されるPCボードには、47 μFのパルク・アルミニウム電解コンデンサも接続する必要があります。

### デジタル・フィルタの群遅延

フィルタの群遅延は、次式で与えられます。

$$GD = \frac{16}{f_{s\_IN}} + \frac{32}{f_{s\_IN}} \text{ seconds for } f_{s\_OUT} > f_{s\_IN}$$

$$GD = \frac{16}{f_{s\_IN}} + \left( \frac{32}{f_{s\_IN}} \right) \times \left( \frac{f_{s\_IN}}{f_{s\_OUT}} \right) \text{ seconds for } f_{s\_OUT} < f_{s\_IN}$$

### ミュート・コントロール

MUTE\_INピンがハイ・レベルにアサートされると、MUTE\_INコントロールはAD1895 FIFOへの入力データをほぼゼロに直線的に減少させて（減衰量-127dB）、ソフト・ミュートを実行します。MUTE\_INがロー・レベルになりアサートが解除されると、MUTE\_INコントロールは入力データの減衰量を0dBまで直線的に減らします。LRCLK\_Iでクロック駆動される12ビット・カウンタを使って、ミュート減衰量を制御します。このため、MUTE\_INのアサートから完全なミュート減衰量-127dBに達するまでに要する時間は、4096 / LRCLK\_I秒になります。同様に、MUTE\_INのアサート解除からミュート減衰量が0dBに到達するまでに要する時間も4096 / LRCLK\_I秒になります。

RESETの発生、またはLRCLK\_IとLRCLK\_Oの間のサンプル・レートの変更により、MUTE\_OUTピンがハイ・レベルにアサートされます。MUTE\_OUTピンは、デジタル・サーボ・ループ内部の高速セトリング・モードが終わるまで、ハイ・レベルを維持します。デジタル・サーボ・ループが低速セトリング・モードに切り替えられると、MUTE\_OUTピンのアサートが解除されます。MUTE\_OUTがアサートされている間、オーディオ出力サンプルに大きな歪みを発生させないために、MUTE\_INピンもアサートしておく必要があります。

### マスター・クロック

MCLK\_Iピンに接続したデジタル・クロック、またはMCLK\_IとMCLK\_Oの間に接続した水晶の基本波または3次高調波を使って、マスター・クロックMCLK\_Iを生成することができます。MCLK\_Iピンは、他のAD1895入力ピンと同様に5V入力対応ピンにすることができます。MCLK\_IとMCLK\_Oの間に基本波モードの水晶を接続して、最大27MHzまでのマスター・クロック周波数を発生することができます。水晶を使って、27MHzを超えるマスター・クロック周波数を発生させる場合は、3倍オーバートーン水晶を使用し、かつ基本波を除去するLCフィルタをMCLK\_Oの出力に接続する（基本波のノッチ・フィルタを使用しない）ようにお薦めします。外付けコンデンサとインダクタの値については、水晶メーカーにご相談ください。

図9a. 基本波モードの回路構成

図9b. 3次高調波の回路構成

AD1895のマスター・クロックには動作周波数の最大値と最小値があります。AD1895の動作を保証するマスター・クロックの最大周波数は30MHzです。30MHzは、サンプリング周波数192kHz + 12%のレート変換をサンプルするには十分過ぎる値です。AD1895のマスター・クロックの最小周波数は、入力および出力サンプル・レートに依存します。マスター・クロックは、最大入力または最大出力サンプル・レートの少なくとも138倍である必要があります。

# AD1895

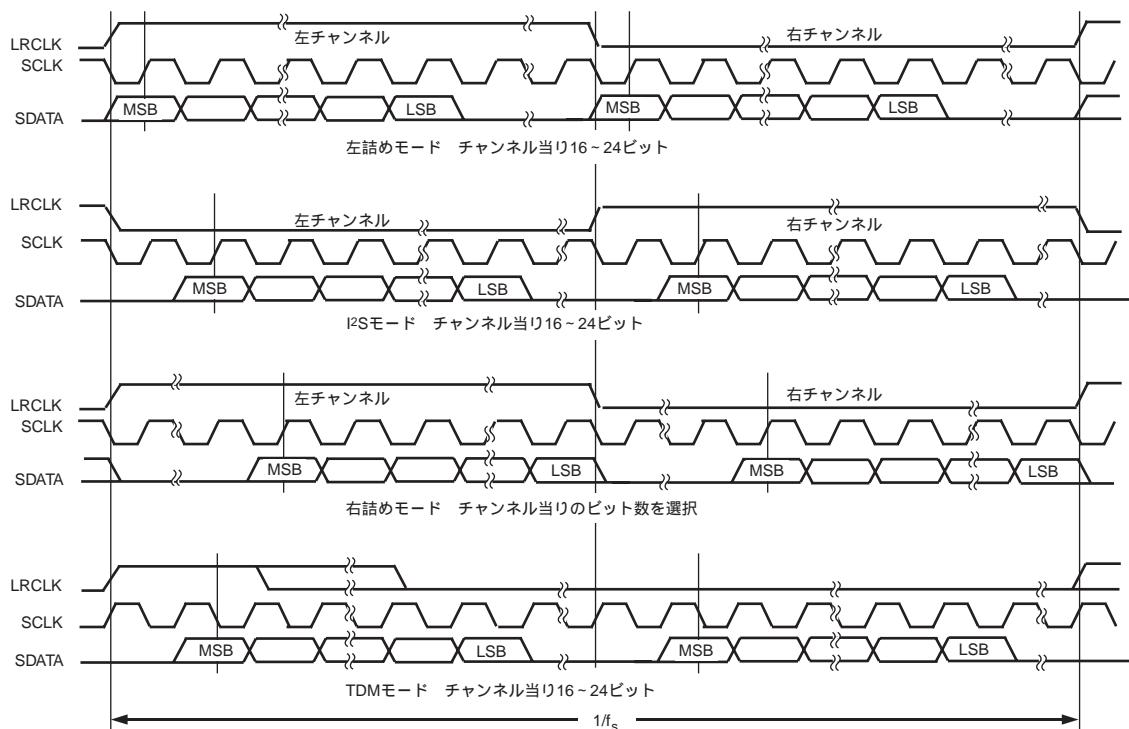

シリアル・データ・ポート データ・フォーマット

シリアル・データ入力ポートのモードは、SMODE\_IN\_0 / 1 / 2ピンのロジック・レベルで設定され、左詰め、I<sup>2</sup>S、右詰め (RJ)、16、18、20、または24ビットが使用できます (表I)。

表I シリアル・データ入力ポートのモード

| SMODE_IN_[0 : 2] |   |   | インターフェース・フォーマット  |

|------------------|---|---|------------------|

| 2                | 1 | 0 |                  |

| 0                | 0 | 0 | 左詰め              |

| 0                | 0 | 1 | I <sup>2</sup> S |

| 0                | 1 | 0 | 未定義              |

| 0                | 1 | 1 | 未定義              |

| 1                | 0 | 0 | 右詰め、16ビット        |

| 1                | 0 | 1 | 右詰め、18ビット        |

| 1                | 1 | 0 | 右詰め、20ビット        |

| 1                | 1 | 1 | 右詰め、24ビット        |

シリアル・データ出力ポートのモードは、SMODE\_OUT\_0 / 1ピンとWLNGTH\_OUT\_0 / 1ピンのロジック・レベルで設定されます。シリアル・モードは、左詰め、I<sup>2</sup>S、右詰めまたはTDMに変更することができます (表II参照)。出力ワード幅は、WLNGTH\_OUT\_0 / 1ピンを使って設定することができます (表III)。出力ワード幅が24ビット未満の場合は、

余ったビットにディザイナが詰め込まれます。右詰めシリアル・データ出力モードでは1フレーム当たり64 SCLK\_Oサイクル (左と右で均等使用) として扱います。

表II シリアル・データ出力ポートのモード

| SMODE_OUT_[0 : 2] |   | インターフェース・フォーマット  |

|-------------------|---|------------------|

| 1                 | 0 |                  |

| 0                 | 0 | 左詰め (LJ)         |

| 0                 | 1 | I <sup>2</sup> S |

| 1                 | 0 | TDMモード           |

| 1                 | 1 | 右詰め (RJ)         |

表III ワード幅

| WLNGTH_OUT_[0 : 1] |   | ワード幅  |

|--------------------|---|-------|

| 1                  | 0 |       |

| 0                  | 0 | 24ビット |

| 0                  | 1 | 20ビット |

| 1                  | 0 | 18ビット |

| 1                  | 1 | 16ビット |

シリアル・モード・フォーマットのタイミング図を、次に示します。

## 注

1 LRCLKは通常、対応する入力または出力サンプル周波数 ( $f_s$ ) で動作します。

2 SCLK周波数は通常  $64 \times LRCLK$  です。ただし、TDMモードでは  $N \times 64 \times f_s$  です。ここで、 $N$  = TDMチェーン内のステレオ・チャンネル数で、マスター・モードでは  $N = 4$  です。

図10. 入力 / 出力シリアル・データのフォーマット

## TDMモードのアプリケーション

TDMモードでは複数のAD1895をディジーチェーン接続して、SHARC® DSPのシリアル入力ポートに接続することができます。AD1895は、64ビット・パラレルロードシフトレジスタを内蔵しています。LRCLK\_Oパルスが到着すると、各AD1895は"L"と"R"のデータを64ビット・シフトレジスタにパラレル・ロードします。シフトレジスタの入力はTDM\_INに、出力はSDATA\_Oに接続されています。SDATA\_Oを次のAD1895のTDM\_INに接続することにより、

SCLK\_Oクロック駆動の大規模なシフトレジスタを構成できます。

ディジーチェーン接続可能なAD1895の数は、SCLK\_Oの最大周波数で制限されますが、この最大周波数は約25MHzです。例えば、出力サンプル・レート $f_s$ が48kHzの場合には、 $512 \times f_s < 25\text{MHz}$ であるため、最大8個のAD1895を接続できます。マスター / TDMモードでは、ディジーチェーン接続可能なAD1895の数は4個に固定されています。

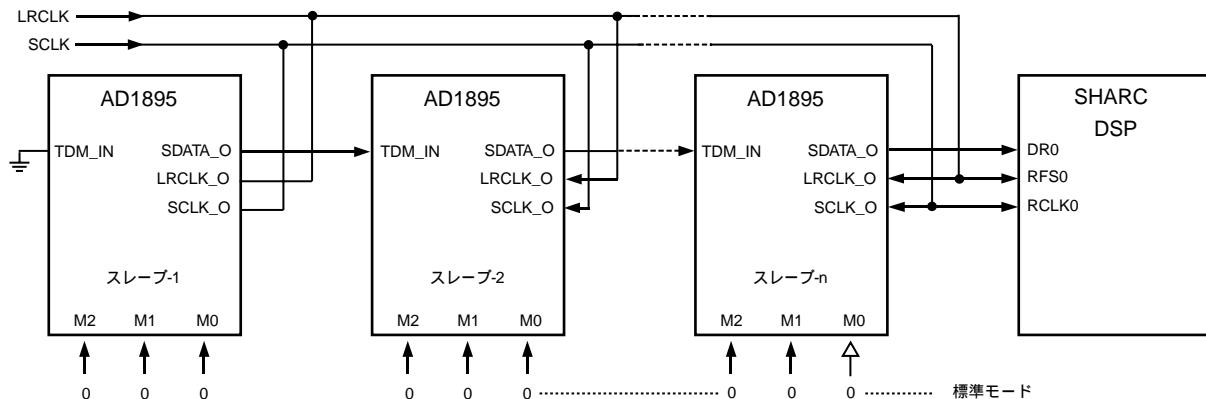

図11. TDMモードでのディジーチェーン構成（すべてのAD1895がクロック・スレーブ）

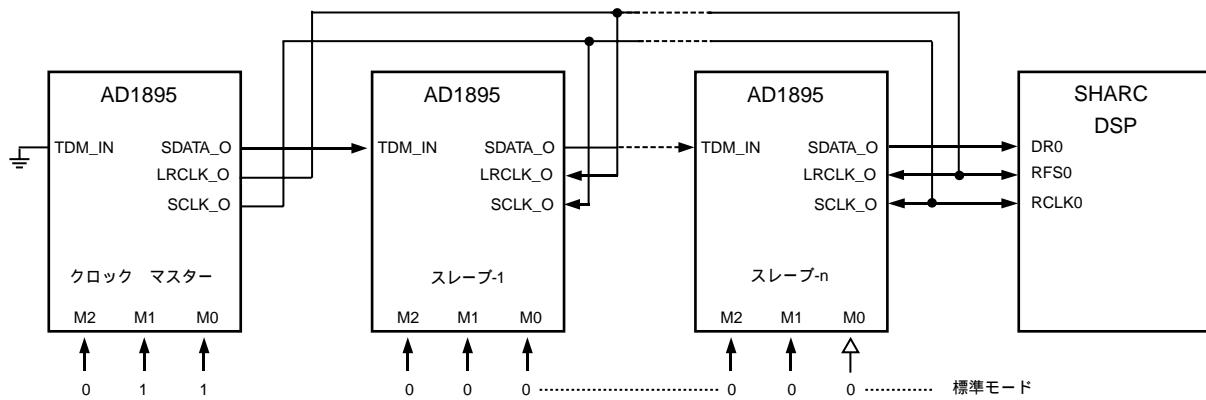

図12. TDMモードでのディジーチェーン構成（先頭のAD1895がクロック・マスター）

# AD1895

シリアル・データ・ポートのマスター・クロック・モード

AD1895のシリアル・ポートのどれかを、マスター・シリアル・データ・ポートに設定できます。ただし、マスターのシリアル・ポートは1つだけで、他はすべてスレーブにする必要があります。マスター・モードでは、AD1895は $256 \times f_s$ 、 $512 f_s$ または $768 \times f_s$ のマスター・クロック (MCLK\_I) を必要とします。最大マスター・クロック周波数30MHzの場合は、最大サンプル・レートは96kHzに制限されます。スレーブ・モードでは、最大192kHzまでのサンプル・レートを処理できます。

いずれかのシリアル・ポートがマスター・モードで動作する場合、マスター・クロックが分周されて、対応するL/Rのサブフレーム・クロック (LRCLK) とシリアル・ビット・クロック (SCLK) が生成されます。マスター・クロック周波数としては、入力または出力サンプル・レートの256倍、512倍または768倍を選択できます。入力シリアル・ポートと出力シリアル・ポートは両方とも、全シリアル・モード (左詰め、I<sup>2</sup>S、右詰め) と出力シリアル・ポートのTDMに対するマスター・モードLRCLKとSCLKの発生をサポートします。

表IV シリアル・データ・ポートの各クロック・モード

| MMODE_0/1/2 |   |   | インターフェース・フォーマット                        |

|-------------|---|---|----------------------------------------|

| 2           | 1 | 0 |                                        |

| 0           | 0 | 0 | 両シリアル・ポートがスレーブ・モード                     |

| 0           | 0 | 1 | 出力シリアル・ポートがマスター、 $768 \times f_s$ _OUT |

| 0           | 1 | 0 | 出力シリアル・ポートがマスター、 $512 \times f_s$ _OUT |

| 0           | 1 | 1 | 出力シリアル・ポートがマスター、 $256 \times f_s$ _OUT |

| 1           | 0 | 0 | 未定義                                    |

| 1           | 0 | 1 | 入力シリアル・ポートがマスター、 $768 \times f_s$ _IN  |

| 1           | 1 | 0 | 入力シリアル・ポートがマスター、 $512 \times f_s$ _IN  |

| 1           | 1 | 1 | 入力シリアル・ポートがマスター、 $256 \times f_s$ _IN  |

## バイパス・モード

BYPASSピンがハイ・レベルにアサートされると、入力データはサンプル・レート・コンバータを通過せずに、シリアル出力ポートに直接出力されます。ワード長が24ビット未満に設定されている場合の出力データのディザ処理は、ディスエーブルされます。このモードは、入力と出力のサンプル・レートが等しく、かつLRCLK\_IとLRCLK\_Oが互いに同期している場合に最適です。このモードは入力データに対して処理を行わないため、非AUDIOデータを通過させるときにも使用できます。

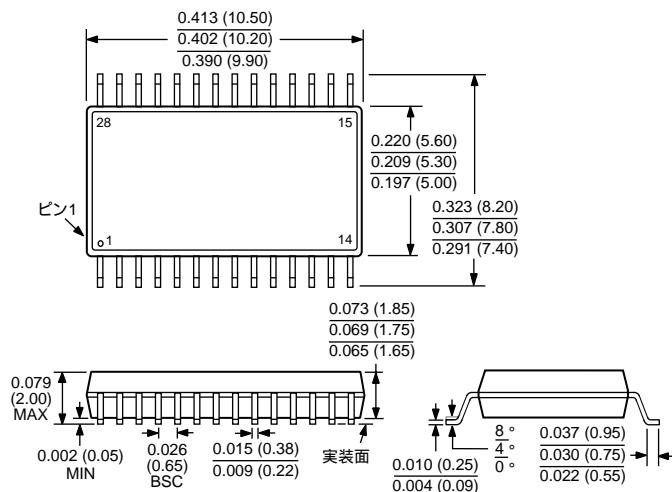

## 外形寸法

サイズはインチと (mm) で示します。

28ピン・シュリンク・スマール・アウトライン・パッケージ (SSOP)

(RS-28)

# AD1895

TDS07/2001/1000

PRINTED IN JAPAN

このデータシートはエコマーク認定の再生紙を使用しています。

24

REV.0