## アプリケーション・ノート

## ADF4360-7 を高い PFD 周波数で使用

**著者: Patrick Walsh、Mike Baker**

## はじめに

**ADF4360-7** は非常に柔軟なシンセサイザ（電圧制御発振器（VCO）付きフェーズロック・ループ（PLL））で、350MHz～1800MHzの周波数を生成することができます。起動後は、オンチップ校正エンジンが出力周波数の高精度チューニングを行います。校正プロセスはほとんどの動作条件下で良好に機能しますが、タイミング上の不確実性誤差が発生する可能性があり、この結果、位相ノイズ性能やスプリアス性能を低下させるチューニング誤差が発生します。このアプリケーション・ノートでは、比較的高いPFD（位相周波数検出器）周波数でデバイスを動作させる場合に最高の性能を維持する方法について述べます。

## 背景

RF設計者は、位相ノイズ性能を向上させるために、PFD周波数を最大限にしようとする傾向があります。ほとんどの場合、PFD周波数を最大限にすることは望ましいことなのですが、規定された動作パラメータの範囲外で ADF4360-7 を動作させてしまうことがあります。

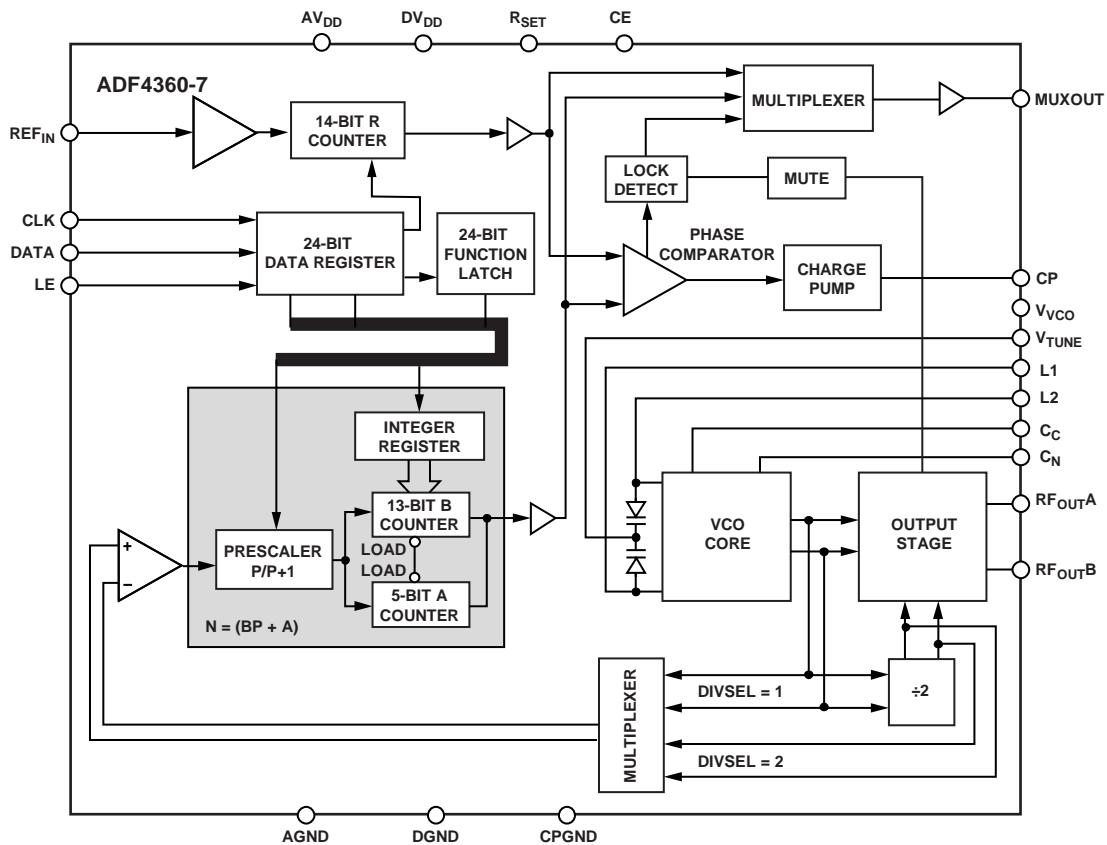

ADF4360-7 のブロック図を図 1 に示します。リファレンス入力 REF<sub>IN</sub> は、PFD 周波数を生成する 14 ビット R カウンタによって 分周されます。VCO の出力は N カウンタに戻され、そこで分周されます。R カウンタと N カウンタの出力は位相コンパレータに 送られます。PLL は位相誤差をゼロにすることによってループ を閉じます。

図 1. ADF4360-7 のブロック図

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料はREV03が古い場合があります。最新の内容については、英語版をご参照ください。

アナログ・デバイセズの PLL シミュレーション・ソフトウェア **ADIsimPLL** は、R レジスタと N レジスタの値、ループ・フィルタ部品の値、ノイズ指数、回路図、その他さまざまなデータを生成します。ADF4360-7 には外付けのインダクタが必要ですが、**ADIsimPLL** を使用すればこれらの値も得られます。

出力周波数を求めるための基本式は次の通りです。

$$f_{OUT} = \frac{1}{2\pi\sqrt{6.2\text{pF}(0.9\text{nH} + L_{EXT})}}$$

ここで、

$f_{OUT}$  は中心周波数、

$L_{EXT}$  はインダクタ値です。

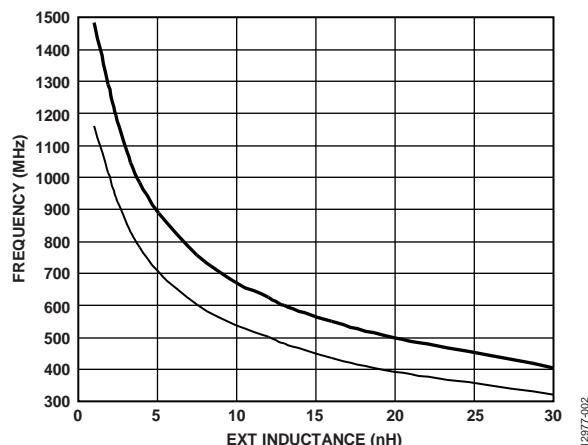

ADF4360-7 の周波数とインダクタンスの関係を図 2 に示します。このプロットが示すように、各インダクタンス値は約 100MHz の周波数範囲を生成できます。**ADIsimPLL** は、計算により目的の周波数がこれら 2 本の線の中央に位置するように部品の値を選びます。内部校正エンジンは、このポイントから、目的の出力周波数が得られるまで VCO をチューニングします。たとえば 24nH のインダクタは通常 405MHz の周波数を生成しますが、これは 350MHz から 450MHz までの範囲のほぼ中央です。

図 2. 外部インダクタンス 対 出力中心周波数

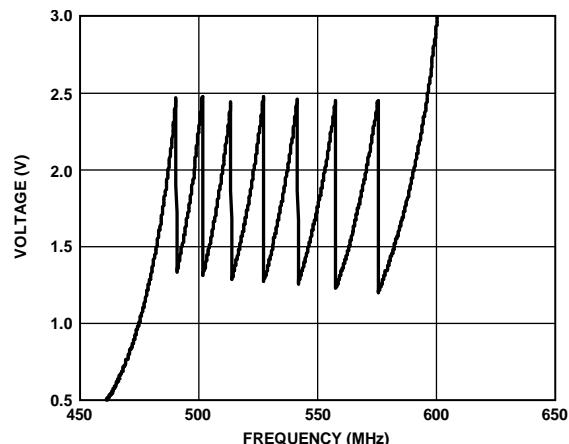

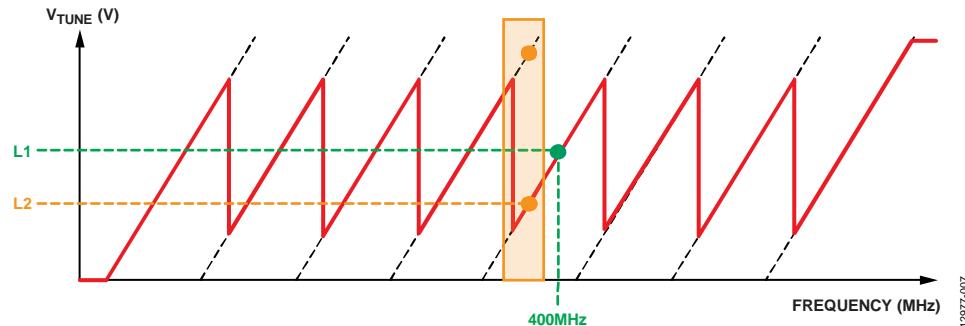

100MHz という比較的広いチューニング範囲は、図 3 に示す 8 つのチューニング・バンドを使用するによって可能になります。インダクタの選択同様、**ADIsimPLL** は、ほぼ中央のチューニング・バンドであるバンド 4 またはバンド 5（左から数えた場合）を選択して、チューニング電圧を 1.875V とします。この水平および垂直のセンタリングが、最大限の柔軟性を備えた校正エンジンを実現します。

最大限の性能を維持するには、どのバンド内でも  $V_{TUNE}$  を 1.25V ~2.5V の範囲に制限する必要があります。これらの制限値を超える場合もあり得ますが、制限値を超えると、出力周波数が不正確になったりスプリアス性能が低下したりします。

図 3.  $V_{TUNE}$  対 周波数

## 校正プロセス

デバイスが周波数校正を行う場合、デバイスは、目的の出力周波数にとってどの VCO バンドが最適のバンドかを決定します。これに続き、通常のクローズド・ループ PLL 動作で  $V_{TUNE}$  の調整が行われて、正しい周波数にロックされます。

校正プロセスの間、分周された VCO 周波数 ( $f_{VCO}/((PB + A) \times BSC)$ ) と、同じく分周された PFD リファレンス周波数 ( $f_{PFD}/BSC$ ) が比較されます。プリスケーラは VCO によってクロックされながら、同期リセットが行われないため、分周された VCO 周波数には常に  $P \times VCO$  サイクルの不確実性が存在します。

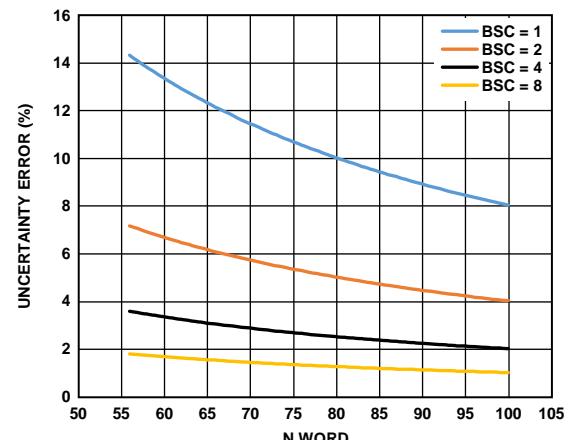

N ワード ( $PB + A$ ) がすべての BSC 分周器の設定により変化するときの、8 のプリスケーラ値に対するこの不確実性誤差を図 4 に示します。

図 4. N ワード 対 不確実性誤差

不確実性誤差は出力周波数の誤差として現れます。このアプリケーション・ノートでは、不確実性誤差を説明するためにひとつの設計例を示します。

低 RF 周波数で動作させると、この不確実性誤差のペーセント値を最小限に抑えるために、BSC 値をできるだけ大きく、PFD 周波数をできるだけ低くします。

たとえば、VCO 周波数が 400MHz で  $P = 8$  の場合、プリスケーラの出力は 50MHz です。したがって、校正回路を駆動する  $P_{OUT}$  と、PFD に送られる N カウンタ出力の次の立ち上がりエッジの間には、 $1/50\text{MHz} = 20\text{ns}$  の不確実性が存在します。

逐次比較回路が適切なバンドを選ぶには5クロック周期を要します。校正クロック周期は次式で定義され、BSCは1、2、4、8の各値にプログラムできます。

$$\text{校正クロック周期} = (1/R_{CLOCK}) \times BSC$$

前の例を続けると、Rクロック=5MHz、BSC=8の時の校正時間は1.6μsです。不確実性が上で求めた値と同じ20nsだとすると、不確実性誤差は次式で計算できます。

$$\text{不確実性誤差} = (20\text{ ns}/1.6\text{ }\mu\text{s}) \times 100\% = 1.25\%$$

目的の400MHzの出力周波数では、この不確実性誤差によって次の周波数誤差が発生します。

$$\begin{aligned}\text{周波数誤差} &= \text{不確実性誤差} \times f_{out} \\ &= 1.2\% \times 400\text{MHz} \\ &= 5\text{MHz}\end{aligned}$$

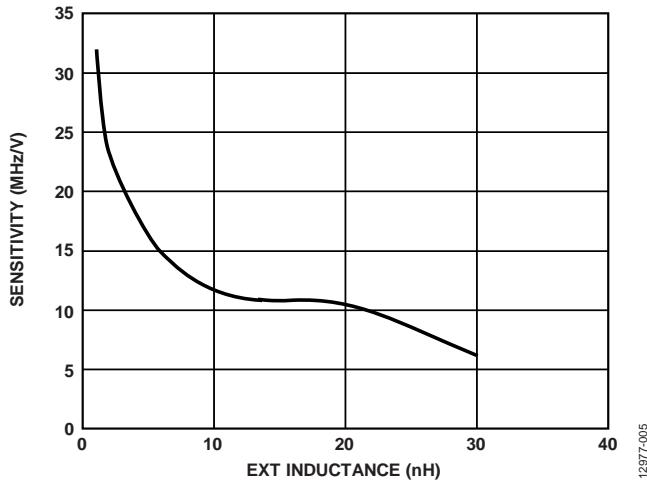

この例をさらに一步進めます。図5を参照してください。400MHzの出力に対し、ADIsimPLLは24nHのインダクタ値が必要だという結果を示します。このインダクタンスに対するVCO感度Kvは、約7.5Hz/Vです。

図5. インダクタンス対チューニング感度

周波数誤差をKvで割ると、V<sub>TUNE</sub>誤差電圧の大きさが得られます。

$$V_{TUNE} \text{ 誤差} = 5 \text{ MHz} \div 7.5 \text{ MHz/V} = 0.67 \text{ V}$$

図7. V<sub>TUNE</sub> チューニング曲線

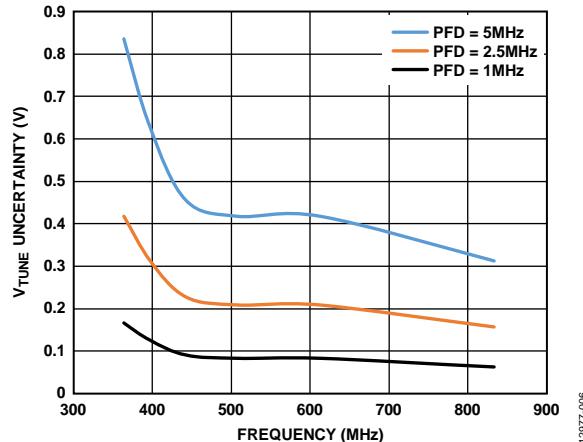

V<sub>TUNE</sub>誤差電圧は、目的のV<sub>TUNE</sub>電圧を1.25V~2.5Vに規定された制限値を超えて駆動する可能性があります。このV<sub>TUNE</sub>誤差電圧とRF周波数およびPFD周波数の関係を図6に示します。

図6. V<sub>TUNE</sub> 誤差

1つの周波数バンドが隣接バンドとオーバーラップする様子を図7に示します。24nHのインダクタにより400MHzの出力周波数が生成されます。理想的な設計では、これは図7に示すL1インダクタです。V<sub>TUNE</sub>を調整して出力周波数を高精度チューニングする際、V<sub>TUNE</sub>は同じバンド内と1.25V~2.5Vの制限範囲内に止まりながら曲線上を上下に移動します。

出力周波数は、部品の誤差によって中心から外れことがあります。校正エンジンはV<sub>TUNE</sub>電圧を調整してこれを補償しようとしていますが、これは、V<sub>TUNE</sub>誤差電圧のためにより難しくなる可能性があります。実際のインダクタでは、周波数がL2で示された位置になることがあります(図7参照)。L2はバンド5にあります。下限値である1.25Vに近くなっています。校正回路内に不確実性誤差がある状態では、校正回路がバンド4を選択しようとする可能性がありますが、この場合、V<sub>TUNE</sub>が上限値の2.5Vを超えることになります。また、V<sub>TUNE</sub>がV<sub>DD</sub>レールに近くなった場合はチャージ・ポンプの性能が低下し、それによって出力周波数性能が悪影響を受けます。

このことは、ADF4360-7のV<sub>TUNE</sub>電圧を1.25V~2.5Vの範囲内に止めるためには、入力REFIN、fout、およびR、N、BSCの各カウンタ値のすべてを考慮する必要があることを示しています。

## V<sub>TUNE</sub>に関する問題の回避

ADF4360-7 データシートの性能仕様は、1.25V～2.5V に規定された V<sub>TUNE</sub>範囲で使用することを前提としています。この範囲を外れて V<sub>TUNE</sub> が V<sub>DD</sub> より 1.0V～0.6V 低い状態で校正回路を作成させると、チャージ・ポンプの適合範囲を外れるので性能が低下し、スプリアスや位相ノイズが増加する結果となります。これらの値を使い、R カウンタと N カウンタの限界値を、REF<sub>IN</sub>、K<sub>V</sub>、RCOUNT、P、および BSC の関数として定めることができます。

すでに示したように、P<sub>OUT</sub> と A および B カウンタの間には、非同期クロッキングによる不確実性誤差が存在します。この不確実性は次式により計算できます。

$$V_{TUNE} \text{ Error Voltage} = \frac{P \times REF_{IN}}{R_{COUNT} \times BSC \times K_V}$$

ここで、

P はプリスケーラ値、

REF<sub>IN</sub> は入力リファレンス周波数、

RCOUNT は R カウンタ、

BSC はバンド選択分周器、

K<sub>V</sub> は PLL 感度です。

目的の V<sub>TUNE</sub> の動作範囲は 1.25V～2.5V です。しかし、ある程度の性能低下はあるものの、デバイスは V<sub>TUNE</sub> が 1.0V から V<sub>DD</sub> - 0.6V の範囲であっても動作します。下限値から検討を始めると、V<sub>TUNE</sub> 誤差電圧を V<sub>TUNE</sub> 下限値から減じた場合、その差は 1V より大きくなればなりません。この差は次式で表すことができます。

$$1.0V < 1.25V - \frac{P \times REF_{IN}}{R_{COUNT} \times BSC \times K_V}$$

この式を整理して RCOUNT について解くと、V<sub>TUNE</sub> の下限値をその動作範囲内に維持することのできる R の最小値が得られます。

$$R_{COUNT} > \frac{P \times REF_{IN}}{BSC \times K_V \times 0.25V}$$

先に挙げた例では、P = 8、REF<sub>IN</sub> = 10MHz、BSC = 8、K<sub>V</sub> = 7.5MHz/V です。これらの値を式に代入すると、RCOUNT ≥ 6 となります。

さらに、V<sub>TUNE</sub> が上限値を超えないような最小 R 値についても検討する必要があります。この場合は、V<sub>TUNE</sub> と V<sub>TUNE</sub> 誤差電圧の合計が V<sub>DD</sub> - 0.6V 未満でなければなりません。この合計値は次式で表されます。

$$VDD - 0.6V > 2.5V + \frac{P \times REF_{IN}}{R_{COUNT} \times BSC \times K_V}$$

これを RCOUNT について解くと、次式が得られます。

$$R_{COUNT} > \frac{P \times REF_{IN}}{BSC \times K_V \times (VDD - 3.1V)}$$

BSC、K<sub>V</sub>、P、および REF<sub>IN</sub> に同じ値を代入して V<sub>DD</sub> を 3.3V に設定すると、RCOUNT ≥ 7 という結果が得られます。V<sub>TUNE</sub> を適合範囲に維持するには、これら 2 つの RCOUNT 値のうちの大きい方の値（この場合は 7）を使用します。

さらに、N の値を次式で計算します。

$$N_{COUNTER} = VCO_{OUT} \times R_{COUNT}/REF_{IN}$$

R カウンタと N カウンタの値は、ADF4360-7 のデータシートに示すように、両方の値がこれらの値の限界値内となるように選択する必要があります。

この設計例では、R カウンタの値は 7 以上とする必要がありました。目的の 400MHz 出力について最小公倍数を考えると、R カウンタを 10、N カウンタを 400 (P = 8、A = 0、B = 50) とするのがひとつの選択肢であることがわかります。この場合の PFD 周波数は 1MHz です。これは ADIsimPLL によるソリューションと同じです。

## まとめ

最初に行なうことは、ADIsimPLL を使用して設計をシミュレーションすることです。このシミュレーションによって許容可能な設計が得られた場合、それ以上の作業は不要です。アナログ・デバイセズの評価用ボードを使って回路をテストすることにより、シミュレーションの検証を行ってください。ADIsimPLL の設計に変更が必要な場合に、不確実性誤差を最小に抑えて最大限の設計マージンを確保するための推奨事項は以下の通りです。

- 最高の位相ノイズ性能を実現するには R カウンタの値をできるだけ小さくしますが、V<sub>TUNE</sub> 誤差電圧を制限値内に維持できる程度の大きさにしてください。

- BSC を最大値にすると、校正時間が最大になり不確実性誤差が減少します。

- 不確実性誤差を減らすには、できるだけ小さいプリスケーラ値を使用します。

- V<sub>TUNE</sub> の誤差電圧のマージンを最大にするには、V<sub>DD</sub> の電圧値をできるだけ大きくします。

- RCOUNT の最小値を求めるための計算結果のどちらかが負の値になった場合、V<sub>TUNE</sub> を許容動作範囲内に維持することはできません。

- 最小公倍数 (LCM) プログラムは、N カウンタと R カウンタの整数値を見つける助けとなります。

## 改訂履歴

1/15—Revision 0:初版