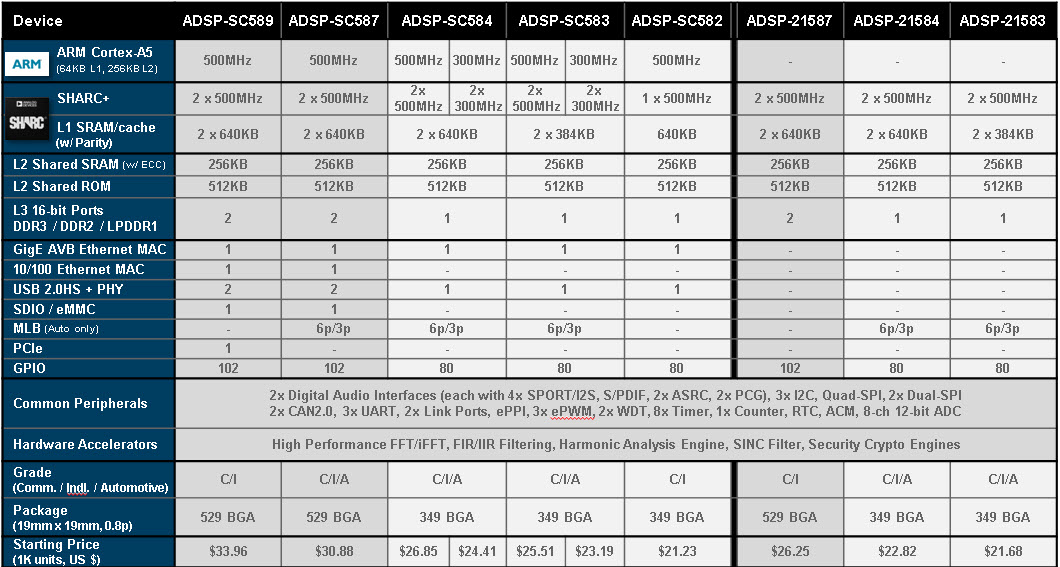

デュアル・コアSHARC+とARM Cortex-A5 SOC、デュアルDDR、2xイーサネット、2xUSB、PCIe、529ボールcspBGA

デュアル・コアSHARC+とARM Cortex-A5 SOC、デュアルDDR、2xイーサネット、2xUSB、PCIe、529ボールcspBGA

デュアル・コアSHARC+とARM Cortex-A5 SOC、デュアルDDR、2xイーサネット、2xUSB、SDIO、529ボールcspBGA

デュアル・コアSHARC+とArm Cortex-A5 SOC、DDR、イーサネット、USB、349ボールcspBGA

デュアル・コアSHARC+とARM Cortex-A5 SOC、DDR、イーサネット、USB、349ボールcspBGA

シングル・コアSHARC+とARM Cortex-A5 SOC、DDR、イーサネット、USB、349ボールcspBGA

デュアル・コア SHARC+ DSP、デュアルDDR、529ボールcspBGA

デュアル・コア SHARC+ DSP、DDR、349ボールcspBGA

BOMコストと基板面積を最適化するシングル・チップSOC

2Wでクラス最高の性能を発揮する低消費電力浮動小数点DSP

高集積・最適化の低消費電力ネットワーク接続エンジン(ADSP-SC58xシリーズのみ)

高度なリアルタイム浮動小数点信号処理を必要とするアプリケーションに最適

SHARCコアとコード互換である新しいSHARC+コアは、倍精度浮動小数点演算をサポート。また、バイトアドレッシング、予測分岐もサポートし、L1 SRAMはキャッシュとしても使用可能

暗号化アクセラレータとOTPメモリによる高度なセキュリティ機能

パリティまたはECC方式を実装したSRAMと障害管理ユニットで実現するデータの保護

さまざまなADSP-SC58x/ADSP-2158x製品群のバリエーション

使いやすい先進的な開発ツール

arm® Cortex®-A5コア用の組込みLinuxのサポート

CCESは、アナログ・デバイセズのBlackfin®、SHARC®、Arm®の各プロセッサ・ファミリ向けに用意された、世界トップクラスの統合開発環境(IDE)です。

ADSP-SC5xxプロセッサ・ファミリ向けのLinuxカーネルおよび開発ツール

アナログ・デバイセズのプロセッサ向けFreeRTOSは、アナログ・デバイセズのプロセッサ用のリアルタイム・オペレーティング・システムです。

HCC EmbeddedのTCP/IPスタックは、主要なプロトコルをすべて備え、IPv4とIPv6の両方をサポートしています。

HCC EmbeddedのUSBスタックは、幅広く使用されている成熟したスタックで、ほぼあらゆるUSB構成に対応しています。

HCC EmbeddedのFATシステムは、FAT 12/16/32準拠のメディアを製品に取り付ける必要のある組み込みアプリケーションで使用するために、全機能を装備し最適化されています。

オーディオ・アプリケーション用の拡張可能なハードウェア/ソフトウェア・プラットフォーム